(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6007796号

(P6007796)

(45) 発行日 平成28年10月12日(2016.10.12)

(24) 登録日 平成28年9月23日(2016.9.23)

(51) Int.Cl.

H01L 21/60 (2006.01)

F 1

H01L 21/60 311Q

請求項の数 2 (全 12 頁)

(21) 出願番号 特願2013-1853 (P2013-1853)

(22) 出願日 平成25年1月9日 (2013.1.9)

(65) 公開番号 特開2014-135354 (P2014-135354A)

(43) 公開日 平成26年7月24日 (2014.7.24)

審査請求日 平成27年1月29日 (2015.1.29)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 浅見 博

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 堀江 義隆

最終頁に続く

(54) 【発明の名称】回路基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

所定のチップが実装される実装領域のパターン及び絶縁膜の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記パターン上の前記チップの各端子が接続される接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内にはんだバンプを形成する第5の工程と、

前記レジストを除去し、前記パターン及び前記絶縁膜の表面が平坦化されている前記実装領域を露出する第6の工程と 10

を含む回路基板の製造方法。

## 【請求項 2】

前記はんだ粒子の表面がフラックスによりコーティングされており、

前記第5の工程を窒素雰囲気中で行う

請求項1に記載の回路基板の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本技術は、回路基板の製造方法に関し、特に、フリップチップ実装を行う場合に用いて

好適な回路基板の製造方法に関する。

【背景技術】

【0002】

従来、LSI等のチップを回路基板に実装する方法の1つとして、フリップチップ実装が用いられている。また、従来、フリップチップ実装の方法の1つとして、回路基板側にはんだバンプを形成し、チップ側の端子と接続する方法が用いられている（例えば、特許文献1、2参照）。回路基板にはんだバンプを形成することにより、チップの端子の先端にはんだバンプを形成する場合と比較して、回路基板のパターンの高さにバラツキが発生しても、チップを回路基板に低荷重で実装することが可能になる。

【0003】

10

また、特許文献1、2に記載の発明では、回路基板に形成するはんだバンプの位置や形状の精度を高める工夫がなされている。具体的には、特許文献1では、配線パターン上に他の部分より幅を広くした接続パッドを形成し、接続パッド上にはんだバンプを形成することが提案されている。また、特許文献2では、回路基板のパターンに粘着性皮膜を形成し、そこにはんだ粉末を付着させ、加熱することによりはんだバンプを形成することが提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許3420076号公報

20

【特許文献2】特許3362079号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1、2に記載の発明では、接続パッド又はパターンの形状に合わせてはんだバンプが形成されるため、それらの形状が異なると、はんだバンプの形状にバラツキが生じ、高さが均一にならない。そのため、フリップチップ実装時にチップの端子の一部をはんだバンプに接続することが困難になり、フリップチップ実装により製造される電子部品の品質が低下する。

【0006】

30

そこで、本技術は、フリップチップ実装により製造される電子部品の品質を向上させるようとするものである。

【課題を解決するための手段】

【0010】

本技術の一側面の回路基板の製造方法は、所定のチップが実装される実装領域のパターン及び絶縁膜の表面を平坦化する第1の工程と、前記実装領域をレジストで覆う第2の工程と、前記パターン上の前記チップの各端子が接続される接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、前記はんだ粒子を溶かし、前記開口内にはんだバンプを形成する第5の工程と、前記レジストを除去し、前記パターン及び前記絶縁膜の表面が平坦化されている前記実装領域を露出する第6の工程とを含む。

40

【0011】

前記はんだ粒子の表面がフラックスによりコーティングし、前記第5の工程を窒素雰囲気中で行うようにすることができる。

【0015】

本技術の一側面においては、所定のチップが実装される実装領域のパターン及び絶縁膜の表面が平坦化され、前記実装領域がレジストで覆われ、前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位置に合わせて同じ形状の開口が前記レジストにそれぞれ形成され、前記開口より径が小さいはんだ粒子が前記開口に充填され、前記はんだ粒子が溶かされ、前記開口内にはんだバンプが形成され、前記レジストが除

50

去され、前記パターン及び前記絶縁膜の表面が平坦化されている前記実装領域が露出される。

【発明の効果】

【0018】

本技術の一側面によれば、回路基板が製造される。また、製造された回路基板を用いることにより、フリップチップ実装により製造される電子部品の品質を向上させることができる。

【図面の簡単な説明】

【0019】

【図1】チップの裏面を模式的に示す図である。

10

【図2】エリア端子又はペリフェラル端子を横から見た図である。

【図3】回路基板の構成例を示す模式図である。

【図4】回路基板のランド近傍の拡大図である。

【図5】回路基板のパッド近傍の拡大図である。

【図6】チップと回路基板の接続位置を示す図である。

【図7】電子部品の構成例を示す模式図である。

【図8】回路基板の製造工程を示す図である。

【図9】回路基板の製造工程を示す図である。

【図10】前処理工程後の回路基板を上から見た模式図である。

【図11】露光・現像工程後の回路基板を上から見た模式図である。

20

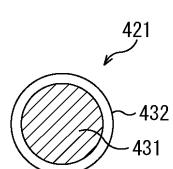

【図12】はんだ粒子の断面を示す模式図である。

【発明を実施するための形態】

【0020】

以下、本技術を実施するための形態（以下、実施の形態という）について説明する。なお、説明は以下の順序で行う。

1. 本技術を適用した電子部品の実施の形態

2. 回路基板の製造方法

3. 変形例

【0021】

<1. 本技術を適用した電子部品の実施の形態>

30

まず、図1乃至図7を参照して、本技術を適用した電子部品の一実施の形態について説明する。

【0022】

[1-1. チップ100の構成例]

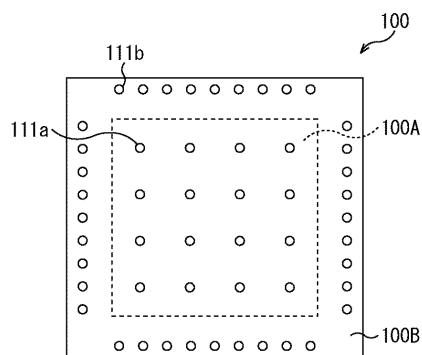

図1は、本技術を適用した電子部品を構成するチップ100の裏面を模式的に示す図である。なお、図を分かりやすくするために、図中、エリア端子111a及びペリフェラル端子111bの符号の図示を一部省略している。

【0023】

チップ100の裏面は、中央の正方形のエリア部100A、及び、その周囲を囲むペリフェラル部100Bの2つの領域に大きく分かれる。

40

【0024】

エリア部100Aには、エリア端子111aが等間隔に格子状に設けられている。各エリア端子111a間のピッチは、例えば130μmとされる。

【0025】

ペリフェラル部100Bには、ペリフェラル端子111bが、チップ100の各辺に沿って等間隔に一列に並ぶように設けられている。各ペリフェラル端子111bのピッチは、例えば100μmとされる。

【0026】

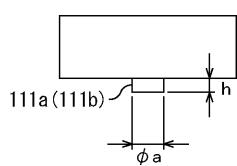

図2は、エリア端子111a又はペリフェラル端子111bを横から見た図である。エリア端子111a及びペリフェラル端子111bは、同一の形状及び材質の円柱状の金属

50

バンプにより構成される。エリア端子 111a 及びペリフェラル端子 111b の径 a は、例えば 30 μm とされ、高さ h は、例えば 15 μm とされる。

#### 【0027】

なお、以下、エリア端子 111a 及びペリフェラル端子 111b を個々に区別する必要がない場合、単に端子 111 と称する。

#### 【0028】

##### [1-2. 回路基板 200 の構成例]

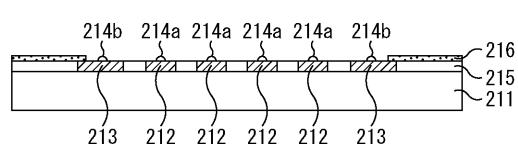

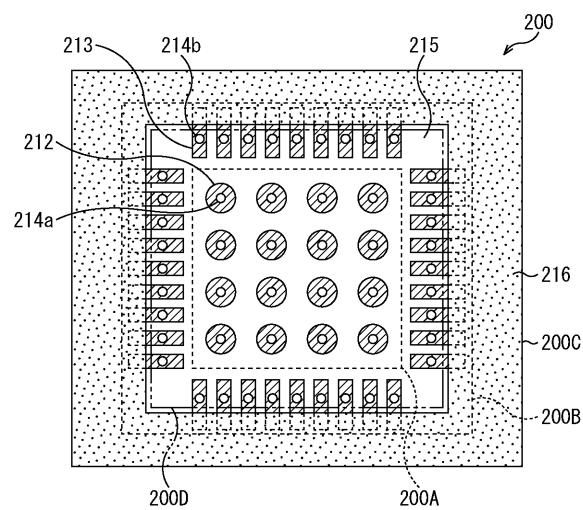

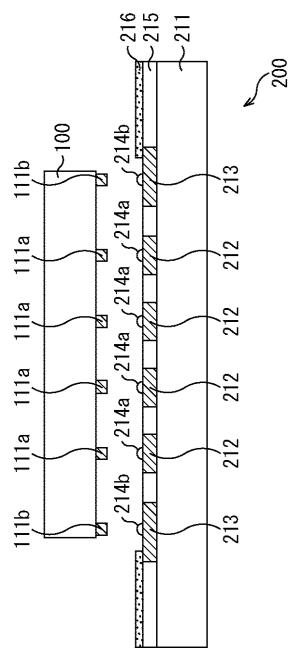

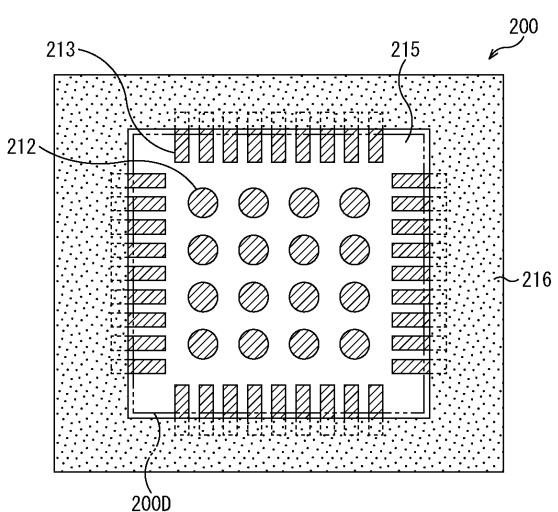

図 3 は、本技術を適用した電子部品を構成し、チップ 100 が実装される回路基板 200 の構成例を示している。図 3 の上の図は、回路基板 200 を上から見た模式図であり、下の図は、回路基板 200 の断面の模式図である。なお、図を分かりやすくするために、図中、ランド 212、パッド 213、はんだバンプ 214a、及び、はんだバンプ 214b の符号の図示を一部省略している。

10

#### 【0029】

回路基板 200 のチップ 100 が実装される実装面は、中央の正方形のエリア部 200A、その周囲を囲むペリフェラル部 200B、及び、そのさらに外側の周縁部 200C の 3 つの領域に大きく分類される。なお、エリア部 200A は、チップ 100 のエリア部 100A に対応する領域であり、エリア部 100A と同じ面積である。ペリフェラル部 200B は、チップ 100 のペリフェラル部 100B に対応する領域であり、ペリフェラル部 100B より広い面積を有する。また、図内の実装面の二点鎖線で示される実装領域 200D に、チップ 100 が実装される。従って、実装領域 200D は、チップ 100 のサイズとほぼ等しくなる。

20

#### 【0030】

エリア部 200A には、ベース基板 211 の上に複数の円形のランド 212 が形成されている。各ランド 212 は、それぞれチップ 100 の各エリア端子 111a の位置に合わせて格子状に並ぶように配置されている。各ランド 212 間のピッチは、例えば 130 μm とされる。

30

#### 【0031】

また、各ランド 212 の表面の中央には、略同じ形状のはんだバンプ 214a がそれぞれ形成されており、各はんだバンプ 214a は、チップ 100 の各エリア端子 111a を接続する接続位置に、格子状に並ぶように配置されている。

#### 【0032】

さらに、ペリフェラル部 200B には、ベース基板 211 の上に複数の矩形のパッド 213 が形成されている。各パッド 213 は、それぞれチップ 100 の各ペリフェラル端子 111b の位置に合わせて、ペリフェラル部 200B の各辺に沿って等間隔に平行に並べられている。

#### 【0033】

また、各パッド 213 の表面のそれぞれ同じ位置に、略同じ形状のはんだバンプ 214b が形成されており、各はんだバンプ 214b は、それぞれチップ 100 の各ペリフェラル端子 111b を接続する接続位置に配置されている。

40

#### 【0034】

さらに、回路基板 200 の実装面のランド 212 及びパッド 213 以外の部分には、絶縁膜 215 が形成されている。また、ランド 212、パッド 213、及び、絶縁膜 215 の表面が平坦になるように、平坦化処理が施されている。

#### 【0035】

さらに、実装面の周縁には、実装領域 200D の少し外側に、実装領域 200D の周縁を囲むようにソルダレジスト 216 が形成されている。そして、各パッド 213 の外周側の端部が、ソルダレジスト 216 により覆われている。

#### 【0036】

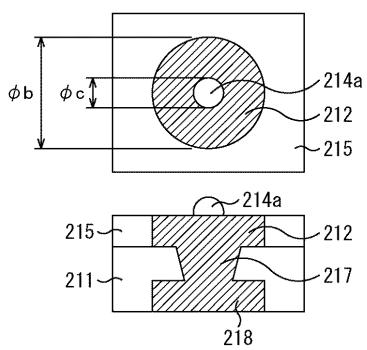

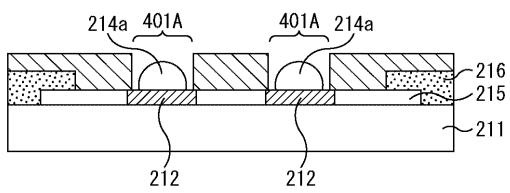

図 4 は、ランド 212 近傍の拡大図である。具体的には、図 4 の上の図は、ランド 212 を上から見た模式図であり、下の図はランド 212 付近の断面の模式図である。

50

## 【0037】

ランド212の径bは、例えば160μmとされる。また、はんだバンプ214aは、略半球状の形状を有しており、その径cは、例えば30μmとされる。

## 【0038】

各ランド212の下部にはビアホール217が設けられている。そして、各ランド212は、ビアホール217を介して、ベース基板211の裏面に形成されている配線パターン218に接続されている。

## 【0039】

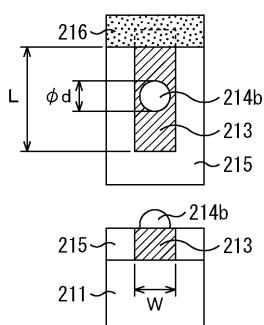

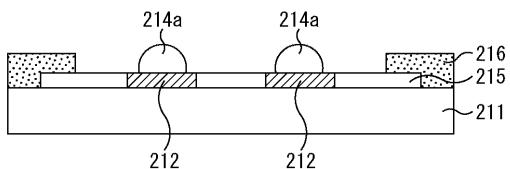

図5は、パッド213近傍の拡大図である。具体的には、図5の上の図は、パッド213を上から見た模式図であり、下の図はパッド213付近の断面の模式図である。

10

## 【0040】

パッド213の長辺のソルダレジスト216に覆われていない部分の長さlは、例えば130μmとされる。パッド213の短辺の幅Wは、例えば35μmとされる。また、はんだバンプ214bは、ランド212のはんだバンプ214aと同様の形状を有しており、その径dは、例えば30μmとされる。

## 【0041】

なお、以下、はんだバンプ214a及びはんだバンプ214bを個々に区別する必要がない場合、単に、はんだバンプ214と称する。

## 【0042】

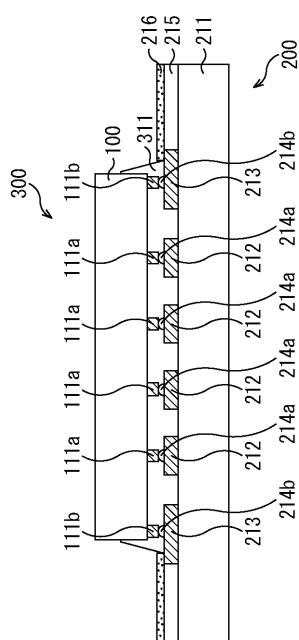

## [1-3. 電子部品300の構成例]

20

本技術を適用した電子部品300は、回路基板200上にチップ100を実装することにより製造される。

## 【0043】

具体的には、図6に示されるように、チップ100の各端子111が、回路基板200の各はんだバンプ214の位置に合わせて、回路基板200に実装される。これにより、図7に示されるように、チップ100の各端子111と回路基板200のはんだバンプ214が接続される。

## 【0044】

このとき、例えば、チップ100を実装する前に回路基板200の実装領域200Dにアンダーフィル311が塗布され、フリップチップボンダによりチップ100が回路基板200に実装される。これにより、チップ100と回路基板200の隙間がアンダーフィル311により充たされ、封止される。アンダーフィル311は、例えば、フラックス機能付の活性化工ポキシ樹脂により構成される。

30

## 【0045】

## &lt;2. 回路基板200の製造方法&gt;

次に、図8乃至図12を参照して、回路基板200の製造方法について説明する。

## 【0046】

図8及び図9は、回路基板200の製造工程を示している。なお、図8及び図9では、図をわかりやすくするために、回路基板200を図3と比べてさらに模式化して示している。また、パッド213上のはんだバンプ214bの形成工程の図示を省略しているが、実際には後述するランド212上のはんだバンプ214aと同じ工程により形成される。

40

## 【0047】

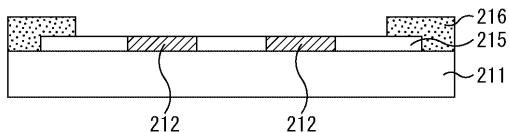

## (1) 前処理工程

まず、ベース基板211のランド212、パッド213、及び、絶縁膜215の表面が平坦になるように平坦化処理が行われる。これにより、ランド212、パッド213、及び、絶縁膜215の高さが均一になり、実装領域200Dの表面が平坦になる。

## 【0048】

次に、実装領域200Dの少し外側に、実装領域200Dの周囲を囲むように、実装面の周縁にソルダレジスト216が形成される。

## 【0049】

50

図10は、前処理工程が行われた後の回路基板200を上から見た模式図である。なお、図を分かりやすくするために、図中、ランド212及びパッド213の符号の図示を一部省略している。

【0050】

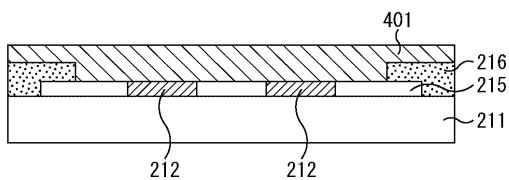

(2) レジスト工程

次に、回路基板200の実装面全体にレジスト401が塗布又はラミネートされる。これにより、実装領域200Dの表面がレジスト401により覆われる。なお、レジスト401は、例えば感光性樹脂により構成され、その厚さは、例えば30μmとされる。

【0051】

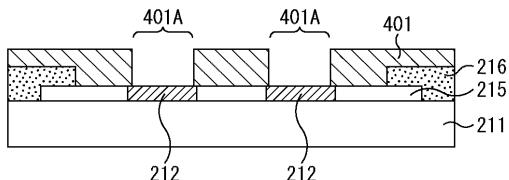

(3) 露光・現像工程

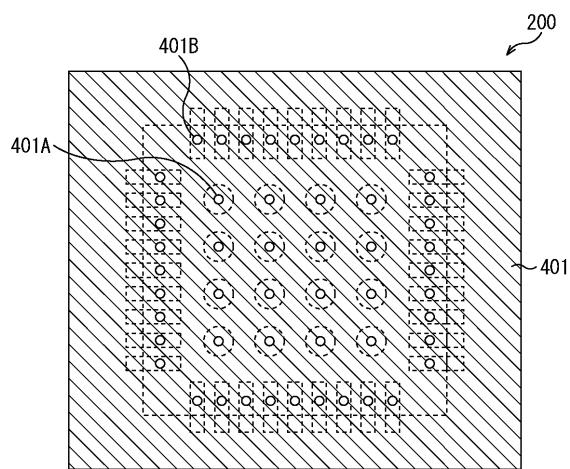

次に、露光及び現像を行うことにより、レジスト401に開口401A及び開口401B(図11)が形成される。

【0052】

図11は、露光・現像工程が行われた後の回路基板200を上から見た模式図である。なお、図を分かりやすくするために、図中、開口401A及び開口401Bの符号の図示を一部省略している。

【0053】

開口401A及び開口401Bは、同じ形状の円形の開口であり、その径は例えば30μmとされる。これは、はんだバンプ214a及びはんだバンプ214bと同じ径である。

【0054】

開口401Aは、各ランド212上のチップ100の各エリア端子111aが接続される接続位置に合わせて形成される。これにより、各ランド212の各エリア端子111aが接続される部分、換言すれば、はんだバンプ214aが形成される部分が露出する。

【0055】

開口401Bは、各パッド213上のチップ100の各ペリフェラル端子111bが接続される接続位置に合わせて形成される。これにより、各パッド213の各ペリフェラル端子111bが接続される部分、換言すれば、はんだバンプ214bが形成される部分が露出する。

【0056】

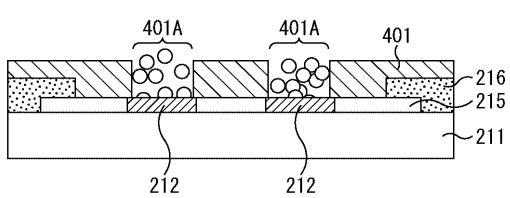

(4) はんだ粒子充填工程

次に、レジスト401の開口401A及び開口401Bに、それぞれ略同量の粉状のはんだ粒子が充填される。

【0057】

図12は、はんだ粒子421の断面を模式的に示している。はんだ粒子421は、略球状のはんだ(Sn3Ag0.5Cu)431の表面をフラックス(例えば、ロジン)によりコーティングしたものである。はんだ粒子421の径は、開口401A及び開口401Bの径より小さく、例えば、はんだ431の径は10μmとされ、コート432の厚みは2μmとされる。また、はんだ431は、常温で固体のモノマーであり、はんだ粒子421は、常温でタックフリーである。

【0058】

(5) リフロー工程

次に、窒素雰囲気中においてリフローが行われる。これにより、回路基板200全体が加熱され、開口401A内及び開口401B内のはんだ粒子421が溶け、開口401A及び開口401B内において、略同じ形状のはんだバンプ214a及びはんだバンプ214bがそれぞれ形成される。

【0059】

(6) レジスト除去洗浄工程

次に、レジスト401が全て除去される。レジスト401の除去には、例えば、アミン系剥離液が用いられる。これにより、実装領域200Dが全て露出する。また、はんだ粒

10

20

30

40

50

子421から生じるフラックスの残渣等の洗浄が行われる。

【0060】

このようして、上述した図3に示される回路基板200が製造され、回路基板200の形状が異なるパターン（ランド212及びパッド213）に略同じ形状のはんだバンプ214を形成することができる。また、回路基板200の実装領域200Dの表面が平坦化されているため、各はんだバンプ214の高さを合わせることができる。

【0061】

さらに、従来のソルダレジストをレーザ加工により開口し、クリームはんだを印刷する方法等と比較して、はんだバンプ214を形成する位置の精度が向上し、各はんだバンプ214の位置を、チップ100の各端子111の接続位置に正確に合わせることができる。また、従来の方法で発生していたはんだバンプの脱落や、隣接するはんだバンプの短絡等の不良の発生を抑制することができる。

【0062】

従って、チップ100を回路基板200にフリップチップ実装する場合に、チップ100の各端子111と回路基板200のはんだバンプ214を確実に接続することができる。また、低荷重でチップ100を回路基板200に実装することができ、ランド212の下にビアホール217が形成されていても、ベース基板211等にダメージを与えることが防止される。その結果、電子部品300の不良の発生を抑制し、品質を向上させることができる。

【0063】

<3. 変形例>

以下、上述した本技術の実施の形態の変形例について説明する。

【0064】

[3-1. 製造工程の変形例]

例えば、回路基板200の製造時に、水素や蟻酸等で満たされた還元雰囲気中でリフロー工程を行うようにしてもよい。これにより、はんだ粒子の表面をフラックスによりコーティングする必要がなくなる。

【0065】

[3-2. はんだバンプを形成するパターンの変形例]

また、以上に示した回路基板200のパターン（ランド212及びパッド213）の形状は、その一例であり、この例に限定されるものではない。パターンの形状の種類も上述した2種類に限定されるものではなく、1種類、或いは、3種類以上の場合にも本技術を適用することができる。しかも、本技術によれば、回路基板上に露出しているパターンによらずに、略同一形状のはんだバンプを、所定の位置に高精度に形成することができる。

【0066】

[3-3. 端子111、はんだバンプ214等の形状、寸法の変形例]

さらに、上述したチップ100の端子111、はんだバンプ214、レジスト401の開口401A、401B、及び、はんだ粒子421等の形状や寸法は、その一例であり、必要に応じて変更することができる。例えば、以上の説明では、チップ100の端子111の径を、はんだバンプ214の径と同じにする例を示したが、はんだバンプ214の径より大きくしたり、又は、小さくしたりすることができる。

【0067】

また、例えば、本技術は以下のよう構成も取ることができる。

【0068】

(1)

所定のチップが実装される実装領域の表面が平坦化され、かつ、露出しており、

前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位置にそれぞれ略同じ形状のはんだバンプが形成されている

回路基板。

(2)

10

20

30

40

50

前記実装領域の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記パターン上の各前記接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内に前記はんだバンプを形成する第5の工程と、

前記レジストを除去する第6の工程と

を含む工程により製造される前記(1)に記載の回路基板。

(3)

前記実装領域の周囲を囲むように前記回路基板の実装面の周縁にソルダレジストが形成 10

されている

前記(1)又は(2)に記載の回路基板。

(4)

所定のチップが実装される実装領域の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位置

に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内にはんだバンプを形成する第5の工程と、

前記レジストを除去する第6の工程と 20

を含む回路基板の製造方法。

(5)

前記はんだ粒子の表面がフラックスによりコーティングされており、

前記第5の工程を窒素雰囲気中で行う

前記(4)に記載の回路基板の製造方法。

(6)

チップと、

前記チップを実装する回路基板と

を備え、

前記回路基板は、

前記チップが実装される実装領域の表面が平坦化され、かつ、露出しており、

前記実装領域に形成されているパターン上の前記チップの各端子が接続される接続位

置にそれぞれ略同じ形状のはんだバンプが形成されている

電子部品。

(7)

前記回路基板は、

前記実装領域の表面を平坦化する第1の工程と、

前記実装領域をレジストで覆う第2の工程と、

前記パターン上の各前記接続位置に合わせて同じ形状の開口を前記レジストにそれぞれ形成する第3の工程と、

前記開口より径が小さいはんだ粒子を前記開口に充填する第4の工程と、

前記はんだ粒子を溶かし、前記開口内に前記はんだバンプを形成する第5の工程と、

前記レジストを除去する第6の工程と

を含む工程により製造される

前記(6)に記載の電子部品。

【符号の説明】

【0069】

100 チップ, 100A エリア部, 100B ペリフェラル部, 111a

エリア端子, 111b ペリフェラル端子, 200 回路基板, 200A エリア

部, 200B ペリフェラル部, 200D 実装領域, 211 ベース基板, 2 50

1 2 ランド, 2 1 3 パッド, 2 1 4 a, 2 1 4 b はんだバンプ, 2 1 5 絶縁膜, 2 1 6 ソルダレジスト, 3 0 0 電子部品, 3 1 1 アンダーフィル, 4 0 1 レジスト, 4 0 1 A, 4 0 1 B 開口, 4 2 1 はんだ粒子, 4 3 1 はんだ, 4 3 2 コート

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

(1) 前処理

(2) レジスト処理

(3) 露光・現像

【図9】

図9

(4) はんだ粒子充填

(5) リフロー処理

(6) レジスト除去、洗浄

【図10】

図10

【図11】

図11

【図12】

図12

---

フロントページの続き

(56)参考文献 特開平11-191565(JP, A)

特開2009-239142(JP, A)

特開2006-173654(JP, A)

特開昭64-040174(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H05K 3/10 - 3/38