US 20020032712A1

Mar. 14, 2002

### (19) United States (12) Patent Application Publication (10) Pub. No.: US 2002/0032712 A1 Miyasaka et al.

### (54) EXPONENTIAL CALCULATION DEVICE AND DECODING DEVICE

(76) Inventors: Shuji Miyasaka, Osaka (JP); Takeshi Fujita, Osaka (JP); Masahiro Sueyoshi, Osaka (JP); Akihisa Kawamura, Osaka (JP); Masaharu Matsumoto, Osaka (JP); Takashi Katayama, Osaka (JP); Kazutaka Abe, Osaka (JP); Kosuke Nishio, Osaka (JP)

> Correspondence Address: **Ratner & Prestia** P.O. Box 980 Valley Forge, PA 19482 (US)

- (21) Appl. No.: 09/929,156

- (22) Filed: Aug. 14, 2001

#### **Related U.S. Application Data**

Division of application No. 09/244,155, filed on Feb. (62) 3, 1999, now Pat. No. 6,304,890.

#### (30)**Foreign Application Priority Data**

| Feb. 4, 1998  | (JP) | 10-023022 |

|---------------|------|-----------|

| May 14, 1998  | (JP) | 10-131636 |

| May 28, 1998  | (JP) | 10-147348 |

| Jan. 14, 1999 | (JP) | 11-008562 |

| Jan. 26, 1999 | (JP) | 11-017702 |

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

#### (57)ABSTRACT

(43) Pub. Date:

A device of the present invention is an exponential calculation device for calculating  $x^{-}(a/b)$  (where a and b are each an integer constant) for a given input value of x. The device includes: an input control section for outputting a value of x', wherein x'=x when  $x \leq A$  (where A is a threshold value within a variable range of x) and x'=x/2 b when x>A: a core section for outputting a value of z'=x' (a/b); and an output control section for outputting a value of z, wherein z=z'when  $x \ge A$  and z=z'\*2 a when x>A.

|    | 0    | 0. 000000 - ROM1 |

|----|------|------------------|

|    | 1    | 1. 000000        |

|    | 2    | 2.519842         |

|    | 3    | 4. 326749        |

|    | 4    | 6.349604         |

|    | 5    | 8.549880         |

|    | 6    | 10. 902724       |

|    | 7    | 13. 390518       |

|    | 8    | 16.00000         |

|    | 9    | 18.720754        |

| 10 |      |                  |

|    | 500  | 3968. 502530     |

| 11 | 77   |                  |

|    | 1014 | 10187.100875     |

|    | 1015 | 10200. 498344    |

|    | 1016 | 10213. 900213    |

|    | 1017 | 10227. 306480    |

|    | 1018 | 10240.717141     |

|    | 1019 | 10254.132195     |

|    | 1020 | 10267.551638     |

|    | 1021 | 10280. 975446    |

|    | 1022 | 10294. 403678    |

|    | 1023 | 10307.836271     |

|    |      |                  |

|     | ·    |                  |

|-----|------|------------------|

|     | 0.   | 0. 000000 - ROM2 |

|     | 1    | 1. 000000        |

|     | 2    | 1. 259921        |

|     | 3    | 1. 442250        |

|     | 4    | 1. 587401        |

|     | 5    | 1. 709976        |

|     | 6    | 1. 817121        |

|     | 7    | 1. 912931        |

|     | 8    | 2.000000         |

|     | 9    | 2.080084         |

| 5   |      |                  |

|     | 500  | 7.937005         |

| L C | 7    |                  |

|     | 1014 | 10.046451        |

|     | 1015 | 10.049752        |

|     | 1016 | 10.053051        |

|     | 1017 | 10.056349        |

|     | 1018 | 10.059644        |

|     | 1019 | 10.062936        |

|     | 1020 | 10.066227        |

|     | 1021 | 10.069516        |

|     | 1022 | 10.072802        |

|     | 1023 | 10.076086        |

|     |      |                  |

| - |     |                                        |

|---|-----|----------------------------------------|

|   | 0   | 0. 000000~ROM3                         |

|   | 1   | 1. 000000                              |

|   | 2   | 1. 259921                              |

|   | 3   | 1. 442250                              |

|   | 4   | 1. 587401                              |

|   | 5   | 1. 709976                              |

|   | 6   | 1.817121                               |

|   | 7   | 1. 912931                              |

|   | 8   | 2.000000                               |

|   | 9   | 2.080084                               |

| 4 | 2   | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

|   | 130 | 5.065797                               |

| Ţ | 11  |                                        |

|   | 248 | 6. 282761                              |

|   | 249 | 6. 291195                              |

|   | 250 | 6. 299605                              |

|   | 251 | 6. 307994                              |

|   | 252 | 6. 316360                              |

|   | 253 | 6. 324704                              |

|   | 254 | 6. 333026                              |

| L | 255 | 6. 341326                              |

|   |     |                                        |

FIG.11

| adrs:j           | data:2^(j/3)                                                                                    |

|------------------|-------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3 | 010000000000000000000000000000000000<br>01010000101000101000101111100110<br>0110010110010111111 |

|   |            |                               | ROM4 |

|---|------------|-------------------------------|------|

|   | 0          | 8.000000                      |      |

|   | 1          | 8.005205                      | P    |

|   | 2          | 8.010403                      |      |

|   | 3          | 8.015595                      |      |

|   | 4          | 8.020779                      |      |

|   | 5          | 8.025957                      |      |

|   | 6          | 8.031129                      |      |

|   | 7          | 8.036293                      |      |

|   | 8          | 8.041452                      |      |

|   | 9          | 8.046603                      |      |

|   | 10         | 8.051748                      |      |

| 2 |            |                               |      |

|   |            | [`                            | r i  |

|   | 504        | 10.053051                     |      |

|   | 505        | 10.056349                     |      |

|   | 506        | 10.059644                     |      |

|   | 507        | 10.062936                     |      |

|   |            |                               |      |

|   | 508        | 10.066227                     |      |

|   | 508<br>509 | $\frac{10.066227}{10.069516}$ |      |

|   |            |                               |      |

|   | 509        | 10.069516                     |      |

| adrs:k | data:2^((k-B)/3) (B=10)                 |

|--------|-----------------------------------------|

| 0      | 000001100101100101111111110101001       |

| 1      | 000010000000000000000000000000000000000 |

| 2      | 00001010000101000101000101111100        |

| 3      | 000011001011001011111111101010010       |

| 4      | 000100000000000000000000000000000000000 |

| 5      | 00010100001010001010001011111001        |

| 6      | 000110010110010111111111010100101       |

| 7      | 001000000000000000000000000000000000000 |

| 8      | 00101000010100010100010111110011        |

| 9      | 00110010110010111111110101001010        |

| 10     | 010000000000000000000000000000000000000 |

| 11     | 01010000101000101000101111100110        |

| 12     | 01100101100101111111101010010100        |

| 13     | 011111111111111111111111111111111111111 |

|    | adrs:a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | data F(a)                                                  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| () | adrs;q<br>0 1 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 13 14 5 6 7 8 9 10 11 2 13 14 5 16 7 8 9 21 22 32 4 5 6 7 8 9 10 11 2 3 3 4 5 6 7 8 9 10 11 2 3 3 4 5 6 7 8 9 10 11 2 3 3 4 5 6 7 8 9 10 11 2 3 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 11 11 11 11 11 11 11 11 11 11 11 | data F(q)                                                  |

|    | 8187<br>8188<br>8188<br>8189<br>8190<br>8191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 &$ |

| adrs;p           | data G(p)                                                  |

|------------------|------------------------------------------------------------|

| 0<br>1<br>2<br>3 | $\begin{array}{c} 0 \ 1 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \$ |

| ( | adrs;q                                                                                                                                        | data H(q)                                                 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|   | 0<br>123456789011234567890112345678901123456789012345678901222222222222233333<br>450012234565506789001234555555555555555555555555555555555555 | $\begin{array}{c} 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 $ |

Patent Application Publication Mar. 14, 2002 Sheet 21 of 30

| adrs;(p,j) | data I(p,k)                             |

|------------|-----------------------------------------|

| (0,0)      | 000100000000000000000000000000000000000 |

| (0,1)      | 00010100001010001010001011111001        |

| (0,2)      | 000110010110010111111111010100101       |

| (0,3)      | 001000000000000000000000000000000000000 |

| (0,4)      | 00101000010100010100010111110011        |

| (1,0)      | 00010011000001101111111000001010        |

| (1,1)      | 00010111111110010001000011010111        |

| (1,2)      | 00011110001101000011011111100111        |

| (1,3)      | 001001100000110111111100000101000       |

| (1,4)      | 00101111111100100010000110101110        |

| (2,0)      | 00010110101000001001111001100110        |

| (2,1)      | 00011100100000100011111000000111        |

| (2,2)      | 00100011111010110011010110000111        |

| (2,3)      | 00101101010000010011110011001100        |

| (2,4)      | 00111001000001000111110000001110        |

| (3,0)      | 000110101110100010011111110011001       |

| (3,1)      | 00100001111001110001111100100101        |

| (3,2)      | 00101010101101110000001000010001        |

| (3,3)      | 001101011101000100111111100110010       |

| (3,4)      | 01000011110011100011111001001011        |

| adrs;(p,j)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | data I (p,j)                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| $ \begin{array}{c} (0,2) \\ (0,2) \\ (0,0,0) \\ (0,0,0) \\ (0,0,0) \\ (0,0,0) \\ (1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ (1,1,2) \\ $ | $\begin{array}{c} 0 & 0 & 0 & 0 & 0 & 1 & 0 & 1 & 0 & 0 &$ |

| adrs;q                                                                                                                                   | data H(q)                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15                                                       | $\begin{array}{c} 0 0 1 1 0 0 1 0 1 1 1 0 0 1 0 1 1 1 1 $            |

| 236<br>237<br>238<br>239<br>240<br>241<br>242<br>243<br>244<br>245<br>246<br>247<br>248<br>249<br>250<br>251<br>252<br>253<br>254<br>255 | $\begin{array}{c} 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 & 1 & 0 & 1 & 1$ |

|   | 0            | 0. 000000      |

|---|--------------|----------------|

|   | 1            | 1. 000000      |

|   | 2            | 2. 519842      |

|   | 3            | 4. 326749      |

|   | 4            | 6.349604       |

|   | 5            | 8. 549880      |

|   | 6            | 10. 902724     |

|   | 7            | 13.390518      |

|   | 8            | 16.00000       |

|   | 9            | 18.720754      |

|   |              |                |

|   |              | Ĩ Ĩ            |

|   | 8180         | 164817.910834  |

|   | 818 <b>1</b> | 164844.776566  |

|   | 8182         | 164871. 643393 |

|   | 8183         | 164898. 511315 |

|   | 8184         | 164925. 380331 |

|   | 8185         | 164952. 250442 |

|   | 8186         | 164979. 121647 |

|   | 8187         | 165005. 993946 |

|   | 8188         | 165032. 867339 |

|   | 8189         | 165059.741827  |

|   | 8190         | 165086. 617408 |

| l | 8191         | 165113. 494083 |

|   |              |                |

| adrs                                   | :x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br>                     |                                         |                  |                          | <br>  |                  |                  |        | da                                             | nto | ı f                                   | $\overline{(\mathbf{x})}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\overline{)}$                           |                                          |                                         |             |                  |                  | <br> |                                |                                        |                                        |                                           |                                         |       |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------|------------------|--------------------------|-------|------------------|------------------|--------|------------------------------------------------|-----|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------------------|-------------|------------------|------------------|------|--------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------|-----------------------------------------|-------|

|                                        | 012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890123456789001234567890123456789001234567890012345678900123456789001234567890012345678900123456789001234567890012345678900123456789000000000000000000000000000000000000 |                          | 000000000000000000000000000000000000000 |                  |                          |       |                  |                  |        |                                                |     | 0000000011111000001111000001111100001 | 0000001111100011110001110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110001100011000110000 | 0000110001000101001010101010101010101010 | 0101010110011100001111100000000000000011 | 100000011001010001110001111111001111111 |             |                  |                  |      | 001001110110001010100101110000 | 01111011110101001111100010101001111110 | 00101011110100100000110101010111110011 | 00011011010000111001011001011111001111001 | 000101100111001100101010101010100000000 |       |

| 818<br>818<br>818<br>818<br>819<br>819 | 37<br>38<br>39<br>90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ) 1<br>) 1<br>) 1<br>) 1 | 00000                                   | 1<br>1<br>1<br>1 | 0 (<br>0 (<br>0 (<br>0 ( | 00000 | 1<br>1<br>1<br>1 | 0<br>0<br>0<br>0 | 000000 | 1 (<br>1 (<br>1 <sup>-</sup><br>1 <sup>-</sup> |     | ) 0<br>0<br>) 0<br>) 1                | 1<br>1<br>0<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1<br>0<br>0                              | 0<br>0<br>1<br>1                         | 1<br>0<br>1<br>0                        | 1<br>1<br>1 | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 |      | 1<br>1<br>0<br>1               | 0<br>0<br>1<br>0                       | 0<br>0<br>1<br>0                       | 1<br>0<br>1<br>0                          | 1 1<br>0 0<br>1 0<br>0 0<br>1 1         | ))))) |

| adrs;y%4         | data g(y)                             |

|------------------|---------------------------------------|

| 0<br>1<br>2<br>3 | 0100000000000000000000000000000000000 |

### EXPONENTIAL CALCULATION DEVICE AND DECODING DEVICE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

**[0002]** The present invention relates to an exponential calculation device and a decoding device for performing a predetermined calculation for a given encoded bit stream. More particularly, the present invention relates to an exponential calculation device for calculating  $\hat{x}$  (a/b) and a decoding device for calculating  $\hat{x}$  (a/b) \*2 (y/c) for given integer values x and y contained in a bit stream which has been encoded based on the MPEG (moving picture experts group) 2 audio encoding standard "AAC".

[0003] 2. Description of the Related Art

**[0004]** Conventionally, in order to calculate  $z=\hat{x}$  (a/b) for a given value of x (where a and b are constant values), values of  $\hat{x}$  (a/b) for all the possible values of x are stored in a table whose addresses are associated with the respective values of x. The value of z for a given value of x is obtained by reading out the value stored in the table.

**[0005]** In this specification, "x to a power of (a/b)" is represented as " $\hat{x}$  (a/b)", where the symbol " $^{"}$  denotes the use of an exponential function, and the symbol "/" denotes a division function. The symbol "\*" will also be used herein to denote a multiplication function.

[0006] FIG. 27 illustrates a table containing values of  $\hat{x}$  (4/3) for values of x in a range of  $0 \le x \le 8191$ . A decoding operation based on the MPEG 2 audio encoding standard AAC requires calculation of  $\hat{x}$  (4/3) for a value of x in the range from 0 to 8191. When the conventional method of obtaining the value of  $\hat{x}$  (a/b) is employed in the exponential calculation involved in decoding data encoded based on the MPEG 2 audio encoding standard AAC, an input value of x is used as an address for reading out the corresponding value from a table provided in advance, as illustrated in FIG. 27, to obtain the value of  $\hat{x}$  (4/3) an output value z.

**[0007]** In order to decode an encoded bit stream so as to obtain the intended data, it is necessary to perform a predetermined calculation process. A bit stream encoded based on the MPEG 2 audio encoding standard AAC contains a quantization code "x" and a scaling factor "y". The quantization code "x" and the scaling factor "y" are both integers. In the case of the MPEG 2 audio encoding standard AAC, the decoding device calculates  $\hat{x}$  (a/b)\*2 (y/c) (where a,b and c are constants) for given values of x and y. Details of the MPEG 2 audio encoding standard AAC are disclosed in ISO/IEC 13818-7:1997, pp.57-59.

[0008] Conventionally, an operation of calculating  $\hat{x}$  (a/b)\*2 (y/c) for given values of x and y has been performed as follows with a DSP (digital signal processor) of a fixed point format.

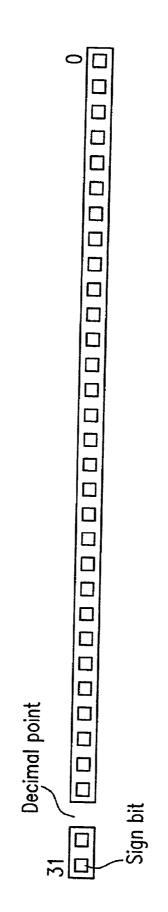

[0009] FIG. 28 illustrates an exemplary 32-bit fixed point format. Referring to FIG. 28, where the bit 0 is the least significant bit and the bit 31 is the most significant bit, the decimal point is fixed between the bit 30 and the bit 29. In particular, bit 30 represents the integral portion of a value, while the bits 29-0 represent the fractional portion of the value. Bit 31 is the sign bit indicating whether the value is positive or negative. Such a numeric representation with a fixed decimal point is called a "fixed point format".

**[0010]** For example, a value "f" represented in the 32-bit fixed point format, as illustrated in **FIG. 28**, can vary in the range of  $-2 \le 1 \le 2$ . Then, in order to perform a calculation with a fixed-point-format processing unit, such as a DSP, values involved in the calculation are adjusted so that they are each in the range of +2.0 before performing the intended calculation.

[0011] In the MPEG 2 audio encoding standard AAC, x can vary in the range of  $0 \le x < 8192$ , whereas y can vary in the range of  $-100 \le y < 156$ . Consider a calculation of Expression (1) below for x and y having such ranges.

$$\hat{\mathbf{x}}$$

(4/3)\*2 (y/4) (1)

**[0012]** Expression (1) may be calculated as follows based on the prior art technique with a fixed-point-format processing unit. First, Expression (1) is converted to Expression (2) below.

$$\hat{\mathbf{x}}$$

(4/3)\*2 ((y%4)/4)\*2 int(y/4) (2)

**[0013]** In Expression (2), "(y%4)" represents a remainder of a division y/4, and "int(y/4)" represents a quotient (integer) of the division y/4. In the calculation of Expression (2),  $\hat{x}$  (4/3) is first calculated. The calculation  $\hat{x}$  (4/3) is typically performed using a ROM table. In particular, values of  $\hat{x}$  (4/3) for various values of x are calculated and stored in a table in advance. Then, the value of  $\hat{x}$  (4/3) for a given value of x is obtained by referencing the ROM table using the value of x as the address of the table.

**[0014]** The calculation of Expression (1) or (2) assumes the use of a fixed-point-format processing unit. In particular, different values of  $\hat{x}$  (4/3) are normalized and stored in a table in advance, with the maximum value thereof being normalized to a value which does not exceed 1.0.

**[0015]** FIG. 29 illustrates the contents of a first table for use with a conventional decoding device. The table illustrated in FIG. 29 contains values of f(x) for the range of  $0 \le x < 8192$  at addresses which correspond to the respective values of x. The values of f(x) are obtained by first calculating  $\hat{x}$  (4/3) for various values of x, and then dividing the calculated values by 2-18 to normalize the values so that none of them exceeds 1.0.

**[0016]** In the calculation of Expression (2), 2 ((y%4)/4) is then calculated. Typically, 2 ((y%4)/4) is also calculated using a ROM table. In particular, different values of 2 ((y%4)/4) for various integers (y%4) are calculated and stored in a table in advance. Then, an integer (y%4) is used as an address for referencing the table so as to obtain the value of 2 ((y%4)/4) for the integer (y%4).

**[0017]** FIG. 30 illustrates the contents of a second table for use with a conventional decoding device. The second table illustrated in FIG. 30 contains values of g(y) for the address values (y%4) in the range from 0 to 3. The values of g(y) are obtained by normalizing values of 2 ((y%4)/4) so that none of them exceeds 2.0.

**[0018]** After such a table is provided, the value of Expression (2) can be obtained. First, the first table illustrated in **FIG. 29** is referenced using an input integer x as an address so as to obtain the normalized value f(x) for  $\hat{x}$  (4/3). Then, (y%4) is calculated for a given integer of y. Subsequently,

the calculated value of (y%4) is used as an address to obtain a value of g(y)=2 ((y%4)/4) from the second table illustrated in **FIG. 30**. Then, a multiplier is used to calculate f(x)\*g(y)so as to obtain a multiplied value f(x)\*g(y)=(x,y). Since the obtained value f(x) is within the range of  $\pm 1$  while the obtained value g(y) is within the range of  $\pm 2$ , the multiplication result h(x,y) should always has a value in the range of  $\pm 2$ .

**[0019]** Then, h(x,y) is multiplied by 2 int(y/4) so as to obtain a multiplied value i(x,y) as a calculation result of Expression (2). The multiplication can be performed by a bit shift operation. In the bit shift operation, it is assumed that a limit operation (so called a "clipping operation") is performed when the final calculation result exceeds the range of  $\pm 2$ . Thus, in the prior art, the calculation  $i(x,y)=\hat{x}$  (4/3)\*2 (y/4) is performed using a large-capacity table.

**[0020]** Use of the above conventional method for obtaining a value of  $\hat{x}$  (a/b) requires a large memory area for the table containing different values of  $\hat{x}$  (a/b). For example, assuming that the stored values of  $\hat{x}$  (a/b) are 32-bit fixed point values, the table illustrated in **FIG. 27** would require a memory area of 32 K bytes. Thus, when x has a wide variable range, large-scale hardware has to be employed for the large memory area required.

**[0021]** Moreover, in the conventional method of calculating  $\hat{x}$  (a/b)\*2 (y/c), the number of significant digits of the calculated value f(x) is undesirably small for relatively small input integers of x, as those in the upper portion of **FIG. 29**. For example, the value f(x) corresponding to address x=2 uses only the lower 14 bits of the 32 bits that are available. Thus, a calculation performed by using such a table results in a poor accuracy in the calculation result. Moreover, the conventional calculation method employs a wide range of x (i.e., 0-8191), and accordingly requires a memory area as large as 8191\*32 bits. Consequently, a conventional decoding device requires a table having a very large capacity.

### SUMMARY OF THE INVENTION

**[0022]** According to one aspect of the invention, an exponential calculation device for calculating  $\hat{x}$  (a/b) (where a and b are each an integer constant) for a given input value of x is provided. The device includes: an input control section for outputting a value of x', wherein  $\hat{x}$  x when  $x \le A$  (where A is a threshold value within a variable range of x) and x'=x/2 b when x>A; a core section for outputting a value of z'=x' (a/b); and an output control section for outputting a value of z, wherein z=z' when  $x\le A$  and z=z'\*2 a when x>A.

[0023] In one embodiment of the invention, the input control section calculates the value of x' by shifting x down by b bits when x>A.

**[0024]** In another embodiment of the invention, the core section stores in a table values of x' (a/b) for all possible values of x' (where  $0 \le x' \le A$ ).

**[0025]** In still another embodiment of the invention, A is set to a value such that x is less than or equal to A at a frequency equal to or greater than a predetermined value.

**[0026]** According to another aspect of this invention, an exponential calculation device for calculating  $\hat{x}$  (a/b) (where a and b are each an integer constant) for a given input value of x is provided. The device includes: an input control

section for outputting a value of x', wherein x'=x when  $x \le A$ (where A is a threshold value within a variable range of x) and x'=x/2 (b\*n) when x>A (where n is an integer which satisfies x/2 (b\*n) $\le A$ ); a core section for outputting a value of z'=x' (a/b); and an output control section for outputting a value of z, wherein z=z' when  $x \le A$  and z=z'\*2 (a\*n) when x>A.

[0027] In one embodiment of the invention, the input control section calculates the value of x' by shifting x down by  $(b^*n)$  bits when x>A.

**[0028]** In another embodiment of the invention, the core section stores in a table values of x' (a/b) for all possible values of x'(where  $0 \le x' \le A$ ).

**[0029]** In still another embodiment of the invention, A is set to a value such that x is less than or equal to A at a frequency equal to or greater than a predetermined value.

**[0030]** According to still another aspect of this invention, an exponential calculation device for calculating  $\hat{x}$  (a/b) (where a and b are each an integer constant) for a given input value of x is provided. The device includes: an input control section for outputting a value of x', wherein x'=x when x  $\leq A$  (where A is a threshold value within a variable range of x) and x'=x/2 b when x>A; a core section for outputting a value of z'=x' ((a%b)/b); an output control section for outputting a value of z, wherein z=z' when x  $\leq A$  and z=z'\*2 (a%b) when x>A; and a multiplication section for outputting z\*( $\hat{x}$  (int(a/b)))).

**[0031]** In one embodiment of the invention, A is set to a value such that x is less than or equal to A at a frequency equal to or greater than a predetermined value.

**[0032]** According to still another aspect of this invention, an exponential calculation device for calculating  $\hat{x}$  (a/b) (where a and b are each an integer constant) for a given input value of x is provided. The device includes: a determination section for outputting a parameter j (j is an integer which is not negative) for specifying a value of x; an input control section for outputting a value of x', wherein x'=x when  $x \le A$ (where A is a threshold value within a variable range of x) and x'=x/2 j when x>A; a core section for outputting a value of z'=x'(a/b); and an output control section for outputting a value of z, wherein z=z'when  $x \le A$  and z=z'\*2 (j\*a/b) when x>A.

**[0033]** In one embodiment of the invention, the output control section includes a memory section for storing values of 2 ( $j^*a/b$ ) using j as an address; and the value of z is calculated by reading out a corresponding value of 2 ( $j^*a/b$ ) from the memory section when x>A.

**[0034]** In another embodiment of the invention, A=2 B (B is an integer constant); and the determination section determines the value of j such that  $2 (B+(j-1)) \le x > 2 (B+j)$  when x > 2 b and such that j=0 when  $x \le 2$  b.

**[0035]** According to still another aspect of this invention, an exponential calculation device for calculating  $\hat{x}$  (a/b) (where a and b are each an integer constant) for a given input value of x is provided. The device includes: a determination section for outputting a value of k which denotes a number of digits of x represented in a binary form; an input control section for outputting a value of x', wherein the value of x' is obtained by shifting x up by (B–k) bits when the value of (B–k) is positive and by shifting x down by (k–B) bits when the value of (B-k) is negative; a core section for outputting a value of z'=x' (a/b); and an output control section for outputting a value of z=z'\*(2((k-B)\*a/b)).

[0036] In one embodiment of the invention, the output control section includes a memory section for storing values of 2 ((k-B)\*a/b) using k as an address; and the value of z is calculated by reading out a corresponding value of 2 ((k-B)\*a/b) from the memory section.

**[0037]** In another embodiment of the invention, the core section includes a memory section for storing values of q (a/b) (where 2 (B-1) $\leq$ q>2 B, and q is an integer) using at least lower (B-1) bits of q as an address; and the value of z' is calculated by reading out a corresponding value of q (a/b) from the memory section using the at least lower (B-1) bits of x' as an address.

[0038] According to still another aspect of this invention, there is provided a decoding device for extracting a variable quantization code x and a variable scaling factor y from an input bit stream containing the quantization code x and the scaling factor y and calculating  $\hat{x} (a/b)^{*2} (y/c)$  (where a, b and c are each an integer constant). The device includes: an isolation section for isolating x and y from the input bit stream; a first bit shift section for, when  $x \le 2 N$  (where N is a predetermined threshold value), shifting x by a number of bits according to N so as to convert x to x1 which is in a fixed point format; a first memory section for storing, for all possible values of q (where q is an integer such that  $0 \le q \le 2$ N), using q as an address, values of H(q) which have been converted to a fixed point format by shifting q((a-b)/b) by a number of bits according to M (where M is an integer value of  $(N^{*}(a-b))/b)$ ; a second memory section for storing, for all possible values of p (where  $0 \le p < c$ ), values of G(p)=2 (p/c) in a fixed point format; a division section for calculating y1, where y1=int(y/c); a modulo calculation section for calculating y2=y%c; a multiplication section for outputting a value obtained by multiplying together a value of H(x)which has been read out from the first memory section using x as an address, a value of G(y2) which has been read out from the second memory section using y2 as an address and a value of x1 which has been converted by the first bit shift section; and a second bit shift section for shifting the output value from the multiplication section by a number of bits according to y1 obtained by the division section.

[0039] In one embodiment of the invention, the number of bits according to N is (D-N) (where D is a number of significant digits of a fractional portion of a number involved in a fixed point calculation operation); and the number of bits according to y1 is (y1+(N+M)).

[0040] In another embodiment of the invention, M is an integer obtained by rounding up  $(N^*(a-b))/b$ .

[0041] In still another embodiment of the invention, a=4, b=3 and c=4.

**[0042]** In still another embodiment of the invention, the device further includes: a determination section for outputting a determination result being true when  $x \le 2$  N and being false when x>2 N; and a second division section for outputting the value of x without alteration when the determination result is true and for outputting a value obtained by dividing x by (2 (b\*i)). The first bit shift section shifts x by a number of bits according to (N+b\*i) (where i is an integer which is not negative) when the determination result is false.

The first memory section stores values of H(q) for values of q which are within the variable range of x. The second bit shift section shifts the value output from the multiplication section by a number of bits according to y1 when the determination result is true and by a number of bits according to y1 and a\*i when the determination result is false.

**[0043]** In still another embodiment of the invention, the number of bits according to N is (D-N); the number of bits according to  $(N+b^*i)$  is  $D-(N+b^*i)$ ; the number of bits according to according to M is (D-M); the number of bits according to according to y1 is (y1+N+M); and the number of bits according to y1 and a\*i is  $(y1+N+M+a^*i)$ .

[0044] In still another embodiment of the invention, the value of i is determined so that x satisfies  $2(N+b(i-1)) < x \le 2$  (N+bi).

**[0045]** In still another embodiment of the invention, the device further includes a determination section for outputting a determination result being true when  $x \le 2$  N and being false when x > 2 N, and further outputting a parameter i for specifying a value of x. The first bit shift section and the second division section and the second shifting section operate according to the determination result from the determination section.

**[0046]** In still another embodiment of the invention, the second bit shift section shifts the value output from the multiplication section by a number of bits according to y1 when the determination result is true and by a number of bits according to  $y_1+(a^*i)$  when the determination result is false.

[0047] According to still another aspect of this invention, there is provided a decoding device for extracting a variable quantization code x and a variable scaling factor y from an input bit stream containing the quantization code x and the scaling factory and calculating  $\hat{x}$  (a/b)\*2 (y/c) (where a, b and c are each an integer constant). The device includes: an isolation section for isolating x and y from the input bit stream; a determination section for outputting a determination result being true when  $x \le 2 N$  (where N is a predetermined threshold value) and being false when x>2 N, and further outputting a parameter j for specifying a value of x; a first bit shift section for shifting x by a number of bits according to N when the determination result is true and by a number of bits according to (N+j) when the determination result is false so as to convert x to x1 which is in a fixed point format; a first division section for calculating y1, where  $y_1=int(y/c)$ ; a second division section for outputting a value of x', wherein x'=x when the determination result is true and x' is an integer value of (x/(2 j)); a first memory section for storing, for all possible values of q (where q is an integer such that  $0 \le q \le 2N$ ) within a variable range of x', using q as an address, values of H(q) which have been converted to a fixed point format by shifting q((a-b)/b) by a number of bits according to M (where M is an integer value of (N\*(a-b))/ b); an adjustment coefficient generation section for generating values of I (p, j) in a fixed point format according to 2 (p/c) \* 2 (j/b) for all possible values of p such that  $0 \le p < c$ and all possible values of j; a modulo calculation section for calculating y2=y%c: a multiplication section for outputting a value obtained by multiplying together a value of H(x')which has been read out from the first memory section using x' as an address, a value of I(y2,j) corresponding to y2 and j which has been generated by the adjustment coefficient generation section and a value of x1 which has been converted by the first bit shift section; and a second bit shift section for shifting the output value from the multiplication section by a number of bits according to y1 when  $x \le 2 N$  and by a number of bits according to y1 and j when x>2 N.

[0048] In one embodiment of the invention, the adjustment coefficient generation section includes a second memory section for storing values of I(p,j) using p and j as an address.

**[0049]** In another embodiment of the invention, the value of j is determined so as to satisfy 2  $(N+(j-1)<x\leq 2 (N+j))$  when x>2 N, whereas j=0 when  $x\leq 2 N$ .

[0050] In still another embodiment of the invention, a=4, b=3 and c=4.

[0051] According to still another aspect of this invention, there is provided a decoding device for extracting a variable quantization code x and a variable scaling factor y from an input bit stream containing the quantization code x and the scaling factory and calculating  $\hat{x}$  (a/b)2 (y/c) (where a, b and c are each an integer constant). The device includes: an isolation section for isolating x and y from the input bit stream; a determination section for determining a number k of digits of x represented in a binary form; a second division section for outputting a value of x', wherein the value of x' is obtained by shifting x up by (N-k) bits when the value of (N-k) is positive and by shifting x down by (k-N) bits when the value of (N-k) is negative; a first bit shift section for shifting x by a number of bits according to k so as to convert x to x1 which is in a fixed point format; a first division section for calculating y1, where y1=int(y/c); a first memory section for storing, using at least lower (N-1) bits of q (where q is an integer such that 2  $(N-1) \leq q < 2 N$ ) as an address, values of H(q) which have been converted to a fixed point format by shifting q ((a-b)/b) by a number of bits according to M (where M is an integer value of  $(N^*(a-b))$ )/b); an adjustment coefficient generation section for generating values of I(p,k) in a fixed point format according to 2 (p/c)\*2 ((k–N)/b) for all possible values of p such that  $0 \leq p < c$  and all possible values of k; a modulo calculation section for calculating y2=y%c; a multiplication section for outputting a value obtained by multiplying together a value of H(x') which has been read out from the first memory section using the at least lower (N-1) bits of x' as an address, a value of I(y2,k) corresponding to y2 and k which has been generated by the adjustment coefficient generation section and a value of x1 which has been converted by the first bit shift section; and a second bit shift section for shifting the output value from the multiplication section by a number of bits according to y1, M and k.

[0052] In one embodiment of the invention, the adjustment coefficient generation section includes a second memory section for storing values of I(p,k) using p and k as an address.

[0053] In another embodiment of the invention, a=4, b=3 and c=4.

**[0054]** Thus, the invention described herein makes possible the advantages of: (1) reducing the hardware scale of an exponential calculation device which is capable of calculating  $\hat{x}$  (a/b) for a given value of x, by reducing the memory area to be used for a table; (2) realizing a decoding device capable of calculating  $\hat{x}$  (a/b)\*2 (y/c) with a high accuracy using a fixed-point-format processing unit even

when the integer x is considerably smaller than the maximum value of the variable range thereof; (3) realizing a decoding device which only has a table for relatively small integers x and still is capable of calculating  $\hat{x}$  (a/b)\*2 (y/c) even for a large value of x by using the small-capacity table; and (4) realizing a calculation method capable of a calculation involving a large value of x using a small-capacity table by the use of a simple bit shift operation, thereby realizing a decoding device capable of rapidly calculating  $\hat{x}$ (a/b)\*2 (y/c) for any given values of x and y.

**[0055]** These and other advantages of the present invention will become apparent to those skilled in the art upon reading and understanding the following detailed description with reference to the accompanying figures.

### BRIEF DESCRIPTION OF THE DRAWINGS

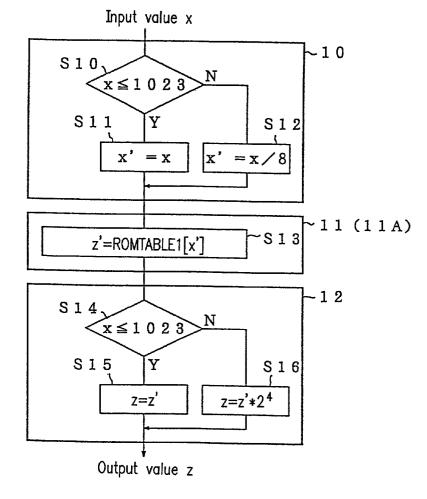

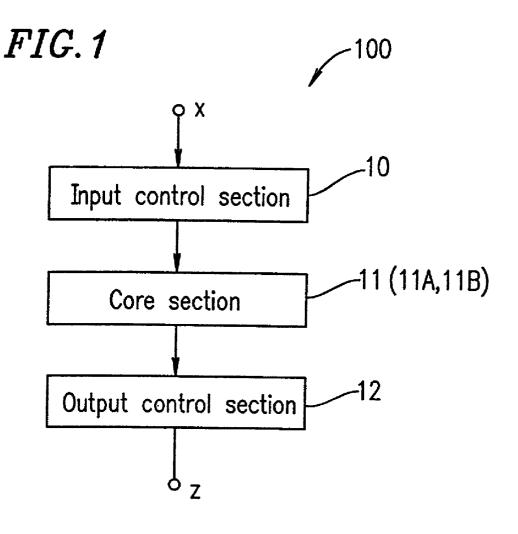

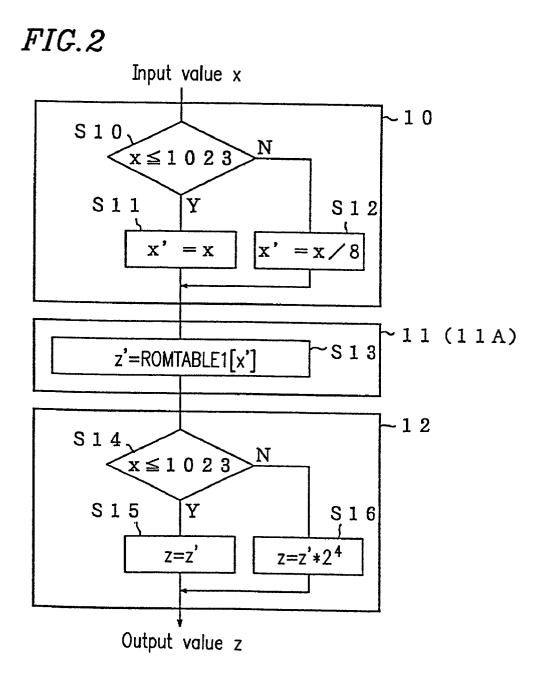

**[0056]** FIG. 1 is a block diagram illustrating a structure of an exponential calculation device 100 according to Example 1 of the present invention;

**[0057] FIG. 2** is a flow chart illustrating a signal processing method for the exponential calculation device **100**;

[0058] FIG. 3 illustrates the contents of a ROM Table 1 of a core section 11A of the exponential calculation device 100;

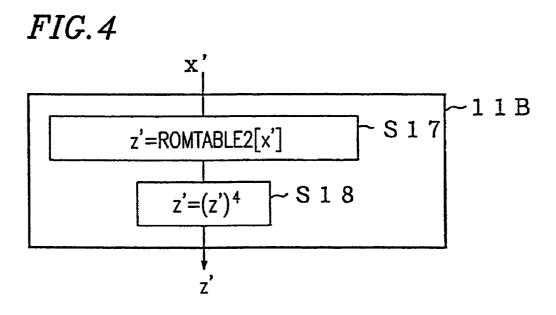

[0059] FIG. 4 is a flow chart illustrating a signal processing method for another core section 11B of the exponential calculation device 100;

[0060] FIG. 5 illustrates the contents of a ROM Table 2 of the core section 11B of the exponential calculation device 100;

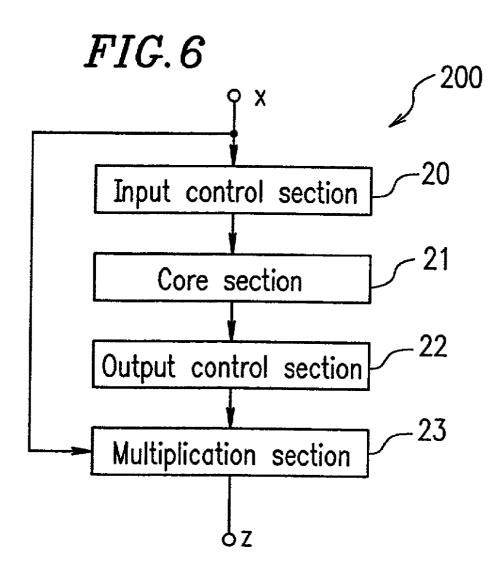

**[0061] FIG. 6** is a block diagram illustrating a structure of an exponential calculation device **200** according to Example 2 of the present invention;

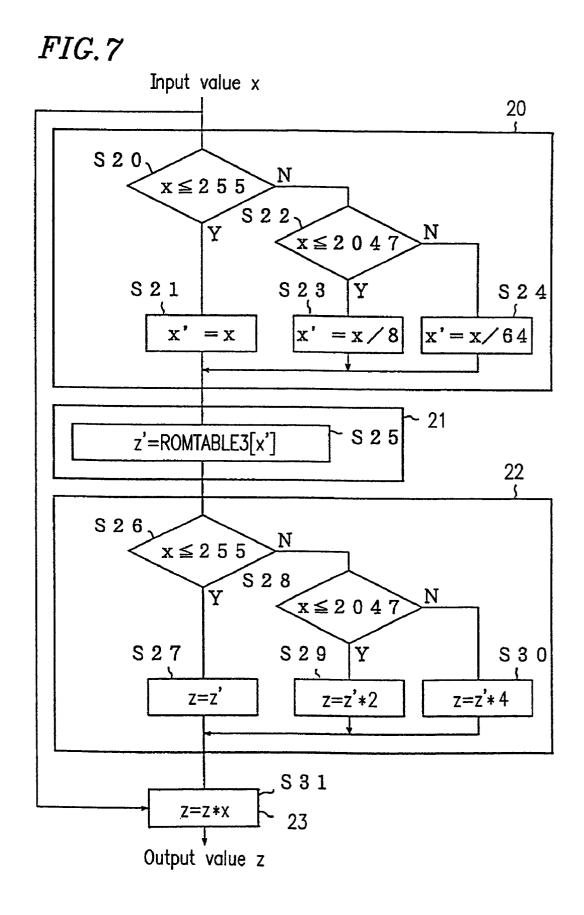

**[0062] FIG. 7** is a flow chart illustrating a signal processing method for the exponential calculation device **200**;

**[0063] FIG. 8** illustrates the contents of a ROM Table 3 of a core section **21** of the exponential calculation device **200**;

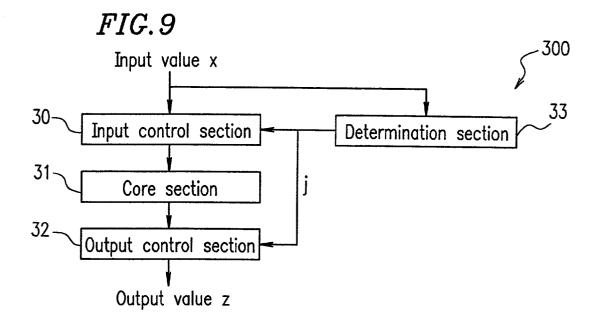

**[0064] FIG. 9** is a block diagram illustrating a structure of an exponential calculation device **300** according to Example 3 of the present invention;

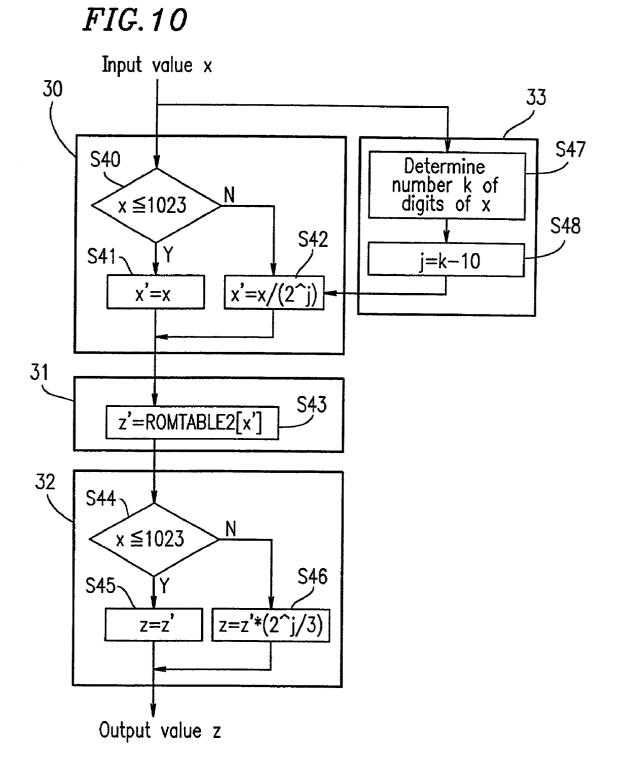

[0065] FIG. 10 is a flow chart illustrating a signal processing method for the exponential calculation device 300;

[0066] FIG. 11 illustrates a table for providing a value of 2(j/3) in an output control section 32 of the exponential calculation device 300;

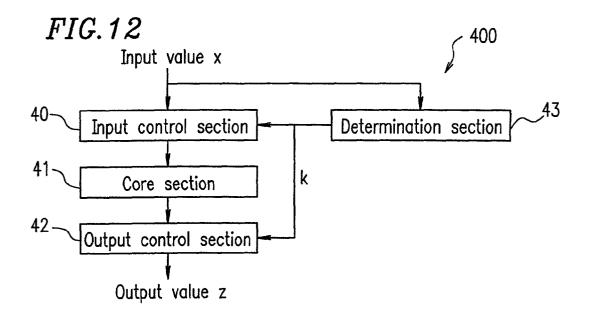

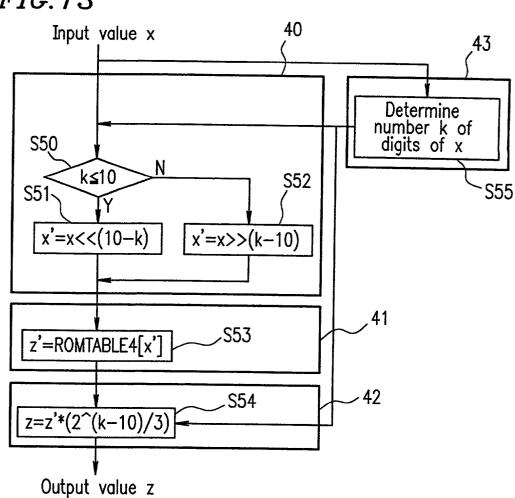

**[0067]** FIG. 12 is a block diagram illustrating a structure of an exponential calculation device 400 according to Example 4 of the present invention;

**[0068]** FIG. 13 is a flow chart illustrating a signal processing method for the exponential calculation device **400**;

[0069] FIG. 14 illustrates the contents of a ROM Table 4 of a core section 41 of the exponential calculation device 400;

[0070] FIG. 15 illustrates a table for providing a value of 2 ((k-B)/3) in an output control section 42 of the exponential calculation device 400;

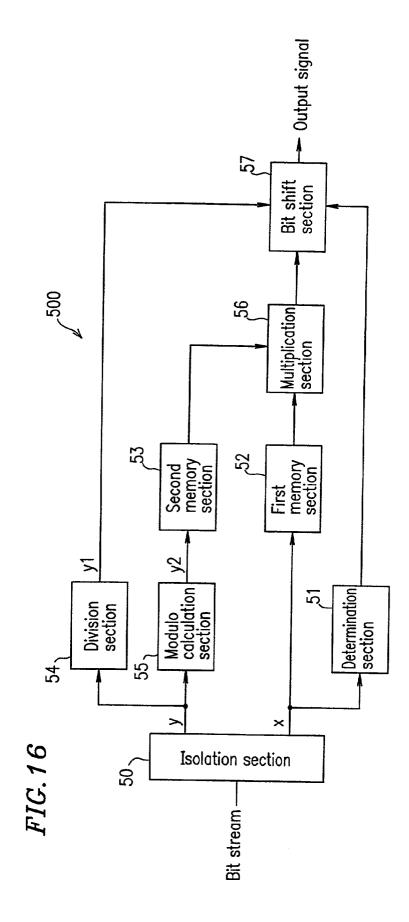

[0072] FIG. 17 illustrates the contents of a first memory section 52 of the decoding device 500;

[0073] FIG. 18 illustrates the contents of a second memory section 53 of the decoding device 500 and a second memory section 64 of a decoding device 600;

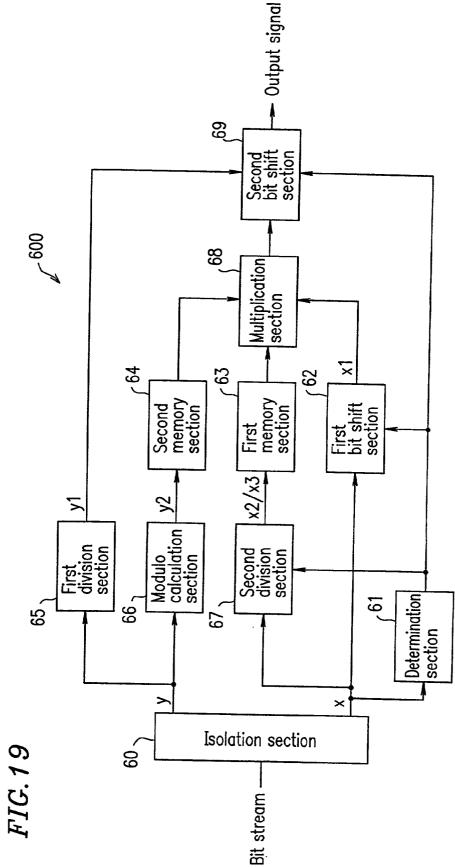

**[0074] FIG. 19** is a block diagram illustrating a structure of the decoding device **600** according to Example 6 of the present invention;

[0075] FIG. 20 illustrates the contents of a first memory section 63 of the decoding device 600 and a first memory section 73 of a decoding device 700;

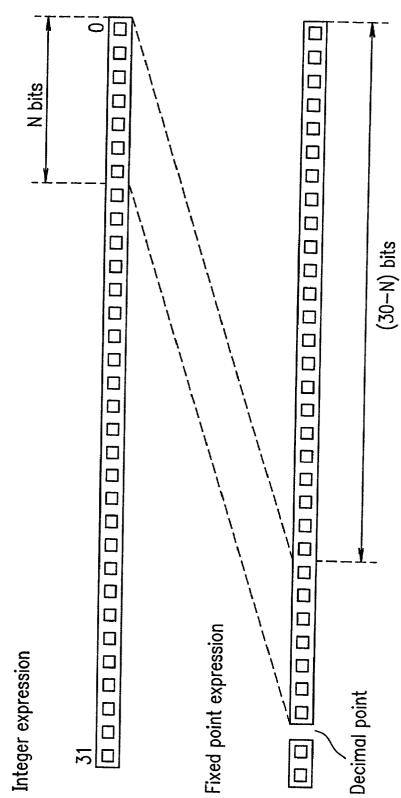

[0076] FIG. 21 illustrates a method of converting an integer value to value of a fixed point format;

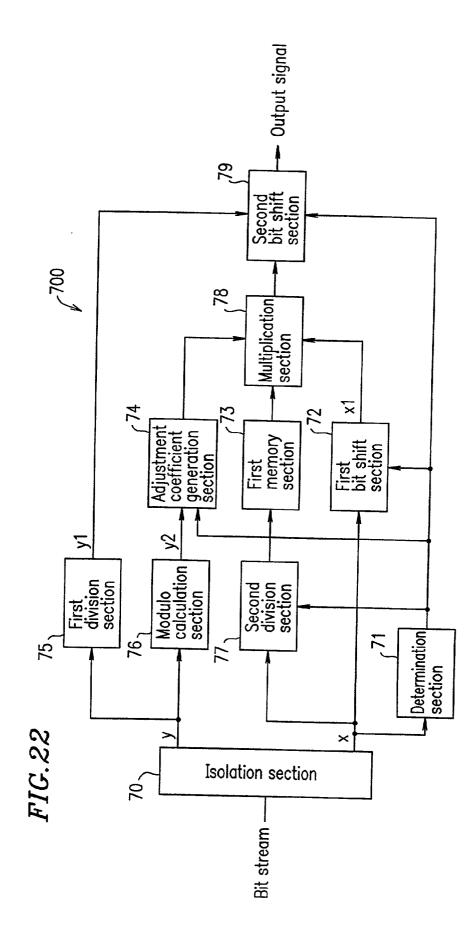

[0077] FIG. 22 is a block diagram illustrating a structure of the decoding device 700 according to Example 7 of the present invention;

[0078] FIG. 23 illustrates the contents of an adjustment coefficient generation section 74 of the decoding device 700;

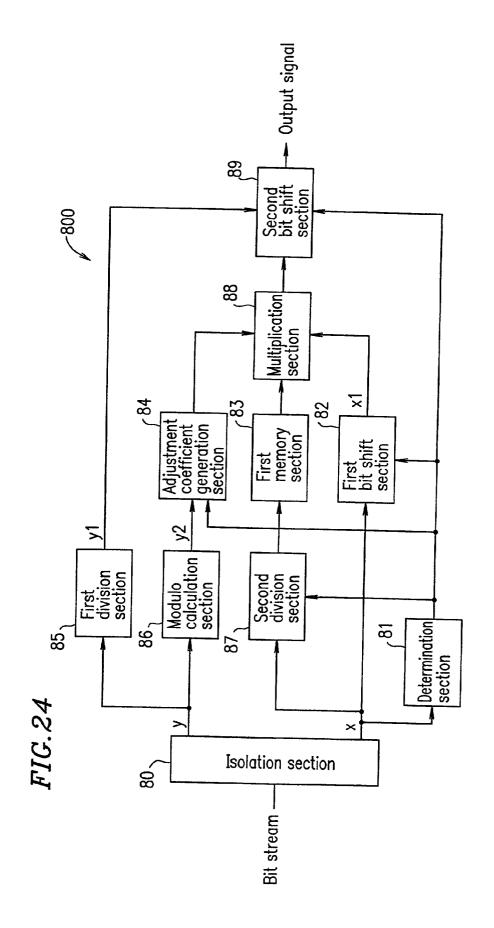

**[0079] FIG. 24** is a block diagram illustrating a structure of the decoding device **800** according to Example 8 of the present invention;

[0080] FIG. 25 illustrates the contents of an adjustment coefficient generation section 84 of the decoding device 800;

[0081] FIG. 26 illustrates the contents of a first memory section 83 of the decoding device 800;

**[0082]** FIG. 27 illustrates table of values of  $\hat{x}$  (4/3) for  $0 \le x \le 8191$  which is provided in a conventional exponential calculation device;

[0083] FIG. 28 illustrates an exemplary fixed point format;

**[0084] FIG. 29** illustrates the contents of a first table used in a conventional decoding device; and

**[0085] FIG. 30** illustrates the contents of a second table used in the conventional decoding device.

### DESCRIPTION OF THE PREFERRED EMBODIMENTS

**[0086]** The principle of the present invention will first be described. An exponential calculation device of the present invention only requires a table containing values of  $\hat{x}$  (a/b) for input values of x less than or equal to a predetermined value A, and still is capable of obtaining a value of  $\hat{x}$  (a/b) for any input value of x. The present invention does not require a large table for storing values of  $\hat{x}$  (a/b) for input values of x greater than A, and accordingly requires a memory area much smaller than that of the conventional exponential calculation device which requires a large table for storing values of  $\hat{x}$  (a/b) for all the possible input values of x.

**[0087]** The basic principle of operation of the exponential calculation device of the present invention will now be described based on arithmetic expressions. Assuming the input value to the exponential calculation device is x and the

value to be obtained is  $z=\hat{x}$  (a/b), where the input value x represents an amplitude of a signal used in decoding audio data, for example, and A denotes a threshold value of the variable range of x.

**[0088]** When  $x \le A$ , the value of  $\hat{x}$  (a/b) for the input value of x is already provided in a table, whereby the value of  $\hat{x}$  (a/b) can easily be obtained or retrieved from the table.

**[0089]** When x>A, x is first divided by a predetermined value to obtain x' such that x' A. A value x' (a/b) is read out from the table and is multiplied by the predetermined value so as to obtain the value of  $\hat{x}$  (a/b) for the given value of x. In this way, a value of  $\hat{x}$  (a/b) for any given value of x can be obtained. For example, when a=4 and b=3, and when x is in the range of 8\*A≦x>A, x' is first obtained as x'=x/8. Then, a corresponding value is read out from the table for the value of x', thereby obtaining z'. Since z'=(x/8) (4/3), the value of z= $\hat{x}$  (4/3) can be obtained as z'\*(8 (4/3))=z'\*16.

### EXAMPLE 1

**[0090]** An exponential calculation device according to

**[0091]** Example 1 of the present invention will now be described with reference to the figures. The exponential calculation device of this example performs an exponential calculation  $\hat{x}$  (4/3). In this example, the range of the input value of x is 0-8191. The range of the exponentiated value  $\hat{x}$  (4/3) and the range of the input value of x conform to the MPEG 2 audio AAC standard (see ISO/IEC 13818-7:1997, P57).

[0092] FIG. 1 is a block diagram illustrating a structure of an exponential calculation device 100 according to Example 1 of the present invention. The exponential calculation device 100 includes an input control section 10, a core section 11 and an output control section 12.

[0093] FIG. 2 is a flow chart illustrating signal processing performed by the exponential calculation device 100, showing respective signal processing steps performed by the input control section 10, the core section 11 and the output control section 12. Referring to FIG. 2, the respective components of the exponential calculation device 100 will now be described in detail.

[0094] The input control section 10 determines if the input value of x is less than or equal to a threshold value A (e.g., 1023 in this example). If the input value of x is less than or equal to 1023, the input control section 10 provides the value of x, without alteration, as x' to the core section 11. If the input value of x exceeds 1023, the input control section 10 provides a value obtained by dividing x by 2 3 as x' to the core section 11.

[0095] The core section 11 provides the value of x' (4/3) for the value of x', which is in the range from 0 to 1023.

[0096] The core section 11 illustrated in FIG. 2 is one example of the core section 11 and will hereinbelow be referred to as the "core section 11A". The core section 11A has a ROM Table 1 (z'=ROMTABLE1[x']). The core section 11A outputs a value read out from the ROM Table 1 for the value of x' as z'.

**[0097]** FIG. 3 illustrates the contents of the ROM Table 1 of the core section 11A. The ROM Table 1 contains values of x' (4/3) which have been calculated for value of x' in the range from 0 to 1023.

[0098] The output control section 12 provides the output value z' from the core section 11A, without alteration, as z when the input value of x is less than or equal to 1023, and provides a value obtained by multiplying the output value from core section 11A by 2 4 as z when x exceeds 1023.

[0099] An operation of the exponential calculation device 100 having such a structure will now be described. First, step S10 determines if a given value of x is less than or equal to 1023. When x does not exceed 1023, the process proceeds to step S11, thereby providing the value of x, without alteration, as x' to the core section 11A. If it is determined that x exceeds 1023, the process proceeds to step S12 so as to provide x' by dividing x by 2 3 to the core section 11A. The division of x by 2 3 can be performed, for example, by shifting x down by 3 bits or by first adding 4 to x and then shifting down the obtained value by 3 bits for a "0-down-1-up" round-off process, where 0.0's are rounded down and 0.1's are rounded up.

[0100] Next, in step S13, the core section 11A reads out from the ROM Table 1, as illustrated in FIG. 3, a value of x' (4/3) for the value of x' provided by the input control section 10.

**[0101]** FIG. 4 is a flow chart illustrating a signal processing procedure performed by another exemplary core section 11B for use with the exponential calculation device 100. The core sections 11A and 11B, as illustrated in FIGS. 2 and 4, respectively, may be used inter-changeably in the present invention. The core section 11B stores in a ROM Table 2 values of  $\hat{x}$  (L/b) for values of x' from 0 to the threshold value A, wherein L=a/m (where m is a positive constant). The core section 11B raises z' (from the ROM Table 2) to the power of m, and outputs the resulting value as new z'.

**[0102]** FIG. 5 illustrates the contents of the ROM Table 2 of the core section 11B. The core section 11B uses the ROM Table 2 (z'=ROMTABLE2[x']) which stores values of x' (L/b) for m=4 and L=1 (i.e., x' ( $\frac{1}{3}$ )) for values of x' in the range from 0 to 1023. Referring to FIG. 4, in step S17, z' is read out from the ROM Table 2 and, in step S18, z' is raised to the power of 4, thereby obtaining the value of x' ( $\frac{4}{3}$ ). Such an additional exponential calculation as is required in this core section 11B can easily be processed by a multiplier of a DSP, thereby maintaining a small capacity of the ROM table.

[0103] Referring back to FIG. 2, in step S14, the output control section 12 determines if the input value of x is less than or equal to 1023. When x is less than or equal to 1023, the process proceeds to step S15, thereby outputting the output value from the core section 11, without alteration. When it is determined that the input value of x exceeds 1023 in step S14, the process proceeds to step S16, thereby outputting a value obtained by multiplying the output value from the core section 11 by 2 4.

**[0104]** As described above, the present invention does not require providing values of  $\hat{x}$  (a/b) for all the possible values of x contemplated (e.g., 0-8191 in this example), but only requires providing values of  $\hat{x}$  (a/b) for input values of x less than or equal to the predetermined threshold value A=1023. In this way, values of  $\hat{x}$  (a/b) for input values of x exceeding A can also be approximately calculated. Thus, it is possible to effect an exponential calculation with small-scale hardware.

**[0105]** Herein, **1023** is selected as the threshold value A for the following reasons. Under the MPEG 2 audio AAC standard, the input value of  $\hat{x}$  (4/3) can range from 0 to 8191. In fact, however, values from 0 to 1023 are involved in most cases. Therefore, for x ranging from 0 to 1023, the calculation  $\hat{x}$  (4/3) should accurately be performed so as not to deteriorate the sound quality. However, for x of 1024 or greater, since x rarely takes such a large value, the sound quality would not significantly deteriorate even if the calculation is not as accurate as that for x ranging from 0 to 1023. Accordingly, for x exceeding 1023, an approximate calculation can be performed according to the method of the present example.

**[0106]** Among the values from 0 to 1023, actual calculations particularly involve, in most cases, values from 0 to 255. Accordingly, the statistic threshold value A may be set to 255. The following example of the invention will discuss an example where the statistic threshold value is set to 255.

# EXAMPLE 2

[0107] Example 2 of the present invention will now be described with reference to the figures. This example provides an exponential calculation device for obtaining a value of  $\hat{x}$  (4/3), as an exemplary exponentiated value  $\hat{x}$  (a/b). The exponential calculation device of the present example can be characterized in that it performs the exponential calculation  $\hat{x}$  (a/b) by performing two exponential calculations for an integral portion of a/b and for a fractional portion thereof (where a and b are each an integer, and a>b). The exponential calculation for the integral portion of a/b can therefore be expressed as  $\hat{x}$  (int(a/b)), whereas the exponential calculation for the fractional portion of a/b can be expressed as  $\hat{x}$ ((a%b)/b). The symbol "int()" as used herein denotes a round-down operation, where any fractional portion of the number is cut off, and the symbol "%" as used herein denotes a modulo operation for obtaining a remainder (integer) of a division.

**[0108]** As in Example 1, the range of input values of x is from 0 to 8191, conforming to the MPEG 2 audio AAC standard (see ISO/IEC 13818-7:1997, P57).

[0109] FIG. 6 is a block diagram illustrating a structure of an exponential calculation device 200 according to Example 2 of the present invention. The exponential calculation device 200 includes an input control section 20, a core section 21, an output control section 22 and a multiplication section 23.

**[0110]** FIG. 7 is a flow chart illustrating a signal processing method of the exponential calculation device 200, showing the respective signal processing procedures performed by the input control section 20, the core section 21, the output control section 22 and the multiplication section 23.

**[0111]** When the input value of x is less than or equal to 255 (first threshold value A1), the input control section **20** provides the value of x, without alteration, to the core section **21** as x'. When the input value of x exceeds 255 but is less than or equal to 2047 (second threshold value A2), the input control section **20** provides a value obtained by dividing x by 2 3 to the core section **21** as x'. When the input value of x is equal to or grater than 2048, the input control section **20** provides a value obtained by dividing x by **26** to the core section **21** as x'.

**[0112] FIG. 8** illustrates the contents of a ROM Table 3 of the exponential calculation device **200**. The core section **21** has the ROM Table 3, as illustrated in **FIG. 8**, and provides values of x' ((a%b)/b) (i.e., x' ( $\frac{1}{3}$ )) for values of x' from 0 to 255. The values of x' ( $\frac{1}{3}$ ) for values of x' from 0 to 255 are stored in the ROM Table 3 in advance.

**[0113]** When the input value of x is less than or equal to the first threshold value A1, the output control section 22 outputs the output value from the core section 21, without alteration. When the input value of x exceeds the first threshold value A1 but less than or equal to the second threshold value A2, the output control section 22 outputs a value obtained by multiplying the output value z' from the core section 21 by 2 (a%b) as z. When the input value of x exceeds the second threshold value A2, the output control section 22 outputs a value obtained by multiplying the output value z' from the core section 21 by 2 (a%b) as z. When the input value of x exceeds the second threshold value A2, the output control section 22 outputs a value obtained by multiplying the output value from the core section 21 by 2 ((a%b)\*2). The multiplication section 23 multiplies  $\hat{x}$  (int (a/b)) with the output value z from the output control section 22 so as to output the multiplied value as a new value of z.

[0114] An operation of the exponential calculation device 200 of Example 2 having such a structure will now be described. Referring to FIG. 7, in step S20, the input control section 20 determines if the input value of x is less than or equal to the first threshold value, 255. When the input value of x is less than or equal to 255, the process proceeds to step S21, thereby providing the value x, without alteration, to the core section 21 as x'. If it is determined in step S20 that the input value of x is equal to or greater than 256, the process proceeds to step S22, where it is determined if the input value of x is less than or equal to the second threshold value A2, 2047. When x is less than or equal to 2047, the process proceeds to step S23, where a value obtained by dividing x by 2 3 is provided to the core section 21 as x'. When it is determined in step S22 that the input value of x is equal to or greater than 2048, the process proceeds to step S24, where a value obtained by dividing x by 2 6 is provided to the core section 21 as x.

**[0115]** The division of x by 2 3 can be performed, for example, by shifting x down by 3 bits or by first adding 4 to x and then shifting down the obtained value by 3 bits for the "0-down-1-up" round-off process. The division of x by 2 6 can be performed, for example, by shifting x down by 6 bits or by first adding 32 to x and then shifting down the obtained value by 6 bits for the "0-down-1-up" round-off process.

[0116] Then, in step S25, the core section 21 reads out a value of  $x'(\frac{1}{3})$  from the ROM Table 3, as illustrated in FIG. 8, for a value of x' provided by the input control section 20.

[0117] Then, in step S26, the output control section 22 determines if the input value of x is less than or equal to 255. If x is less than or equal to 255, the process proceeds to step S27, thereby outputting the output value from the core section 21, without alteration. When it is determined in step S26 that the input value of x is equal to or greater than 256, the process proceeds to step S28. Step S28 determines if the input value of x is less than or equal to 2047. If x is less than or equal to 2047, the process proceeds to step S29. If x is equal to or greater than 2048, the process proceeds to step S30. Step S29 outputs a value obtained by multiplying the output value from the core section 21 by 2 1, and Step S30 outputs a value obtained by multiplying the output value from the core section 21 by 2 2.

**[0118]** Finally, instep S31, the multiplication section 23 multiplies the input value of x with the output value from the output control section 22. In this instance, the value to be obtained is  $\hat{x}$  (4/3), and the output value from the output control section 22 is  $\hat{x}$  ( $\frac{1}{3}$ ). Therefore,  $\hat{x}$  (4/3) is calculated by multiplying the original value of x with  $\hat{x}$  ( $\frac{1}{3}$ ).

**[0119]** As described above, in the present example, an exponential calculation device for calculating  $\hat{x}$  (a/b) (where a>b) for an input value of x includes a core section for providing values of x' ((a%b)/b) for values of x' from 0 to A. Moreover, the exponential calculation device of the present invention is provided with a multiplication section for multiplying a value of  $\hat{x}$  (int (a/b)), for an input value of x, with an output value from the output control section.

**[0120]** Thus, it is not required to store values of  $\hat{x}$  (a/b) for all the possible input values of x contemplated (0 to 8191 in this example), but it is only required to store values of  $\hat{x}$  ((a%b)/b) for input values of x less than or equal to the predetermined value A (255 in this example). In this way, it is possible to exponentiate any value of x. Thus, it is possible to perform, using small-scale hardware, an exponential calculation with a fractional exponent.

#### EXAMPLE 3

**[0121]** An exponential calculation device according to Example 3 of the present invention will now be described with reference to the figures. This example provides an exponential calculation device for obtaining a value of  $\hat{x}$  ( $\frac{1}{3}$ ), as an exemplary exponentiated value  $\hat{x}$  (a/b). The input value of x is assumed to range from 0 to 8191.

[0122] FIG. 9 is a block diagram illustrating a structure of an exponential calculation device 300 according to Example 3 of the present invention. The exponential calculation device 300 includes an input control section 30, a core section 31, an output control section 32 and a determination section 33.

[0123] FIG. 10 is a flow chart illustrating a signal processing method of the exponential calculation device 300, showing the respective signal processing procedures performed by the input control section 30, the core section 31, the output control section 32 and the determination section 33.

[0124] The input control section 30 determines if the input value of x is less than or equal to the threshold value A (e.g., 1023 in this example). If x is less than or equal to 1023, the input control section 30 provides the value of x, without alteration, to the core section 31 as x'. If x is greater than 1023, the input control section 30 provides a value obtained by dividing x by 2 j to the core section 31 as x'.

**[0125]** The value of j is determined by the determination section **33** as follows. The determination section **33** first determines the number k of digits of x represented in a binary form, and then determines the value of j such that j=k-10. For example, when the input value of x is equal to or greater than 1024 and less than 2048, the value of j is 1. The value "10" is the number of digits of a value 1024 represented in the binary form. Accordingly, the value of j represents by how many digits x is greater than the threshold value A in the binary form.

**[0126]** As the core section **11B** of Example 1, the core section **31** includes a ROM Table 2, as illustrated in **FIG. 5**.