(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3793190号

(P3793190)

(45) 発行日 平成18年7月5日(2006.7.5)

(24) 登録日 平成18年4月14日(2006.4.14)

(51) Int.C1.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 27/092  | (2006.01) | HO1L 27/08 | 321D |

| HO1L 21/8238 | (2006.01) | HO1L 27/08 | 321N |

| HO1L 21/28   | (2006.01) | HO1L 21/28 | 301R |

| HO1L 29/423  | (2006.01) | HO1L 21/28 | 301S |

| HO1L 29/49   | (2006.01) | HO1L 29/58 | G    |

請求項の数 8 (全 21 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2003-327517 (P2003-327517) |

| (22) 出願日  | 平成15年9月19日 (2003.9.19)       |

| (65) 公開番号 | 特開2005-93856 (P2005-93856A)  |

| (43) 公開日  | 平成17年4月7日 (2005.4.7)         |

| 審査請求日     | 平成15年9月19日 (2003.9.19)       |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100058479<br>弁理士 鈴江 武彦                |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                 |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                |

| (74) 代理人  | 100084618<br>弁理士 村松 貞男                |

| (74) 代理人  | 100092196<br>弁理士 橋本 良郎                |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

第1素子領域および第2素子領域を有する半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の全面にこのゲート絶縁膜に対してエッチング選択比を有するマスク材を形成した後、このマスク材を選択的にエッチングして前記第1素子領域に位置する前記ゲート絶縁膜部分を露出させるための開口部を形成する工程と、

前記開口部を含むマスク材の全面に第1導電材料膜を形成する工程と、

前記第1導電材料膜をパターニングして少なくとも前記第1素子領域に位置する前記ゲート絶縁膜部分にパターン状の第1導電材料膜を形成した後、露出したマスク材をエッチング除去する工程と、

前記パターン状の第1導電材料膜を含む前記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成し、この第2導電材料膜で前記第2素子領域に位置する前記ゲート絶縁膜部分を覆う工程と、

前記第1素子領域のゲート絶縁膜上に前記第1導電材料膜を有する第1ゲート電極を形成すると共に、前記第2素子領域のゲート絶縁膜上に前記第2導電材料膜からなる第2ゲート電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

## 【請求項2】

第1素子領域および第2素子領域を有する半導体基板上の層間絶縁膜に複数のゲート溝

をそれら底部に前記各素子領域が位置する前記半導体基板表面をそれぞれ露出させるよう

に形成する工程と、

前記各ゲート溝を含む全面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の全面にこのゲート絶縁膜に対してエッチング選択比を有するマスク

材を形成した後、このマスク材を選択的にエッチングして前記第1素子領域に位置する前

記ゲート溝のゲート絶縁膜部分を露出させるための開口部を形成する工程と、

前記開口部を含むマスク材の全面に第1導電材料膜を形成する工程と、

前記第1導電材料膜を前記開口部を除く前記マスク材表面が露出するまで化学機械研磨

することによりパターニングして前記第1素子領域に位置する前記ゲート溝を含む前記開

口部内にパターン状の第1導電材料膜を形成する工程と、

露出したマスク材をエッチング除去して前記第2素子領域に位置するゲート溝を露出さ

せる工程と、

前記パターン状の第1導電材料膜および前記第2素子領域に位置するゲート溝を含む前

記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する工

程と、

前記第1素子領域のゲート溝内のゲート絶縁膜上に前記第1導電材料膜を有する第1ゲ

ート電極を形成すると共に、前記第2素子領域のゲート溝内のゲート絶縁膜上に前記第2

導電材料膜からなる第2ゲート電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

#### 【請求項3】

第1素子領域および第2素子領域を有する半導体基板上の層間絶縁膜に複数のゲート溝

をそれら底部に前記各素子領域が位置する前記半導体基板表面をそれぞれ露出させるよう

に形成する工程と、

前記各ゲート溝の内面を含む全面にゲート絶縁膜を形成する工程と、

前記各ゲート溝内を含む前記ゲート絶縁膜全面にこのゲート絶縁膜に対してエッチング

選択比を有するマスク材を形成した後、前記層間絶縁膜上のゲート絶縁膜表面が露出する

まで化学機械研磨することにより前記各ゲート溝にマスク材をそれぞれ埋め込む工程と、

前記第1素子領域に位置する前記ゲート溝内のマスク材を選択的にエッチング除去して

そのゲート溝内のゲート絶縁膜部分を露出させる工程と、

前記露出したゲート溝内のゲート絶縁膜、前記層間絶縁膜および残存したマスク材の上

に薄い第1導電材料膜を形成する工程と、

前記第1導電材料膜をパターニングして前記第1素子領域に位置する前記ゲート溝内の

ゲート絶縁膜を含む前記層間絶縁膜上にパターン状の第1導電材料膜を形成すると共に、

前記残存したマスク材を露出させる工程と、

露出した残存マスク材をエッチング除去して前記第2素子領域に位置するゲート溝を露

出させる工程と、

前記パターン状の第1導電材料膜および前記第2素子領域に位置するゲート溝を含む前

記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する工

程と、

前記第1素子領域のゲート溝内のゲート絶縁膜上に前記第1導電材料膜を有する第1ゲ

ート電極を形成すると共に、前記第2素子領域のゲート溝内のゲート絶縁膜上に前記第2

導電材料膜からなる第2ゲート電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

#### 【請求項4】

前記ゲート絶縁膜は、高比誘電率絶縁材料から作られることを特徴とする請求項1ない

し3いずれか記載の半導体装置の製造方法。

#### 【請求項5】

前記マスク材は、TEOSから作られることを特徴とする請求項1ないし3いずれか記

載の半導体装置の製造方法。

#### 【請求項6】

10

20

30

40

50

前記マスク材のエッティングは、湿式エッティングまたはケミカルドライエッティングによりなされることを特徴とする請求項 1 ないし 3 いずれか記載の半導体装置の製造方法。

【請求項 7】

前記第 1 導電材料膜は、窒化金属膜であり、前記第 2 導電材料膜は金属膜であることを特徴とする請求項 1 ないし 3 いずれか記載の半導体装置の製造方法。

【請求項 8】

前記各ゲート電極の形成工程は、前記第 2 導電材料膜、パターン状の第 1 導電材料膜およびゲート絶縁膜を前記各ゲート溝を除く前記層間絶縁膜の表面が露出するまで化学機械研磨することによりなされることを特徴とする請求項 2 または 3 記載の半導体装置の製造方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、詳しくは仕事関数の異なるゲート電極を有する半導体装置の製造方法に係わる。

【背景技術】

【0002】

近年、サブ  $\mu$ m の MOSFET 素子の開発に伴ってゲート電極の空乏化が重要な課題となっている。従来、ゲート電極として不純物をドープした多結晶シリコンが採用されている。しかしながら、不純物ドープ多結晶シリコンからなるゲート電極のゲート絶縁膜界面に生じる空乏層によって、絶縁膜の膜厚が実効的に増加し、駆動力の低下を生じる。この駆動力の低下は、ゲート絶縁膜の微細化が進むと無視できない問題になる。

20

【0003】

このような多結晶シリコンに代えて金属からなるゲート電極を採用することによりゲート電極の空乏層を抑えることが有効である。また、金属ゲート電極はシリコンのミッドバンドギャップに相当する仕事関数を有するために、例えば NMOS および PMOS の領域で対称的しきい値電圧を形成することができる単一ゲート電極として適用することができる。

【0004】

しかしながら、例えばミッドバンドギャップに相当する仕事関数を有する金属ゲート電極を単一ゲート電極とする CMOS において、NMOS および PMOS の素子領域でのフラットバンド電圧（絶対値）が減少されて、不純物ドープ多結晶シリコン電極を用いた場合と比べてしきい値電圧（絶対値）が増加する現象が生じる。しきい値電圧を下げるために、カウンタドーピングを用いて埋め込みチャンネルを形成することができるが、その場合には MOSFET 素子の短チャンネル効果が増加し、微細な素子が形成できない。

30

【0005】

このようなことから、例えば CMOS において NMOS および PMOS の素子領域に互いに異なる仕事関数を持つ金属ゲートを各々形成することが行われている。特許文献 1 には、半導体素子のデュアル金属ゲートの形成方法が開示されている。このデュアル金属ゲート形成方法は、PMOS 領域および NMOS 領域を有し、かつ前記 PMOS 領域および NMOS 領域の各々の上にダミーゲートが形成された半導体基板を供する工程と、前記ダミーゲートを覆うように前記半導体基板上に層間絶縁膜を形成する工程と、前記ダミーゲートが露出されるまで前記層間絶縁膜を研磨する工程と、前記 PMOS 領域と NMOS 領域とに形成されたダミーゲートからいずれか一つを選択的に除去して、第 1 金属ゲート領域を特定する第 1 溝を形成する工程と、前記第 1 溝を含んだ半導体基板の全領域上に第 1 ゲート絶縁膜と第 1 金属膜を順次形成する工程と、前記層間絶縁膜が露出されるまで前記第 1 金属膜と第 1 ゲート絶縁膜とをエッティングして前記第 1 溝内に第 1 金属ゲートを形成する工程と、残りのダミーゲートを除去して第 2 金属ゲート領域を特定する第 2 溝を形成する工程と、前記第 2 溝を含んだ半導体基板の全領域上に第 2 ゲート絶縁膜と第 2 金属膜を順次形成する工程と、前記層間絶縁膜が露出されるまで前記第 2 金属膜と第 2 ゲート絶

40

50

縁膜とをエッティングして前記第2溝内に第2金属ゲートを形成する工程とを含む。

【0006】

しかしながら、前記特許文献1の方法では1つのダミーゲートを除去して第1溝を形成し、この第1溝に第1ゲート絶縁膜および第1金属ゲートを埋め込んだ後、別の(残りの)ダミーゲートを除去して第2溝を形成し、この第2溝に第2ゲート絶縁膜および第2金属ゲートを埋め込んでデュアル金属ゲートを形成するため、ゲート絶縁膜の成膜工程が2回必要で、工程が煩雑になる。また、第2ゲート絶縁膜を成膜する工程において第1金属ゲートが露出しているため、第2ゲート絶縁膜の信頼性を低下させる。さらに、第2ゲート絶縁膜を600以上の高温で成膜すると、露出した第2金属ゲートが劣化する虞がある。

10

【特許文献1】特開2002-198441

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、半導体基板上に1回のみの成膜工程でゲート絶縁膜を形成した後、このゲート絶縁膜上に仕事関数の異なる導電材料を有するゲート電極をそれぞれ形成することが可能な半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0008】

本発明の第1態様によると、第1素子領域および第2素子領域を有する半導体基板上にゲート絶縁膜を形成する工程と、

20

前記ゲート絶縁膜の全面にこのゲート絶縁膜に対してエッティング選択比を有するマスク材を形成した後、このマスク材を選択的にエッティングして前記第1素子領域に位置する前記ゲート絶縁膜部分を露出させるための開口部を形成する工程と、

前記開口部を含むマスク材の全面に第1導電材料膜を形成する工程と、

前記第1導電材料膜をパターニングして少なくとも前記第1素子領域に位置する前記ゲート絶縁膜部分にパターン状の第1導電材料膜を形成した後、露出したマスク材をエッティング除去する工程と、

前記パターン状の第1導電材料膜を含む前記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成し、この第2導電材料膜で前記第2素子領域に位置する前記ゲート絶縁膜部分を覆う工程と、

30

前記第1素子領域のゲート絶縁膜上に前記第1導電材料膜を有する第1ゲート電極を形成すると共に、前記第2素子領域のゲート絶縁膜上に前記第2導電材料膜からなる第2ゲート電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法が提供される。

【0009】

本発明の第2態様によると、第1素子領域および第2素子領域を有する半導体基板上の層間絶縁膜に複数のゲート溝をそれら底部に前記各素子領域が位置する前記半導体基板表面をそれぞれ露出させるように形成する工程と、

前記各ゲート溝を含む全面にゲート絶縁膜を形成する工程と、

40

前記ゲート絶縁膜の全面にこのゲート絶縁膜に対してエッティング選択比を有するマスク材を形成した後、このマスク材を選択的にエッティングして前記第1素子領域に位置する前記ゲート溝のゲート絶縁膜部分を露出させるための開口部を形成する工程と、

前記開口部を含むマスク材の全面に第1導電材料膜を形成する工程と、

前記第1導電材料膜を前記開口部を除く前記マスク材表面が露出するまで化学機械研磨することによりパターニングして前記第1素子領域に位置する前記ゲート溝を含む前記開口部内にパターン状の第1導電材料膜を形成する工程と、

露出したマスク材をエッティング除去して前記第2素子領域に位置するゲート溝を露出させる工程と、

前記パターン状の第1導電材料膜および前記第2素子領域に位置するゲート溝を含む前

50

記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する工程と、

前記第1素子領域のゲート溝内のゲート絶縁膜上に前記第1導電材料膜を有する第1ゲート電極を形成すると共に、前記第2素子領域のゲート溝内のゲート絶縁膜上に前記第2導電材料膜からなる第2ゲート電極を形成する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

【0010】

本発明の第3の態様によると、第1素子領域および第2素子領域を有する半導体基板上の層間絶縁膜に複数のゲート溝をそれら底部に前記各素子領域が位置する前記半導体基板表面をそれぞれ露出させるように形成する工程と、

10

前記各ゲート溝の内面を含む全面にゲート絶縁膜を形成する工程と、

前記各ゲート溝内を含む前記ゲート絶縁膜全面にこのゲート絶縁膜に対してエッチング選択比を有するマスク材を形成した後、前記層間絶縁膜上のゲート絶縁膜表面が露出するまで化学機械研磨することにより前記各ゲート溝にマスク材をそれぞれ埋め込む工程と、

前記第1素子領域に位置する前記ゲート溝内のマスク材を選択的にエッチング除去してそのゲート溝内のゲート絶縁膜部分を露出させる工程と、

前記露出したゲート溝内のゲート絶縁膜、前記層間絶縁膜および残存したマスク材の上に薄い第1導電材料膜を形成する工程と、

前記第1導電材料膜をパターニングして前記第1素子領域に位置する前記ゲート溝内のゲート絶縁膜を含む前記層間絶縁膜上にパターン状の第1導電材料膜を形成すると共に、前記残存したマスク材を露出させる工程と、

20

露出した残存マスク材をエッチング除去して前記第2素子領域に位置するゲート溝を露出させる工程と、

前記パターン状の第1導電材料膜および前記第2素子領域に位置するゲート溝を含む前記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する工程と、

前記第1素子領域のゲート溝内のゲート絶縁膜上に前記第1導電材料膜を有する第1ゲート電極を形成すると共に、前記第2素子領域のゲート溝内のゲート絶縁膜上に前記第2導電材料膜からなる第2ゲート電極を形成する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

30

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施形態を詳細に説明する。

【0012】

(第1実施形態)

(第1工程)

第1素子領域および第2素子領域を有する半導体基板上にゲート絶縁膜を形成する。つづいて、このゲート絶縁膜の全面にこのゲート絶縁膜に対してエッチング選択比を有するマスク材を形成した後、このマスク材を選択的にエッチングして前記第1素子領域に位置する前記ゲート絶縁膜部分を露出させるための開口部を形成する。

40

【0013】

前記第1素子領域および第2素子領域は、例えば前記半導体基板に形成した薄溝型素子分離領域で分離する。

【0014】

前記ゲート絶縁膜は、例えばシリケート、高比誘電率絶縁材料から作ることができる。特に、高比誘電率絶縁材料からゲート絶縁膜を形成すればその膜厚を厚くすることが可能になるため、トンネルリークを抑制ないし防止して高信頼性の半導体装置を製造できる。このような高比誘電率絶縁材料としては、例えばTa<sub>2</sub>O<sub>5</sub>、またはHf<sub>x</sub>Al<sub>y</sub>Zr<sub>1-y</sub>Pdの少なくとも1つの金属を含む酸化物、酸窒化物、およびシリケートを挙げることができる。

50

## 【0015】

前記マスク材は、前記ゲート絶縁膜に対してエッチング選択比を有する材料であれば如何なるものでもよいが、特に第1導電材料膜と反応しない材料、例えばTEOS、シリザン、ボロンリン添加ガラス(BPSG)、ポリアリレンのような有機材料から形成されることが好ましい。

## 【0016】

## (第2工程)

前記開口部を含むマスク材の全面に第1導電材料膜を形成する。つづいて、この第1導電材料膜をパターニングして少なくとも前記第1素子領域に位置する前記ゲート絶縁膜部分にパターン状の第1導電材料膜を形成する。この時、前記マスク材が露出される。露出したマスク材をエッチング除去することにより、前記マスク材で覆われた前記第2素子領域が位置するゲート絶縁膜部分が露出する。

10

## 【0017】

前記第1工程、第2工程でのマスク材のエッチングは、湿式エッチング法またはケミカルドライエッチング法を採用することが好ましい。このような湿式エッチング法またはケミカルドライエッチング法を採用することにより、プラズマエッチング法に比べて下地のゲート絶縁膜へのエッチングダメージを低減することが可能になる。

## 【0018】

## (第3工程)

前記パターン状の第1導電材料膜を含む前記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する。この時、第2導電材料膜の一部は前記第2素子領域に位置するゲート絶縁膜部分に直接接する。つづいて、前記パターン状の第1導電材料膜および第2導電材料膜を例えればレジストパターンをマスクとしたリアクティブイオンエッチング(RIE)によりパターニングすることにより前記第1素子領域のゲート絶縁膜上に前記第1導電材料膜および第2導電材料膜の積層膜からなる第1ゲート電極を形成すると共に、前記第2素子領域のゲート絶縁膜上に前記第2導電材料膜からなる第2ゲート電極を形成する。形成された第1ゲート電極は、積層構造を有するが、その仕事関数はゲート絶縁膜に接する第1導電材料膜により決定される。

20

## 【0019】

前記第1、第2の導電材料膜において、NMOS側の導電材料としては例えばTiN、WN、TaN、MoSi、WSiなどの仕事関数が4.6eV未満の金属、金属の窒化物、シリサイド、合金などの金属材料が適している。また、PMOS側の導電材料としては例えばW、Ta、Pt、Moなどの仕事関数が4.6eV以上の金属、シリサイド、合金などの金属材料を使うのが適している。ただし、必ずしも前記材料、仕事関数に限定されるものではない。また、同じ金属材料でも成膜条件により仕事関数が異なる場合があるので上げた例は一例に過ぎない。例えばWは、仕事関数が4.3~5.2の間で変化することが知られているため、NMOS、PMOS両方に使用できる場合もある。

30

## 【0020】

以上、第1実施形態によれば仕事関数の異なる導電材料を有する第1、第2のゲート電極を備えた半導体装置を製造することができる。

40

## 【0021】

また、仕事関数の異なる第1、第2のゲート電極下のゲート絶縁膜は1回のみの成膜工程により形成できるため、従来のように仕事関数の異なる第1、第2の金属ゲートを形成する毎にゲート絶縁膜を形成、つまり2回のゲート絶縁膜の成膜工程が必要である場合に比べて、半導体装置の製造工程の簡略化、量産化が可能になる。

## 【0022】

さらに、ゲート絶縁膜を例えれば600以上的高温で成膜しても、仕事関数の異なる第1、第2のゲート電極はこのゲート絶縁膜の成膜後に形成するため、その成膜工程でのゲート電極への熱影響を回避でき、信頼性の高い半導体装置を製造できる。

## 【0023】

50

(第2実施形態)

(第1工程)

第1素子領域および第2素子領域を有する半導体基板上の層間絶縁膜に複数のゲート溝をそれら底部に前記各素子領域が位置する前記半導体基板表面をそれぞれ露出させるように形成する。つづいて、これらゲート溝を含む全面にゲート絶縁膜を形成する。ひきつづき、このゲート絶縁膜の全面にこのゲート絶縁膜に対してエッティング選択比を有するマスク材を形成する。この後、前記マスク材を選択的にエッティングして前記第1素子領域に位置する前記ゲート溝のゲート絶縁膜部分を露出させるための開口部を形成する。

【0024】

前記第1素子領域および第2素子領域は、例えば前記半導体基板に形成した薄溝型素子分離領域で分離する。 10

【0025】

前記層間絶縁膜は、例えばシリコン酸化膜を用いることができる。

【0026】

前記ゲート絶縁膜およびマスク材は、前記第1実施形態で説明したのと同様な材料のものを用いることができる。

【0027】

(第2工程)

前記開口部を含むマスク材の全面に第1導電材料膜を形成する。つづいて、この第1導電材料膜をパターニングして前記第1素子領域に位置する前記ゲート溝を含む前記開口部内にパターン状の第1導電材料膜を形成する。同時に、前記マスク材が露出される。この後、露出したマスク材をエッティング除去して第2素子領域に位置するゲート溝を露出させる。 20

【0028】

前記パターン状の第1導電材料膜は、例えば1)レジストパターンをマスクとしたリアクティブイオンエッティング(RIE)によりパターニングする方法、2)前記第1導電材料膜を前記開口部を除く前記マスク材表面が露出するまで化学機械研磨(CMP:Chemical Mechanical polishing)する方法、を採用することができる。特に、2)の方法は1)の方法に比べて工程の簡略化を図ることが可能になる。

【0029】

前記第1工程、第2工程でのマスク材のエッティングは、湿式エッティング法またはケミカルドライエッティング法を採用することが好ましい。このような湿式エッティング法またはケミカルドライエッティング法を採用することにより、プラズマエッティング法に比べて下地のゲート絶縁膜へのエッティングダメージを低減することが可能になる。 30

【0030】

(第3工程)

前記パターン状の第1導電材料膜および前記第2素子領域に位置するゲート溝を含む前記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する。この時、第2導電材料膜の一部は前記第2素子領域に位置するゲート溝内のゲート絶縁膜部分に直接接する。つづいて、前記パターン状の第1導電材料膜および第2導電材料膜を例えばレジストパターンをマスクとしたRIEによりパターニングすることにより前記第1素子領域のゲート溝内にゲート絶縁膜を介して第1導電材料膜が埋め込まれた構造の第1ゲート電極を形成すると共に、前記第2素子領域のゲート溝内にゲート絶縁膜を介して第2導電材料膜が埋め込まれた構造の第2ゲート電極を形成する。形成された第1ゲート電極は、績層構造を有するが、その仕事関数はゲート絶縁膜に接する第1導電材料膜により決定される。 40

【0031】

前記第1、第2の導電材料膜において、NMOS側の導電材料としては例えばTiN、WN, TaN, MoSi, WSiなどの仕事関数が4.6eV未満の金属、金属の窒化物、シリサイド、合金などの金属材料が適している。また、PMOS側の導電材料としては

例えばW, Ta, Pt, Moなどの仕事関数が4.6eV以上の金属、シリサイド、合金などの金属材料を使うのが適している。ただし、必ずしも前記材料、仕事関数に限定されるものではない。また、同じ金属材料でも成膜条件により仕事関数が異なる場合があるので上げた例は一例に過ぎない。例えばWは、仕事関数が4.3~5.2の間で変化することが知られているため、NMOS、PMOS両方に使用できる場合もある。

#### 【0032】

なお、前記第1、第2のゲート電極の形成において前記第2導電材料膜、パターン状の第1導電材料膜およびゲート絶縁膜を前記各ゲート溝を除く前記層間絶縁膜の表面が露出するまでCMP処理することによって、前記第1素子領域のゲート溝内にゲート絶縁膜を介して第1導電材料からなる第1ゲート電極を埋め込むと共に、前記第2素子領域のゲート溝内にゲート絶縁膜を介して第2導電材料からなる第2ゲート電極を埋め込んでもよい。このような方法によれば、第1、第2のゲート電極を形成した後の表面を平坦化することが可能になる。10

#### 【0033】

以上、第2実施形態によれば少なくともゲート溝にゲート絶縁膜を介して仕事関数の異なる導電材料が埋め込まれた第1、第2のゲート電極を備えた半導体装置を製造することができる。

#### 【0034】

また、仕事関数の異なる第1、第2のゲート電極下のゲート絶縁膜は1回のみの成膜工程により形成できるため、従来のように仕事関数の異なる第1、第2の金属ゲートを形成する毎にゲート絶縁膜を形成、つまり2回のゲート絶縁膜の成膜工程が必要である場合に比べて、半導体装置の製造工程の簡略化、量産化が可能になる。20

#### 【0035】

さらに、ゲート絶縁膜を例えば600以上的高温で成膜しても、仕事関数の異なる第1、第2のゲート電極はこのゲート絶縁膜の成膜後に形成するため、その成膜工程でのゲート電極への熱影響を回避でき、信頼性の高い半導体装置を製造できる。

#### 【0036】

(第3実施形態)

(第1工程)

第1素子領域および第2素子領域を有する半導体基板上の層間絶縁膜に複数のゲート溝をそれら底部に前記各素子領域が位置する前記半導体基板表面をそれぞれ露出させるように形成する。つづいて、これらゲート溝を含む全面にゲート絶縁膜を形成する。ひきつづき、各ゲート溝内のゲート絶縁膜上にこのゲート絶縁膜に対してエッチング選択比を有するマスク材をそれぞれ選択的に形成する。つまり、マスク材を前記ゲート溝内に埋め込む。30

#### 【0037】

前記第1素子領域および第2素子領域は、例えば前記半導体基板に形成した薄溝型素子分離領域で分離する。

#### 【0038】

前記層間絶縁膜は、例えばシリコン酸化膜を用いることができる。40

#### 【0039】

前記ゲート絶縁膜およびマスク材は、前記第1実施形態で説明したのと同様な材料のものを用いることができる。

#### 【0040】

各ゲート溝内へのマスク材の選択的な形成は、例えば全面にマスク材を形成した後、このマスク材を前記ゲート溝を除く前記層間絶縁膜上のゲート絶縁膜が露出するまでCMP処理する方法を採用することができる。

#### 【0041】

(第2工程)

前記第1素子領域に位置する前記ゲート溝内のマスク材を選択的にエッチング除去して50

そのゲート溝内のゲート絶縁膜部分を露出させる。つづいて、この露出したゲート溝内のゲート絶縁膜、前記層間絶縁膜および残存したマスク材の上に薄い第1導電材料膜を形成する。この第1導電材料膜をパターニングして前記第1素子領域に位置する前記ゲート溝内のゲート絶縁膜を含む前記層間絶縁膜上にパターン状の第1導電材料膜を形成する。同時に、残存したマスク材を露出させる。

【0042】

前記パターン状の第1導電材料膜は、例えばレジストパターンをマスクとしたRIEによりパターニングする方法を採用することができる。

【0043】

(第3工程)

露出した残存マスク材をエッティング除去して前記第2素子領域に位置するゲート溝を露出させる。つづいて、前記パターン状の第1導電材料膜および前記第2素子領域に位置するゲート溝を含む前記ゲート絶縁膜上に前記第1導電材料膜と仕事関数の異なる第2導電材料膜を形成する。この時、第2導電材料膜の一部は前記第2素子領域に位置するゲート溝内のゲート絶縁膜部分に直接接する。ひきつづき、前記パターン状の第1導電材料膜および第2導電材料膜を例えばレジストパターンをマスクとしたRIEによりパターニングすることにより前記第1素子領域のゲート溝内にゲート絶縁膜を介して第1導電材料膜が埋め込まれた構造の第1ゲート電極を形成すると共に、前記第2素子領域のゲート溝内にゲート絶縁膜を介して第2導電材料膜が埋め込まれた構造の第2ゲート電極を形成する。形成された第1ゲート電極は、績層構造を有するが、その仕事関数はゲート絶縁膜に接する第1導電材料膜により決定される。

【0044】

前記第2工程、第3工程でのマスク材のエッティング除去は、湿式エッティング法またはケミカルドライエッティング法を採用することが好ましい。このような湿式エッティング法またはケミカルドライエッティング法を採用することにより、プラズマエッティング法に比べて下地のゲート絶縁膜へのエッティングダメージを低減することが可能になる。

【0045】

前記第1、第2の導電材料膜において、NMOS側の導電材料としては例えばTiN、WN、TaN, MoSi, WSiなどの仕事関数が4.6eV未満の金属、金属の窒化物、シリサイド、合金などの金属材料が適している。また、PMOS側の導電材料としては例えばW, Ta, Pt, Moなどの仕事関数が4.6eV以上の金属、シリサイド、合金などの金属材料を使うのが適している。ただし、必ずしも前記材料、仕事関数に限定されるものではない。また、同じ金属材料でも成膜条件により仕事関数が異なる場合があるので上げた例は一例に過ぎない。例えばWは、仕事関数が4.3~5.2の間で変化することが知られているため、NMOS、PMOS両方に使用できる場合もある。

【0046】

なお、前記第1、第2のゲート電極の形成において前記第2導電材料膜、パターン状の第1導電材料膜およびゲート絶縁膜を前記各ゲート溝を除く前記層間絶縁膜の表面が露出するまでCMP処理することによって、前記第1素子領域のゲート溝内にゲート絶縁膜を介して第1導電材料からなる第1ゲート電極を埋め込むと共に、前記第2素子領域のゲート溝内にゲート絶縁膜を介して第2導電材料からなる第2ゲート電極を埋め込んでもよい。このような方法によれば、第1、第2のゲート電極を形成した後の表面を平坦化することが可能になる。

【0047】

以上、第3実施形態によれば少なくともゲート溝にゲート絶縁膜を介して仕事関数の異なる導電材料が埋め込まれた第1、第2のゲート電極を備えた半導体装置を製造することができる。

【0048】

また、仕事関数の異なる第1、第2のゲート電極下のゲート絶縁膜は1回のみの成膜工程により形成できるため、従来のように仕事関数の異なる第1、第2の金属ゲートを形成

する毎にゲート絶縁膜を形成、つまり2回のゲート絶縁膜の成膜工程が必要である場合に比べて、半導体装置の製造工程の簡略化、量産化が可能になる。

【0049】

さらに、ゲート絶縁膜を例えば600以上の中温で成膜しても、仕事関数の異なる第1、第2のゲート電極はこのゲート絶縁膜の成膜後に形成するため、その成膜工程でのゲート電極20、21への熱影響を回避でき、信頼性の高い半導体装置を製造できる。

【0050】

以下、本発明の実施例を図面を参照して説明する。

【0051】

(実施例1)

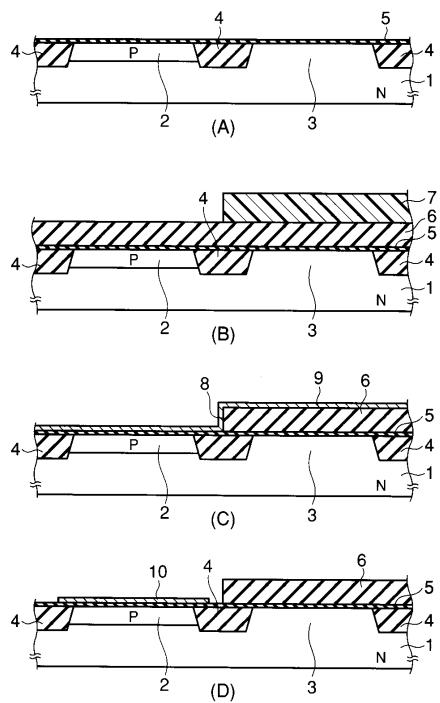

まず、図1の(A)に示すようにN型の半導体基板(例えばN型シリコンウェハ)1にバッファ酸化膜、窒化シリコン膜(いずれも図示せず)を形成し、この窒化シリコン膜上にレジストパターンを形成し、このレジストパターンをマスクとして窒化シリコン膜を選択的にエッティングして前記バッファ酸化膜の素子領域に窒化シリコン膜パターンを形成した。この窒化シリコン膜パターンをマスクとしてリアクティブイオンエッティングにより前記バッファ酸化膜およびシリコンウェハ1をエッティングして溝を形成した。つづいて、全面の酸化シリコン膜を堆積し、CMP処理を施して窒化シリコン膜パターン上面まで平坦化する。その後、窒化シリコン膜パターンとバッファ酸化膜を除去することにより図1の(A)の左側から第1素子領域2、第2素子領域3に分離するための浅溝型素子分離(STI)領域4を形成した。つづいて、前記第1素子領域2にP型不純物、例えばボロンをイオン注入し、活性化することによりP型素子領域とした。なお、前記第2素子領域3はN型素子領域となる。必要に応じて、シリコンウェハ1の各素子領域2、3にチャンネル制御のためのP型またはN型不純物、例えばボロンまたはリンのイオン注入、活性化アニールを実施して各素子領域2、3の不純物濃度の調整を行った。ひきつづき、前記バッファ酸化膜を除去し、CVD法により例えば厚さ4~8nmのTa<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜5を前記シリコンウェハ1の各素子領域2、3上に形成した。

【0052】

次いで、図1の(B)に示すように全面にマスク材である厚さ10~50nmのTEOS膜6を堆積した後、前記P型素子領域2に対応する箇所が開口されたレジストパターン7を形成した。このTEOS膜6の堆積時(成膜時)の温度を600以下に抑えることにより、前記Ta<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜5の劣化を低減することができる。つづいて、図1の(C)に示すように前記レジストパターン7をマスクとして前記TEOS膜6を例えばフッ酸水溶液で選択的に湿式エッティングして前記P型素子領域2に位置する前記ゲート絶縁膜5部分を露出させるための開口部8を形成した。このTEOS膜6の選択的なエッティングにおいて、フッ酸水溶液による湿式エッティングを採用することにより、その下地であるゲート絶縁膜5へのダメージを抑えることができた。ひきつづき、前記レジストパターン7を剥離除去した後、CVD法により全面に第1導電材料膜である例えば厚さ10nmの窒化チタン膜(TiN膜)9を堆積した。この時、TiN膜9の一部は前記TEOS膜6の開口部8から露出され、P型素子領域2に位置するゲート絶縁膜5部分の上に形成された。また、N型素子領域3側は前記TEOS膜6で覆われているため、そのゲート絶縁膜5部分へのTiN膜9の直接的な接触を回避してTa<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜5の影響を防ぐことができた。

【0053】

次いで、図1の(D)に示すように図示しないレジストパターンをマスクとして前記TiN膜9を例えば過酸化水溶液で選択的に湿式エッティングして前記P型素子領域2に位置する前記ゲート絶縁膜5部分の上にパターン状のTiN膜10を形成した。この時、N型素子領域3に位置するゲート絶縁膜5は前記マスク材6で覆われているため、エッチャントである前記過酸化水溶液に接するのを防止され、成膜時の良好な膜質を維持できた。また、前記マスク材であるTEOS膜6が露出した。つづいて、図2の(E)に示すように露出したTEOS膜6を例えばフッ酸水溶液で湿式エッティングして除去した後、全面に例

えば厚さ 250 nm のタンゲステン (W) 膜 11 を堆積した。このような TEOS 膜 6 の除去において、フッ酸水溶液による湿式エッティングを採用することにより、その下地であるゲート絶縁膜 43 へのダメージを抑えることができた。また、堆積された前記 W 膜 11 の一部は N 型素子領域 3 に位置するゲート絶縁膜 5 部分の上に形成された。

#### 【0054】

次いで、図示しないレジストパターンをマスクとして前記 W 膜 11 およびパターン状の TiN 膜 10、W 膜 11 単独をそれぞれ RIE のような異方性エッティングにより選択的に除去して P 型素子領域 2 のゲート絶縁膜 5 上に TiN 膜 10 および W 膜 11 からなる第 1 ゲート電極 12 を形成した。同時に、N 型素子領域 3 のゲート絶縁膜 5 上に W からなり、第 1 ゲート電極 12 と一端側で接続された第 2 ゲート電極 13 を形成した。この後、レジストパターンを剥離、除去し、再度、図示しないレジストパターンを N 型素子領域 3 に形成し、このレジストパターンおよび第 1 ゲート電極 12 をマスクとして N 型不純物、例えば砒素を P 型素子領域 2 にイオン注入し、活性化して N 型のソース、ドレイン拡散層 14, 15 を形成した。ひきつづき、レジストパターンを剥離、除去し、再度、図示しないレジストパターンを P 型素子領域 2 に形成し、このレジストパターンおよび第 2 ゲート電極 13 をマスクとして P 型不純物、例えばボロンを N 型素子領域 3 にイオン注入し、活性化して P 型のソース、ドレイン拡散層 16, 17 を形成した（図 2 の (F) 図示）。その後、図示しないが、全面に酸化シリコン膜のような層間絶縁膜を堆積し、前記 N 型のソース、ドレイン拡散層および P 型のソース、ドレイン拡散層に対応する層間絶縁膜部分にコンタクトホールを開口した。Ti / TiN をコンタクトホールから露出するシリコンウェハに堆積し、アニールして前記ウェハと反応させ、シリサイド化させて接触抵抗を低減した。ひきつづき、A1 膜の堆積、パターニングにより前記コンタクトホールを通して前記 N 型のソース、ドレイン拡散層および P 型のソース、ドレイン拡散層に接続される配線を前記層間絶縁膜上に形成することにより、TiN を主たるゲート材料とする第 1 ゲート電極を有する NMOS と W を主たるゲート材料とする第 2 ゲート電極を有する PMOS を備えた相補型 MOS 半導体装置 (CMOS) を製造した。

10 20 30

#### 【0055】

このような実施例 1 によれば、窒化チタン (TiN) を主たるゲート材料とする第 1 ゲート電極 12 を有する NMOS とタンゲステン (W) を主たるゲート材料とする第 2 ゲート電極 13 を有する PMOS とを 1 チップ上に形成することができるため、しきい値スイングのような性能を犠牲にすることなく、低しきい値を持つ高性能の CMOS を製造できた。

30

#### 【0056】

また、仕事関数の異なる第 1、第 2 のゲート電極 12, 13 下のゲート絶縁膜 5 を 1 回のみの成膜工程により形成できるため、従来のように仕事関数の異なる第 1、第 2 の金属ゲートを形成する毎にゲート絶縁膜を形成する、つまり 2 回のゲート絶縁膜の成膜工程、が必要である、場合に比べて CMOS を量産的に製造できた。

#### 【0057】

さらに、ゲート絶縁膜 5 の形成後においてそのゲート絶縁膜 5 (MOSFET として機能するゲート絶縁膜部分) は TiN 膜 9 のパターニング時にマスク材である TEOS 膜 6 で覆われているため、そのパターニング時のエッチャントである過酸化水溶液に接するのを防止して良好な膜質のゲート絶縁膜 5 を有する CMOS を製造できた。

40

#### 【0058】

さらに、ゲート絶縁膜 5 を高誘電率材料である  $Ta_2O_5$  から作ることによって、その膜厚を例えば 4 ~ 8 nm と厚くすることが可能になるため、トンネルリーアクを抑制ないし防止して高信頼性の CMOS を製造できた。

#### 【0059】

##### (実施例 2)

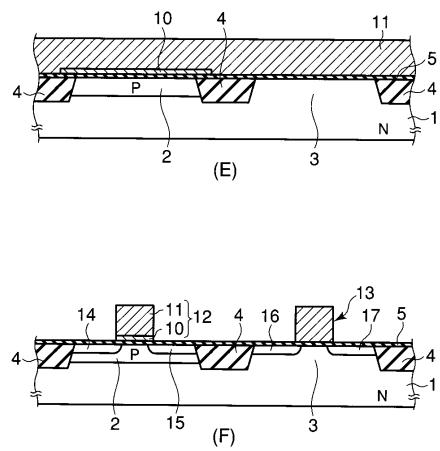

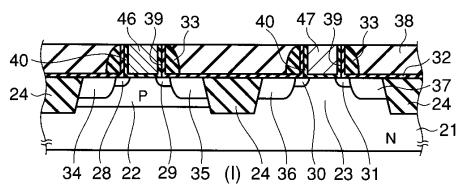

まず、図 3 の (A) に示すように N 型の半導体基板 (例えば N 型シリコンウェハ) 21 に前述した実施例 1 と同様な方法で左側から第 1, 第 2 の素子領域 22, 23 に分離するため

50

の浅溝型素子分離(S T I)領域2 4を形成した。つづいて、前記第1素子領域2 2にP型不純物、例えばボロンをイオン注入し、活性化することによりP型素子領域とした。なお、前記第2素子領域2 3はN型素子領域となる。必要に応じて、シリコンウェハ2 1の各素子領域2 2, 2 3にチャンネル制御のためのP型またはN型不純物、例えばボロンまたはリンのイオン注入、活性化アニールを実施して各素子領域2 2, 2 3の不純物濃度の調整を行った。なお、チャンネルイオン注入は通常、ゲート電極の形成前に行なわれるが、ダマシングートプロセスでは後述するゲート溝を形成した後での実施できるために必ずしもこの段階で行わなくてもよい。つづいて、バッファ酸化膜を残存させた状態で全面にCVD法により厚さ2 0 0 nmの多結晶シリコン膜、厚さ4 0 nmの窒化シリコン膜のこの順序で堆積した。ひきつづき、図示しないレジストパターンを前記窒化シリコン膜上に形成し、RIE等の異方性エッチングにより前記窒化シリコン膜および多結晶シリコン膜をエッチングし、前記各素子領域2 2, 2 3に多結晶シリコン膜2 5および窒化シリコン膜2 6の積層膜からなるダミーゲート2 7を形成した。このダミーゲート2 7は、例えば前記P型素子領域2 2およびN型素子領域2 3をそれぞれ横切るように平面的に見て略U形をなしている。レジストパターンを剥離、除去し、再度、図示しないレジストパターンをN型素子領域2 3に形成し、このレジストパターンおよびP型素子領域2 2側に位置するダミーゲート2 7部分をマスクとしてN型不純物、例えば砒素をP型素子領域2 2にイオン注入し、活性化して低濃度のN型のソース、ドレイン拡散層2 8, 2 9を形成した。ひきつづき、レジストパターンを剥離、除去し、再度、図示しないレジストパターンをP型素子領域2 2に形成し、このレジストパターンおよびN型素子領域2 3側のダミーゲート2 7部分をマスクとしてP型不純物、例えばボロンをN型素子領域2 3にイオン注入し、活性化して低濃度のP型のソース、ドレイン拡散層3 0, 3 1を形成した。

10

#### 【0060】

次いで、前記ダミーゲート2 7を含むシリコンウェハ2 1上に厚さ2 0 nmの窒化シリコン膜3 2、厚さ7 0 nmの酸化シリコン膜を順次堆積した後、酸化シリコン膜をRIEなどの異方性エッチングを施した。この時、図3の(B)に示すように前記ダミーゲート2 7の側面に酸化シリコンからなる側壁3 3が形成された。つづいて、図示しないレジストパターンをN型素子領域2 3に形成し、このレジストパターン、P型素子領域2 2側に位置するダミーゲート2 7部分および側壁3 3をマスクとしてN型不純物、例えば砒素をP型素子領域2 2にイオン注入し、活性化して高濃度のN型のソース、ドレイン拡散層3 4, 3 5を形成した。ひきつづき、レジストパターンを剥離、除去し、再度、図示しないレジストパターンをP型素子領域2 2に形成し、このレジストパターン、N型素子領域2 3側のダミーゲート2 7部分および側壁3 3をマスクとしてP型不純物、例えばボロンをN型素子領域2 3にイオン注入し、活性化して高濃度のP型のソース、ドレイン拡散層3 7, 3 7を形成した。このような工程によりP型素子領域2 2およびN型素子領域2 3にLDD構造のソース、ドレインがそれぞれ形成された。なお、Ti, Coなどのシリサイドを前記ソース、ドレインに形成して低抵抗化することを許容する。

20

#### 【0061】

次いで、図3の(C)に示すようにダミーゲート2 7を含むシリコンウェハ2 1全面に例えば厚さ3 0 0 nmの酸化シリコン膜を堆積させた後、前記酸化シリコン膜をダミーゲート2 7上面の窒化シリコン膜3 2部分が露出するまでCMP処理を施して表面が平坦な第1層の層間絶縁膜3 8を形成した。つづいて、前記ダミーゲート2 7上に露出した窒化シリコン膜3 2およびダミーゲート2 7を構成する窒化シリコン膜2 6を熱リン酸処理でそれぞれ除去し、多結晶シリコン膜2 5をケミカルドライエッチング(CDE)で除去し、図示しないバッファ酸化膜を希フッ酸処理によりエッチングしてダミーゲート2 7を除去することにより図3の(D)に示すようにP型素子領域2 2およびN型素子領域2 3に一部がそれぞれ延出され、平面的に見て略U形をなすゲート溝3 9を形成した。なお、チャネル部分の不純物濃度調整のイオン注入をダミーゲート形成前に行わなかった場合にはこの時点でチャネル領域に不純物を導入することが可能である。

30

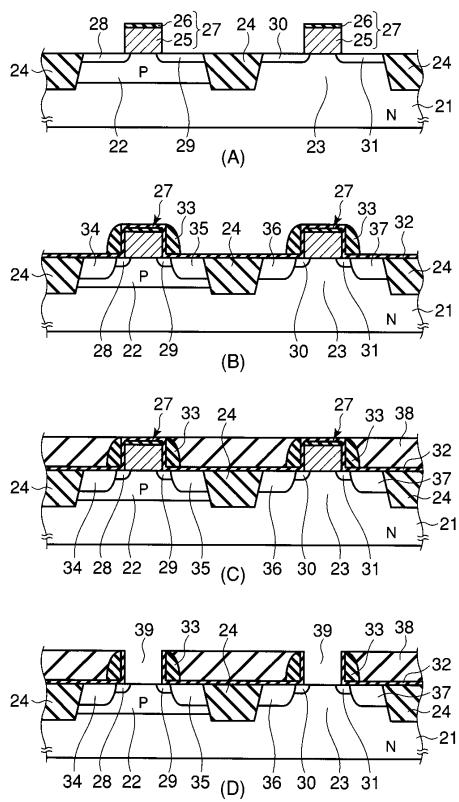

#### 【0062】

次いで、図4の(E)に示すように前記ゲート溝39底面に露出したP型素子領域22およびN型素子領域23を含む前記第1層の層間絶縁膜38上にTa<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜40を形成した。なお、Taと各素子領域22、23のシリコンとの反応を防ぐためにゲート絶縁膜40の形成に先立って、例えば各素子領域22、23のシリコン表面を窒化処理して界面層を形成することが好ましい。これらのゲート絶縁膜40の形成後に必要に応じて膜質を改善するためポストアニールを行うことを許容する。前記Ta<sub>2</sub>O<sub>5</sub>の代わりに酸化シリコンからなるゲート絶縁膜を形成する場合には、前記バッファ酸化膜を除去した後に前記ゲート溝39底面に露出したシリコンウェハ21を酸化することによりゲート絶縁膜を形成してもよい。つづいて、前記ゲート溝39内を含む第1層の層間絶縁膜38にTEOS膜41をゲート溝39を埋め込む、例えば100nmの厚さに堆積した。このTEOS膜41の堆積時(成膜時)の温度を600以下に抑えることにより、前記Ta<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜40の劣化を低減することができる。

#### 【0063】

次いで、図4の(F)に示すように図示しないレジストパターンをマスクとして前記TEOS膜41を例えばフッ酸水溶液で選択的に湿式エッチングして前記P型素子領域22に位置する前記ゲート絶縁膜40部分を露出させるための開口部42を形成した。このTEOS膜41の選択的なエッチングにおいて、フッ酸水溶液による湿式エッチングを採用することにより、その下地であるゲート絶縁膜40へのダメージを抑えることができた。ひきつづき、前記レジストパターンを剥離除去した後、CVD法により全面に第1導電材料膜である窒化チタン膜(TiN膜)43を前記ゲート溝39および前記TEOS膜41の開口部42を埋め込む、例えば10nmの厚さに堆積した。この時、TiN膜43の一部は前記TEOS膜41の開口部42および前記ゲート溝39から露出され、P型素子領域22に位置するゲート絶縁膜40部分の上に形成された。また、N型素子領域23側のゲート溝39は前記TEOS膜41で覆われているため、そのゲート溝39内に位置するゲート絶縁膜40部分へのTiN膜43の直接的な接触を回避してTa<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜40の影響を防ぐことができた。

#### 【0064】

次いで、前記TiN膜43をCMP処理することにより図4の(G)に示すように前記TEOS膜41の開口部42および前記P型素子領域22側のゲート溝39内に前記TEOS膜41と面一な埋め込みTiN膜44を形成した。つづいて、図4の(H)に示すように露出したTEOS膜41を例えばフッ酸水溶液で湿式エッチングして除去した後、全面にタンゲステン(W)膜45を露出した前記ゲート溝39を埋め込む、例えば50nmの厚さに堆積した。このようなTEOS膜41の除去において、フッ酸水溶液による湿式エッチングを採用することにより、その下地であるゲート絶縁膜40へのダメージを抑えることができた。また、堆積された前記W膜45の一部はN型素子領域23に位置するゲート絶縁膜40部分の上に形成された。

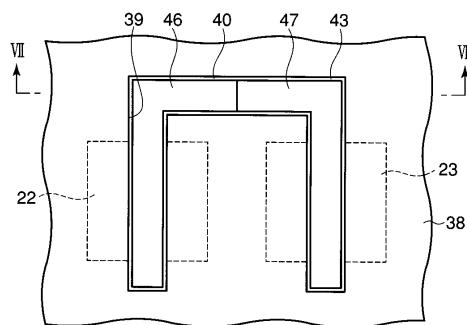

#### 【0065】

次いで、前記W膜45および埋め込みTiN膜44を前記第1層の層間絶縁膜38上のゲート絶縁膜40部分が露出するまでCMP処理を施し、さらに露出したゲート絶縁膜40部分をCMP処理した。これにより前記第1層の層間絶縁膜38の前記P型素子領域22側に位置するゲート溝39内にTiNからなる第1ゲート電極46を前記層間絶縁膜38と面一に形成した。同時に、前記第1層の層間絶縁膜38の前記N型素子領域23側に位置するゲート溝39内にWからなる第2ゲート電極47を前記層間絶縁膜38と面一に形成した(図5の(I)、図6および図7図示)。なお、図6は図5の(I)の平面図、図7は図6のVII-VII線に沿う断面図である。前記第1、第2のゲート電極46、47は図6および図7に示すように一端側で互いに繋がって、平面から見て略U形をなしている。

#### 【0066】

その後、図示しないが、全面に酸化シリコン膜のような第2層目の層間絶縁膜を堆積し、高濃度の前記N型のソース、ドレイン拡散層およびP型のソース、ドレイン拡散層に対応する第1層、第2層の層間絶縁膜部分にコンタクトホールを開口した。Ti/TiNを

10

20

30

40

50

コンタクトホールから露出するシリコンウェハに堆積し、アニールして前記ウェハと反応させ、シリサイド化させて接触抵抗を低減した。ひきつづき、A1膜の堆積、パターニングにより前記コンタクトホールを通して前記N型のソース、ドレイン拡散層およびP型のソース、ドレイン拡散層に接続される配線を前記第2層の層間絶縁膜上に形成することにより、TiNからなる第1ゲート電極46を有するNMOSとWからなり、前記第1ゲート電極46と一端側で接続された第2ゲート電極47を有するPMOSを備えた相補型MOS半導体装置(CMOS)を製造した。

## 【0067】

このような実施例2によれば、第1層の層間絶縁膜38のゲート溝39に仕事関数の異なる窒化チタン(TiN)からなる第1ゲート電極46およびタンゲステン(W)からなる第2ゲート電極47が互いに接続して埋め込まれたPMOSとNMOSとを1チップ上に形成することができ、しきい値スイッチングのような性能を犠牲にすることなく、低しきい値を持つ高性能で表面が平坦なCMOSを製造できた。

## 【0068】

また、仕事関数の異なる第1、第2のゲート電極46、47下のゲート絶縁膜40を1回のみの成膜工程により形成できるため、従来のように仕事関数の異なる第1、第2の金属ゲートを形成する毎にゲート絶縁膜を形成する、つまり2回のゲート絶縁膜の成膜工程が必要である、場合に比べてCMOSを量産的に製造できた。

## 【0069】

さらに、ゲート絶縁膜40の形成後においてN型素子領域23に位置するゲート絶縁膜40部分はTiN膜43の堆積時にマスク材であるTEOS膜41で覆われているため、TiN膜43の直接的な接触を回避でき、良好な膜質のゲート絶縁膜40を有するCMOSを製造できた。

## 【0070】

さらに、ゲート絶縁膜40を高誘電率材料であるTa<sub>2</sub>O<sub>5</sub>から作ることによって、その膜厚を例えば4~8nmと厚くすることが可能になるため、トンネルリリークを抑制ないし防止して高信頼性のCMOSを製造できた。

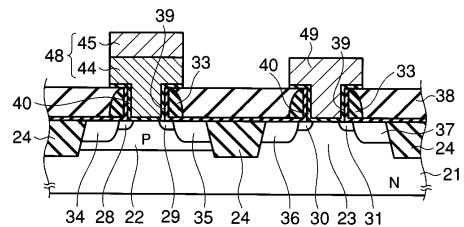

## 【0071】

前述した実施例2では、第1、第2のゲート電極46、47を第1層の層間絶縁膜38のゲート溝39内に埋め込んだ構造にしたが、これに限定されない。例えば、前述した図4の(H)の工程でW膜45を堆積した後、W膜45、埋め込みTiN膜44およびゲート絶縁膜40をCMP処理する代わりにレジストパターンをマスクとするRIEを行なって、図8に示すようにTiN膜44およびW膜44からなり、ゲート溝39内に一部が埋め込まれると共に、前記層間絶縁膜38表面から突出した第1ゲート電極48を形成し、かつWからなり、ゲート溝39内に一部が埋め込まれると共に、前記層間絶縁膜38表面から突出した第2ゲート電極49を形成してもよい。

## 【0072】

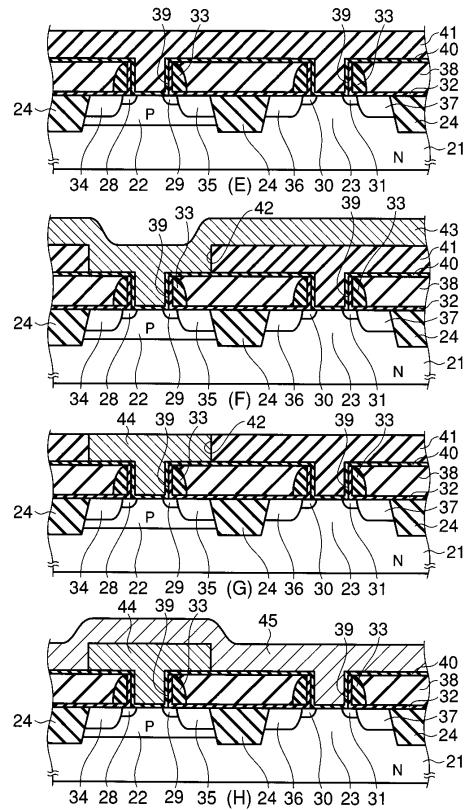

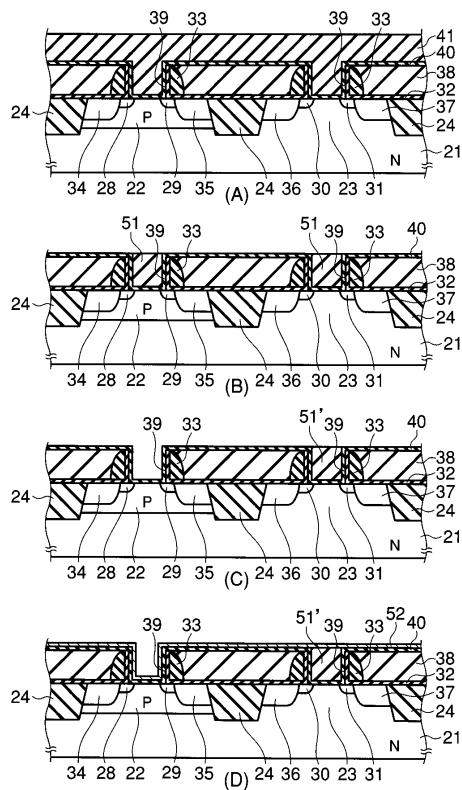

## (実施例3)

前述した実施例2と同様な方法によりP型素子領域22およびN型素子領域23に一部がそれぞれ延出され、平面的に見て略U形をなすゲート溝39を形成した。つづいて、前記ゲート溝39底面に露出したP型素子領域22およびN型素子領域23を含む層間絶縁膜38上にTa<sub>2</sub>O<sub>5</sub>からなるゲート絶縁膜40を形成した。ひきつづき、前記ゲート溝39内を含む第1層の層間絶縁膜38にマスク材であるTEOS膜41をそのゲート溝39を埋め込む、例えば100nmの厚さに堆積した(図9の(A)図示)。

## 【0073】

次いで、図9の(B)に示すように前記TEOS膜41を前記第1層の層間絶縁膜38上のゲート絶縁膜40部分が露出するまでCMP処理を施すことによって、前記ゲート溝39内にTEOS埋め込み材51を形成した。つづいて、図9の(C)に示すようにP型素子領域22に位置する前記ゲート溝39部分内のTEOS埋め込み材51部分を例えばフッ酸水溶液で湿式エッチングにより選択的に除去してP型素子領域22に位置する前記ゲ

10

20

30

40

50

ート溝 3 9 部分内のゲート絶縁膜 4 0 部分を露出させた。このような T E O S 埋め込み材 5 1 の選択的な除去において、フッ酸水溶液による湿式エッチングを採用することにより、その下地であるゲート絶縁膜 4 0 へのダメージを抑えることができた。

#### 【 0 0 7 4 】

次いで、図 9 の ( D ) に示すように前記露出したゲート溝 3 9 を含む全面に C V D 法により全面に第 1 導電材料膜である例えば厚さ 1 0 nm の窒化チタン膜 ( T i N 膜 ) 6 2 を堆積した。この T i N 膜 5 2 は、仕事関数を決定するだけであるので 1 0 nm と薄膜であってもよい。この工程において、前記 T i N 膜 5 2 の一部は前記 P 型素子領域 2 2 に位置する露出したゲート溝 3 9 内のゲート絶縁膜 4 0 部分の上に形成された。また、N 型素子領域 2 3 に位置するゲート溝 3 9 は残存した T E O S 埋め込み材 5 1 ' で覆われているため、そのゲート溝 3 9 内のゲート絶縁膜 4 0 部分への T i N 膜 5 2 の直接的な接触を回避して T a<sub>2</sub>O<sub>5</sub> からなるゲート絶縁膜 4 0 の影響を防ぐことができた。

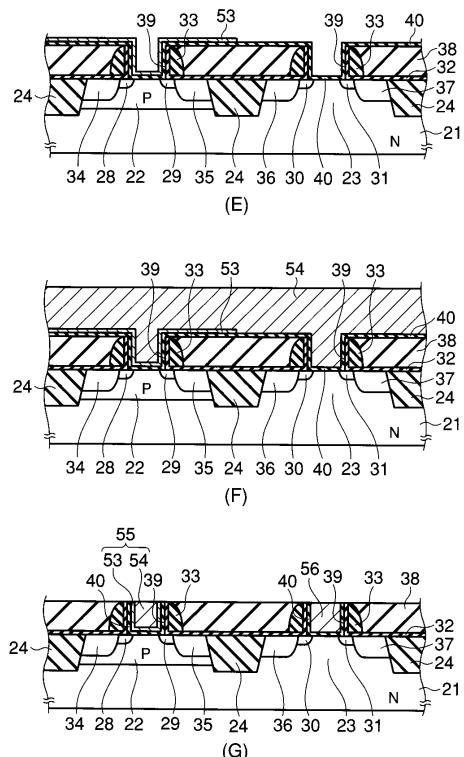

#### 【 0 0 7 5 】

次いで、図 1 0 の ( E ) に示すように前記 T i N 膜 5 2 を図示しないレジストパターンをマスクとして N 型素子領域 2 3 に位置するゲート溝 3 9 内の残存した T E O S 埋め込み材 5 1 ' が露出するように図示しないレジストパターンをマスクとして前記 T i N 膜 5 2 を例えば過酸化水溶液で選択的に湿式エッチングしてパターン状の T i N 膜 5 3 を形成した。この時、N 型素子領域 2 3 に位置するゲート溝 3 9 内のゲート絶縁膜 4 0 部分は残存した T E O S 埋め込み材 5 1 ' で覆われているため、エッチャントである前記過酸化水溶液に接するのを防止され、成膜時の良好な膜質を維持できた。つづいて、露出した残存 T E O S 埋め込み材 5 1 ' 部分を例えばフッ酸水溶液で湿式エッチングにより選択的に除去して前記ゲート溝 3 9 内のゲート絶縁膜 4 0 部分を露出させた。このような T E O S 埋め込み材 5 1 ' 部分の選択的な除去において、フッ酸水溶液による湿式エッチングを採用することにより、その下地であるゲート絶縁膜 4 0 へのダメージを抑えることができた。

#### 【 0 0 7 6 】

次いで、図 1 0 の ( F ) に示すように全面にタンゲステン ( W ) 膜 5 4 を露出した前記ゲート溝 3 9 部分を埋め込む、例えば 5 0 nm の厚さに堆積した。堆積された前記 W 膜 5 4 の一部は、N 型素子領域 2 3 に位置するゲート溝 3 9 内のゲート絶縁膜 4 0 部分の上に形成された。

#### 【 0 0 7 7 】

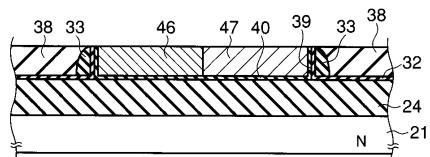

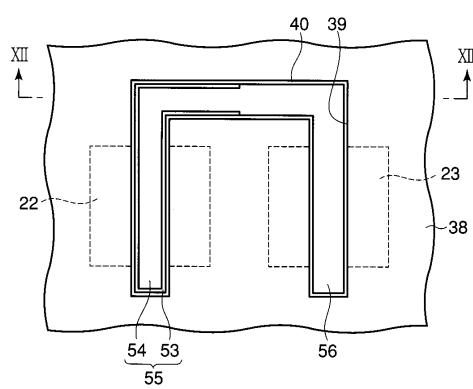

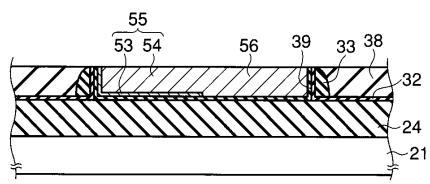

次いで、前記 W 膜 5 4 およびパターン状の T i N 膜 5 3 を前記第 1 層の層間絶縁膜 3 8 上のゲート絶縁膜 4 0 部分が露出するまで C M P 处理を施し、さらに露出したゲート絶縁膜 4 0 部分を C M P 处理した。これにより前記第 1 層の層間絶縁膜 3 8 の前記 P 型素子領域 2 2 側に位置するゲート溝 3 9 内に T i N 膜 5 3 および W 膜 5 4 からなる第 1 ゲート電極 5 5 を前記層間絶縁膜 3 8 と面一に形成した。同時に、前記第 1 層の層間絶縁膜 3 8 の前記 N 型素子領域 2 3 側に位置するゲート溝 3 9 内に W からなる第 2 ゲート電極 5 6 を前記層間絶縁膜 3 8 と面一に形成した ( 図 1 0 の ( G ) 、図 1 1 および図 1 2 図示 ) 。なお、図 1 1 は図 1 0 の ( G ) の平面図、図 1 2 は図 1 1 の XII - XII 線に沿う断面図である。前記第 1 , 第 2 のゲート電極 5 5 , 5 6 は図 1 1 および図 1 2 に示すように一端側で互いに繋がって、平面から見て略 U 形をなしている。

#### 【 0 0 7 8 】

その後、図示しないが、全面に酸化シリコン膜のような第 2 層目の層間絶縁膜を堆積し、高濃度の前記 N 型のソース、ドレイン拡散層および P 型のソース、ドレイン拡散層に対応する第 1 層、第 2 層の層間絶縁膜部分にコンタクトホールを開口した。T i / T i N をコンタクトホールから露出するシリコンウェハに堆積し、アニールして前記ウェハと反応させ、シリサイド化させて接触抵抗を低減した。ひきつづき、A 1 膜の堆積、パターニングにより前記コンタクトホールを通して前記 N 型のソース、ドレイン拡散層および P 型のソース、ドレイン拡散層に接続される配線を前記第 2 層の層間絶縁膜上に形成することにより、T i N 膜 5 3 および W 膜 5 4 からなる第 1 ゲート電極 5 5 を有する N M O S と W からなり、前記第 1 ゲート電極 5 5 と一端側で接続された第 2 ゲート電極 5 6 を有する P

10

20

30

40

50

MOSを備えた相補型MOS半導体装置(CMOS)を製造した。

【0079】

このような実施例3によれば、第1層の層間絶縁膜38のゲート溝39に仕事関数の異なる窒化チタン(TiN)を主たるゲート材料とする第1ゲート電極55およびタンゲステン(W)を主たるゲート材料とする第2ゲート電極56が埋め込まれたPMOSとNMOSとを1チップ上に形成することができ、しきい値スイッチングのような性能を犠牲にすることなく、低しきい値を持つ高性能で表面が平坦なCMOSを製造できた。

【0080】

また、仕事関数の異なる第1、第2のゲート電極55, 56下のゲート絶縁膜40を1回のみの成膜工程により形成できるため、従来のように仕事関数の異なる第1、第2の金属ゲートを形成する毎にゲート絶縁膜を形成する、つまり2回のゲート絶縁膜の成膜工程が必要である、場合に比べてCMOSを量産的に製造できた。

10

【0081】

さらに、ゲート絶縁膜40の形成後においてN型素子領域23に位置するゲート絶縁膜40部分はTiN膜52の堆積時にマスク材である残存したTEOS埋め込み材51'で覆われているため、TiN膜52の直接的な接触を回避できた。また、N型素子領域23に位置するゲート溝39内のゲート絶縁膜40部分はTiN膜52のパターニング時に残存したTEOS埋め込み材51'で覆われているため、そのパターニング時のエッチャントである過酸化水溶液に接するのを防止できた。その結果、良好な膜質のゲート絶縁膜40を有するCMOSを製造できた。

20

【0082】

さらに、ゲート絶縁膜40を高誘電率材料であるTa<sub>2</sub>O<sub>5</sub>から作ることによって、その膜厚を例えば4~8nmと厚くすることが可能になるため、トンネルリリークを抑制ないし防止して高信頼性のCMOSを製造できた。

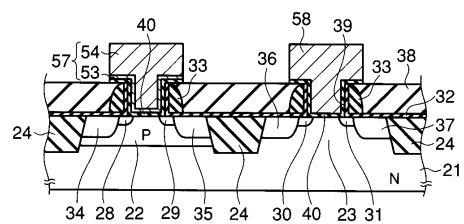

【0083】

前述した実施例3では、第1、第2のゲート電極55, 56を第1層の層間絶縁膜38のゲート溝39内に埋め込んだ構造にしたが、これに限定されない。例えば、前述した図10の(F)の工程でW膜54を堆積した後、W膜54、パターン状にTiN膜53およびゲート絶縁膜40をCMP処理する代わりにレジストパターンをマスクとするRIEを行なって、図13に示すようにTiN膜53およびW膜54からなり、ゲート溝39内に一部が埋め込まれると共に、前記層間絶縁膜38表面から突出した第1ゲート電極57を形成し、かつWからなり、ゲート溝39内に一部が埋め込まれると共に、前記層間絶縁膜38表面から突出した第2ゲート電極58を形成してもよい。

30

【0084】

なお、本発明は前述した実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲で種々に変形して実施することができる。

【0085】

特にゲート電極の組合せについてはW、TiNに限定されるものではない。

【0086】

また、ゲート絶縁膜もTa<sub>2</sub>O<sub>5</sub>の他、シリコン酸化膜、シリコン窒化膜、高誘電体とシリコンとのシリケートなど限定されるものではない。

40

【0087】

さらに、本発明は2種類以上の異なる仕事関数を持つ半導体装置の製造方法であって、必ずしも相補型MOSのNMOSとPMOSの各トランジスタの電極に限定されるものではない。例えば、トランジスタの電極とメモリ領域のコントロールゲートを異なる仕事関数の金属で形成したい場合にも応用できる。また、ミッドギャップの電極とN型ゲートまたはP型ゲートとのトランジスタの組み合わせも考えられる。

【0088】

さらに、ゲートの形状も例えばU字形としたが、これに限定されない。必ずしもひとつのゲート溝にNMOS、PMOS両電極が形成される必要もない。一つのゲート溝にNM

50

OS または PMOS だけの電極が形成される形態にしてもよい。

【産業上の利用可能性】

【0089】

以上詳述したように、本発明によれば互いに仕事関数の異なる導電材料を主たるゲート材料とする第1ゲート電極および第2ゲート電極をそれぞれ有する複数のトランジスタを1チップ上に形成することができるため、しきい値スイングのような性能を犠牲にすることなく、低しきい値を持つ高性能の相補型MOS半導体装置のような半導体装置を量産的に製造し得る方法を提供できる。

【図面の簡単な説明】

【0090】

10

【図1】本発明の実施例1における相補型半導体装置の製造工程を示す断面図。

【図2】本発明の実施例1における相補型半導体装置の製造工程を示す断面図。

【図3】本発明の実施例2における相補型半導体装置の製造工程を示す断面図。

【図4】本発明の実施例2における相補型半導体装置の製造工程を示す断面図。

【図5】本発明の実施例2における相補型半導体装置の製造工程を示す断面図。

【図6】図5の相補型半導体装置を示す平面図。

【図7】図6の相補型半導体装置のVII-VII線に沿う断面図。

【図8】本発明の実施例2における相補型半導体装置の変形例を示す断面図。

【図9】本発明の実施例3における相補型半導体装置の製造工程を示す断面図。

【図10】本発明の実施例3における相補型半導体装置の製造工程を示す断面図。

20

【図11】図10の相補型半導体装置を示す平面図。

【図12】図11の相補型半導体装置のXII-XII線に沿う断面図。

【図13】本発明の実施例3における相補型半導体装置の変形例を示す断面図。

【符号の説明】

【0091】

1, 21...半導体基板 (N型シリコンウェハ)、2, 22...P型素子領域、3, 23...N型素子領域、4, 24...素子分離領域、5, 40...ゲート絶縁膜、6, 41...TEOS膜 (マスク材)、9, 43, 52...TiN膜 (第1導電材料膜)、11, 45, 54...W膜 (第2導電材料膜)、12, 13, 46, 47, 48, 49, 55, 56, 57, 58...ゲート電極、14, 28, 34...N型ソース拡散層、15, 29, 35...N型ドレイン拡散層、16, 30, 36...P型ソース拡散層、17, 31, 37...P型ドレイン拡散層、27...ダミーゲート、39...ゲート溝、51, 51'...TEOS埋め込み材。

30

【図1】

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

【 図 6 】

【図9】

【 四 7 】

【 8 】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(72)発明者 斎藤 友博

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

審査官 宇多川 勉

(56)参考文献 特開平11-074369 (JP, A)

特開2001-284466 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8238

H01L 21/28

H01L 27/092

H01L 29/423

H01L 29/49