(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6503157号

(P6503157)

(45) 発行日 平成31年4月17日(2019.4.17)

(24) 登録日 平成31年3月29日(2019.3.29)

(51) Int.Cl.

F 1

|      |        |           |      |        |

|------|--------|-----------|------|--------|

| GO2F | 1/1343 | (2006.01) | GO2F | 1/1343 |

| GO2F | 1/1333 | (2006.01) | GO2F | 1/1333 |

| GO2F | 1/1368 | (2006.01) | GO2F | 1/1368 |

請求項の数 4 (全 34 頁)

(21) 出願番号 特願2014-54832 (P2014-54832)

(22) 出願日 平成26年3月18日 (2014.3.18)

(65) 公開番号 特開2014-209204 (P2014-209204A)

(43) 公開日 平成26年11月6日 (2014.11.6)

審査請求日 平成29年3月13日 (2017.3.13)

(31) 優先権主張番号 特願2013-59637 (P2013-59637)

(32) 優先日 平成25年3月22日 (2013.3.22)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 田辺 融

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 福留 貴浩

栃木県栃木市都賀町升塚161-2 アド

パンスト フィルム ディバイス インク

株式会社内

(72) 発明者 森谷 幸司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板と、

前記第1の基板上の素子層と、

前記素子層上の液晶素子と、

前記液晶素子上の導電膜と、

前記導電膜上の樹脂膜と、

前記樹脂膜上の第1の電極と

前記第1の電極と第1の絶縁膜を介して重なる領域を有する第2の電極と、

前記第2の電極上の第2の基板と、を有し、

10

前記素子層は、酸化物半導体をチャネル形成領域に含むトランジスタを有し、

前記トランジスタは、前記液晶素子への画像信号の供給を制御する機能を有し、

前記液晶素子は、画素電極と、共通電極と、前記画素電極及び前記共通電極から電界が加えられる液晶層と、を有し、

前記画素電極は、第2の絶縁膜を介して前記共通電極と重なる領域を有し、

前記画素電極は、前記共通電極上に位置し、

前記画素電極は、前記共通電極の開口部を介して前記トランジスタのソース又はドレインの一方と電気的に接続されており、

前記共通電極の開口部は、前記トランジスタのチャネル形成領域と重なっており、

前記トランジスタのチャネル形成領域は、前記共通電極と重なっておらず、

20

前記第1の電極は、前記第2の電極と交差しており、

前記導電膜には第1の電位が供給される液晶表示装置であって、

前記液晶表示装置は、前記第1の電極と前記第2の電極とを用いて位置情報の取得を行う機能を有する液晶表示装置。

## 【請求項2】

第1の基板と、

前記第1の基板上の素子層と、

前記素子層上の液晶素子と、

前記液晶素子上の導電膜と、

前記導電膜上の樹脂膜と、

前記樹脂膜上の第1の電極と 10

前記第1の電極と第1の絶縁膜を介して重なる領域を有する第2の電極と、

前記第2の電極上の第2の基板と、を有し、

前記素子層は、酸化物半導体をチャネル形成領域に含むトランジスタを有し、

前記トランジスタは、前記液晶素子への画像信号の供給を制御する機能を有し、

前記液晶素子は、画素電極と、共通電極と、前記画素電極及び前記共通電極から電界が

加えられる液晶層と、を有し、

前記画素電極は、第2の絶縁膜を介して前記共通電極と重なる領域を有し、

前記画素電極は、前記共通電極上に位置し、

前記画素電極は、前記共通電極の開口部を介して前記トランジスタのソース又はドレインの一方と電気的に接続されており、 20

前記共通電極の開口部は、前記トランジスタのチャネル形成領域と重なっており、

前記トランジスタのチャネル形成領域は、前記共通電極と重なっておらず、

前記第1の電極は、前記第2の電極と交差しており、

前記導電膜は、前記共通電極と電気的に接続される液晶表示装置であって、

前記液晶表示装置は、前記第1の電極と前記第2の電極とを用いて位置情報の取得を行う機能を有する液晶表示装置。 30

## 【請求項3】

第1の基板と、

前記第1の基板上の素子層と、

前記素子層上の液晶素子と、

前記液晶素子上の導電膜と、

前記導電膜上の樹脂膜と、

前記樹脂膜上の第1の電極と 30

前記第1の電極と第1の絶縁膜を介して重なる領域を有する第2の電極と、

前記第2の電極上の第2の基板と、を有し、

前記素子層は、酸化物半導体をチャネル形成領域に含むトランジスタを有し、

前記トランジスタは、前記液晶素子への画像信号の書き込みを制御する機能を有し、

前記液晶素子は、画素電極と、共通電極と、前記画素電極及び前記共通電極から電界が

加えられる液晶層と、を有し、 40

前記画素電極は、第2の絶縁膜を介して前記共通電極と重なる領域を有し、

前記画素電極は、前記共通電極上に位置し、

前記画素電極は、前記共通電極の開口部を介して前記トランジスタのソース又はドレインの一方と電気的に接続されており、

前記共通電極の開口部は、前記トランジスタのチャネル形成領域と重なっており、

前記トランジスタのチャネル形成領域は、前記共通電極と重なっておらず、

前記第1の電極は、前記第2の電極と交差しており、

前記導電膜には第1の電位が供給される液晶表示装置であって、

第1の期間と、第2の期間と、を有し、

前記第1の期間では静止画の表示を行い、 50

前記第2の期間では動画の表示を行い、

前記第1の期間における一定期間内の前記液晶素子への前記画像信号の書き込みの回数は、前記第2の期間における一定期間内の前記液晶素子への前記画像信号の書き込みの回数よりも少なく、

前記液晶表示装置は、前記第1の電極と前記第2の電極とを用いて位置情報の取得を行う機能を有する液晶表示装置。

【請求項4】

第1の基板と、

前記第1の基板上の素子層と、

前記素子層上の液晶素子と、

前記液晶素子上の導電膜と、

前記導電膜上の樹脂膜と、

前記樹脂膜上の第1の電極と

前記第1の電極と第1の絶縁膜を介して重なる領域を有する第2の電極と、

前記第2の電極上の第2の基板と、を有し、

前記素子層は、酸化物半導体をチャネル形成領域に含むトランジスタを有し、

前記トランジスタは、前記液晶素子への画像信号の供給を制御する機能を有し、

前記液晶素子は、画素電極と、共通電極と、前記画素電極及び前記共通電極から電界が加えられる液晶層と、を有し、

前記画素電極は、第2の絶縁膜を介して前記共通電極と重なる領域を有し、

前記画素電極は、前記共通電極上に位置し、

前記画素電極は、前記共通電極の開口部を介して前記トランジスタのソース又はドレインの一方と電気的に接続されており、

前記共通電極の開口部は、前記トランジスタのチャネル形成領域と重なっており、

前記トランジスタのチャネル形成領域は、前記共通電極と重なっておらず、

前記第1の電極は、前記第2の電極と交差しており、

前記導電膜は、前記共通電極と電気的に接続される液晶表示装置であって、

第1の期間と、第2の期間と、を有し、

前記第1の期間では静止画の表示を行い、

前記第2の期間では動画の表示を行い、

前記第1の期間における一定期間内の前記液晶素子への前記画像信号の書き込みの回数は、前記第2の期間における一定期間内の前記液晶素子への前記画像信号の書き込みの回数よりも少なく、

前記液晶表示装置は、前記第1の電極と前記第2の電極とを用いて位置情報の取得を行う機能を有する液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置に関する。特に、本発明は、タッチパネルの機能を有する液晶表示装置に関する。

【背景技術】

【0002】

タッチパネルは、指またはスタイルスなどが指示した位置を検出し、その位置情報を含む信号を生成することができる位置入力装置としての機能を有する。タッチパネルの中でも、静電容量方式は、赤外線方式などの光学式と違って外光に左右されずに位置情報の取得が可能である。さらに、静電容量方式は、抵抗膜方式に比べて位置情報の取得を高速で行うことができ、電極を物理的に摩耗させることもない。よって、近年では、静電容量方式のタッチパネルの市場における普及率が高まっている。

【0003】

また、タッチパネルを有する液晶表示装置には、タッチパネルの機能の一部を液晶パネル

10

20

30

40

50

の内部に組み込むインセルタイプと、偏光板と液晶パネルの間にタッチパネルを設けるオンセルタイプとがある。インセルタイプはオンセルタイプよりも、タッチパネルを有する液晶表示装置の薄型化、軽量化に有利である。

【0004】

下記の特許文献1には、静電容量方式のタッチパネルを有するインセルタイプの液晶表示装置について記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009-244958号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、液晶に横電界が掛かるFFS(Fringing Field Switching)モードなどの液晶パネルは、液晶に縦電界が掛かるTN(Twisted Nematic)モードなどの液晶パネルに比べて、押圧によりセルギャップが多少変化しても、液晶の配向が乱れにくい。よって、液晶に横電界が掛かる横電界モードの液晶パネルを、タッチパネルを有する液晶表示装置に用いることで、押圧が画像の表示に影響を及ぼすのを防ぐことができる。

【0007】

20

しかし、横電界モードの液晶パネルでは、トランジスタが形成された素子基板に対向する対向基板に電極が存在しない。そのため、対向基板に蓄積される電荷の分布を制御することが難しく、静電気の影響などにより、対向基板の一部に多くの電荷が蓄積される場合がある。その場合、蓄積された電荷によって、液晶に余計な電界が局所的に加わってしまい、輝度にむらが生じやすい。

【0008】

また、静電容量方式のタッチパネルでは、タッチパネルに含まれる電極どうし、または、これらの電極と指などの導電体との間に形成される、微小な容量の変化を検出することで、位置情報の取得を行う。そのため、液晶パネルの動作に必要な信号の電位の変化が、タッチパネルにおける位置情報の取得時にノイズとして悪影響を及ぼす恐れがある。特に、インセルタイプのタッチパネルを有する液晶表示装置では、タッチパネルの配線または電極と、トランジスタが形成された素子基板との距離が、オンセルタイプのタッチパネルを有する液晶表示装置に比べて短いため、タッチパネルの配線または電極と、液晶パネルに含まれる配線または電極との間に形成される寄生容量が大きくなりやすい。従って、インセルタイプのタッチパネルを有する液晶表示装置の方が、オンセルタイプのタッチパネルを有する液晶表示装置よりも、液晶パネルの動作に必要な信号の電位の変化がタッチパネルにおける位置情報の取得時にノイズとして悪影響を及ぼす恐れが大きい。

30

【0009】

また、インセルタイプのタッチパネルを有する液晶表示装置では、オンセルタイプのタッチパネルを有する液晶表示装置に比べて、位置情報を取得するための電極と、指などの導電体との距離が長い。そのため、インセルタイプのタッチパネルを有する液晶表示装置では、位置情報の取得の感度が低く、信号対雑音比(SN比)が小さくなりやすかった。

40

【0010】

上述したような技術的背景のもと、本発明の一態様は、輝度のむらが生じるのを防ぐことができる、タッチパネルを有する液晶表示装置の提供を課題の一つとする。或いは、本発明の一態様は、ノイズの影響を防ぎ、位置情報の取得を行うことができる液晶表示装置の提供を課題の一つとする。

【課題を解決するための手段】

【0011】

本発明の一態様に掛かる液晶表示装置は、絶縁膜を間に挟んで部分的に重なる画素電極及

50

び共通電極を第1基板に有する。また、絶縁膜を間に挟んで部分的に重なる一対の電極と、一対の電極を覆う樹脂膜と、樹脂膜上の導電膜とを第2基板に有する。そして、第1基板と第2基板とは、上記画素電極及び共通電極と、上記導電膜とが対向しており、なおかつ、第1基板と第2基板の間には液晶層が設けられている。

【0012】

第2基板に位置する一対の電極及び導電膜は、可視光に対して透光性を有する導電材料が用いられている。第2基板を透過した可視光は、一対の電極及び導電膜を通って、液晶層に入射する。

【0013】

また、第2基板に位置する導電膜には、所定の電位が与えられている。例えば、第2基板に位置する導電膜は、第1基板に位置する共通電極に電気的に接続されても良く、この場合、導電膜には共通電極と同じ電位が与えられることとなる。

10

【0014】

本発明の一態様では、一対の電極が第2基板に位置することで、第2基板に蓄積した電荷を、一対の電極のいずれか一方を介して放電させることができる。よって、第2基板の一部に電荷が蓄積するのを防ぎ、それにより、液晶層に局所的な電圧が加わるのを防ぎ、輝度にむらが生じるのを防ぐことができる。

【0015】

また、本発明の一態様では、第1基板に位置する画素電極及び共通電極と第2基板に位置する一対の電極との間に導電膜が存在することにより、画素電極または共通電極と上記導電膜の間に新たな寄生容量が形成され、なおかつ、一対の電極と上記導電膜の間に新たな寄生容量が形成される。そして、上記新たな寄生容量が形成された状態で、上記導電膜に所定の電位が与えられることで、画素電極に与えられる電位が変化しても、一対の電極の電位が変化するのを防ぐことができ、位置情報の取得により一対の電極の電位が変化しても、画素電極または共通電極の電位が変化するのを防ぐことができる。よって、本発明の一態様では、インセルタイプの液晶表示装置であっても、液晶パネルの動作に必要な信号の電位の変化が、タッチパネルにおける位置情報の取得時にノイズとして悪影響を及ぼすのを防ぐことができる。

20

【発明の効果】

【0016】

30

本発明の一態様により、輝度のむらが生じるのを防ぐことができる、タッチパネルを有する液晶表示装置を提供することができる。或いは、本発明の一態様により、ノイズの影響を防ぎ、位置情報の取得を行うことができる液晶表示装置を提供することができる。

【図面の簡単な説明】

【0017】

【図1】液晶表示装置の構成を示す図。

【図2】液晶表示装置の構成を示す図。

【図3】電極の形状を示す図。

【図4】電極の断面構造を示す図。

【図5】画素部及び画素の構成を示す図。

40

【図6】液晶表示装置の構成を示す図。

【図7】画素の上面図。

【図8】パネルの断面図。

【図9】素子基板の作製方法を示す図。

【図10】素子基板の作製方法を示す図。

【図11】対向基板の作製方法を示す図。

【図12】液晶表示装置の上面図。

【図13】液晶表示装置の断面図。

【図14】電子機器の図。

【発明を実施するための形態】

50

## 【0018】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

## 【0019】

なお、本明細書において液晶表示装置とは、液晶素子が各画素に形成されたパネルと、駆動回路またはコントローラを含むIC等を当該パネルに実装した状態にあるモジュールとを、その範疇に含む。

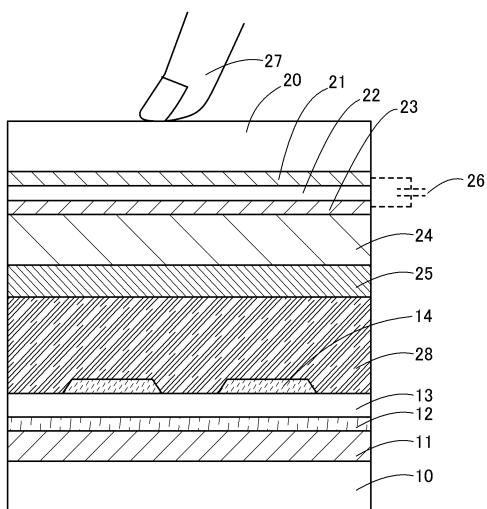

## 【0020】

## 液晶表示装置の画素の積層構造例

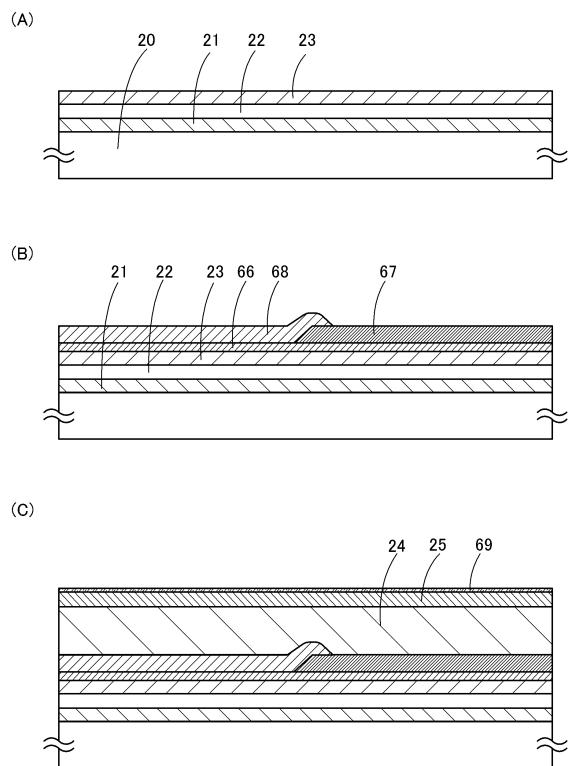

図1に、本発明の一態様に係る液晶表示装置の、画素の積層構造の一例を示す。

## 【0021】

本発明の一態様に係る液晶表示装置は、第1基板10に位置する、トランジスタなどの半導体素子、配線などが含まれる素子層11と、素子層11上の電極12と、電極12上の絶縁膜13と、絶縁膜13上において電極12と部分的に重なる電極14とを有する。電極12及び電極14は、一方が、画像信号に従って電位が制御される画素電極に相当し、他方が、画像信号に関わらず所定の電位が与えられる共通電極に相当する。

## 【0022】

さらに、本発明の一態様に係る液晶表示装置は、第2基板20に位置する、互いに部分的に重なり合う第1電極21及び第2電極23と、第1電極21と第2電極23の間に位置する絶縁膜22と、第1電極21及び第2電極23を覆う樹脂膜24と、樹脂膜24上の導電膜25とを有する。

## 【0023】

また、第1基板10と第2基板20とは、電極12及び電極14と、導電膜25とが対向しており、なおかつ、第1基板10と第2基板20の間において、電極12及び電極14と、導電膜25の間には、液晶材料を含む液晶層28が設けられている。電極12及び電極14と、上記電極12及び電極14から電界が加えられる液晶層28とにより、液晶素子が構成される。液晶層28に電界が加えられることで、液晶層28に含まれる液晶材料の配向が制御され、液晶層28の透過率が変化する。

## 【0024】

樹脂膜24は、第1電極21及び第2電極23の形状により導電膜25の平坦性が損なわれるのを防ぐ機能を有する。すなわち、第1電極21及び第2電極23が凹凸を有していても、第1電極21及び第2電極23と導電膜25の間に樹脂膜24を設けることで、第1電極21及び第2電極23の表面よりも導電膜25の表面の平坦性を高くすることができる。そして、図1では図示することを省略しているが、絶縁膜13及び電極14上と、導電膜25上には、それぞれ配向膜が設けられている。よって、樹脂膜24を設けることで、導電膜25の表面の平坦性を高め、延いては導電膜25上の配向膜の平坦性をも高めることができる。

## 【0025】

また、指などの導電体27が第2基板20に接近または接触することで、第1電極21及び第2電極23に付加した容量の静電容量は変化する。上記静電容量の変化を読み取ることで、導電体27の位置情報を取得することができる。例えば、位置情報の取得は、第1電極21と第2電極23の間に形成される容量26が有する、静電容量の変化を読み取ることで行うことができる。或いは、位置情報の取得は、第1電極21と第2電極23のそれぞれと、導電体27との間に形成される容量が有する、静電容量の変化を読み取ることで、行うことができる。

## 【0026】

また、本発明の一態様に係る液晶表示装置では、第2基板20が可視光に対して透光性を有し、なおかつ、第2基板20に位置する第1電極21及び第2電極23と、導電膜25

10

20

30

40

50

とには、可視光に対して透光性を有する導電材料が用いられているものとする。第2基板20として、例えば、ガラス基板、樹脂を有するプラスチック等の基板などを用いることができる。また、透光性を有する導電材料として、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛、酸化ケイ素を添加したインジウム錫酸化物などを用いることができる。

【0027】

第2基板20を透過した可視光は、第1電極21及び第2電極23と、導電膜25とを通って、液晶層28に入射する。

10

【0028】

本発明の一態様では、上述したように、位置情報の取得を行うのに用いる第1電極21及び第2電極23が第2基板20に位置している。上記構成により、第2基板20に蓄積した電荷を、第1電極21及び第2電極23のいずれか一方を介して放電させることができる。よって、第2基板20の一部に電荷が蓄積するのを防ぎ、それにより、液晶層28に局所的な電圧が加わるのを防ぎ、輝度にむらが生じるのを防ぐことができる。

【0029】

また、本発明の一態様では、第1基板10と第2基板20の間に、位置情報の取得を行うための第1電極21及び第2電極23が位置する、インセルタイプの液晶表示装置である。ただし、インセルタイプの液晶表示装置であっても、第1基板10に位置する電極12及び電極14と、第2基板20に位置する第1電極21及び第2電極23との間に導電膜25が存在することにより、電極12または電極14と導電膜25の間に新たな寄生容量が形成され、なおかつ、第1電極21または第2電極23と導電膜25の間に新たな寄生容量が形成される。そして、上記新たな寄生容量が形成された状態で、導電膜25に所定の電位が与えられることで、電極12または電極14に与えられる電位が変化しても、第1電極21及び第2電極23の電位が変化するのを防ぐことができる。なおかつ、位置情報の取得により第1電極21または第2電極23の電位が変化しても、電極12または電極14の電位が変化するのを防ぐことができる。したがって、位置情報を取得する際に、電極12または電極14に与えられる電位の変化が、ノイズとして位置情報に含まれてしまうのを防ぐことができ、当該ノイズの影響を受けずに位置情報の取得を行うことができる。

20

【0030】

また、本発明の一態様に係る液晶表示装置では、電極12または電極14に、位置情報の取得を行う機能を持たせた液晶表示装置とは異なり、画像の表示と、位置情報の取得とを、互いに独立させて行うことができる。また、本発明の一態様では、導電膜25の存在により、画像の表示と位置情報の取得とを並行して行ったとしても、位置情報の取得による第1電極21及び第2電極23の電位の変化が、画像の表示に影響を及ぼすのを防ぐことができ、なおかつ、画像の表示による電極12または電極14の電位の変化が、位置情報の取得に影響を及ぼすのを防ぐことができる。よって、画像の表示が行われない帰線期間などの短い期間内に高速で位置情報の取得を行う必要がなく、位置情報の取得を行うための制御を行う駆動回路の負担を小さく抑えることができる。

30

【0031】

また、位置情報の取得を行うための一対の電極を、第2基板20が有する第1の面と第2の面とに分けて形成する液晶表示装置の場合、電極の形成時において、第2基板20の両面に物理的に接触することなく第2基板20を支持することが難しいため、電極を形成するための装置、或いは作製工程が複雑になる。本発明の一態様に係る液晶表示装置では、第1電極21及び第2電極23と、導電膜25とを、第2基板20が有する一方の面にまとめて形成することができるので、第1電極21及び第2電極23を形成するための装置、或いは作製工程を簡素化することができる。

40

【0032】

50

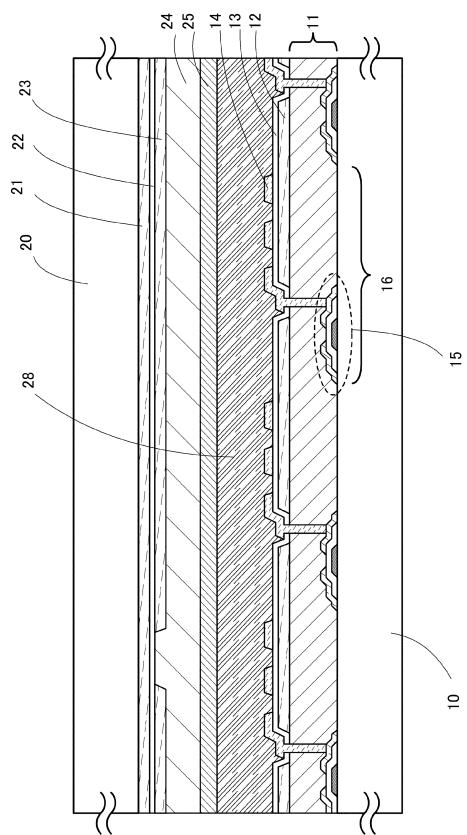

## 液晶表示装置の画素の積層構造例 2

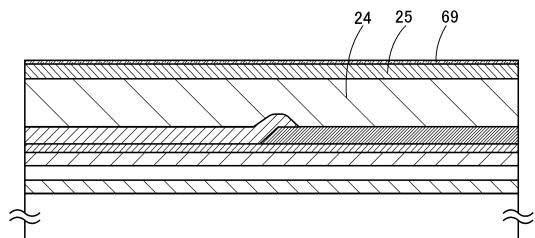

次いで、図 1 に示した液晶表示装置の、画素のより詳細な積層構造の一例を図 2 に示す。

## 【 0 0 3 3 】

図 2 に示す液晶表示装置では、図 1 に示した液晶表示装置と同様に、第 1 基板 10 に位置する、素子層 11 と、素子層 11 上の電極 12 と、電極 12 上の絶縁膜 13 と、絶縁膜 13 上において電極 12 と部分的に重なる電極 14 とを有する。そして、図 2 では、素子層 11 にトランジスタ 15 が含まれており、トランジスタ 15 のソース及びドレインの一方が、電極 14 に電気的に接続されている。すなわち、図 2 では、電極 14 が画素電極、電極 12 が共通電極である場合を例示している。

## 【 0 0 3 4 】

10

画素電極である電極 14 は、画素 16 ごとに電気的に分離しており、共通電極である電極 12 は、複数の画素 16 間で電気的に接続されている。

## 【 0 0 3 5 】

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して電気的に接続している状態も、その範疇に含む。

## 【 0 0 3 6 】

20

また、トランジスタのソースとは、活性層として機能する半導体膜の一部であるソース領域、或いは上記半導体膜に電気的に接続されたソース電極を意味する。同様に、トランジスタのドレインとは、活性層として機能する半導体膜の一部であるドレイン領域、或いは上記半導体膜に電気的に接続されたドレイン電極を意味する。また、ゲートはゲート電極を意味する。

## 【 0 0 3 7 】

30

また、トランジスタが有するソースとドレインは、トランジスタのチャネル型及び各端子に与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、n チャネル型トランジスタでは、低い電位が与えられる端子がソースと呼ばれ、高い電位が与えられる端子がドレインと呼ばれる。また、p チャネル型トランジスタでは、低い電位が与えられる端子がドレインと呼ばれ、高い電位が与えられる端子がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

## 【 0 0 3 8 】

また、図 2 に示す液晶表示装置では、図 1 に示した液晶表示装置と同様に、第 2 基板 20 に位置する、第 1 電極 21 と、第 1 電極 21 上の絶縁膜 22 と、絶縁膜 22 を間に挟んで、第 1 電極 21 と部分的に重なる第 2 電極 23 と、第 1 電極 21 及び第 2 電極 23 を覆う樹脂膜 24 と、樹脂膜 24 上の導電膜 25 とを有する。

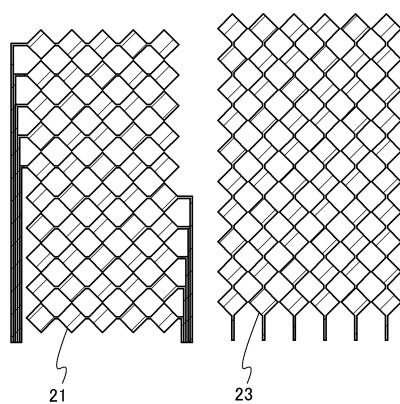

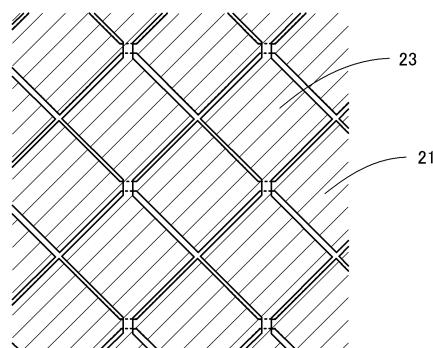

## 【 0 0 3 9 】

40

図 3 (A) に、第 1 電極 21 と第 2 電極 23 のそれぞれの形状を平面図にて示す。また、図 3 (B) に、重なり合った第 1 電極 21 及び第 2 電極 23 を拡大した平面図を示す。

## 【 0 0 4 0 】

図 3 (A) に示すように、液晶表示装置には、複数の第 1 電極 21 と、複数の第 2 電極 23 とが交差するように設けられている。図 3 (A) では、複数の第 1 電極 21 と、複数の第 2 電極 23 とは、矩形状の導電膜が複数接続された形状を有している。そして、複数の第 1 電極 21 と、第 2 複数の電極 23 とは、図 3 (B) に示すように、導電膜の矩形状を有する部分の位置が互いにずれるように、配置されている。そして、第 1 電極 21 と第 2 電極 23 の交差する部分には、第 1 電極 21 と第 2 電極 23 が接触しないように、間に図 1 及び図 2 で示した絶縁膜 22 が設けられている。第 1 電極 21 と第 2 電極 23 の交差する部分には、容量が形成される。

50

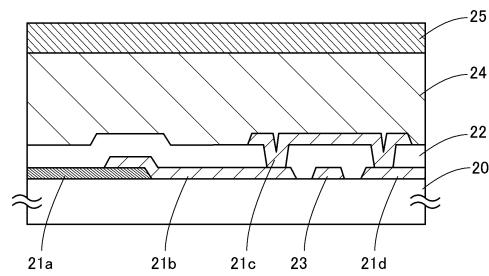

## 【0041】

図4に、第1電極21と第2電極23とが交差する部分における、第2基板20の断面図を一例として示す。図4では、第1電極21が、電気的に接続された導電膜21a乃至導電膜21dを有する場合を例示している。導電膜21a、導電膜21b、導電膜21d、及び第2電極23は、同一の絶縁表面上(図4では第2基板20上である場合を例示)に形成されている。そして、導電膜21a、導電膜21b、導電膜21d、及び第2電極23上には、絶縁膜22が設けられている。導電膜21cは、第2電極23を跨ぐように絶縁膜22上に設けられており、なおかつ、導電膜21cは、絶縁膜22に設けられた開口部において、導電膜21b及び導電膜21dに接続されている。上記構成により、第2電極23に接触することなく、導電膜21a乃至導電膜21dを含む第1電極21と、第2電極23とを交差させることができる。

## 【0042】

第1電極21と第2電極23は、可視光に対して透光性を有する、上述した様な導電材料を用いて形成することができる。ただし、導電膜21aが引き回しのための配線である場合、導電膜21aは必ずしも可視光に対して透光性を有する導電材料で形成する必要はない。

## 【0043】

## 画素部の回路構成例

次いで、液晶表示装置の画素部の回路構成例について説明する。

## 【0044】

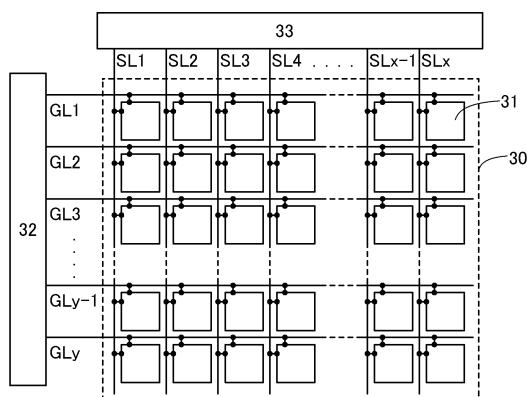

図5に示す画素部30には、複数の画素31と、画素31を行毎に選択するための、配線GL1乃至配線GLy(yは自然数)で示される配線GLと、選択された画素31に画像信号を供給するための、配線SL1乃至配線SLx(xは自然数)で示される配線SLとが、設けられている。配線GLへの信号の入力は、駆動回路32により制御されている。配線SLへの画像信号の入力は、駆動回路33により制御されている。複数の画素31は、配線GLの少なくとも一つと、配線SLの少なくとも一つとに、それぞれ接続されている。

## 【0045】

なお、画素部30に設けられる配線の種類及びその数は、画素31の構成、数及び配置によって決めることができる。具体的に、図5に示す画素部30の場合、x列×y行の画素31がマトリクス状に配置されており、配線SL1乃至配線SLx、配線GL1乃至配線GLyが、画素部30内に配置されている場合を例示している。

## 【0046】

図5(B)に、画素の構成例を示す。図5(B)に示す画素31は、液晶素子34と、当該液晶素子34への画像信号の供給を制御するトランジスタ35とを有する。

## 【0047】

液晶素子34は、画素電極と、共通電極と、画素電極と共通電極の間の電圧が印加される液晶材料を含んだ液晶層とを有している。そして、図5(B)では、液晶素子34がFFSモードである場合を例示しており、画素電極と共通電極とが絶縁膜を挟んで重なる領域を有している。当該領域は、画素電極と共通電極の間に印加される電圧VLcを保持するための容量としての機能を有する。図5(B)では、上記容量を容量素子36として、図示する。

## 【0048】

トランジスタ35は、配線SLに入力される画像信号の電位を、液晶素子34の画素電極に与えるか否かを制御する。液晶素子34の共通電極には、所定の基準電位Vcomが与えられている。

## 【0049】

以下、液晶素子34と、トランジスタ35の、具体的な接続関係について説明する。

## 【0050】

図5(B)に示す画素31では、トランジスタ35のゲートが配線GLに電気的に接続さ

10

20

30

40

50

れている。トランジスタ35のソース及びドレインの一方は、配線S-Lに接続され、トランジスタ35のソース及びドレインの他方は、液晶素子34の画素電極に接続されている。

【0051】

なお、画素31は、必要に応じて、トランジスタ、ダイオード、抵抗素子、容量素子、インダクタなどのその他の回路素子を、さらに有していても良い。

【0052】

図5(B)では、画素31において、画像信号の画素31への入力を制御するスイッチとして、一のトランジスタ35を用いる場合を例示している。しかし、画素31において、複数のトランジスタを一のスイッチとして機能させても良い。複数のトランジスタが一のスイッチとして機能する場合、上記複数のトランジスタは並列に接続されていても良いし、直列に接続されていても良いし、直列と並列が組み合わされて接続されていても良い。

10

【0053】

なお、本明細書において、トランジスタが直列に接続されている状態とは、例えば、第1のトランジスタのソースまたはドレインの一方のみが、第2のトランジスタのソースまたはドレインの一方のみに接続されている状態を意味する。また、トランジスタが並列に接続されている状態とは、第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの他方が第2のトランジスタのソースまたはドレインの他方に接続されている状態を意味する。

20

【0054】

トランジスタ35のオフ電流が極めて小さい場合、液晶素子34に与えられる電圧が保持される期間を長く確保することができる。そのため、静止画のように、連続する幾つかのフレーム期間に渡って、画素31に同じ画像情報を有する画像信号が書き込まれる場合などは、駆動周波数を低くする、言い換えると一定期間内における画素31への画像信号の書き込み回数を少なくしても、階調の表示を維持することができる。例えば、高純度化された酸化物半導体をチャネル形成領域に含むトランジスタ35を用いることで、画像信号の書き込みの間隔を10秒以上、好ましくは30秒以上、さらに好ましくは1分以上にすることができる。そして、画像信号が書き込まれる間隔を長くすればするほど、消費電力をより低減することができる。

30

【0055】

液晶素子34では、画素電極と共通電極の間に与えられる電圧の値に従って、液晶分子の配向が変化し、透過率が変化する。よって、液晶素子34は、配線S-Lに与えられる画像信号の電位によって、その透過率が制御されることで、階調を表示することができる。

【0056】

なお、液晶は、電圧が印加されてからその透過率が収束するまでの応答時間が、一般的に十数msec程度である。よって、液晶の応答の遅さが動画のぼやけとして視認されやすい。そこで、本発明の一態様では、液晶素子34に印加する電圧を一時的に大きくして液晶の配向を速く変化させるオーバードライブ駆動を用いるようにしても良い。オーバードライブ駆動を用いることで、液晶の応答速度を上げ、動画のぼやけを防ぎ、動画の画質を改善することができる。

40

【0057】

また、トランジスタ35が非導通状態になった後においても、液晶素子34の透過率が収束せずに変化し続けると、液晶の比誘電率が変化するため、液晶素子34の保持する電圧が変化しやすい。特に、本発明の一態様のように、液晶素子34に接続される容量素子36の容量値が小さい場合、上述した液晶素子34の保持する電圧の変化は顕著に起こりやすい。しかし、上記オーバードライブ駆動を用いることで、応答時間を短くすることができるので、トランジスタ35が非導通状態になった後における液晶素子34の透過率の変化を小さくすることができる。したがって、液晶素子34に並列で接続される容量素子36の容量値が小さい場合でも、トランジスタ35が非導通状態になった後に、液晶素子3

50

4の保持する電圧が変化するのを防ぐことができる。

【0058】

液晶表示装置の構成例

次いで、本発明の一態様に係る液晶表示装置の構成例について説明する。

【0059】

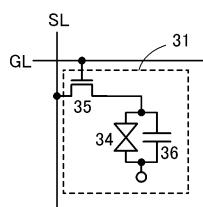

図6に、本発明の一態様に係る液晶表示装置の構成を、一例としてブロック図で示す。図6に示す液晶表示装置40は、画素31を画素部30に複数有するパネル38と、コントローラ41とを有する。さらに、図6に示す液晶表示装置40は、CPU43と、画像処理回路44と、画像メモリ45とを有する。また、図6に示す液晶表示装置40は、パネル38に、駆動回路32と、駆動回路33とを有する。

10

【0060】

コントローラ41は、駆動回路32や駆動回路33などの動作を制御する各種の駆動信号を、パネル38に供給する機能を有する。駆動信号には、駆動回路33の動作を制御する駆動回路33用のスタートパルス信号、駆動回路33用のクロック信号、駆動回路32の動作を制御する駆動回路32用のスタートパルス信号、駆動回路32用のクロック信号などが含まれる。

【0061】

画素部30は、各画素31において階調を表示することで画像を表示する機能を有するほか、位置情報を取得する入力装置としての機能をも有する。また、CPU43は、画素部30において取得された位置情報に従って、入力された命令をデコードし、液晶表示装置40が有する各種回路の動作を統括的に制御することで、当該命令を実行する機能を有する。

20

【0062】

よって、画素部30において取得された位置情報に従って、パネル38を動作状態から停止状態に移行させるための命令、或いは、画素部30を停止状態から動作状態に移行させるための命令を、CPU43が実行することができる。

【0063】

例えば、画素部30において取得された位置情報に従って、画素部30を動作状態から停止状態に移行させる命令が送られてきた場合、CPU43は、画素部30への電源電圧の供給を停止させ、なおかつ、パネル38への駆動信号の供給を停止させるように、コントローラ41に命令を出すことができる。

30

【0064】

或いは、画素部30において取得された位置情報に従って、画素部30を停止状態から動作状態に移行させる命令が送られてきた場合、CPU43は、画素部30への電源電圧の供給を再開させるように、なおかつ、パネル38への駆動信号の供給を再開させるように、コントローラ41に命令を出すことができる。

【0065】

画像メモリ45は、液晶表示装置40に入力された画像情報を有する画像データ46を、記憶する機能を有する。なお、図6では、画像メモリ45を1つだけ液晶表示装置40に設ける場合を例示しているが、複数の画像メモリ45が液晶表示装置40に設けられても良い。例えば、赤、青、緑などの色相にそれぞれ対応する3つの画像データ46により、画素部30にフルカラーの画像が表示される場合、各色相の画像データ46に対応した画像メモリ45を、それぞれ設けるようにしても良い。

40

【0066】

画像メモリ45には、例えばDRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)等の記憶回路を用いることができる。或いは、画像メモリ45に、VRAM(Video RAM)を用いても良い。

【0067】

画像処理回路44は、コントローラ41からの命令に従い、画像データ46の画像メモリ

50

45への書き込みと、画像データ46の画像メモリ45からの読み出しを行い、画像データ46から画像信号を生成する機能を有する。

【0068】

画素のレイアウト

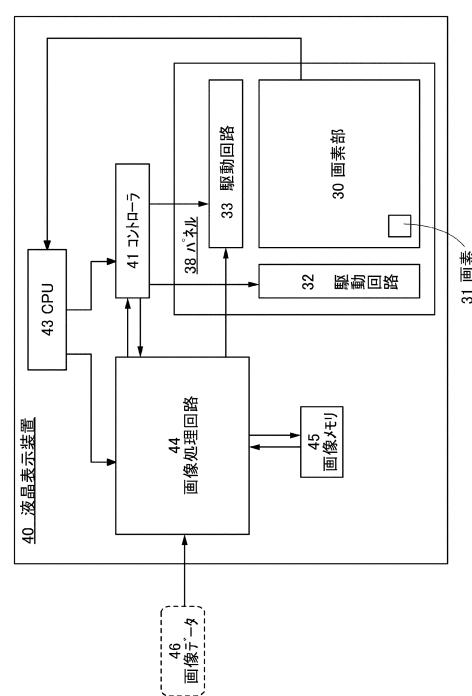

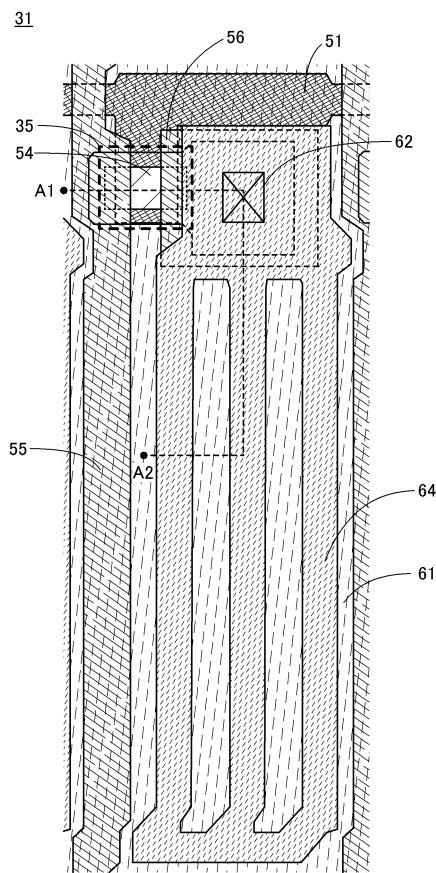

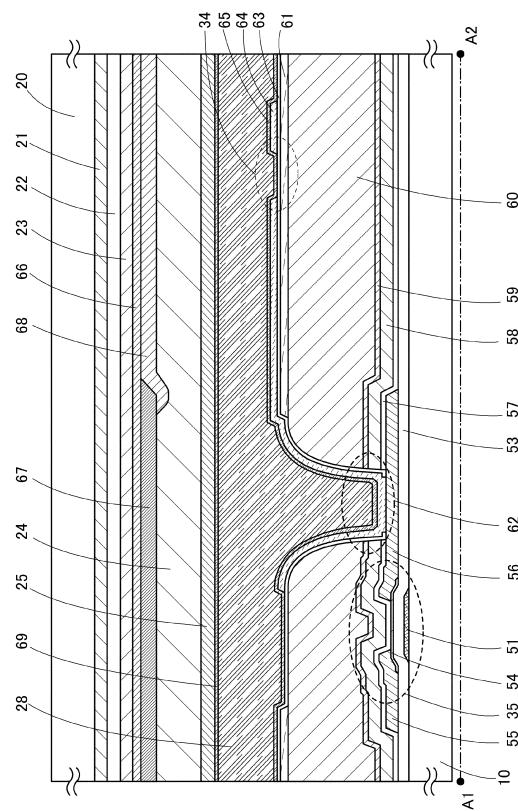

次いで、図5(B)に示す画素31の一例を図7に示す。なお、図7では、画素31のレイアウトを明確にするために、ゲート絶縁膜などの各種の絶縁膜や酸化物膜を省略している。また、図7に示す素子基板を用いて形成された液晶表示装置の断面図を、図8に示す。図8に示す液晶表示装置のうち、第1基板10を含む素子基板は、図7の破線A1-A2における断面図に相当する。

【0069】

図7及び図8に示す画素31は、絶縁表面を有する第1基板10上に、トランジスタ35のゲートとしての機能と、配線GLとしての機能を有する導電膜51が、設けられている。

【0070】

また、導電膜51を覆うように、第1基板10上には絶縁膜53が設けられている。そして、絶縁膜53を間に挟んで導電膜51と重なる位置に、トランジスタ35の半導体膜54が設けられている。半導体膜54上には、導電膜55及び導電膜56が設けられている。導電膜55は、配線SLとしての機能と、トランジスタ35のソースまたはドレインとしての機能とを有する。導電膜56は、トランジスタ35のソースまたはドレインとしての機能を有する。

【0071】

半導体膜54、導電膜55、及び導電膜56上には、酸化物膜57、絶縁膜58、及び絶縁膜59が順に積層されている。そして、絶縁膜59上には、有機樹脂膜60が設けられている。酸化物膜57、絶縁膜58、及び絶縁膜59と、有機樹脂膜60とには開口部62が設けられている。

【0072】

有機樹脂膜60上の開口部62以外の領域には、共通電極としての機能を有する導電膜61が設けられている。そして、導電膜61上には、絶縁膜63が設けられており、絶縁膜63上において導電膜61と部分的に重なる位置には画素電極としての機能を有する導電膜64が設けられている。絶縁膜63には、開口部62と重なる位置に開口部を有しており、絶縁膜63の当該開口部において、導電膜64が導電膜56に接続されている。また、導電膜64上には配向膜65が設けられている。

【0073】

また、第1基板10と対向するように、第2基板20が設けられている。第2基板20上には、部分的に重なり合う第1電極21及び第2電極23と、第1電極21と第2電極23の間に位置する絶縁膜22とが設けられている。第1電極21及び第2電極23上には、絶縁膜66が設けられている。

【0074】

絶縁膜66上には、可視光を遮る機能を有する遮蔽膜67と、特定の波長範囲の可視光を透過する着色層68とが、設けられている。遮蔽膜67及び着色層68上には、樹脂膜24が設けられており、樹脂膜24上には導電膜25が設けられている。また、導電膜25上には配向膜69が設けられている。

【0075】

そして、第1基板10と第2基板20の間には、配向膜65と配向膜69に挟まれるように、液晶材料を含む液晶層28が設けられている。液晶素子34は、導電膜61、導電膜64、及び液晶層28を有する。

【0076】

なお、半導体膜54に酸化物半導体が用いられている場合、導電膜55及び導電膜56に用いられる導電性材料によっては、導電膜55及び導電膜56中の金属が、酸化物半導体から酸素を引き抜くことがある。この場合、半導体膜54のうち、導電膜55及び導電膜

10

20

30

40

50

5 6 に接する領域が、酸素欠損の形成により n 型化されうる。

【 0 0 7 7 】

n 型化された領域は、ソース領域またはドレイン領域として機能するため、半導体膜 5 4 と導電膜 5 5 及び導電膜 5 6 との間におけるコンタクト抵抗を下げることができる。よって、n 型化された領域が形成されることで、トランジスタ 3 5 の移動度及びオン電流を高めることができ、それにより、トランジスタ 3 5 を用いた半導体装置の高速動作を実現することができる。

【 0 0 7 8 】

なお、導電膜 5 5 及び導電膜 5 6 中の金属による酸素の引き抜きは、導電膜 5 5 及び導電膜 5 6 をスパッタリング法などにより形成する際に起こりうるし、導電膜 5 5 及び導電膜 5 6 を形成した後に行われる加熱処理によっても起こりうる。

10

【 0 0 7 9 】

また、n 型化される領域は、酸素と結合し易い導電性材料を導電膜 5 5 及び導電膜 5 6 に用いることで、より形成されやすくなる。上記導電性材料としては、例えば、A l、C r、C u、T a、T i、M o、W などが挙げられる。

【 0 0 8 0 】

作製方法

次いで、図 7 に示した素子基板の作製方法について、一例を挙げて説明する。なお、酸化物半導体膜にチャネル形成領域を有するトランジスタ 3 5 を例に挙げて素子基板の作製方法について説明するが、トランジスタ 3 5 は、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの半導体膜を活性層に用いることもできる。

20

【 0 0 8 1 】

図 9 ( A ) に示すように、第 1 基板 1 0 上に導電膜を形成した後、上記導電膜をエッティング等により形状を加工 ( パターニング ) することで、導電膜 5 1 を形成する。

【 0 0 8 2 】

第 1 基板 1 0 としては、後の作製工程において耐えうる程度の耐熱性を有する基板が望ましく、例えば、ガラス基板、石英基板、セラミック基板、サファイア基板等が用いられる。

【 0 0 8 3 】

導電膜 5 1 としては、アルミニウム、チタン、クロム、コバルト、ニッケル、銅、イットリウム、ジルコニア、モリブデン、ルテニウム、銀、タンタル及びタンゲステンを一種以上含む導電性材料でなる膜を 1 層または 2 層以上積層させて用いるとよい。例えば、導電膜 5 1 として、窒化タンゲステン膜上に銅膜を積層した導電膜や、単層のタンゲステン膜を用いることができる。

30

【 0 0 8 4 】

次いで、導電膜 5 1 を覆うように、絶縁膜 5 3 を形成した後、絶縁膜 5 3 上において導電膜 5 1 と重なる位置に、半導体膜 5 4 を形成する ( 図 9 ( B ) 参照 ) 。

【 0 0 8 5 】

絶縁膜 5 3 としては、酸化アルミニウム、酸化マグネシウム、酸化珪素、酸化窒化珪素、窒化酸化珪素、窒化珪素、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム及び酸化タンタルを一種以上含む絶縁膜を、単層で、または積層させて用いればよい。

40

【 0 0 8 6 】

例えば、2 層構造の絶縁膜 5 3 とする場合、1 層目を窒化珪素膜とし、2 層目を酸化珪素膜とした多層膜とすればよい。2 層目の酸化珪素膜は酸化窒化珪素膜にすることができる。また、1 層目の窒化珪素膜を窒化酸化珪素膜とすることができる。

【 0 0 8 7 】

酸化珪素膜は、欠陥密度の小さい酸化珪素膜を用いると好ましい。具体的には、電子スピニ共鳴 ( E S R : E l e c t r o n S p i n R e s o n a n c e ) にて g 値が 2.0 0 1 の信号に由来するスピニのスピニ密度が  $3 \times 10^{17}$  spins / cm<sup>3</sup> 以下、好ま

50

しくは  $5 \times 10^{-6}$  spins/cm<sup>3</sup> 以下である酸化珪素膜を用いる。酸化珪素膜は、過剰に酸素を有する酸化珪素膜を用いると好ましい。窒化珪素膜は水素及びアンモニアの放出量が少ない窒化珪素膜を用いる。水素、アンモニアの放出量は、TDS (Thermal Desorption Spectroscopy: 昇温脱離ガス分光法) 分析にて測定すればよい。

#### 【0088】

半導体膜 54 として、酸化物半導体膜を用いることができる。半導体膜 54 として用いる酸化物半導体膜に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタの閾値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜の形成後において、脱水化処理（脱水素化処理）を行い酸化物半導体膜から、水素、又は水分を除去して不純物が極力含まれないようにすることができる。

10

#### 【0089】

なお、酸化物半導体膜への脱水化処理（脱水素化処理）によって、酸化物半導体膜から酸素が減少してしまうことがある。よって、脱水化処理（脱水素化処理）によって増加した酸素欠損を補填するため酸素を酸化物半導体膜に加える処理を行うことができる。

#### 【0090】

このように、酸化物半導体膜は、脱水化処理（脱水素化処理）により、水素または水分が除去され、加酸素化処理により酸素欠損を補填することによって、i型（真性）化またはi型に限りなく近く実質的にi型（真性）である酸化物半導体膜とすることができます。

20

#### 【0091】

次いで、半導体膜 54 及び絶縁膜 53 上に導電膜を形成した後、当該導電膜の形状をエッティング等により加工することにより、半導体膜 54 に接する導電膜 55 及び導電膜 56 を形成する（図 9（C）参照）。導電膜 55 及び導電膜 56 は、導電膜 51 と同じ導電性材料を用いることができる。

#### 【0092】

次いで、第1基板 10 を覆うように、酸化物膜または絶縁膜を形成する。図 9（D）では、酸化物膜 57、絶縁膜 58 及び絶縁膜 59 を順に積層するように形成する場合を例示する。

#### 【0093】

30

酸化物膜 57 には、金属酸化物を用いることが望ましい。酸化物膜 57 を用いることで、シリコンが含まれた絶縁膜 58 と、半導体膜 54 とを、離隔することができる。よって、半導体膜 54 に、インジウムを含む金属酸化物が用いられている場合に、酸素との結合エネルギーがインジウムよりも大きいシリコンが、半導体膜 54 の端部において、インジウムと酸素の結合を切断し、酸素欠損を形成するのを防ぐことができる。それにより、本発明の一態様では、トランジスタの信頼性をさらに高めることができる。

#### 【0094】

具体的に、酸化物膜 57 は、スパッタリング法により、金属の原子数比が 1:6:4、1:3:4、若しくは 1:3:2 である、In-Ga-Zn 系酸化物ターゲットを用いて、形成することができる。

40

#### 【0095】

絶縁膜 59 は、絶縁膜 58 を形成した後、大気に曝すことなく連続的に形成することができる。絶縁膜 58 を形成した後、大気開放せず、原料ガスの流量、圧力、高周波電力及び基板温度の一以上を調整して、絶縁膜 59 を連続的に形成することで、絶縁膜 58、及び絶縁膜 59 における界面の不純物濃度を低減することができると共に、絶縁膜 59 に含まれる酸素を半導体膜 54 に移動させることができ、半導体膜 54 の酸素欠損量を低減することができる。

#### 【0096】

プラズマ CVD 装置の真空排気された処理室内に載置された基板を 180 以上 400 以下、さらに好ましくは 200 以上 370 以下に保持し、処理室に原料ガスを導入し

50

て処理室内における圧力を 30 Pa 以上 250 Pa 以下、さらに好ましくは 40 Pa 以上 200 Pa 以下とし、処理室内に設けられる電極に高周波電力を供給する条件により、絶縁膜 58 として酸化珪素膜または酸化窒化珪素膜を形成する。

【0097】

絶縁膜 58 の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

【0098】

上記条件を用いることで、絶縁膜 58 として酸素を透過する酸化絶縁膜を形成することができる。また、絶縁膜 58 を設けることで、後に形成する絶縁膜 59 の形成工程において、酸化物膜 57 へのダメージ低減が可能である。

10

【0099】

なお、シリコンを含む堆積性気体に対する酸化性気体の流量を 100 倍以上とすることでき、絶縁膜 58 における水素の含有量を低減することができると共に、絶縁膜 58 に含まれるダングリングボンドを低減することができる。絶縁膜 59 から移動する酸素は、絶縁膜 58 に含まれるダングリングボンドによって捕獲される場合があるため、絶縁膜 59 に含まれる酸素を効率よく半導体膜 54 へ移動させ、半導体膜 54 に含まれる酸素欠損を補填することができる。この結果、半導体膜 54 に混入する水素量を低減できると共に半導体膜 54 に含まれる酸素欠損を低減させることができると共に、トランジスタの閾値電圧のマイナスシフトを抑制することができると共に、トランジスタのソース及びドレインにおけるリーク電流を低減することができる、トランジスタの電気的特性を向上させることができる。

20

【0100】

本実施の形態では、絶縁膜 58 として、流量 20 sccm のシラン及び流量 3000 sccm の一酸化二窒素を原料ガスとし、処理室の圧力を 40 Pa、基板温度を 220 とし、27.12 MHz の高周波電源を用いて 100 W の高周波電力を平行平板電極に供給したプラズマ CVD 法により、厚さ 50 nm の酸化窒化珪素膜を形成する。なお、プラズマ CVD 装置は電極面積が 6000 cm<sup>2</sup> である平行平板型のプラズマ CVD 装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると  $1.6 \times 10^{-2} \text{ W/cm}^2$  である。当該条件により、酸素を透過する酸化窒化珪素膜を形成することができる。

30

【0101】

絶縁膜 59 は、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 180 以上 260 以下、さらに好ましくは 180 以上 230 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を 100 Pa 以上 250 Pa 以下、さらに好ましくは 100 Pa 以上 200 Pa 以下とし、処理室内に設けられる電極に 0.17 W/cm<sup>2</sup> 以上 0.5 W/cm<sup>2</sup> 以下、さらに好ましくは 0.25 W/cm<sup>2</sup> 以上 0.35 W/cm<sup>2</sup> 以下の高周波電力を供給する条件により、酸化珪素膜または酸化窒化珪素膜を形成する。

40

【0102】

絶縁膜 59 の成膜条件として、上記圧力の処理室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、絶縁膜 59 中における酸素含有量が化学量論的組成よりも多くなる。しかしながら、基板温度が、上記温度であると、シリコンと酸素の結合力が弱いため、加熱により酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化絶縁膜を形成することができる。また、酸化物膜 57 上に絶縁膜 58 が設けられている。このため、絶縁膜 59 の形成工程において、絶縁膜 58 が酸化物膜 57 の保護をする機能を有する。この結果、半導体膜 54 へのダメージを低減しつつ、パワー密度の高い高周波電力を用いて絶縁膜 59 を形成することができる。

50

## 【0103】

本実施の形態では、絶縁膜59として、流量160sccmのシラン及び流量4000sccmの一酸化二窒素を原料ガスとし、処理室の圧力を200Pa、基板温度を220とし、27.12MHzの高周波電源を用いて1500Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ400nmの酸化窒化珪素膜を形成する。なお、プラズマCVD装置は電極面積が6000cm<sup>2</sup>である平行平板型のプラズマCVD装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると2.5×10<sup>-1</sup>W/cm<sup>2</sup>である。

## 【0104】

次いで、少なくとも絶縁膜59を形成した後に加熱処理を行い、絶縁膜58または絶縁膜59に含まれる酸素を酸化物膜57及び半導体膜54に移動させ、酸化物膜57及び半導体膜54の酸素欠損を補填することが好ましい。なお、該加熱処理は、半導体膜54の脱水素化または脱水化を行う加熱処理として行えばよい。

## 【0105】

次いで、第1基板10を覆うように有機樹脂膜60を形成する。有機樹脂膜60は、後に形成される導電膜61及び導電膜64の下地となる膜であり、トランジスタや導電膜等により、共通電極として機能する導電膜61と、画素電極として機能する導電膜64とに、凹凸が形成されるのを防ぐ機能を有する。有機樹脂膜60には、アクリル樹脂、ポリイミド樹脂等を用いることができる。

## 【0106】

そして、有機樹脂膜60、酸化物膜57、絶縁膜58、絶縁膜59に開口部62を形成する（図10（A）参照）。開口部62において、導電膜56が部分的に露出される。

## 【0107】

なお、開口部62は、一のフォトマスクを用いて形成しても良いし、有機樹脂膜60に開口部を形成するためのフォトマスクと、酸化物膜57、絶縁膜58、絶縁膜59に開口部を形成するためのフォトマスクとを、それぞれ用いて形成することもできる。

## 【0108】

次いで、有機樹脂膜60上に透明導電膜を形成し、当該透明導電膜をエッチング等により所望の形状に加工して導電膜61を形成した後、導電膜61及び有機樹脂膜60上に絶縁膜63を形成する。そして、開口部62において、導電膜56が部分的に露出されるような開口部を絶縁膜63に形成する（図10（B）参照）。

## 【0109】

絶縁膜63は、外部から水や不純物の侵入を防ぐ機能を有する。また、絶縁膜63は、導電膜61と導電膜64が重なった領域に形成される容量素子36の誘電体としての機能を有する。絶縁膜63は、窒化物または窒化酸化物でなる絶縁膜が好ましく、例えば、窒化シリコン膜、窒化酸化シリコン膜を形成すればよい。

## 【0110】

次いで、絶縁膜63上に透明導電膜を形成し、エッチング等により当該透明導電膜の形状を加工することで、導電膜64を形成する。導電膜64は導電膜56に接続されている。その後、導電膜64上に配向膜65を形成する（図10（C）参照）。

## 【0111】

なお、導電膜61及び導電膜64を形成するのに用いられる透明導電膜としては、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛、酸化ケイ素を添加したインジウム錫酸化物等を含む導電膜を用いることができる。

## 【0112】

また、配向膜65は、ポリイミド、ポリビニルアルコールなどの有機樹脂を用いて形成することができ、その表面には、ラビングなどの、液晶分子を一定方向に配列させるための配向処理が施されている。ラビングは、配向膜65に接するように、ナイロンなどの布を

10

20

30

40

50

巻いたローラーを回転させて、上記配向膜65の表面を一定方向に擦ることで、行うことができる。なお、酸化珪素などの無機材料を用い、配向処理を施すことなく、蒸着法で配向特性を有する配向膜65を直接形成することも可能である。

【0113】

以上までの作製工程により、図7に示す素子基板を形成することができる。

【0114】

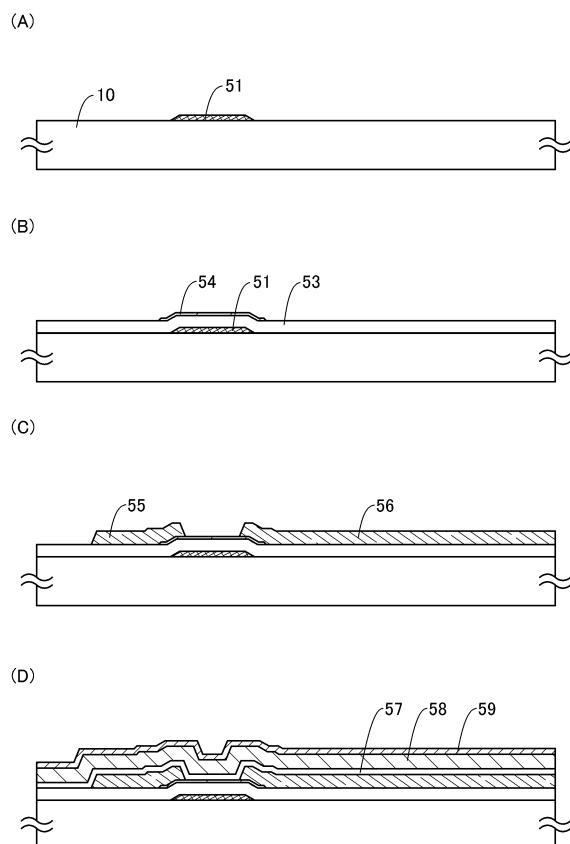

また、図11(A)に示すように、第2基板20上に第1電極21と、第1電極21上の絶縁膜22と、絶縁膜22上の第2電極23とを形成する。第2基板20は可視光に対して透光性を有しており、ガラス基板、石英基板などを用いることができる。或いは、後に行われる作製工程に耐えうる程度の耐熱性を有するのであれば、プラスチック基板などを用いることができる。

10

【0115】

第1電極21及び第2電極23は、透光性を有する導電材料を用いることができる。例えば、透光性を有する導電材料として、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを含む酸化亜鉛、酸化ケイ素を含むインジウム錫酸化物などを用いることができる。本実施の形態では、酸化珪素を含む酸化インジウムスズを用いて、膜厚220nmの第1電極21及び第2電極23を形成する。

【0116】

20

次いで、図11(B)に示すように、第1電極21及び第2電極23上に絶縁膜66を形成した後、絶縁膜66上に、可視光を遮る機能を有する遮蔽膜67と、特定の波長範囲の可視光を透過する着色層68とを形成する。図11(B)では、遮蔽膜67を形成した後に着色層68を形成する場合を例示しており、遮蔽膜67と着色層68とが、部分的に重なり合っている。遮蔽膜67には、カーボンブラック、二酸化チタンよりも酸化数が小さい酸化チタンなどの黒色顔料を含む有機樹脂を用いることができる。または、遮蔽膜67には、クロム膜を用いる事も可能である。

【0117】

次いで、図11(C)に示すように、遮蔽膜67及び着色層68上に、アクリルなどの有機樹脂を用いて樹脂膜24を形成した後、樹脂膜24上に導電膜25及び配向膜69を順に形成する。

30

【0118】

樹脂膜24は、後に形成される導電膜25の平坦性を高めるために、1μm乃至3μm程度の膜厚を有することが望ましい。本実施の形態では、アクリルを用いて膜厚1μm程度の樹脂膜24を形成する。

【0119】

導電膜25は、第1電極21及び第2電極23と同様に、透光性を有する導電材料を用いることができる。本実施の形態では、酸化珪素を含む酸化インジウムスズを用いて、膜厚220nmの導電膜25を形成する。

【0120】

40

また、配向膜69は、配向膜65と同様の材料を用い、同様の作製方法で形成することができる。

【0121】

上記作製工程により、対向基板を形成することができる。

【0122】

素子基板と対向基板を形成した後は、図8に示すように第1基板10と第2基板20との間に液晶層28を封入すれば、液晶表示装置のパネルを形成することができる。液晶層28を形成するために行われる液晶の注入は、ディスペンサ式(滴下式)を用いても良いし、ディップ式(汲み上げ式)を用いていても良い。

【0123】

50

### 半導体膜について

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified Oxide Semiconductor）は、i型（真性半導体）又はi型に限りなく近い。そのため、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタは、オフ電流が著しく小さく、信頼性が高い。

#### 【0124】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長が $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が $1\text{V}$ から $10\text{V}$ の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}\text{A}$ 以下という特性を得ることができる。この場合、トランジスタのチャネル幅で規格化したオフ電流は、 $100\text{zA}/\mu\text{m}$ 以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、高純度化された酸化物半導体膜を上記トランジスタのチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が $3\text{V}$ の場合に、数十 $\text{yA}/\mu\text{m}$ という、さらに小さいオフ電流が得られることが分かった。従つて、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく小さい。

#### 【0125】

なお、特に断りがない限り、本明細書でオフ電流とは、遮断領域においてトランジスタのソースとドレイン間に流れる電流を意味する。

#### 【0126】

なお、半導体膜として酸化物半導体膜を用いる場合、酸化物半導体としては、少なくともインジウム（In）あるいは亜鉛（Zn）を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有することが好ましい。また、スタビライザーとしてアルミニウム（Al）を有することが好ましい。また、スタビライザーとしてジルコニウム（Zr）を含むことが好ましい。

#### 【0127】

酸化物半導体の中でもIn-Ga-Zn系酸化物、In-Sn-Zn系酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記In-Ga-Zn系酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

#### 【0128】

また、他のスタビライザーとして、ランタノイドである、ラントン（La）、セリウム（Ce）、プラセオジム（Pr）、ネオジム（Nd）、サマリウム（Sm）、ユウロピウム（Eu）、ガドリニウム（Gd）、テルビウム（Tb）、ジスプロシウム（Dy）、ホルミウム（Ho）、エルビウム（Er）、ツリウム（Tm）、イッテルビウム（Yb）、ルテチウム（Lu）のいずれか一種または複数種を含んでいてもよい。

#### 【0129】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物（IGZOとも表記する）、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、

10

20

30

40

50

$\text{Sn-Ga-Zn}$  系酸化物、 $\text{Al-Ga-Zn}$  系酸化物、 $\text{Sn-Al-Zn}$  系酸化物、 $\text{In-Hf-Zn}$  系酸化物、 $\text{In-La-Zn}$  系酸化物、 $\text{In-Pr-Zn}$  系酸化物、 $\text{In-Nd-Zn}$  系酸化物、 $\text{In-Sm-Zn}$  系酸化物、 $\text{In-Eu-Zn}$  系酸化物、 $\text{In-Gd-Zn}$  系酸化物、 $\text{In-Tb-Zn}$  系酸化物、 $\text{In-Dy-Zn}$  系酸化物、 $\text{In-Ho-Zn}$  系酸化物、 $\text{In-Er-Zn}$  系酸化物、 $\text{In-Tm-Zn}$  系酸化物、 $\text{In-Yb-Zn}$  系酸化物、 $\text{In-Lu-Zn}$  系酸化物、 $\text{In-Sn-Ga-Zn}$  系酸化物、 $\text{In-Hf-Ga-Zn}$  系酸化物、 $\text{In-Al-Ga-Zn}$  系酸化物、 $\text{In-Sn-Al-Zn}$  系酸化物、 $\text{In-Sn-Hf-Zn}$  系酸化物、 $\text{In-Hf-Al-Zn}$  系酸化物を用いることができる。

## 【0130】

10

なお、例えば、 $\text{In-Ga-Zn}$  系酸化物とは、 $\text{In}$  と  $\text{Ga}$  と  $\text{Zn}$  を含む酸化物という意味であり、 $\text{In}$  と  $\text{Ga}$  と  $\text{Zn}$  の比率は問わない。また、 $\text{In}$  と  $\text{Ga}$  と  $\text{Zn}$  以外の金属元素を含んでいてもよい。 $\text{In-Ga-Zn}$  系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

## 【0131】

例えば、 $\text{In:Ga:Zn} = 1:1:1$  ( $= 1/3:1/3:1/3$ ) あるいは  $\text{In:Ga:Zn} = 2:2:1$  ( $= 2/5:2/5:1/5$ ) の原子数比の  $\text{In-Ga-Zn}$  系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $\text{In:Sn:Zn} = 1:1:1$  ( $= 1/3:1/3:1/3$ )、 $\text{In:Sn:Zn} = 2:1:3$  ( $= 1/3:1/6:1/2$ ) あるいは  $\text{In:Sn:Zn} = 2:1:5$  ( $= 1/4:1/8:5/8$ ) の原子数比の  $\text{In-Sn-Zn}$  系酸化物やその組成の近傍の酸化物を用いるとよい。

20

## 【0132】

例えば、 $\text{In-Sn-Zn}$  系酸化物では比較的容易に高い移動度が得られる。しかしながら、 $\text{In-Ga-Zn}$  系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

## 【0133】

以下では、酸化物半導体膜の構造について説明する。

## 【0134】

30

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、 $\text{CAAC-OS}$  ( $\text{C Axis Aligned Crystalline Oxide Semiconductor}$ ) 膜などをいう。

## 【0135】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

## 【0136】

40

微結晶酸化物半導体膜は、例えば、 $1\text{ nm}$  以上  $10\text{ nm}$  未満の大きさの微結晶（ナノ結晶ともいう。）を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

## 【0137】

$\text{CAAC-OS}$  膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が  $100\text{ nm}$  未満の立方体内に収まる大きさである。従って、 $\text{CAAC-OS}$  膜に含まれる結晶部は、一辺が  $10\text{ nm}$  未満、 $5\text{ nm}$  未満または  $3\text{ nm}$  未満の立方体内に収まる大きさの場合も含まれる。 $\text{CAAC-OS}$  膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、 $\text{CAAC-OS}$  膜について詳細な説明を行う。

## 【0138】

$\text{CAAC-OS}$  膜を透過型電子顕微鏡 (TEM: Transmission Elect

50

ron Microscope) によって観察すると、結晶部同士の明確な境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

【0139】

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察(断面TEM観察)すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-OS膜の被形成面または上面と平行に配列する。

【0140】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

10

【0141】

一方、CAAC-OS膜を、試料面と概略垂直な方向からTEMによって観察(平面TEM観察)すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

【0142】

断面TEM観察および平面TEM観察より、CAAC-OS膜の結晶部は配向性を有していることがわかる。

20

【0143】

CAAC-OS膜に対し、X線回折(XRD: X-Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaN<sub>0.4</sub>の結晶を有するCAAC-OS膜のout-of-plane法による解析では、回折角(2 $\theta$ )が31°近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub>の結晶の(009)面に帰属されることから、CAAC-OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

【0144】

一方、CAAC-OS膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、2 $\theta$ が56°近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub>の結晶の(110)面に帰属される。InGaN<sub>0.4</sub>の単結晶酸化物半導体膜であれば、2 $\theta$ を56°近傍に固定し、試料面の法線ベクトルを軸(a軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAAC-OS膜の場合は、2 $\theta$ を56°近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

30

【0145】

以上のことから、CAAC-OS膜では、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面TEM観察で確認された層状に配列した金属原子の各層は、結晶のab面に平行な面である。

40

【0146】

なお、結晶部は、CAAC-OS膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAAC-OS膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAAC-OS膜の形状をエッティングなどによって変化させた場合、結晶のc軸がCAAC-OS膜の被形成面または上面の法線ベクトルと平行にならないこともある。

【0147】

また、CAAC-OS膜中の結晶化度が均一でなくてもよい。例えば、CAAC-OS膜の結晶部が、CAAC-OS膜の上面近傍からの結晶成長によって形成される場合、上面

50

近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

【0148】

なお、 $InGaZnO_4$  の結晶を有する C A A C - O S 膜の out - of - plane 法による解析では、 $2\theta$  が  $31^\circ$ 。近傍のピークの他に、 $2\theta$  が  $36^\circ$ 。近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$ 。近傍のピークは、C A A C - O S 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。C A A C - O S 膜は、 $2\theta$  が  $31^\circ$ 。近傍にピークを示し、 $2\theta$  が  $36^\circ$ 。近傍にピークを示さないことが好ましい。

【0149】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

【0150】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

【0151】

C A A C - O S 膜は、例えば、多結晶である金属酸化物ターゲットを用い、スパッタリング法によって成膜する。当該ターゲットにイオンが衝突すると、ターゲットに含まれる結晶領域が a - b 面から劈開し、a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状またはペレット状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、C A A C - O S 膜を成膜することができる。

【0152】

また、C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

【0153】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、処理室内に存在する不純物濃度（水素、水、二酸化炭素、及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が  $-80^\circ$  以下、好ましくは  $-100^\circ$  以下である成膜ガスを用いる。

【0154】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を  $100^\circ$  以上  $740^\circ$  以下、好ましくは  $200^\circ$  以上  $500^\circ$  以下として成膜する。成膜時の基板加熱温度を高めることで、平板状またはペレット状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、平板状またはペレット状のスパッタリング粒子の平らな面が基板に付着する。

【0155】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積 % 以上、好ましくは 100 体積 % とする。

【0156】

ターゲットの一例として、 $In - Ga - Zn$  系酸化物ターゲットについて以下に示す。

【0157】

$InO_x$  粉末、 $GaO_y$  粉末及び $ZnO_z$  粉末を所定の mol 数比で混合し、加圧処理後、 $1000^\circ$  以上  $1500^\circ$  以下の温度で加熱処理をすることで多結晶である  $In - Ga - Zn$  系酸化物ターゲットとする。なお、X、Y 及び Z は任意の正数である。ここで、所定の mol 数比は、例えば、 $InO_x$  粉末、 $GaO_y$  粉末及び $ZnO_z$  粉末が、 $2:2:1$ 、 $8:4:3$ 、 $3:1:1$ 、 $1:1:1$ 、 $4:2:3$  または  $3:1:2$  である。なお、粉末の種類、及びその混合する mol 数比は、作製するターゲットによって適宜変更すればよい。

10

20

30

40

50

## 【0158】

なお、アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちNaは、酸化物半導体膜に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散してNa<sup>+</sup>となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、或いは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフトすることによるノーマリオン化、移動度の低下等の、トランジスタの電気的特性の劣化が起こり、加えて、特性のばらつきも生じる。具体的に、二次イオン質量分析法によるナトリウム(Na)濃度の測定値は、 $5 \times 10^{-1}$   $6 / \text{cm}^3$  以下、好ましくは $1 \times 10^{-1}$   $6 / \text{cm}^3$  以下、更に好ましくは $1 \times 10^{-1}$   $5 / \text{cm}^3$  以下とするとよい。同様に、リチウム(Li)濃度の測定値は、 $5 \times 10^{-1}$   $5 / \text{cm}^3$  以下、好ましくは $1 \times 10^{-1}$   $5 / \text{cm}^3$  以下とするとよい。同様に、カリウム(K)濃度の測定値は、 $5 \times 10^{-1}$   $5 / \text{cm}^3$  以下、好ましくは $1 \times 10^{-1}$   $5 / \text{cm}^3$  以下とするとよい。10

## 【0159】

また、インジウムを含む金属酸化物が用いられている場合に、酸素との結合エネルギーがインジウムよりも大きいシリコンや炭素が、インジウムと酸素の結合を切断し、酸素欠損を形成することがある。そのため、シリコンや炭素が酸化物半導体膜に混入していると、アルカリ金属やアルカリ土類金属の場合と同様に、トランジスタの電気的特性の劣化が起こりやすい。よって、酸化物半導体膜におけるシリコンや炭素の濃度は低いことが望ましい。具体的に、二次イオン質量分析法による炭素(C)濃度の測定値、またはシリコン(Si)濃度の測定値は、 $1 \times 10^{-1}$   $8 / \text{cm}^3$  以下とするとよい。上記構成により、トランジスタの電気的特性の劣化を防ぐことができ、液晶表示装置の信頼性を高めることができる。20

## 【0160】

また、ソース電極及びドレイン電極に用いられる導電性材料によっては、ソース電極及びドレイン電極中の金属が、酸化物半導体膜から酸素を引き抜くことがある。この場合、酸化物半導体膜のうち、ソース電極及びドレイン電極に接する領域が、酸素欠損の形成によりn型化される。30

## 【0161】

n型化された領域は、ソース領域またはドレイン領域として機能するため、酸化物半導体膜とソース電極及びドレイン電極との間ににおけるコンタクト抵抗を下げることができる。よって、n型化された領域が形成されることで、トランジスタの移動度及びオン電流を高めることができ、それにより、トランジスタを用いたスイッチ回路の高速動作を実現することができる。

## 【0162】

なお、ソース電極及びドレイン電極中の金属による酸素の引き抜きは、ソース電極及びドレイン電極をスパッタリング法などにより形成する際に起こりうるし、ソース電極及びドレイン電極を形成した後に行われる加熱処理によっても起こりうる。40

## 【0163】

また、n型化される領域は、酸素と結合し易い導電性材料をソース電極及びドレイン電極に用いることで、より形成されやすくなる。上記導電性材料としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどが挙げられる。

## 【0164】

また、酸化物半導体膜は、単数の金属酸化物膜で構成されているとは限らず、積層された複数の金属酸化物膜で構成されていても良い。例えば、第1乃至第3の金属酸化物膜が順に積層されている半導体膜の場合、第1の金属酸化物膜及び第3の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つを、その構成要素に含み、伝導帯下端のエネルギーが第2の金属酸化物膜よりも0.05eV以上、0.07eV以上、0.1eV以上または0.15eV以上、かつ2eV以下、1eV以下、0.5eV以下また50

は0.4eV以下、真空準位に近い酸化物膜である。さらに、第2の金属酸化物膜は、少なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

【0165】

上記構成の半導体膜をトランジスタが有する場合、ゲート電極に電圧を印加することで、半導体膜に電界が加わると、半導体膜のうち、伝導帯下端のエネルギーが小さい第2の金属酸化物膜にチャネル領域が形成される。即ち、第2の金属酸化物膜とゲート絶縁膜との間に第3の金属酸化物膜が設けられることによって、ゲート絶縁膜と離隔している第2の金属酸化物膜に、チャネル領域を形成することができる。

【0166】

また、第3の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つをその構成要素に含むため、第2の金属酸化物膜と第3の金属酸化物膜の界面では、界面散乱が起こりにくい。従って、当該界面においてキャリアの動きが阻害されにくいため、トランジスタの電界効果移動度が高くなる。

10

【0167】

また、第2の金属酸化物膜と第1の金属酸化物膜の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、トランジスタの閾値電圧が変動してしまう。しかし、第1の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つをその構成要素に含むため、第2の金属酸化物膜と第1の金属酸化物膜の界面には、界面準位が形成されにくい。よって、上記構成により、トランジスタの閾値電圧等の電気的特性のばらつきを、低減することができる。

20

【0168】

また、金属酸化物膜間に不純物が存在することによって、各膜の界面にキャリアの流れを阻害する界面準位が形成されることがないよう、複数の金属酸化物膜を積層させることが望ましい。積層された金属酸化物膜の膜間に不純物が存在していると、金属酸化物膜間ににおける伝導帯下端のエネルギーの連続性が失われ、界面近傍において、キャリアがトラップされるか、あるいは再結合により消滅してしまうからである。膜間ににおける不純物を低減させることで、主成分である一の金属を少なくとも共に有する複数の金属酸化物膜を、単に積層させるよりも、連続接合（ここでは特に伝導帯下端のエネルギーが各膜の間で連続的に変化するU字型の井戸構造を有している状態）が形成されやすくなる。

30

【0169】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa乃至 $1 \times 10^{-4}$  Pa程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

【0170】

高純度の真性な酸化物半導体を得るためにには、各チャンバー内を高真空排気するのみならず、スパッタリングに用いるガスの高純度化も重要である。上記ガスとして用いる酸素ガスやアルゴンガスの露点を、-40以下、好ましくは-80以下、より好ましくは-100以下とし、使用するガスの高純度化を図ることで、酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

40

【0171】

例えば、第1の金属酸化物膜または第3の金属酸化物膜は、アルミニウム、シリコン、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、スズ、ランタン、セリウムまたはハフニウムを、第2の金属酸化物膜よりも高い原子数比で含む酸化物膜であればよい。具体的に、第1の金属酸化物膜または第3の金属酸化物膜として、第2の金属酸化物膜よりも上述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物膜を用いると良い。前述の元素は酸素と強く結合するため、酸

50

素欠損が酸化物膜に生じることを抑制する機能を有する。よって、上記構成により、第1の金属酸化物膜または第3の金属酸化物膜を、第2の金属酸化物膜よりも酸素欠損が生じにくい酸化物膜にすることができる。

#### 【0172】

具体的に、第2の金属酸化物膜と、第1の金属酸化物膜または第3の金属酸化物膜とが、共にIn-M-Zn系酸化物膜である場合、第1の金属酸化物膜または第3の金属酸化物膜の原子数比を $In : M : Zn = x_1 : y_1 : z_1$ 、第2の金属酸化物膜の原子数比を $In : M : Zn = x_2 : y_2 : z_2$ とすると、 $y_1 / x_1$ が $y_2 / x_2$ よりも大きくなるように、その原子数比を設定すれば良い。なお、元素MはInよりも酸素との結合力が強い金属元素であり、例えばAl、Ti、Ga、Y、Zr、Sn、La、Ce、NdまたはHf等が挙げられる。好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも1.5倍以上大きくなるように、その原子数比を設定すれば良い。さらに好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも2倍以上大きくなるように、その原子数比を設定すれば良い。より好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも3倍以上大きくなるように、その原子数比を設定すれば良い。さらに、第2の金属酸化物膜において、 $y_2$ が $x_2$ 以上であると、トランジスタに安定した電気的特性を付与できるため好ましい。ただし、 $y_2$ が $x_2$ の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$ は、 $x_2$ の3倍未満であると好ましい。

10

#### 【0173】

なお、第1の金属酸化物膜及び第3の金属酸化物膜の厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、第2の金属酸化物膜の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下であり、さらに好ましくは3nm以上50nm以下である。

20

#### 【0174】

3層構造の半導体膜において、第1の金属酸化物膜乃至第3の金属酸化物膜は、非晶質または結晶質の両方の形態を取りうる。ただし、チャネル領域が形成される第2の金属酸化物膜が結晶質であることにより、トランジスタに安定した電気的特性を付与することができるため、第2の金属酸化物膜は結晶質であることが好ましい。

#### 【0175】

なお、チャネル形成領域とは、トランジスタの半導体膜のうち、ゲート電極と重なり、かつソース電極とドレイン電極に挟まれる領域を意味する。また、チャネル領域とは、チャネル形成領域において、電流が主として流れる領域をいう。

30

#### 【0176】

例えば、第1の金属酸化物膜及び第3の金属酸化物膜として、スパッタリング法により形成したIn-Ga-Zn系酸化物膜を用いる場合、第1の金属酸化物膜及び第3の金属酸化物膜の成膜には、In-Ga-Zn系酸化物( $In : Ga : Zn = 1 : 3 : 2$  [原子数比])であるターゲットを用いることができる。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力0.4Paとし、基板温度を200とし、DC電力0.5kWとすればよい。

#### 【0177】

40

また、第2の金属酸化物膜をCAC-OS膜とする場合、第2の金属酸化物膜の成膜には、In-Ga-Zn系酸化物( $In : Ga : Zn = 1 : 1 : 1$  [原子数比])であり、多結晶のIn-Ga-Zn系酸化物を含むターゲットを用いることが好ましい。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力を0.4Paとし、基板の温度300とし、DC電力0.5kWとすることができる。

#### 【0178】

なお、トランジスタは、半導体膜の端部が傾斜している構造を有していても良いし、半導体膜の端部が丸みを帯びる構造を有していても良い。

#### 【0179】

50

また、複数の積層された金属酸化物膜を有する半導体膜をトランジスタに用いる場合においても、ソース電極及びドレイン電極に接する領域が、n型化されていても良い。上記構成により、トランジスタの移動度及びオン電流を高め、トランジスタを用いた液晶表示装置の高速動作を実現することができる。さらに、複数の積層された金属酸化物膜を有する半導体膜をトランジスタに用いる場合、n型化される領域は、チャネル領域となる第2の金属酸化物膜にまで達していることが、トランジスタの移動度及びオン電流を高め、液晶表示装置のさらなる高速動作を実現する上で、より好ましい。

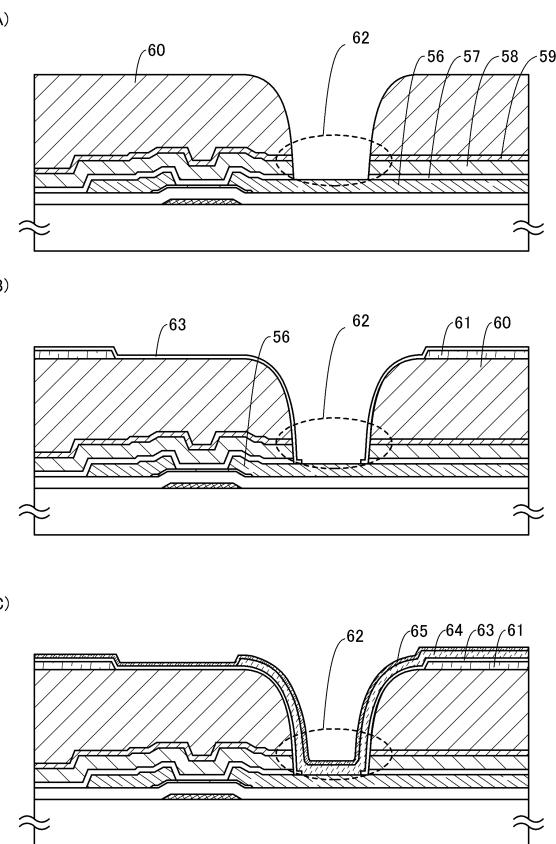

## 【0180】

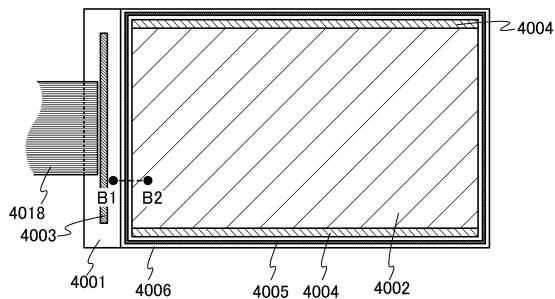

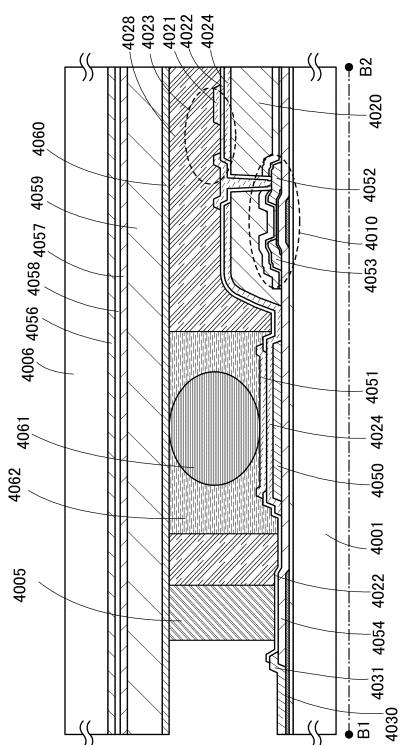

## 液晶表示装置の上面図と断面図

本発明の一態様に係る液晶表示装置の外観について、図12を用いて説明する。図12は、第1基板4001と第2基板4006とを封止材4005によって接着させた液晶表示装置の上面図である。また、図13は、図12の破線B1-B2における断面図に相当する。なお、図12では、FFSモードの液晶表示装置を例示している。

10

## 【0181】

第1基板4001上に設けられた画素部4002と、一対の駆動回路4004とを囲むように、封止材4005が設けられている。また、画素部4002、駆動回路4004の上に第2基板4006が設けられている。よって、画素部4002と、駆動回路4004とは、第1基板4001と封止材4005と第2基板4006とによって封止されている。

## 【0182】

また、第1基板4001上の封止材4005によって囲まれている領域とは異なる領域に、駆動回路4003が実装されている。

20

## 【0183】

また、第1基板4001上に設けられた画素部4002、駆動回路4004は、トランジスタを複数有している。図13では、画素部4002に含まれるトランジスタ4010を例示している。

## 【0184】

画素部4002及び駆動回路4004において、トランジスタ4010上には、樹脂を用いた絶縁膜4020が設けられている。そして、絶縁膜4020上には、液晶素子4023の画素電極4021と、共通電極4024とが、間に絶縁膜4022を挟んで設けられている。

30

## 【0185】

なお、図13では、共通電極4024上に画素電極4021が設けられている場合を例示しているが、画素電極4021上に共通電極4024が設けられていても良い。

## 【0186】

また、図13に示すように、本発明の一態様では、絶縁膜4020は、パネルの端部において除去されている。そして、絶縁膜4020の除去されている領域において、導電膜4050が形成されており、共通電極4024が導電膜4050と接している。また、絶縁膜4022に設けられた開口部において共通電極4024と接するように、導電膜4051が設けられている。

## 【0187】

40

導電膜4050と、トランジスタ4010のソースまたはドレインとして機能する導電膜4052及び導電膜4053とは、一の導電膜をエッチングすることで形成することができる。また、画素電極4021と、導電膜4051とは、一の導電膜をエッチングすることで形成することができる。

## 【0188】

また、第2基板4006には、位置情報の取得を行うための第1電極4056及び第2電極4057が、絶縁膜4058を間に挟んで重なり合っている。第1電極4056及び第2電極4057上には樹脂膜4059が設けられており、樹脂膜4059上には、導電膜4060が設けられている。

## 【0189】

50

そして、導電膜 4060 は、導電膜 4051 と、樹脂膜 4062 中に分散された導電性を有する導電性粒子 4061 を介して電気的に接続されている。すなわち、共通電極 4024 と導電膜 4060 とは、パネルの端部において、導電性粒子 4061 を介して電気的に接続されていることとなる。樹脂膜 4062 には、熱硬化性樹脂、または紫外線硬化樹脂を用いることができる。また、導電性粒子 4061 には、例えば球状の有機樹脂を Au や Ni、Co 等の薄膜状の金属で被覆した粒子を用いることができる。

【0190】

なお、図 13 では配向膜を図示しなかったが、配向膜を絶縁膜 4022 及び共通電極 4024 上と、導電膜 4060 上とに設ける場合、導電膜 4060 と、導電性粒子 4061 と、導電膜 4051 とを電気的に接続するために、導電膜 4060 と重なる部分において配向膜を一部除去し、導電膜 4051 と重なる部分において配向膜を一部除去すれば良い。

10

【0191】

また、絶縁膜 4022 は、パネルの端部において、ゲート絶縁膜 4054 と接している。絶縁膜 4022 及びゲート絶縁膜 4054 の、水、水素などのプロッキング効果が高い場合、パネルの端部において絶縁膜 4022 及びゲート絶縁膜 4054 が接することで、パネルの端部から、または封止材 4005 から、水、水素などがトランジスタ 4010 の有する半導体膜に侵入するのを、防ぐことができる。

【0192】

また、第 1 基板 4001 と、第 2 基板 4006との間には、液晶層 4028 が設けられている。液晶素子 4023 は、画素電極 4021、共通電極 4024、及び液晶層 4028 を有する。

20

【0193】

液晶素子 4023 では、画素電極 4021 と共通電極 4024 の間に与えられる電圧の値に従って、液晶層 4028 に含まれる液晶分子の配向が変化し、透過率が変化する。よって、液晶素子 4023 は、画素電極 4021 に与えられる画像信号の電位によって、その透過率が制御されることで、階調を表示することができる。

【0194】

なお、本発明の一態様に係る液晶表示装置では、カラーフィルタを用いることでカラーの画像を表示しても良いし、異なる色相の光を発する複数の光源を順次点灯させることで、カラーの画像を表示しても良い。

30

【0195】

また、駆動回路 4003 からの画像信号や、FPC 4018 からの各種制御信号及び電位は、引き回し配線 4030 及び 4031 を介して、駆動回路 4004 または画素部 4002 に与えられる。

【0196】

液晶表示装置を用いた電子機器の構成例

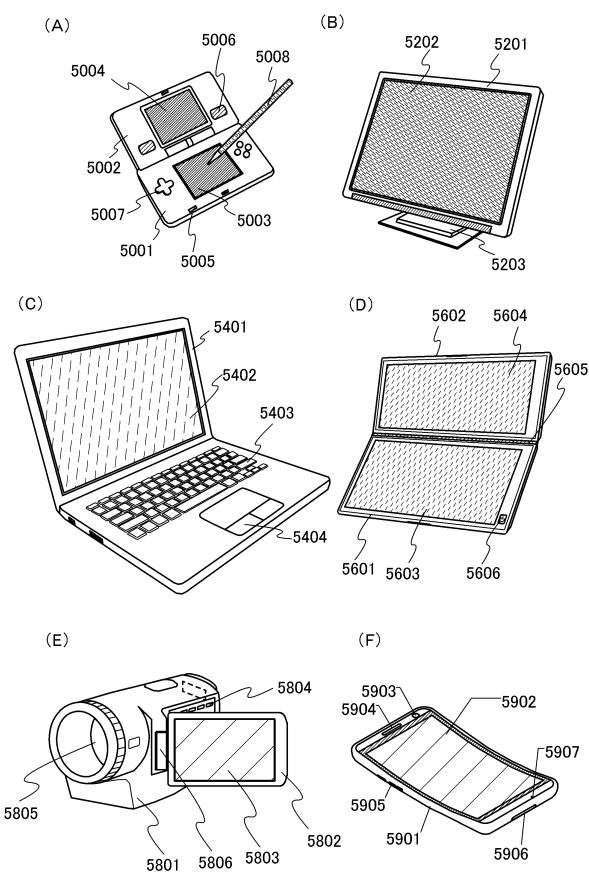

本発明の一態様に係る液晶表示装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的には DVD : Digital Versatile Disc 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る液晶表示装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラなどのカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図 14 に示す。

40

【0197】

図 14 (A) は携帯型ゲーム機であり、筐体 5001、筐体 5002、表示部 5003、表示部 5004、マイクロホン 5005、スピーカー 5006、操作キー 5007、スタイルス 5008 等を有する。表示部 5003 または表示部 5004 に、本発明の一態様に

50

係る液晶表示装置を用いることができる。なお、図14(A)に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

【0198】

図14(B)は表示機器であり、筐体5201、表示部5202、支持台5203等を有する。表示部5202に、本発明の一態様に係る液晶表示装置を用いることができる。なお、表示機器には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示機器が含まれる。

【0199】

図14(C)はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。表示部5402に、本発明の一態様に係る液晶表示装置を用いることができる。

【0200】

図14(D)は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602の間の角度は、接続部5605により変更が可能となっている。第1表示部5603における映像を、接続部5605における第1筐体5601と第2筐体5602の間の角度に従って、切り替える構成としても良い。第1表示部5603または第2表示部5604に、本発明の一態様に係る液晶表示装置を用いることができる。

【0201】

図14(E)はビデオカメラであり、第1筐体5801、第2筐体5802、表示部5803、操作キー5804、レンズ5805、接続部5806等を有する。操作キー5804及びレンズ5805は第1筐体5801に設けられており、表示部5803は第2筐体5802に設けられている。そして、第1筐体5801と第2筐体5802とは、接続部5806により接続されており、第1筐体5801と第2筐体5802の間の角度は、接続部5806により変更が可能となっている。表示部5803における映像の切り替えを、接続部5806における第1筐体5801と第2筐体5802の間の角度に従って行う構成としても良い。表示部5803に、本発明の一態様に係る液晶表示装置を用いることができる。

【0202】

図14(F)は携帯電話であり、筐体5901に、表示部5902、マイク5907、スピーカー5904、カメラ5903、外部接続部5906、操作用のボタン5905が設けられている。携帯電話が有する回路に、本発明の一態様に係る液晶表示装置を用いることができる。また、本発明の一態様に係る液晶表示装置を、可携性を有する基板に形成した場合、図14(F)に示すような曲面を有する表示部5902に当該液晶表示装置を適用することが可能である。

【符号の説明】

【0203】

- 10 第1基板

- 11 素子層

- 12 電極

- 13 絶縁膜

- 14 電極

- 15 トランジスタ

- 16 画素

- 20 第2基板

- 21 電極

10

20

30

40

50

|         |        |    |

|---------|--------|----|

| 2 1 a   | 導電膜    |    |

| 2 1 b   | 導電膜    |    |

| 2 1 c   | 導電膜    |    |

| 2 1 d   | 導電膜    |    |

| 2 2     | 絶縁膜    |    |

| 2 3     | 電極     |    |

| 2 4     | 樹脂膜    |    |

| 2 5     | 導電膜    |    |

| 2 6     | 容量     |    |

| 2 7     | 導電体    | 10 |

| 2 8     | 液晶層    |    |

| 3 0     | 画素部    |    |

| 3 1     | 画素     |    |

| 3 2     | 駆動回路   |    |

| 3 3     | 駆動回路   |    |

| 3 4     | 液晶素子   |    |

| 3 5     | トランジスタ |    |

| 3 6     | 容量素子   |    |

| 3 8     | パネル    |    |

| 4 0     | 液晶表示装置 | 20 |

| 4 1     | コントローラ |    |

| 4 3     | C P U  |    |

| 4 4     | 画像処理回路 |    |

| 4 5     | 画像メモリ  |    |

| 4 6     | 画像データ  |    |

| 5 1     | 導電膜    |    |

| 5 3     | 絶縁膜    |    |

| 5 4     | 半導体膜   |    |

| 5 5     | 導電膜    |    |

| 5 6     | 導電膜    | 30 |

| 5 7     | 酸化物膜   |    |

| 5 8     | 絶縁膜    |    |

| 5 9     | 絶縁膜    |    |

| 6 0     | 有機樹脂膜  |    |

| 6 1     | 導電膜    |    |

| 6 2     | 開口部    |    |

| 6 3     | 絶縁膜    |    |

| 6 4     | 導電膜    |    |

| 6 5     | 配向膜    |    |

| 6 6     | 絶縁膜    | 40 |

| 6 7     | 遮蔽膜    |    |

| 6 8     | 着色層    |    |

| 6 9     | 配向膜    |    |

| 4 0 0 1 | 第1基板   |    |

| 4 0 0 2 | 画素部    |    |

| 4 0 0 3 | 駆動回路   |    |

| 4 0 0 4 | 駆動回路   |    |

| 4 0 0 5 | 封止材    |    |

| 4 0 0 6 | 第2基板   |    |

| 4 0 1 0 | トランジスタ | 50 |

|         |             |    |

|---------|-------------|----|

| 4 0 1 8 | F P C       |    |

| 4 0 2 0 | 絶縁膜         |    |

| 4 0 2 1 | 画素電極        |    |

| 4 0 2 2 | 絶縁膜         |    |

| 4 0 2 3 | 液晶素子        |    |

| 4 0 2 4 | 共通電極        |    |

| 4 0 2 8 | 液晶層         |    |

| 4 0 3 0 | 配線          |    |

| 4 0 5 0 | 導電膜         | 10 |

| 4 0 5 1 | 導電膜         |    |

| 4 0 5 2 | 導電膜         |    |

| 4 0 5 3 | 導電膜         |    |

| 4 0 5 4 | ゲート絶縁膜      |    |

| 4 0 5 6 | 電極          |    |

| 4 0 5 7 | 電極          |    |

| 4 0 5 8 | 絶縁膜         |    |

| 4 0 5 9 | 樹脂膜         |    |

| 4 0 6 0 | 導電膜         |    |

| 4 0 6 1 | 導電性粒子       |    |

| 4 0 6 2 | 樹脂膜         | 20 |

| 5 0 0 1 | 筐体          |    |

| 5 0 0 2 | 筐体          |    |

| 5 0 0 3 | 表示部         |    |

| 5 0 0 4 | 表示部         |    |

| 5 0 0 5 | マイクロホン      |    |

| 5 0 0 6 | スピーカー       |    |

| 5 0 0 7 | 操作キー        |    |

| 5 0 0 8 | スタイラス       |    |

| 5 2 0 1 | 筐体          |    |

| 5 2 0 2 | 表示部         | 30 |

| 5 2 0 3 | 支持台         |    |

| 5 4 0 1 | 筐体          |    |

| 5 4 0 2 | 表示部         |    |

| 5 4 0 3 | キーボード       |    |

| 5 4 0 4 | ポインティングデバイス |    |

| 5 6 0 1 | 筐体          |    |

| 5 6 0 2 | 筐体          |    |

| 5 6 0 3 | 表示部         |    |

| 5 6 0 4 | 表示部         |    |

| 5 6 0 5 | 接続部         | 40 |

| 5 6 0 6 | 操作キー        |    |

| 5 8 0 1 | 筐体          |    |

| 5 8 0 2 | 筐体          |    |

| 5 8 0 3 | 表示部         |    |

| 5 8 0 4 | 操作キー        |    |

| 5 8 0 5 | レンズ         |    |

| 5 8 0 6 | 接続部         |    |

| 5 9 0 1 | 筐体          |    |

| 5 9 0 2 | 表示部         |    |

| 5 9 0 3 | カメラ         | 50 |

5 9 0 4      スピーカー

5 9 0 5      ボタン

5 9 0 6      外部接続部

5 9 0 7      マイク

【図1】

【図2】

【図3】

(A)

(B)

【図4】

【図5】

(A)

(B)

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1 】

【図12】

(C)

### 【図13】

【 図 1 4 】

---

フロントページの続き

(72)発明者 黒崎 大輔

栃木県栃木市都賀町升塚161-2 アドバンスト フィルム ディバイス インク株式会社内

(72)発明者 大野 正勝

栃木県栃木市都賀町升塚161-2 アドバンスト フィルム ディバイス インク株式会社内

審査官 鈴木 俊光

(56)参考文献 登録実用新案第3154829(JP, U)

特開2012-113090(JP, A)

特開2010-191287(JP, A)

特開2008-185785(JP, A)

特表2009-540374(JP, A)

特開2012-220670(JP, A)

特開2011-248356(JP, A)

特開2010-175940(JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1343

G02F 1/1333

G02F 1/1368

G06F 3/041

G06F 3/044