| DOMANDA DI INVENZIONE NUMERO | 102021000030482 |

|------------------------------|-----------------|

| Data Deposito                | 01/12/2021      |

| Data Pubblicazione           | 01/06/2023      |

# Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 01     | L           | 21     | 66          |

## Titolo

RILEVATORE DI CREPE PER PIASTRINE A SEMICONDUTTORE

#### DESCRIZIONE

del brevetto per invenzione industriale dal titolo: "RILEVATORE DI CREPE PER PIASTRINE A SEMICONDUTTORE" di 1) STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI 2

20864 AGRATE BRIANZA (MB)

di 2) STMICROELECTRONICS INTERNATIONAL N.V.

di nazionalità olandese

agente attraverso la sede centrale e filiale svizzera situata a: CHEMIN DU CHAMP-DES-FILLES 39

1228 PLAN-LES-OUATES GENEVA (SVIZZERA)

Inventori: GIACOMINI Mauro, DISEGNI Fabio Enrico Carlo,

NARWAL Rajesh, SAINI Pravesh Kumar, HARESHBHAI NIRANJANI

Mayankkumar

\* \* \*

La presente invenzione riguarda un gruppo per rilevare un difetto strutturale in una piastrina a semiconduttore.

Il processo di singolazione di fetta (wafer) per piastrine è una fase di produzione sensibile (nello specifico per tecnologie LowK e ultra-LowK). Per rendere sicuro questo processo, è possibile rilevare cedimenti correlati alla scheggiatura e alle crepe nell'anello di tenuta delle piastrine (durante la fase di produzione di "Back-end-Of-Line", BEOL (estremità posteriore di linea)), utilizzando un

cosiddetto rilevatore di crepe.

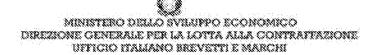

Facendo riferimento alla figura 1, una piastrina 10 è mostrata in una vista in pianta dall'alto e include un sensore, o rilevatore, di crepe 1. Il sensore di crepe 1 è, in una forma di realizzazione esemplificativa della tecnica nota, formato da diversi elementi:

- una linea conduttiva 2 (avente la propria resistenza), disposta in un'area di anello di tenuta 4 della piastrina 10 o tra l'anello di tenuta 4 e una linea di taglio 6;

- una cella di rilevatore 8, disposta in un anello I/O7 della piastrina 10; e

- una logica di test 9, incorporata in una porzione di nucleo 5 della piastrina 10, configurata per testare il sensore resistivo 1 utilizzando la cella di rilevatore 8.

La linea conduttiva 2 è sostanzialmente una striscia continua di materiale conduttivo, avente una certa resistenza, che si estende tra due nodi elettrici E1, E2. La linea conduttiva 2 può essere formata da una o due sottolinee; nel caso di due sotto-linee, una sotto-linea è posta tra l'area di anello di tenuta 4 e l'anello I/O 7 ed è anche nota come "sensore interno" e l'altra sotto-linea è posta all'interno dell'area di anello di tenuta 4 ed è anche nota come "sensore esterno". Ciascuna sotto-linea è realizzata come una catena passante (si veda la figura 2). Questa soluzione con due sotto-linee, o sotto-sensori, permette di

rilevare, oltre alle crepe, anche difetti di delaminazione. Considerando il sensore esterno, strisce a N pozzetti possono essere inserite nei terminali di sensori in modo da non "interrompere" la continuità del metallo dell'area di anello di tenuta 4.

Misurare la continuità elettrica del sensore 1 durante EWS ("Electrical Wafer Sorting" (smistamento di fetta elettrica)) e FT ("Final Test" (test finale)) attraverso la cella di rilevatore 8 consente di rilevare, e scartare, le porzioni dell'anello di tenuta aventi crepe. L'influenza di un bin specifico e SBL su questo test consentirà un monitoraggio corretto del tasso di difetto e di intraprendere azioni adatte in caso di necessità.

L'uso del sensore 1 migliora la robustezza del prodotto di chip, consente il rilevamento di crepe nella BEOL al "tempo zero", che impedisce la distribuzione di parti deboli che diventano parti guaste nell'applicazione cliente (quando i vincoli termomeccanici o di umidità svolgono un ruolo significativo). L'uso del sensore 1 ha un impatto trascurabile sul tempo di test (richiede di testare un semplice resistore) e non introduce disturbi di funzionalità per i prodotti RF.

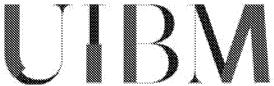

La figura 2, come anticipato, mostra una vista in sezione trasversale di una forma di realizzazione di (una porzione di) un sensore di crepe 1 secondo la tecnica nota.

Il sensore di crepe 1 della figura 2 può essere utilizzato per piastrine con una struttura di interconnessione di più di due strati di metallo. I segmenti conduttivi di substrato 11 sono disposti in un substrato 12. Una prima porzione del segmento conduttivo di substrato 11 è collegata ad un primo segmento conduttivo 14 nel livello di metallizzazione M1. Una seconda porzione del segmento conduttivo di substrato 11 è collegata ad un secondo segmento conduttivo 15 nel livello di metallizzazione M1. Il primo segmento conduttivo 14 è collegato ad una pluralità di ulteriori segmenti conduttivi 16 nei livelli di metallizzazione superiori attraverso una pluralità di collegamenti interstrato. Analogamente, secondo segmento conduttivo 15 è collegato ad una pluralità di ulteriori segmenti conduttivi 18 nei livelli di metallizzazione superiori attraverso una pluralità di rispettivi collegamenti interstrato.

I collegamenti interstrato possono comprendere contatti e/o plug/vie.

La struttura delle figure 1 e 2 può essere utilizzata per rilevare crepe che possono formarsi quando le piastrine 10 vengono separate (singolate) dalla fetta. Come detto, il rilevatore di crepe è un sensore resistivo costituito da un filo di metallo con due nodi elettrici. Questo filo di metallo è posto attorno alla piastrina vicino all'anello di tenuta. Misurare la continuità di questo filo consente di

rilevare crepe.

Per testare la piastrina 10 per le crepe viene applicata una tensione attraverso i nodi elettrici E1, E2. Una corrente scorre durante l'applicazione della tensione verso i due nodi E1, E2. Se non vi è nessuna (o quasi nessuna) caduta di tensione sulla linea resistiva 2, il sensore è intatto e non si crea o si forma una crepa. Se vi è una qualche caduta di tensione sulla linea resistiva 2, il sensore può essere rotto parzialmente e, se vi è una caduta di tensione completa o quasi completa sulla linea resistiva 2, il sensore può essere tagliato o gravemente danneggiato.

A questa soluzione si applicano alcune limitazioni. In particolare, può essere presente una grande dispersione di resistenza di sensore, per via di variazioni di processo, e pertanto è difficile impostare limiti affidabili; inoltre, il test richiede molto tempo per essere completato (all'incirca 10 ms); per di più, la misurazione richiede una disposizione fuori dal chip.

Come soluzione alternativa, può anche essere eseguito un test digitale.

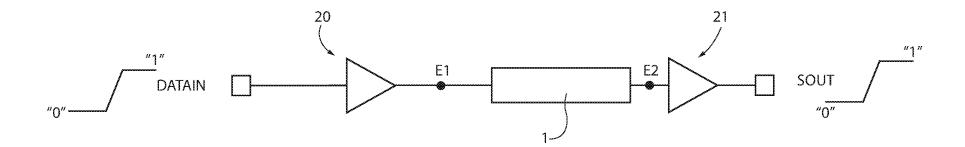

La figura 3 mostra una progettazione di circuito per eseguire il test digitale.

In questo esempio, un segnale digitale DATAIN è impostato come ingresso al nodo elettrico E1 del sensore di crepe 1. Il segnale DATAIN va dal valore digitale "0" al

valore digitale "1". Uno stadio di buffer di ingresso 20 è fornito per ricevere il segnale DATAIN, raddrizzare il segnale DATAIN e pilotare correttamente il sensore di crepe 1 attraverso il nodo E1. Uno stadio di buffer di uscita 21 è fornito accoppiato al nodo elettrico di uscita E2 del sensore di crepe 1, per ricevere il segnale che si propaga attraverso il sensore di crepe 1, raddrizzare il segnale e fornire all'uscita un segnale digitale SOUT.

In una possibile implementazione, il segnale DATAIN è generato dalla logica di test 9 e lo stadio di buffer di ingresso 20 fa parte della cella di rilevatore 8, analogamente, il segnale SOUT è ricevuto dalla logica di test 9 e lo stadio di buffer di uscita 21 fa parte della cella di rilevatore 8.

Nel caso non sia presente alcuna crepa (ovvero, la linea resistiva 2 non è interrotta da una crepa), il segnale SOUT corrisponde al segnale DATAIN ed è ricevuto con un certo ritardo temporale. Al contrario, in caso di interruzioni della linea resistiva 2, non è ricevuto alcun segnale SOUT o il segnale SOUT differisce considerevolmente dal segnale DATAIN. Viene quindi rilevata una crepa o altro problema lungo la linea resistiva 2.

Alcune limitazioni emergono dall'uso della soluzione della figura 3.

In particolare, gli utenti sperimentano una grande

dispersione della costante RC del sensore (per via di variazioni di processo di fabbricazione), pertanto sarebbe difficile impostare limiti affidabili; inoltre, è difficile misurare il tempo di transizione esatto (dato che dovrebbe essere fissata una finestra di campionamento). Inoltre, questa misurazione richiede una disposizione fuori dal chip.

L'obiettivo della presente invenzione è superare i problemi illustrati in precedenza.

Secondo la presente invenzione, è fornito un gruppo per rilevare un difetto strutturale in una piastrina a semiconduttore, come definito nella rivendicazione 1.

Per una migliore comprensione della presente invenzione, le sue forme di realizzazione preferite vengono ora descritte, puramente a titolo di esempio non limitativo e in riferimento ai disegni allegati, in cui:

- la figura 1 è una vista dall'alto di una piastrina a semiconduttore includente un rilevatore di crepe secondo la tecnica nota;

- la figura 2 è una vista in sezione di un rilevatore di crepe secondo la tecnica nota, da cui si può apprezzare che il rilevatore di crepe è formato in una pluralità di strati e vie di metallo;

- la figura 3 mostra un circuito per effettuare misure digitali dal rilevatore di crepe, secondo la tecnica nota;

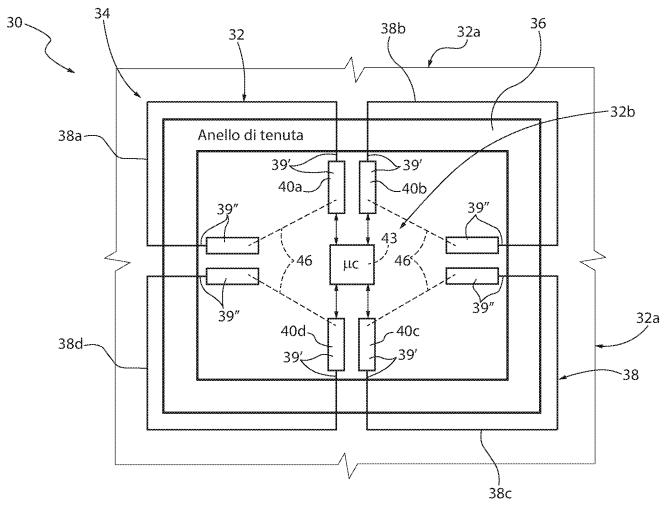

- la figura 4 è una vista dall'alto di una piastrina a

semiconduttore includente un rilevatore di crepe secondo una forma di realizzazione della presente invenzione;

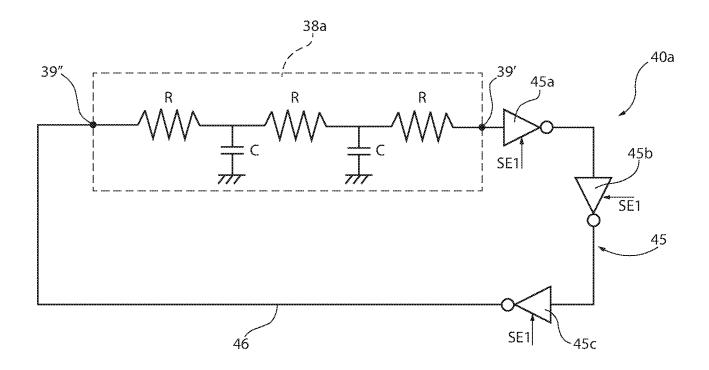

- la figura 5 mostra schematicamente una rappresentazione elettrica di una porzione di un rilevatore di crepe dotato di un anello oscillante monodirezionale, secondo una forma di realizzazione della presente invenzione;

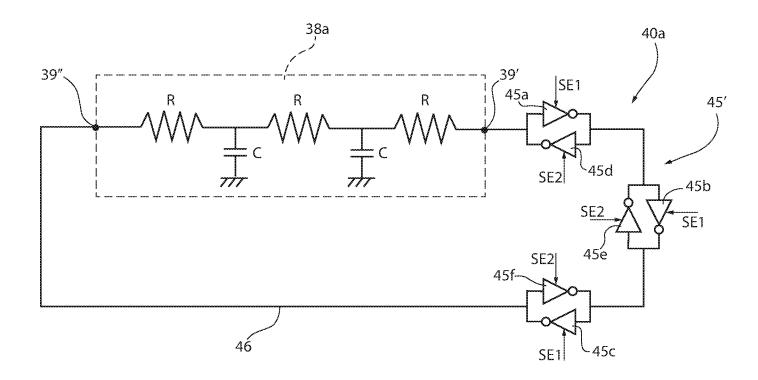

- la figura 6 mostra schematicamente una rappresentazione elettrica di una porzione di un rilevatore di crepe dotato di un anello oscillante bidirezionale, secondo un'ulteriore forma di realizzazione della presente invenzione;

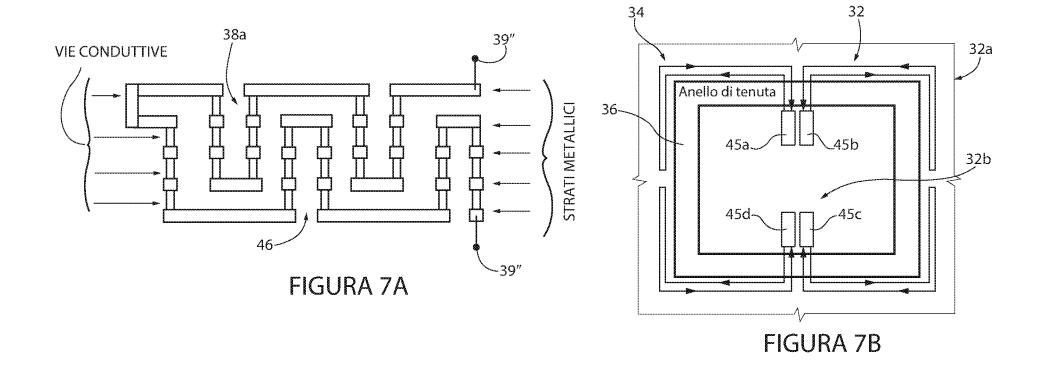

- la figura 7A è una vista in sezione schematica di una porzione del rilevatore di crepe, secondo una forma di realizzazione della presente invenzione;

- la figura 7B è una vista dall'alto della piastrina a semiconduttore includente il rilevatore di crepe secondo la forma di realizzazione della figura 7A;

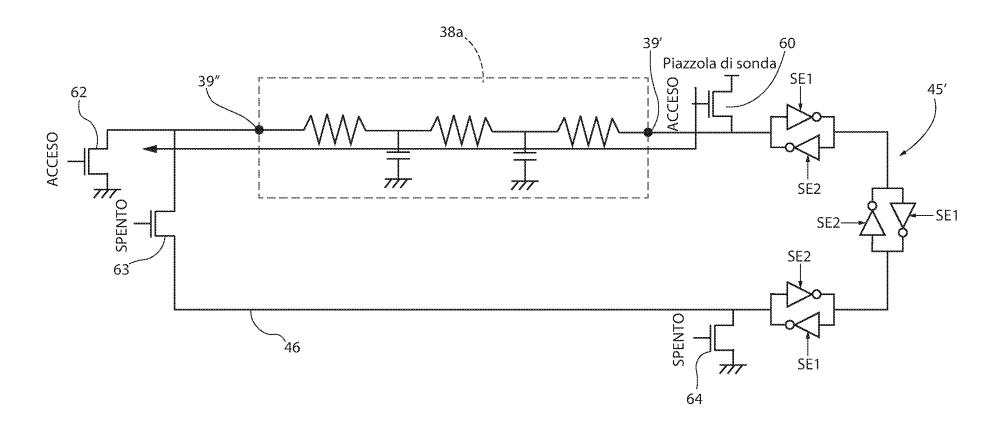

- la figura 8 mostra una rappresentazione elettrica di una porzione di un rilevatore di crepe per effettuare una misurazione resistiva, secondo una forma di realizzazione della presente invenzione;

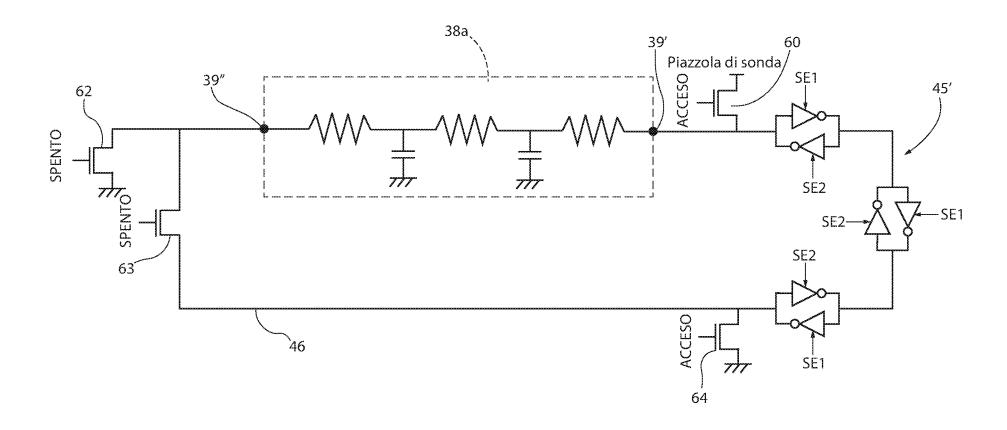

- la figura 9 mostra una rappresentazione elettrica di una porzione di un rilevatore di crepe per eseguire un test di dispersione, secondo una forma di realizzazione della

## presente invenzione;

- la figura 10 è una vista in sezione corrispondente alla vista della figura 7A, in cui è presente un difetto che causa dispersione di corrente, che può essere rilevato dal sensore di crepe della figura 9; e

- la figura 11 mostra una rappresentazione elettrica di una porzione di un rilevatore di crepe per effettuare una misurazione resistiva, secondo un'ulteriore forma di realizzazione della presente invenzione.

La figura 4 mostra una piastrina 30 che alloggia un sensore di rilevamento di crepe 32 (indicato nel seguito anche come "sensore di crepe"), secondo una forma di realizzazione della presente invenzione.

In modo non mostrato nei disegni, la piastrina 30 deriva da una fetta a semiconduttore comprendente una pluralità di piastrine 30 formate attraverso una superficie superiore della fetta, dopo che le piastrine a semiconduttore sono state tagliate (ovvero tagliate in singole piastrine da una fetta). La piastrina 30 è tipicamente di forma quadrata o rettangolare. La piastrina 30 comprende un circuito integrato (non mostrato in dettaglio).

Dopo la fabbricazione di una pluralità di piastrine sulla fetta, la pluralità di piastrine vengono separate l'una dall'altra lungo linee di taglio (la cosiddetta fase di "singolazione"). Le linee di taglio sono situate in

corrispondenza del perimetro della piastrina 30, per cui al termine del processo di fabbricazione è possibile utilizzare una sega per staccare una piastrina dalle piastrine adiacenti lungo le linee di taglio. La singolazione delle piastrine può anche essere eseguita, per esempio, mediante taglio laser o incisione laser seguito da taglio mediante sega.

Il sensore di crepe 32 è formato in almeno uno strato di materiale conduttivo (strato di metallo) della piastrina 30, più preferibilmente in una pluralità di strati di metallo sovrapposti separati l'uno dall'altro da strati dielettrici o isolanti e collegati per mezzo di vie passanti attraverso tali strati dielettrici o isolanti. Il sensore di crepe 32 è formato, in particolare, almeno in parte lungo una regione perimetrale 34 della piastrina 30, come mostrato nella figura 4. In dettaglio, il sensore di crepe 32 è formato da un bordo 32a della piastrina 32 e una regione interna 32b della piastrina 32, in cui la regione interna 32b alloggia il circuito integrato. In una forma di realizzazione, una regione di tenuta, o anello di tenuta, 36 è anche presente tra il bordo 32a e la regione interna 32b. Un anello di tenuta è, per esempio, una struttura a più strati composta da strati conduttivi e isolanti che si alternano. Attraverso ciascuno degli strati isolanti passano molteplici vie che forniscono percorsi elettrici tra strati di adiacenti. Lo strato più basso di metallo nella struttura di

tenuta fa contatto elettrico con il substrato, che può essere di tipo p o di tipo n. L'anello di tenuta 36 può essere omesso.

Il sensore di crepe 32 comprende una struttura resistiva 38 di materiale conduttivo (indicata nel seguito anche come "struttura conduttiva") che si estende, o è integrata, in prossimità del bordo 32a, almeno in parte tra (in una vista dall'alto) l'anello di tenuta 36 e il bordo 32a. La struttura conduttiva 38 comprende una pluralità di segmenti resistivi da 38a a 38d di materiale conduttivo (nel seguito, denominati anche "segmenti conduttivi"), formati in uno o più strati di metallo della piastrina 30; in altri termini, la struttura conduttiva è formata in una pluralità di strati di metallo in un sistema di interconnessione a più livelli, in cui le vie vengono utilizzate per collegare un livello di metallo ad un altro (analogamente alla tecnica anteriore mostrata nella figura 2). Ogni segmento conduttivo 38a-d comprende una prima estremità 39' e una seconda estremità 39".

Sebbene i segmenti conduttivi 38a-d si estendano principalmente lungo il bordo 32a, la prima estremità 39' e la seconda estremità 39" sono nella regione interna 32b (pertanto, almeno una porzione dei segmenti conduttivi 38a-d si estende dal bordo 32a alla regione interna 32b, o viceversa, attraverso l'anello di tenuta 36). La prima estremità 39' e la seconda estremità 39" di ogni segmento

conduttivo 38a-d sono accoppiate a rispettive porzioni di estremità di un rispettivo modulo oscillatore da 40a a 40d; ogni modulo oscillatore da 40a a 40d include elementi (in particolare, in una forma di realizzazione, dispositivi elettronici passivi) configurati per generare oscillanti, aventi la propria frequenza, attraverso il segmento conduttivo 38a-d. La frequenza dei oscillanti può essere utilizzata per controllare l'integrità strutturale della piastrina 30. Infatti, le frequenze dei segnali oscillanti in ogni segmento conduttivo da 38a a 38d possono essere misurate e confrontate con una frequenza di riferimento (valore preimpostato) o confrontate tra loro. In caso di confronto con una frequenza di riferimento, il risultato del confronto è indicativo della presenza di un difetto. In caso di confronto di una frequenza con un'altra frequenza (appartenente a diversi segmenti da 38a a 38d), il risultato del confronto è indicativo della presenza di un difetto.

Mezzi di calcolo, quali un microcontrollore 43, sono presenti per eseguire operazioni mirate a verificare la presenza del difetto strutturale, come discusso meglio nel seguito. Il microcontrollore 43 può essere integrato nella piastrina a semiconduttore 30 (nella regione 32b) o disposto all'esterno della piastrina a semiconduttore 30. Il microcontrollore 43 è accoppiato operativamente ai moduli

oscillatori da 40a a 40d.

In dettaglio, se la frequenza in un segmento conduttivo da 38a a 38d è diversa dalla frequenza di riferimento (frequenza attesa), è probabilmente presente un difetto strutturale in corrispondenza della regione della piastrina 30 che alloggia tale segmento conduttivo. Il rilevamento può essere effettuato confrontando, mediante il microcontrollore 43, la frequenza del segnale oscillante nel segmento conduttivo da 38a a 38d sotto test con un valore di frequenza atteso (predefinito, memorizzato in una memoria). Possono essere impostate tolleranze durante l'esecuzione di tale confronto di frequenze.

Quando la frequenza di un segnale in un segmento conduttivo da 38a a 38d viene confrontata con le frequenze dei segnali negli altri segmenti conduttivi da 38a a 38d, viene rilevato un difetto strutturale quando le frequenze non sono uguali o sostanzialmente uguali tra loro. In questo caso, viene effettuata una misurazione differenziale. Per esempio, le due frequenze appartenenti ai due rispettivi segmenti conduttivi da 38a a 38d vengono sottratte e il risultato (la differenza) viene controllato rispetto ad un intervallo predefinito di valori attesi. In particolare, se la differenza è maggiore di una soglia, si ritiene che le due frequenze siano diverse l'una dall'altra e viene rilevato un difetto nella piastrina 30.

Anche in questo caso, possono essere impostate tolleranze durante l'esecuzione di tale confronto frequenze. Il rilevamento può essere eseguito confrontando, mediante il microcontrollore 43, la frequenza del segnale oscillante nel segmento conduttivo da 38a a 38d sotto test con la frequenza del segnale oscillante in uno o più degli altri segmenti conduttivi da 38a a 38d. In questo ultimo caso, il difetto viene rilevato se la frequenza misurata per il segmento conduttivo sotto test è sostanzialmente diversa dalla frequenza misurata negli altri segmenti conduttivi da 38b a 38d. In linea di principio, non è importante sapere quale frequenza è "corretta", ovvero quella del segmento sotto test o quella dell'altro segmento/degli altri segmenti. Infatti, fintantoché viene rilevato un difetto, l'intera piastrina 30 deve essere accantonata/sostituita.

L'assenza del segnale oscillante è anche un'indicazione della presenza di un difetto strutturale.

Facendo specifico riferimento alla forma di realizzazione della figura 4, quattro moduli oscillatori da 40a a 40d sono disposti all'interno della regione 32b. Con la presente soluzione, l'utilizzo di quattro segmenti conduttivi 38a-d al posto di un singolo segmento conduttivo (come nella tecnica nota) e l'esecuzione di misurazioni di frequenza separate per ciascuno di essi forniscono un'indicazione precisa della possibile difettosità

(associata ad una crepa o alla determinazione della rispettiva porzione della piastrina 30) della piastrina 30 sotto test.

L'approccio che prevede il confronto reciproco delle frequenze dei segnali nei segmenti da 38a a 38d richiede che tutti i segmenti conduttivi da 38a a 38d e i moduli oscillatori 40a, 40b siano strutturalmente equivalenti in modo tale che, in condizioni normali (assenza di difetti), le frequenze abbiano 10 stesso valore approssimativamente lo stesso valore quando vengono prese in considerazione variazioni normali da parte microcontrollore 43 che sta effettuando i confronti. rilevamento del problema (crepa, dispersione, ecc.), questo approccio, non è dipendente da parametri assoluti, ma dipende da un errore relativo rilevato in un segmento conduttivo da 38a a 38d rispetto alle misurazioni effettuate negli altri segmenti conduttivi da 38a a 38d.

In una forma di realizzazione alternativa, può anche essere controllato ad ogni modo l'intervallo assoluto del parametro misurato attraverso PVT.

Facendo riferimento alla figura 5, il segmento conduttivo 38a e il modulo oscillatore 40a accoppiato ad esso sono mostrati in dettagli, secondo una forma di realizzazione.

Nella forma di realizzazione della figura 5, il

rilevamento viene eseguito facendo funzionare a percorso chiuso ogni segmento conduttivo da 38a a 38d (qui, come detto, è mostrato soltanto il segmento 38a come esempio) come struttura oscillante che impiega soltanto elementi passivi. Il modulo oscillatore 40a (i moduli oscillatori da 40b a 40d sono analoghi) include una catena 45 formata dalle serie di un numero dispari di gate o inverter NOT 45a, 45b, 45c (per esempio, tre inverter). Ogni inverter ha una porta di ingresso, una porta di uscita e una porta di controllo adatte a ricevere un segnale di abilitazione (o segnale di controllo) SE1 che "accende" (on) e "speque" (off) rispettivo inverter. Gli inverter sono collegati in serie tra loro in modo tale che la porta di uscita di un inverter sia collegata alla porta di ingresso dell'altro inverter nel collegamento in serie. In particolare, la porta di ingresso dell'inverter 45a è collegata alla prima estremità 39' del segmento 38a; la porta di uscita dell'inverter 45a è collegata alla porta di ingresso dell'inverter 45b; la porta di uscita dell'inverter 45b è collegata alla porta di 45c; e ingresso dell'inverter la porta di dell'inverter 45c è collegata alla seconda estremità 39" del 38a. Il collegamento della porta di segmento dell'inverter 45c alla seconda estremità 39" è formato da una linea conduttiva 46 che passa attraverso la regione 32b della piastrina 30 (come rappresentato schematicamente nella figura 4 con linea tratteggiata) o, in alternativa, lungo il perimetro della piastrina 30, analogamente al segmento 38a (si veda la figura 7B).

Il segmento conduttivo 38 è rappresentato schematicamente come una struttura elettrica RC.

Collegando la catena 45 a entrambe le estremità 39', 39" del segmento conduttivo 38a, formando così un percorso chiuso, viene formato un oscillatore ad anello. Un segnale di frequenza viene pertanto generato e può essere rilevato dal microcontrollore 43. L'oscillatore ad anello in questo esempio comprende tre inverter a tre stati in un anello, la cui uscita oscilla tra due livelli di tensione, che rappresentano gli stati logici "vero" e "falso". Il segnale abilitazione SE1 viene utilizzato per attivare e di disattivare il modulo oscillatore 40a, quando richiesto durante l'uso. Per esempio, quando SE="1", gli inverter sono "accesi" (o "attivi" o in "stato di conduzione") e il modulo oscillatore 40a inizia a oscillare e può essere osservata una frequenza in un qualsiasi punto nel percorso chiuso; tale frequenza può essere misurata attraverso mezzi e tecniche noti.

Per esempio, il microcontrollore 43 è accoppiato agli inverter 45a-c nella catena 45 per fornire il segnale di attivazione SE1 soltanto quando deve essere eseguito un test e per disattivare altrimenti gli inverter.

Vi possono essere molteplici metodi per misurare la frequenza nel percorso chiuso. In una forma di realizzazione l'analisi della frequenza esemplificativa, può essere effettuata acquisendo, da parte del microcontrollore 43, il segnale nell'oscillatore ad anello (per esempio, il segnale presente in corrispondenza della porta di uscita di uno qualsiasi degli inverter nella catena 45) e contando i fronti di risalita di tale segnale. Per misurare la frequenza, altri parametri del segnale possono essere controllati microcontrollore 43 (per esempio il fronte di discesa del segnale o gli stati logici "0" o "1" del segnale). La frequenza così misurata può, come già discusso, essere confrontata con un valore preimpostato (per esempio memorizzato in una memoria) o confrontata con le frequenze misurate del segnale in uno o più degli altri segmenti conduttivi da 38b a 38d/catene 45.

Il circuito mostrato è in grado di misurare finemente, durante il test, la frequenza e pertanto l'RC effettivo. Le misure fini forniscono la capacità di correlazione tra:

- misura nativa in corrispondenza di EWS;

- valori misurati in corrispondenza di FT (essendo la sorgente principale di taglio delle crepe);

- guasti gravi dopo caratterizzazione di sollecitazione (Burn-In, saldatura, cicli termici);

- guasti gravi dal campo.

La costante RC del segmento conduttivo è dominante rispetto agli elementi CMOS (ovvero, gli inverter della catena 45), consentendo pertanto una misura di frequenza che è sostanzialmente immune da contributi indesiderati.

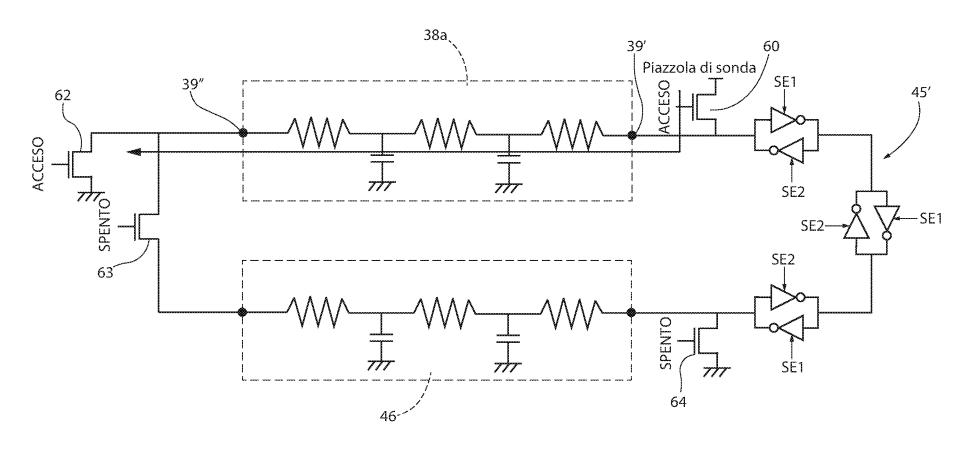

La figura 6 mostra un'ulteriore forma di realizzazione di un modulo oscillatore (qui, per esempio il modulo oscillatore 40a, ma gli altri moduli oscillatori da 40b a 40d sono gli stessi), in cui viene impiegata e implementata struttura oscillante bidirezionale 45'. Qui, inverter da 45a a 45c nella catena è disposto a contatto elettrico parallelo con un altro inverter da 45d a 45f, per consentire la generazione di un segnale oscillante entrambe le direzioni in senso orario e in senso antiorario. Quando deve essere generato un segnale in direzione in senso orario, i corrispondenti inverter da 45a a 45c vengono accesi impostando il segnale SE1="1" e gli altri inverter da 45d a 45f vengono spenti impostando il segnale SE2="0". Quando deve essere generato un segnale nella direzione in senso antiorario, i corrispondenti inverter da 45d a 45f vengono accesi impostando il segnale SE2="1" e gli altri inverter da 45a a 45c vengono spenti impostando il segnale SE1="0".

In questa forma di realizzazione, l'effetto di una resistenza anomala di una porzione del segmento conduttivo 38a (per via per esempio di una crepa o una crepa parziale) può essere rilevato confrontando insieme le frequenze dei

due segnali nelle direzioni in senso orario e in senso antiorario per lo stesso segmento conduttivo 38a. In questo caso, viene effettuata una misurazione differenziale. Per esempio, le due frequenze di segnale nelle direzioni in senso orario e in senso antiorario vengono sottratte l'una dall'altra e il risultato (la differenza) viene controllato rispetto ad un intervallo predefinito di valori attesi. In particolare, se la differenza è maggiore di una soglia, si ritiene che le due frequenze siano diverse l'una dall'altra e viene rilevato un difetto nella piastrina 30.

Un difetto strutturale che influisce soltanto su una porzione del segmento conduttivo 38a aumenta localmente la resistenza elettrica del segmento conduttivo 38a (lo stesso si applica agli altri segmenti conduttivi da 38b a 38d). Un'alta resistenza soltanto in una porzione del segmento conduttivo 38a può ridurre la frequenza del segnale in senso orario (tale frequenza essendo minore del valore atteso). Al contrario, la frequenza del segnale in senso antiorario può essere influenzata diversamente o non influenzata per nulla. Pertanto, confrontando le due frequenze insieme, si fornisce un'indicazione della presenza, o assenza, di un difetto nel segmento 38a sotto test. Questo metodo può essere applicato alla topologia di circuito secondo la presente invenzione, e anche alle topologie di circuito della tecnica nota.

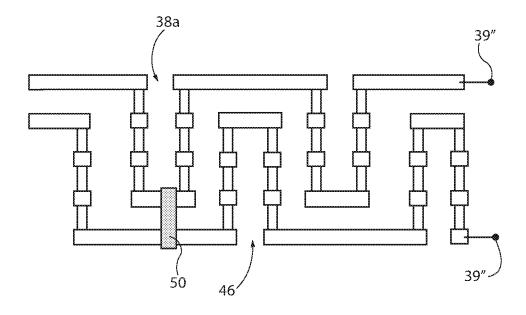

La figura 7A mostra un'implementazione strutturale del

segmento conduttivo 38a (gli altri segmenti 38b-d essendo equivalenti) e della linea conduttiva 46 che collega la seconda estremità 39" alla catena 45, quando tale linea conduttiva 46 è formata in corrispondenza del perimetro della piastrina 30, ovvero fuori dalla regione 32b, e, più in particolare, tra l'anello di tenuta 36 e il bordo 32a. La linea conduttiva 46 è formata attraverso vari strati di metallo, analogamente al segmento conduttivo 38a. In questo caso, infatti, il segmento conduttivo da 38a a 38d e la rispettiva linea conduttiva 46 sono formati come due serpentine passanti e di metallo interlacciate, con le due estremità 39' e 39" collegate alla catena 45 o 45', come già mostrato nelle figure 5 e 6.

In un'ulteriore forma di realizzazione, figura 8, un difetto può essere rilevato mediante una misurazione di resistenza. Ciò può essere effettuato applicando una tensione attraverso una sonda e controllando la corrente proveniente da essa, per calcolare la resistenza in un modo noto di per sé. Tutti gli inverter da 45a a 45f della struttura oscillante bidirezionale 45' sono disabilitati (SE1=SE"="0") durante questo test.

Un dato numero di commutatori (rappresentati come transistori) è accoppiato al sensore di crepe per eseguire questo test. In particolare, un commutatore 60 collega la prima estremità 39' alla piazzola di sonda, per alimentare

una corrente di test alla prima estremità 39'; un commutatore 62 collega la seconda estremità 39" alla massa; un commutatore 63 collega la seconda estremità 39" alla linea conduttiva 46; e un commutatore 64 collega la linea conduttiva 46 alla massa.

Per eseguire un test resistivo del segmento conduttivo 38a, i commutatori 60 e 62 sono accesi e i commutatori 63 e 64 sono spenti. Una corrente di test scorre dalla piazzola di sonda alla massa, passando attraverso la linea conduttiva 38. Una resistenza elettrica del segmento 38a può essere misurata in un modo noto e confrontata con un valore atteso. Un risultato di tale confronto è indicativo di una resistenza anomala nel segmento 38a, che può indicare la presenza di un difetto strutturale.

In alternativa, la resistenza elettrica del segmento 38a può essere misurata e confrontata con la resistenza elettrica di un altro segmento, per esempio il segmento 38b. In questo caso, viene effettuata una misurazione differenziale. Per esempio, i due valori di resistenza appartenenti ai due rispettivi segmenti conduttivi 38a, 38b vengono sottratti l'uno dall'altro e il risultato (la differenza) viene controllato rispetto ad un intervallo predefinito di valori attesi. In particolare, se la differenza è maggiore di una soglia, si ritiene che i due valori di resistenza siano diversi l'uno dall'altro e viene

rilevato un difetto nella piastrina 30.

In un'ulteriore forma di realizzazione, figura 9, può essere eseguito un test di dispersione. Per fare ciò, viene applicata una tensione attraverso una sonda e la corrente proveniente da essa viene controllata; idealmente, tale corrente dovrebbe essere trascurabile. Tutti gli inverter della struttura oscillante 45' sono disabilitati, o non presenti, durante questo test, come nella figura 8. Durante questo test, il commutatore 60 è acceso, per collegare la prima estremità 39' alla piazzola di sonda, per alimentare la corrente di test. Occorre evidenziare che il commutatore 64 è anch'esso acceso, per collegare la linea conduttiva 46 alla massa. Tutti gli altri commutatori 62 e 63 sono spenti. Questo test può rilevare un cortocircuito tra le due serpentine (quella del segmento 38 e quella della linea 46), esemplificato nella figura 10 dal collegamento indesiderato 50. Tutti gli altri elementi della figura 10 corrispondono a quelli della figura 7A, già discussa. Nel caso sia presente un cortocircuito, viene rilevata alta corrente (al di sopra di una certa soglia, preimpostato) da parte della sonda e viene rivelato il difetto.

La figura 11 mostra un'ulteriore forma di realizzazione della presente invenzione. La forma di realizzazione della figura 11 si basa sulla forma di realizzazione della figura 8 (gli elementi corrispondenti sono identificati con gli

stessi numeri di riferimento e non descritti ulteriormente). Nella figura 11, la linea conduttiva 46 è progettata e fabbricata per essere strutturalmente e/o elettricamente equivalente o uguale al segmento conduttivo 38a (e anche ai segmenti conduttivi da 38b a 38d). Nella forma di realizzazione della figura 11, la linea conduttiva 46 è rappresentata schematicamente come una struttura elettrica RC. Anche se la figura 11 si basa sulla figura 8, la progettazione proposta della linea conduttiva 46 si applica ugualmente alla forma di realizzazione della figura 9.

I vantaggi dell'invenzione descritta in precedenza, secondo le varie forme di realizzazione, emergono chiaramente dalla precedente descrizione.

In particolare, la fornitura di un multi sensore su un singolo chip, la conversione di resistenza di sensore in una frequenza misurabile e l'uso di un sensore interlacciato a doppia serpentina forniscono (singolarmente o in combinazione) i seguenti vantaggi: tempo di test ridotto, scartamento migliorato, possibilità di scartamento differenziale (tra i quattro sensori) sul chip, fornitura di un primo livello di localizzazione di guasto topografico, misura fine della resistenza di sensore, miglioramento della capacità di correlazione richiesta per sintonizzazione di capacità di limite di accettazione.

Infine, è evidente che possono essere apportate

modifiche e variazioni a quanto è stato descritto e illustrato nella presente, senza con ciò discostarsi dall'ambito di protezione della presente invenzione, come definito nelle rivendicazioni allegate.

### RIVENDICAZIONI

1. Gruppo per rilevare un difetto strutturale in una piastrina a semiconduttore (30), comprendente un sensore di rilevamento di difetto e mezzi di calcolo (43),

in cui il sensore di rilevamento di difetto include:

una pluralità di percorsi resistivi (38a-d) di materiale elettricamente conduttivo nella piastrina a semiconduttore (30), ciascuno dei quali ha una prima estremità (39') e una seconda estremità (39") e si estende in una rispettiva regione della piastrina a semiconduttore in prossimità di un perimetro (32a) della piastrina a semiconduttore, circondando parzialmente una porzione interna (32b) della piastrina a semiconduttore (30); e

una pluralità di strutture di generazione di segnali (45), ciascuna delle quali è accoppiata elettricamente alla prima estremità (39') e alla seconda estremità (39") di un rispettivo percorso resistivo (38a-d) ed è configurata per fornire un rispettivo segnale di test al percorso resistivo (38a-d);

e in cui i mezzi di calcolo (43) sono accoppiati operativamente alla pluralità di strutture di generazione di segnali (45) e sono configurati per:

controllare le strutture di generazione di segnali (45) per generare i segnali di test;

acquisire i segnali di test in ogni percorso resistivo

(38a-d);

testare una caratteristica elettrica dei percorsi resistivi (38a-d) eseguendo un'analisi dei segnali di test acquisiti; e

rilevare la presenza di detto difetto strutturale nella piastrina a semiconduttore (30) in base a un risultato di detta analisi dei segnali di test acquisiti.

- 2. Gruppo secondo la rivendicazione 1, in cui ogni percorso resistivo (38a-d) include un percorso chiuso formato da un primo sotto-percorso che si estende dalla prima estremità (39') ad un punto di collegamento intermedio e un secondo sotto-percorso che si estende dal punto di collegamento intermedio alla seconda estremità (39").

- 3. Gruppo secondo la rivendicazione 1 o la rivendicazione 2, in cui la piastrina a semiconduttore (30) comprende un anello di tenuta (36) che circonda la porzione interna (32b), ogni percorso resistivo (38a-d) estendendosi tra l'anello di tenuta (36) e il perimetro (32a) ad eccezione della prima e della seconda estremità (39', 39") che si estendono attraverso l'anello di tenuta (36) verso la porzione interna (32b).

- 4. Gruppo secondo una qualsiasi delle rivendicazioni precedenti, in cui ogni struttura di generazione di segnali (45) comprende un generatore di corrente che può essere attivato per fornire il segnale di test, che è una corrente

elettrica, al rispettivo percorso resistivo (38a-d);

e in cui i mezzi di calcolo (43) sono configurati per:

controllare le strutture di generazione di segnali (45)

attivando il generatore di corrente;

testare la caratteristica elettrica dei percorsi resistivi (38a-d) misurando un valore di resistenza elettrica che ogni percorso resistivo (38a-d) oppone al flusso della corrente elettrica.

- 5. Gruppo secondo la rivendicazione 4, in cui i mezzi di calcolo (43) sono inoltre configurati per testare la caratteristica elettrica dei percorsi resistivi (38a-d) eseguendo una misurazione differenziale dei valori di resistenza elettrica tra detta pluralità di percorsi resistivi (38a-d).

- 6. Gruppo secondo la rivendicazione 5, in cui detto difetto viene rilevato se un risultato della misurazione differenziale non rientra in un intervallo predefinito di valori attesi.

- 7. Gruppo secondo una qualsiasi delle rivendicazioni da 1 a 3, in cui ogni struttura di generazione di segnali (45) comprende un dispositivo oscillatore (45) includente un numero dispari di inverter (da 45a a 45c) collegati in collegamento elettrico in serie l'uno all'altro tra la prima estremità (39') e la seconda estremità (39"), detto dispositivo oscillatore (45) formando, con il rispettivo

percorso resistivo (38a-d) a cui è accoppiato, un oscillatore ad anello monodirezionale.

8. Gruppo secondo una qualsiasi delle rivendicazioni da 1 a 3, in cui ogni struttura di generazione di segnali (45) comprende un dispositivo oscillatore (45') includente un primo insieme di inverter (da 45a a 45c) in numero dispari collegati in collegamento elettrico in serie l'uno all'altro tra la prima estremità (39') e la seconda estremità (39") e un secondo insieme di inverter (da 45d a 45f) in numero dispari collegati in collegamento elettrico in serie l'uno all'altro tra la prima estremità (39') e la seconda estremità (39") in collegamento anti-parallelo rispetto al primo insieme di inverter (da 45a a 45c),

detto dispositivo oscillatore (45) formando, con il rispettivo percorso resistivo (38a-d) a cui è accoppiato, un oscillatore ad anello bidirezionale.

- 9. Gruppo secondo una qualsiasi delle rivendicazioni 7 e 8, in cui il segnale di test è un segnale di oscillazione avente una frequenza di oscillazione, i mezzi di calcolo (43) essendo configurati per testare la caratteristica elettrica dei percorsi resistivi (38a-d) eseguendo un'analisi della frequenza di oscillazione del segnale di test appartenente al percorso resistivo (38a-d) sotto test.

- 10. Gruppo secondo la rivendicazione 9, in cui i mezzi di calcolo (43) sono configurati per eseguire detta analisi

della frequenza di oscillazione confrontando la frequenza di oscillazione del segnale di test appartenente al percorso resistivo (38a-d) sotto test con una frequenza di un altro segnale di test appartenente ad un altro percorso resistivo (38a-d) della pluralità di percorsi resistivi (da 38a a 38d).

- 11. Gruppo secondo la rivendicazione 9 o 10, in cui i mezzi di calcolo (43) sono configurati per eseguire detta analisi della frequenza di oscillazione eseguendo una misurazione differenziale della frequenza di oscillazione del segnale di test appartenente al percorso resistivo (38a-d) sotto test con una frequenza di un altro segnale di test appartenente ad un altro percorso resistivo (38a-d) della pluralità di percorsi resistivi (da 38a a 38d).

- 12. Gruppo secondo la rivendicazione 11, in cui detto difetto viene rilevato se un risultato della misurazione differenziale non rientra in un intervallo predefinito di valori attesi.

- 13. Gruppo secondo la rivendicazione 9, in cui i mezzi di calcolo (43) sono configurati per eseguire detta analisi della frequenza di oscillazione confrontando la frequenza di oscillazione del segnale di test appartenente al percorso resistivo (38a-d) sotto test con una frequenza di riferimento attesa.

- 14. Gruppo secondo la rivendicazione 8 o la rivendicazione 9 quando dipendente dalla rivendicazione 8,

in cui i mezzi di calcolo (43) sono inoltre configurati per testare un percorso resistivo (da 38a a 38d) mediante:

attivazione del primo insieme di inverter (da 45a a 45c) accoppiati a detto percorso resistivo (da 38a a 38d) sotto test, determinando così la generazione di un rispettivo segnale di test che scorre in una prima direzione attraverso il percorso resistivo (da 38a a 38d) sotto test e, contemporaneamente, disattivazione del secondo insieme di inverter (da 45d a 45f) accoppiati in collegamento antiparallelo al primo insieme attivato di inverter (da 45a a 45c) di detto percorso resistivo (da 38a a 38d) sotto test;

acquisizione di un primo valore di frequenza del segnale di test che scorre in detta prima direzione;

disattivazione del primo insieme di inverter (da 45a a 45c) accoppiati al percorso resistivo (da 38a a 38d) sotto test e, contemporaneamente, attivazione del secondo insieme di inverter (da 45d a 45f) accoppiati al percorso resistivo (da 38a a 38d) sotto test, determinando così la generazione di un altro segnale di test che scorre in una seconda direzione, opposta alla prima direzione, attraverso il percorso resistivo (da 38a a 38d) sotto test;

acquisizione di un secondo valore di frequenza del segnale di test che scorre in detta seconda direzione;

confronto del primo valore di frequenza con il secondo valore di frequenza;

associazione di uno stato fisico della piastrina a semiconduttore (30) a un risultato di detto confronto del primo valore di frequenza con il secondo valore di frequenza.

FIGURA 3

FIGURA 4

FIGURA 5

FIGURA 6

FIGURA 8

FIGURA 9

FIGURA 10

FIGURA 11