(12) 发明专利

(10) 授权公告号 CN 109817172 B

(45) 授权公告日 2022.04.01

(21) 申请号 201811382451.0

(51) Int.CI.

(22) 申请日 2018.11.20

G09G 3/36 (2006.01)

(65) 同一申请的已公布的文献号

G09G 3/3208 (2016.01)

申请公布号 CN 109817172 A

(56) 对比文件

(43) 申请公布日 2019.05.28

CN 1691113 A, 2005.11.02

(30) 优先权数据

US 2016203769 A1, 2016.07.14

2017-223602 2017.11.21 JP

CN 107799078 A, 2018.03.13

(73) 专利权人 拉碧斯半导体株式会社

CN 107180617 A, 2017.09.19

地址 日本神奈川县横滨市港北区新横滨2-

4-8 (邮政编码:222-8575)

CN 100466048 C, 2009.03.04

(72) 发明人 相泽洋喜

US 2007195054 A1, 2007.08.23

(74) 专利代理机构 北京同立钧成知识产权代理

有限公司 11205

CN 104900200 A, 2015.09.09

代理人 马爽 藏建明

审查员 凤艳艳

(54) 发明名称

显示驱动器及半导体装置

(57) 摘要

本发明提供一种显示驱动器及半导体装置。显示驱动器包括：数据收集部，收集对应于各像素的亮度电平的第一～第N像素数据片，并在时钟信号的边沿时刻输出；第一～第N放大器，放大对应于第一～第N像素数据片的第一～第N分级电压而获得第一～第N驱动电压；以及偏电压生成部，生成设定各放大器的动作电流的电流值的偏电压并供给至各放大器。偏电压生成部存储将动作电流的电流值设定成第一电流值的偏电压的第一电压值及将动作电流的电流值设定成比第一电流值低的第二电流值的偏电压的第二电压值。偏电压生成部在从时钟信号的边沿时间点经过第一时段的期间生成具有第一电压值的偏电压，并在经过第一时段的时间点将偏电压的电压值切换成第二电压值。

1. 一种显示驱动器，其对具有第1～第N数据线的显示装置进行驱动，其中N为2以上的整数，其特征在于，所述显示驱动器包括：

数据收集部，接收针对每个像素表示基于影像信号的亮度电平的第1～第N像素数据片，并在时钟信号的边沿的时刻输出所述第1～第N像素数据片；

分级电压生成部，将从所述数据收集部输出的所述第1～第N像素数据片转换成第1～第N分级电压；

第1～第N放大器，将对所述第1～第N分级电压进行放大所得的第1～第N驱动电压供给至所述第1～第N数据线；以及

偏电压生成部，生成设定所述第1～第N放大器的各者的动作电流的电流值的偏电压并供给至所述第1～第N放大器，且

所述偏电压生成部包括存储第1信息与第2信息的寄存器，所述第1信息表示第1电压值作为将所述动作电流的电流值设定成第1电流值的所述偏电压的电压值，所述第2信息表示第2电压值作为将所述动作电流的电流值设定成比所述第1电流值低的第2电流值的所述偏电压的电压值，

从所述时钟信号的所述边沿的时间点到经过第1时段的时间点的期间，生成具有所述第1信息所表示的所述第1电压值的所述偏电压，在经过所述第1时段的时间点将所述偏电压的电压值切换成所述第2信息所表示的所述第2电压值。

2. 根据权利要求1所述的显示驱动器，其特征在于，所述第1时段具有与响应所述分级电压中的从表示最低亮度的电压值向表示最高亮度的电压值的转变，由所述放大器输出的所述驱动电压的电压值从对应于所述最低亮度的电压值转变为对应于所述最高亮度的电压值花费的时间对应的时段长度。

3. 根据权利要求1或2所述的显示驱动器，其特征在于，所述寄存器中存储表示所述第1时段的信息。

4. 根据权利要求1或2所述的显示驱动器，其特征在于，所述偏电压生成部包括：

电流源，生成基准电流；以及

电压调整部，基于所述基准电流生成基准偏电压，通过对所述基准偏电压实施基于所述第1信息的调整来获得所述第1电压值，并通过对所述基准偏电压实施基于所述第2信息的调整来获得所述第2电压值。

5. 根据权利要求1或2所述的显示驱动器，其特征在于，所述放大器包括：

差分段，生成以所输入的所述分级电压与所输出的输出电压的电压比对第1动作电流进行2分割而得的第1电流及第2电流；

电流镜段，通过将对应于所述第1电流及所述第2电流的差的第2动作电流供给至驱动节点或从所述驱动节点引出，在所述驱动节点生成输出驱动电压；

输出段，通过将对应于所述输出驱动电压的输出电流供给至输出节点或从所述输出节点引出，在所述输出节点生成所述输出电压；以及

偏压调整部，根据所述偏电压调整所述第1动作电流及第2动作电流的电流值。

6. 根据权利要求1或2所述的显示驱动器，其特征在于，包括：

扫描驱动器，对在所述显示装置中与所述第1～第N数据线交叉配置的第1～第M水平扫描线依序施加水平扫描脉冲，并对所述第1～第M水平扫描线的各者依序进行驱动，其中M为

2以上的整数,且

在驱动所述第1～第M水平扫描线中配置于远离所述第1～第N放大器的位置的所述水平扫描线时,所述偏电压生成部使用的所述第1时段的长度比驱动配置于靠近所述第1～第N放大器的位置的所述水平扫描线时所述偏电压生成部使用的所述第1时段的长度长。

7.根据权利要求1所述的显示驱动器,其特征在于,包括:

切换判定部,将所述第1～第N驱动电压中电压值的转变幅度最大的驱动电压的电压值超过规定的参照电压值的时间点设定为经过所述第1时段的时间点。

8.根据权利要求1所述的显示驱动器,其特征在于,包括:

切换判定部,将所述第1～第N驱动电压中电压值的转变幅度最大的驱动电压的电压值与对应于所述转变幅度最大的驱动电压的所述分级电压的电压值变得相等的时间点设定成经过所述第1时段的时间点。

9.一种半导体装置,其包括对具有第1～第N数据线的显示装置进行驱动的显示驱动器,其中N为2以上的整数,其特征在于,所述半导体装置包括:

数据收集部,接收针对每个像素表示基于影像信号的亮度电平的第1～第N像素数据片,并在时钟信号的边沿的时刻输出所述第1～第N像素数据片;

分级电压生成部,将从所述数据收集部输出的所述第1～第N像素数据片转换成第1～第N分级电压;

第1～第N放大器,将对所述第1～第N分级电压进行放大所得的第1～第N驱动电压供给至所述第1～第N数据线;以及

偏电压生成部,生成设定所述第1～第N放大器的各者的动作电流的电流值的偏电压并供给至所述第1～第N放大器,且

所述偏电压生成部包括存储第1信息与第2信息的寄存器,所述第1信息表示第1电压值作为将所述动作电流的电流值设定成第1电流值的所述偏电压的电压值,所述第2信息表示第2电压值作为将所述动作电流的电流值设定成比所述第1电流值低的第2电流值的所述偏电压的电压值,

在从所述时钟信号的所述边沿的时间点到经过第1时段的时间点的期间,生成具有所述第1信息所表示的所述第1电压值的所述偏电压,在经过所述第1时段的时间点将所述偏电压的电压值切换成所述第2信息所表示的所述第2电压值。

## 显示驱动器及半导体装置

### 技术领域

[0001] 本发明涉及一种根据影像信号驱动显示装置的显示驱动器及包括所述显示驱动器的半导体装置。

### 背景技术

[0002] 对作为显示装置的例如液晶显示面板或有机电致发光(electroluminescence, EL)面板进行驱动的显示驱动器中,包含将对应于由影像信号表示的亮度电平的分级电压放大并供给至显示装置的源极线的多个输出放大器。

[0003] 另外,伴随着近年的显示装置的大画面化、高精细化,对于输出放大器,期望缩短输出电压的上升或下降时间,即所谓的高转换速率(slew rate)化。且说,输出放大器例如包含运算放大器,可通过增加在自身的差分段流动的电流来提高转换速率,但相应地产生耗电量增加的问题。

[0004] 因此,提出有如下的技术:在显示驱动器内设置具有与输出放大器同样的电气特性的伪放大器(dummy amplifier),仅在使所述伪放大器动作时的输出电平的转变时段的期间增加在输出放大器的差分段流动的电流,以实现高转换速率化(例如,参照日本专利特开2012-27127号公报(专利文献1))。

### 发明内容

[0005] [发明所要解决的问题]

[0006] 但是,在采用所述技术的情况下,必须在显示驱动器内设置伪放大器,所以相应地驱动器的尺寸变大。

[0007] 另外,此伪放大器自身消耗与输出放大器同样的电力,所以妨碍低耗电化。进而,伴随着制造偏差,在从伪放大器输出的电压的转变时段与从输出放大器输出的电压的转变时段中产生有误差的情况下,无法在正确的时间点进行如所述那样的转换速率的切换。由此,难以确实地降低耗电量且难以高速地驱动显示装置。

[0008] 因此,本发明的目的在于提供一种能够抑制装置规模的增加,以低电耗且高速地驱动显示装置的显示驱动器及半导体装置。

[0009] [解决问题的技术手段]

[0010] 本发明的显示驱动器是对具有第1～第N(N为2以上的整数)数据线的显示装置进行驱动的显示驱动器,其包括:数据收集部,接收针对每个像素表示基于影像信号的亮度电平的第1～第N像素数据片,并在时钟信号的边沿时刻输出所述第1～第N像素数据片;分级电压生成部,将从所述数据收集部输出的所述第1～第N像素数据片转换成第1～第N分级电压;第1～第N放大器,将对所述第1～第N分级电压进行放大所得的第1～第N驱动电压供给至所述第1～第N数据线;以及偏电压生成部,生成设定所述第1～第N放大器的各者的动作电流的电流值的偏电压并供给至所述第1～第N放大器,所述偏电压生成部包括存储第1信息与第2信息的寄存器,所述第1信息表示第1电压值作为将所述动作电流的电流值设定成

第1电流值的所述偏电压的电压值,所述第2信息表示第2电压值作为将所述动作电流的电流值设定成比所述第1电流值低的第2电流值的所述偏电压的电压值,在从所述时钟信号的边沿时间点到经过第1时段的时间点的期间,生成具有所述第1信息所表示的所述第1电压值的所述偏电压,在经过所述第1时段的时间点将所述偏电压的电压值切换成所述第2信息所表示的所述第2电压值。

[0011] 另外,本发明的半导体装置是包括对具有第1~第N(N为2以上的整数)数据线的显示装置进行驱动的显示驱动器的半导体装置,其包括:数据收集部,接收针对每个像素表示基于影像信号的亮度电平的第1~第N像素数据片,并在时钟信号的边沿时刻输出所述第1~第N像素数据片;分级电压生成部,将从所述数据收集部输出的所述第1~第N像素数据片转换成第1~第N分级电压;第1~第N放大器,将对所述第1~第N分级电压进行放大所得的第1~第N驱动电压供给至所述第1~第N数据线;以及偏电压生成部,生成对所述第1~第N放大器的各者的动作电流的电流值进行设定的偏电压并供给至所述第1~第N放大器,且所述偏电压生成部包括存储第1信息与第2信息的寄存器,所述第1信息表示第1电压值作为将所述动作电流的电流值设定成第1电流值的所述偏电压的电压值,所述第2信息表示第2电压值作为将所述动作电流的电流值设定成比所述第1电流值低的第2电流值的所述偏电压的电压值,在从所述时钟信号的所述边沿时间点到经过第1时段的时间点的期间,生成具有所述第1信息所表示的所述第1电压值的所述偏电压,在经过所述第1时段的时间点将所述偏电压的电压值切换成所述第2信息所表示的所述第2电压值。

[0012] [发明的效果]

[0013] 本发明的显示驱动器中,使将在时钟信号的边沿时刻所供给的分级电压放大而生成驱动电压的放大器的动作电流,在从时钟信号的边沿时间点到经过第1时段的时间点的期间,高于所述经过第1时段的时间点以后的动作电流。

[0014] 由此,在要求高速响应的驱动电压的上升或下降的区间中,能使放大器的转换速率变高,所以可实现驱动电压的上升或下降时间的缩短。另一方面,在经过第1时段的时间点以后的电压值成为恒定的区间中,能使放大器的动作电流变低,所以可实现低耗电化。

[0015] 因而,与通过设置将分级电压放大的放大器以及与此放大器同样的特性的伪放大器并使所述伪放大器动作来检测驱动电压的转变时段的装置相比,能够以小规模的构成,确实地以低电耗且高速地驱动显示装置。

## 附图说明

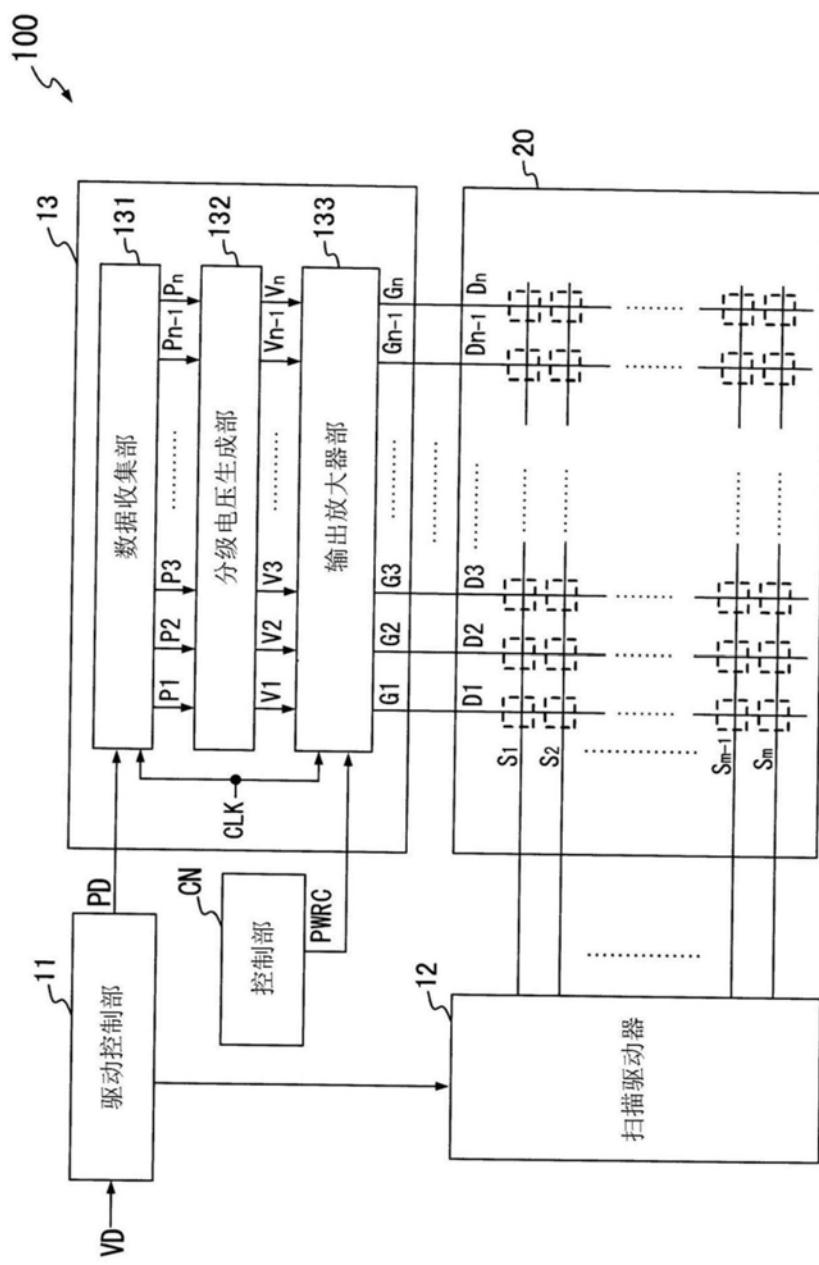

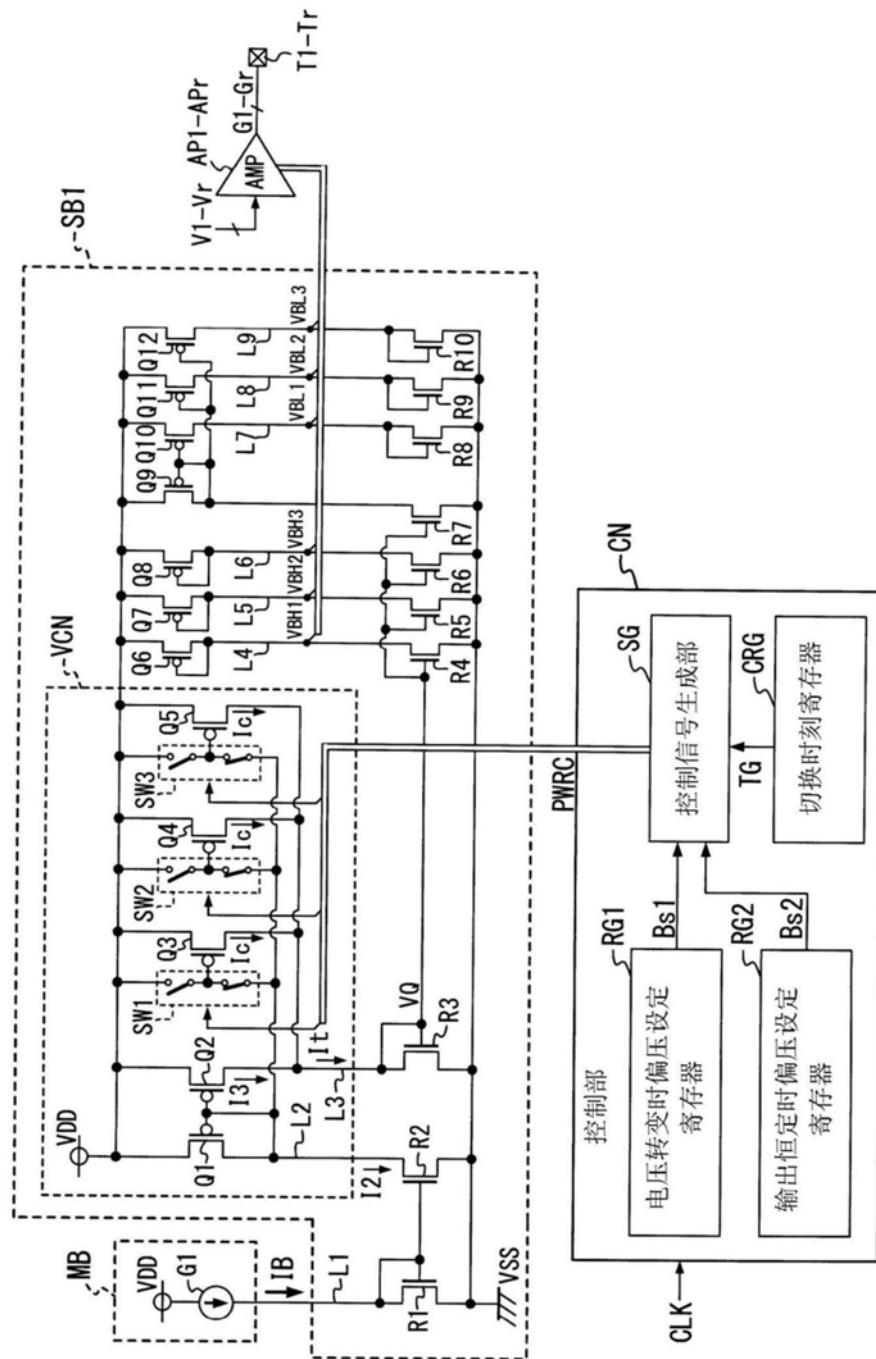

[0016] 图1是表示包含本发明的显示驱动器的显示装置100的构成的方块图。

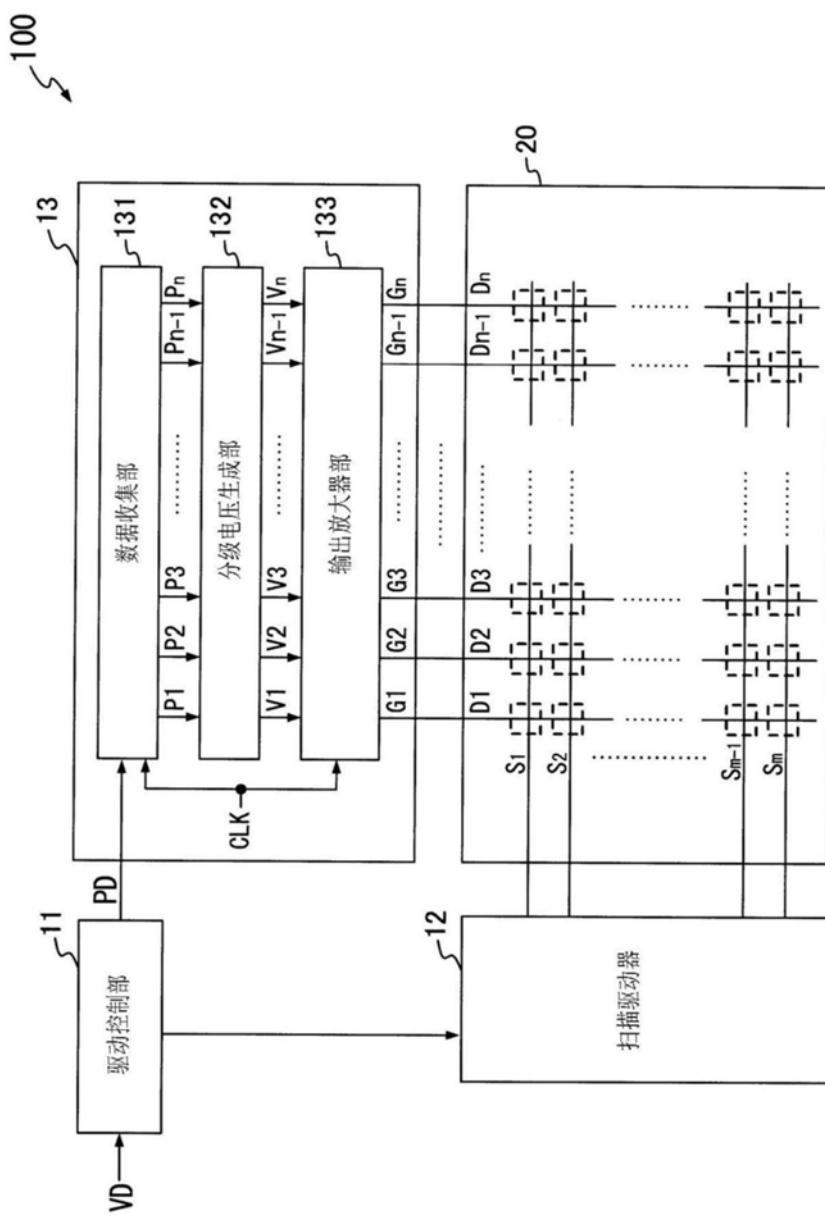

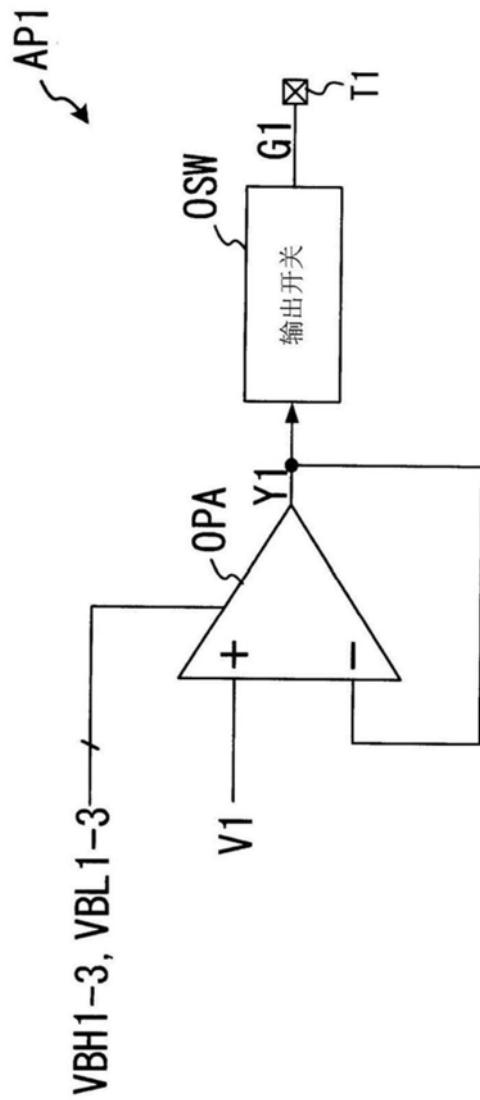

[0017] 图2是表示输出放大器部133的内部构成的方块图。

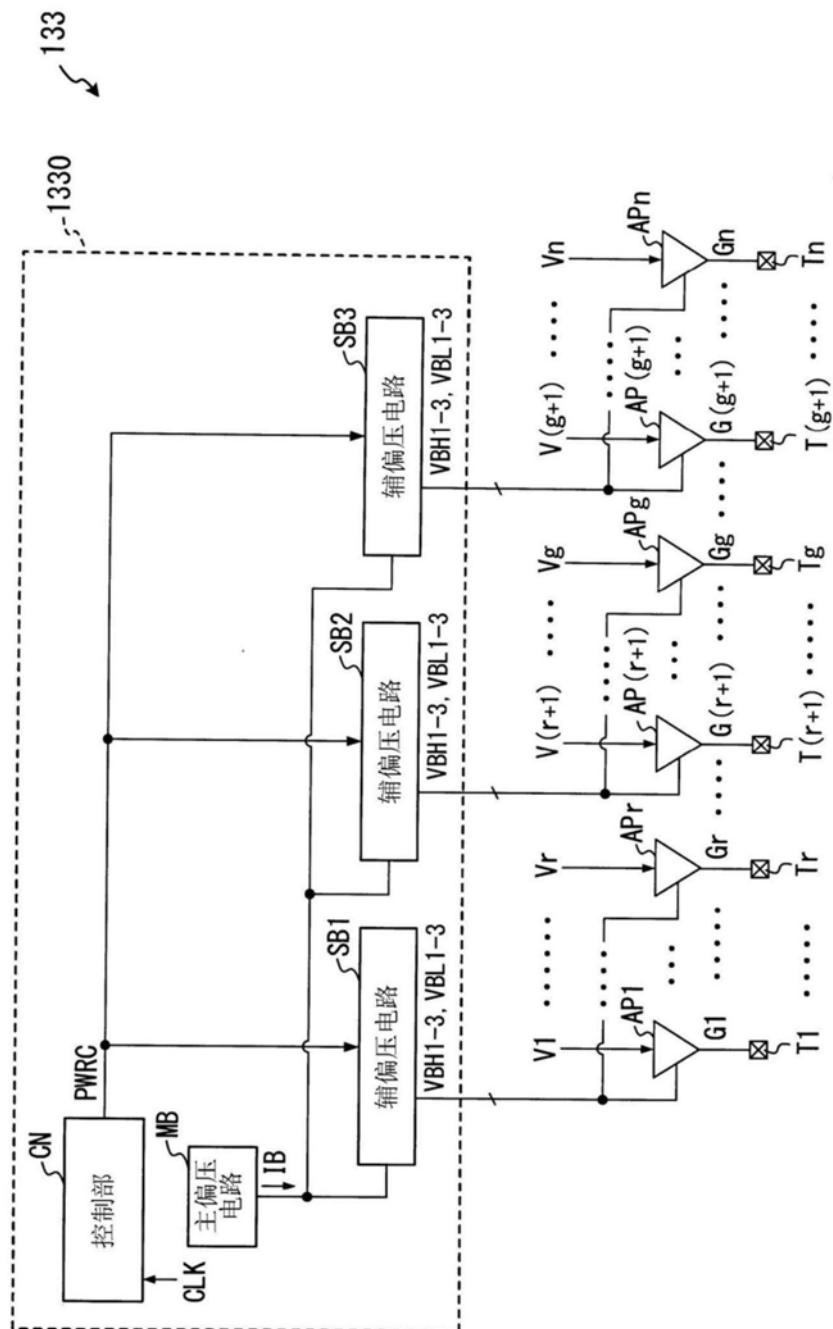

[0018] 图3是详细表示控制部CN、主偏压电路MB及辅偏压电路SB1的内部构成的一例的图。

[0019] 图4是表示放大器AP1的内部构成的一例的电路图。

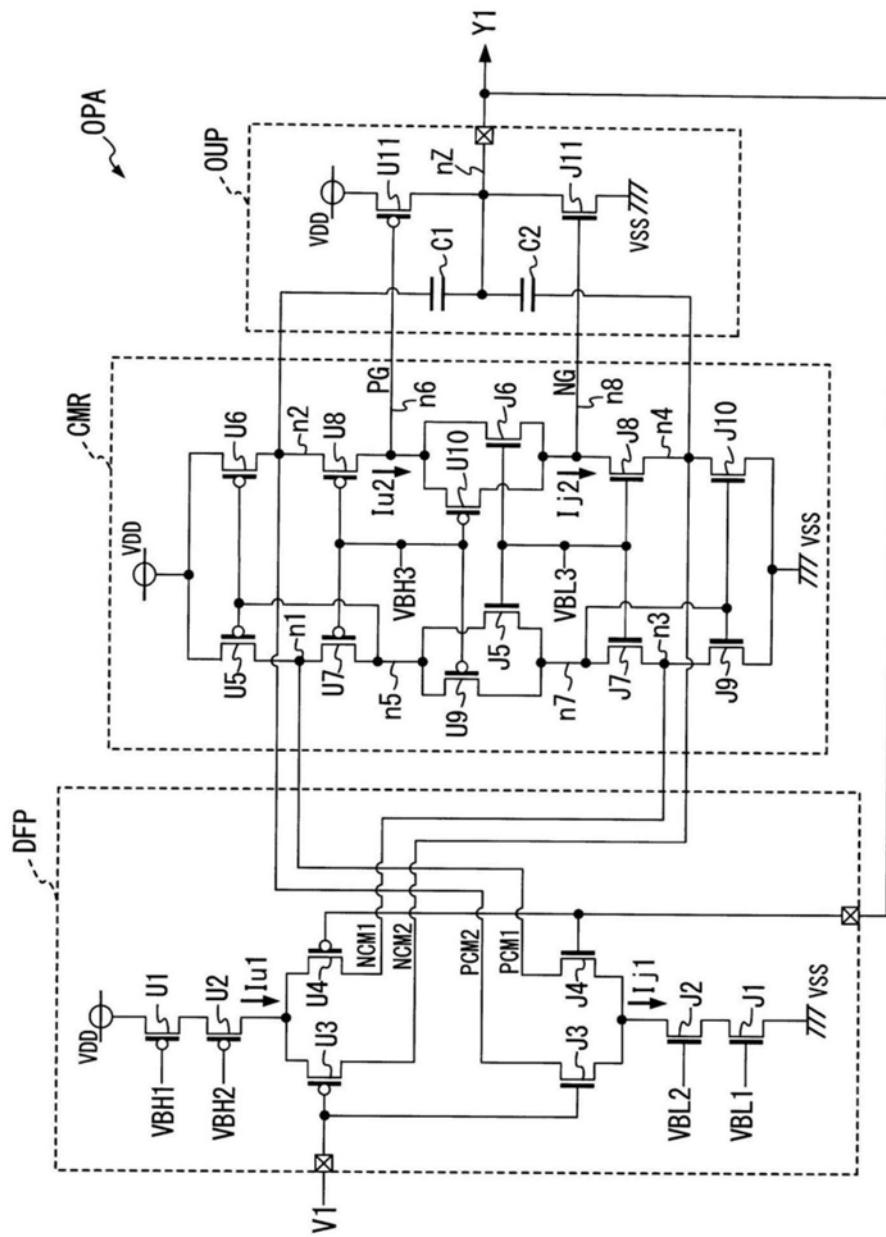

[0020] 图5是表示运算放大器OPA的内部构成的电路图。

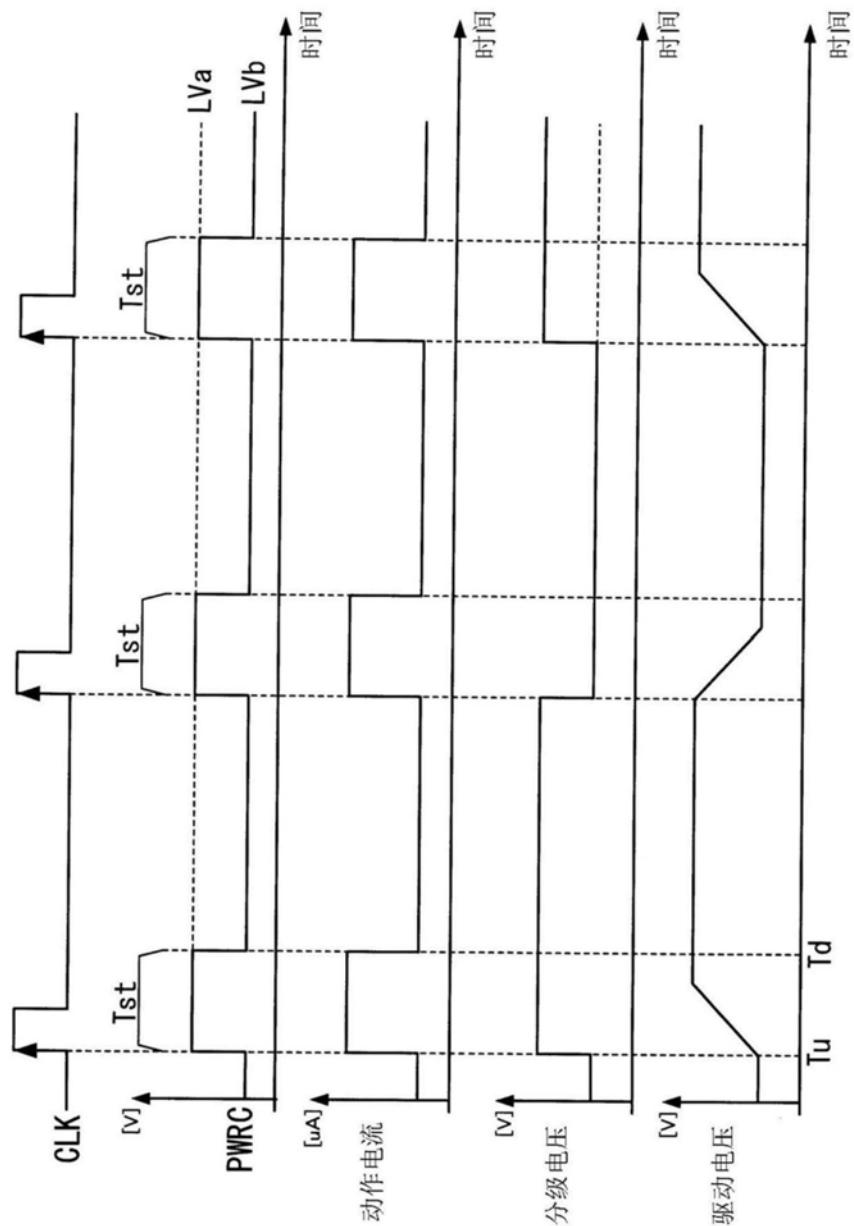

[0021] 图6是表示控制信号生成部SG生成的偏电压控制信号PWRC的一例、与放大器AP1~放大器APr中在放大器AP1的内部流动的动作电流的推移的时序图。

[0022] 图7是详细表示控制部CN、主偏压电路MB及辅偏压电路SB1的内部构成的另一例的

图。

[0023] 图8是详细表示控制部CN、主偏压电路MB及辅偏压电路SB1的内部构成的另一例的图。

[0024] 图9是表示将显示装置20的水平扫描线S1～水平扫描线Sm区分为3个时的区域E1～区域E3的形态的图。

[0025] 图10是表示针对每个区域E1～区域E3而设定的高SR时段Tst的图。

[0026] 图11是表示将控制部CN设置在数据驱动器13的外部时的显示装置100的构成的方块图。

[0027] 符号的说明

[0028] 13:数据驱动器

[0029] 133:输出放大器部

[0030] 1330:偏电压生成部

[0031] AP1～APn:放大器

[0032] CN:控制部

[0033] MB:主偏压电路

[0034] RG1:电压转变时偏压设定寄存器

[0035] RG2:输出恒定时偏压设定寄存器

[0036] SB1～SB3:辅偏压电路

## 具体实施方式

[0037] 以下,参照附图对本发明的实施例进行详细说明。

[0038] 图1是表示包含本发明的显示驱动器的显示装置100的构成的方块图。如图1所示,显示装置100具有:驱动控制部11、扫描驱动器12、数据驱动器13、及显示装置20。

[0039] 显示装置20例如包含有机EL面板或液晶显示面板等。显示装置20中形成有沿二维屏幕的水平方向伸展的水平扫描线S1～水平扫描线Sm(m为2以上的整数)、以及沿二维屏幕的垂直方向伸展的数据线D1～数据线Dn(n为2以上的整数)。在水平扫描线与数据线的各交叉部的区域(由虚线包围的区域)形成有显示单元。

[0040] 再者,水平扫描线S1～水平扫描线Sm连接于扫描驱动器12,数据线D1～数据线Dn连接于数据驱动器13。

[0041] 驱动控制部11从影像信号VD中检测水平同步信号并供给至扫描驱动器12。另外,驱动控制部11基于影像信号VD生成图像数据信号PD,并将其供给至数据驱动器13,所述图像数据信号PD包含以例如8比特的亮度分级表示像素的亮度电平的像素数据片的列。

[0042] 扫描驱动器12在与从驱动控制部11供给的水平同步信号同步的时刻,将水平扫描脉冲依次施加至显示装置20的水平扫描线S1～水平扫描线Sm的各者。

[0043] 数据驱动器13形成在半导体集成电路(integrated circuit, IC)芯片中,且包含数据收集部131、分级电压生成部132及输出放大器部133。

[0044] 数据收集部131以一条水平扫描线为单位即以每n个为单位收集图像数据信号PD中包含的像素数据片。数据收集部131将所收集的n个像素数据片设为像素数据P1～像素数据Pn,并将所述像素数据P1～像素数据Pn在时钟信号CLK的例如上升边沿的时刻供给至分

级电压生成部132。

[0045] 分级电压生成部132将从数据收集部131供给的像素数据P1～像素数据Pn转换成具有与各个亮度电平对应的电压值的分级电压V1～分级电压Vn，并供给至输出放大器部133。

[0046] 图2是表示输出放大器部133的内部构成的一例的方块图。如图2所示，输出放大器部133具有：偏电压生成部1330，包含主偏压电路MB、辅偏压电路SB1～辅偏压电路SB3、及控制部CN；以及放大器AP1～放大器APn。

[0047] 放大器AP1～放大器APn将对分级电压V1～分级电压Vn进行放大所得的n个电压设为驱动电压G1～驱动电压Gn，并将驱动电压G1～驱动电压Gn的各者经由半导体IC芯片的输出端子T1～输出端子Tn而输出。输出端子T1～输出端子Tn分别连接于显示装置20的数据线D1～数据线Dn。

[0048] 再者，放大器AP1～放大器APn的各者例如包含运算放大器，并根据从辅偏压电路SB1～辅偏压电路SB3供给的偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3，设定所述运算放大器的差分段、及电流镜段中流动的动作电流。由此，放大器AP1～放大器APn的各者根据偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3调整自身的输出转换速率。

[0049] 主偏压电路MB生成具有规定的恒定电流的基准电流IB，并将基准电流IB分别供给至辅偏压电路SB1～辅偏压电路SB3。

[0050] 辅偏压电路SB1～辅偏压电路SB3的各者基于基准电流IB，而生成具有与偏电压控制信号PWRC相应的电压值的偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3。

[0051] 辅偏压电路SB1将所生成的偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3供给至当将放大器AP1～放大器APn区分成3个组时的属于第1组的放大器AP1～放大器APr(r为小于n的整数)。辅偏压电路SB2将所述偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3供给至放大器AP1～放大器APn中属于第2组的放大器AP(r+1)～放大器APg(g为大于r且小于n的整数)。辅偏压电路SB3将实施了所述电压值的调整的偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3供给至放大器AP1～放大器APn中的属于第3组的放大器AP(g+1)～放大器APn。

[0052] 控制部CN生成设定偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3的电压值的偏电压控制信号PWRC，并将偏电压控制信号PWRC供给至辅偏压电路SB1～辅偏压电路SB3。

[0053] 以下，对控制部CN、主偏压电路MB、辅偏压电路SB1～辅偏压电路SB3的内部构成进行详细说明。再者，辅偏压电路SB1～辅偏压电路SB3的各者的内部构成相同，因此仅抽取所述辅偏压电路SB1进行说明。

[0054] 图3是表示控制部CN、主偏压电路MB及辅偏压电路SB1的内部构成的一例的图。

[0055] 控制部CN包含电压转变时偏压设定寄存器RG1、输出恒定时偏压设定寄存器RG2、切换时刻寄存器CRG及控制信号生成部SG。

[0056] 电压转变时偏压设定寄存器RG1中存储有偏电压信息Bs1，所述偏电压信息Bs1表示用以在驱动电压G的上升或下降时段中使放大器AP1～放大器APr高转换速率化的偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3的电压值。电压转变时偏压设定寄存器RG1将偏电压信息Bs1供给至控制信号生成部SG。

[0057] 输出恒定时偏压设定寄存器RG2中存储有偏电压信息Bs2,所述偏电压信息Bs2表示用以在驱动电压G的电压值的转变量成为小于规定值的输出恒定段中使放大器AP1～放大器Apr低耗电化的偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3的电压值。输出恒定时偏压设定寄存器RG2将偏电压信息Bs2供给至控制信号生成部SG。

[0058] 切换时刻寄存器CRG中存储有表示对偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3的电压值进行切换的时刻的切换时刻信息TG。切换时刻寄存器CRG将切换时刻信息TG供给至控制信号生成部SG。

[0059] 控制信号生成部SG基于时钟信号CLK、切换时刻信息TG、偏电压信息Bs1及偏电压信息Bs2,生成偏电压控制信号PWRC。

[0060] 即,控制信号生成部SG在时钟信号CLK的例如上升边沿时刻,首先收集偏电压信息Bs1及偏电压信息Bs2中的偏电压信息Bs1。接着,控制信号生成部SG生成偏电压控制信号PWRC,并将偏电压控制信号PWRC供给至所述辅偏压电路SB1,其中,所述偏电压控制信号PWRC用以使具有偏电压信息Bs1所表示的电压值的偏电压(VBH1～VBH3、VBL1～VBL3)在辅偏压电路SB1侧生成。这里,控制信号生成部SG在切换时刻信息TG所表示的时刻收集偏电压信息Bs2。而且,控制信号生成部SG生成偏电压控制信号PWRC,并将偏电压控制信号PWRC供给至所述辅偏压电路SB1,其中,所述偏电压控制信号PWRC用以使具有偏电压信息Bs2所表示的电压值的偏电压(VBH1～VBH3、VBL1～VBL3)在辅偏压电路SB1侧生成。

[0061] 再者,偏电压控制信号PWRC例如,如图3所示包含指定辅偏压电路SB1中包含的P通道金属氧化物半导体(Metal-Oxide-Semiconductor,MOS)型的晶体管Q3～晶体管Q5中设定成导通状态的晶体管的数量的信息。

[0062] 主偏压电路MB具有电流源G1,所述电流源G1接受电源电位VDD而生成基准电流IB,并将基准电流IB经由节点L1供给至辅偏压电路SB1。

[0063] 辅偏压电路SB1具有:包含P通道MOS型的晶体管Q1～晶体管Q5及开关电路SW1～开关电路SW3的电压调整部VCN、P通道MOS型的晶体管Q6～晶体管Q12、以及N通道MOS型的晶体管R1～晶体管R10。

[0064] 晶体管R1的自身的漏极端及栅极端连接于节点L1与晶体管R2的栅极端。对晶体管R1及晶体管R2各自的源极端施加有接地电位VSS。晶体管R2的漏极端经由节点L2而与电压调整部VCN连接。

[0065] 根据所述构成,晶体管R2使对应于基准电流IB的电流I2在节点L2中流动。

[0066] 电压调整部VCN的晶体管Q1及晶体管Q2各自的栅极端连接于节点L2。对晶体管Q1及晶体管Q2各自的源极端施加有电源电位VDD。晶体管Q2的漏极端经由节点L3而连接于晶体管R3的漏极端及栅极端。对晶体管R3的源极端施加有接地电位VSS。

[0067] 根据所述构成,晶体管Q2将对应于所述电流I2的电流I3送出至节点L3,由此,在所述节点L3生成基准偏电压VQ。

[0068] 对电压调整部VCN的晶体管Q3～晶体管Q5的各者的源极端施加有电源电位VDD,并将各个漏极端连接于节点L3。

[0069] 开关电路SW1根据偏电压控制信号PWRC设定成将电源电位VDD供给至晶体管Q3的栅极端的状态(称为断开状态)、或将节点L2连接于晶体管Q3的栅极端的状态(称为接通状态)。开关电路SW2根据偏电压控制信号PWRC设定成将电源电位VDD供给至晶体管Q4的栅极

端的状态(称为断开状态)、或将节点L2连接于晶体管Q4的栅极端的状态(称为接通状态)。开关电路SW3根据偏电压控制信号PWRC设定成将电源电位VDD供给至晶体管Q5的栅极端的状态(称为断开状态)、或将节点L2连接于晶体管Q5的栅极端的状态(称为接通状态)。

[0070] 晶体管Q3仅在开关电路SW1成为接通状态的情况下成为导通状态,并将对应于所述电流I2的电流Ic送出至节点L3。晶体管Q4仅在开关电路SW2成为接通状态的情况下成为导通状态,并将对应于所述电流I2的电流Ic送出至节点L3。晶体管Q5仅在开关电路SW3成为接通状态的情况下成为导通状态,并将对应于所述电流I2的电流Ic送出至节点L3。

[0071] 根据所述构成,电压调整部VCN将使对应于基准电流IB的电流I3、与从根据偏电压控制信号PWRC而设定成导通状态的晶体管Q3～晶体管Q5送出的电流Ic合成所得的合成电流It送出至节点L3。通过将合成电流It送出至节点L3而生成的基准偏电压VQ的电压值得以调整。

[0072] 例如,在电压调整部VCN接收到将晶体管Q3～晶体管Q5中设定成导通状态的晶体管的数量表示为零的偏电压控制信号PWRC的情况下,在节点L3中流动的合成电流It成为电流I3。

[0073] 另外,在电压调整部VCN接收到将晶体管Q3～晶体管Q5中设定成导通状态的晶体管的数量表示为“2”的偏电压控制信号PWRC的情况下,例如仅将晶体管Q3～晶体管Q5中的晶体管Q3及晶体管Q4设定成导通状态。由此,合成电流It成为将电流I3加上从晶体管Q3及晶体管Q4的各者送出的电流Ic而成的电流( $I3+2 \cdot Ic$ )。

[0074] 即,图3所示的电压调整部VCN根据偏电压控制信号PWRC而以4个阶段调整基准偏电压VQ的电压值,由此生成具有偏电压信息Bs1或偏电压信息Bs2所表示的电压值的基准偏电压VQ。

[0075] 在图3中,晶体管R4～晶体管R7的各者的栅极端连接于所述晶体管R3的栅极端及节点L3,对晶体管R4～晶体管R7的各者的源极端施加有接地电位VSS。晶体管R4的漏极端经由节点L4而连接于晶体管Q6的栅极端及漏极端。晶体管R5的漏极端经由节点L5而连接于晶体管Q7的栅极端及漏极端。晶体管R6的漏极端经由节点L6而连接于晶体管Q8的栅极端及漏极端。对晶体管Q6～晶体管Q8的各者的源极端施加有电源电位VDD。

[0076] 晶体管R7的漏极端连接于晶体管Q9的漏极端、及晶体管Q9～晶体管Q12的各者的栅极端。对晶体管Q9～晶体管Q12的各者的源极端施加有电源电位VDD。晶体管Q10的漏极端经由节点L7而连接于晶体管R8的栅极端及漏极端。晶体管Q11的漏极端经由节点L8而连接于晶体管R9的栅极端及漏极端。晶体管Q12的漏极端经由节点L9而连接于晶体管R10的栅极端及漏极端。对晶体管R8～晶体管R10的各者的源极端施加有接地电位VSS。

[0077] 在所述包含晶体管R4及晶体管Q6的电路中,晶体管R4使与供给至自身的栅极端的基准偏电压VQ对应的电流流到节点L4。由此,在此节点L4生成的电压作为偏电压VBH1而供给至放大器AP1～放大器APr。

[0078] 在包含晶体管R5及晶体管Q7的电路中,晶体管R5使与供给至自身的栅极端的基准偏电压VQ对应的电流流到节点L5。由此,在此节点L5生成的电压作为偏电压VBH2而供给至放大器AP1～放大器APr。

[0079] 在包含晶体管R6及晶体管Q8的电路中,晶体管R6使与供给至自身的栅极端的基准偏电压VQ对应的电流流到节点L6中。由此,在此节点L6生成的电压作为偏电压VBH3而供给

至放大器AP1～放大器APr。

[0080] 再者,晶体管R7使与供给至自身的栅极端的基准偏电压VQ对应的电流经由晶体管Q9而流动。由此,与此基准偏电压VQ对应的电流从晶体管Q10～晶体管Q12的各者的漏极端被分别送出至节点L7～节点L9。

[0081] 此时,晶体管Q10将对应于基准偏电压VQ的电流送出至节点L7,由此在此节点L7生成的电压作为偏电压VBL1而供给至放大器AP1～放大器APr。另外,晶体管Q11将对应于基准偏电压VQ的电流送出至节点L8,由此在此节点L8生成的电压作为偏电压VBL2而供给至放大器AP1～放大器APr。另外,晶体管Q12将对应于基准偏电压VQ的电流送出至节点L9,由此在此节点L9生成的电压作为偏电压VBL3而供给至放大器AP1～放大器APr。

[0082] 放大器AP1～放大器APr的各者具有相同的内部构成。因此,以下抽取放大器AP1～放大器APr中的放大器AP1,对其内部构成进行详细说明。

[0083] 图4是概略地表示放大器AP1的内部构成的方块图。如图4所示,放大器AP1包含运算放大器OPA及输出开关OSW。

[0084] 运算放大器OPA包含连接有输出端与反相输入端的、所谓的电压跟随器(voltage follower),将以增益1对在反相输入端接受的分级电压V1进行放大所得的输出电压Y1供给至输出开关OSW。运算放大器OPA根据偏电压VBH1～偏电压VBH3及偏电压VBL1～偏电压VBL3来调整自身的动作电流,由此变更输出转换速率。输出开关OSW仅在接通状态时将输出电压Y1作为驱动电压G1而从半导体IC芯片的输出端子T1中输出。

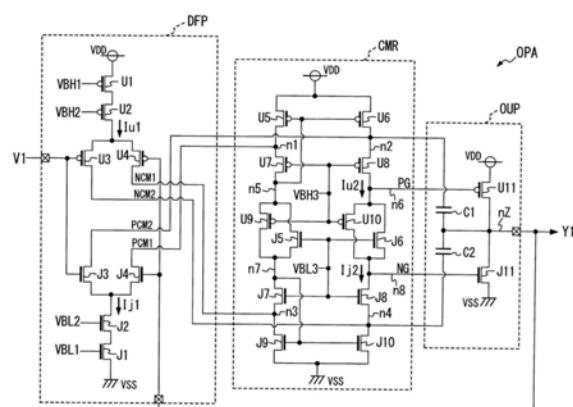

[0085] 图5表示运算放大器OPA的内部构成的电路图。运算放大器OPA包含差分段DFP、电流镜段CMR、及输出段OUP。

[0086] 差分段DFP包含P通道MOS型晶体管U1～晶体管U4、及N通道MOS型晶体管J1～晶体管J4。

[0087] 对晶体管U1的源极端施加有电源电位VDD,对栅极端供给有偏电压VBH1。晶体管U1的漏极端连接于晶体管U2的源极端。对晶体管U2的栅极端供给有偏电压VBH2,漏极端连接于晶体管U3及晶体管U4的各者的源极端。

[0088] 根据所述构成,晶体管U1及晶体管U2基于电源电位VDD,生成具有与偏电压VBH1及偏电压VBH2相应的电流值的动作电流Iu1,并将动作电流Iu1供给至晶体管U3及晶体管U4。

[0089] 晶体管U3及晶体管U4生成以在各自的栅极端接受到的分级电压V1与所述运算放大器OPA的输出即输出电压Y1的电压比对从晶体管U2供给的动作电流Iu1进行2分割而得的电流作为电流NCM1及电流NCM2。晶体管U3及晶体管U4将电流NCM1及电流NCM2经由各自的漏极端而供给至电流镜段CMR的节点n3及节点n4。

[0090] 即,晶体管U3将对应于分级电压V1的电压值的电流NCM2供给至电流镜段CMR的节点n4。晶体管U4将对应于输出电压Y1的电压值的电流NCM1供给至电流镜段CMR的节点n3。

[0091] 对晶体管J1的源极端施加有接地电位VSS,对栅极端供给有偏电压VBL1。晶体管J1的漏极端连接于晶体管J2的源极端。对晶体管J2的栅极端供给有偏电压VBL2,漏极端连接于晶体管J3及晶体管J4各自的源极端。

[0092] 根据所述构成,晶体管J1及晶体管J2生成具有与偏电压VBL1及偏电压VBL2相应的电流值的动作电流Ij1,并将动作电流Ij1从晶体管J3及晶体管J4的源极端引出。

[0093] 晶体管J3及晶体管J4生成以在各自的栅极端接受到的分级电压V1与输出电压Y1

的电压比对动作电流Ij1进行2分割而得的电流作为电流PCM1及电流PCM2。晶体管J3及晶体管J4将电流PCM1及电流PCM2经由各自的漏极端而从电流镜段CMR的节点n1及节点n2引出。

[0094] 即，晶体管J3将对应于分级电压V1的电流PCM2从电流镜段CMR的节点n2引出，并将电流PCM2供给至晶体管J2的漏极端。晶体管J4将对应于输出电压Y1的电流PCM1从电流镜段CMR的节点n1引出，并将电流PCM1供给至晶体管J2的漏极端。

[0095] 再者，在差分段DFP中，根据偏电压VBH1及偏电压VBH2调整所述动作电流Iu1的电流值，进而，根据偏电压VBL1及偏电压VBL2调整所述动作电流Ij1的电流值。由此，例如偏电压VBH1及偏电压VBH2的电压值越低，则越大的电流被供给至电流镜段CMR的节点n3及节点n4。另外，例如偏电压VBL1及偏电压VBL2的电压值越高，则越大的电流从电流镜段CMR的节点n1及节点n2引出。

[0096] 电流镜段CMR包含P通道MOS型晶体管U5～晶体管U10、以及N通道MOS型晶体管J5～晶体管J10。

[0097] 对晶体管U5及晶体管U6各自的源极端施加有电源电位VDD，且各个栅极端彼此连接。晶体管U5的漏极端经由节点n1而连接于晶体管U7的源极端。晶体管U6的漏极端经由节点n2而连接于晶体管U8的源极端。

[0098] 对晶体管U7及晶体管U8的栅极端均施加有偏电压VBH3。晶体管U7的漏极端经由节点n5而连接于所述晶体管U5及晶体管U6各自的栅极端、晶体管U9的源极端、晶体管J5的漏极端。

[0099] 晶体管U8的漏极端经由作为高电位侧的驱动节点的节点n6而连接于晶体管U10的源极端及晶体管J6的漏极端。

[0100] 对晶体管U9及晶体管U10各自的栅极端施加有偏电压VBH3。晶体管U9的漏极端及晶体管J5的源极端经由节点n7而连接于晶体管J7的漏极端。

[0101] 晶体管U10的漏极端及晶体管J6的源极端经由作为低电位侧的驱动节点的节点n8而连接于晶体管J8的漏极端。对晶体管J5及晶体管J6各自的栅极端施加有偏电压VBL3。

[0102] 对晶体管J7及晶体管J8各自的栅极端施加有偏电压VBL3。晶体管J7的源极端经由节点n3而连接于晶体管J9的漏极端。晶体管J8的源极端经由节点n4而连接于晶体管J10的漏极端。

[0103] 对晶体管J9及晶体管J10各自的源极端施加有接地电位VSS，所述晶体管J9及晶体管J10各自的栅极端连接于晶体管J7的漏极端。

[0104] 根据所述构成，在电流镜段CMR中，具有对应于从差分段DFP供给的电流PCM1与电流PCM2的差的电流值的动作电流Iu2在节点n6中流动。进而，在电流镜段CMR中，具有对应于从差分段DFP供给的电流NCM1与电流NCM2的差的电流值的动作电流Ij2在节点n8中流动。

[0105] 由此，在电流镜段CMR中，将对应于电流PCM1与电流PCM2的差的动作电流Iu2供给至作为驱动节点的节点n6，或从节点n6中引出，由此在节点n6生成高电位侧的输出驱动电压PG。电流镜段CMR将此输出驱动电压PG供给至输出段OUP的P通道MOS型晶体管U11的栅极端。

[0106] 另外，在电流镜段CMR中，将对应于电流NCM1与电流NCM2的差的动作电流Ij2供给至作为驱动节点的节点n8，或从节点n8中引出，由此在节点n8生成低电位侧的输出驱动电压NG。电流镜段CMR将此输出驱动电压NG供给至输出段OUP的N通道MOS型晶体管J11的栅极。

端。

[0107] 输出段OUP除了包含所述晶体管U11及晶体管J11之外,还包含相位补偿用的电容器C1及电容器C2。

[0108] 电容器C1的一端连接于电流镜段CMR的节点n2,其另一端连接于输出节点nZ。电容器C2的一端连接于电流镜段CMR的节点n4,其另一端连接于输出节点nZ。

[0109] 对晶体管U11的源极端施加有电源电位VDD,对其栅极端供给有所述的输出驱动电压PG。晶体管U11基于电源电位而生成对应于输出驱动电压PG的电流,并将所生成的电流供给至输出节点nZ,由此使输出节点nZ的电位增加。

[0110] 对晶体管J11的源极端施加有接地电位VSS,对其栅极端供给有所述的输出驱动电压NG。晶体管J11将对应于输出驱动电压NG的电流从输出节点nZ引出,由此使输出节点nZ的电位降低。

[0111] 通过所述晶体管U11及晶体管J11的动作,在输出节点nZ生成输出电压Y1,且输出电压Y1经由输出端子而被输出。此时,所输出的输出电压Y1返回并被供给至差分段DFP的高电位侧的晶体管U4的栅极端、及低电位侧的晶体管J4的栅极端的各者。

[0112] 且说,在电流镜段CMR中,根据偏电压VBH3及偏电压VBL3而调整在所述作为驱动节点的节点n6及节点n8中流动的动作电流Iu2及动作电流Ij2的电流值。

[0113] 例如,偏电压VBH3的电压值越低,在作为驱动节点的节点n6中流动的动作电流Iu2变得越大,偏电压VBL3的电压值越高,在作为驱动节点的节点n8中流动的动作电流Ij2变得越大。由此,输出驱动电压PG及输出驱动电压NG的上升时间及下降时间变快,所以运算放大器OPA的转换速率变高。

[0114] 另一方面,偏电压VBH3的电压值越高,在作为驱动节点的节点n6中流动的动作电流Iu2变得越小,偏电压VBL3的电压值越低,在作为驱动节点的节点n8中流动的动作电流Ij2变得越小。由此,运算放大器OPA的耗电量下降。

[0115] 总之,运算放大器OPA包含进行以下动作的差分段、电流镜段、输出段及偏压调整部。即,差分段(DFP)生成以所输入的分级电压(V)与所输出的输出电压(Y)的电压比对第1动作电流(Iu1、Ij1)进行2分割而得的第1电流(PCM1、NCM1)及第2电流(PCM2、NCM2)。电流镜段(CMR)将对应于第1电流与第2电流的差的第2动作电流(Iu2、Ij2)供给至驱动节点(n6、n8)或从此驱动节点引出,由此在驱动节点生成输出驱动电压(PG、NG)。输出段(OUP)将对应于所述输出驱动电压的输出电流供给至输出节点(nZ)或从输出节点引出,由此在输出节点生成输出电压(Y)。偏压调整部(U1、U2、J1、J2、U8、U10、J6、J8)根据偏电压(VBH1～VBH3、VBL1～VBL3)来调整第1动作电流(Iu1、Ij1)及第2动作电流(Iu2、Ij2)的电流值。

[0116] 接着,对图3所示的构成的动作进行说明。

[0117] 图6是表示图3所示的控制信号生成部SG生成的偏电压控制信号PWRC的一例、与在放大器AP1～放大器APr中的放大器AP1的内部流动的动作电流的推移的时序图。

[0118] 这里,设为在切换时刻寄存器CRG中存储有切换时刻信息TG,所述切换时刻信息TG如图6所示,将从时钟信号CLK的上升边沿的时间点起经过高转换速率时段Tst(以下,也称为高SR时段Tst)的时间点表示为切换时刻。再者,高SR时段Tst是例如在输入至放大器AP的分级电压从表示最低亮度的状态转变成表示最高亮度的状态时,驱动电压G从表示最低亮度的电压值到转变成表示最高亮度的电压值所花费的时间加上规定的裕度(margin)时段

而得到的时段。

[0119] 在图6中,控制信号生成部SG首先从时钟信号CLK的上升边沿时间点Tu起,经过切换时刻信息TG所示的高SR时段Tst,生成以下的偏电压控制信号PWRC,并将偏电压控制信号PWRC供给至辅偏压电路SB1。即,控制信号生成部SG生成偏电压控制信号PWRC,所述偏电压控制信号PWRC用以使具有偏电压信息Bs1所表示的电压值、即使各放大器高转换速率化的电压值的偏电压在辅偏压电路SB1侧生成。例如,控制信号生成部SG生成表示将3个晶体管Q3～晶体管Q5全部设定成导通状态的具有信号电平LVa的偏电压控制信号PWRC,并将偏电压控制信号PWRC供给至辅偏压电路SB1。

[0120] 根据所述偏电压控制信号PWRC,辅偏压电路SB1的电压调整部VCN将合成电流It(I3+3·Ic)送出至节点L3,由此调整基准偏电压VQ的电压值。辅偏压电路SB1基于实施了电压值的调整的基准偏电压VQ,而生成具有与偏电压信息Bs1所示的电压值对应的电压值的偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3,并将偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3供给至放大器AP1～放大器APr。

[0121] 而且,在经过了所述高SR时段Tst的时间点Td以后到接下来的时钟信号CLK的上升边沿的时间点的期间,控制信号生成部SG生成以下的偏电压控制信号PWRC。即,控制信号生成部SG生成偏电压控制信号PWRC,所述偏电压控制信号PWRC用以使具有偏电压信息Bs2所表示的电压值、即使各放大器低耗电化的电压值的偏电压在辅偏压电路SB1侧生成。

[0122] 例如,控制信号生成部SG生成表示将3个晶体管Q3～晶体管Q5全部设定成断开状态的具有信号电平LVb的偏电压控制信号PWRC,并将偏电压控制信号PWRC供给至辅偏压电路SB1。

[0123] 根据所述偏电压控制信号PWRC,辅偏压电路SB1的电压调整部VCN不对通过电流I3而生成的基准偏电压VQ进行变更电压值的调整。因而,此时,辅偏压电路SB1基于仅通过电流I3而生成的基准偏电压VQ,生成具有与偏电压信息Bs2所表示的电压值对应的电压值的偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3,并将偏电压VBH1～偏电压VBH3、偏电压VBL1～偏电压VBL3供给至放大器AP1～放大器APr。

[0124] 根据所述动作,如图6所示,在从时钟信号CLK的上升时间点TU到高SR时段Tst的期间,在各放大器AP的差分段DFP及电流镜段CMR流动的动作电流比在经过高SR时段Tst的时间点以后流动的动作电流大。

[0125] 由此,在要求高速响应的驱动电压的上升或下降区间中,放大器AP的转换速率变高,所以从放大器AP输出的驱动电压的上升或下降时间也变短。

[0126] 另一方面,在从经过了高SR时段Tst的时间点Td到接下来的时钟信号CLK的上升边沿的时间点的期间,在放大器AP的差分段DFP及电流镜段CMR流动的动作电流如图6所示,比在高SR时段Tst内流动的动作电流小。

[0127] 由此,在不要求高速响应的驱动电压的电压值恒定的区间中,放大器AP所消耗的电力变少。

[0128] 因而,根据输出放大器部133,与除设置放大器AP1～放大器APn之外还设置伪放大器,并使此伪放大器动作来检测驱动电压的转变时段的装置相比,能够以小规模的构成,确实地以低电耗且高速地驱动显示装置20。

[0129] 另外,根据图3所示的构成,若在电压转变时偏压设定寄存器RG1及输出恒定时偏

压设定寄存器RG2中事先存储表示所需的偏电压的电压值的信息(Bs1、Bs2)，则在辅偏压电路SB内生成具有所述电压值的偏电压(VBH1～VBH3、VBL1～VBL3)。

[0130] 因而，对于放大器AP1～放大器APn的制品发货前的偏电压的调整变得容易，并且即便在制品发货后，通过适宜地变更所述偏电压的电压值，能够分别对应于省电模式及高速(通常)模式。

[0131] 再者，虽然在所述实施例中，将使各放大器高转换速率化的时段即高SR时段Tst的时段长度固定，但也可适宜变更此高SR时段Tst的时段长度。

[0132] 图7是鉴于所述方面而成的表示控制部CN、主偏压电路MB、及辅偏压电路SB1的内部构成的另一例的图。再者，在图7所示的构成中，省略控制部CN中包含的切换时刻寄存器CRG，取而代之，设置切换判定部CDP。其他构成与图3所示的构成相同。

[0133] 图7所示的切换判定部CDP判定从放大器AP1～放大器APr中输出的驱动电压G1～驱动电压Gr中电压值的转变幅度最大的驱动电压的电压值是否超过规定的参照电压值。这里，在判定为电压值的转变幅度最大的驱动电压的电压值超过了规定的参照电压值的时间点，切换判定部CDP将切换指令信号CGT供给至控制信号生成部SG。根据此切换指令信号CGT，控制信号生成部SG将偏电压控制信号PWRC所表示的电压值从偏电压信息Bs1所示的电压值切换为偏电压信息Bs2所示的电压值。

[0134] 因而，电压值的转变幅度最大的驱动电压的电压值超过参照电压值的时间点成为经过了高SR时段Tst的时间点Td。

[0135] 根据所述构成，与将高SR时段Tst的时段长度固定的情况相比，能够缩短所述时段长度，所以可进一步实现消耗电力的下降。

[0136] 另外，在所述实施例中，切换判定部CDP将电压值的转变幅度最大的驱动电压的电压值与规定的参照电压值进行比较，但也可将所述驱动电压的电压值与输入至输出所述驱动电压的放大器AP的分级电压进行比较。此时，切换判定部CDP在驱动电压的电压值与分级电压的电压值变得相等的时间点、即驱动电压的上升或下降区间结束的时间点，将切换指令信号CGT供给至控制信号生成部SG。

[0137] 且说，在显示装置20中，水平扫描线S1～水平扫描线Sm中施加有水平扫描脉冲的水平扫描线S上的n个显示单元通过从数据驱动器13经由数据线D1～数据线Dn而供给的驱动电压G1～驱动电压Gn而成为驱动对象。

[0138] 因而，对配置于远离数据驱动器13的位置的显示单元施加的驱动电压的上升或下降时间比对配置于靠近数据驱动器13的位置的显示单元施加的驱动电压的上升或下降时间长。

[0139] 因此，使将配置于远离放大器AP1～放大器APn的位置的显示单元设为驱动对象时使用的高SR时段Tst的时段长度比将配置于靠近放大器AP1～放大器APn的位置的显示单元设为驱动对象时使用的高SR时段Tst的时段长度长。

[0140] 图8是鉴于所述方面而成的表示控制部CN、主偏压电路MB、及辅偏压电路SB1的内部构成的另一例的图。再者，在图8所示的构成中，除采用切换时刻寄存器CRG1～切换时刻寄存器CRG3来取代控制部CN中包含的切换时刻寄存器CRG，且采用控制信号生成部SGa来取代控制信号生成部SG这一点以外的其他构成与图3所示的构成相同。

[0141] 因此，以下以切换时刻寄存器CRG1～切换时刻寄存器CRG3、及控制信号生成部SGa

的动作为中心,对其动作进行说明。

[0142] 在切换时刻寄存器CRG1中存储有切换时刻信息TG1,所述切换时刻信息TG1表示对将显示装置20的显示区域例如如图9所示分割成区域E1～区域E3时的属于区域E1的各水平扫描线S进行驱动时使用的高SR时段Tst的时段长度t1。切换时刻寄存器CRG1将此切换时刻信息TG1供给至控制信号生成部SGa。

[0143] 在切换时刻寄存器CRG2中存储有切换时刻信息TG2,所述切换时刻信息TG2表示比所述时段长度t1更长的时段长度t2作为对图9所示的属于区域E2的各水平扫描线S进行驱动时使用的高SR时段Tst的时段长度。切换时刻寄存器CRG2将此切换时刻信息TG2供给至控制信号生成部SGa。

[0144] 在切换时刻寄存器CRG3中存储有切换时刻信息TG3,所述切换时刻信息TG3表示比所述时段长度t2更长的时段长度t3作为图9所示的属于区域E3的各水平扫描线S进行驱动时使用的高SR时段Tst的时段长度。切换时刻寄存器CRG3将此切换时刻信息TG3供给至控制信号生成部SGa。

[0145] 在扫描驱动器12将水平扫描脉冲施加至图9所示的属于区域E1的水平扫描线S的各者的时段中,控制信号生成部SGa从切换时刻信息TG1～切换时刻信息TG3中收集切换时刻信息TG1。而且,如图10所示,为了在具有切换时刻信息TG1所示的时段长度t1的高SR时段Tst的期间使各放大器高转换速率化,控制信号生成部SGa将具有信号电平LVa的偏电压控制信号PWRC供给至电压调整部VCN。

[0146] 另外,在扫描驱动器12将水平扫描脉冲施加至图9所示的属于区域E2的水平扫描线S的各者的时段中,控制信号生成部SGa从切换时刻信息TG1～切换时刻信息TG3中收集切换时刻信息TG2。而且,如图10所示,为了在具有切换时刻信息TG2所示的时段长度t2的高SR时段Tst的期间使各放大器高转换速率化,控制信号生成部SGa将具有信号电平LVa的偏电压控制信号PWRC供给至电压调整部VCN。

[0147] 另外,在扫描驱动器12将水平扫描脉冲施加至图9所示的属于区域E3的水平扫描线S的各者的时段中,控制信号生成部SGa从切换时刻信息TG1～切换时刻信息TG3中收集切换时刻信息TG3。而且,如图10所示,为了在具有切换时刻信息TG3所示的时段长度t3的高SR时段Tst的期间使各放大器高转换速率化,控制信号生成部SGa将具有信号电平LVa的偏电压控制信号PWRC供给至电压调整部VCN。

[0148] 即,以使得在水平扫描线S1～水平扫描线Sm中,对配置于远离放大器AP1～放大器APn的位置的水平扫描线S进行驱动时使用的高SR时段Tst的长度比配置于靠近放大器AP1～放大器APn的位置的水平扫描线S进行驱动时使用的高SR时段Tst的长度长的方式,对高SR时段Tst的长度进行变更。

[0149] 由此,在显示装置20的显示区域的整个区域,能够使驱动电压G1～驱动电压Gn的各者的上升或下降时间均匀。

[0150] 再者,在所述实施例中,各放大器AP通过接受1个分级电压V并将其放大来生成1个驱动电压G。然而,各放大器AP也可采用接受多个分级电压V并将各分级电压V的平均电压生成为1个驱动电压G的多输入型的放大器。

[0151] 再者,在所述实施例中,在半导体IC芯片中包含的数据驱动器13内设置有控制部CN,但如图11所示,也可将所述控制部CN设置在数据驱动器13的外部、即包含数据驱动器13

的半导体IC芯片的外部。

[0152] 总之,本发明的显示驱动器13只要是在对具有N(N为2以上的整数)个数据线的显示装置20进行驱动时,包含以下的数据收集部、分级电压生成部、第1~第N放大器、及偏电压生成部即可。

[0153] 即,数据收集部131接受针对每个像素表示基于影像信号VD的亮度电平的第1~第N像素数据片P1~Pn,并将所述第1~第N像素数据片在时钟信号CLK的边沿时刻输出。分级电压生成部132将从数据收集部输出的第1~第N像素数据片转换成第1~第N分级电压V1~Vn。第1~第N放大器AP1~APn将对第1~第N分级电压进行放大所得的第1~第N驱动电压G1~Gn供给至第1~第N数据线D1~Dn。偏电压生成部1330生成设定第1~第N放大器的各者的动作电流Iu1、Ij1、Iu2、Ij2的电流值的偏电压VBH1~VBH3、VBL1~VBL3并供给至第1~第N放大器。

[0154] 再者,偏电压生成部包含存储第1信息Bs1与第2信息Bs2的寄存器RG1、RG2,所述第1信息Bs1表示第1电压值作为用以将动作电流的电流值设定成第1电流值的偏电压的电压值,所述第2信息Bs2表示第2电压值作为用以将动作电流的电流值设定成比所述第1电流值低的第2电流值的偏电压的电压值。

[0155] 这里,偏电压生成部在从时钟信号CLK的边沿时间点到经过第1时段Tst的时间点Td的期间生成具有第1信息Bs1所表示的第1电压值的偏电压。而且,偏电压生成部在经过第1时段Tst的时间点Td将偏电压的电压值转换成第2信息Bs2所表示的第2电压值。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10