(43) International Publication Date

2 July 2015 (02.07.2015)

(51) International Patent Classification:

**H01L 29/786** (2006.01)    **H01L 27/115** (2006.01)

**G02F 1/1368** (2006.01)    **H01L 29/417** (2006.01)

**H01L 21/28** (2006.01)    **H01L 29/423** (2006.01)

**H01L 21/336** (2006.01)    **H01L 29/49** (2006.01)

**H01L 21/8242** (2006.01)    **H01L 29/788** (2006.01)

**H01L 21/8247** (2006.01)    **H01L 29/792** (2006.01)

**H01L 27/105** (2006.01)    **H01L 51/50** (2006.01)

**H01L 27/108** (2006.01)

(21) International Application Number:

**PCT/IB2014/066898**

(22) International Filing Date:

15 December 2014 (15.12.2014)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

2013-269701 26 December 2013 (26.12.2013)    **JP**

(71) Applicant: **SEMICONDUCTOR ENERGY LABORATORY CO., LTD.** [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa 2430036 (JP).

(72) Inventors: **MIYAIRI, Hidekazu**; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa 2430036 (JP). **SASAGAWA, Shinya**.

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, ID, IL, IN, IR, IS, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

*[Continued on next page]*

(54) Title: SEMICONDUCTOR DEVICE

**FIG. 7B**

(57) Abstract: A semiconductor device that is suitable for miniaturization is provided. A semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first conductor, a second insulator over the second barrier film, and a semiconductor over the second insulator is provided. The first conductor is surrounded by the first barrier film and the second barrier film.

---

**Published:**

— *with international search report (Art. 21(3))*

## DESCRIPTION

**SEMICONDUCTOR DEVICE****TECHNICAL FIELD**

5 [0001]

The present invention relates to an object, a method, or a manufacturing method. In addition, the present invention relates to a process, a machine, manufacture, or a composition of matter. In particular, one embodiment of the present invention relates to a semiconductor device, a display device, a light-emitting device, a power storage device, a storage device, a driving method thereof, or a manufacturing method thereof.

10 [0002]

In this specification and the like, a semiconductor device generally means a device that can function by utilizing semiconductor characteristics. A transistor and a semiconductor circuit are embodiments of semiconductor devices. An arithmetic device, a memory device, an imaging device, an electro-optical device, a power generation device (e.g., a thin film solar cell and an organic thin film solar cell), and an electronic appliance each may include a semiconductor device.

20 **BACKGROUND ART**

[0003]

A technique in which a transistor is formed using a semiconductor material has attracted attention. The transistor is applied to a wide range of electronic devices such as an integrated circuit (IC) or an image display device (also simply referred to as a display device). As semiconductor materials applicable to the transistor, silicon-based semiconductor materials have been widely used, but oxide semiconductors have been attracting attention as alternative materials.

25 [0004]

For example, a technique for formation of a transistor using zinc oxide or an In-Ga-Zn-based oxide semiconductor as an oxide semiconductor is disclosed (see Patent Documents 1 and 2).

30 [0005]

In recent years, demand for integrated circuits in which semiconductor elements such as miniaturized transistors are integrated with high density has risen with increased performance and reductions in the size and weight of electronic appliances.

[Reference]

5 [Patent Document]

[0006]

[Patent Document 1] Japanese Published Patent Application No. 2007-123861

[Patent Document 2] Japanese Published Patent Application No. 2007-096055

10 DISCLOSURE OF INVENTION

[0007]

An object of one embodiment of the present invention is to provide a high-integrated semiconductor device.

[0008]

15 An object of another embodiment of the present invention is to provide a highly reliable semiconductor device.

[0009]

20 Another object of one embodiment of the present invention is to provide a semiconductor device with favorable electrical characteristics. Another object of the present invention is to provide a highly reliable semiconductor device. Another object is to provide a semiconductor device with a novel structure.

[0010]

25 Note that the descriptions of these objects do not disturb the existence of other objects. In one embodiment of the present invention, there is no need to achieve all the objects. Other objects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

MEANS FOR SOLVING THE PROBLEMS

[0011]

30 One embodiment of the present invention is a semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first

conductor, a second insulator over the second barrier film, and a semiconductor over the second insulator. The first conductor is surrounded by the first barrier film and the second barrier film.

[0012]

5 Another embodiment of the present invention is a semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first conductor, a second insulator over the second barrier film, and a semiconductor over the second insulator. The first insulator includes a groove or opening, at least part 10 of the first conductor is provided in the groove or opening, and the first conductor is surrounded by the first barrier film and the second barrier film.

[0013]

15 Another embodiment of the present invention is a semiconductor device including a semiconductor, a first conductor over and in contact with the semiconductor, and a second conductor provided in an opening formed in the semiconductor and the first conductor.

[0014]

20 Another embodiment of the present invention is a semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first conductor, a second insulator over the second barrier film, a semiconductor over the second insulator, a second conductor over and in contact with the semiconductor, and a third conductor that is provided in an opening formed in the semiconductor and the second conductor and is electrically connected to the first 25 element.

[0015]

30 Another embodiment of the present invention is a semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first conductor, a second insulator over the second barrier film, a semiconductor over the second insulator, a second conductor over and in contact with the semiconductor, a third insulator over the semiconductor and the second conductor, and

a third conductor overlapping the semiconductor with the third insulator positioned between the third conductor and the semiconductor. The first insulator includes a groove or opening, at least part of the first conductor is provided in the groove or opening, the first conductor is surrounded by the first barrier film and the second barrier film, and a fourth conductor that is provided in an opening provided in the semiconductor and the second conductor and electrically connected to the first element is included.

[0016]

Another embodiment of the present invention is a semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first conductor, a second insulator over the second barrier film, a semiconductor over the second insulator, a second conductor over and in contact with the semiconductor, a third insulator over the semiconductor and the second conductor, a third conductor overlapping the semiconductor with the third insulator positioned between the third conductor and the semiconductor, a third barrier film over the third conductor, and a second element over the third barrier film. The first conductor is surrounded by the first barrier film and the second barrier film, and a fourth conductor that is provided in an opening provided in the semiconductor and the second conductor and electrically connected to the first element and the second element is included.

[0017]

Another embodiment of the present invention is a semiconductor device including a first element, a first insulator over the first element, a first barrier film over the first insulator, a first conductor over the first barrier film, a second barrier film over the first conductor, a second insulator over the second barrier film, a semiconductor over the second insulator, a second conductor over and in contact with the semiconductor, a third insulator over the semiconductor and the second conductor, a third conductor overlapping the semiconductor with the third insulator positioned between the third conductor and the semiconductor, a third barrier film over the third conductor, and a second element over the third barrier film. The first insulator includes a groove or opening, at least part of the first conductor is provided in the groove or opening, the first conductor is surrounded by the first barrier film and the

second barrier film, and a fourth conductor that is provided in an opening provided in the semiconductor and the second conductor and electrically connected to the first element and the second element is included.

[0018]

5 Furthermore, it is preferable that the first, second, and third barrier films each include at least one of silicon nitride, silicon nitride oxide, aluminum oxide, aluminum oxynitride, gallium oxide, gallium oxynitride, yttrium oxide, yttrium oxynitride, hafnium oxide, and hafnium oxynitride.

[0019]

10 As the second barrier film, an In-Ga-Zn-based oxynitride semiconductor film, an In-Sn-based oxynitride semiconductor film, an In-Ga-based oxynitride semiconductor film, an In-Zn-based oxynitride semiconductor film, a Sn-based oxynitride semiconductor film, an In-based oxynitride semiconductor film, a metal nitride film (e.g., InN or ZnN), or the like can be used, and a stack formed using at least 15 one or more of the above materials may be used.

[0020]

20 Furthermore, it is preferable that the semiconductor device further include an insulating film including oxide between the first barrier film and the semiconductor, and that the insulating film include a region containing oxygen in excess of the stoichiometric composition.

[0021]

The insulating film including oxide preferably includes a region having a hydrogen concentration of lower than  $5 \times 10^{18}$  atoms/cm<sup>3</sup>.

[0022]

25 The semiconductor preferably includes a region having a hydrogen concentration of lower than  $5 \times 10^{18}$  atoms/cm<sup>3</sup>.

[0023]

30 It is preferable that the second element be a transistor and the third insulator be a gate insulating film of the transistor. The gate insulating film preferably has a region with a hydrogen concentration of lower than  $5 \times 10^{18}$  atoms/cm<sup>3</sup>.

[0024]

It is preferable that the subthreshold swing value of the transistor be greater than or equal to 60 mV/dec. and less than or equal to 100 mV/dec.

[0025]

According to one embodiment of the present invention, a semiconductor device 5 that is suitable for miniaturization can be provided.

[0026]

A semiconductor device with favorable electrical characteristics can be provided. Furthermore, a highly reliable semiconductor device can be provided. A semiconductor device or the like with a novel structure can be provided. Note that the 10 description of these effects does not disturb the existence of other effects. One embodiment of the present invention does not necessarily achieve all the objects listed above. Other effects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

## 15 BRIEF DESCRIPTION OF DRAWINGS

[0027]

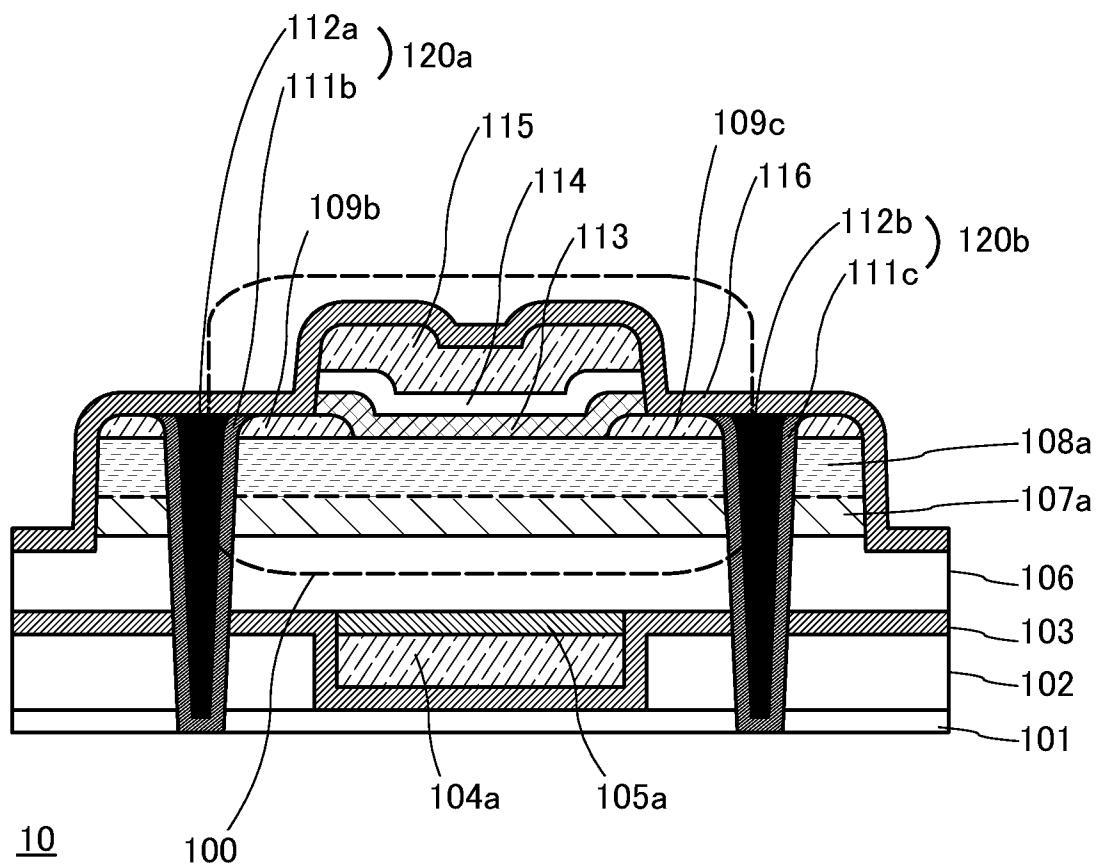

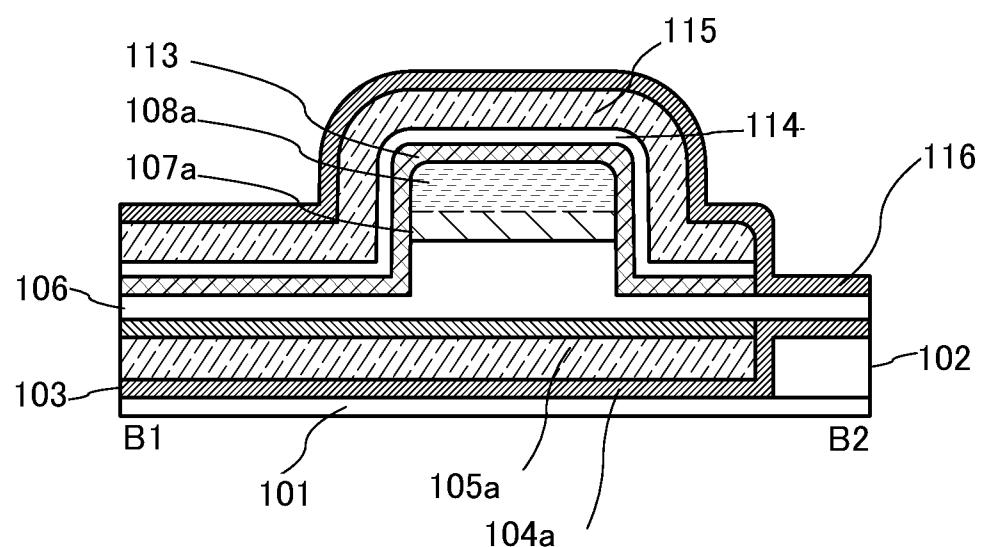

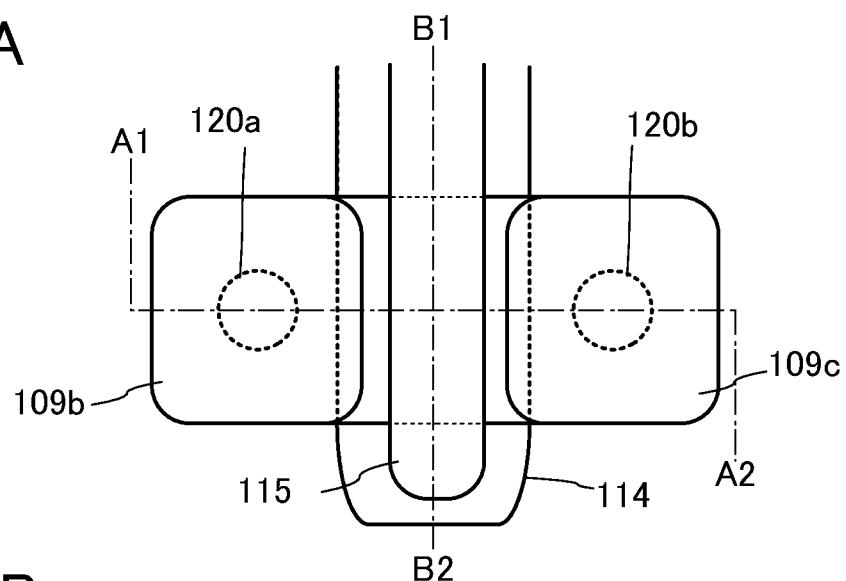

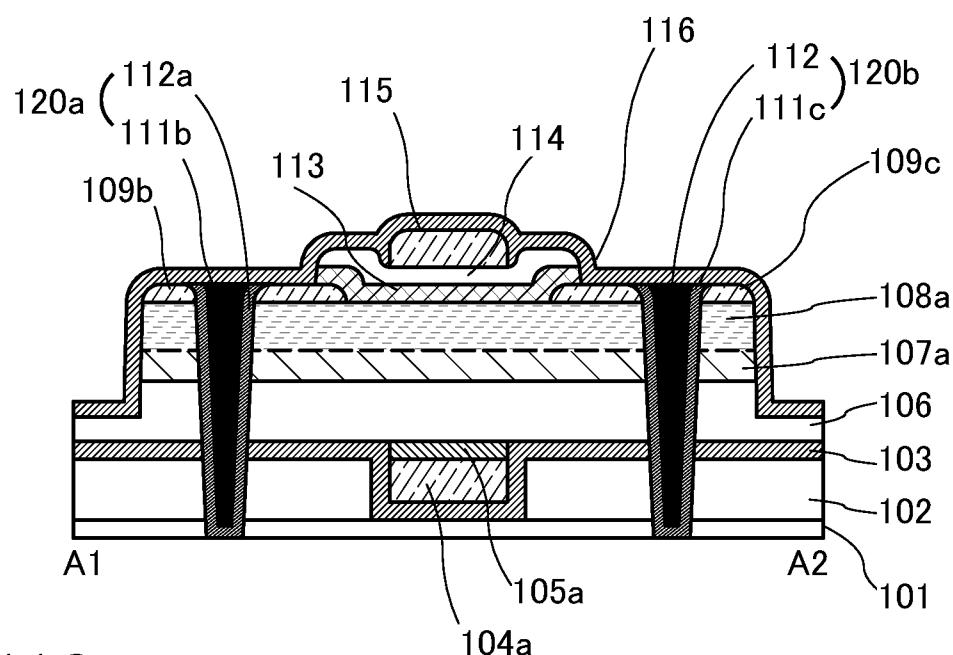

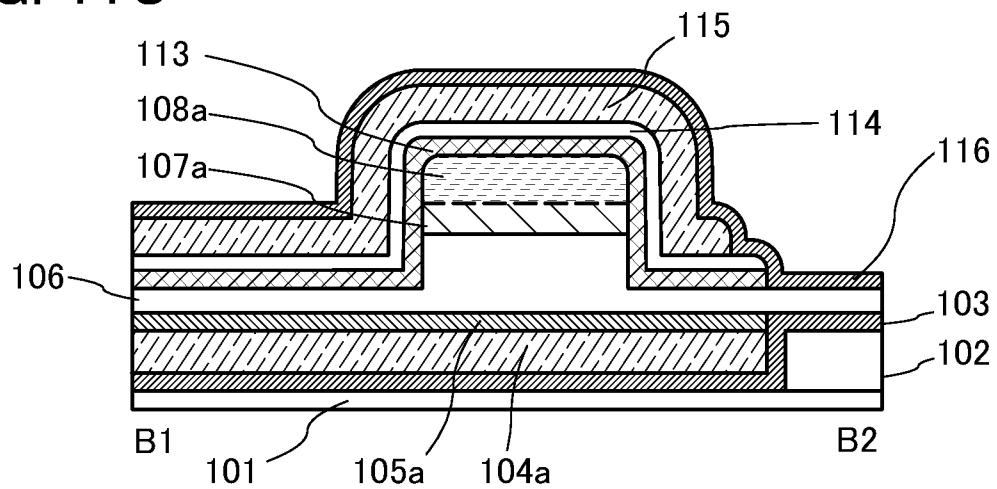

FIG. 1 illustrates a structure example of a semiconductor device of an embodiment.

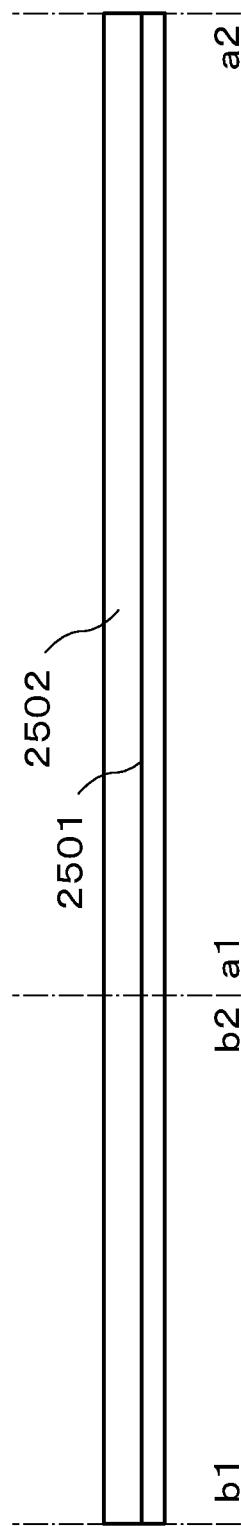

FIG. 2 illustrates a stacked-layer structure included in a semiconductor device 20 of an embodiment.

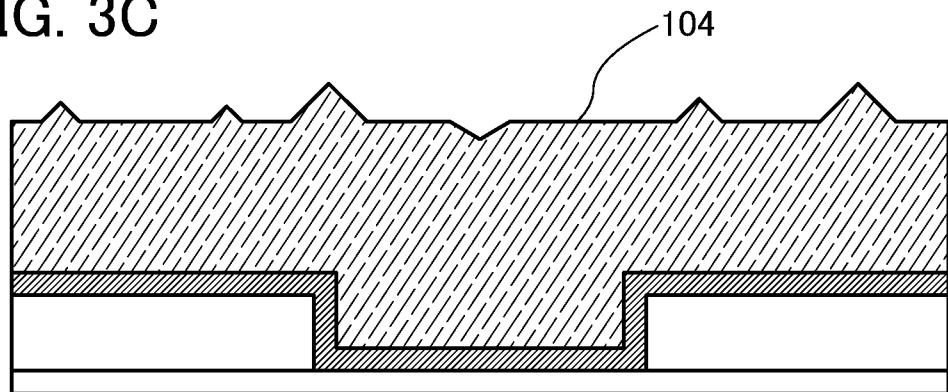

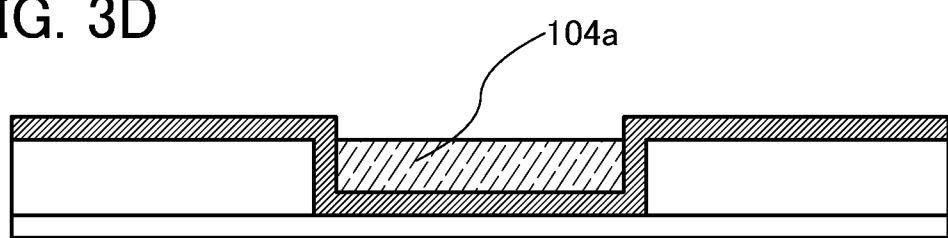

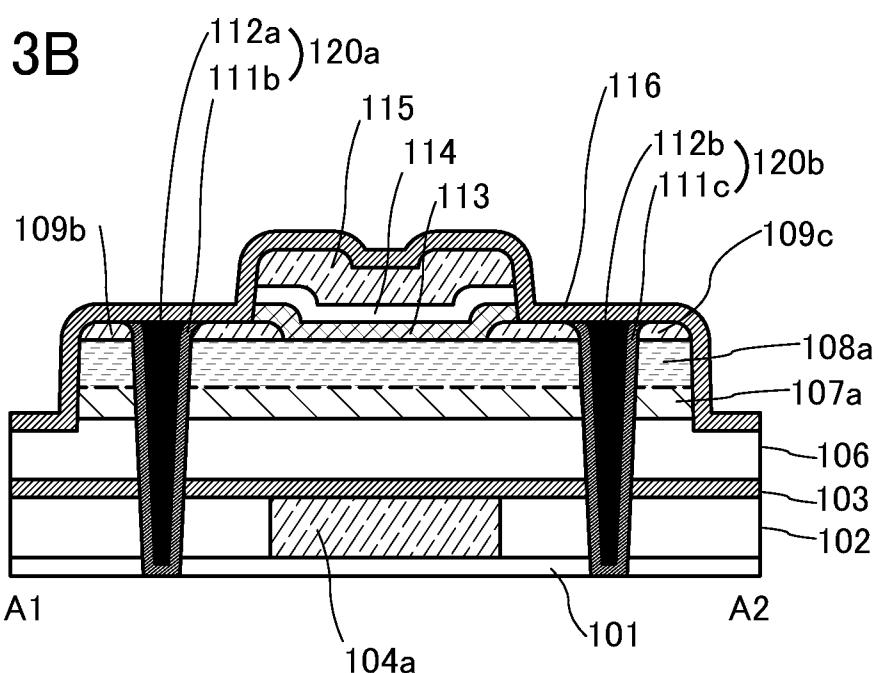

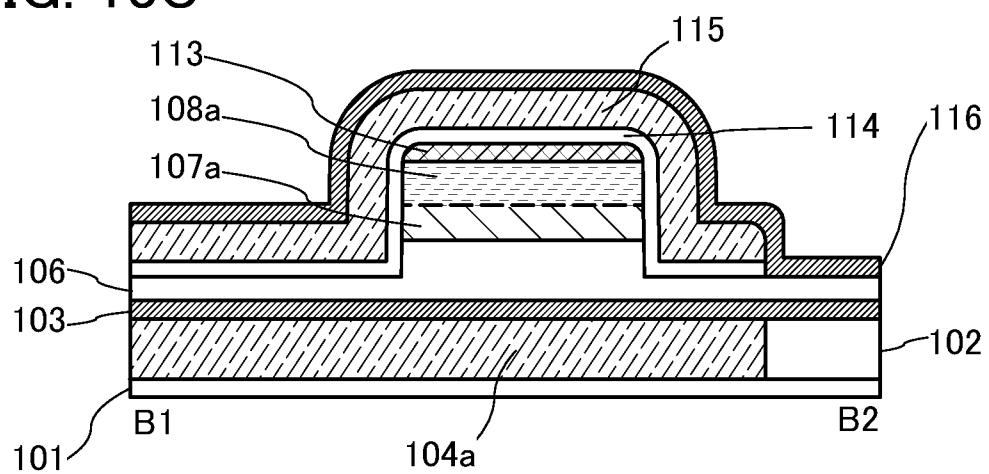

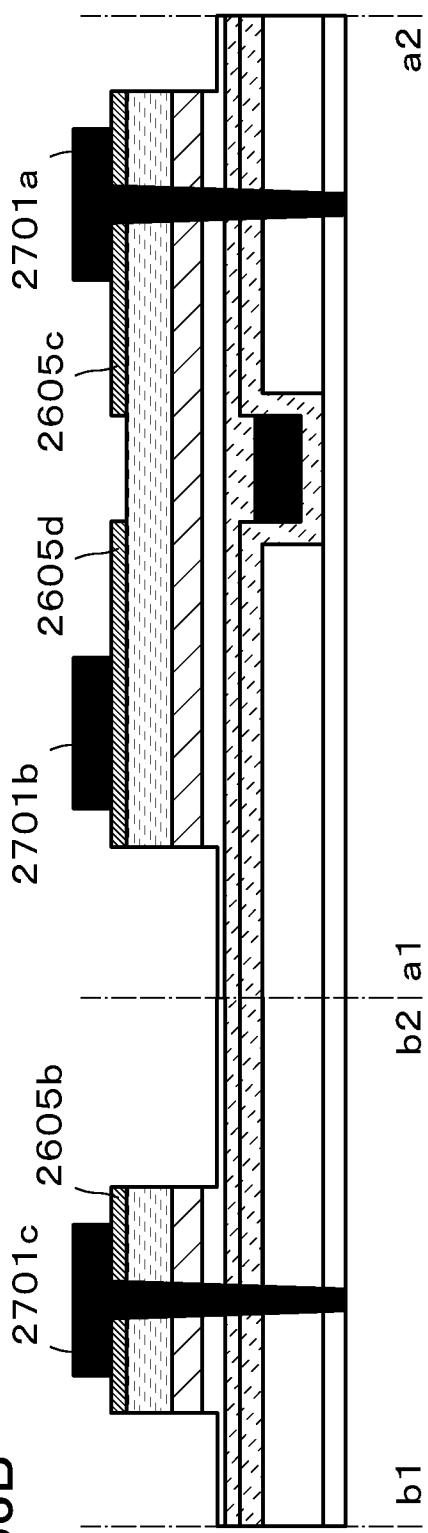

FIGS. 3A to 3D illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

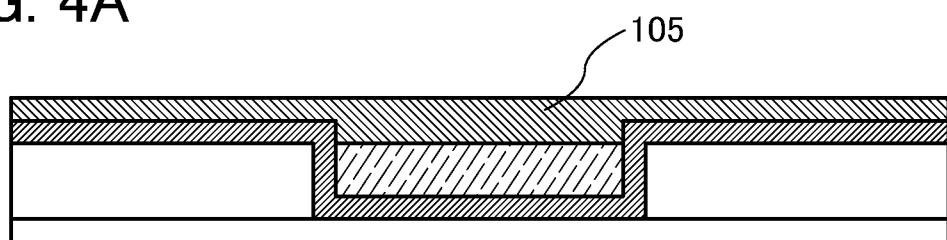

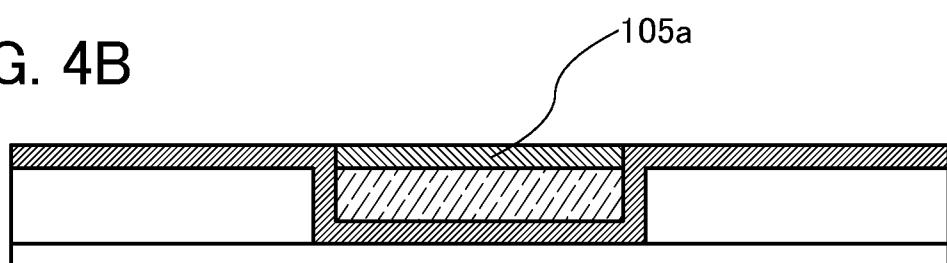

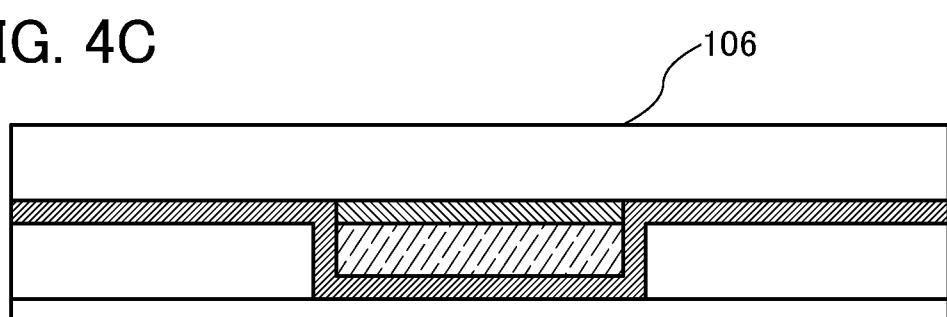

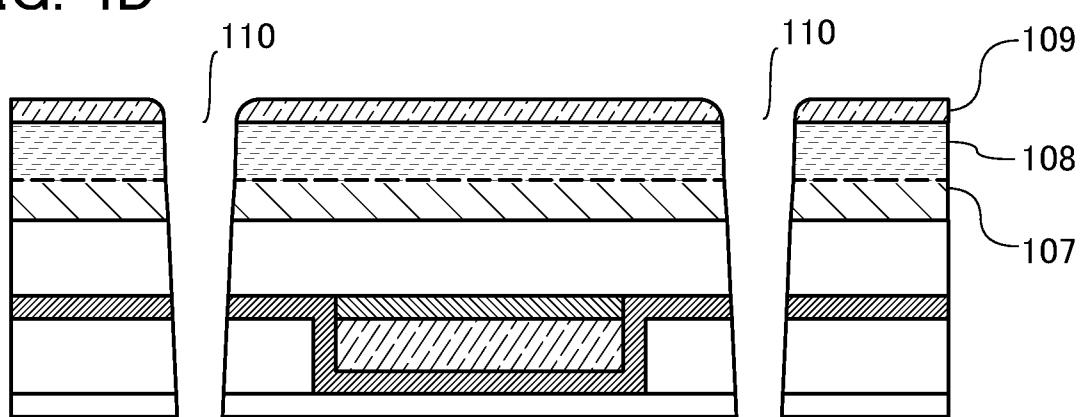

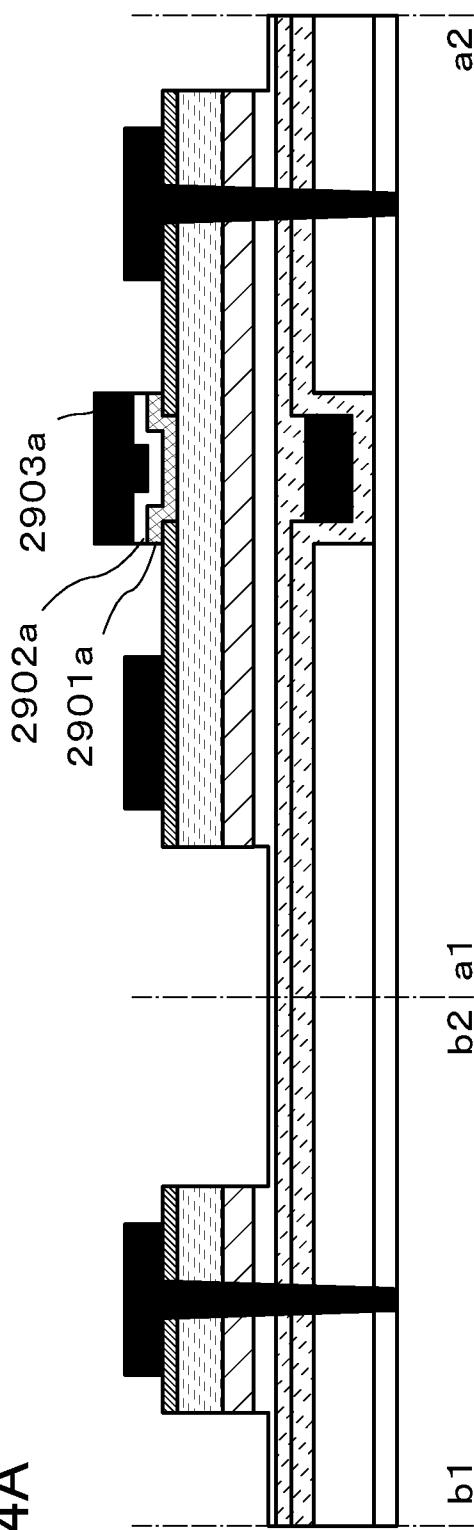

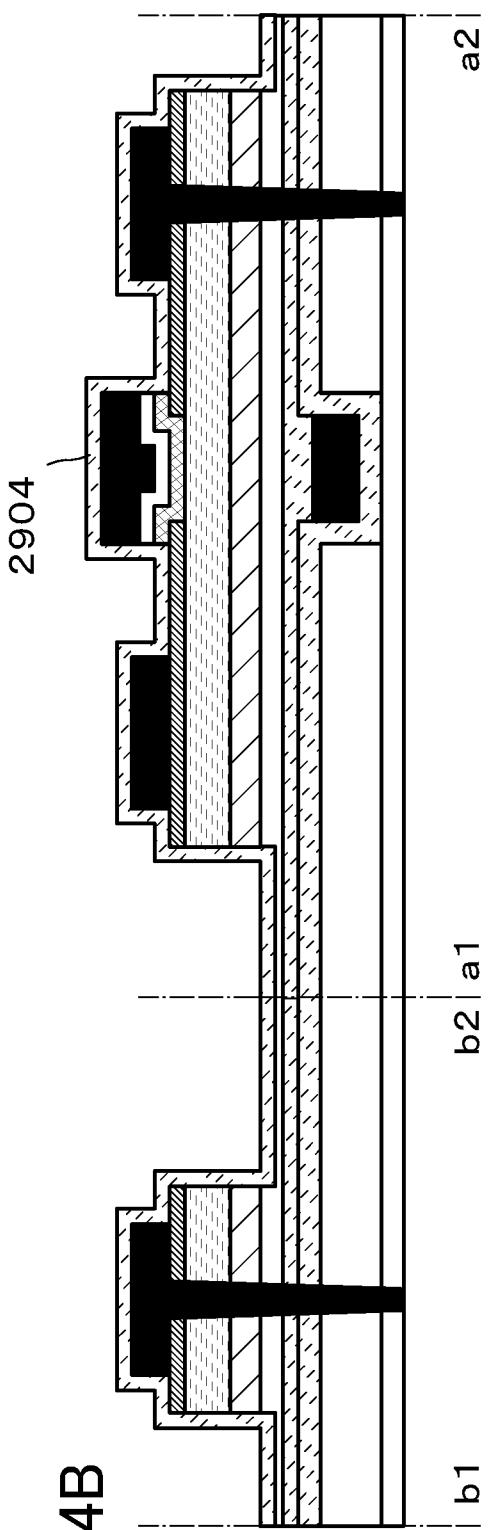

FIGS. 4A to 4D illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

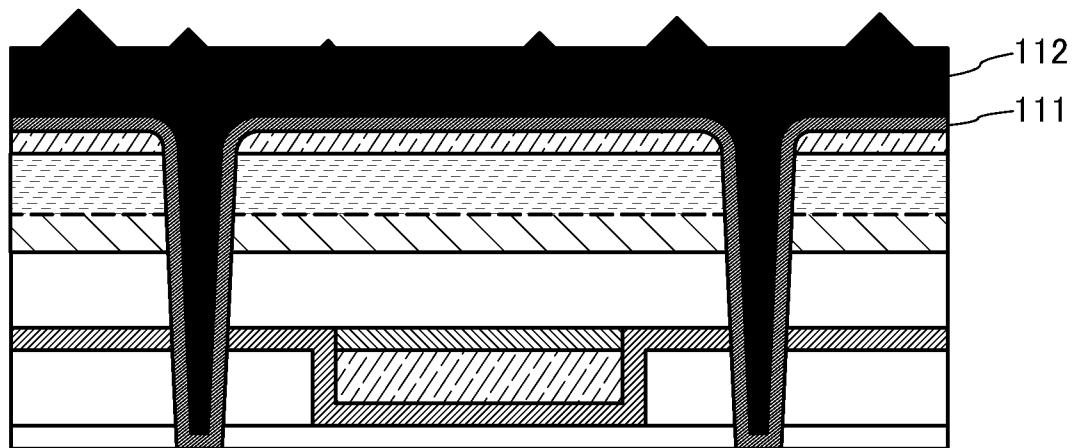

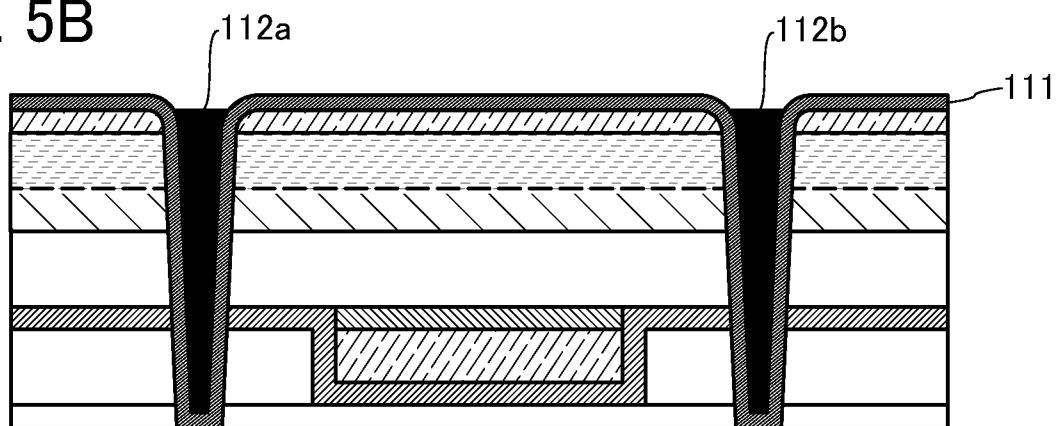

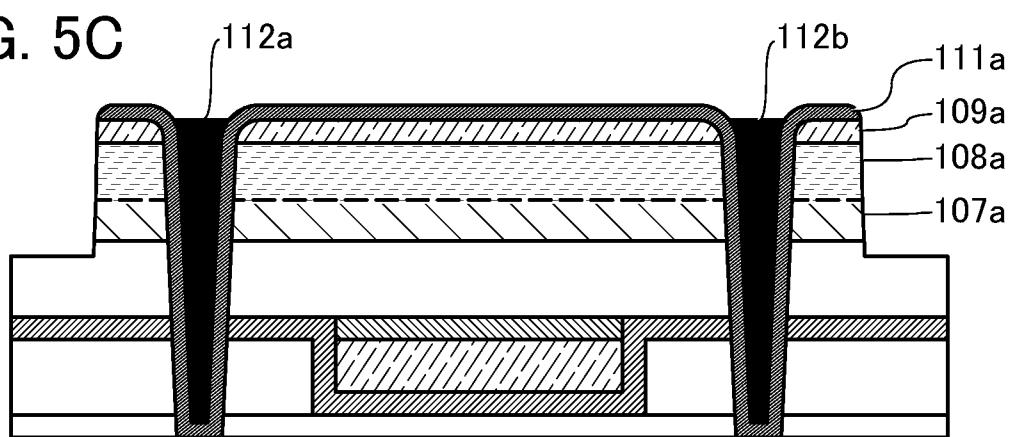

FIGS. 5A to 5C illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

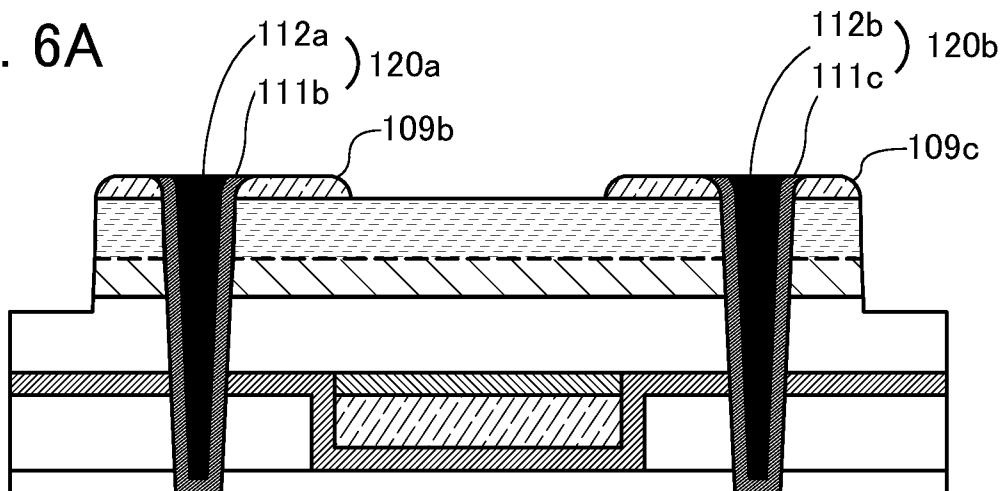

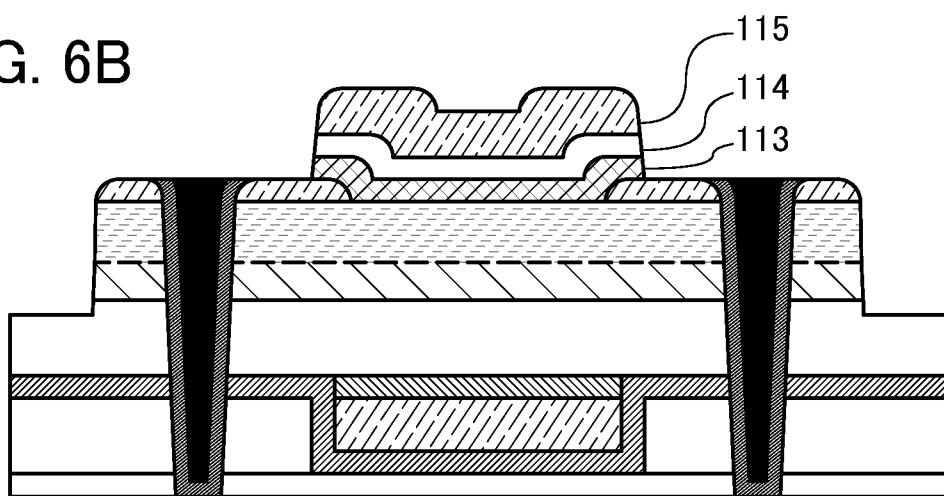

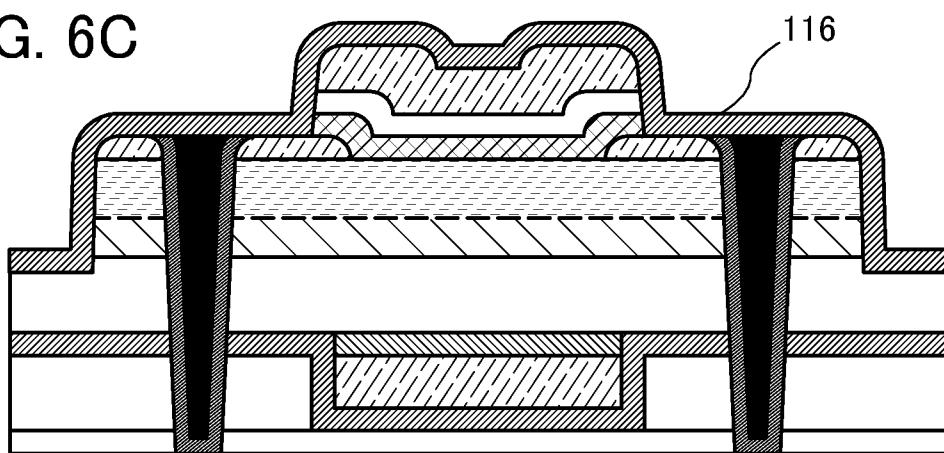

FIGS. 6A to 6C illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

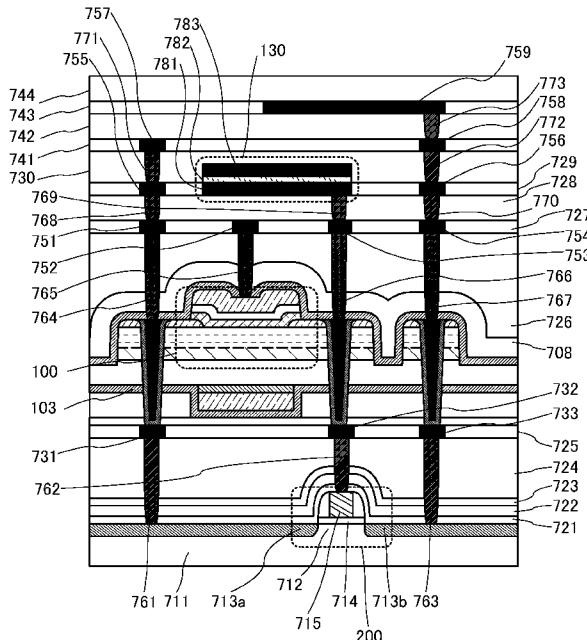

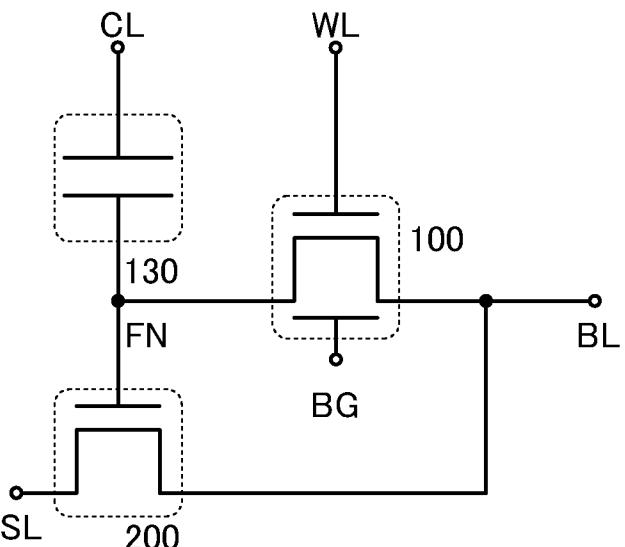

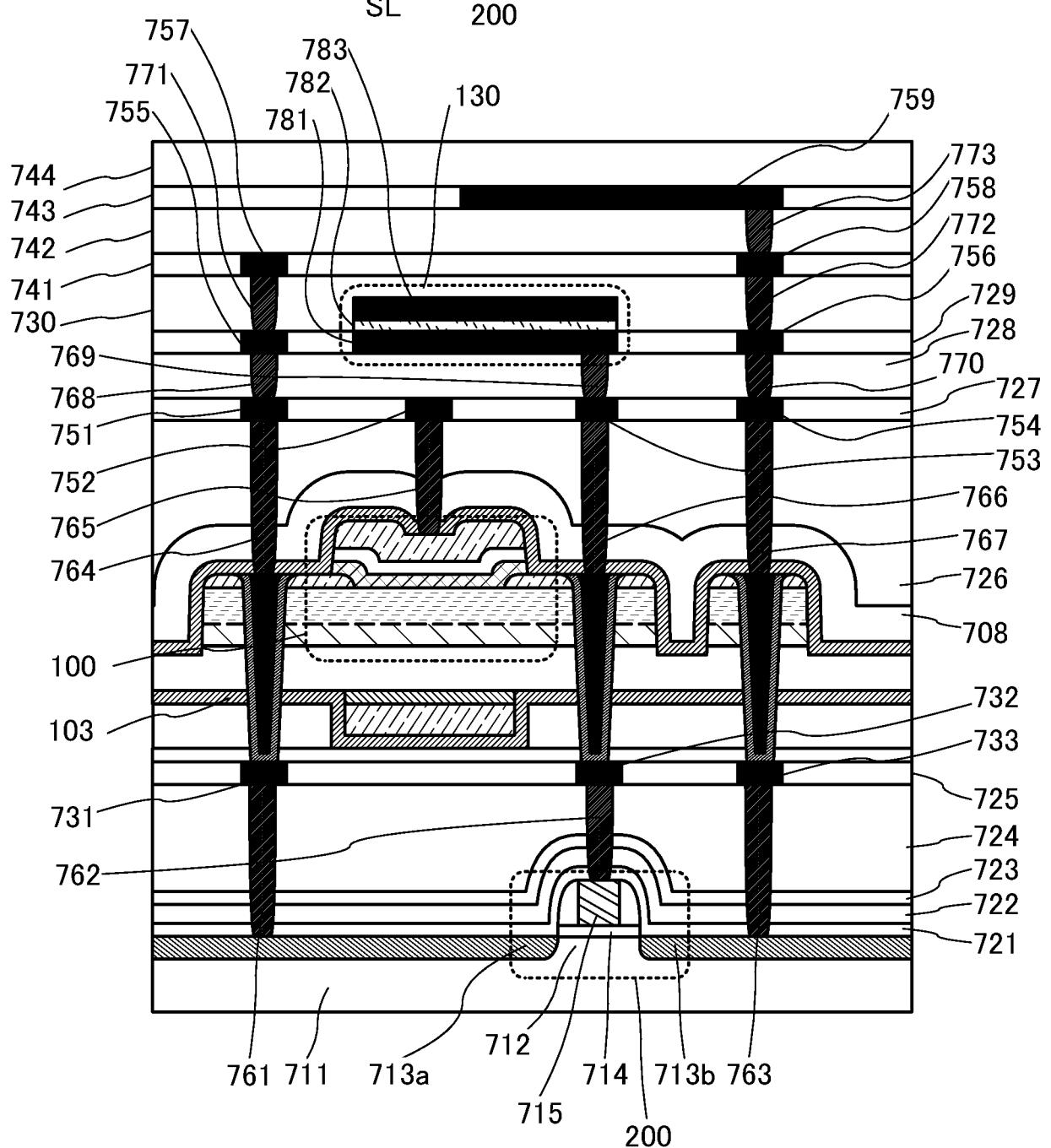

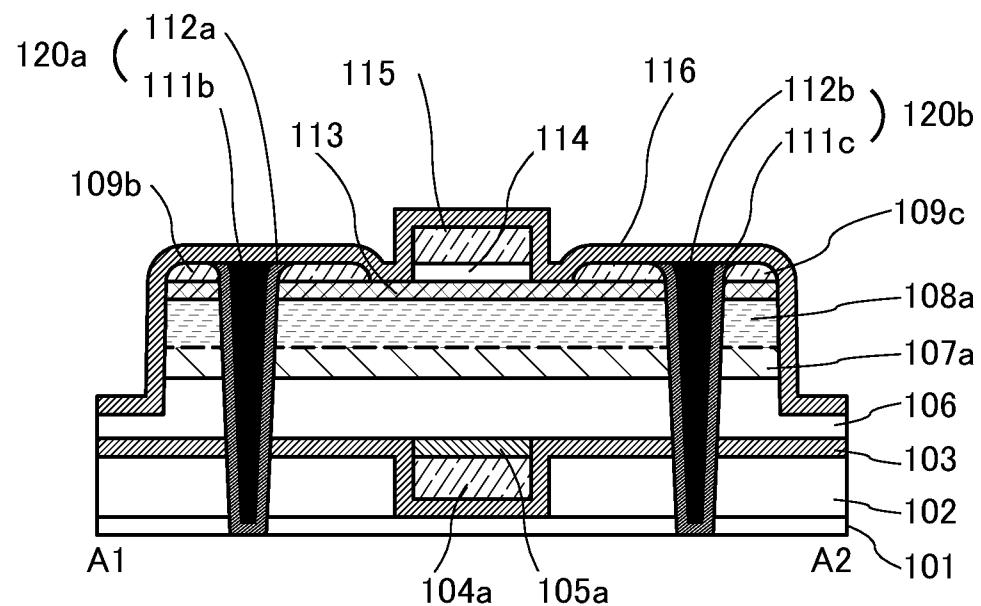

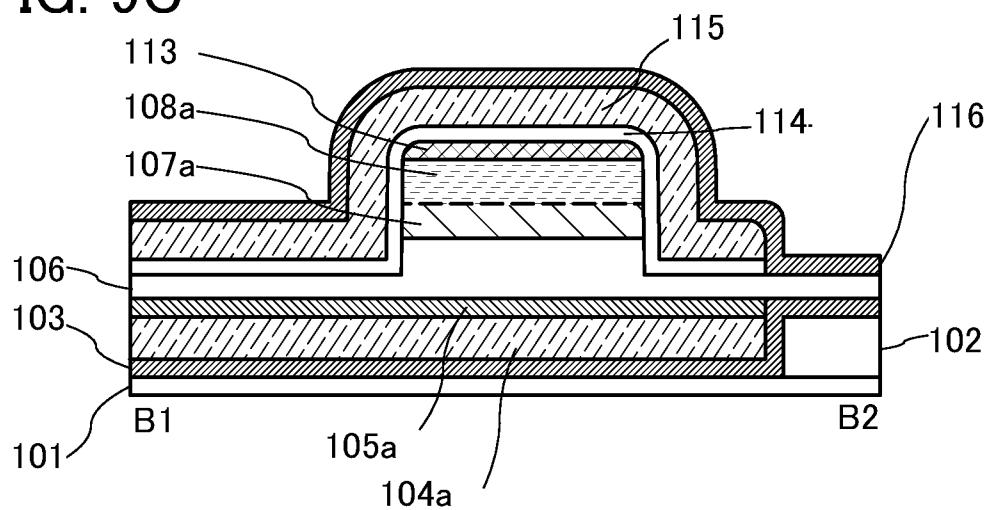

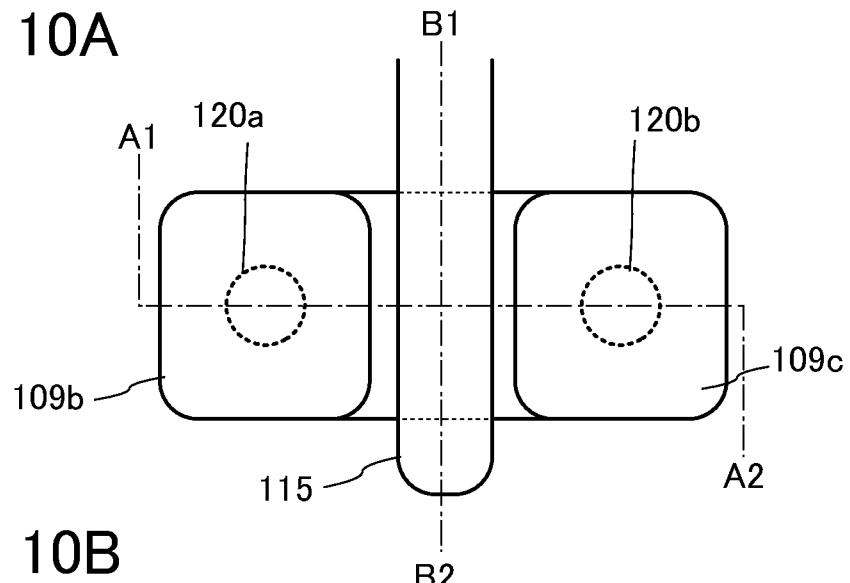

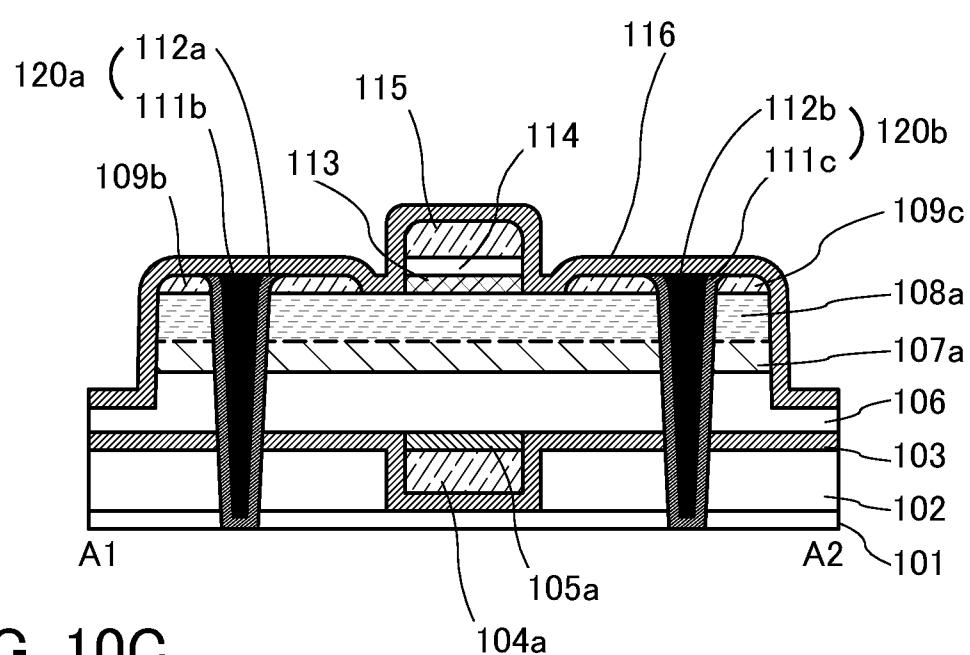

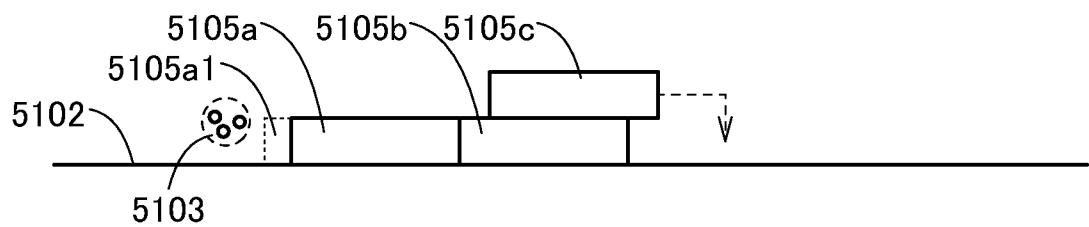

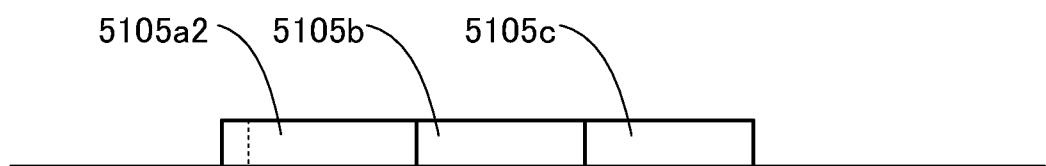

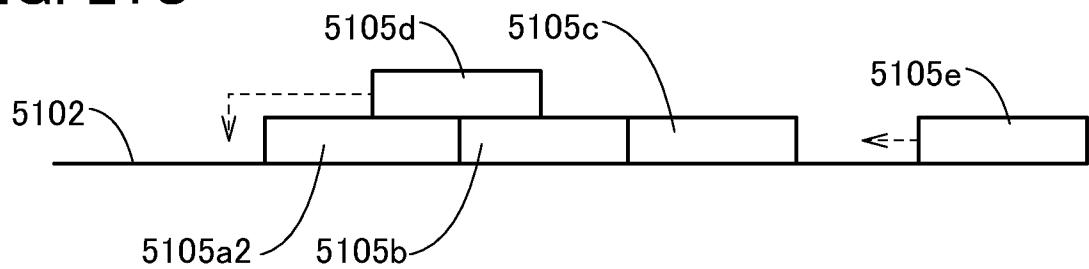

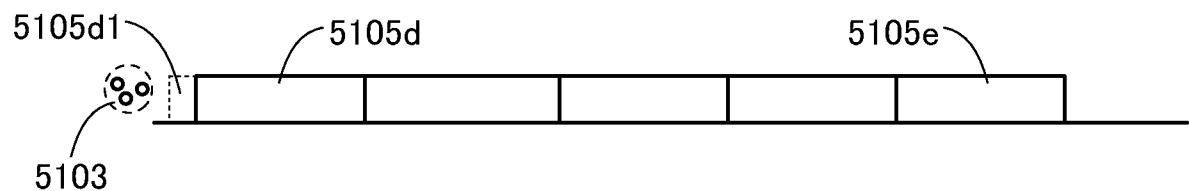

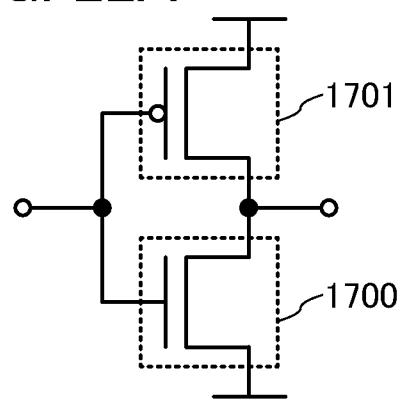

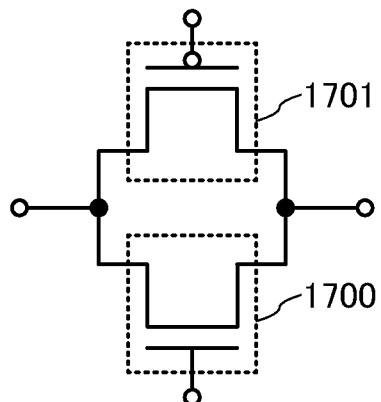

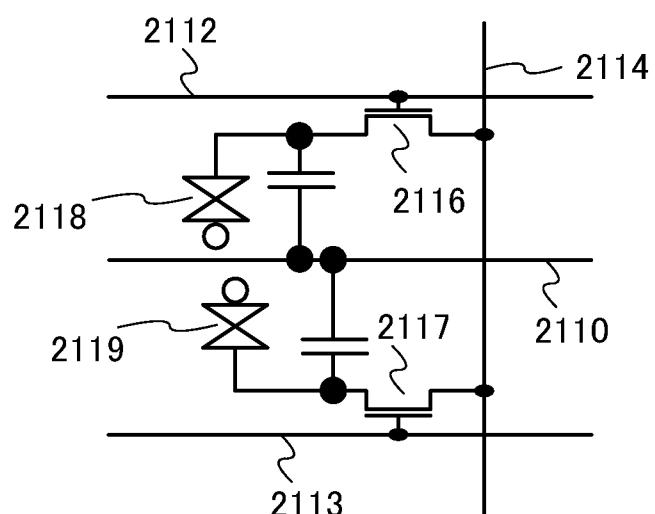

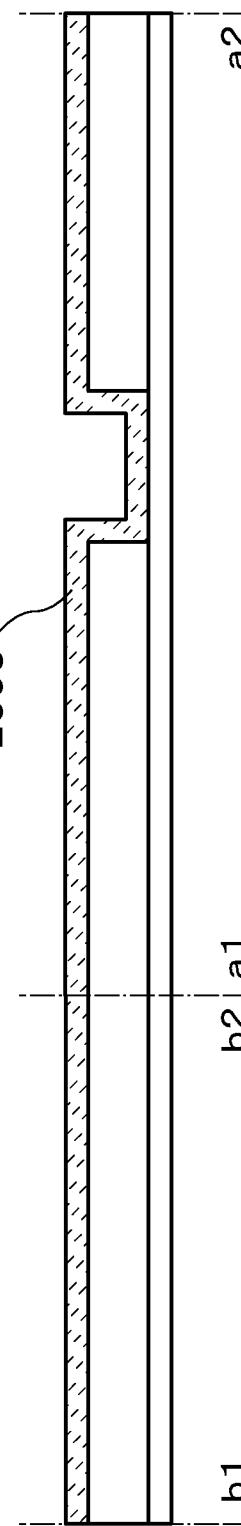

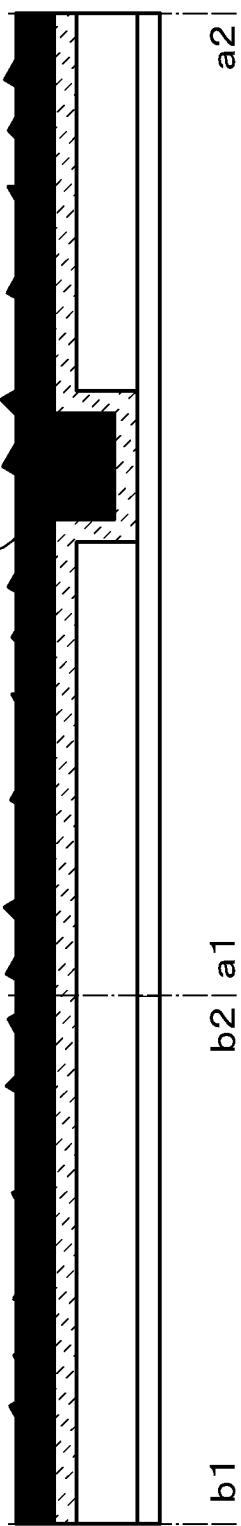

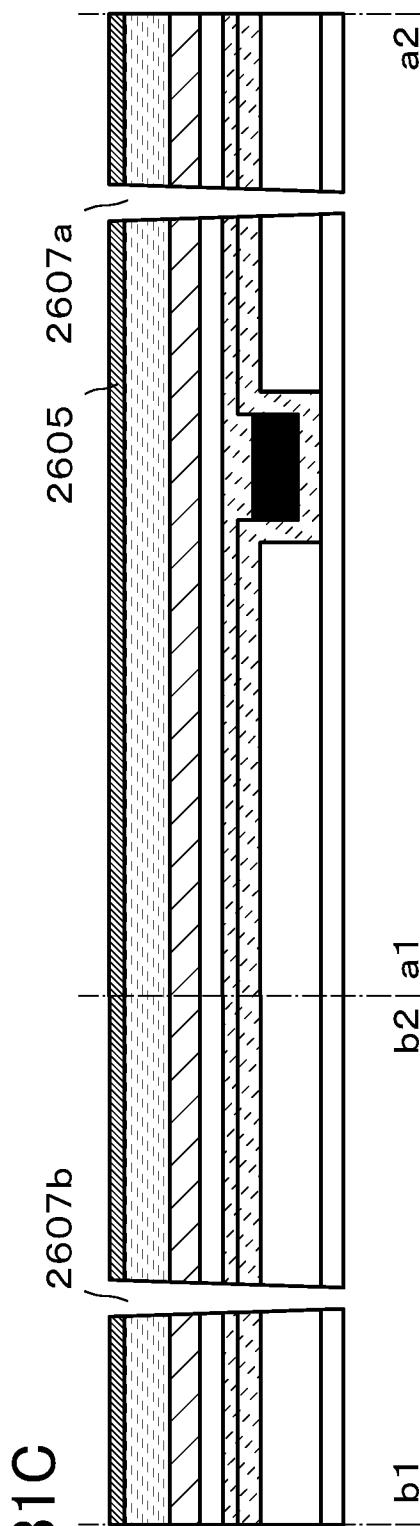

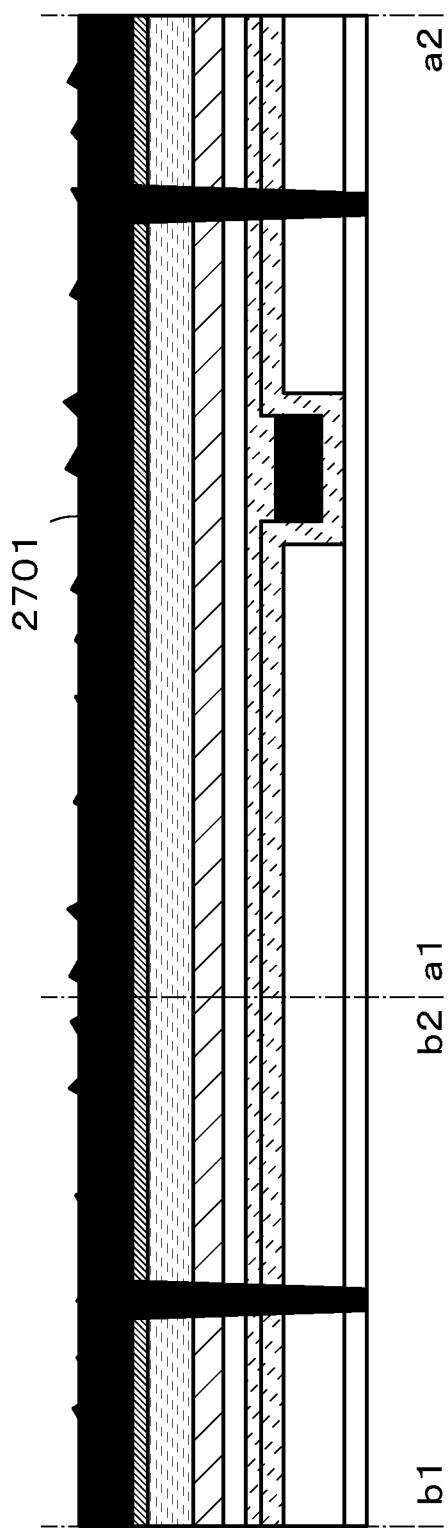

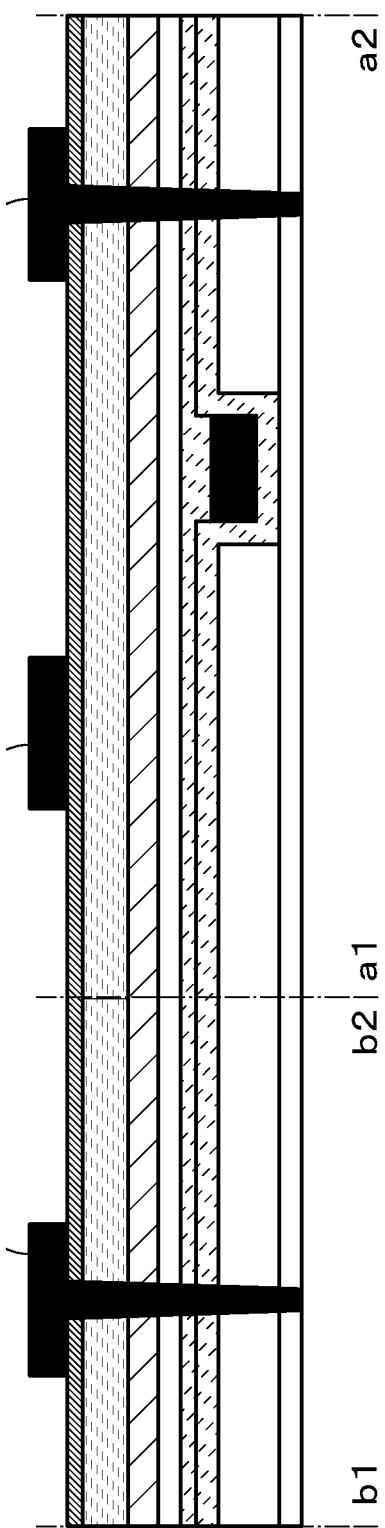

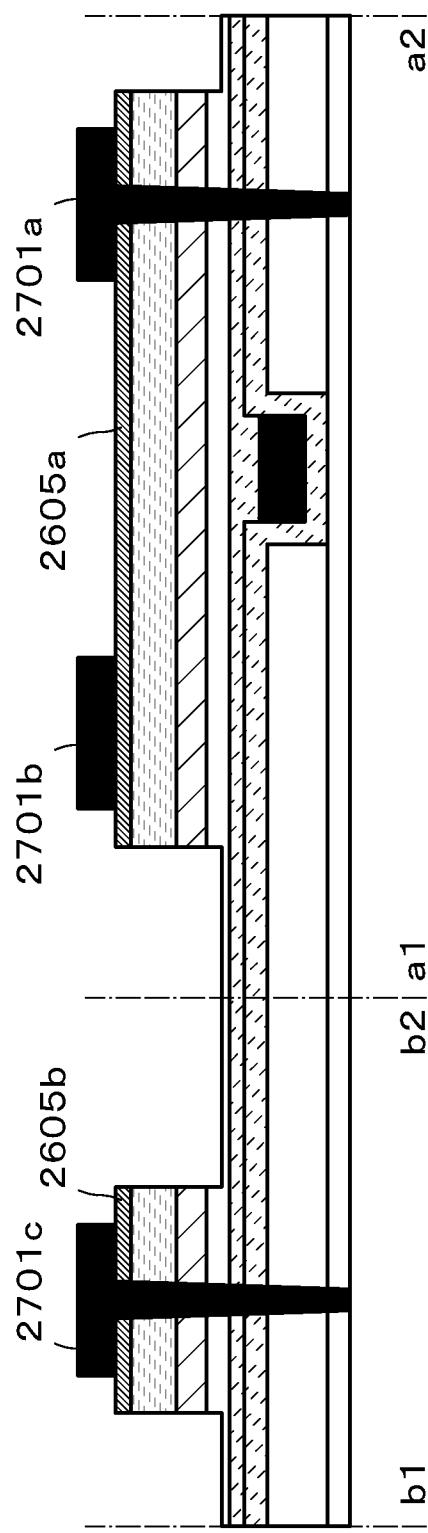

FIG. 7A is a circuit diagram of a semiconductor device of an embodiment and 30 FIG. 7B illustrates a structure example of the semiconductor device.

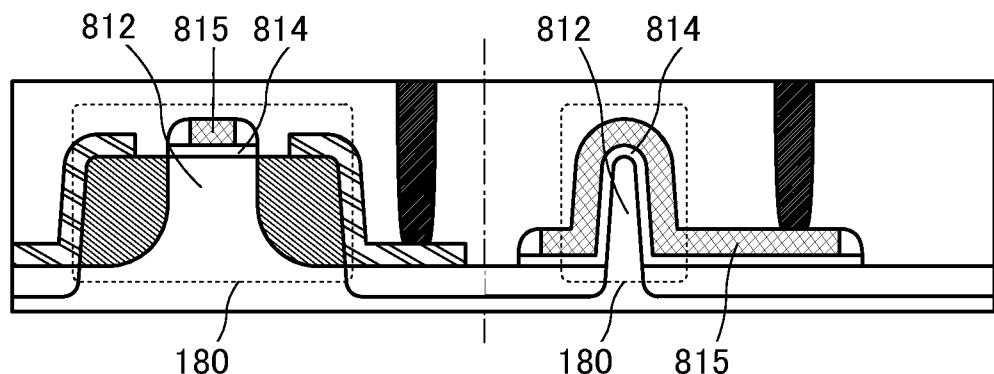

FIG. 8 illustrates a structure example of a semiconductor device of an embodiment.

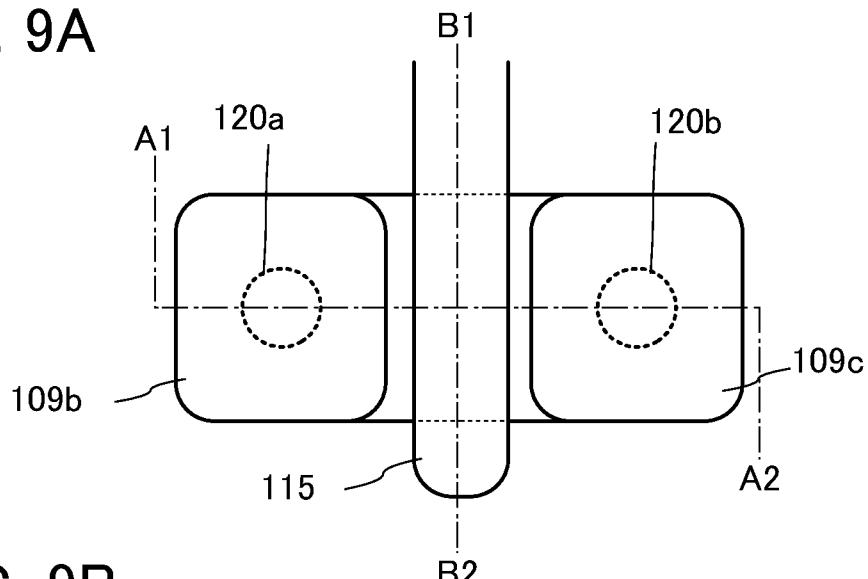

FIGS. 9A to 9C illustrate a structure example of a semiconductor device of an embodiment.

FIGS. 10A to 10C illustrate a structure example of a semiconductor device of an embodiment.

5 FIGS. 11A to 11C illustrate a structure example of a semiconductor device of an embodiment.

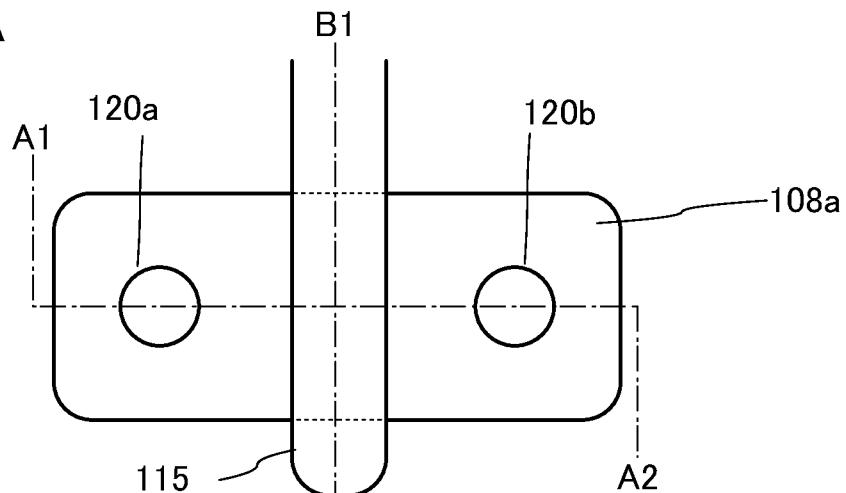

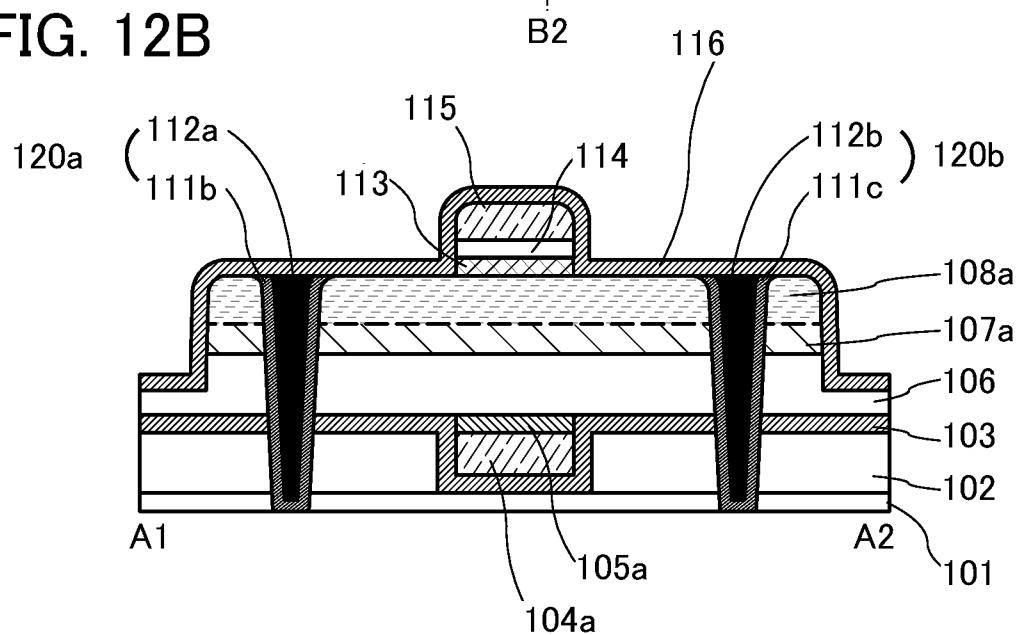

FIGS. 12A to 12C illustrate a structure example of a semiconductor device of an embodiment.

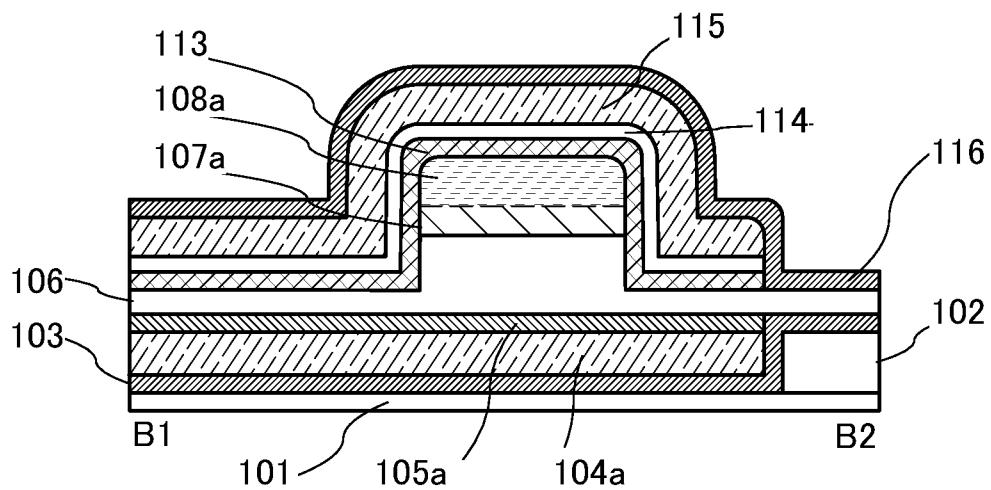

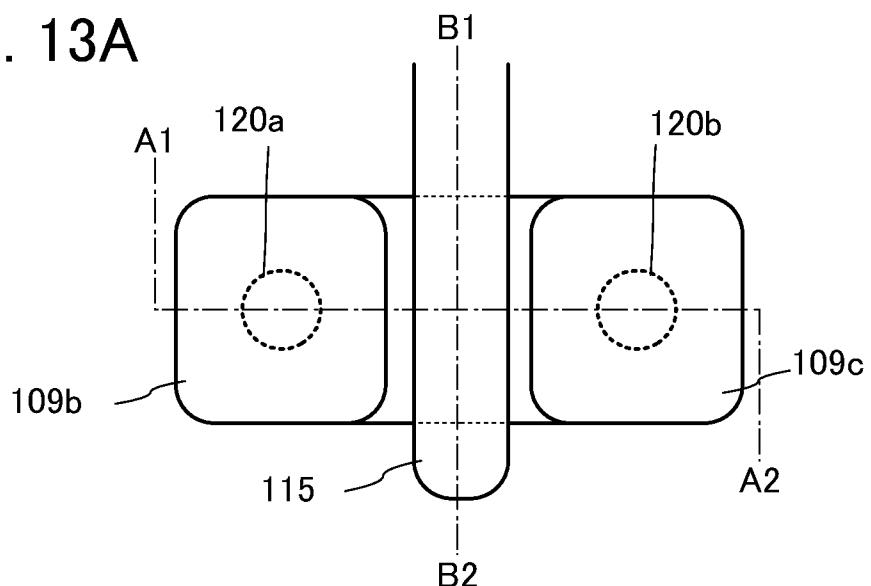

10 FIGS. 13A to 13C illustrate a structure example of a semiconductor device of an embodiment.

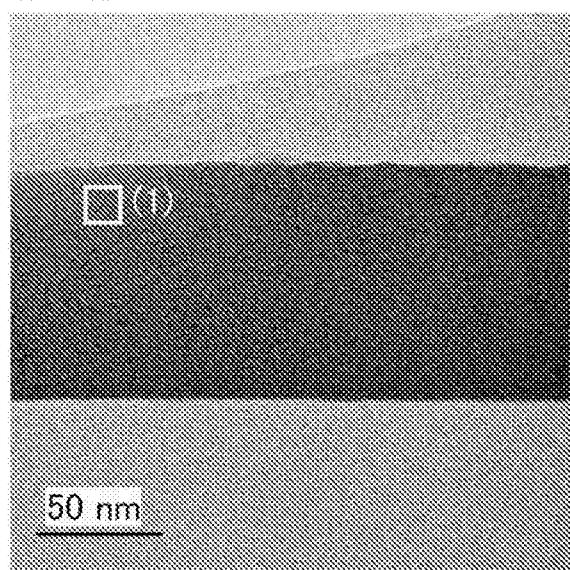

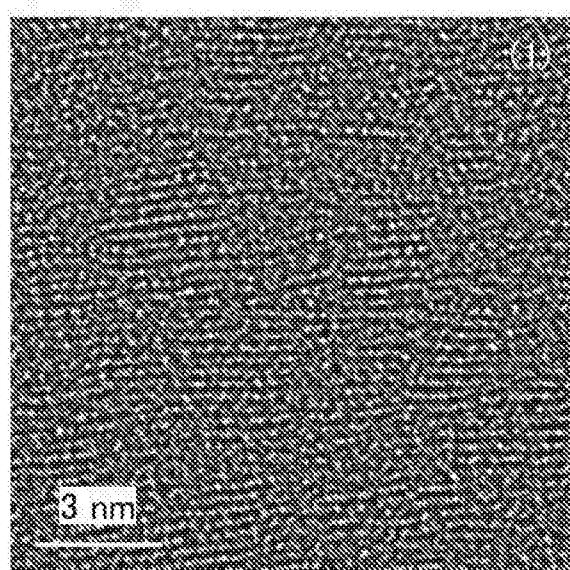

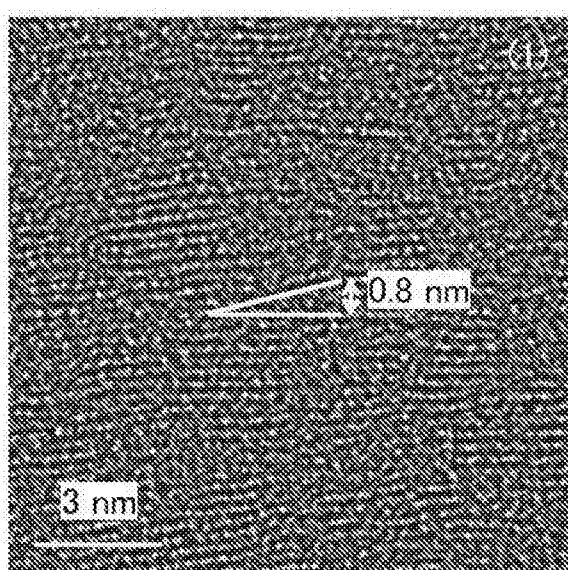

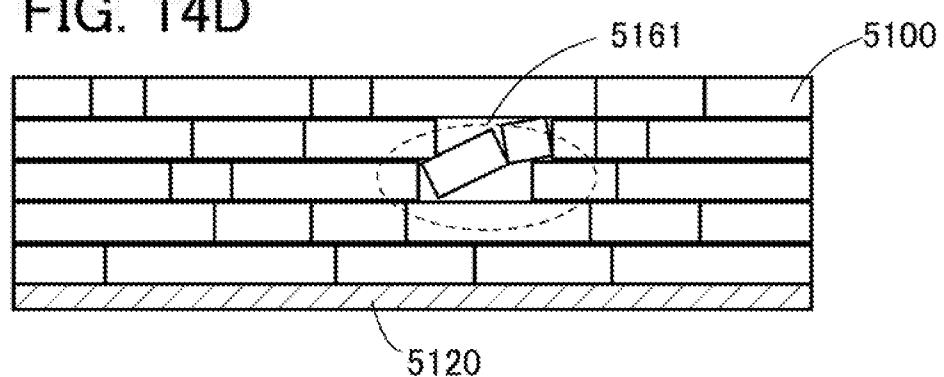

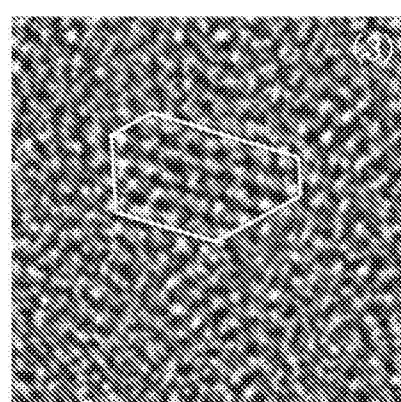

FIGS. 14A to 14D are Cs-corrected high-resolution TEM images of a cross section of a CAAC-OS and a cross-sectional schematic view of a CAAC-OS.

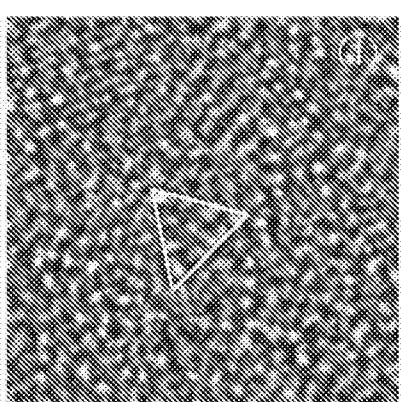

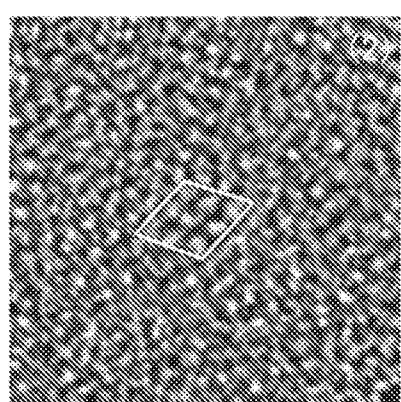

FIGS. 15A to 15D are Cs-corrected high-resolution TEM images of a plane of a CAAC-OS.

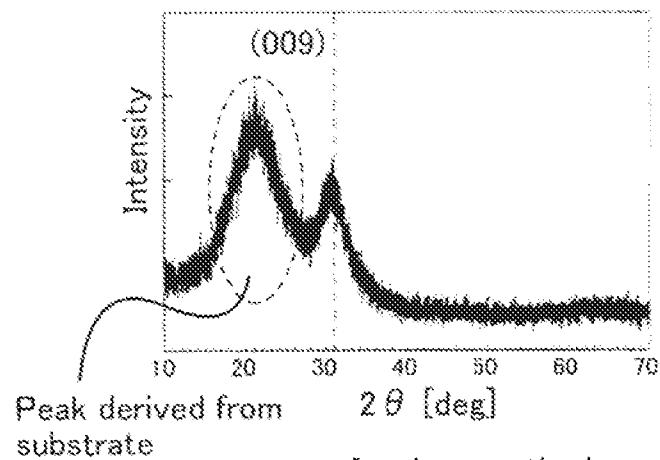

15 FIGS. 16A to 16C show structural analysis of a CAAC-OS and a single crystal oxide semiconductor by XRD.

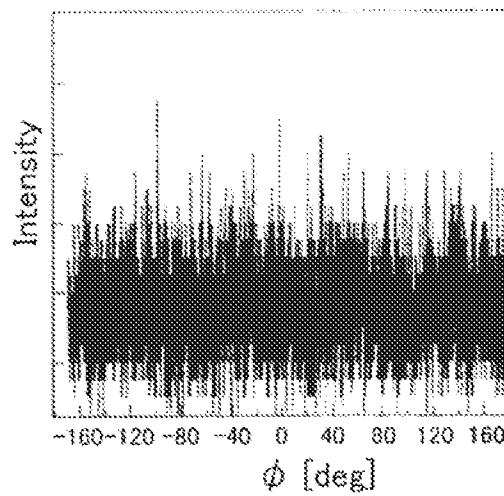

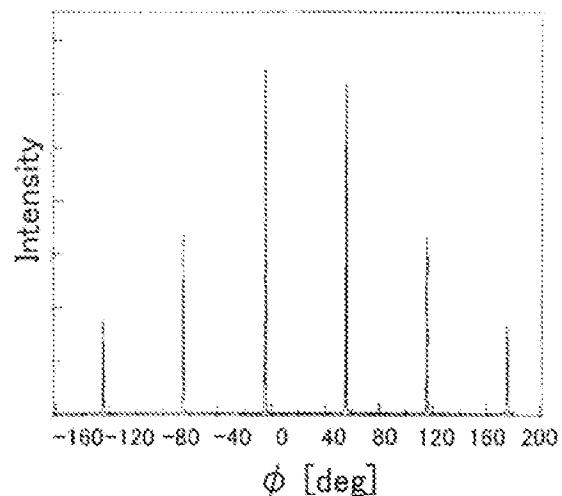

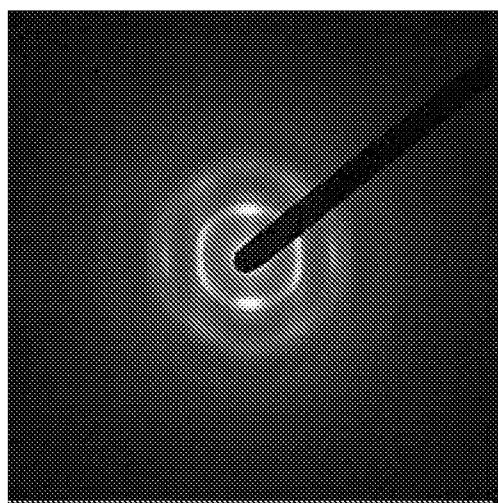

FIGS. 17A and 17B show electron diffraction patterns of a CAAC-OS.

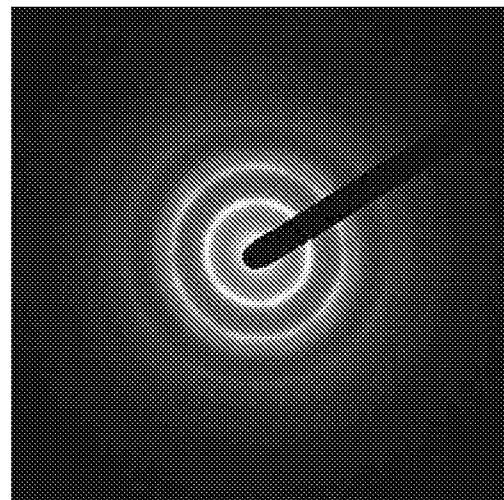

FIG. 18 shows a change of crystal parts of an In-Ga-Zn oxide owing to electron irradiation.

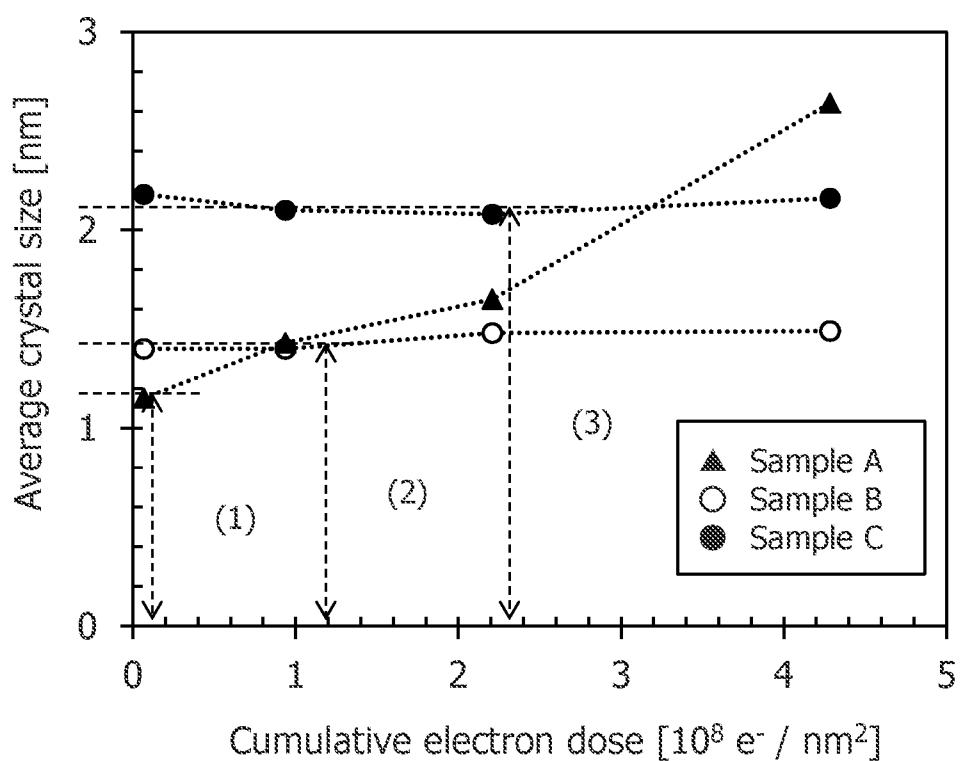

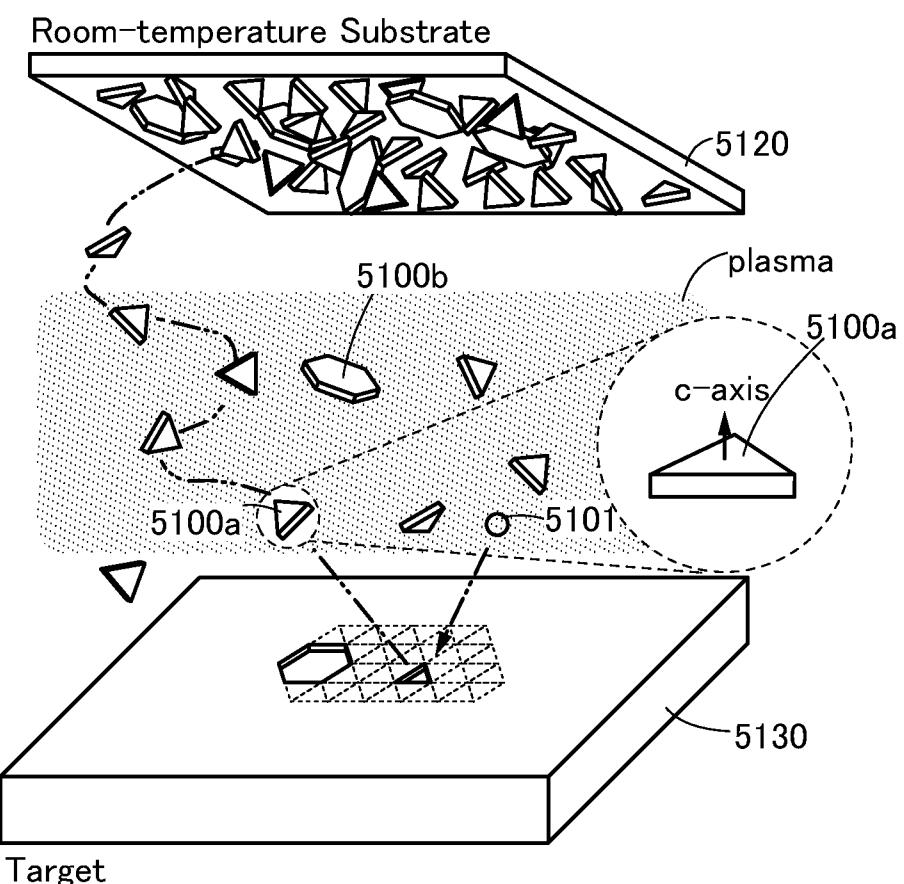

20 FIGS. 19A and 19B are schematic views showing deposition models of a CAAC-OS and an nc-OS.

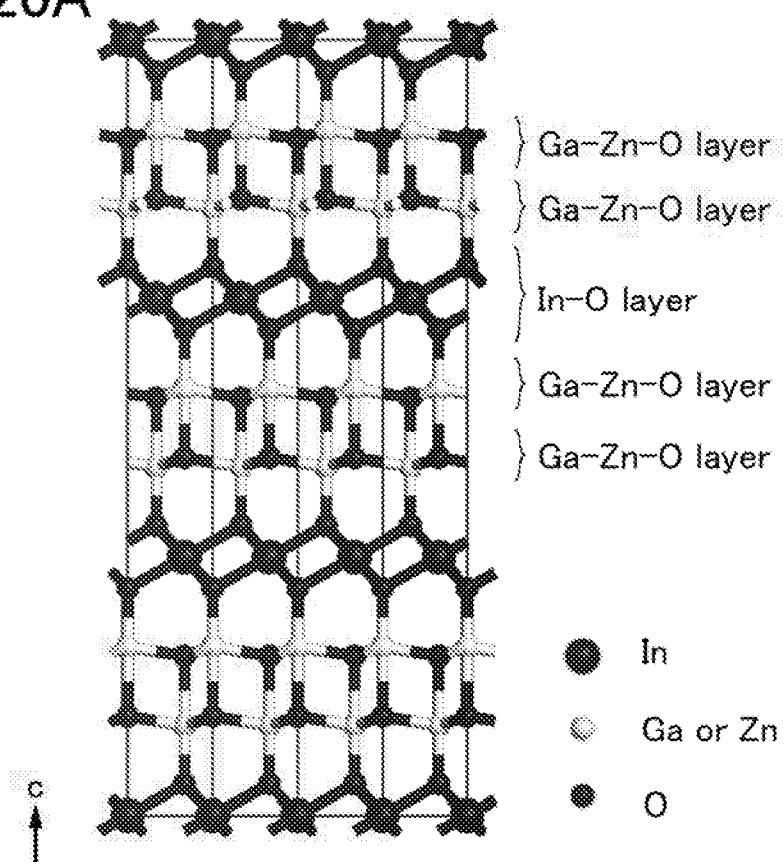

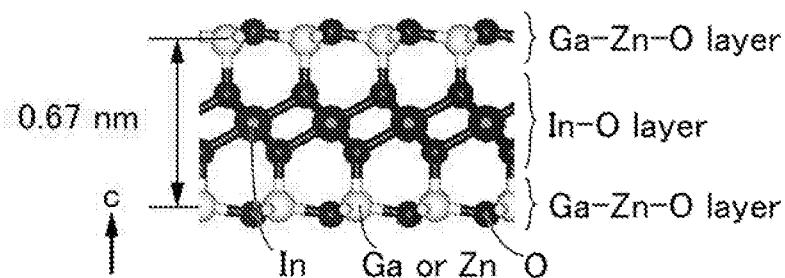

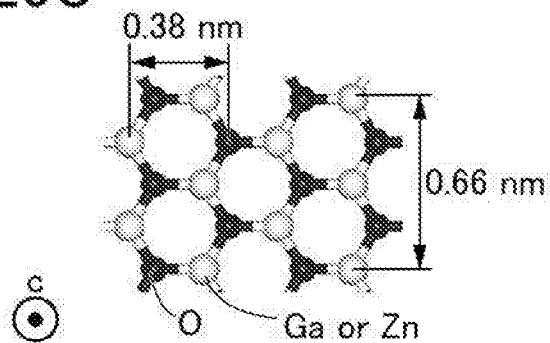

FIGS. 20A to 20C show an  $\text{InGaZnO}_4$  crystal and a pellet.

FIGS. 21A to 21D are schematic views illustrating a deposition model of a CAAC-OS.

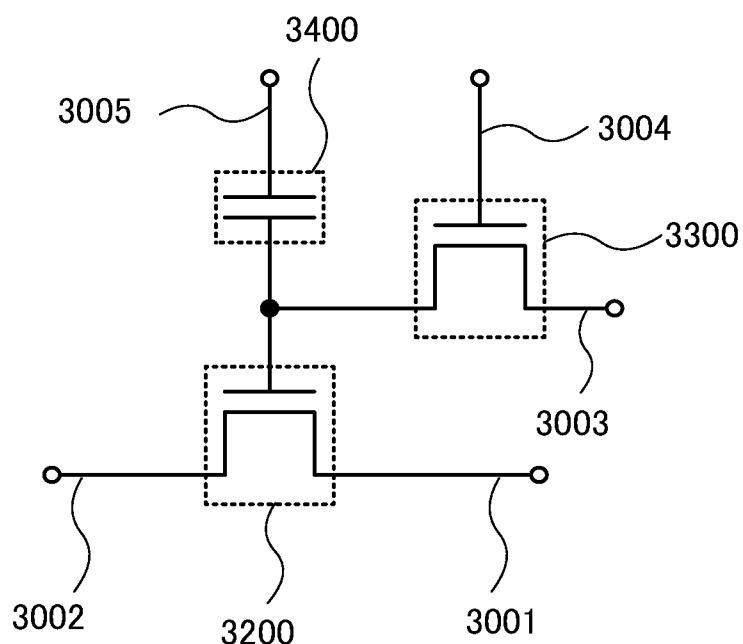

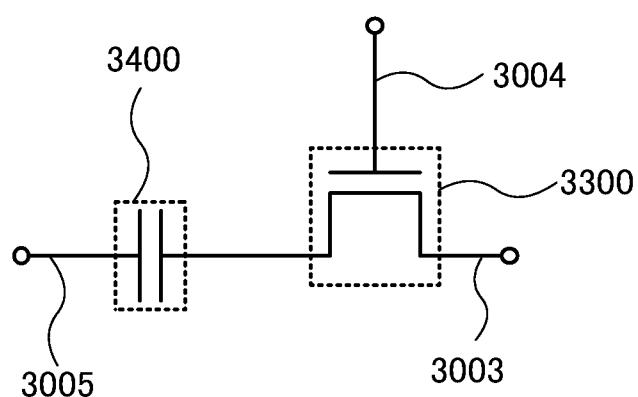

25 FIGS. 22A to 22D are each a circuit diagram illustrating an embodiment.

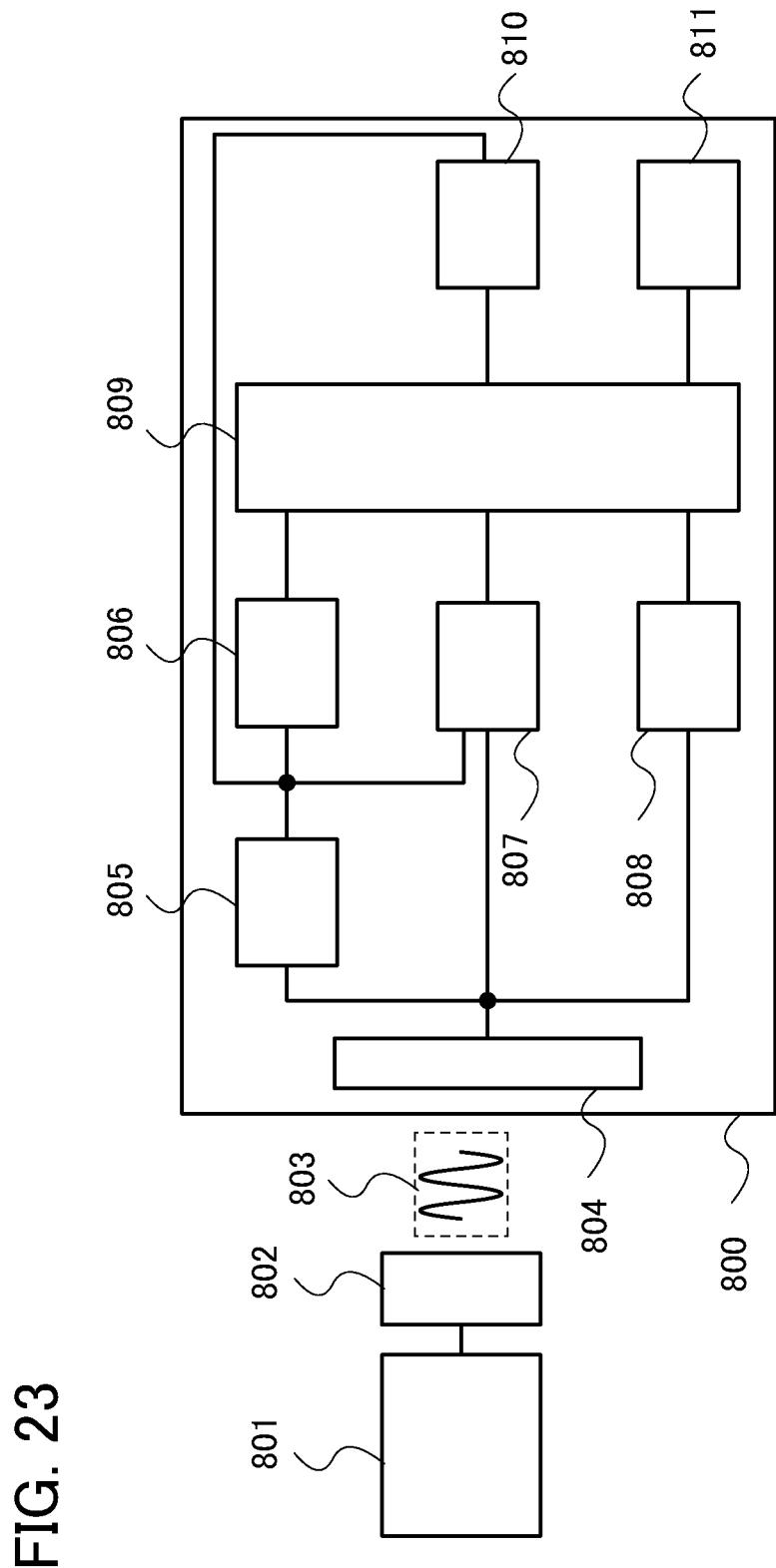

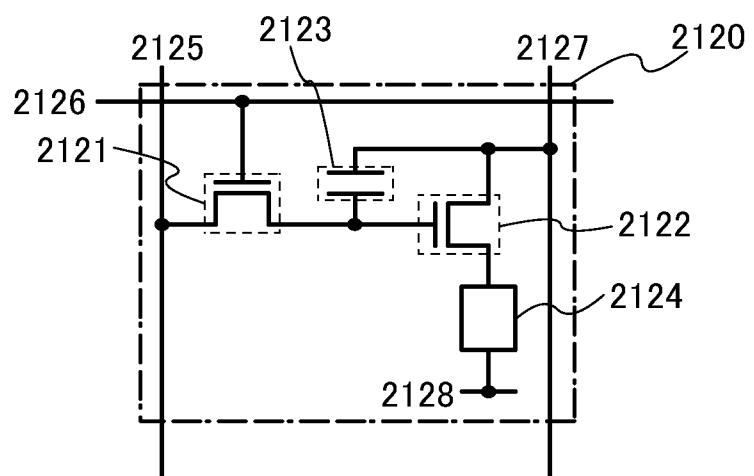

FIG. 23 illustrates a structure example of an RF device of an embodiment.

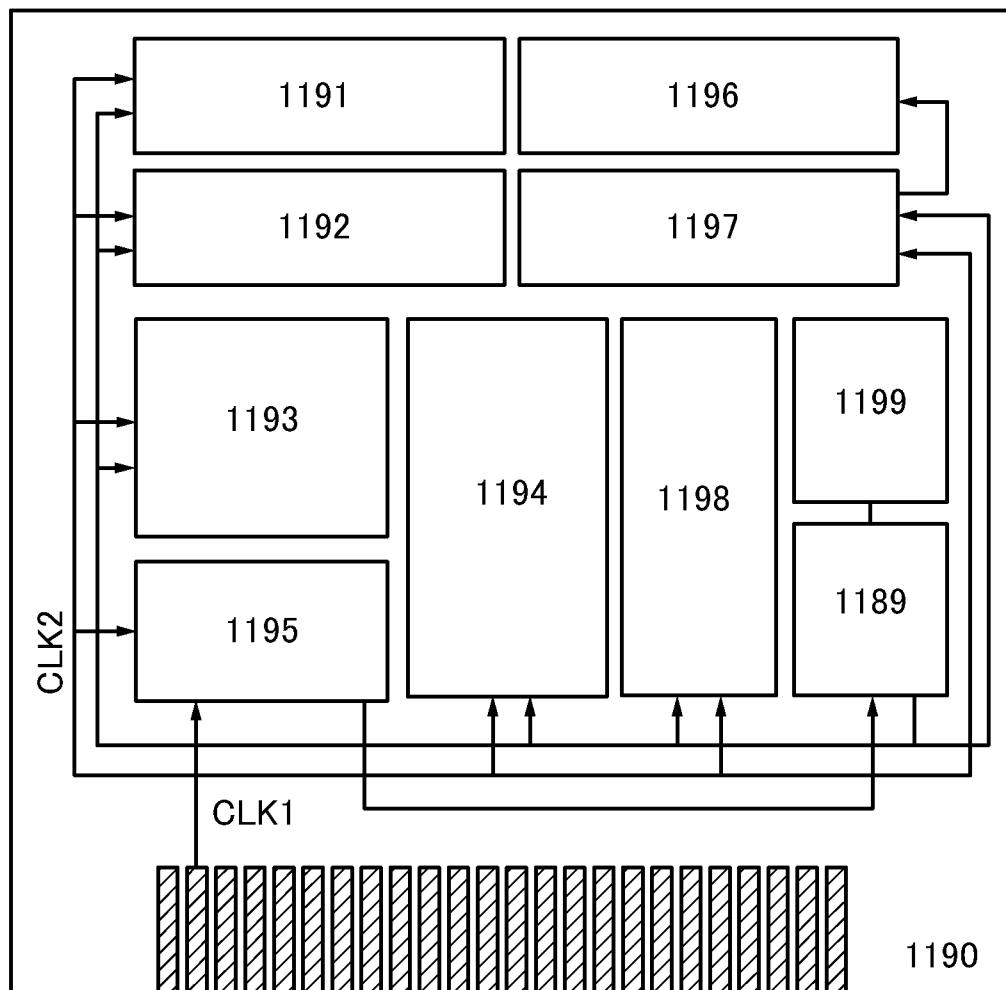

FIG. 24 illustrates a structure example of a CPU of an embodiment.

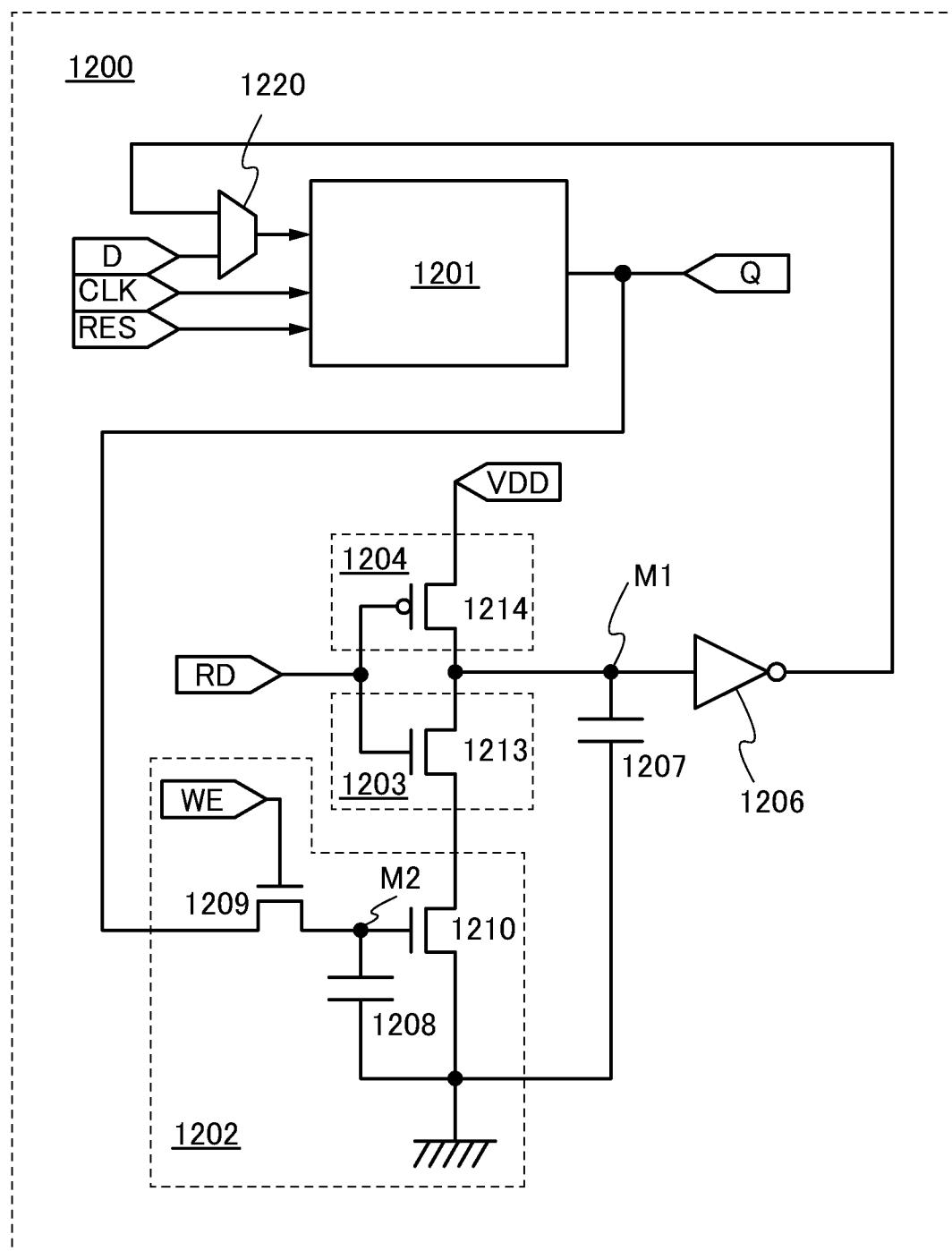

FIG. 25 is a circuit diagram of a memory element of an embodiment.

FIGS. 26A to 26C are circuit diagrams of display devices of an embodiment.

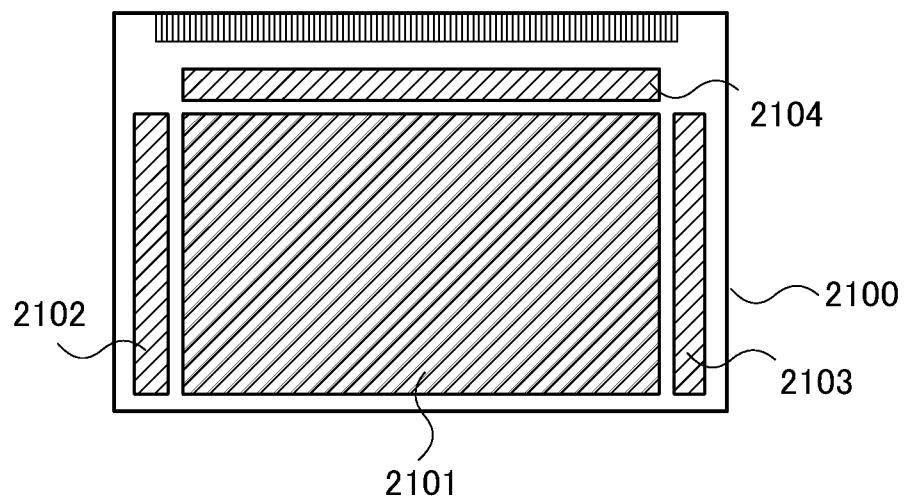

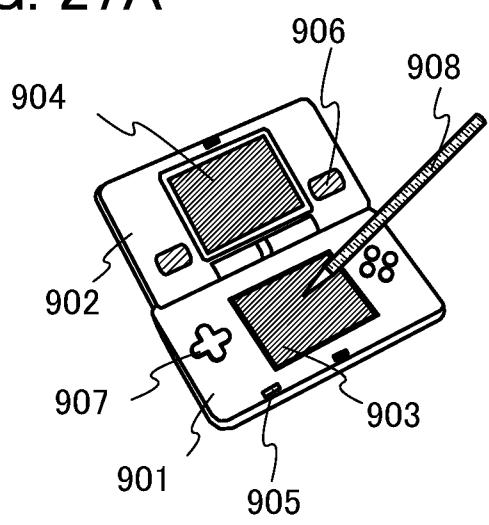

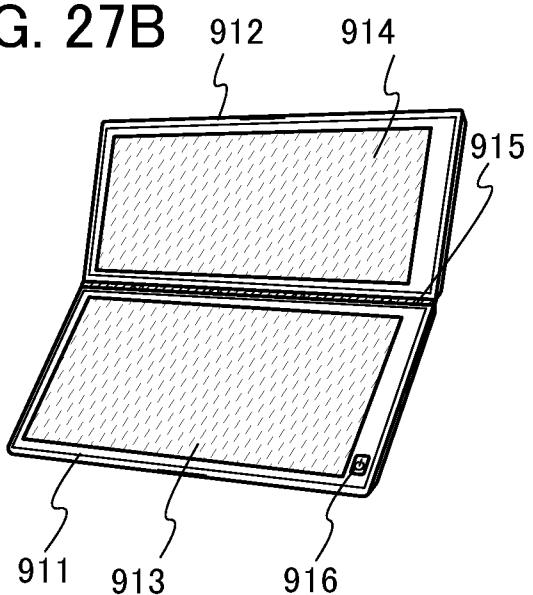

30 FIGS. 27A to 27F illustrate electronic appliances of an embodiment.

FIGS. 28A to 28F each illustrate an application example of an RF device of an embodiment.

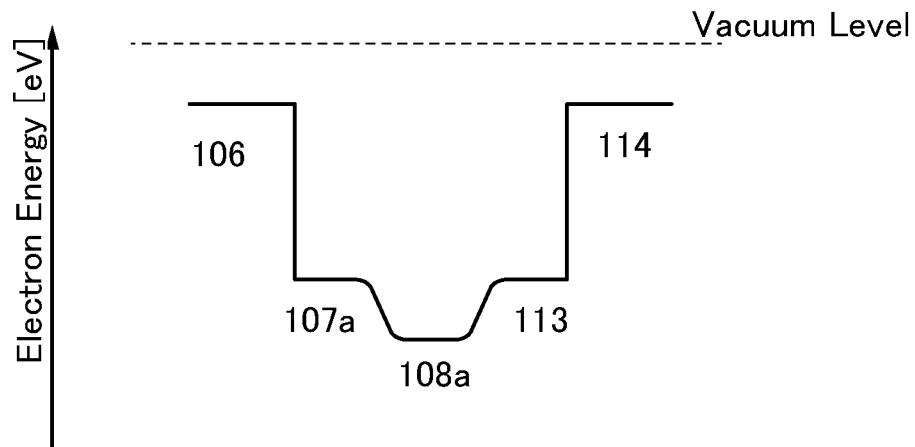

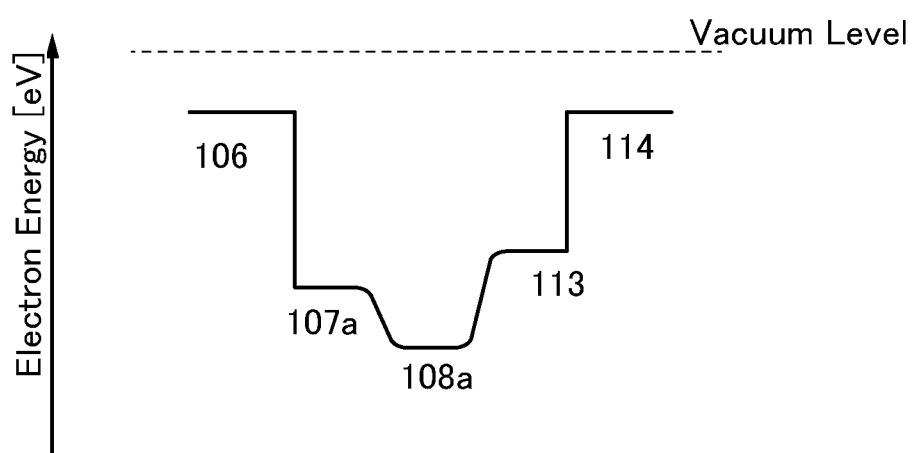

FIGS. 29A and 29B each illustrate a band structure of an embodiment.

FIGS. 30A to 30C illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

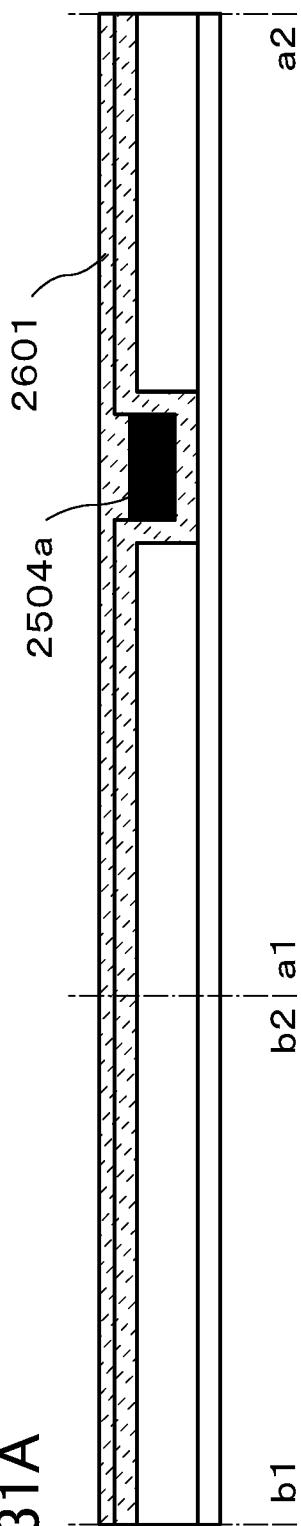

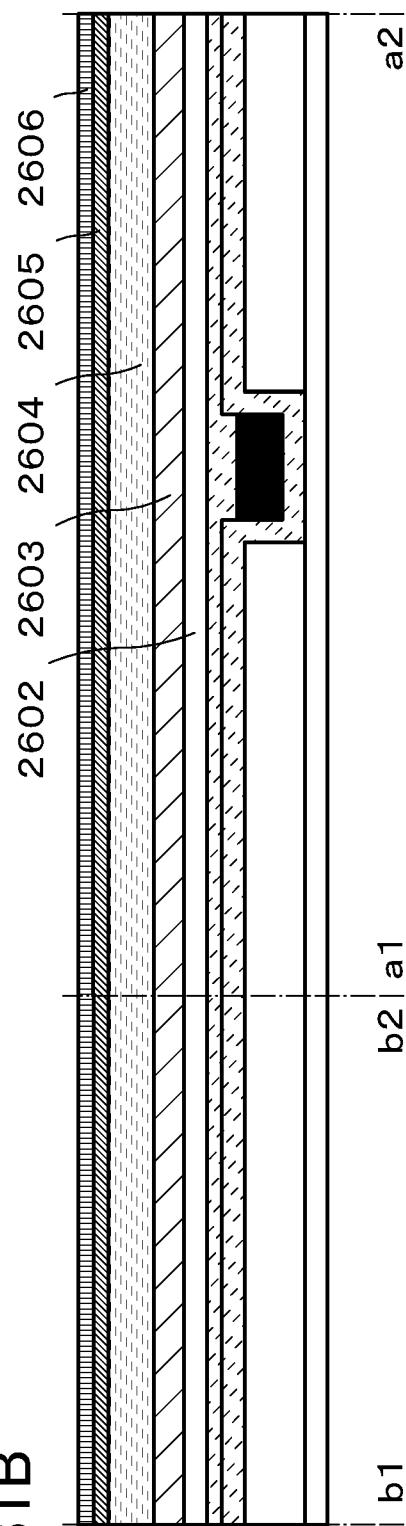

5 FIGS. 31A to 31C illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

FIGS. 32A and 32B illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

FIGS. 33A and 33B illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

10 FIGS. 34A and 34B illustrate an example of a method for manufacturing a semiconductor device of an embodiment.

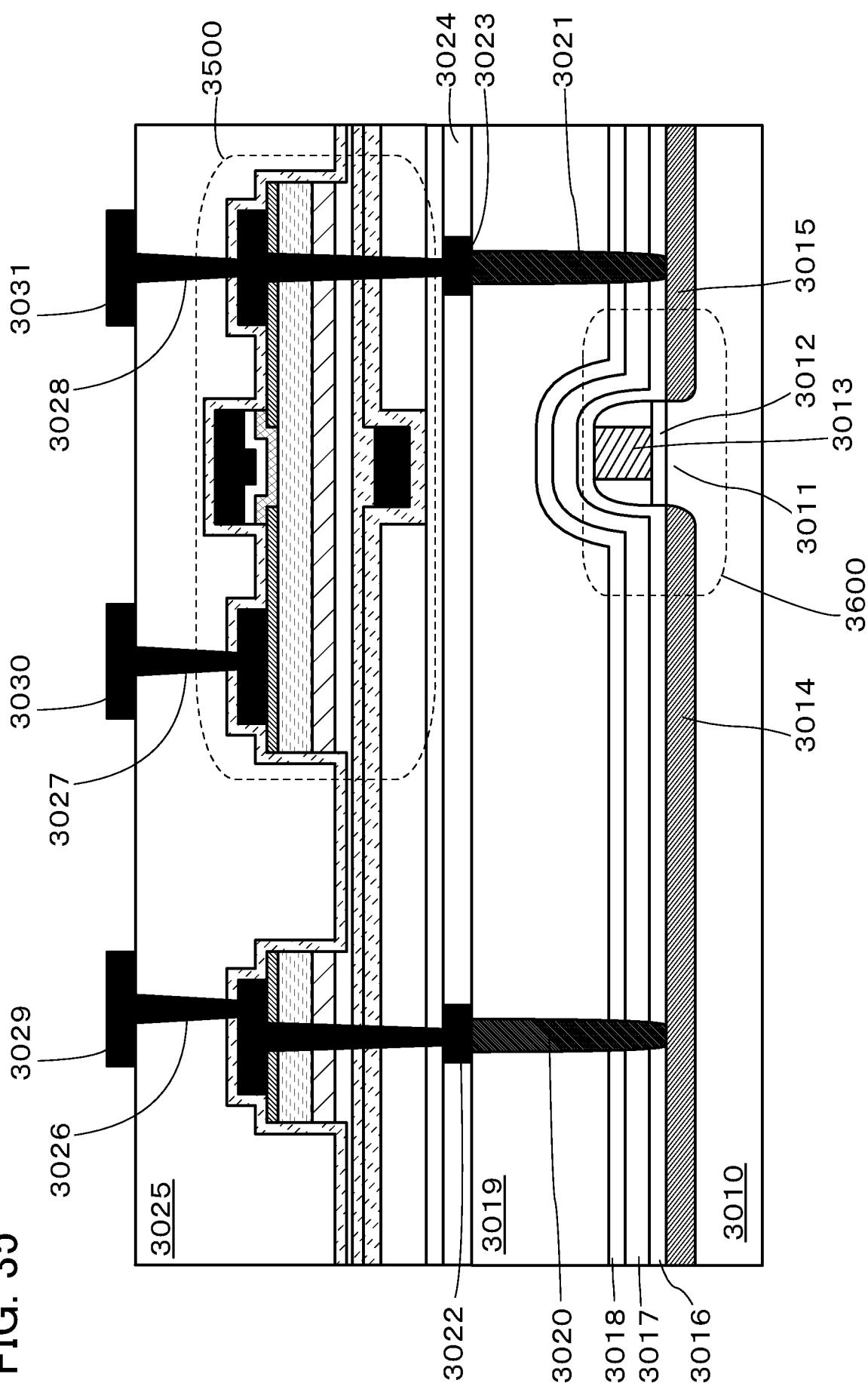

FIG. 35 illustrates a structure example of a semiconductor device of an embodiment.

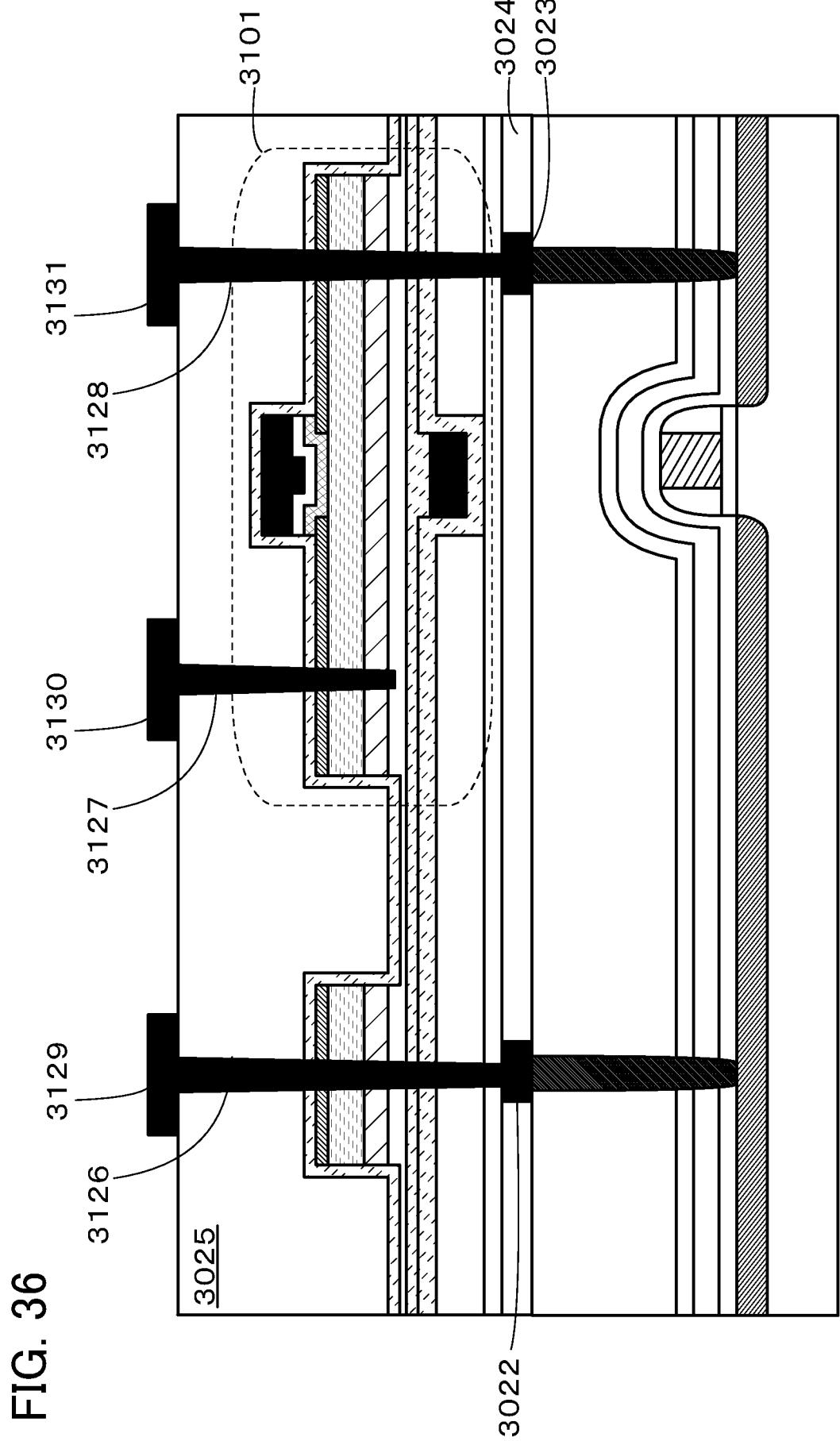

15 FIG. 36 illustrates a structure example of a semiconductor device of an embodiment.

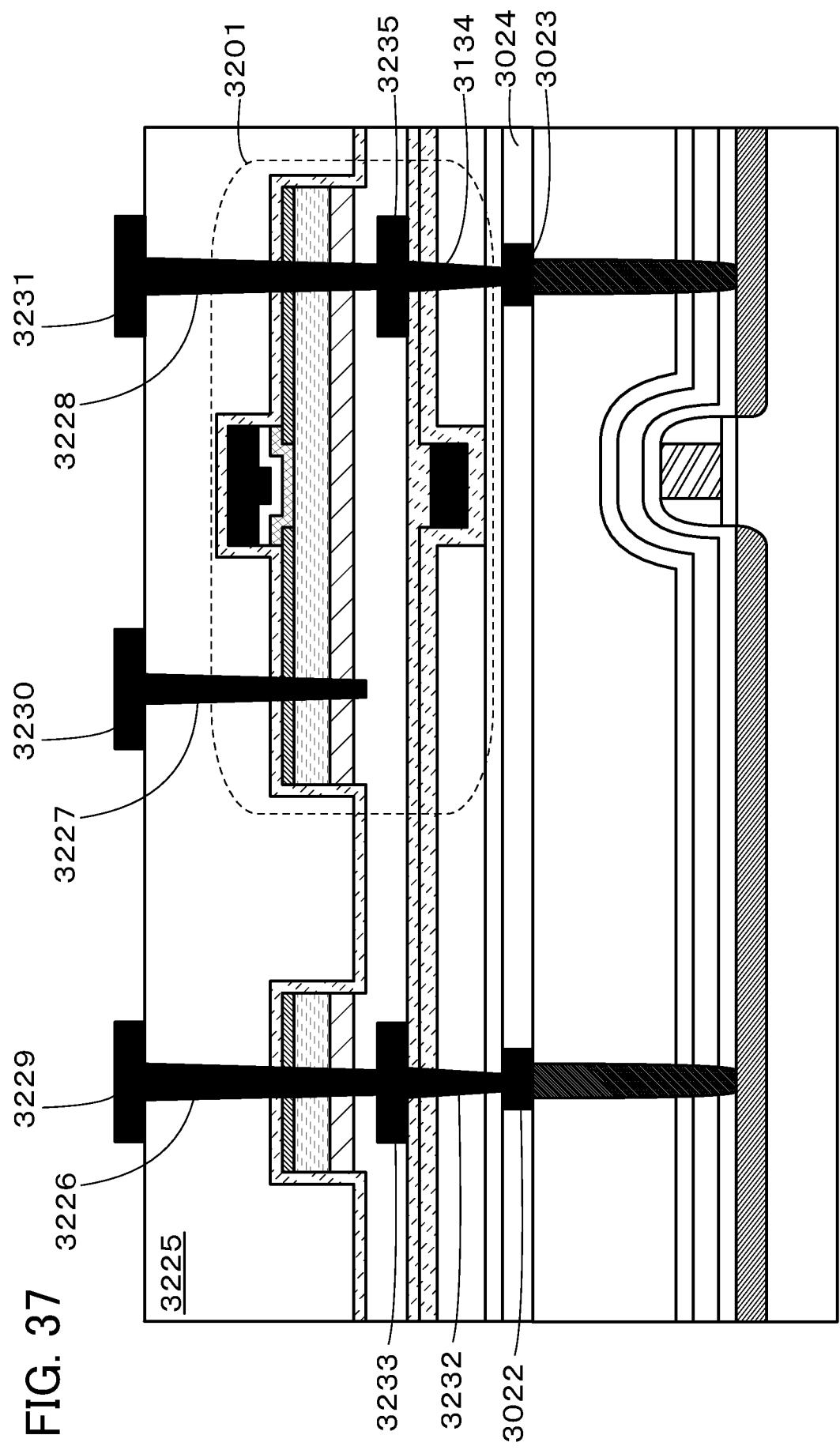

FIG. 37 illustrates a structure example of a semiconductor device of an embodiment.

## BEST MODE FOR CARRYING OUT THE INVENTION

20 [0028]

Embodiments will be described in detail with reference to drawings. Note that the present invention is not limited to the description below, and it is easily understood by those skilled in the art that various changes and modifications can be made without departing from the spirit and scope of the present invention.

25 Accordingly, the present invention should not be interpreted as being limited to the content of the embodiments below.

[0029]

Note that in the structures of the invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description of such portions is not repeated. Furthermore, the same hatching pattern is applied to portions having similar functions, and the portions are not especially denoted by reference numerals in some cases.

[0030]

Note that in each drawing described in this specification, the size, the layer thickness, or the region of each component is exaggerated for clarity in some cases. Therefore, embodiments of the present invention are not limited to such a scale.

5 [0031]

Note that in this specification and the like, ordinal numbers such as “first”, “second”, and the like are used in order to avoid confusion among components and do not limit the number.

[0032]

10 Note that in this specification and the like, an electrode and a wiring electrically connected to the electrode may be a single component. In other words, there are cases where a portion of a wiring functions as an electrode and where a portion of an electrode functions as a wiring.

[0033]

15 A transistor is a kind of semiconductor elements and can achieve amplification of current or voltage, switching operation for controlling conduction or non-conduction, or the like. A transistor in this specification includes an insulated-gate field effect transistor (IGFET) and a thin film transistor (TFT).

[0034]

20 In this specification, the term “parallel” indicates that the angle formed between two straight lines is greater than or equal to  $-10^\circ$  and less than or equal to  $10^\circ$ , and accordingly also includes the case where the angle is greater than or equal to  $-5^\circ$  and less than or equal to  $5^\circ$ . A term “substantially parallel” indicates that the angle formed between two straight lines is greater than or equal to  $-30^\circ$  and less than or equal to  $30^\circ$ . In addition, the term “perpendicular” indicates that the angle formed between two straight lines ranges from  $80^\circ$  to  $100^\circ$ , and accordingly includes the case where the angle ranges from  $85^\circ$  to  $95^\circ$ . A term “substantially perpendicular” indicates that the angle formed between two straight lines is greater than or equal to  $60^\circ$  and less than or equal to  $120^\circ$ .

25

30 [0035]

In this specification, trigonal and rhombohedral crystal systems are included in

a hexagonal crystal system.

[0036]

(Embodiment 1)

[Structure example of stacked-layer structure]

5 An example of a stack 10 including a transistor 100 that is applicable to a semiconductor device of one embodiment of the present invention is described below.

FIG. 1 is a schematic cross-sectional view of the stack 10 described below.

[0037]

A variety of elements can be formed to be stacked over or below the stack 10.

10 FIG. 2 illustrates an example in which the stack 10 is stacked over a stack 20, and a stack 30 is stacked over the stack 10. For example, it is possible to employ a structure that is formed in such a manner that the stack 20 is formed using a single crystal silicon semiconductor, the stack 10 is formed thereover, and an element such as a capacitor is formed as the stack 30 thereover.

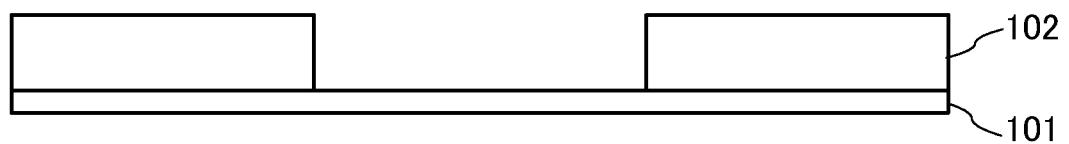

15 [0038]

The stack 10 includes an insulator 102 that is in contact with the top surface of an insulator 101; a groove or opening that is formed in the insulator 102; a barrier film 103 that is in contact with the inside of the groove or opening and the top surface of the insulator 102; a conductor 104a that is provided in the groove or opening of the 20 insulator 102 with the barrier film 103 positioned therebetween; a barrier film 105a that is in contact with the top surface of the conductor 104a; an insulator 106 that is in contact with the top surface of the barrier film 103 and the top surface of the barrier film 105a; a semiconductor 107a that is in contact with the top surface of the insulator 106; a semiconductor 108a that is in contact with the top surface of the semiconductor 107a; a 25 conductor 109b and a conductor 109c that are in contact with the top surface of the semiconductor 108a and separated from each other in a region overlapping the semiconductor 108a; a plurality of plugs 120a and 120b that are provided in openings formed in at least the conductor 109b, the conductor 109c, the semiconductor 108a, and the semiconductor 107a; a semiconductor 113 that is in contact with the top surface of the semiconductor 108a; an insulator 114 that is in contact with the top surface of the semiconductor 113; a conductor 115 that is in contact with the top surface of the insulator 114; and a barrier film 116 that covers at least the semiconductor 107a, the 30

semiconductor 108a, and the semiconductor 113.

[0039]

The semiconductor 108a overlaps the conductor 104a and the barrier film 105a. The conductor 104a functions as a second gate electrode.

5 [0040]

Furthermore, since the conductor 104a is surrounded by the barrier film 103 and the barrier film 105a, oxidation of the conductor 104a can be prevented.

[0041]

One of the conductors 109b and 109c functions as a source electrode and the 10 other functions as a drain electrode. Since at least the side surfaces of the plugs 120a and 120b are in contact with the semiconductor 108a, one of the plugs 120a and 120b functions as a source electrode and the other functions as a drain electrode. Note that the plug 120a is formed of conductors 111b and 112a, and the plug 120b is formed of conductors 111c and 112b.

15 [0042]

Furthermore, the plugs 120a and 120b are formed in the openings provided in the conductors 109b and 109c, the semiconductor 108a, and the semiconductor 107a; as a result, the size of the semiconductor device can be reduced.

[0043]

20 The insulator 114 is provided between the semiconductor 108a and the conductor 115, and functions as a gate insulating film.

[0044]

The conductor 115 overlaps the semiconductor 108a and functions as a first gate electrode.

25 [0045]

Note that the transistor 100 includes at least the semiconductor 108a, the insulator 114, the conductor 115, and the like.

[0046]

An approximately 50-nm-thick silicon nitride is preferably used as the insulator 30 101. An approximately 150-nm-thick silicon oxide deposited using tetra-ethyl-ortho-silicate (TEOS) is preferably used as the insulator 102.

[0047]

Any material can be used for the insulator 102 as long as the etching rate of the insulator 102 is different from that of the insulator 101. Each of the insulator 101 and the insulator 102 can be formed with a single layer or stacked layers using, for example, silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, aluminum oxide, 5 aluminum oxynitride, aluminum nitride oxide, aluminum nitride, or the like.

[0048]

The insulator 102 functions as a planarization film for eliminating a level difference caused by a structure or the like underlying the insulator 102. A top surface of the insulator 102 may be planarized by a chemical mechanical polishing (CMP) 10 method or the like to increase the planarity of the top surface.

[0049]

Examples of materials that can be used for the barrier film 103 and the barrier film 116 are silicon nitride, silicon nitride oxide, aluminum oxide, aluminum oxynitride, gallium oxide, gallium oxynitride, yttrium oxide, yttrium oxynitride, hafnium oxide, and 15 hafnium oxynitride. Aluminum oxide is particularly preferable because of its excellent barrier property against water or hydrogen.

[0050]

The barrier film 103 and the barrier film 116 each may be a stack of a layer of a material relatively impermeable to water or hydrogen and a layer containing an 20 insulating material. The barrier film 103 and the barrier film 116 each may be, for example, a stack of a layer containing silicon oxide or silicon oxynitride, a layer containing a metal oxide, and the like.

[0051]

It is preferable that hydrogen, water, or the like in the layers under the barrier 25 film 103 be reduced as much as possible or degasification be inhibited. Hydrogen or water might become a factor that causes changes in the electrical characteristics of an oxide semiconductor. Hydrogen or water diffusing from the layers under the barrier film 103 to the layers over the barrier film 103 can be inhibited owing to the barrier film 103.

30 [0052]

In order to reduce hydrogen or water contained in the layers under the barrier film 103 as much as possible or to inhibit degasification, heat treatment for removing

the hydrogen or the water is preferably performed before the formation of the barrier film 103 or immediately after the formation of openings for forming the plugs 120a and 120b in the barrier film 103. The heat treatment is preferably performed at as high a temperature as possible within the range that does not adversely affect the heat 5 resistance of the conductive films and the like in the semiconductor device and the electrical characteristics of the transistor. Specifically, the temperature may be, for example, higher than or equal to 450 °C, preferably higher than or equal to 490 °C, further preferably higher than or equal to 530 °C, or may be higher than or equal to 650 °C. It is preferable that the heat treatment be performed in an inert gas atmosphere or 10 a reduced pressure atmosphere for 1 hour or longer, preferably 5 hours or longer, further preferably 10 hours or longer. In addition, the temperature of the heat treatment may be determined in consideration of the heat resistance, a material of a wiring, an electrode, or a plug included in the semiconductor device; in the case where the heat resistance of the material is low, the heat treatment may be performed at lower than or 15 equal to 550 °C, lower than or equal to 600 °C, lower than or equal to 650 °C, or lower than or equal to 800 °C. Such heat treatment may be performed at least once but is preferably performed more than once.

[0053]

For the barrier film 103 and the barrier film 116, a material relatively 20 impermeable to oxygen is preferably used. The material has excellent barrier properties against oxygen as well as hydrogen and water. Use of such a material can prevent oxygen that is released at the time of heating the insulator 106 from diffusing into layers below the barrier film 103 and layers over the barrier film 116. As a result, the amount of oxygen which is released from the insulator 106 to be supplied to the 25 semiconductor 107a, the semiconductor 108a, and the semiconductor 113 can be increased.

[0054]

In this manner, with the barrier film 103, the concentration of hydrogen or 30 water contained in each layer provided below the barrier film 103 is reduced or the hydrogen or water is removed, and diffusion of hydrogen or water into the semiconductor 107a, the semiconductor 108a, and the semiconductor 113 is prevented.

Therefore, the hydrogen or water content of each of the semiconductor 107a, the semiconductor 108a, and the semiconductor 113 can be extremely low. For example, the hydrogen concentration of the semiconductor 107a, the semiconductor 108a, the semiconductor 113, or the insulator 114 can be reduced to lower than  $5 \times 10^{18}$  atoms/cm<sup>3</sup>, preferably lower than  $1 \times 10^{18}$  atoms/cm<sup>3</sup>, further preferably lower than  $3 \times 10^{17}$  atoms/cm<sup>3</sup>.

[0055]

It is preferable that the conductor 104a be formed using a metal selected from tantalum, tungsten, titanium, molybdenum, chromium, niobium, and the like, or an alloy material or a compound material including any of the metals as its main component. Alternatively, polycrystalline silicon to which an impurity such as phosphorus is added can be used. Still alternatively, a stacked-layer structure including a film of metal nitride and a film of any of the above metals may be used. As a metal nitride, tungsten nitride, molybdenum nitride, or titanium nitride can be used. When the metal nitride film is provided, adhesiveness of the metal film can be increased; thus, separation can be prevented.

[0056]

The conductor 104a can also be formed using a light-transmitting conductive material such as indium tin oxide, indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium zinc oxide, or indium tin oxide to which silicon oxide is added. It is also possible to have a stacked-layer structure formed using the above light-transmitting conductive material and the above metal.

[0057]

For example, the conductor 104a can have a stacked-layer structure of three layers. A stacked-layer structure formed of titanium as a first layer, titanium nitride as a second layer over the first layer, and tungsten as a third layer over the second layer may be employed.

[0058]

As the barrier film 105a, an In-Ga-Zn-based oxynitride semiconductor film, an In-Sn-based oxynitride semiconductor film, an In-Ga-based oxynitride semiconductor

film, an In-Zn-based oxynitride semiconductor film, a Sn-based oxynitride semiconductor film, an In-based oxynitride semiconductor film, a film of a metal nitride (such as InN or ZnN), or the like can be used. These films each have a work function higher than or equal to 5 eV, preferably higher than or equal to 5.5 eV, which is higher

5 than the electron affinity of the oxide semiconductor. Thus, the threshold voltage of the transistor including an oxide semiconductor can be shifted in the positive direction, and what is called a normally-off switching element can be achieved. For example, in the case of using an In-Ga-Zn-based oxynitride semiconductor film, a nitrogen-containing In-Ga-Zn-based oxynitride semiconductor film having a higher

10 nitrogen concentration than at least the semiconductor 107a, specifically having a nitrogen concentration of higher than or equal to 7 at.%, is used.

[0059]

For the barrier film 105a, a material to which oxygen is not easily diffused is preferably used. Thus, oxidation of the conductor 104a can be prevented. An

15 increase in the resistance value of the conductor 104a can be prevented.

[0060]

An oxide material from which oxygen is partly released due to heating is preferably used for the insulator 106.

[0061]

As the oxide material from which oxygen is released due to heating, oxide containing oxygen in excess of the stoichiometric composition is preferably used. Part of oxygen is released due to heating from an oxide film containing oxygen in excess of the stoichiometric composition. The oxide film containing oxygen in excess of the stoichiometric composition is an oxide film of which the amount of released oxygen

20 converted into oxygen atoms is greater than or equal to  $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>, and preferably greater than or equal to  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> in thermal desorption spectroscopy (TDS) analysis. Note that the temperature of the film surface in the TDS analysis is preferably higher than or equal to 100 °C and lower than or equal to 700 °C, or higher than or equal to 100 °C and lower than or equal to 500 °C.

25

[0062]

For example, as such a material, a material containing silicon oxide or silicon

oxynitride is preferably used. Alternatively, a metal oxide can be used. Examples of the metal oxide include aluminum oxide, aluminum oxynitride, gallium oxide, gallium oxynitride, yttrium oxide, yttrium oxynitride, hafnium oxide, and hafnium oxynitride. Note that in this specification, “silicon oxynitride” refers to a material that contains 5 oxygen at a higher proportion than nitrogen, and “silicon nitride oxide” refers to a material that contains nitrogen at a higher proportion than oxygen. In the case where an oxide semiconductor is used as a semiconductor material, oxygen released from the insulator 106 is supplied to the oxide semiconductor, so that oxygen vacancy in the oxide semiconductor can be reduced. Consequently, changes in the electrical 10 characteristics of the transistor can be reduced and the reliability of the transistor can be improved.

[0063]

When the difference in level between the top surface of the barrier film 103 and the top surface of the barrier film 105a does not exist before formation of the insulator 15 106, the insulator 106 can be formed thin.

[0064]

The semiconductor 108a may include a semiconductor such as a silicon-based semiconductor in a region where a channel is formed. It is particularly preferable that the semiconductor 108a include a semiconductor having a wider band gap than silicon. 20 The semiconductor 108a preferably includes an oxide semiconductor. A semiconductor material having a wider band gap and a lower carrier density than silicon is preferably used because off-state leakage current of the transistor can be reduced.

[0065]

For example, the semiconductor preferably includes at least indium (In) or zinc 25 (Zn) as the oxide semiconductor. It is further preferable that the semiconductor include an In-*M*-Zn-based oxide (*M* is a metal such as Al, Ti, Ga, Ge, Y, Zr, Sn, La, Ce, or Hf).

[0066]

As the semiconductor, it is particularly preferable to use an oxide 30 semiconductor film including a plurality of crystal parts whose c-axes are aligned perpendicular to a surface on which the semiconductor is formed or the top surface of the semiconductor and in which the adjacent crystal parts have no grain boundary.

[0067]

The use of such a material for the semiconductor makes it possible to provide a highly reliable transistor in which a change in the electrical characteristics is inhibited.

[0068]

5 Note that details of a preferable mode and a formation method of an oxide semiconductor that can be used for the semiconductor are described later in an embodiment described below.

[0069]

10 A semiconductor device of one embodiment of the present invention preferably includes an oxide layer, which contains as its constituent element at least one of the metal elements constituting an oxide semiconductor, between the oxide semiconductor and an insulator that overlaps the oxide semiconductor. In this way, a trap state is prevented from being formed at the interface between the oxide semiconductor and the insulator that overlaps the oxide semiconductor.

15 [0070]

That is, one embodiment of the present invention preferably has a structure in which each of the top surface and the bottom surface of at least the channel formation region of the oxide semiconductor is in contact with an oxide layer that functions as a barrier film for preventing formation of an interface state of the oxide semiconductor.

20 With this structure, formation of oxygen vacancy and entry of impurities which cause formation of carriers in the oxide semiconductor and the interface can be prevented. Thus, a highly purified intrinsic oxide semiconductor can be obtained. The highly purified intrinsic oxide semiconductor refers to an intrinsic or substantially intrinsic oxide semiconductor. It is thus possible to reduce variation in the electrical 25 characteristics of a transistor including the oxide semiconductor and to provide a highly reliable semiconductor device.

[0071]

Note that in this specification and the like, in the case of the substantially purified oxide semiconductor, the carrier density thereof is lower than  $1 \times 10^{17} /cm^3$ , 30 lower than  $1 \times 10^{15} /cm^3$ , or lower than  $1 \times 10^{13} /cm^3$ . With a highly purified intrinsic oxide semiconductor, the transistor can have stable electrical characteristics.

[0072]

The semiconductor 107a is provided between the insulator 106 and the semiconductor 108a.

[0073]

5 The semiconductor 113 is provided between the semiconductor 108a and the insulator 114 functioning as a gate insulating film.

[0074]

10 It is preferable that the semiconductor 107a and the semiconductor 113 each contain an oxide containing one or more kinds of metal elements which are the same as those of the semiconductor 108a.

[0075]

Note that the boundary between the semiconductor 108a and the semiconductor 107a and the boundary between the semiconductor 108a and the semiconductor 113 might be unclear.

15 [0076]

For example, the semiconductors 107a and 113 contain In or Ga; typically, a material such as In-Ga-based oxide, In-Zn-based oxide, or In-*M*-Zn-based oxide (*M* is Al, Ti, Ga, Y, Zr, La, Ce, Nd, or Hf) that has energy of the bottom of the conduction band closer to the vacuum level than that of the semiconductor 108a is used. Typically, 20 the difference in energy at the bottom of the conduction band between the semiconductor 107a or 113 and the semiconductor 108a is preferably 0.05 eV or more, 0.07 eV or more, 0.1 eV or more, or 0.15 eV or more and 2 eV or less, 1 eV or less, 0.5 eV or less, or 0.4 eV or less. Gallium oxide or the like can be used for the semiconductor 113. Note that the semiconductor 113 might function as part of the 25 gate insulating film depending on circumstances.

[0077]

For each of the semiconductors 107a and 113 between which the semiconductor 108a is provided, an oxide that contains a larger amount of Ga serving as a stabilizer than the semiconductor 108a is used, which can inhibit release of oxygen 30 from the semiconductor 108a.

[0078]

For example, when an In-Ga-Zn-based oxide having an atomic ratio of

In:Ga:Zn = 1:1:1, or 3:1:2 is used for the semiconductor 108a, an In-Ga-Zn-based oxide having an atomic ratio of In:Ga:Zn = 1:3:2, 1:3:4, 1:3:6, 1:6:4, 1:6:8, 1:6:10, 1:9:6, or the like can be used for the semiconductors 107a and 113. In each of the semiconductors 108a, 107a, and 113, the proportions of the atoms in the above atomic ratio vary within a range of  $\pm 20\%$  as an error. For the semiconductors 107a and 113, materials with the same composition ratio or materials with different composition ratios may be used.

[0079]

Furthermore, when an In-*M*-Zn-based oxide is used for the semiconductor 108a, an oxide containing metal elements in the atomic ratio satisfying the following conditions is preferably used for a target for forming a semiconductor film to be the semiconductor 108a. Given that the atomic ratio of the metal elements in the oxide is In:*M*:Zn =  $x_1:y_1:z_1$ ,  $x_1/y_1$  is greater than or equal to 1/3 and less than or equal to 6, preferably greater than or equal to 1 and less than or equal to 6, and  $z_1/y_1$  is greater than or equal to 1/3 and less than or equal to 6, preferably greater than or equal to 1 and less than or equal to 6. Note that when  $z_1/y_1$  is less than or equal to 6, a CAAC-OS film to be described later is easily formed. Typical examples of the atomic ratio of the metal elements in the target are In:*M*:Zn = 1:1:1, In:*M*:Zn = 3:1:2, or the like.

[0080]

When an In-*M*-Zn-based oxide is used for the semiconductors 107a and 113, an oxide containing metal elements in the following atomic ratio is preferably used for a target for forming oxide films to be the semiconductors 107a and 113. Given that the atomic ratio of the metal elements in the target is In:*M*:Zn =  $x_2:y_2:z_2$ , it is preferable that  $x_2/y_2$  be less than  $x_1/y_1$ , and  $z_2/y_2$  be greater than or equal to 1/3 and less than or equal to 6, preferably greater than or equal to 1 and less than or equal to 6. Note that when  $z_2/y_2$  is less than or equal to 6, a CAAC-OS film to be described later is easily formed. Typical examples of the atomic ratio of the metal elements in the target are In:*M*:Zn = 1:3:4, 1:3:6, 1:3:8, or the like.

[0081]

By using a material whose energy level of the bottom of the conduction band is closer to the vacuum level than that of the semiconductor 108a is used for the

semiconductors 107a and 113, a channel is mainly formed in the semiconductor 108a, so that the semiconductor 108a serves as a main current path. In this manner, when the semiconductor 108a in which a channel is formed is provided between the semiconductors 107a and 113 that contain the same metal elements, formation of 5 interface states between these films is inhibited, and thus the reliability of the electrical characteristics of the transistor is improved.

[0082]

Note that, without limitation to those described above, a material with an appropriate composition may be used depending on required semiconductor 10 characteristics and electrical characteristics (e.g., field-effect mobility and threshold voltage) of a transistor. Furthermore, in order to obtain required semiconductor characteristics of the transistor, it is preferable that the carrier density, the impurity concentration, the defect density, the atomic ratio of a metal element to oxygen, the interatomic distance, the density, and the like of the semiconductors 108a, 107a, and 15 113 be set to appropriate values.

[0083]

Here, a region (mixed region) where the semiconductor 107a and the semiconductor 108a are mixed might be provided between the semiconductor 107a and the semiconductor 108a. A mixed region of the semiconductor 108a and the semiconductor 113 might be provided between the semiconductor 108a and the semiconductor 113. The mixed region has a low density of interface states. For that reason, the stack of the semiconductor 107a, the semiconductor 108a, and the semiconductor 113 has a band structure where energy at each interface is changed continuously (continuous junction).

25 [0084]

Here, the band structure is described (FIGS. 29A and 29B). For easy understanding, the band structure is illustrated with the energy (Ec) at the bottom of the conduction band of each of the insulator 106, the semiconductor 107a, the semiconductor 108a, the semiconductor 113, and the insulator 114 functioning as a gate 30 insulating film.

[0085]

As illustrated in FIGS. 29A and 29B, the energy of the bottom of the

conduction band changes continuously in the semiconductor 107a, the semiconductor 108a, and the semiconductor 113. This can be understood also from the fact that the constituent elements are common among the semiconductors 107a, 108a, and 113 and oxygen is easily diffused among the semiconductors 107a, 108a, and 113. Thus, the 5 semiconductor 107a, 108a, and 113 have a continuous physical property although they are a stack of layers having different compositions.

[0086]

The oxide semiconductors that are stacked and contain the same main components have not only a simple stacked-layer structure of the layers but also a 10 continuous energy band (here, in particular, a well structure having a U shape in which the conduction band minimum continuously varies among the layers (U-shape well)). In other words, the stacked-layer structure is formed such that there exists no impurities that form a defect level such as a trap center or a recombination center at each interface. If impurities exist between the stacked layers in the multilayer film, the continuity of the 15 energy band is lost and carriers disappear by a trap or recombination at the interface.

[0087]

Note that FIG. 29A illustrates the case where the Ec of the semiconductor 107a are equal to the Ec of the semiconductor 113; however, they may be different from each other. For example, part of the band structure in the case where the Ec of the 20 semiconductor 113 is higher than the Ec of the semiconductor 107a is illustrated in FIG. 29B.

[0088]

According to FIGS. 29A and 29B, the semiconductor 108a serves as a well, and a channel is formed in the semiconductor 108a. Note that since the energies at the 25 bottoms of the conduction bands are changed continuously, the semiconductor 107a, the semiconductor 108a, and the semiconductor 113 can also be referred to as a U-shaped well. Furthermore, a channel formed to have such a structure can also be referred to as a buried channel.

[0089]

Note that trap states resulting from impurities or defects might be formed in the 30 vicinity of the interfaces between the insulating film such as a silicon oxide film and each of the semiconductor 107a and the semiconductor 113. Owing to the

semiconductor 107a and the semiconductor 113, the semiconductor 108a can be separated from the trap states. However, when the energy difference in Ec between the semiconductor 108a and the semiconductor 107a or the semiconductor 113 is small, an electron in the semiconductor 108a might reach the trap state by passing over the energy 5 difference. Since the electron is trapped at the trap state, a negative fixed charge is generated at the interface with the insulating film, causing the threshold voltage of the transistor to be shifted in the positive direction.

[0090]

Thus, to reduce a change in the threshold voltage of the transistor, an energy 10 difference between the Ec of the semiconductor 108a and the Ec of each of the semiconductors 107a and 113 is necessary. Each of the energy differences is preferably greater than or equal to 0.1 eV, further preferably greater than or equal to 0.15 eV.

[0091]

15 The semiconductor 107a, 108a, and 113 preferably include crystal parts. In particular, when a crystal in which c-axes are aligned is used, the transistor can have stable electrical characteristics.

[0092]

20 In the band structure illustrated in FIG. 29B, instead of the semiconductor 113, an In-Ga-based oxide (e.g., with an atomic ratio of In:Ga = 7:93) may be provided between the semiconductor 108a and the insulator 114 functioning as a gate insulating film.

[0093]

25 An oxide which has a higher electron affinity than those of the semiconductor 107a and the semiconductor 113 is used for the semiconductor 108a. For example, as the semiconductor 108a, an oxide having an electron affinity higher than those of the semiconductor 107a and the semiconductor 113 by greater than or equal to 0.07 eV and less than or equal to 1.3 eV, preferably greater than or equal to 0.1 eV and less than or equal to 0.7 eV, further preferably greater than or equal to 0.15 eV and less than or 30 equal to 0.4 eV is used. Note that the electron affinity refers to an energy difference between the vacuum level and the bottom of the conduction band.

[0094]

Here, it is preferable that the thickness of the semiconductor 108a be at least larger than that of the semiconductor 107a. The thicker the semiconductor 108a is, the larger the on-state current of the transistor is. The thickness of the semiconductor 107a may be set as appropriate as long as formation of an interface state at the interface with the semiconductor 108a is inhibited. For example, the thickness of the semiconductor 108a is larger than that of the semiconductor 107a, preferably 2 times or more, further preferably 4 times or more, still further preferably 6 times or more as large as that of the semiconductor 107a. Note that the above does not apply in the case where the on-state current of the transistor need not be increased, and the thickness of the semiconductor 107a may be equal to or greater than that of the semiconductor 108a.

[0095]

The thickness of the semiconductor 113 may be set as appropriate, in a manner similar to that of the semiconductor 107a, as long as formation of an interface state at the interface with the semiconductor 108a is inhibited. For example, the thickness of the semiconductor 113 may be set smaller than or equal to that of the semiconductor 107a. If the semiconductor 113 is thick, it may become difficult for the electric field from the conductor 115 functioning as a gate electrode to reach the semiconductor 108a. Therefore, it is preferable that the semiconductor 113 be thin; for example, thinner than the semiconductor 108a. Note that the thickness of the semiconductor 113 is not limited to the above, and may be set as appropriate depending on a driving voltage of the transistor in consideration of the withstand voltage of the insulator 114 functioning as a gate insulating film.

[0096]

Here, in the case where the semiconductor 108a is in contact with an insulator including a different constituent element (e.g., an insulator including a silicon oxide film), an interface state might be formed at the interface of the two layers and the interface state forms a channel. At this time, another transistor having a different threshold voltage appears, so that an apparent threshold voltage of the transistor is varied. However, in the transistor of this structure, the semiconductor 107a contains one or more kinds of metal elements that constitute the semiconductor 108a. Therefore, an interface state is not easily formed at the interface between the semiconductor 107a and the semiconductor 108a. Thus, providing the semiconductor

107a makes it possible to reduce variations or changes in electrical characteristics of the transistor, such as threshold voltage.

[0097]

When a channel is formed at the interface between the insulator 114 functioning as a gate insulating film and the semiconductor 108a, interface scattering occurs at the interface and the field-effect mobility of the transistor is reduced in some cases. In the transistor of this structure, however, the semiconductor 113 contains one or more kinds of metal elements that constitute the semiconductor 108a. Therefore, scattering of carriers is less likely to occur at the interface between the semiconductor 108a and the semiconductor 113, and thus the field-effect mobility of the transistor can be increased.

[0098]

The conductors 109b and 109c are formed to have a single-layer structure or a stacked-layer structure including any of metals such as aluminum, titanium, chromium, nickel, copper, yttrium, zirconium, molybdenum, silver, tantalum, and tungsten and an alloy containing any of these metals as its main component. For example, a single-layer structure of an aluminum film containing silicon, a two-layer structure in which an aluminum film is stacked over a titanium film, a two-layer structure in which an aluminum film is stacked over a tungsten film, a two-layer structure in which a copper film is stacked over a copper-magnesium-aluminum alloy film, a two-layer structure in which a copper film is stacked over a titanium film, a two-layer structure in which a copper film is stacked over a tungsten film, a three-layer structure in which a titanium film or a titanium nitride film, an aluminum film or a copper film, and a titanium film or a titanium nitride film are stacked in this order, a three-layer structure in which a molybdenum film or a molybdenum nitride film, an aluminum film or a copper film, and a molybdenum film or a molybdenum nitride film are stacked in this order, and the like can be given. Note that a transparent conductive material containing indium oxide, tin oxide, or zinc oxide may be used.

[0099]

The insulator 114 may be formed to have a single layer or stacked layers using, for example, silicon oxide, silicon oxynitride, silicon nitride oxide, aluminum oxide, hafnium oxide, gallium oxide, Ga-Zn-based metal oxide, silicon nitride, and the like.

[0100]

The insulator 114 may be formed using a high-k material such as hafnium silicate ( $\text{HfSiO}_x$ ), hafnium silicate to which nitrogen is added ( $\text{HfSi}_x\text{O}_y\text{N}_z$ ), hafnium aluminate to which nitrogen is added ( $\text{HfAl}_x\text{O}_y\text{N}_z$ ), hafnium oxide, or yttrium oxide.

5 [0101]

For example, the insulator 114 can be formed using an oxide insulating film including aluminum oxide, magnesium oxide, silicon oxide, silicon oxynitride, gallium oxide, germanium oxide, yttrium oxide, zirconium oxide, lanthanum oxide, neodymium oxide, hafnium oxide, tantalum oxide, or the like, a nitride insulating film including silicon nitride, silicon nitride oxide, aluminum nitride, aluminum nitride oxide, or the like, or a mixed material of any of these.

[0102]

As the insulator 114, like the insulator 106, an oxide insulating film that contains oxygen in excess of the stoichiometric composition is preferably used.

15 [0103]

When the specific material is used for the gate insulating film, electrons are trapped in the gate insulating film under the specific conditions and the threshold voltage can be increased. For example, like a stacked-layer film of silicon oxide and hafnium oxide, part of the gate insulating film uses a material having a lot of electron 20 trap states, such as hafnium oxide, aluminum oxide, and tantalum oxide, and the state where the potential of the gate electrode is higher than that of the source electrode or the drain electrode is kept for one second or more, typically one minute or more at a higher temperature (a temperature higher than the operating temperature or the storage temperature of the semiconductor device, or a temperature of 125 °C or higher and 450 °C or lower, typically a temperature of 150 °C or higher and 300 °C or lower). Thus, 25 electrons are moved from the semiconductor layer to the gate electrode, and some of the electrons are trapped by the electron trap states.

[0104]

In the transistor in which a necessary amount of electrons is trapped by the 30 electron trap states in this manner, the threshold voltage is shifted in the positive direction. By controlling the voltage of the gate electrode, the amount of electrons to

be trapped can be controlled, and thus the threshold voltage can be controlled. Furthermore, the treatment for trapping the electrons may be performed in the manufacturing process of the transistor.

[0105]

5 For example, the treatment is preferably performed at any step before factory shipment, such as after the formation of a wire metal connected to the source electrode or the drain electrode of the transistor, after the preceding process (wafer processing), after a wafer-dicing step, after packaging, or the like. In either case, it is preferable that the transistor be not exposed to temperatures of 125 °C or higher for one hour or

10 more after the process for trapping electrons.

[0106]

15 The conductor 115 can be formed using, for example, a metal selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, and tungsten; an alloy containing any of these metals as a component; an alloy containing any of these metals in combination; or the like. Further, one or more metals selected from manganese and zirconium may be used. Alternatively, a semiconductor typified by polycrystalline silicon doped with an impurity element such as phosphorus, or a silicide such as nickel silicide may be used. Furthermore, the conductor 115 may have a single-layer structure or a stacked-layer structure of two or more layers. For example, a

20 single-layer structure of an aluminum film containing silicon, a two-layer structure in which a titanium film is stacked over an aluminum film, a two-layer structure in which a titanium film is stacked over a titanium nitride film, a two-layer structure in which a tungsten film is stacked over a titanium nitride film, a two-layer structure in which a tungsten film is stacked over a tantalum nitride film or a tungsten nitride film, a

25 three-layer structure in which a titanium film, an aluminum film, and a titanium film are stacked in this order, and the like can be given. Alternatively, an alloy film containing aluminum and one or more metals selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, and scandium may be used.

[0107]

30 The conductor 115 can also be formed using a light-transmitting conductive material such as indium tin oxide, indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin

oxide containing titanium oxide, indium zinc oxide, or indium tin oxide to which silicon oxide is added. It is also possible to have a stacked-layer structure formed using the above light-transmitting conductive material and the above metal.

[0108]

5 Examples of a material for adjusting a work function which can be used for the conductor 115 include titanium nitride, tantalum nitride, tungsten, tungsten nitride, ruthenium, n-type polycrystalline silicon, and p-type polycrystalline silicon. For example, to obtain the transistor 100 that is normally off, a material with a high work function is preferably used. Examples of the material with a high work function 10 include tungsten, tungsten nitride, and ruthenium.

[0109]

15 Furthermore, an In-Ga-Zn-based oxynitride semiconductor film, an In-Sn-based oxynitride semiconductor film, an In-Ga-based oxynitride semiconductor film, an In-Zn-based oxynitride semiconductor film, a Sn-based oxynitride semiconductor film, an In-based oxynitride semiconductor film, or a film of a metal nitride (e.g., InN or ZnN), or the like may be provided between the conductor 115 and the insulator 114. These films each have a work function higher than or equal to 5 eV, 20 preferably higher than or equal to 5.5 eV, which is higher than the electron affinity of the oxide semiconductor. Thus, the threshold voltage of the transistor including an oxide semiconductor can be shifted in the positive direction, and what is called a normally-off switching element can be achieved. For example, as an In-Ga-Zn-based oxynitride semiconductor film, an In-Ga-Zn-based oxynitride semiconductor film having a higher nitrogen concentration than at least a semiconductor 108a, specifically 25 an In-Ga-Zn-based oxynitride semiconductor film having a nitrogen concentration higher than or equal to 7 at.%, is used.

[0110]

The above is the description of a structural example.

[0111]

30 Note that part or the whole of this embodiment can be freely combined with, applied to, or replaced with part or the whole of another embodiment.

[0112]

(Embodiment 2)

[Example of manufacturing method]

An example of a method for manufacturing the semiconductor device described in the above structure example is described below with reference to FIGS. 3A to 3D, FIGS. 4A to 4D, FIGS. 5A to 5C, and FIGS. 6A to 6C.

5 [0113]

The insulator 102 is formed over the insulator 101. An approximately 50-nm-thick silicon nitride is preferably used as the insulator 101. Alternatively, an approximately 150-nm-thick silicon oxide formed using TEOS is preferably used as the insulator 102.

10 [0114]

The insulator 101 and the insulator 102 each can be formed to have a single layer or stacked layers using, for example, silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, aluminum oxide, aluminum oxynitride, aluminum nitride oxide, aluminum nitride, and the like.

15 [0115]

The insulator 101 and the insulator 102 each may be deposited by a sputtering method, a chemical vapor deposition (CVD) method (including a thermal CVD method, a plasma enhanced CVD (PECVD) method, and the like), a metal organic CVD (MOCVD) method, a molecular beam epitaxy (MBE) method, an atomic layer deposition (ALD) method, a pulsed laser deposition (PLD) method, a high density plasma CVD (HDP-CVD) method, a low pressure CVD (LP-CVD) method, an atmospheric pressure CVD (AP-CVD) method, a collimated sputtering method, a long throw sputtering method, or the like.

[0116]

25 In particular, it is preferable that the insulator be formed by a CVD method, further preferably a plasma CVD method because embeddability can be improved. It is preferable to use a thermal CVD method, an MOCVD method, or an ALD method in order to reduce plasma damage.

[0117]

30 Next, heat treatment is performed. The heat treatment can be performed, for example, at a temperature higher than or equal to 490 °C and lower than the strain point of the substrate in an inert gas atmosphere such as a rare gas atmosphere or a nitrogen

gas atmosphere or in a reduced-pressure atmosphere.

[0118]

This heat treatment inhibits detachment or degasification of substances from a stack which includes the insulator 102 and layers provided below the insulator. The substances such as hydrogen adversely affect a semiconductor formed over the insulator 102. Note that although the heat treatment is preferably performed, it may be omitted if not particularly needed. Alternatively, the heat treatment may be performed after a step for forming an opening or groove in the insulator, which is described next.

[0119]

10 Next, the opening or groove is formed in the insulator 102. To form the opening in the insulator 102, it is preferable to select a combination of materials with which the etching selectivity of the insulator 102 with respect to the insulator 101 is high.

[0120]

15 The opening or groove in the insulator 102 can be formed by a photolithography method or the like. A resist mask is formed over the insulator 102 and an unnecessary portion of the insulator 102 is removed. Then, the resist mask is removed; thus, the opening or groove can be formed in the insulator 102 (FIG. 3A).

[0121]

20 Here, a method for processing a film is described. In the case of finely processing a film, a variety of fine processing techniques can be used. For example, a method may be used in which a resist mask formed by a photolithography process or the like is subjected to slimming treatment. Alternatively, a method may be used in which a dummy pattern is formed by a photolithography process or the like, the dummy pattern is provided with a sidewall and is then removed, and a film is etched using the remaining sidewall as a mask. In order to achieve a high aspect ratio, anisotropic dry etching is preferably used for etching of a film. Alternatively, a hard mask formed of an inorganic film or a metal film may be used.

[0122]

30 As light used to form the resist mask, light with an i-line (with a wavelength of 365 nm), light with a g-line (with a wavelength of 436 nm), light with an h-line (with a wavelength of 405 nm), or light in which the i-line, the g-line, and the h-line are mixed

can be used. Alternatively, ultraviolet light, KrF laser light, ArF laser light, or the like can be used. Exposure may be performed by liquid immersion exposure technique. As the light for the exposure, extreme ultra-violet light (EUV) or X-rays may be used. Instead of the light for the exposure, an electron beam can be used. It is preferable to 5 use extreme ultra-violet light (EUV), X-rays, or an electron beam because extremely minute processing can be performed. Note that in the case of performing exposure by scanning of a beam such as an electron beam, a photomask is not needed.

[0123]

An organic resin film having a function of improving adhesion between the 10 film to be processed and a resist film may be formed before the resist film serving as a resist mask is formed. The organic resin film can be formed to planarize a surface by covering a step under the film by a spin coating method or the like, and thus can reduce variation in thickness of the resist mask over the organic resin film. In a particularly minute process, the organic resin film is preferably formed using a material functioning 15 as an anti-reflection film against light for exposure. Examples of such an organic resin film serving as an anti-reflection film include bottom anti-reflection coating (BARC) film. The organic resin film may be removed at the same time as the removal of the resist mask or after the resist mask is removed.

[0124]

20 The barrier film 103 is provided over the insulator 102 in which the opening or groove is formed. An approximately 50-nm-thick aluminum oxide is preferably used as the barrier film 103 (FIG. 3B).

[0125]

It is preferable that the amount of released hydrogen of the stack provided 25 under the barrier film 103, which is measured by thermal desorption spectrometry (TDS) analysis, at a substrate surface temperature of 400 °C be lower than or equal to 130 %, preferably lower than or equal to 110 % of that at a substrate surface temperature of 300°C. Alternatively, it is preferable that the amount of released hydrogen molecules measured by TDS analysis at a substrate surface temperature of 30 450 °C be lower than or equal to 130 %, preferably lower than or equal to 110 % of that at a substrate surface temperature of 350 °C.

[0126]

The barrier film 103 has a function of inhibiting diffusion of water and hydrogen from the layers under the barrier film 103. Note that the barrier film 103 may have an opening or a plug for electrically connecting an electrode or a wiring provided over the barrier film 103 to an electrode or a wiring provided under the barrier film 103.

[0127]

Examples of a material that can be used for the barrier film 103 include silicon nitride, silicon nitride oxide, aluminum oxide, aluminum oxynitride, gallium oxide, gallium oxynitride, yttrium oxide, yttrium oxynitride, hafnium oxide, and hafnium oxynitride. Aluminum oxide is particularly preferable because of its excellent barrier property against water, hydrogen, or oxygen.

[0128]

The barrier film 103 may be a stack of a layer of a material relatively impermeable to water or hydrogen and a layer containing an insulating material. The barrier film 103 may be, for example, a stack of a layer containing silicon oxide or silicon oxynitride, a layer containing a metal oxide, and the like.

[0129]

For the barrier film 103, a material relatively impermeable to oxygen is preferably used. The material given above has excellent barrier properties against oxygen as well as hydrogen and water. The use of any of the materials can suppress diffusion of oxygen released when the insulator 106 formed later is heated to the layers below the barrier film 103. As a result, the amount of oxygen which is released from the insulator 106 to be supplied to a semiconductor 107, a semiconductor 108, and the semiconductor 113 can be increased.

[0130]

The amount of water and hydrogen contained in the barrier film 103 itself is also preferably low. For example, it is preferable to use, for the barrier film 103, a material having an amount of released hydrogen molecules ( $M/z = 2$ ) measured by TDS of less than  $2 \times 10^{15}/\text{cm}^2$ , preferably less than  $1 \times 10^{15}/\text{cm}^2$ , further preferably less than  $5 \times 10^{14}/\text{cm}^2$  at a substrate surface temperature ranging from 20 °C to 600 °C.

Alternatively, it is preferable to use, for the barrier film 103, a material having an amount of released water molecules (mass-to-charge ratio  $M/z = 18$ ) measured by TDS of less than  $1 \times 10^{16} / \text{cm}^2$ , preferably less than  $5 \times 10^{15} / \text{cm}^2$ , and further preferably less than  $2 \times 10^{12} / \text{cm}^2$  at a substrate surface temperature from 20 °C to 600 °C.

5 [0131]

Next, a conductor 104 is provided over the barrier film 103 (FIG. 3C).

[0132]

It is preferable that the conductor 104 be formed using a metal selected from tantalum, tungsten, titanium, molybdenum, chromium, niobium, and the like, or an alloy material or a compound material including any of the metals as its main component. 10 Alternatively, polycrystalline silicon to which an impurity such as phosphorus is added can be used. Still alternatively, a stacked-layer structure including a film of metal nitride and a film of any of the above metals may be used. As a metal nitride, tungsten nitride, molybdenum nitride, or titanium nitride can be used. When the metal nitride 15 film is provided, adhesiveness of the metal film can be increased; thus, separation can be prevented.

[0133]

The conductor 104 can also be formed using a light-transmitting conductive material such as indium tin oxide, indium oxide containing tungsten oxide, indium zinc 20 oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium zinc oxide, or indium tin oxide to which silicon oxide is added. It is also possible to have a stacked-layer structure formed using the above light-transmitting conductive material and the above metal.

[0134]

25 The conductor 104 can be formed by a sputtering method, an evaporation method, a CVD method (including a thermal CVD method, an MOCVD method, a PECVD method, and the like), or the like. It is preferable to use a thermal CVD method, an MOCVD method, or an ALD method in order to reduce plasma damage.

[0135]

30 Next, the conductor 104 may be planarized by a chemical mechanical polishing (CMP) method or the like.

[0136]

At this time, the conductor 104 may be polished by a CMP method until the level of the top surface of the barrier film 103 over a region of the insulator 102 in which the opening or groove is not provided is the same as that of the top surface of the conductor 104, or polishing may be stopped in the middle of the processing.

[0137]

Next, the conductor 104 is etched to obtain the conductor 104a. Here, it is preferable that the level of the top surface of the conductor 104a be lower than that of the top surface of the barrier film 103 over the region of the insulator 102 in which the opening or groove is not provided, in particular, be lower than it by approximately 50 nm (FIG. 3D).

[0138]

Next, a barrier film 105 is provided over the barrier film 103 and the conductor 104a (FIG. 4A).

15 [0139]

An In-Ga-Zn-based oxynitride semiconductor film, an In-Sn-based oxynitride semiconductor film, an In-Ga-based oxynitride semiconductor film, an In-Zn-based oxynitride semiconductor film, a Sn-based oxynitride semiconductor film, an In-based oxynitride semiconductor film, a metal nitride (InN, ZnN, or the like) film can be provided as the barrier film 105. These films each have a work function higher than or equal to 5 eV, preferably higher than or equal to 5.5 eV, which is higher than the electron affinity of the oxide semiconductor. Thus, the threshold voltage of the transistor including an oxide semiconductor can be shifted in the positive direction, and what is called a normally-off switching element can be achieved. For example, as an 20 In-Ga-Zn-based oxynitride semiconductor film, an In-Ga-Zn-based oxynitride semiconductor film having a higher nitrogen concentration than at least the semiconductor 108a, specifically an In-Ga-Zn-based oxynitride semiconductor film having a nitrogen concentration higher than or equal to 7 at.%, is used.

25 [0140]

For the barrier film 105, a material to which oxygen is not easily diffused is preferably used. Therefore, oxidation of the conductor 104a can be prevented, and an increase in the resistance value of the conductor 104a can be inhibited. The barrier

film 105 can be formed using a material, a deposition method, and the like similar to those of the barrier film 103.

[0141]

Next, the barrier film 105 is polished by a CMP method until the level of the top surface of the barrier film 103 over the region of the insulator 102 in which the opening or groove is not provided is the same as that of the top surface of the barrier film 105, whereby the barrier film 105a is obtained (FIG. 4B). Although FIG. 4B illustrates the example in which the barrier film 105a is obtained by polishing using a CMP method, the barrier film 105 is not necessarily polished.

10

[0142]

Next, the insulator 106 having a thickness of approximately 100 nm is provided (FIG. 4C).

[0143]

15

It is preferable that the insulator 106 be an insulator which releases oxygen by heat treatment or the like in a later step. The released oxygen is used in order to reduce oxygen vacancy in the oxide semiconductor, so that the electrical characteristics and reliability of the transistor can be improved. Meanwhile, in the case where a semiconductor element or the like using single crystal silicon is formed below the stack 10, when released oxygen reaches the single crystal silicon, the electrical characteristics 20 and reliability of the semiconductor element might deteriorate. The aluminum oxide film has a function of preventing oxygen from being mixed into the element positioned below the stack 10. Thus, even if the silicon oxynitride film containing excess oxygen is provided, an element (e.g., a transistor including single crystal silicon) with good electrical characteristics and high reliability can be manufactured.

25

[0144]

30

The insulator 106 can be formed by, for example, a sputtering method, a CVD method (including a thermal CVD method, a PECVD method, and the like), an MOCVD method, an MBE method, an ALD method, a PLD method, or the like. In particular, it is preferable that the insulator be formed by a CVD method, further preferably a plasma CVD method, because coverage can be further improved. It is preferable to use a thermal CVD method, an MOCVD method, or an ALD method in order to reduce plasma damage.

[0145]

To make the insulator 106 contain excess oxygen, the insulator 106 may be formed in an oxygen atmosphere, for example. Alternatively, a region excessively containing oxygen may be formed by introducing oxygen into the insulator 106 that has 5 been formed. Both the methods may be combined.

[0146]

For example, oxygen (at least including any of oxygen radicals, oxygen atoms, and oxygen ions) is introduced into the insulator 106 which has been formed, whereby a region excessively containing oxygen is formed. Oxygen can be introduced by an ion 10 implantation method, an ion doping method, a plasma immersion ion implantation method, plasma treatment, or the like.

[0147]

A gas containing oxygen can be used for oxygen introducing treatment. As the gas containing oxygen, oxygen, dinitrogen monoxide, nitrogen dioxide, carbon 15 dioxide, carbon monoxide, and the like can be used. Furthermore, a rare gas and/or hydrogen may be included in the gas containing oxygen for the oxygen introduction treatment. For example, a mixed gas of carbon dioxide, hydrogen, and argon can be used.

[0148]

20 After the insulator 106 is formed, the insulator 106 may be subjected to planarization treatment using a CMP method or the like to improve the planarity of the top surface of the insulator 106.

[0149]

It is preferable that the top surface of the barrier film 103 and the top surface of 25 the barrier film 105a be processed by a CMP method so that a level difference is unlikely to be formed. In other words, the process is performed so that a level difference is not formed on the surface where the insulator 106 is formed, whereby the thickness of the insulator 106 can be small. Here, although the thickness of the insulator 106 is 100 nm, it can be smaller than 100 nm.

30 [0150]

Next, the semiconductor 107 and the semiconductor 108 are formed. For example, a 15-nm-thick oxide semiconductor and a 20- to 40-nm-thick oxide

semiconductor are used as the semiconductor 107 and the semiconductor 108, respectively. These semiconductors are preferably formed by a sputtering method. At this time, the oxide semiconductor of the semiconductor 107 is formed using a target having an atomic ratio of In:Ga:Zn = 1:3:4. The oxide semiconductor of the semiconductor 108 is formed using a target having an atomic ratio of In:Ga:Zn = 1:1:1.

5 [0151]

The semiconductors 107 and 108 are preferably formed successively without contact with the air.

10 [0152]

After the semiconductors 107 and 108 are formed, heat treatment is preferably performed. The heat treatment may be performed at a temperature higher than or equal to 250 °C and lower than or equal to 650 °C, preferably higher than or equal to 300 °C and lower than or equal to 500 °C, in an inert gas atmosphere, in an atmosphere containing an oxidizing gas at 10 ppm or more, or under reduced pressure.

15 Alternatively, the heat treatment may be performed in such a manner that heat treatment is performed in an inert gas atmosphere, and then another heat treatment is performed in an atmosphere containing an oxidization gas at 10 ppm or more, in order to compensate desorbed oxygen. The heat treatment may be performed just after the formation of the semiconductors or may be performed after the semiconductors are processed into the 20 island-shaped semiconductor. Through the heat treatment, oxygen can be supplied from the insulator 106 or the like to the semiconductors 107 and 108; thus, oxygen vacancy in the semiconductor film can be reduced.

[0153]

Next, a conductor 109 is provided. Approximately 100-nm-thick tungsten is 25 preferably used as the conductor 109. A sputtering method can be used for depositing the conductor 109.