(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6463619号

(P6463619)

(45) 発行日 平成31年2月6日(2019.2.6)

(24) 登録日 平成31年1月11日(2019.1.11)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4B 1/10 (2006.01)  | HO4B 1/10 L  |

| HO4B 3/06 (2006.01)  | HO4B 3/06 C  |

| HO4L 25/03 (2006.01) | HO4L 25/03 C |

| HO3M 1/74 (2006.01)  | HO3M 1/74    |

請求項の数 21 (全 13 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2014-217922 (P2014-217922) |

| (22) 出願日     | 平成26年10月27日 (2014.10.27)     |

| (65) 公開番号    | 特開2015-89126 (P2015-89126A)  |

| (43) 公開日     | 平成27年5月7日 (2015.5.7)         |

| 審査請求日        | 平成29年10月25日 (2017.10.25)     |

| (31) 優先権主張番号 | 61/898, 421                  |

| (32) 優先日     | 平成25年10月31日 (2013.10.31)     |

| (33) 優先権主張国  | 米国 (US)                      |

| (31) 優先権主張番号 | 14/340, 463                  |

| (32) 優先日     | 平成26年7月24日 (2014.7.24)       |

| (33) 優先権主張国  | 米国 (US)                      |

|           |                                                                             |

|-----------|-----------------------------------------------------------------------------|

| (73) 特許権者 | 512187343<br>三星ディスプレイ株式会社<br>Samsung Display Co., Ltd.<br>大韓民国京畿道龍仁市器興区三星路1 |

| (74) 代理人  | 100121382<br>弁理士 山下 託嗣                                                      |

| (72) 発明者  | モハマド ヘクマット<br>アメリカ合衆国、95112 カリフォルニア、サン ジョセ、デブコン ドライブ 217                    |

| (72) 発明者  | アミール アミルカニー<br>アメリカ合衆国、95112 カリフォルニア、サン ジョセ、デブコン ドライブ 217                   |

最終頁に続く

(54) 【発明の名称】受信機およびこれを備えるディスプレイ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のFET(電界効果トランジスタ)および第2のFETが差動対の構成で接続される、第1のFETおよび第2のFETを備える第1の差動増幅器と、

第1のDAC出力が前記第1のFETのバルク端子に接続される、第1のDAC出力を備える電圧モードデジタルアナログコンバータ(DAC)と、

前記DACに接続されるDAC電圧制限回路と、

を備え、

前記DAC電圧制限回路は、

前記DACの最大DAC出力電圧に等しい複製電圧を生成する複製回路と、

前記最大DAC出力電圧を制御する制御電圧を生成するフィードバック増幅器とを備え、この制御電圧は、前記複製電圧と、前記差動対の構成のテール部の電圧との差に比例する予測的決定フィードバックイコライゼーションを有する受信機。

## 【請求項 2】

第1のFET(電界効果トランジスタ)および第2のFETが差動対の構成で接続される、第1のFETおよび第2のFETを備える第1の差動増幅器と、

第1のDAC出力が前記第1のFETのバルク端子に接続される、第1のDAC出力を備える電圧モードデジタルアナログコンバータ(DAC)と、

前記DACに接続されるDAC電圧制限回路と、

を備え、

10

20

前記 D A C は、

D A C 抵抗器と、

複数の分岐と、

バイアス制御入力と、

を備え、

前記 D A C 電圧制限回路は、

前記第 1 の F E T の一の入出力端子、及び、前記第 2 の F E T の対応する一の入出力端子に共に接続されるノードである、前記第 1 の差動増幅器の共通ノードに接続される基準電圧入力と、

前記 D A C の複数の分岐のうちの一つの分岐のサイズが調節された複製を備え、且つ、複製電圧出力を有する複製回路と、

を備える予測的決定フィードバックイコライゼーションを有する受信機。

【請求項 3】

前記 D A C の複数の分岐のそれぞれは、分岐電流ソースを備えることを特徴とする請求項 2 に記載の受信機。

【請求項 4】

前記 D A C の第 1 の分岐の分岐電流ソースは、第 1 のゲート幅を有する F E T として前記 F E T のゲートが D A C のバイアス制御入力に接続される F E T を備え、前記 D A C の複数の分岐のうちの残りの分岐の分岐電流ソースは、前記第 1 のゲート幅の 2 の累乗に増加するゲート幅を有する F E T を備えることを特徴とする請求項 3 に記載の受信機。

【請求項 5】

前記複製回路は、直列に接続された、電流ソース複製 F E T、スイッチングトランジスタ複製 F E T および複製抵抗器を備えることを特徴とする請求項 3 に記載の受信機。

【請求項 6】

前記 D A C の複数の分岐のそれぞれの分岐電流ソースはそれぞれのゲート幅を有する F E T を備え、

前記複製抵抗器の抵抗は、 $k$  が複製サイズ調節要素であるとき、前記 D A C 抵抗器の抵抗の  $k$  倍であり、

前記電流ソース複製 F E T のゲート幅は、前記 D A C の複数の分岐の分岐電流ソースのゲート幅の和であることを特徴とする請求項 5 に記載の受信機。

【請求項 7】

前記 D A C 電圧制限回路は、第 1 の入力および第 2 の入力を有し、前記第 1 の入力は複製電圧出力に接続され、前記第 2 の入力は基準電圧入力に接続されるフィードバック増幅器を備えることを特徴とする請求項 5 に記載の受信機。

【請求項 8】

前記フィードバック増幅器は、前記第 1 の入力における電圧が前記第 2 の入力における電圧と実質的に等しく維持されるように構成されることを特徴とする請求項 7 に記載の受信機。

【請求項 9】

前記フィードバック増幅器は出力を備え、前記出力は第 1 のバイアス制御 F E T のゲートに接続され、前記第 1 のバイアス制御 F E T は第 2 のバイアス制御 F E T と直列に接続され、前記第 2 のバイアス制御 F E T はダイオード接続されることを特徴とする請求項 8 に記載の受信機。

【請求項 10】

前記第 2 のバイアス制御 F E T は電流ミラーにおいて基準装置として作動するように構成され、前記電流ソース複製 F E T および前記 D A C の分岐電流ソースの F E T は電流ミラーにおけるミラー装置であることを特徴とする請求項 9 に記載の受信機。

【請求項 11】

前記第 1 の差動増幅器の前記第 1 の F E T および前記第 2 の F E T は  $n$  - チャンネル F E T であり、

10

20

30

40

50

前記第1のFETのソースは前記第1の差動増幅器の共通ノードに接続され、前記第2のFETのソースは前記第1の差動増幅器の共通ノードに接続されることを特徴とする請求項10に記載の受信機。

【請求項12】

前記DACは第1のDAC出力および第2のDAC出力を備える差動DACであり、前記第2のDAC出力は前記第2のFETのバルク端子に接続されることを特徴とする請求項2に記載の受信機。

【請求項13】

前記DACの複数の分岐のそれぞれは、分岐電流ソースを備えることを特徴とする請求項12に記載の受信機。

10

【請求項14】

前記DACの第1の分岐の前記分岐電流ソースは、第1のゲート幅を有するFETとして前記FETのゲートが前記DACのバイアス制御入力に接続されるFETを備え、前記DACの複数の分岐のうちの残りの分岐の分岐電流ソースは、前記第1のゲート幅の2の累乗で増加するゲート幅を有するFETを備えることを特徴とする請求項13に記載の受信機。

【請求項15】

前記複製回路は、直列に接続された、電流ソース複製FETと、スイッチングトランジスタ複製FETおよび複製抵抗器を備えることを特徴とする請求項13に記載の受信機。

20

【請求項16】

前記DACの複数の分岐のそれぞれの分岐電流ソースは、それぞれのゲート幅を有するFETを備え、

前記複製抵抗器の抵抗は、 $k$ が複製サイズ調節要素であるとき、前記DAC抵抗器の抵抗の $k$ 倍であり、

前記電流ソース複製FETのゲート幅は、前記DACの複数の分岐の分岐電流ソースのゲート幅の和であることを特徴とする請求項15に記載の受信機。

【請求項17】

前記DAC電圧制限回路は第1の入力および第2の入力を有し、前記第1の入力は複製電圧出力に接続され、前記第2の入力は基準電圧入力に接続されるフィードバック増幅器を備えることを特徴とする請求項15に記載の受信機。

30

【請求項18】

前記フィードバック増幅器は増幅器出力を備え、前記増幅器出力は第1のバイアス制御FETのゲートに接続され、前記第1のバイアス制御FETは第2のバイアス制御FETと直列に接続され、前記第2のバイアス制御FETはダイオード接続されることを特徴とする請求項17に記載の受信機。

【請求項19】

第1のFETおよび第2のFETを備える第2の差動増幅器をさらに備え、前記第2の差動増幅器における前記第1のFETおよび第2のFETは差動対の構成で接続されることを特徴とする請求項12に記載の受信機。

【請求項20】

前記第1のDAC出力は、前記第2の差動増幅器の第2のFETのバルク端子に接続され、前記第2のDAC出力は、前記第2の差動増幅器の第1のFETのバルク端子に接続されることを特徴とする請求項19に記載の受信機。

40

【請求項21】

デジタル出力を備えるタイミングコントローラと、

I C入力、及び、請求項1に記載の受信機を備えるドライバ集積回路I Cと、を備え、

前記受信機の受信機入力が、前記I C入力に接続され、

前記タイミングコントローラの前記デジタル出力は、前記ドライバI Cの前記I C入力に接続されることを特徴とするディスプレイ。

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

以下の説明は、理想的ではない（例えば、損失性）チャンネルを通じたデジタルデータの伝送に係り、さらに詳しくは、理想的ではないチャンネルを通じた伝送の結果として現れるシンボル間干渉を緩和するための予測的決定フィードバックイコライザに関する。

## 【背景技術】

## 【0002】

高速デジタルデータリンクは、特に、伝送チャンネル内に損失、反射またはその他の不完全性がある状況下でシンボル間干渉による困難をきたすことがある。シンボル間干渉の影響により与えられたクロックサイクル中に受信された信号が、当該クロックサイクル中に送信機において送信されたビットとそれ以前の数回のクロックサイクル中に送信されたビットの線形組み合わせになることがある。シンボル間干渉の影響は、決定フィードバックイコライゼーション（decision feedback equalization : DFE）と呼ばれる技術を用いて緩和することができ、この技術は、受信された信号を数回の以前のクロックサイクル中に受信されたビットの線形組み合わせに対して、それぞれのクロックサイクル中のサンプリング時点で訂正することを含む。

10

## 【0003】

直前に受信されたビットからの寄与は第1のタップ（tap）と呼ばれ、予測的決定フィードバックイコライゼーション（予測的DFE、推論的なDFEまたはループ展開DFEとも呼ばれる）と呼ばれる技術を用いて生成することができるが、この技術においては、一つの項は直前に受信されたビットにおける受信された1に対応し、他の一つの項は受信された0に対応する二つの訂正項が計算されて、直前のクロックサイクル上において受信されたビットの二進値が使用可能になると、これらの二つの訂正項のうちの適切な項をマルチプレクサ（MUX）を用いて選択する。

20

特に、電流デジタルアナログコンバータ（DAC）は比較器の出力電流に電流を加えるために用いられることがある、これは、受信された信号をサンプリングするために用いられるクロック動作比較器内において、差動対として実現される（組み入れられる）。出力に加えられた電流は、正しいサイズ調節要素をもって以前のビットを効果的に実現する。この接近方式（アプローチ）はいくつかの欠点を有している。DACは電力を消耗し、静電容量負荷を示すため、回路の速度を制限する。

30

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

このため、適切な電力を消耗しながら改善された速度を達成する予測的フィードバックイコライゼーションのためのシステムが求められている。

## 【課題を解決するための手段】

## 【0005】

予測的決定フィードバックイコライザにおいて、一つまたはそれ以上の電界効果トランジスタ（FET）のボディバイアス（body bias、基板バイアス）が予測的タップのためのオフセットを提供するために用いられる。一実施形態において、予測的決定フィードバックイコライザの予測タップは差動増幅器構成内において二つのFETで構成された差動増幅器を備え、一つまたは二つのFETのボディバイアスは差動増幅器内においてオフセットを提供するように制御される。一実施形態において、ボディバイアス電圧を提供するためにDAC抵抗器を駆動する電流DACが用いられ、電流DACの電流ソースのバイアスを制御するために最大可能DAC出力電圧を形成する複製（replica、レプリカ）回路を備えるフィードバック回路が用いられる。

40

## 【0006】

本発明の一実施形態によれば、第1の電界効果トランジスタ（FET）および第2のFETが差動対の構成で接続される第1の電界効果トランジスタ（FET）および第2のF

50

E Tを備える第1の差動増幅器と、第1のD A C出力が前記第1のF E Tのバルク端子に接続される第1のD A C出力を備える電圧モードデジタルアナログコンバータ(D A C)と、前記D A Cに接続されるD A C電圧制限回路と、を備える予測的決定フィードバックイコライゼーションを有する受信機が提供される。

## 【0007】

一実施形態において、前記D A Cは、D A C抵抗器と、複数の分岐と、バイアス制御入力と、を備え、前記D A C電圧制限回路は、前記第1の差動増幅器の共通ノードに接続される基準電圧入力と、前記D A Cの複数の分岐のうちの一つの分岐のサイズが調節された複製(replica)を備え、且つ、複製電圧出力を有する複製回路と、を備える。

## 【0008】

一実施形態において、前記D A Cの複数の分岐のそれぞれは、分岐電流ソースを備える。

## 【0009】

一実施形態において、前記D A Cの第1の分岐の分岐電流ソースは、第1のゲート幅を有するF E Tとして前記F E TのゲートがD A Cのバイアス制御入力に接続されるF E Tを備え、前記D A Cの複数の分岐のうちの残りの分岐の分岐電流ソースは、前記第1のゲート幅の2の累乗に増加するゲート幅を有するF E Tを備える。

## 【0010】

一実施形態において、前記複製回路は直列に接続された電流ソース複製F E T、スイッチングトランジスタ複製F E Tおよび複製抵抗器を備える。

## 【0011】

一実施形態において、前記D A Cの複数の分岐のそれぞれの分岐電流ソースはそれぞれのゲート幅を有するF E Tを備え、前記複製抵抗器の抵抗は、kが複製サイズ調節要素(replica scaling factor)であるとき、前記D A C抵抗器の抵抗のk倍であり、前記電流ソース複製F E Tのゲート幅は、前記D A Cの複数の分岐の分岐電流ソースのゲート幅のゲート幅の和である。

## 【0012】

一実施形態において、前記バイアス回路は、第1の入力および第2の入力を有し、前記第1の入力は複製電圧出力に接続され、前記第2の入力は基準電圧入力に接続されるフィードバック増幅器を備える。

## 【0013】

一実施形態において、前記フィードバック増幅器は、前記第1の入力における電圧が前記第2の入力における電圧と実質的に等しく維持されるように構成される。

## 【0014】

一実施形態において、前記フィードバック増幅器は出力を備え、前記出力は第1のバイアス制御F E Tのゲートに接続され、前記第1のバイアス制御F E Tは第2のバイアス制御F E Tと直列に接続され、前記第2のバイアス制御F E Tはダイオード接続される。

## 【0015】

一実施形態において、前記第2のバイアス制御F E Tは電流ミラーにおいて基準装置として作動するように構成され、前記電流ソース複製F E Tおよび前記D A Cの分岐電流ソースのF E Tは電流ミラーにおけるミラー装置である。

## 【0016】

一実施形態において、前記第1の差動増幅器の前記第1のF E Tおよび前記第2のF E Tはn-チャンネルF E Tであり、前記第1のF E Tのソースは前記第1の差動増幅器の共通ノードに接続され、前記第2のF E Tのソースは前記第1の差動増幅器の共通ノードに接続される。

## 【0017】

一実施形態において、前記D A Cの複数の分岐のそれぞれは、分岐電流ソースを備える。

## 【0018】

10

20

30

40

50

一実施形態において、前記受信機は第1のD A C出力および第2のD A C出力を備え、前記第2のD A C出力は前記第2のF E Tのバルク端子に接続される。

【0019】

一実施形態において、前記D A Cの第1の分岐の前記電流ソースは、第1のゲート幅を有するF E Tとして前記F E Tのゲートが前記D A Cのバイアス制御入力に接続されるF E Tを備え、前記D A Cの複数の分岐のうちの残りの分岐の分岐電流ソースは、前記第1のゲート幅の2の累乗に増加するゲート幅を有するF E Tを備える。

【0020】

一実施形態において、前記複製回路は、直列に接続された電流ソース複製F E Tと、スイッチングトランジスタ複製F E Tおよび複製抵抗器を備える。

10

【0021】

一実施形態において、前記D A Cの複数の分岐のそれぞれの分岐電流ソースは、それぞれのゲート幅を有するF E Tを備え、前記複製抵抗器の抵抗は、 $k$ が複製サイズ調節要素(replica scaling factor)であるとき、前記D A C抵抗器の抵抗の $k$ 倍であり、前記電流ソース複製F E Tのゲート幅は、前記D A Cの複数の分岐の分岐電流ソースのゲート幅のゲート幅の和である。

【0022】

一実施形態において、前記バイアス回路は第1の入力および第2の入力を有し、前記第1の入力は複製電圧出力に接続され、前記第2の入力は基準電圧入力に接続されるフィードバック増幅器を備える。

20

【0023】

一実施形態において、前記フィードバック増幅器は増幅器出力を備え、前記増幅器出力は第1のバイアス制御F E Tのゲートに接続され、前記第1のバイアス制御F E Tは第2のバイアス制御F E Tと直列に接続され、前記第2のバイアス制御F E Tはダイオード接続される。

【0024】

一実施形態において、前記受信機は、第1のF E Tおよび第2のF E Tを備える第2の差動増幅器をさらに備え、前記第1のおよび第2のF E Tは異なる対の構成で接続される。

【0025】

30

一実施形態において、前記第1のD A C出力は、前記第2の差動増幅器の第2のF E Tのバルク端子に接続され、前記第2のD A C出力は、前記第2の差動増幅器の第1のF E Tのバルク端子に接続される。

【0026】

一実施形態において、前記受信機は、デジタル出力を備えるタイミングコントローラと、I C入力と、前記I C入力に接続される受信機の受信機入力と、を備えるドライバ集積回路I Cと、を備え、前記タイミングコントローラの前記デジタル出力は、前記ドライバI Cの前記I C入力に接続される。

【図面の簡単な説明】

【0027】

40

本発明のこのような特徴と利点およびその他の特徴とメリットは、明細書、請求項および添付図面を参照して認識されて理解される筈である：

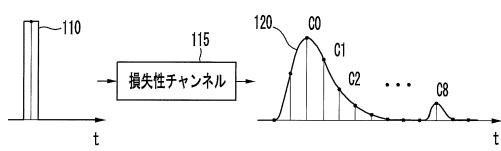

【図1A】理想的ではない(例えば、損失性)チャンネルへの入力信号と前記理想的ではないチャンネルからの出力を示し、シンボル間干渉の効果を示す概略的構成図である。

【図1B】シンボル間干渉の効果を示す信号、およびシンボル間干渉の効果が本発明の一実施形態に係るフィードバックイコライゼーションによって緩和された信号を示すグラフである。

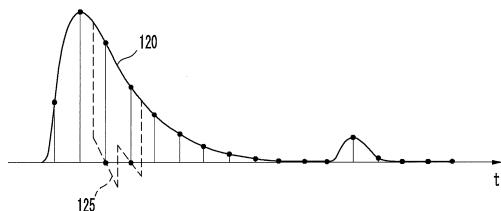

【図2】直接的な決定フィードバックイコライゼーションのためのシステムの概略的構成図である。

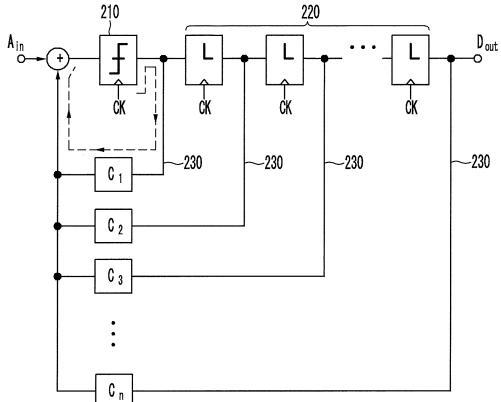

【図3】本発明の一実施形態に係る予測的決定フィードバックイコライゼーションのため

50

のシステムの概略的構成図である。

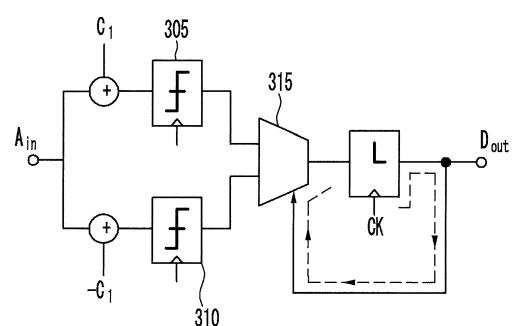

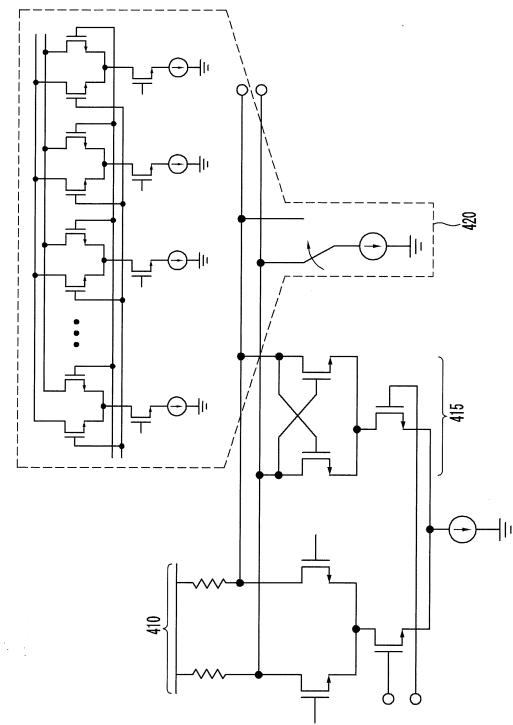

【図4】スライサの出力に電流デジタルアナログコンバータ（D A C）を用いた予測的決定フィードバックイコライゼーションのためのシステムの概略的構成図である。

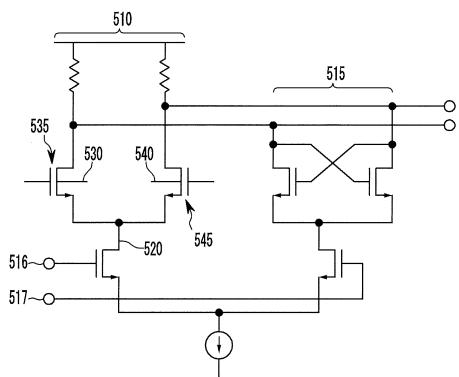

【図5】本発明の一実施形態に係るボディバイアスを有するスライサの概略的構成図である。

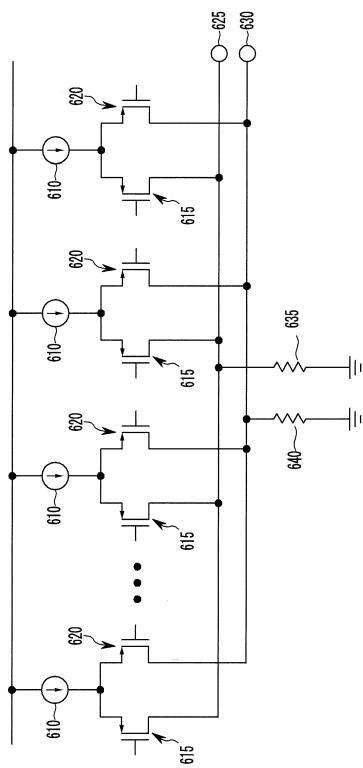

【図6】本発明の一実施形態に係るボディバイアスを提供するための電圧モードD A Cの概略的構成図である。

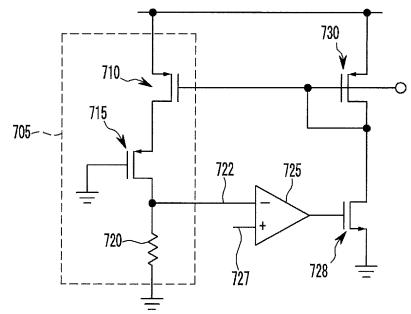

【図7】本発明の一実施形態に係るD A Cバイアスを調節するための回路の概略的構成図である。

【図8】本発明の一実施形態に係るボディバイアスを用いる予測的決定フィードバックイコライゼーションを採用したディスプレイのブロック図である。 10

【発明を実施するための態様】

【0028】

以下、添付図面に結び付けて記述した詳細な説明は、本発明により提供される予測的決定フィードバックイコライザ（predictive decision feedback equalizers）のためのボディバイアススライサデザイン（body-biased slicer design）の実施形態を記述するためのものであり、本発明を構成したり使用したりする形態のみを開示するためのものではない。この説明は、例示された実施形態と結びつけて本発明の特徴を記述する。しかしながら、本発明の思想と範囲内において実現されるように意図された他の実施形態によっても同一若しくは均等の機能および構造が達成される。本発明の他の個所に表示されたように、同じ要素の番号は、同じ要素または特徴を示すためのものである。 20

【0029】

本特許出願は2013年10月31日付で出願され、タイトルが「予測的決定フィードバックイコライザのためのボディバイアススライサデザイン（BODY - BIASED SLICER DESIGN FOR PREDICTIVE DECISION FEEDBACK EQUALIZERS）」である米国予備出願第61/898,421号に対する優先権を主張し、これに伴う利益を受けることを希望し、前記出願の全体的な内容は本明細書に参照として取り込まれている。

【0030】

図1Aを参照すると、一実施形態において、送信機によって送信された信号が単一の正方形パルス110である場合、この信号は、理想的ではない（例えば、損失性）チャンネル115を介して伝送された後に、送信された信号とは異なる形態を有する受信信号120となる。受信された信号120は、主サンプリング時間、すなわち、データが受信機においてサンプリングされる時間に対応するサンプリング時間に $C_0$ の値を有し、理想的ではないチャンネルの不完全な特性のために、送信されたパルス110の効果が複数のサンプリング間隔に亘って持続されて残余値 $C_1$ 、 $C_2$ などと呼ばれる残余信号値を取る。このような残余信号は、後続して送信されるデータパルスに対応する信号と同じ時間に受信され、その上に重なるためシンボル間干渉を引き起こす。 30

【0031】

図1Bを参照すると、送信されたパルスが0であるか、あるいは、1であるかに対する決定が受信機において下された後に、決定フィードバックイコライゼーションが使用される。一応このような決定が下されると、送信されたパルスの形態が推定され、複数のサンプリング時間遅延における残余値が計算され、このようにして計算された残余値を、後続して受信される信号120から差し引いて、補正された信号125においてシンボル間干渉の影響を低減する。 40

【0032】

図2を参照すると、関連技術の実施形態において、受信された信号をクロック動作比較器210で、次いで、シフトレジスタ220で処理することにより、直接的D F Eが達成される。クロック動作比較器の出力とシフトレジスタのタップを含むそれぞれの連続したタップ230は、以前のサンプリング時間に受信したビットを含む。それぞれのタップ2 50

30 には残余値に対応する定数が乗算され、受信信号にフィードバックされて加算され、これをもって以前に受信されたビットからの残余値を打ち消す。最初のタップからの経路は臨界経路 (critical path) と呼ばれ、これは経路に沿うタイミングが直接的 D F E 回路の動作において最大の難題 (challenge) を提示するためである：この経路において、以前のビットが解決されてそのタップの値  $C_1$  が乗算され、次いで、一つの単位間隔 (unit interval : U I) における電流入力から差し引かれる。

#### 【0033】

図 3 を参照すると、関連する技術の一実施形態に係る予測的 D F E において、回路の二つの分岐における入力信号に異なるオフセットを加算し、各結果をそれぞれのクロック動作比較器 305、310 におけるデジタル値に変換することにより、受信されたビットの 0 または 1 にそれぞれ対応する二つの可能な結果が予め計算される。以前に受信されたビットが 0 であるか、あるいは、1 であるかに対する決定が受信機において下されるとすぐに、マルチブレクサ 315 において正しい結果が選択される。予測的 D F E は、一つまたはそれ以上の予測タップを有する。図 4 を参照すると、前記事前計算 (pre-calculation) は、それぞれ電界効果トランジスタ (FET) から構成された差動増幅器 410、ラッチ 415 および電流 D A C 420 を備える回路を用いて達成することができる。前記差動増幅器とラッチはクロックの補完位相によってクロック動作されて、クロック動作比較器または「スライサ (slicer)」を形成し、前記電流 D A C はオフセット電流を前記差動増幅器の出力に加算する。この方法において用いられた前記電流 D A C は追加的な電力を消耗し、最初のタップがシステムにおいて最大のタップである場合があるため、電流 D A C を前記スライサに接続することにより課せられる寄生静電容量と共に伴う回路速度における性能減少がかなり多い。

#### 【0034】

図 5 を参照すると、一実施形態において、予測的 D F E 回路において予測タップ、例えば、最初のタップが能動的にスイッチングを行わず、このため、補正を高速ノードに加算する必要がないという洞察的予測が予測的 D F E 回路において用いられる。この実施形態のスライサは、差動増幅器 510 およびラッチ 515 を備える。前記差動増幅器 510 およびラッチ 515 は、第 1 のクロック入力 516 および第 2 のクロック入力 517 に供給されるクロックの補完位相によってクロッキングされる (クロック動作される)。スライサの差動増幅器 510 内のトランジスタのうちの一つまたは二つ (両方) の 4 番目の端子または「バルク」端子は最初のタップオフセットを実現するために用いられ、このとき、前記最初のタップはデータ経路の上に直接に位置しない。前記差動増幅器 510 は差動的対の構成内において、共通ノードまたは「テール (tail) 部」520 の各 FET の一つの端子に接続された二つの FET 535、545 を備える。前記差動増幅器オフセットは、オフセット電圧を一つまたはそれ以上の FET の 4 番目の端子に加えられるバイアスとして提供することにより実現される。4 番目の端子に対するこのようなバイアスまたは「ボディバイアス (body bias、基板バイアス)」は、差動増幅器 510 の FET のうちの一つに加えられる単一端子方式により加えられるか、あるいは、回路内の対称性を確保するために第 1 のバイアスは差動増幅器 510 の第 1 の FET 535 の 4 番目の端子 530 に、且つ、第 2 の補完的バイアスは差動増幅器 510 の第 2 の FET 545 の 4 番目の端子 540 に差動方式により加えられる。

#### 【0035】

一実施形態において、差動バイアスは図 6 の差動 D A C によって生成される。この D A C において、n 個の電流ソース 610 の各集合が電流を供給し、このとき、n は、D A C のビット数である。各電流ソース 610 は FET を備えるか、あるいは、これにより構成され、これらの電流ソース FET のゲートは、D A C のバイアス制御入力において外部から供給される D A C 電流ソースバイアス電圧に接続される。各電流ソース FET のゲート幅はセット内の以前の電流ソース FET のゲート幅の二倍に等しいため、各電流ソース 610 によって供給される電流を、セット内の以前の電流ソース 610 の電流の二倍にする。最小の電流ソース FET は、単位電流ソースゲート幅と呼ばれるゲート幅を有し、単位

10

20

30

40

50

分岐電流と呼ばれる分岐電流を供給する。各電流ソースは、第1のD A Cスイッチングトランジスタ、例えば、スイッチングF E T 6 1 5および第2のD A Cスイッチングトランジスタ、例えば、スイッチングF E T 6 2 0を備え、第1のD A C出力6 2 5および第2のD A C出力6 3 0にそれぞれ接続されるD A Cの二つの分岐に電流を供給する。各分岐のスイッチングF E Tはそれぞれの制御信号によってオンまたはオフに切り替わり、これらの制御信号はD A Cの出力を制御する。他の実施形態において、直列に接続された連続した電流ソース内の電流の割合は2とは異なる値を有し、または、電流ソースによって供給される電流が等比数列を形成しないこともある。第1のD A C分岐は全て第1の抵抗器6 3 5に接続され、第2のD A C分岐は全て第2の抵抗器6 4 0に接続されて、第1の抵抗器6 3 5と第2の抵抗器6 4 0のそれぞれに流れる合計の電流が二つの補完D A C出力6 2 5、6 3 0においてそれぞれの出力電圧を生成するようになる。单一端子D A Cを使用する実施形態において、各D A C電流ソース6 1 0はD A Cの一つの分岐にのみ電流を供給し、各分岐は一つのスイッチングF E Tを備え、前記分岐はD A C抵抗器に接続されて、D A Cの分岐において流れる合計の電流がD A C出力における電圧を生成するようになる。一実施形態において、差動D A Cが予測的D F E回路の一つの分岐にオフセット電圧を供給するために用いられる。そして、同じ差動D A Cが、第2の分岐において二つのD A C出力の接続を差動増幅器内のF E Tの4番目の端子に置き換えられることにより予測的D F E回路の他の分岐において反対のオフセットを提供するために用いられる。一実施形態において、ボディバイアスとして供給されるオフセット電圧はD A Cによって供給される代わりに、固定電圧ソースであるオフセット電圧ソースの他のソースまたは「オフセット電圧ソース」によって供給される。10

#### 【0036】

一実施形態において、F E Tデバイスにおいてバルクが順バイアス(forward biasing)されることを避ける必要がある。これは、最大のD A C出力電圧を制限するための回路または「D A C電圧制限回路」を用いて最大のD A C出力電圧をスライサテール部の電圧よりも低くするか、あるいは、少なくとも前記最大のD A C出力電圧がスライサテール部の電圧をダイオード降下よりも少量だけ超えるようにすることにより、バルクにおいて発生する順バイアスによるわずかな漏れ電流を小さくして達成することができる。最大のD A C出力電圧は、全ての第1のスイッチングF E T 6 1 5がターンオンされたこと、または、全ての第2のスイッチングF E Tがターンオンされたことに対応し、結果的に最大のD A C電流(電流ソース6 1 0によって提供される合計の電流)がD A C抵抗器6 3 5、6 4 0のうちの一つを介して駆動される。図7は、一実施形態に係るD A C電圧制限回路を示す。この回路において、電流は、直列に接続された電流ソース複製(replica)F E T 7 1 0、スイッチングトランジスタ複製F E T 7 1 5および複製抵抗器7 2 0を備えるか、あるいは、これらから構成される複製回路7 0 5を介して接地に流れる。電流ソース複製F E T 7 1 0のゲートは、D A C内の電流ソースF E Tのゲートに(すなわち、D A Cのバイアス制御入力に)接続される。電流ソース複製F E Tのゲート幅は、単位電流ソースゲート幅の( $2n - 1$ ) / k倍であり、スイッチングトランジスタ複製F E T 7 1 5は、例えば、図示のごとく、ゲートの接地によってターンオンされる。このような構成の結果、電流ソース複製F E T 7 1 0と、スイッチングトランジスタ複製F E T 7 1 5および複製抵抗器7 2 0を介して最大のD A C電流の1 / k倍に等しい量の電流が流れ、ここで、kは、複製サイズ調節要素である。前記複製抵抗器7 2 0は、複製電圧出力7 2 2における電圧、すなわち、複製抵抗器7 2 0を通しての電圧降下がD A Cの最大の出力電圧に等しくなるように、D A C抵抗器6 3 5、6 4 0のうちのいずれか一つの抵抗のk倍に等しい抵抗を有する。前記抵抗器は、D A C電流ソース制御電圧を制御するための負のフィードバックループのフィードバック増幅器から構成された作動増幅器(o p - a m p)7 2 5の反転された入力に接続される。前記フィードバック増幅器7 2 5の非反転入力7 2 7は基準電圧入力として働き、スライサテール部5 2 0に接続される(図5)。前記フィードバック増幅器7 2 5は、基準F E T 7 3 0に接続されたダイオードを通して電流を制御する電流調節F E T 7 2 8のゲートを駆動する。前記基準F E T 7 3 0は、電流ソース20

ス複製 F E T 7 1 0 および電流ソース F E T を D A C 内にミラーリング装置として備える電流ミラーの基準装置である。

【 0 0 3 7 】

複製回路内のフィードバック増幅器 7 2 5 の反転入力における電圧として存在する最大の D A C 出力電圧がスライサテール部の電圧を超えるとき、フィードバック増幅器の出力は減少され、電流制御 F E T 7 2 8 を通して流れる電流を低減する。その結果、基準 F E T 7 3 0 を通して流れる電流が減少され、これにより、D A C 電流ソース F E T および電流ソース複製 F E T 7 1 0 を通して流れる電流も減少される。このような方式によりフィードバック増幅器 7 2 5 を通してのフィードバックによって、最大の D A C 出力電圧がスライサテール部電圧を超えて増加することが是正される。

10

【 0 0 3 8 】

作動に際して、システムコントローラは、D A C 出力を理想的ではない（例えば、損失的）チャンネルの行動様式を測定またはシミュレーションした結果に基づいて作動する前に予め決定された値に設定するか、あるいは、システムコントローラは、過去の動作に基づいて D A C チャンネルを設定し、このような設定（および D F E 内の他の D A C の設定）は、D F E の性能が満足できるものであるか、あるいは、最適化するまで調整される。エラー探知コードが送信されたデータに用いられた場合、D F E の性能は、例えば、ピットエラー率に基づいて測定される。傾斜による下降過程は、最小または許容可能なピットエラー率を見出すために用いられる。

20

【 0 0 3 9 】

スライサテール部 5 2 0 における電圧は、前記スライサがクロックまたは差動入力対の切り替わりによって制御されるトランジスタによって接地に接続される結果として変動される。このような変動は、前記変動がほとんど影響を及ぼさないようにするためにフィードバック増幅器 7 2 5 によって実現される制御ループの帯域幅よりも十分に上にあり、あるいは、この変動は、スライサテール部の電圧に存在する高周波数変動をなくすように選択された蓄電器を有するスライサのテール部に補完的クロック信号を接続することにより抑えられる。

【 0 0 4 0 】

フィードバック増幅器 7 2 5 によって実現された制御ループの利得および帯域幅は、フィードバック増幅器 7 2 5 の利得と帯域幅および複製抵抗器の値をはじめとして様々な要素の影響を受ける。一実施形態において、このループの单一利得周波数は 1 0 0 k H z と 1 0 M H z との間ににおいて、速い起動を提供するのに十分に高い値であり、しかしながら、ループ安定性を阻害する程度に高くないように選択される。

30

【 0 0 4 1 】

図 8 を参照すると、一実施形態において、ディスプレイ 8 0 5 は、理想的ではない（例えば、損失的）チャンネル 8 2 0 を介して、ドライバ集積回路（ドライバ I C ）8 1 5 に高速デジタルデータを送られるように構成されたタイミングコントローラ 8 1 0 を備える。前記ドライバ I C は、シンボル間干渉による影響を受けた信号を受信し、本発明の一実施形態に係るシンボル間干渉の影響を緩和するように構成された受信機を備える。

【 0 0 4 2 】

この明細書において、予測的決定フィードバックイコライザのためのボディバイアススライサデザインの特定の実施形態を記述したが、当該分野における通常の技術を有する者であれば、様々な修正と変更を容易に実現することができる筈である。例えば、この明細書において説明されて例示された回路において、スライサに n - チャンネル F E T が用いられ、且つ、電圧モード D A C に p - チャンネル F E T が用いられたが、p - チャンネル F E T をスライサに用いるか、あるいは、n - チャンネル F E T を電圧モード D A C に用いる補完的回路を採択してもよい。よって、本発明の原理によって構成された予測的決定フィードバックイコライザのためのボディバイアススライサデザインはこの明細書において特定的に記述されたものとは異なるように実現されてもよいものと理解されるべきである。なお、本発明は以下の請求項およびこれと均等な事項によって定義される。

40

50

【図 1 A】

### 【図1B】

【圖2】

【 义 3 】

【図4】

【圖 5】

〔 四 6 〕

【 図 7 】

【図8】

---

フロントページの続き

審査官 浦口 幸宏

(56)参考文献 特開2012-075192(JP,A)

特開2009-225018(JP,A)

Xuelin ZHANG et al. , A 6.25-Gbps 4-tap Low-Power Decision Feedback Equalizer in 0.13μm CMOS Technology , 2013 IEEE International Conference of Electron Devices and Solid-State Circuits , IEEE , 2011年 6月 , U R L , <https://ieeexplore.ieee.org/document/6628236>

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88

H04B 1/10 - 1/14

H04B 1/76 - 3/44

H04B 3/50 - 3/60

H04B 7/00 - 7/015

H04B 15/00 - 15/06

H04L 25/00 - 25/66