(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-134498

(P2012-134498A)

(43) 公開日 平成24年7月12日(2012.7.12)

| (51) Int.Cl.                | F 1    |          | テーマコード (参考)         |

|-----------------------------|--------|----------|---------------------|

| <b>H01G 4/30</b> (2006.01)  | HO1G   | 4/30     | 301F                |

| <b>H05K 1/18</b> (2006.01)  | HO5K   | 1/18     | J                   |

| <b>H01G 2/06</b> (2006.01)  | HO1G   | 1/035    | C                   |

| <b>H05K 3/34</b> (2006.01)  | HO1G   | 1/035    | E                   |

| <b>H05K 13/02</b> (2006.01) | HO5K   | 3/34     | 501D                |

|                             | 審査請求 有 | 請求項の数 27 | O L (全 19 頁) 最終頁に続く |

|              |                              |          |                                                                                    |

|--------------|------------------------------|----------|------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2011-276870 (P2011-276870) | (71) 出願人 | 594023722<br>サムソン エレクトローメカニックス カンパニー リミテッド.<br>大韓民国、キョンギード、スウォン、ヨントンゲ、マエタン3-ドン 314 |

| (22) 出願日     | 平成23年12月19日 (2011.12.19)     | (74) 代理人 | 100088605<br>弁理士 加藤 公延                                                             |

| (31) 優先権主張番号 | 10-2010-0131716              | (74) 代理人 | 100130384<br>弁理士 大島 孝文                                                             |

| (32) 優先日     | 平成22年12月21日 (2010.12.21)     | (72) 発明者 | アン・ヨン・ギュ<br>大韓民国、448-981 キョンギード、ヨンインーシ、スジーグ、ソンボクードン、エルジー・ビレッジ・2チャ・アパートメント 202-403  |

| (33) 優先権主張国  | 韓国 (KR)                      |          |                                                                                    |

最終頁に続く

(54) 【発明の名称】積層セラミックキャパシタの回路基板実装構造、方法及び回路基板のランドパターン、積層セラミックキャパシタの包装体並びに整列方法

## (57) 【要約】

【課題】圧電現象による振動によって発生される騒音を減少させることができる積層セラミックキャパシタの回路基板実装構造、実装方法及びこのため回路基板のランドパターン等を提供する。

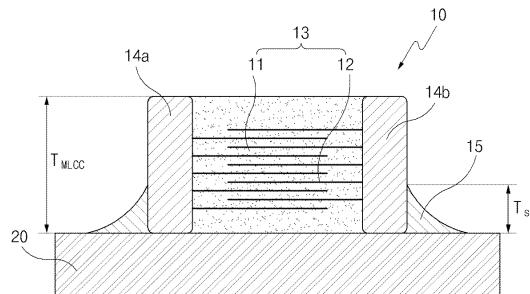

【解決手段】内部電極12が設けられた誘電体シート1が積層され、内部電極12と並列接続する外部端子電極14a, 14bが両端部に設けられた積層セラミックキャパシタ10の回路基板20への実装構造であって、積層セラミックキャパシタ10の内部電極層と凹路基板とは、互いに水平方向になるように配置され、外部端子電極14a, 14bと回路基板20のランドとを導電接続し、外部端子電極14a, 14bとランドとを導電接続する導電材15の高さ( $T_s$ )は、積層セラミックキャパシタ10の厚さ( $T_{MLCC}$ )の1/3未満である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

内部電極の設けられた誘電体シートが積層され、該内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装構造であって、

前記積層セラミックキャパシタの内部電極層と前記回路基板とは、互いに水平方向になるように配置されて、前記外部端子電極と前記回路基板のランドとを導電接続し、

前記外部端子電極と前記ランドとを導電接続する導電材の高さ( $T_s$ )は、前記積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の1/3未満である積層セラミックキャパシタの回路基板実装構造。

**【請求項 2】**

前記積層セラミックキャパシタは、水平方向に実装されるようにテーピング処理され、その幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似である請求項1に記載の積層セラミックキャパシタの回路基板実装構造。

**【請求項 3】**

前記積層セラミックキャパシタの誘電体層の層数は、200層以上である請求項1または2に記載の積層セラミックキャパシタの回路基板実装構造。

**【請求項 4】**

前記積層セラミックキャパシタの誘電体層の誘電体の厚さは、 $3\mu m$ 以下である請求項1または2に記載の積層セラミックキャパシタの回路基板実装構造。

**【請求項 5】**

前記積層セラミックキャパシタの誘電体層は、層数が200層以上で、誘電体の厚さは、 $3\mu m$ 以下である請求項1または2に記載の積層セラミックキャパシタの回路基板実装構造。

**【請求項 6】**

内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、

前記積層セラミックキャパシタの内部電極層と前記回路基板が互いに水平方向になるように配置されて、前記外部端子電極と前記回路基板のランドとを導電接続し、

前記外部端子電極と前記ランドとを導電接続する導電材の高さ( $T_s$ )は、前記積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の1/3未満である積層セラミックキャパシタの回路基板実装方法。

**【請求項 7】**

前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似である請求項6に記載の積層セラミックキャパシタの回路基板実装方法。

**【請求項 8】**

前記積層セラミックキャパシタの誘電体層の層数は、200層以上である請求項6または7に記載の積層セラミックキャパシタの回路基板実装方法。

**【請求項 9】**

前記積層セラミックキャパシタの誘電体層の誘電体の厚さは、 $3\mu m$ 以下である請求項6または7に記載の積層セラミックキャパシタの回路基板実装方法。

**【請求項 10】**

前記積層セラミックキャパシタの誘電体層は、層数が200層以上で、誘電体の厚さは、 $3\mu m$ 以下である請求項6または7に記載の積層セラミックキャパシタの回路基板実装方法。

**【請求項 11】**

内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、

前記回路基板の表面に前記積層セラミックキャパシタが実装されるランドを設け、

前記積層セラミックキャパシタの内部電極層と前記回路基板が互いに水平方向になるよ

10

20

30

40

50

うに配置して前記外部端子電極と前記回路基板のランドとを導電接続し、

前記ランドは、前記積層セラミックキャパシタの外部端子電極の設けられた個所に対応するように離間されて前記回路基板の表面に複数個設けられ、

前記積層セラミックキャパシタの幅を $W_{MLCC}$ 、長さを $L_{MLCC}$ として定義し、前記離間された各ランドのうちのいずれか一方のランドの外側縁と他方のランドの外側縁とを基準として、基板で占める幅を $W_{LAND(a)}$ 、長さを $L_{LAND(a)}$ として定義すると、

$W_{MLCC} \leq L_{MLCC} \leq W_{LAND(a)}$ 及び $L_{LAND(a)} \leq L_{MLCC}$ の関係は、下式、

$$0 < L_{LAND(a)} / L_{MLCC} \leq 1.2 \quad 1.2$$

$$0 < W_{LAND(a)} / W_{MLCC} \leq 1.2 \quad 1.2$$

10

を満たす積層セラミックキャパシタの回路基板実装方法。

#### 【請求項 12】

内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、

前記回路基板の表面に前記積層セラミックキャパシタが実装されるランドを設け、

前記積層セラミックキャパシタの内部電極層と前記回路基板とが互いに水平方向になるように配置して前記外部端子電極と前記回路基板のランドとを導電接続し、

前記ランドは、ハンダ付け量の減少のために、前記積層セラミックキャパシタの外部端子電極の設けられた縁部に対応するように離間されて前記回路基板の表面に複数個設けられる、積層セラミックキャパシタの回路基板実装方法。

20

#### 【請求項 13】

前記積層セラミックキャパシタの幅を $W_{MLCC}$ 、長さを $L_{MLCC}$ として定義し、前記離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅を $W_{LAND(b)}$ 、長さを $L_{LAND(b)}$ として定義すると、

$W_{MLCC} \leq L_{MLCC} \leq W_{LAND(b)}$ 及び $L_{LAND(b)} \leq L_{MLCC}$ の関係は、下式、

$$0 < L_{LAND(b)} / L_{MLCC} \leq 1.2$$

$$0 < W_{LAND(b)} / W_{MLCC} \leq 1.2$$

を満たす請求項 12 に記載の積層セラミックキャパシタの回路基板実装方法。

#### 【請求項 14】

前記外部端子電極と前記ランドとを導電接続する導電材の高さ( $T_s$ )は、前記積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の $1/3$ 未満である請求項 11 ~ 13 のうちのいずれか一つに記載の積層セラミックキャパシタの回路基板実装方法。

30

#### 【請求項 15】

前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似である請求項 11 ~ 13 のうちのいずれか一つに記載の積層セラミックキャパシタの回路基板実装方法。

#### 【請求項 16】

前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似である請求項 14 に記載の積層セラミックキャパシタの回路基板実装方法。

40

#### 【請求項 17】

内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタが実装される回路基板上のランドパターンであって、

前記ランドパターンは、前記積層セラミックキャパシタの外部端子電極の設けられた個所に対応するように離間されて前記回路基板の表面に複数個設けられ、

前記積層セラミックキャパシタの幅を $W_{MLCC}$ 、長さを $L_{MLCC}$ として定義し、前記離間された各ランドのうちのいずれか一方のランドの外側縁と他方のランドの外側縁とを基準として、基板で占める幅を $W_{LAND(a)}$ 、長さを $L_{LAND(a)}$ として定義すると、

50

$W_{MLCC} \times L_{MLCC} \times W_{LAND(a)} \text{ 及び } L_{LAND(a)}$  の関係は、下式、

$0 < L_{LAND(a)} / L_{MLCC} \quad 1.2$

$0 < W_{LAND(a)} / W_{MLCC} \quad 1.2$

を満たす回路基板上のランドパターン。

#### 【請求項 18】

内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタが実装される回路基板上のランドパターンであって、

前記ランドパターンは、ハンダ付け量の減少のために、前記積層セラミックキャパシタの外部端子電極の設けられた縁部に対応するように離間されて前記回路基板の表面に複数個設けられ、

前記積層セラミックキャパシタの幅を  $W_{MLCC}$ 、長さを  $L_{MLCC}$  として定義し、前記離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅を  $W_{LAND(b)}$ 、長さを  $L_{LAND(b)}$  として定義すると、

$W_{MLCC} \times L_{MLCC} \times W_{LAND(b)} \text{ 及び } L_{LAND(b)}$  の関係は、下式、

$0 < L_{LAND(b)} / L_{MLCC} \quad 1.2$

$0 < W_{LAND(b)} / W_{MLCC} \quad 1.2$

を満たす回路基板上のランドパターン。

#### 【請求項 19】

内部電極の設けられた誘電体シートが積層され、前記内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタと、

前記積層セラミックキャパシタが収納される収納部が設けられる包装シートと、を含み、

前記内部電極は、前記収納部の底面を基準に水平に配置されるように整列され、前記積層セラミックキャパシタが整列された包装シートがリール形態に巻き取られた積層セラミックキャパシタの包装体。

#### 【請求項 20】

前記包装シートに結合され、前記積層セラミックキャパシタを覆う包装膜をさらに含む請求項 19 に記載の積層セラミックキャパシタの包装体。

#### 【請求項 21】

前記積層セラミックキャパシタの包装体は、リール形態に巻き取られた請求項 19 または 20 に記載の積層セラミックキャパシタの包装体。

#### 【請求項 22】

前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅 ( $W_{MLCC}$ ) 及び厚さ ( $T_{MLCC}$ ) が同一または類似である請求項 19 または 20 に記載の積層セラミックキャパシタの包装体。

#### 【請求項 23】

前記積層セラミックキャパシタは、水平方向に実装されるように整列するテーピング処理され、その幅 ( $W_{MLCC}$ ) 及び厚さ ( $T_{MLCC}$ ) が同一または類似である請求項 21 に記載の積層セラミックキャパシタの包装体。

#### 【請求項 24】

幅 ( $W_{MLCC}$ ) 及び厚さ ( $T_{MLCC}$ ) が同一または類似な積層セラミックキャパシタの水平方向整列方法であって、

前記積層セラミックキャパシタを移送部に実装して、該積層セラミックキャパシタが連続して移送されるようにするステップと、

前記移送部によって移送される前記積層セラミックキャパシタに磁場を印加し、内部電極層が該磁場及び磁気抵抗が減る方向に整列されるようにするステップと、を含む積層セラミックキャパシタの水平方向整列方法。

#### 【請求項 25】

前記磁場印加ステップを経った前記積層セラミックキャパシタの前記内部電極層は、前

記移送部の進行方向を基準に水平に配置される請求項 2 4 に記載の積層セラミックキャパシタの水平方向整列方法。

#### 【請求項 2 6】

前記移送部は、前記積層セラミックキャパシタが一定に整列されるようとする一対のガイド部を、さらに含む請求項 2 4 に記載の積層セラミックキャパシタの水平方向整列方法。

#### 【請求項 2 7】

前記一対のガイド部間の間隔  $g$  は、前記積層セラミックキャパシタの幅を  $W_{M L C C}$ 、厚さを  $T_{M L C C}$ 、長さを  $L_{M L C C}$  として定義すると、下式、

$$(W_{M L C C}^2 + T_{M L C C}^2) < g < \min [(L_{M L C C}^2 + T_{M L C C}^2), 10, (L_{M L C C}^2 + W_{M L C C}^2)]$$

を満足する請求項 2 6 に記載の積層セラミックキャパシタの水平方向整列方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は、積層セラミックキャパシタの回路基板実装構造、実装方法及びこのため回路基板のランドパターン、水平方向にテーピングした積層セラミックキャパシタの包装体並びに水平方向整列方法に関する。特に、内部電極が設けられた誘電体シートが積層され、該内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、該回路基板の表面に積層セラミックキャパシタが実装されるランドを設け、積層セラミックキャパシタの内部電極層と回路基板が水平方向になるように配置して、外部端子電極とランドとを導電接続し、外部端子電極とランドとを導電接続する導電材の高さ ( $T_s$ ) は、積層セラミックキャパシタの厚さ ( $T_{M L C C}$ ) の  $1/3$  未満にすることによって、振動騒音を大きく減少させることができる積層セラミックキャパシタの回路基板実装構造、実装方法及びこのため回路基板のランドパターン、水平方向にテーピングした積層セラミックキャパシタの包装体並びに水平方向整列方法に関する。

20

##### 【背景技術】

##### 【0 0 0 2】

一般に、積層型セラミックキャパシタ (Multi-Layered Ceramic Capacitor : MLC) は、移動通信端末、ノート型パソコン、パソコン、携帯端末 (PDA) など多くの電子製品の印刷回路基板に取り付けられ、電気を充電または放電させる重要な役目をするチップ形態のコンデンサーであって、その使用用途及び容量によって多様な大きさ及び積層形態を取っている。

30

##### 【0 0 0 3】

一般に、積層型セラミックキャパシタは、複数の誘電体層間に異なる極性の内部電極が交互に積層された構造を有する。

##### 【0 0 0 4】

このような積層型セラミックキャパシタは、小型化が可能で、且つ高容量が保障され、実装が容易という長所があるので、多様な電子装置の部品として広く使われている。

40

##### 【0 0 0 5】

積層型セラミックキャパシタの積層体を設けるセラミック材料として、誘電率の比較的高いチタン酸バリウムなどの強誘電体材料が一般的に利用されている。このような強誘電体材料は、圧電性及び電歪性を有するため、強誘電体材料に電界が加えられると、応力及び機械的変形が振動として現われ、積層セラミックキャパシタの端子電極から基板側へと該振動が伝達されることになる。

##### 【0 0 0 6】

すなわち、積層セラミックキャパシタに交流電圧が加えられた場合には、該積層セラミックキャパシタの素子本体に X、Y、Z の各方向に沿って応力 ( $F_x$ 、 $F_t$ 、 $F_z$ ) が発生し、それに伴って振動が発生するようになる。この振動が、端子電極から基板へと伝達

50

されて、該基板の全体が音響放射面になって、雑音となる振動音を発生させるようになる。

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【特許文献1】韓国公開特許第10-2000-0047547号公報**

**【特許文献2】韓国公開特許第10-2004-0082995号公報**

**【特許文献3】韓国公開特許第10-2008-0019893号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

10

**【0008】**

このような振動音は、大概、可聴振動数(20~20,000Hz)の振動音にあたることで、該振動音は人に不快な音域にある場合もあり、これに対する解決策が必要になった。

**【0009】**

最近、このような振動音による問題点を解決するために、積層セラミックキャパシタの外部端子の弾性的変形によって振動を防止する技術、圧電及び電歪によって発生する振動の電波を抑制して雑音の発生を低減するようにする別途の部品を取り入れる技術、及び基板の振動を抑制するために実装された積層型セラミックキャパシタの周辺に基板ホールを設ける技術など、多様な技術が示されている。しかしながら、これらの技術では別途の処理工程が必要で、この工程の複雑さに比べて、十分な振動防止の効果が得られていないのが実情であった。

20

**【0010】**

一方、積層セラミックキャパシタには、幅と厚さとが実質的に等しいものがある。幅及び厚さが実質的に等しい積層セラミックキャパシタの場合、印刷回路基板にこれを実装する際、該積層セラミックキャパシタの見掛けからその各内部導体の方向性を認識することができないため、印刷回路基板に積層セラミックキャパシタが、各内部導体の方向性と無関係に実装されてしまう。

**【0011】**

ところが、印刷回路基板に実装される積層セラミックキャパシタの各内部導体の方向によって積層セラミックキャパシタの特性の差が発生し、特に積層セラミックキャパシタの圧電性による振動騒音特性に大きな差が生じる。

30

**【0012】**

最近の実験結果によれば、積層セラミックキャパシタの実装方向、及び、積層セラミックキャパシタの外部電極端子とランドとを連結する導電材の量は、これらが互いに相関関係にあること、また、振動騒音の特性に大きい影響を及ぼすこと、が明らかになった。

**【0013】**

特に、積層セラミックキャパシタの内部電極面が印刷回路基板面と水平になるように実装し、該積層セラミックキャパシタの外部電極端子とランドとを連結する導電材の高さを減少させた場合、振動騒音を大きく減少させることができる。しかし、これを実現するためには、所定の実装構造、実装方法、基板のランドパターン、水平方向にテーピングした積層セラミックキャパシタの包装体並びに水平方向整列方法が必要であるのが実情である。

40

**【0014】**

本発明は上記の問題点に鑑みて成されたものであって、圧電現象による振動によって発生する騒音を減少させることができる積層セラミックキャパシタの回路基板実装構造、実装方法及びこのため回路基板のランドパターン、水平方向にテーピングした積層セラミックキャパシタの包装体並びに水平方向整列方法を提供することに、その目的がある。

**【課題を解決するための手段】**

**【0015】**

50

上記目的を解決するために、本発明の好適な実施形態による積層セラミックキャパシタの回路基板への実装構造は、内部電極が設けられた誘電体シートが積層され、該内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装構造であって、該積層セラミックキャパシタの内部電極層と前記回路基板とは、水平方向になるように配置され、前記外部端子電極と回路基板のランドとを導電接続し、前記外部端子電極と前記ランドとを導電接続する導電材の高さ( $T_s$ )は、前記積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の1/3未満になる。

## 【0016】

前記積層セラミックキャパシタは、リール(Reel)のような包装体で包装される際に、該積層セラミックキャパシタの内部電極が、回路基板に対し水平方向に実装可能なように、一方向に整列させるテーピング(taping)を施したもので、幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似なものであってもよい。ここで、積層セラミックキャパシタの幅及び厚さの同一とは、物理的な完全同一ではなく、社会通念上同一であることを意味し、類似とは、 $0.75 \times T_{MLCC} / W_{MLCC} = 1.5$ の範囲内であることに注意されたい。

10

## 【0017】

一方、積層セラミックキャパシタの内部電極間の誘電体の層数が多いか、または、該誘電体に印加される電界が大きいほど、積層セラミックキャパシタの圧電性による応力及び機械的変形が大きくなる。そのため、誘電体の層数が200層以上、または誘電体の厚さが3μm以下の場合、相当な振動騒音が発生するようになる。

20

## 【0018】

そのため、積層セラミックキャパシタの誘電体層の層数は、200層以上であってもよく、誘電体層の誘電体の厚さは、3μm以下であってもよい。ここで、該積層セラミックキャパシタの誘電体層は、層数が200層以上であると共に誘電体の厚さは3μm以下であってもよい。

## 【0019】

一方、本発明の他の好適な実施形態に係る積層セラミックキャパシタの回路基板実装方法は、内部電極が設けられた誘電体シートが積層され、該内部電極と並列接続される外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、該積層セラミックキャパシタの内部電極層と前記回路基板とが水平方向になるように配置され、前記外部端子電極と前記回路基板のランドとを導電接続し、前記外部端子電極と前記ランドとを導電接続する導電材の高さ( $T_s$ )は、前記積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の1/3未満になるように設定する。

30

## 【0020】

同様に、積層セラミックキャパシタは、水平方向に実装されるように整列させるテーピングを施して、幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似である。

## 【0021】

また、前述のように、積層セラミックキャパシタの誘電体層の層数は、200層以上であってもよく、誘電体層の誘電体の厚さは、3μm以下であってもよい。ここで、該積層セラミックキャパシタの誘電体層は、層数が200層以上であると共に、誘電体の厚さは3μm以下であってもよい。

40

## 【0022】

また、本発明のさらに他の好適な実施形態による積層セラミックキャパシタの回路基板実装方法は、内部電極が設けられた誘電体シートが積層され、該内部電極と並列接続される外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、該回路基板の表面に積層セラミックキャパシタが実装されるランドを設け、該積層セラミックキャパシタの内部電極層と前記回路基板とが水平方向になるように配置して、前記外部端子電極と前記回路基板のランドとを導電接続し、該ランドは、前記積層セラミックキャパシタの外部端子電極の設けられた個所に対応するように離間されて回路基板の表面に複数個設けられている。前記積層セラミックキャパシタの幅を $W_{MLCC}$ 、長さ

50

を  $L_{MLCC}$  として定義し、前記離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅を  $W_{LAND(a)}$  、長さを  $L_{LAND(a)}$  として定義すると、 $W_{MLCC} \cdot L_{MLCC} \cdot W_{LAND(a)}$  及び  $L_{LAND(a)}$  の関係は、 $0 < L_{LAND(a)} / L_{MLCC} \leq 1.2$  、 $0 < W_{LAND(a)} / W_{MLCC} \leq 1.2$  であるのが望ましい。ここで、ランドは、ソルダレジストが覆われることなく露出した部分を意味する。

#### 【0023】

また、本発明のさらに他の好適な実施形態による積層セラミックキャパシタの回路基板実装方法は、内部電極が設けられた誘電体シートが積層され、該内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタの回路基板への実装方法であって、該回路基板の表面に前記積層セラミックキャパシタが実装されるランドを設け、該積層セラミックキャパシタの内部電極層と前記回路基板とが水平方向になるように配置して、前記外部端子電極と回路基板のランドとを導電接続し、該ランドは、ハンダ付け量の減少のために、前記積層セラミックキャパシタの外部端子電極が設けられた縁部に対応するように離間されて、回路基板の表面に複数個設けられる。

10

#### 【0024】

ここで、積層セラミックキャパシタの幅を  $W_{MLCC}$  、長さを  $L_{MLCC}$  として定義し、離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅を  $W_{LAND(b)}$  、長さを  $L_{LAND(b)}$  として定義すると、 $W_{MLCC} \cdot L_{MLCC} \cdot W_{LAND(b)}$  及び  $L_{LAND(b)}$  の関係は、 $0 < L_{LAND(b)} / L_{MLCC} \leq 1.2$  、 $0 < W_{LAND(b)} / W_{MLCC} \leq 1.2$  であるのが望ましい。

20

#### 【0025】

前述のように、ランドが限定された本発明の積層セラミックキャパシタの回路基板実装方法において、外部端子電極とランドとを導電接続する導電材の高さ ( $T_s$ ) は、積層セラミックキャパシタの厚さ ( $T_{MLCC}$ ) の  $1/3$  未満になることが望ましい。

20

#### 【0026】

また、前述のように、ランドが限定された本発明の積層セラミックキャパシタの回路基板実装方法において、該積層セラミックキャパシタは、リールのような包装体で包装される際、積層セラミックキャパシタの内部電極が回路基板に対し、水平方向に実装可能のように一方向に整列するテーピングを施し、幅 ( $W_{MLCC}$ ) 及び厚さ ( $T_{MLCC}$ ) が同一または類似であってもよい。ここで、積層セラミックキャパシタの幅及び厚さが同一または類似であるということは、 $0.75 \leq T_{MLCC} / W_{MLCC} \leq 1.25$  範囲であることを意味する。

30

#### 【0027】

また、本発明は、積層セラミックキャパシタが実装される回路基板上のランドパターンを提供する。本発明によるランドパターンは、誘電体セラミックからなる誘電体層と内部電極層とを交互に積層してなされるセラミック素体と、該素体の両端部で前記内部電極層に設けられた内部電極を交互に並列で接続する一対の外部端子電極とからなる積層セラミックキャパシタが実装される回路基板上のランドパターンである。該ランドパターンは、前記積層セラミックキャパシタの外部端子電極が設けられた個所に対応するように離間され、回路基板の表面に複数個設けられ、該積層セラミックキャパシタの幅を  $W_{MLCC}$  、長さを  $L_{MLCC}$  として定義し、離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅を  $W_{LAND(a)}$  、長さを  $L_{LAND(a)}$  として定義すると、 $W_{MLCC} \cdot L_{MLCC} \cdot W_{LAND(a)}$  及び  $L_{LAND(a)}$  の関係は、 $0 < L_{LAND(a)} / L_{MLCC} \leq 1.2$  、 $0 < W_{LAND(a)} / W_{MLCC} \leq 1.2$  であるのが望ましい。

40

#### 【0028】

また、本発明のさらに他の好適な実施形態による、積層セラミックキャパシタが実装される回路基板上のランドパターンは、誘電体セラミックからなる誘電体層と内部電極層と

50

を交互に積層してなされるセラミック素体と、該素体の両端部で、前記内部電極層に設けられた内部電極を交互に並列で接続する一対の外部端子電極とからなる積層セラミックキャパシタが実装される回路基板上のランドパターンである。該ランドパターンは、ハンダ付け量の減少のために、積層セラミックキャパシタの外部端子電極が設けられた縁部に対応するように離間され、回路基板の表面に複数個設けられ、積層セラミックキャパシタの幅を  $W_{MLCC}$ 、長さを  $L_{MLCC}$  として定義し、離間された各ランドのうちのいずれか一方の外側縁と他方のランドの外側縁とを基準として、基板で占める幅を  $W_{LAND(b)}$ 、長さを  $L_{LAND(b)}$  として定義すると、 $W_{MLCC} < L_{MLCC}$ 、 $W_{LAND(b)} < L_{LAND(b)}$  及び  $L_{LAND(b)} / L_{MLCC} \leq 1.2$ 、 $0 < W_{LAND(b)} / W_{MLCC} \leq 1.2$  であるのが望ましい。

10

## 【0029】

また、本発明のさらに他の好適な実施形態として、振動騒音を低減するために、積層セラミックキャパシタが水平方向に実装された包装体を提供する。該包装体は、内部電極が設けられた誘電体シートが積層され、該内部電極と並列接続する外部端子電極が両端部に設けられた積層セラミックキャパシタと、該積層セラミックキャパシタが収納される収納部とが設けられる包装シートを含み、前記内部電極は、前記収納部の底面を基準に水平に配置されるように整列される。

## 【0030】

積層セラミックキャパシタの包装体は、該包装シートに結合され、該積層セラミックキャパシタを覆う包装膜をさらに含む。積層セラミックキャパシタの包装体は、リール形態に巻取られた形態であってもよい。

20

## 【0031】

また、本発明のさらに他の好適な実施形態として、振動騒音を低減するために、幅 ( $W_{MLCC}$ ) 及び厚さ ( $T_{MLCC}$ ) が同一または類似の積層セラミックキャパシタの水平方向整列方法を提供する。該方法は、積層セラミックキャパシタを連続して移送されるようにする移送部に実装するステップと、該移送部によって移送される積層セラミックキャパシタに磁場を印加し、内部電極層が該磁場と磁気抵抗が減る方向に整列されるようにする磁場印加ステップとを含む。

## 【0032】

該磁場印加ステップを経た積層セラミックキャパシタの内部電極層は、前記移送部の進行方向を基準に水平に配置される。

30

## 【0033】

前記移送部は、積層セラミックキャパシタが一定に整列されるようにする一対のガイド部をさらに含む。

## 【0034】

該一対のガイド部間の間隔  $g$  は、積層セラミックキャパシタの幅を  $W_{MLCC}$ 、厚さを  $T_{MLCC}$ 、長さを  $L_{MLCC}$  として定義すると、下式、

$$(W_{MLCC}^2 + T_{MLCC}^2) < g < \min [(L_{MLCC}^2 + T_{MLCC}^2), (L_{MLCC}^2 + W_{MLCC}^2)]$$

40

を満足する。

## 【発明の効果】

## 【0035】

本発明によれば、簡単な方法で、積層セラミックキャパシタで発生した振動が基板へ伝達されるのを抑制することで、騒音の発生をより一層低減させることができる効果が奏される。

## 【図面の簡単な説明】

## 【0036】

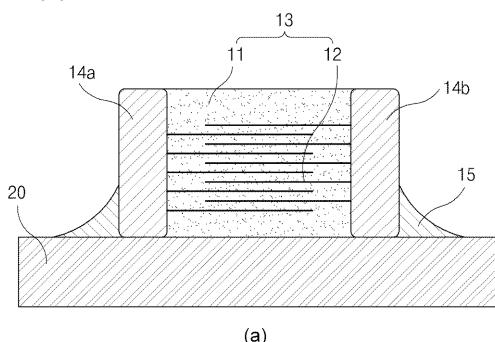

【図1】本発明の方法によって積層セラミックキャパシタが回路基板に実装された状態を示す断面図である。

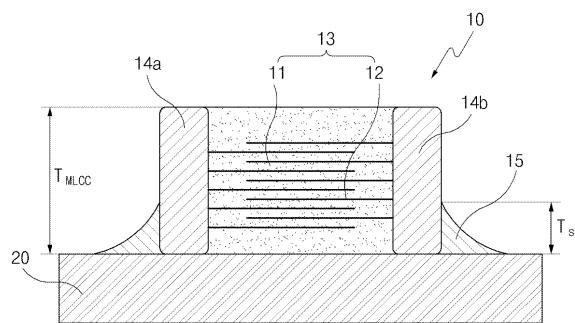

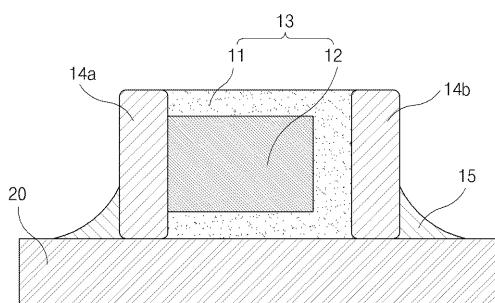

【図2】幅及び厚さが同一または類似である積層セラミックキャパシタ (a) と、幅が厚

50

さより大きい積層セラミックキャパシタ( b )を示す図である。

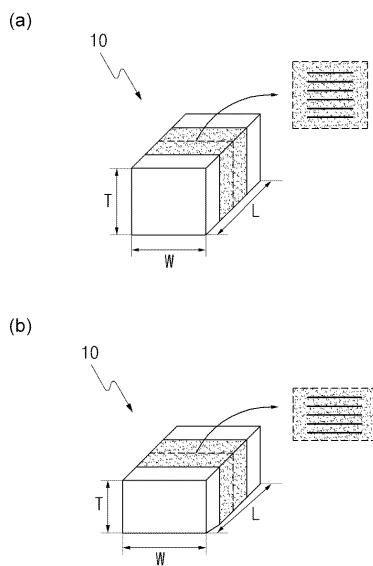

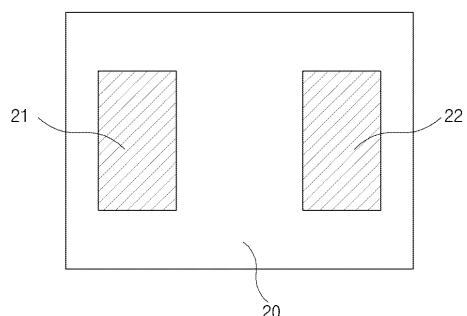

【図3】本発明の一実施形態によるランドパターンを有する回路基板の平面図である。

【図4】本発明の一実施形態によるランドと積層セラミックキャパシタの幅及び長さとの間の相関関係を示す模式図である。

【図5】本発明の他の一実施形態による回路基板の平面図である。

【図6】本発明の他の一実施形態によるランドと積層セラミックキャパシタの幅及び長さとの間の相関関係を示す模式図である。

【図7】本発明の一実施形態による積層セラミックキャパシタを、水平に配置されるように整列させた積層セラミックキャパシタの包装体を示す図面である。

【図8】本発明のさらに他の一実施形態であり、巻取られたリール形態の積層セラミックキャパシタの包装体を示す図面である。

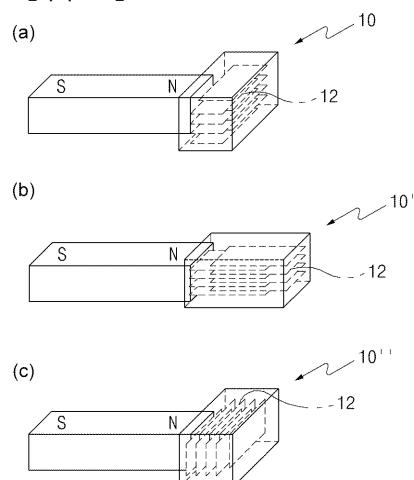

【図9】積層セラミックキャパシタが磁気によって整列した状態を示す模式図である。

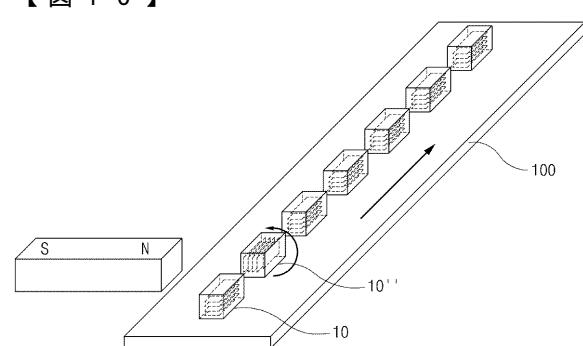

【図10】積層セラミックキャパシタが移送部によって移送される過程で、磁気によって整列する状態を示す模式図である。

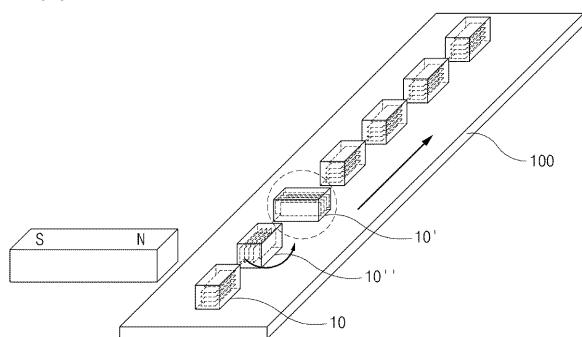

【図11】積層セラミックキャパシタが移送部によって移送される過程で、磁気によって整列する状態を示す模式図である。

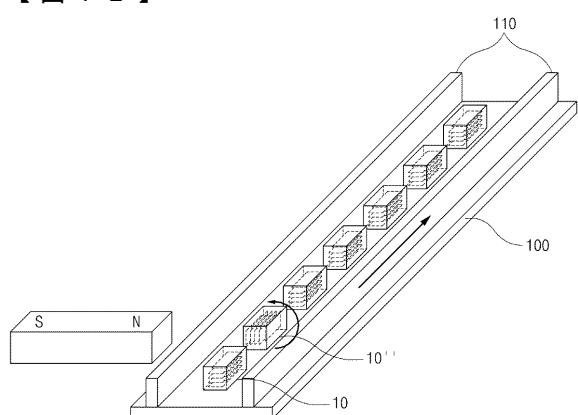

【図12】本発明の一実施形態による積層セラミックキャパシタの水平方向の整列方法を示す模式図である。

【図13】本発明の試験例であって、積層セラミックキャパシタを回路基板上に水平実装する場合( a )と垂直実装する場合( b )とを示す模式図である。

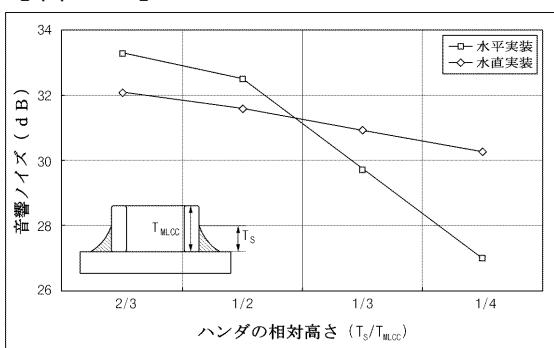

【図14】本発明の試験例であって、積層セラミックキャパシタを回路基板上に水平実装する場合と垂直実装する場合とで、導電材( ハンダ付け )の高さが振動騒音に及ぼす影響を示すグラフである。

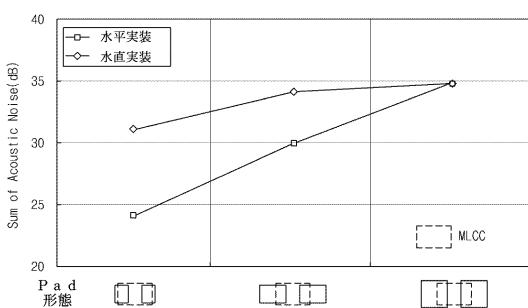

【図15】本発明の試験例であって、積層セラミックキャパシタを回路基板上に水平実装する場合と垂直実装する場合とで、ランドの大きさが振動騒音に及ぼす影響を示すグラフである。

#### 【発明を実施するための形態】

##### 【0037】

本発明の好適な実施の形態について、図面を参考にして詳細に説明する。以下に示される各実施の形態は、当業者にとって本発明の思想が十分に伝達されることができるようするため例として挙げられるものである。従って、本発明は以下に示している各実施の形態に限定されることなく、他の形態で具体化ができる。そして、図面において、装置の大きさ及び厚さなどは、便宜上誇張して表現されることがある。明細書全体にわたる同一の参照符号は、同一の構成要素を示している。

##### 【0038】

本明細書で使われた用語は、実施形態を説明するためのものであって、本発明を制限しようとするものではない。本明細書において、単数形は特別に言及しない限り複数形も含む。明細書で使われる「含む」とは、言及された構成要素、ステップ、動作及び/又は素子は、一つ以上の他の構成要素、ステップ、動作及び/又は素子の存在または追加を排除しないことに理解されたい。

##### 【0039】

まず、添付図面を参照して、本発明について詳記する。

#### 積層セラミックキャパシタの回路基板実装構造及び実装方法

##### 【0040】

図1は、本発明の方法によって積層セラミックキャパシタ10が回路基板に実装された姿を示す断面図である。

##### 【0041】

本発明の積層セラミックキャパシタの回路基板実装構造及び方法は、内部電極12が設けられた誘電体シート11が積層され、該内部電極12と並列接続する外部端子電極14

10

20

30

40

50

a、14bが両端部に設けられた積層セラミックキャパシタの回路基板への実装構造及び方法である。この方法において、前記回路基板20の表面に、積層セラミックキャパシタ10が実装されるランド(図示せず)を設け、該積層セラミックキャパシタ10の内部電極層12と前記回路基板20とが水平方向になるように配置して外部端子電極14a、14bとランドとを導電接続し、該外部端子電極14a、14bとランドとを導電接続する導電材15の高さ( $T_s$ )は、積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の1/3未満に設定される。

#### 【0042】

図1に示すように、積層セラミックキャパシタ10は、誘電体層11と内部電極12とを交互に積層してなる素体13と、該素体13の両端部で内部電極を交互に並列接続している一対の外部電極14a、14bとから構成されている。

10

#### 【0043】

該誘電体層11は、チタン酸バリウムなどを主成分とする強誘電体材料からなり、チタン酸バリウム以外の他の強誘電体材料を含んでもよい。

#### 【0044】

前記内部電極12は、金属ペーストを焼結させた金属薄膜からなり、該金属ペーストとしては、例えばNi、Pd、Ag-Pd、またはCuのような金属材料を主成分とするものが使われてもよい。

#### 【0045】

同様に、前記外部電極14a、14bは、Cu、Niなどのような金属材料から成り、その表面には、ハンダ付け漏れ性を良くするためにハンダメッキが実施されている。

20

#### 【0046】

回路基板20の表面には、積層セラミックキャパシタを実装するためのランドが設けられる。該ランドは、回路基板20の内部のソルダレジストが露出し、該露出したソルダレジストの上面に導電材15がコーティングされ、積層セラミックキャパシタ10を実装するための部位である。回路基板20としては、多層回路基板、断層両面プリント基板などが挙げられ、これに限定されるものではない。

#### 【0047】

積層セラミックキャパシタ10は、図2のように、幅( $W$ )及び厚さ( $T$ )が同一または類似の場合(図2a)と、幅が厚さより大きい場合(図2b)とがある。後者の場合は、意図せずとも、厚さが薄くて常に水平実装になるが、前者の場合には、水平実装と垂直実装とが無作為に行われるようになる。特に、積層セラミックキャパシタがリールのような包装体で包装される場合、積層セラミックキャパシタの内部電極が回路基板に水平方向に実装可能なように、一方向に整列するテーピングを施すことによって、幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が同一または類似の積層セラミックキャパシタの場合、水平実装の際、振動による騒音低減の効果をさらに高めることができる。ここで、積層セラミックキャパシタの幅及び厚さが同一または類似であるとは、 $0.75 \leq T_{MLCC} / W_{MLCC} \leq 1.25$ 範囲内の場合をいう。

30

#### 【0048】

ハンダなどの導電材15は、積層セラミックキャパシタ10と回路基板20との間の振動媒介体の役目をして、導電材15の高さを低くしながら基板への振動の伝達を低下させる。水平実装では、積層セラミックキャパシタ10の圧電性による縁部の振動のうち、上面の振動の伝達が導電材15の高さの低下とともに急に低下することになる。そのため、水平方向に実装する場合には、導電材15の高さの変化による振動騒音の減少幅が非常に大きくなる。

40

#### 【0049】

これに対して、垂直方向に実装する場合には、そのような効果が発生しないため、導電材15の高さの変化による振動騒音の減少幅は大きくない。

#### 【0050】

したがって、積層セラミックキャパシタによる騒音を低減させるためには、積層セラミ

10

20

30

40

50

ックキャパシタ10は、内部電極12を基準として、回路基板20と水平方向になるよう実装して導電材15の高さを減少させることが望ましい。

#### 【0051】

図2に示す積層セラミックキャパシタの幅(W)及び長さ(L)によって、積層セラミックキャパシタは、0603(L×W=0.6mm×0.3mm)、1005、1608、2012、3216、3225などの大きさを有する。3216以上の大きい積層セラミックキャパシタの場合、その厚さに対して導電材の相対高さが低くても、該導電材の絶対量が多いので、振動騒音の低下効果を大きくするためには、該導電材の相対高さを1/4未満にすることが望ましい。

#### 【0052】

導電材15は、回路基板20と積層セラミックキャパシタとの間の電気的接続のために電気が導通する材料から成り、これは限定されるものではない。例えば、ハンダ付け(solder)を用いてもよい。

### ランドパターン

#### 【0053】

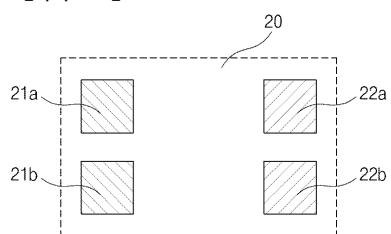

図3は、本発明の一実施形態によるランドパターンを有する回路基板の平面図である。

#### 【0054】

図3に示すように、回路基板20に積層セラミックキャパシタが実装されるランド21、22が示されている。これらのランド21、22は、図1の積層セラミックキャパシタ10の外部端子電極14a、14bが設けられた個所に対応するように離間されて、回路基板の表面に複数個設けられる。これらのランドは、ソルダレシズトが覆われることなく露出した部分を意味する。

#### 【0055】

図3では、一実施形態として、四角形状のランドを2個設けた状態を示すが、これに限定されるものではない。ただ、前述のように、ランド21、22の表面にコーティングされる導電材15が振動騒音に影響を及ぼすが、ランド21、22が占める面積について、図4に示すように、一定の制限を設けることによって導電材の高さを減らすことができる。

#### 【0056】

図4は、本発明の一実施形態によるランド21、22と積層セラミックキャパシタ10との間の幅及び長さの相関関係を示す模式図である。該積層セラミックキャパシタ10の幅を $W_{M L C C}$ 、長さを $L_{M L C C}$ として定義する。また、これらの離間された各ランド21、22のうちのいずれか一つのランド21の外側縁と他方のランド22の外側縁とを基準として、基板で占める幅を $W_{L A N D}(a)$ 、長さを $L_{L A N D}(a)$ として定義する。このとき、 $W_{M L C C} < L_{L A N D}(a) / L_{M L C C}$ 、 $1.2$ 、 $0 < W_{L A N D}(a) / W_{M L C C} < 1.2$ であるのが望ましい。該範囲を外れる場合には、ランド21、22の表面にコーティングされる導電材の体積が大きくなるので、積層セラミックキャパシタ10で発生する振動を、回路基板10に伝達する作用が大きくなり、望ましくない。

#### 【0057】

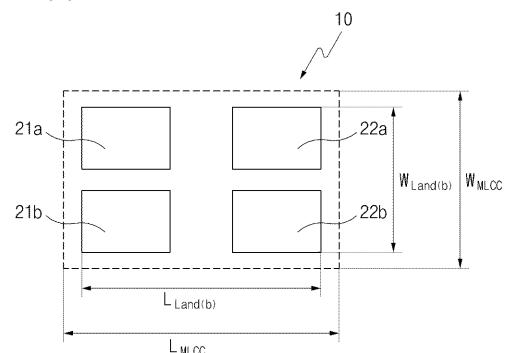

図5は、本発明のさらに他の一実施形態によるランドパターンを有する回路基板の平面図である。

#### 【0058】

図5には、回路基板20に、積層セラミックキャパシタが実装されるランド21a、21b、22a、22bが示されている。これらのランド21a、21b、22a、22bは、ハンダ付け量の減少のために、図1に示す積層セラミックキャパシタ10の外部端子電極14a、14bの各縁部に対応するように、それぞれ離間されて回路基板の表面に複数個設けられる。

#### 【0059】

10

20

30

40

50

図5では、一実施形態として四角形状のランドを4個設けた状態を示すが、これに限定されるものではない。ただ、前述のように、ランド21a、21b、22a、22bの表面にコーティングされる導電材15が振動騒音に影響を及ぼすが、ランド21a、21b、22a、22bが占める面積には、図4に示すように、一定の制限がある。この場合、積層セラミックキャパシタ10の中央部の変位差が大きいことが予想されるため、複数個のランド21a、21b、21c、21dを分散させて、基板への振動の伝達を低減することができるようになる。

#### 【0060】

図6は、本発明のさらに他の一実施形態によるランド21a、21b、22a、22bと積層セラミックキャパシタ10との間の幅、及び長さの相関関係を示す模式図である。

10 該積層セラミックキャパシタ10の幅を $W_{MLCC}$ 、長さを $L_{MLCC}$ として定義し、互いに離間された各ランド21a、21b、22a、22bのうちのいずれか一側のランド21a、22aの外側縁と他側のランド21b、22bの外側縁とを基準として、基板で占める幅を $W_{LAND(b)}$ 、一側のランド21a、21bと他側のランド22a、22bとが、基板で占める長さを $L_{LAND(b)}$ として定義する。このとき、 $W_{MLCC} < L_{MLCC}$ 、 $W_{LAND(b)} < L_{LAND(b)}$ の関係は、 $0 < L_{LAND(b)} / L_{MLCC} < 1.2$ 、 $0 < W_{LAND(b)} / W_{MLCC} < 1.2$ であるのが望ましい。該範囲を外れる場合には、ランド21a、21b、22a、22bの表面にコーティングされる導電材の体積が大きくなるので、積層セラミックキャパシタ10で発生する振動を回路基板10に伝達する作用が大きくなり、望ましくない。

#### 【0061】

一方、この場合、外部端子電極14a、14bとランド21、22とを導電接続する導電材15の高さ( $T_s$ )は、積層セラミックキャパシタの厚さ( $T_{MLCC}$ )の1/3未満とするのが望ましく、1/4未満とするのがさらに望ましい。ここで、積層セラミックキャパシタの外部電極端子の下辺部分のみに導電材が存在して、該導電材の高さがほとんど0の場合もある。積層セラミックキャパシタを水平方向に実装した状態で、導電材15の高さ( $T_s$ )が減少するほど、該導電材15が回路基板20に振動を伝達する程度が、積層セラミックキャパシタを垂直方向に実装した状態よりも遙かに低くなるからである。

#### 【0062】

一方、本発明において、積層セラミックキャパシタは、水平方向にテーピングすると共に、幅( $W_{MLCC}$ )及び厚さ( $T_{MLCC}$ )が等しいものであってもよい。幅及び厚さが等しい場合、テーピング時に、一般的に同じ方向性を有することは難しいが、本発明においては、水平方向に一定にテーピングしたものを使うことによって、振動減少の効果を得ることができる。

### 積層セラミックキャパシタの包装体

#### 【0063】

前述のように、水平方向に一定にテーピングした積層セラミックキャパシタを提供するために、本発明は、水平方向に一定に整列した積層セラミックキャパシタの包装体を提供する。

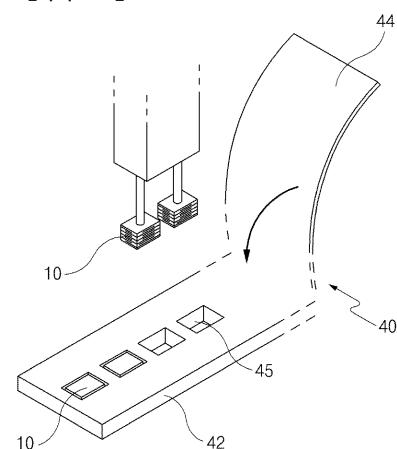

#### 【0064】

図7は、本発明の一実施形態による積層セラミックキャパシタが水平に配置されるように整列された積層セラミックキャパシタの包装体を示す。図8は、本発明のさらに他の一実施形態を示し、巻取られたリール形態の積層セラミックキャパシタの包装体を示す図である。

#### 【0065】

図7を参照すると、本実施形態の積層セラミックキャパシタの包装体40は、積層セラミックキャパシタ10が収納される収納部45が設けられた包装シート42を含む。

#### 【0066】

該包装シート42の収納部45は、積層セラミックキャパシタ10と対応する形状を有

10

20

30

40

50

し、該収納部45の底面を基準として内部電極12が水平に配置されるように移送部を通じて移動される。

【0067】

積層セラミックキャパシタの包装体40は、前記収納部45の底面を基準として、前記内部電極12が水平となるように配置された積層セラミックキャパシタ10が収納された該包装シート42を覆う包装膜44をさらに含む。

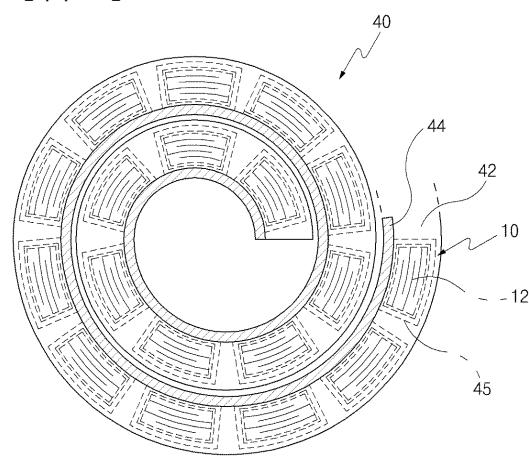

【0068】

図8は、リール形態に巻取られた形状の積層セラミックキャパシタの包装体を示す。この包装体は、図7に示す実施形態の積層セラミックキャパシタの包装体40が回収ロール(図示せず)によって、連続して巻取られて形成される。

10

### 積層セラミックキャパシタの水平方向整列方法

【0069】

方向に、一定に整列した積層セラミックキャパシタの包装体40を提供するため、本発明は、幅及び厚さが同一または類似の積層セラミックキャパシタ10の水平方向整列方法を提供する。

【0070】

ここで、積層セラミックキャパシタの幅及び厚さが同一または類似であるとは、 $0.75 \leq T_{MLCC} / W_{MLCC} \leq 1.25$ 範囲内の場合である。

20

【0071】

前述のように、幅及び厚さが同一または類似の積層セラミックキャパシタの圧電現象による振動騒音を大きく低減させるためには、積層セラミックキャパシタを回路基板に実装の際、積層セラミックキャパシタの内部電極面が回路基板面と水平に実装可能なように、包装体への収納過程において、積層セラミックキャパシタを水平方向に整列させることが必要である。

【0072】

このため、本発明では、磁気力を用いる整列方法を提供する。図9に示すように、積層セラミックキャパシタ10に磁石を近づけると、磁気抵抗が減るよう、内部電極導体が、図9(a)及び(b)に示すような積層セラミックキャパシタ10、10'の方向では、磁石に吸着される。しかし、図9(c)に示すような内部電極導体の積層方向から磁石を近づける積層セラミックキャパシタ10''の方向では、磁石に吸着しないという性質を利用する。

30

【0073】

そのような性質を用いて、幅及び厚さが同一または類似の積層セラミックキャパシタ10を包装体で水平方向に収納するため、移送過程中に、図10のように、磁石を側方に配置して積層セラミックキャパシタ10を水平に整列させる。

【0074】

この場合、図9(c)に示す積層セラミックキャパシタ10''は、磁気力によって、内部電極面が移送部100の移送方向に回転して整列するようになる。

40

【0075】

しかし、図11に示すように、移送過程中、図9(b)に示す積層セラミックキャパシタ10'のような状態(積層方向が磁石に向いている)に配列される場合が発生する。これは、図12に示すように、移送部100に所定の間隔を有する一対のガイド110を設けることによって解決することができる。

【0076】

この場合、該一対のガイド部110間の間隔gは、積層セラミックキャパシタの幅をW<sub>MLCC</sub>、厚さをT<sub>MLCC</sub>、長さをL<sub>MLCC</sub>として定義すると、下式、

$$(W_{MLCC}^2 + T_{MLCC}^2) < g < \min [(L_{MLCC}^2 + T_{MLCC}^2)]$$

50

を満足する。

**【 0 0 7 7 】**

以下では、本発明の好適な実施形態を導出するための試験例について説明することにする。

**【 0 0 7 8 】**

試験例 1：積層セラミックキャパシタを回路基板上に水平実装する場合と垂直実装する場合について、導電材の高さが振動騒音に及ぶ影響の評価

**【 0 0 7 9 】**

まず、積層セラミックキャパシタが水平実装された場合と垂直実装された場合について、ハンダの高さが振動騒音に及ぶ影響を確認するために、マイクロドリルを用いて、ハンダの高さを次第に低くしながら、振動による騒音を測定した。

10

**【 0 0 8 0 】**

図 13 は、積層セラミックキャパシタを回路基板上に水平実装する場合(a)と垂直実装する場合(b)とを示し、図 14 はその測定結果をグラフとして示す。

**【 0 0 8 1 】**

図 14 に示すように、ハンダの高さが低いほど振動騒音が減少することが認められる。特に、垂直実装する場合よりも水平実装する場合のほうが、振動騒音の変化幅が大きいという事実が分かつた。

**【 0 0 8 2 】**

このような事実は、ハンダなどの導電材は、積層セラミックキャパシタと回路基板との間の振動媒介としての役目を有し、該導電材の高さが低くなるにつれて基板への振動の伝達が低下するが、水平実装では、積層セラミックキャパシタの圧電性による縁部の振動の中で上面の振動の伝達が、該導電材の高さの低下とともに急に低下することで生じる。そのため、水平方向に実装する場合には、導電材の高さの変化による振動騒音の減少幅が非常に大きくなる一方、垂直方向に実装する場合には、該効果が発生しないので導電材の高さの変化による振動騒音の減少幅が大きくない。そのため、積層セラミックキャパシタは、内部電極を基準として回路基板と水平方向になるように実装し、ハンダ付け量(高さ)を少なくするのが騒音を減らすのに望ましい、という事実が認められる。

20

**【 0 0 8 3 】**

試験例 2：積層セラミックキャパシタを回路基板上に水平実装する場合と垂直実装する場合について、ランドの大きさが振動騒音に及ぶ影響の評価

30

**【 0 0 8 4 】**

試験例 1において、ハンダの高さによる振動騒音の変化結果に基づいて、追加的にランドの大きさによる振動騒音を測定し、これを図 15 のグラフとして示した。

**【 0 0 8 5 】**

図 15 から理解されるように、ランドの大きさを小さくするほど導電材の高さが低くなり、基板への振動が伝達されにくくなり、振動騒音が減少することが認められた。また、同様に、水平実装する場合、振動騒音が大幅に低減することが認められた。

**【 0 0 8 6 】**

一方、図 2 の積層セラミックキャパシタの幅(W)及び長さ(L)によって、積層セラミックキャパシタは、0603(L × W = 0.6 mm × 0.3 mm)、1005、1608、2012、3216、3225などの大きさを有する場合がある。このような大きさの積層セラミックキャパシタに対して水平実装すると共に、ランドの大きさを小さくした場合、振動騒音が大幅に低下する効果が認められた。しかしながら、3216以上の大きさの積層セラミックキャパシタの場合は、積層セラミックキャパシタの厚さに対して導電材の相対高さが低くても、該導電材の絶対量が多いので、振動騒音の低下効果を大きくするためには、該導電材の相対高さをさらに低くしなければならないことも認められた。

40

**【 0 0 8 7 】**

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、前記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれる

50

ことが意図される。

【符号の説明】

【0 0 8 8】

- 1 0 積層セラミックキャパシタ

- 1 1 誘電体シート

- 1 2 内部電極

- 1 4 a、1 4 b 外部端子電極

- 1 5 導電材

- 2 0 回路基板

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

(a)

(b)

【図 1 4】

【図 1 5】

## フロントページの続き

| (51)Int.Cl.            | F I          | テーマコード(参考) |

|------------------------|--------------|------------|

| H 05 K 13/04 (2006.01) | H 05 K 13/02 | Q          |

| H 01 G 4/12 (2006.01)  | H 05 K 13/04 | Z          |

| H 01 G 13/00 (2006.01) | H 05 K 13/02 | B          |

|                        | H 01 G 4/12  | 3 4 6      |

|                        | H 01 G 13/00 | 3 3 1 D    |

(72)発明者 イ・ビョン・ファ

大韓民国、463-906 キヨンギ - ド、ソンナム - シ、ブンダン - グ、イメ - ドン、イメチヨン・ハンシン・アパートメント 202-904

(72)発明者 パク・ミン・チョル

大韓民国、423-814 キヨンギ - ド、クァンミョン - シ、クァンミョン・6 - ドン、374-63

(72)発明者 パク・サン・ス

大韓民国、443-733 キヨンギ - ド、スウォン - シ、ヨントン - グ、ヨントン・2 - ドン、シンナムシル・ククドン・アパートメント 613-1702

(72)発明者 パク・ドン・ソク

大韓民国、136-833 ソウル、ソンブク - グ、チャンウィ・1 - ドン、209-26

F ターム(参考) 5E001 AB03 AF02

|            |      |      |      |      |      |      |

|------------|------|------|------|------|------|------|

| 5E082 AA01 | AB03 | BC40 | GG10 | GG28 | GG30 | PP09 |

| 5E313 AA03 | AA11 | AA18 | CC01 | DD06 | DD31 | EE50 |

| 5E319 AA03 | AB06 | AC11 | BB05 | CC33 | GG03 |      |

| 5E336 AA04 | CC31 | EE03 | GG15 |      |      |      |