## (12) 发明专利

(10) 授权公告号 CN 110622320 B

(45) 授权公告日 2023.08.08

(21) 申请号 201880019440.8

(72) 发明人 永冈达司 山下侑佑 浦上泰

(22) 申请日 2018.01.26

(74) 专利代理机构 中原信达知识产权代理有限公司 11219

(65) 同一申请的已公布的文献号

申请公布号 CN 110622320 A

专利代理人 高培培 赵晶

(43) 申请公布日 2019.12.27

(51) Int.CI.

H01L 29/78 (2006.01)

(30) 优先权数据

H01L 21/336 (2006.01)

2017-055344 2017.03.22 JP

H01L 29/12 (2006.01)

(85) PCT国际申请进入国家阶段日

H01L 29/861 (2006.01)

2019.09.19

H01L 29/868 (2006.01)

(86) PCT国际申请的申请数据

PCT/JP2018/002487 2018.01.26

(56) 对比文件

WO 2012/141121 A1, 2012.10.18

(87) PCT国际申请的公布数据

CN 101325198 A, 2008.12.17

W02018/173477 JA 2018.09.27

CN 105830217 A, 2016.08.03

(73) 专利权人 丰田自动车株式会社

CN 106463529 A, 2017.02.22

地址 日本爱知县丰田市

CN 101552274 A, 2009.10.07

专利权人 株式会社电装

审查员 韩增智

权利要求书4页 说明书9页 附图7页

## (54) 发明名称

半导体装置

## (57) 摘要

半导体装置具备：半导体基板，具有上表面和下表面；上表面电极，设置在半导体基板的上表面；及下表面电极，设置在半导体基板的下表面。在俯视观察时，半导体基板具有包含半导体基板的中心的第一范围和位于第一范围与半导体基板的外周缘之间的第二范围。在第一范围和第二范围分别设置内置有体二极管的MOSFET结构。MOSFET结构在第一范围与第二范围之间互不相同，以使相对于相同电流密度的体二极管的正向电压在第一范围中比在第二范围中高。

1.一种半导体装置,具备:

半导体基板,具有上表面和下表面;

上表面电极,设置在所述半导体基板的上表面;及

下表面电极,设置在所述半导体基板的下表面,

在俯视观察时,所述半导体基板具有包含所述半导体基板的中心的第一范围和位于所述第一范围与所述半导体基板的外周缘之间的第二范围,

在所述第一范围和所述第二范围分别设置内置有体二极管的MOSFET结构,

所述MOSFET结构在所述第一范围与所述第二范围之间互不相同,以使相对于相同电流密度的所述体二极管的正向电压在所述第一范围内比在所述第二范围内高,

所述MOSFET结构具有与所述上表面电极相接的n型的源极区、与所述下表面电极相接的n型的漏极区、介于所述源极区与所述漏极区之间并与所述上表面电极相接的p型的体区及介于所述体区与所述漏极区之间的n型的漂移区,

在所述第一范围内所述体区与所述上表面电极相接的面积的比例小于在所述第二范围内所述体区与所述上表面电极相接的面积的比例。

2.一种半导体装置,具备:

半导体基板,具有上表面和下表面;

上表面电极,设置在所述半导体基板的上表面;

下表面电极,设置在所述半导体基板的下表面;及

绝缘性的保护膜,覆盖所述上表面电极的一部分,

在俯视观察时,所述半导体基板具有由所述保护膜覆盖的第一范围和未由所述保护膜覆盖的第二范围,

在所述第一范围和所述第二范围分别设置内置有体二极管的MOSFET结构,该体二极管允许从所述上表面电极向所述下表面电极的通电,

所述MOSFET结构在所述第一范围与所述第二范围之间互不相同,以使相对于相同电流密度的所述体二极管的正向电压在所述第一范围内比在所述第二范围内高。

3.一种半导体装置,具备:

半导体基板,具有上表面和下表面;

上表面电极,设置在所述半导体基板的上表面;及

下表面电极,设置在所述半导体基板的下表面,

在所述上表面电极的上表面的至少一部分的范围接合有导电性构件,其中,

在俯视观察时,所述半导体基板具有未由所述导电性构件覆盖的第一范围和由所述导电性构件覆盖的第二范围,

在所述第一范围和所述第二范围分别设置内置有体二极管的MOSFET结构,该体二极管允许从所述上表面电极向所述下表面电极的通电,

所述MOSFET结构在所述第一范围与所述第二范围之间互不相同,以使相对于相同电流密度的所述体二极管的正向电压在所述第一范围内比在所述第二范围内高。

4.根据权利要求2或3所述的半导体装置,其中,

所述MOSFET结构具有与所述上表面电极相接的n型的源极区、与所述下表面电极相接的n型的漏极区、介于所述源极区与所述漏极区之间并与所述上表面电极相接的p型的体区

及介于所述体区与所述漏极区之间的n型的漂移区。

5. 根据权利要求4所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的面积的比例小于在所述第二范围中所述体区与所述上表面电极相接的面积的比例。

6. 根据权利要求1或5所述的半导体装置,其中,

所述第一范围和所述第二范围分别具有所述体区与所述上表面电极彼此相接的多个接触部位,

所述第一范围中的所述接触部位的间隔比所述第二范围中的所述接触部位的间隔宽。

7. 根据权利要求1或5所述的半导体装置,其中,

所述第一范围和所述第二范围分别具有所述体区与所述上表面电极彼此相接的多个接触部位,

所述第一范围中的所述接触部位的一个的面积比所述第二范围中的所述接触部位的一个的面积窄。

8. 根据权利要求6所述的半导体装置,其中,

所述第一范围和所述第二范围分别具有所述体区与所述上表面电极彼此相接的多个接触部位,

所述第一范围中的所述接触部位的一个的面积比所述第二范围中的所述接触部位的一个的面积窄。

9. 根据权利要求1、5、8中任一项所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度低于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度。

10. 根据权利要求4所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度低于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度。

11. 根据权利要求6所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度低于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度。

12. 根据权利要求7所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度低于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的所述体区的p型杂质的浓度。

13. 根据权利要求1、5、8、10~12中任一项所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度大于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度。

14. 根据权利要求4所述的半导体装置,其中,

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度大于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度。

15. 根据权利要求6所述的半导体装置，其中，

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度大于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度。

16. 根据权利要求7所述的半导体装置，其中，

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度大于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度。

17. 根据权利要求9所述的半导体装置，其中，

在所述第一范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度大于在所述第二范围中所述体区与所述上表面电极相接的接触部位的下方的结晶缺陷的密度。

18. 根据权利要求13所述的半导体装置，其中，

在所述第一范围的所述接触部位的下方所述漂移区包含的结晶缺陷的密度大于在所述第二范围的所述接触部位的下方所述漂移区包含的结晶缺陷的密度。

19. 根据权利要求14~17中任一项所述的半导体装置，其中，

在所述第一范围的所述接触部位的下方所述漂移区包含的结晶缺陷的密度大于在所述第二范围的所述接触部位的下方所述漂移区包含的结晶缺陷的密度。

20. 根据权利要求1~3、5、8、10~12、14~18中任一项所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

21. 根据权利要求4所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

22. 根据权利要求6所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

23. 根据权利要求7所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

24. 根据权利要求9所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

25. 根据权利要求13所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

26. 根据权利要求19所述的半导体装置，其中，

所述半导体装置还具备检测半导体基板的温度的温度传感器，

在俯视观察时，所述温度传感器配置于所述半导体基板的中心或其附近。

## 半导体装置

### 技术领域

[0001] 本说明书中公开的技术涉及半导体装置,特别是涉及用于改善半导体装置的温度分布的技术。

### 背景技术

[0002] 日本特开2011-134950号公报公开了一体地形成有IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极晶体管)和续流二极管的半导体装置。这种半导体装置也称为RC(Reverse Conducting,逆导)-IGBT,具有沿着半导体基板的下表面交替地设有IGBT的集电极区和续流二极管的阴极区的结构。在该半导体装置中,集电极区相对于阴极区之比在半导体基板的中央部大,在半导体基板的周缘部小。根据这样的结构,在散热性差的中央部,能抑制半导体基板的发热量,因此能改善半导体装置的温度分布(即,均匀化)。

### 发明内容

[0003] 作为具有与RC-IGBT同样的功能的其他的半导体装置,已知具有内置有体二极管(也称为寄生二极管)的MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor,金氧半场效晶体管)结构的半导体装置。在这种半导体装置中,MOSFET结构的体二极管能够作为续流二极管发挥功能。然而,MOSFET结构的体二极管的与通电相伴的发热量比较大。由此,如果利用体二极管作为续流二极管,则半导体基板容易成为高温,而且,温度分布的变动也容易增大。上述的文献的技术对于温度分布的改善有效,但是RC-IGBT利用了特有的结构,因此无法采用于具有MOSFET结构的半导体装置。

[0004] 因此,本说明书提供用于改善具有MOSFET结构的半导体装置的温度分布的技术。

[0005] 在本说明书公开的技术中,在半导体基板之中确定散热性不同的至少两个范围,在上述的范围之间使MOSFET结构(特别是体二极管涉及的结构)互不相同。详细而言,以相对于相同电流密度的体二极管的正向电压在散热性差的范围中高并在散热性优异的范围中低的方式设计各范围中的MOSFET结构。根据这样的结构,在电流向MOSFET结构的体二极管流动时,在散热性差的范围中,电流密度小,在散热性优异的范围中,电流密度大。其结果是,在散热性不同的多个范围内,温度分布被均匀化。需要说明的是,体二极管的正向电压能够以避免对例如接通电压这样的MOSFET的特性造成影响的方式进行调整。

[0006] 通过本技术的一方面,公开了如下的半导体装置。该半导体装置具备:半导体基板,具有上表面和下表面;上表面电极,设置在半导体基板的上表面;及下表面电极,设置在半导体基板的下表面。在俯视观察时,半导体基板具有包含半导体基板的中心的第一范围和位于第一范围与半导体基板的外周缘之间的第二范围。在第一范围和第二范围分别设置内置有体二极管的MOSFET结构。MOSFET结构在第一范围与第二范围之间互不相同,以使相对于相同电流密度的体二极管的正向电压在第一范围中比在第二范围中高。

[0007] 在上述的半导体装置中,包含半导体基板的中心的第一范围与位于其周围的第二范围相比,在散热性上差。由此,为了使体二极管的电流密度在第一范围中比在第二范围中

小而在第一范围与第二范围之间使MOSFET结构互不相同。根据这样的结构，在散热性差的第一范围内，能抑制体二极管产生的发热量，因此能改善半导体装置的温度分布。

[0008] 通过本技术的另一方面，也公开了如下的半导体装置。该半导体装置具备：半导体基板，具有上表面和下表面；上表面电极，设置在半导体基板的上表面；下表面电极，设置在半导体基板的下表面；及绝缘性的保护膜，覆盖上表面电极的一部分。在俯视观察时，半导体基板具有由保护膜覆盖的第一范围和未由保护膜覆盖的第二范围。在第一范围和第二范围分别设置内置有体二极管的MOSFET结构。MOSFET结构在第一范围与第二范围之间互不相同，以使相对于相同电流密度的体二极管的正向电压在第一范围内比在第二范围内高。

[0009] 在上述的半导体装置中，由于保护膜阻碍散热，因此由保护膜覆盖的第一范围与未由保护膜覆盖的第二范围相比在散热性上差。由此，为了使体二极管的电流密度在第一范围内比在第二范围内小而在第一范围与第二范围之间使MOSFET结构互不相同。根据这样的结构，在散热性差的第一范围内，能抑制体二极管的发热量，因此能改善半导体装置的温度分布。

[0010] 通过本技术的又一方面，还公开了如下的半导体装置。该半导体装置具备：半导体基板，具有上表面和下表面；上表面电极，设置在半导体基板的上表面；下表面电极，设置在半导体基板的下表面；绝缘性的保护膜，覆盖上表面电极的一部分。在上表面电极的上表面的至少一部分的范围接合有例如引线这样的导电性构件。在俯视观察时，半导体基板具有未由导电性构件覆盖的第一范围和由导电性构件覆盖的第二范围。在第一范围和第二范围分别设置内置有体二极管的MOSFET结构。MOSFET结构在第一范围与第二范围之间互不相同，以使相对于相同电流密度的体二极管的正向电压在第一范围内比在第二范围内高。

[0011] 在上述的半导体装置中，能期待通过导电性构件的散热，因此未由导电性构件覆盖的第一范围与由导电性构件覆盖的第二范围相比在散热性上差。由此，为了使体二极管的电流密度在第一范围内比在第二范围内小而在第一范围与第二范围之间使MOSFET结构互不相同。根据这样的结构，在散热性差的第一范围内，能抑制体二极管的发热量，因此能改善半导体装置的温度分布。

## 附图说明

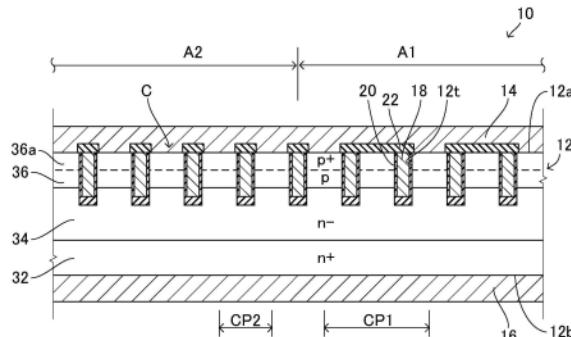

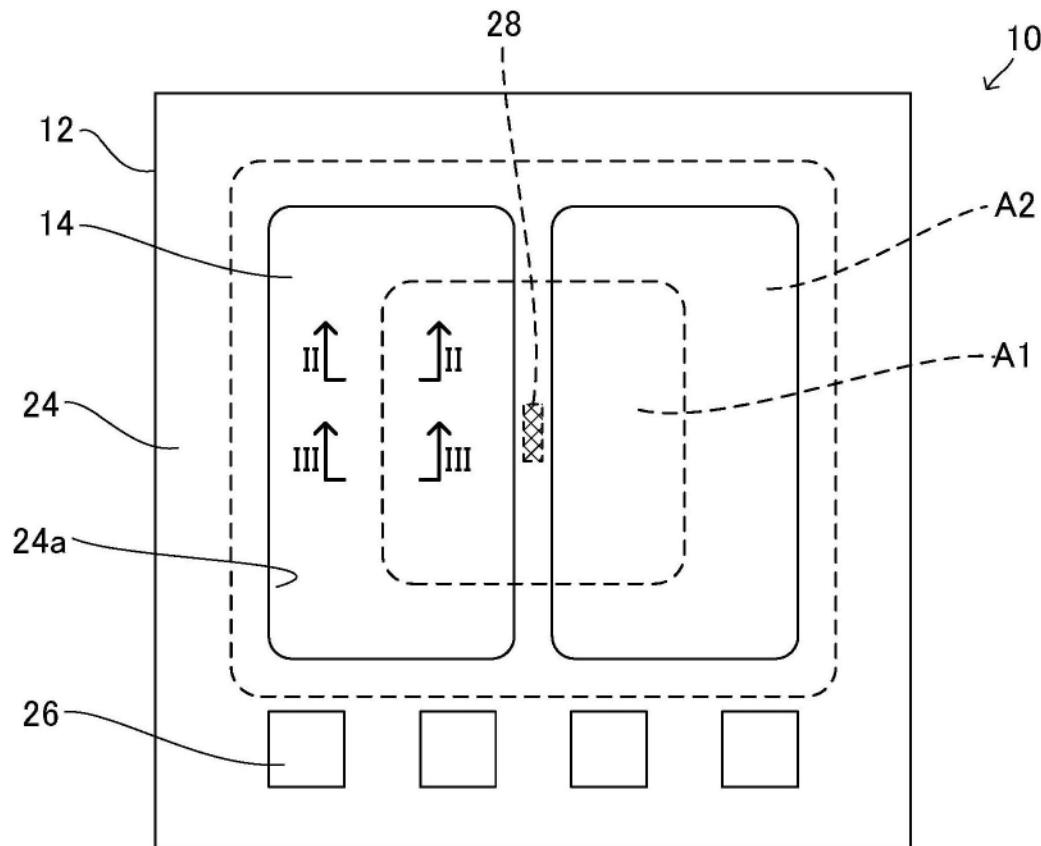

[0012] 图1是实施例1的半导体装置10的俯视图。

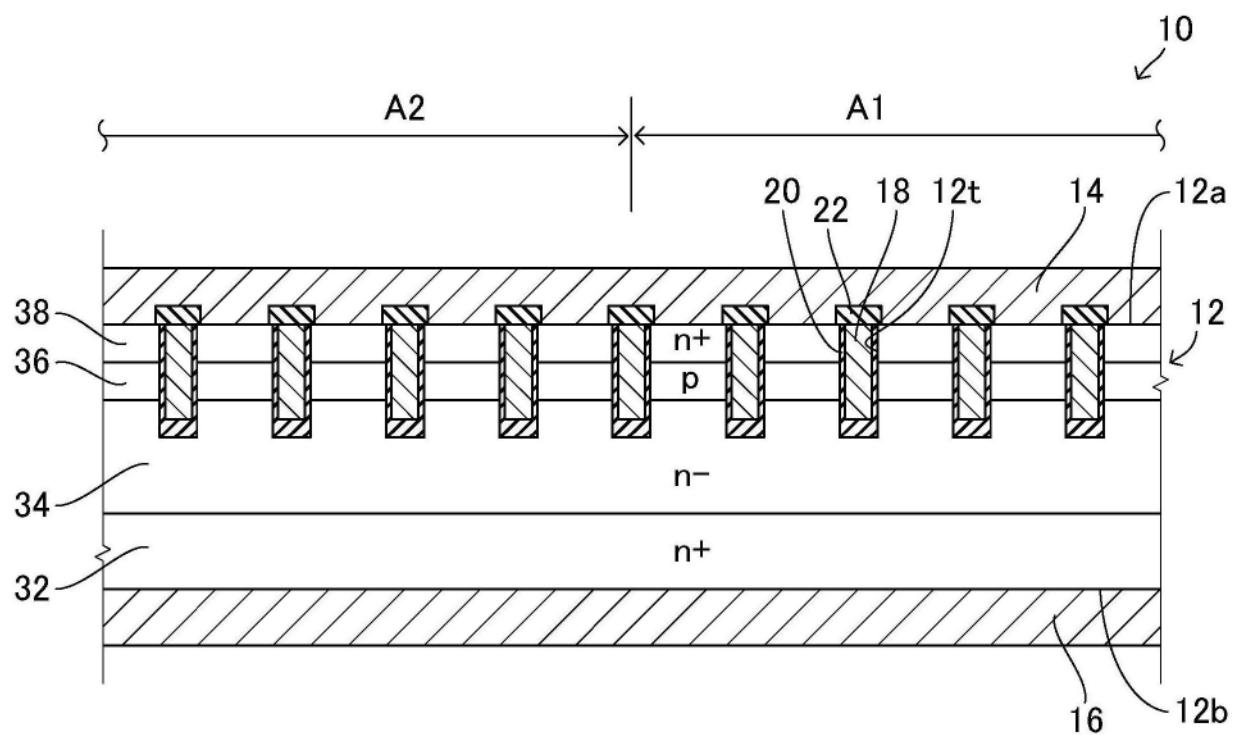

[0013] 图2是图1中的II-II线处的剖视图，沿着源极区38示意性地示出半导体装置10的截面结构。

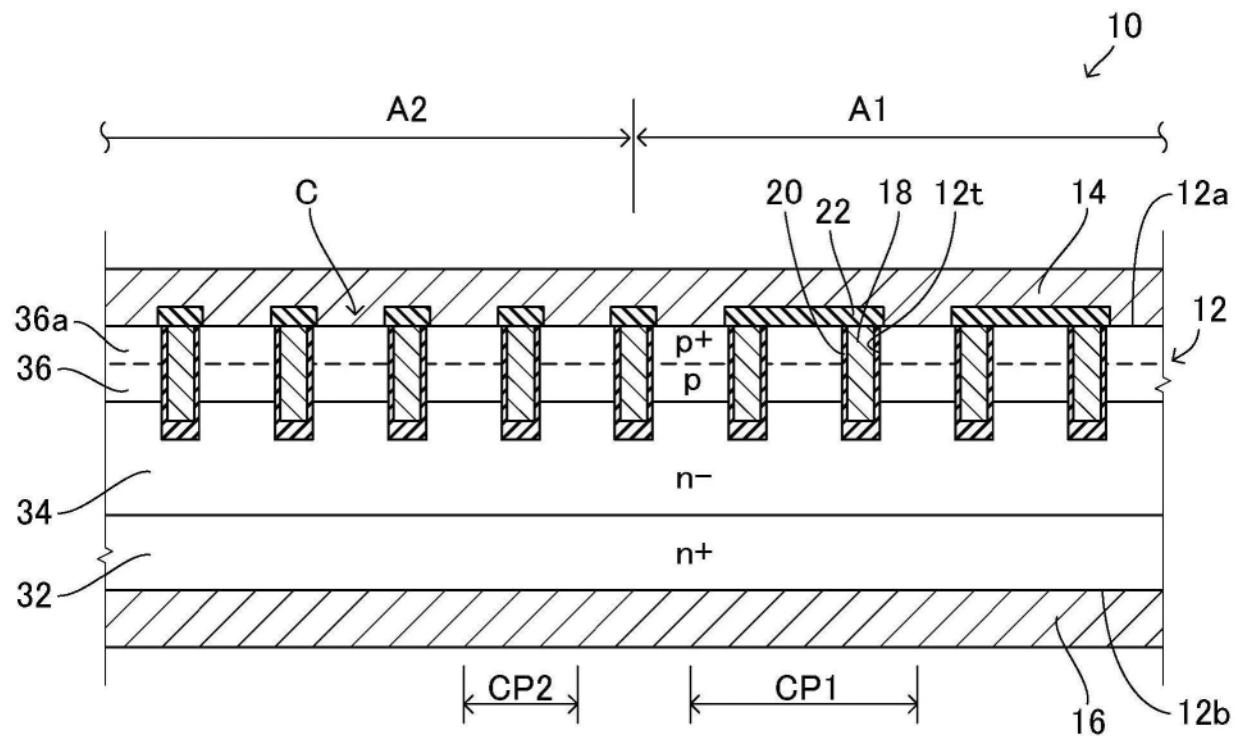

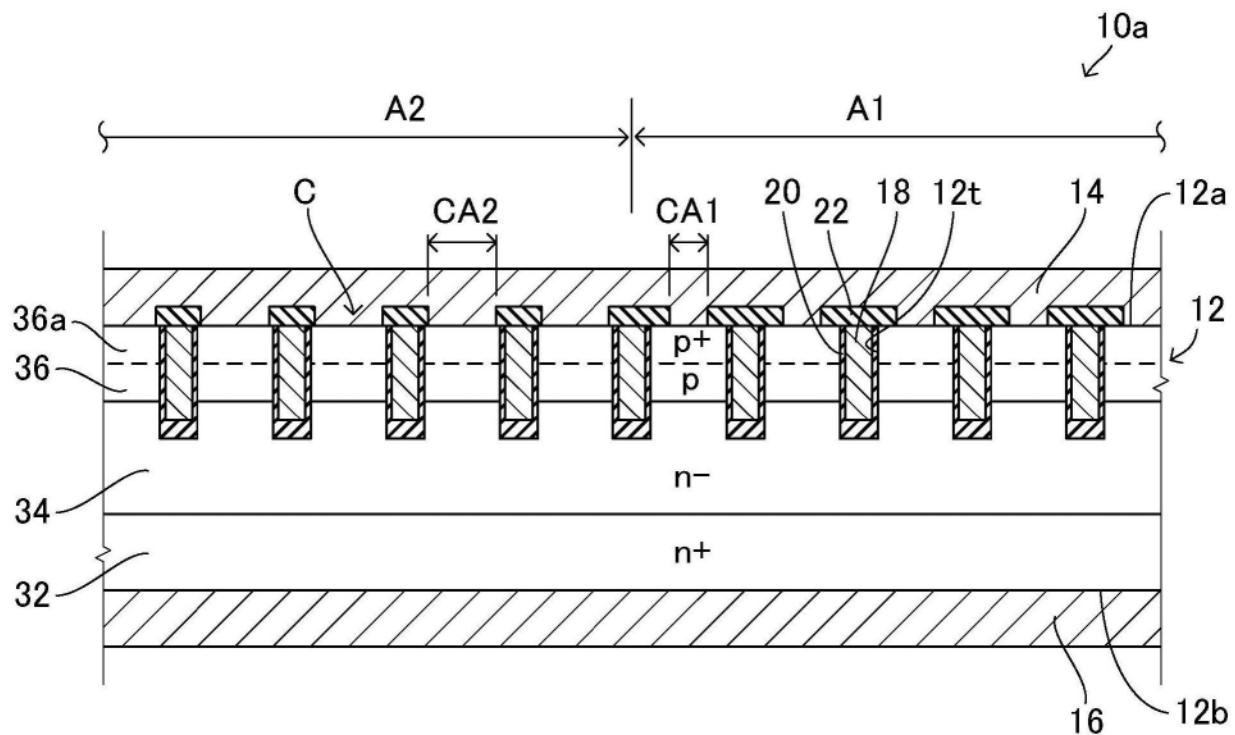

[0014] 图3是图1中的III-III线处的剖视图，沿着体接触区36a示意性地示出半导体装置10的截面结构。在两个范围A1、A2之间，相邻的体接触部位C的间隔CP1、CP2互不相同。

[0015] 图4示出实施例1的变形例的半导体装置10a。在该半导体装置10a中，在两个范围A1、A2之间，各体接触部位C的面积CA1、CA2互不相同。

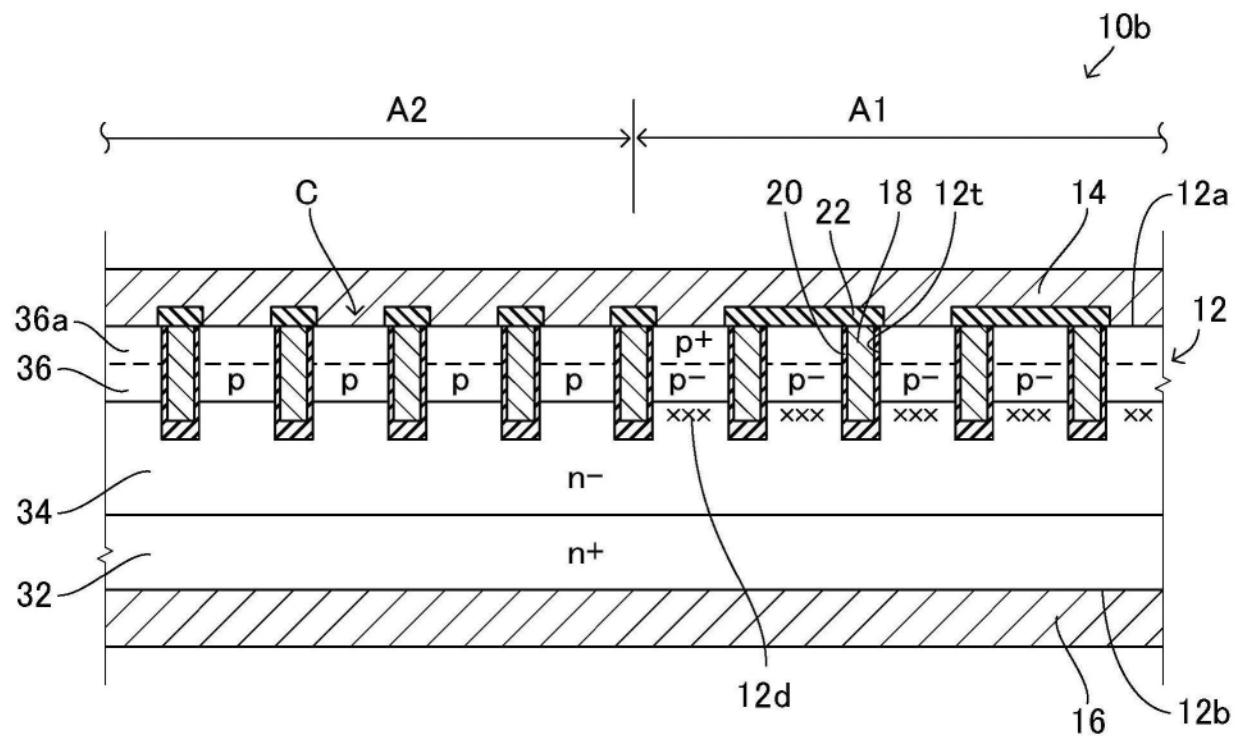

[0016] 图5示出实施例1的另一变形例的半导体装置10b。在该半导体装置10b中，在两个范围A1、A2之间，体接触部位C的下方的体区36的p型杂质的浓度互不相同。而且，在两个范围A1、A2之间，体接触部位C的下方的结晶缺陷12d的密度互不相同。

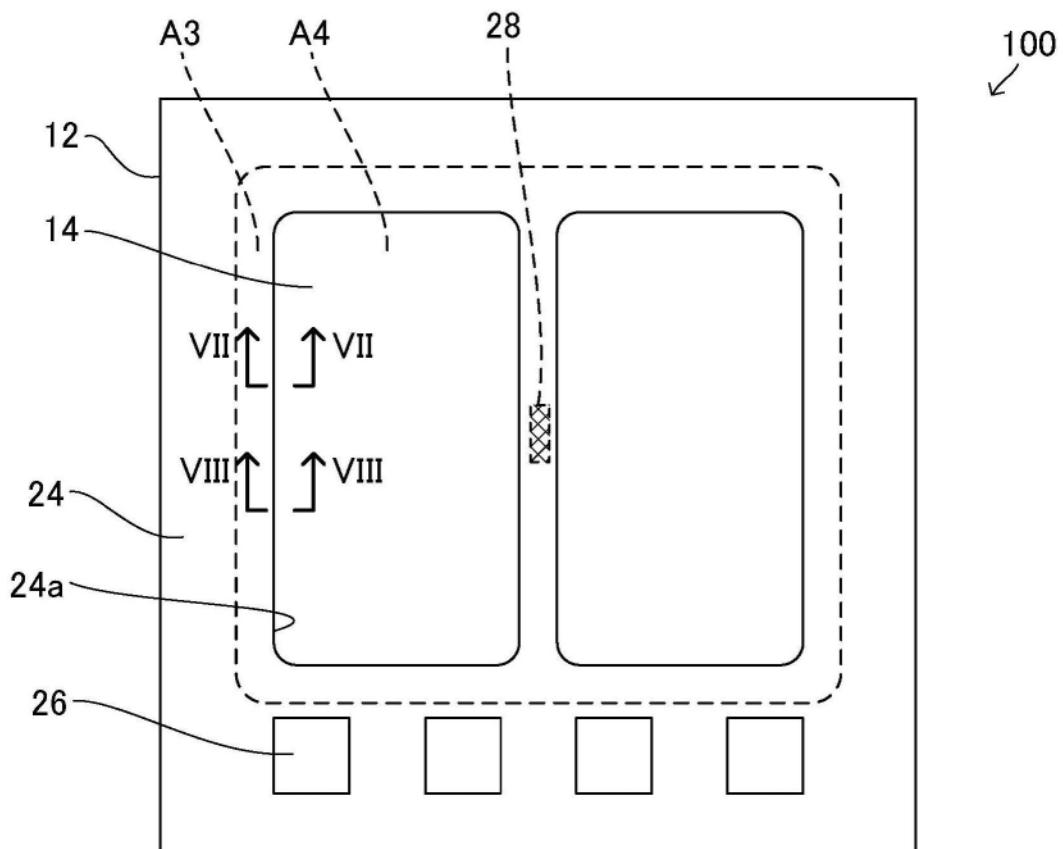

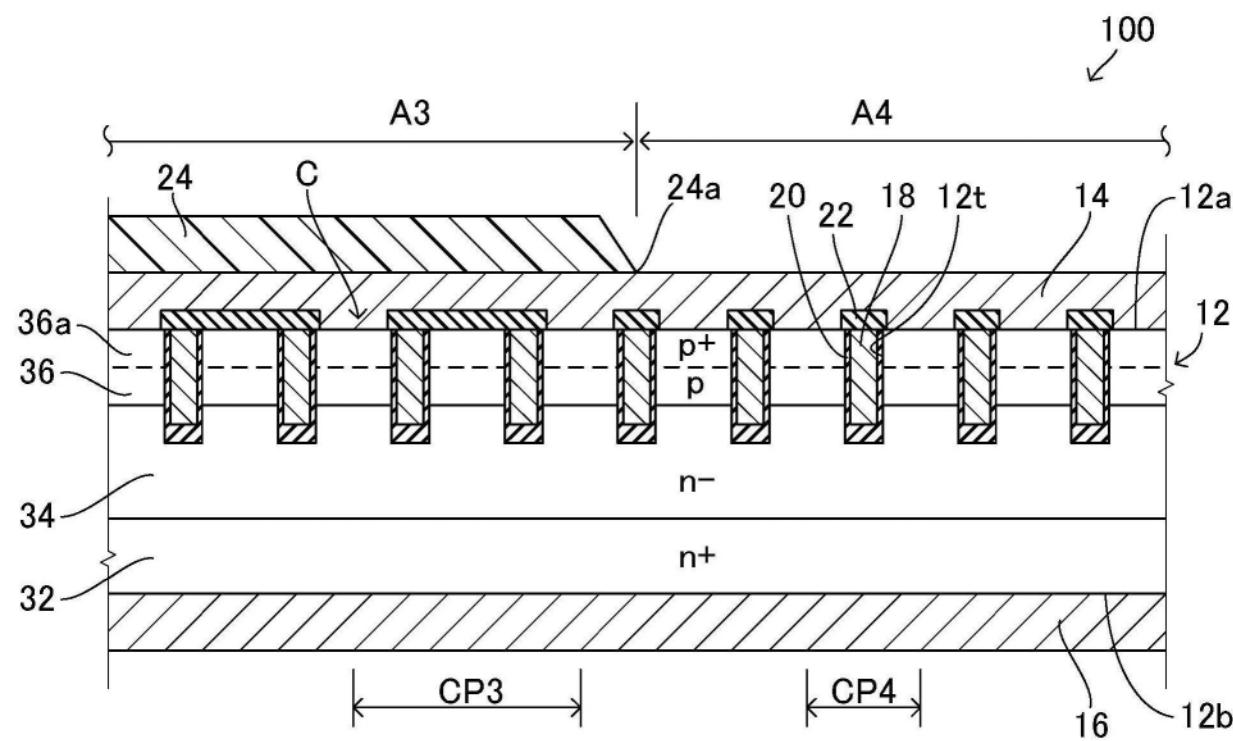

[0017] 图6是实施例2的半导体装置100的俯视图。

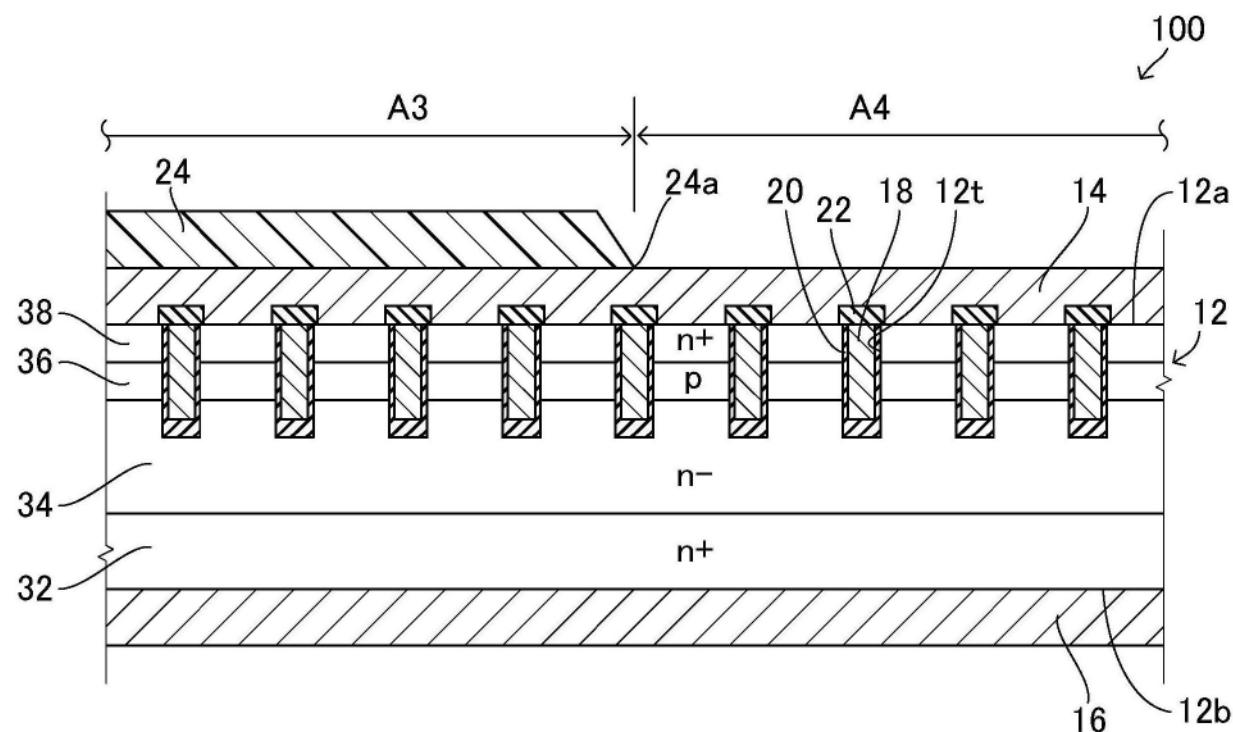

[0018] 图7是图6中的VII-VII线处的剖视图，沿着源极区38示意性地示出半导体装置100

的截面结构。

[0019] 图8是图6中的VIII-VIII线处的剖视图,沿着体接触区36a示意性地示出半导体装置100的截面结构。

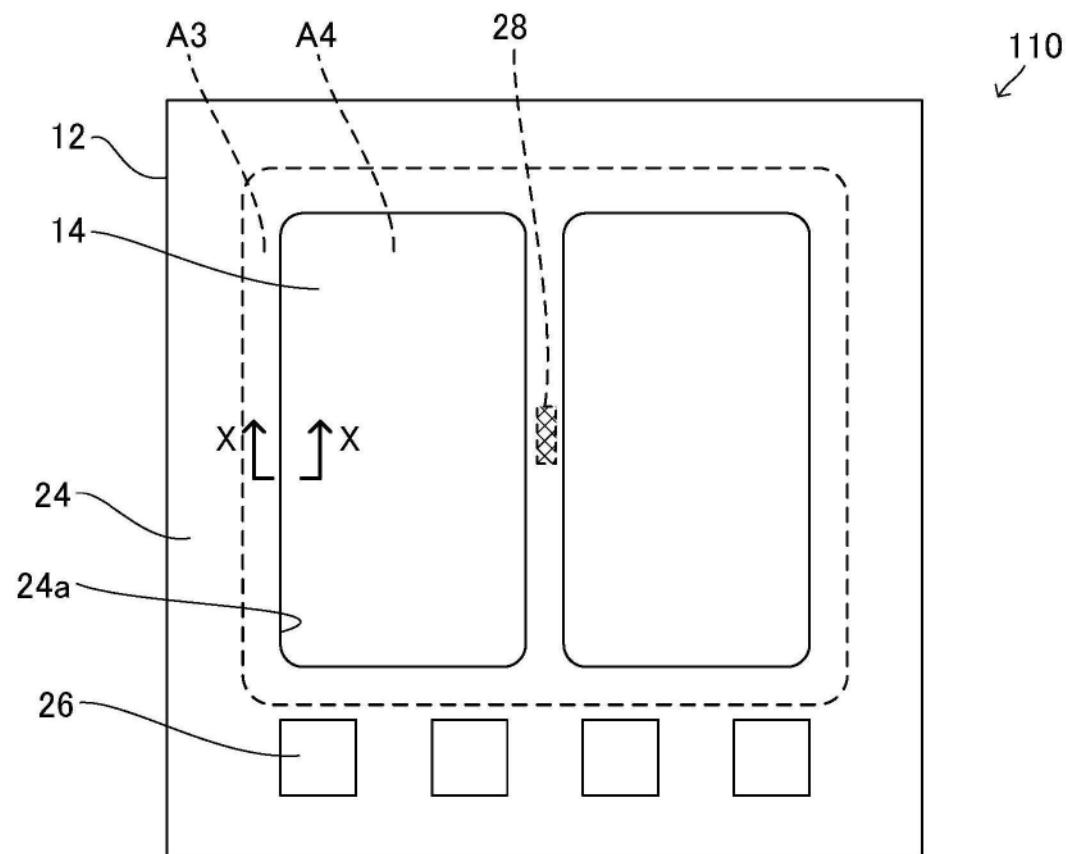

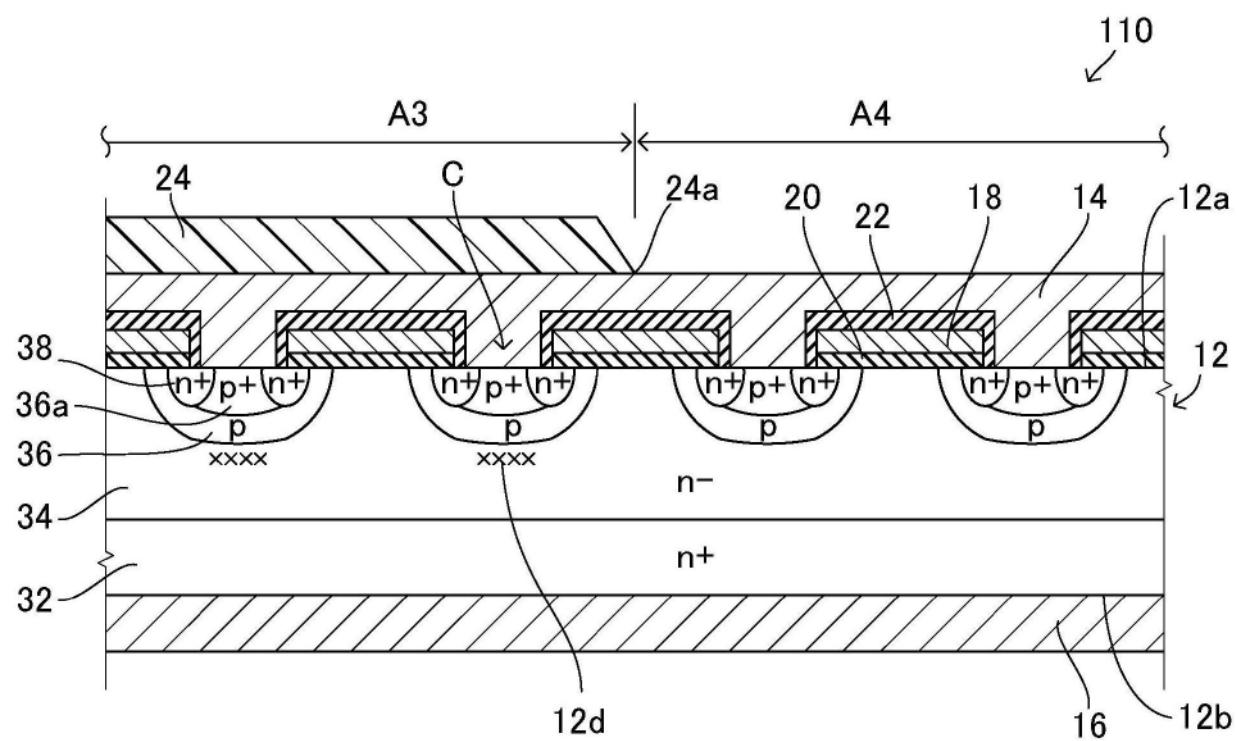

[0020] 图9是实施例3的半导体装置110的俯视图。

[0021] 图10是图9中的X-X线处的剖视图,示意性地示出半导体装置110的截面结构。

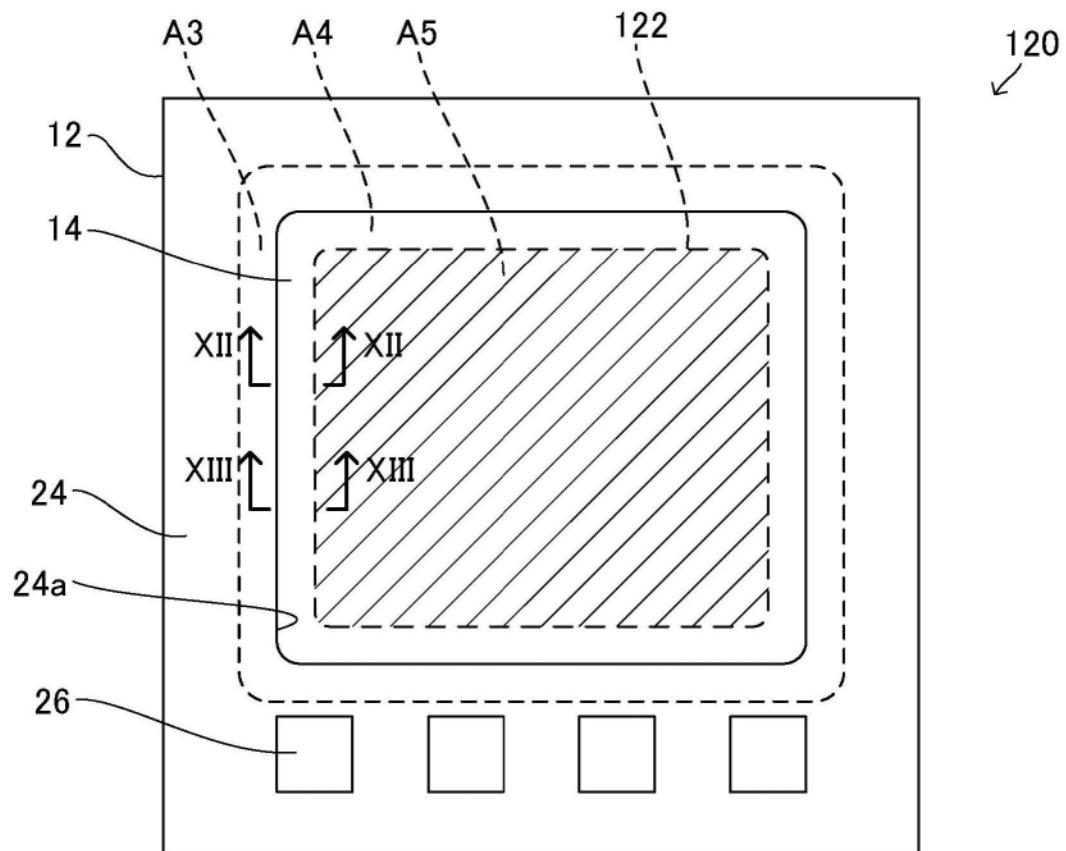

[0022] 图11是实施例4的半导体装置120的俯视图。

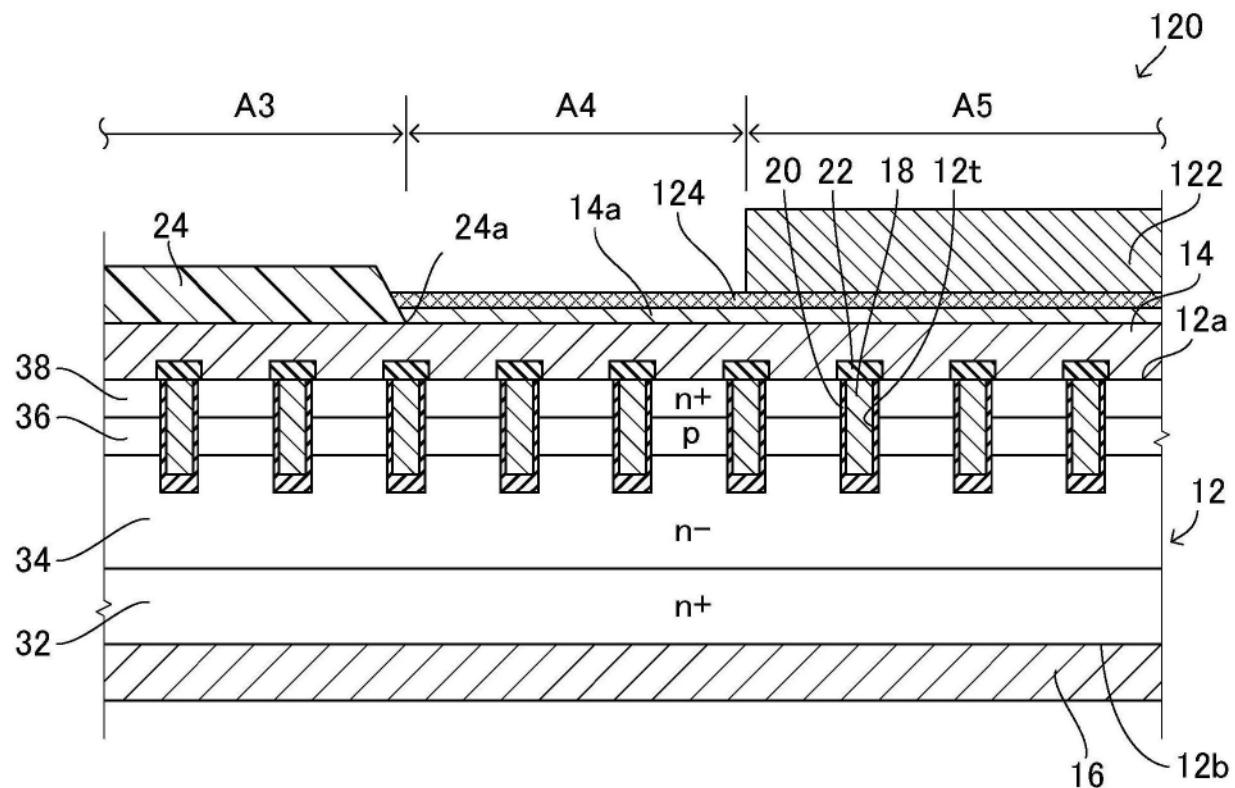

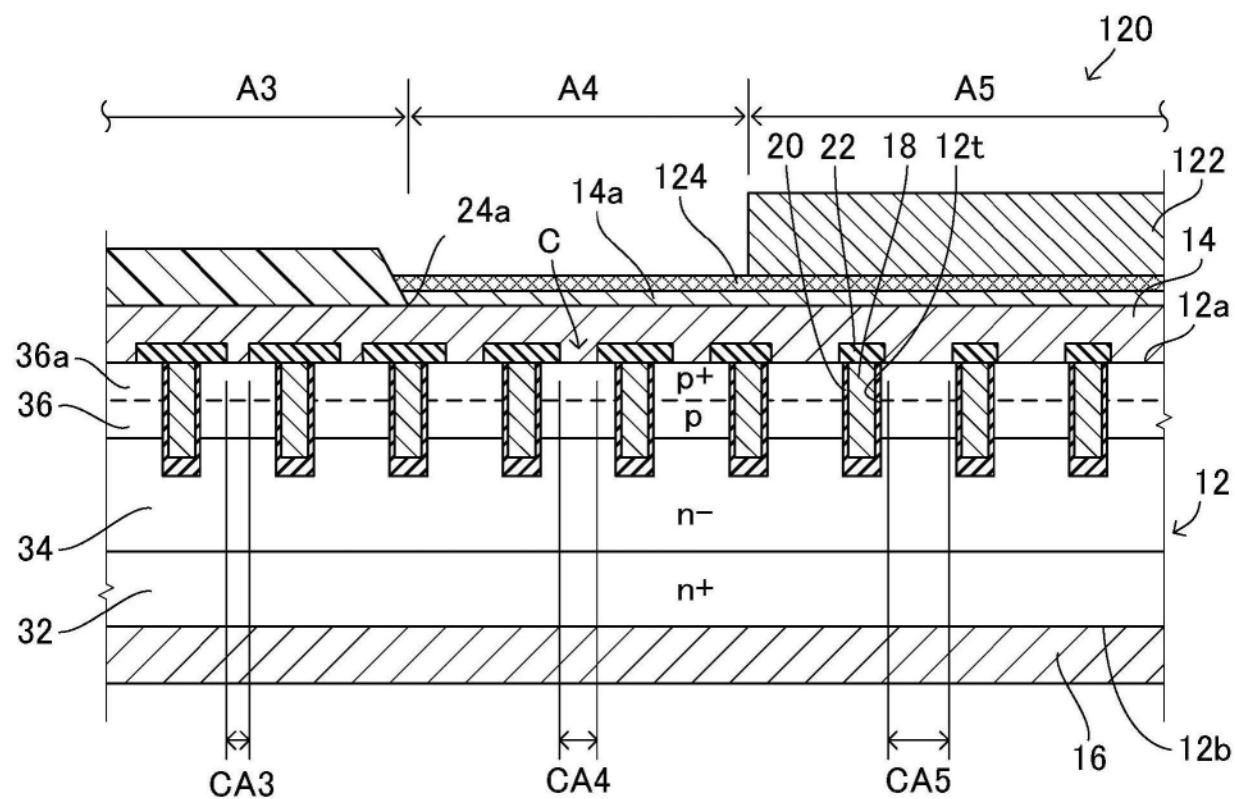

[0023] 图12是图11中的XII-XII线处的剖视图,沿着源极区38示意性地示出半导体装置120的截面结构。

[0024] 图13是图11中的XIII-XIII线处的剖视图,沿着体接触区36a示意性地示出半导体装置120的截面结构。

## 具体实施方式

[0025] 在本技术的一实施方式中,MOSFET结构可以具有与上表面电极相接的n型的源极区、与下表面电极相接的n型的漏极区、介于源极区与漏极区之间并与上表面电极相接的p型的体区及介于体区与漏极区之间的n型的漂移区。根据这样的结构,在MOSFET结构中,通过体区与漂移区之间的pn结,构成允许从上表面电极朝向下表面电极的电流的体二极管。但是,作为其他的实施方式,MOSFET结构可以具有与上述不同的结构。

[0026] 在本技术的一实施方式中,在第一范围中体区与上表面电极相接的面积的比例可以小于在第二范围中体区与上表面电极相接的面积的比例。根据这样的结构,不用使作为MOSFET的特性变化而能够使相对于相同电流密度的体二极管的正向电压在第一范围内比在第二范围内高。

[0027] 作为上述的结构的一方式,第一范围和第二范围分别可以具有体区与上表面电极彼此相接的多个接触部位。这种情况下,第一范围中的接触部位的间隔可以比第二范围中的接触部位的间隔宽。在此基础上或取代于此,第一范围中的接触部位的一个的面积可以比第二范围中的接触部位的一个的面积窄。

[0028] 在本技术的一实施方式中,在第一范围中体区与上表面电极相接的接触部位的下方的体区的p型杂质的浓度可以低于在第二范围中体区与上表面电极相接的接触部位的下方的体区的p型杂质的浓度。根据这样的结构,也不用使作为MOSFET的特性变化而能够使相对于相同电流密度的体二极管的正向电压在第一范围内比在第二范围内高。

[0029] 在本技术的一实施方式中,在第一范围中体区与上表面电极相接的接触部位的下方的结晶缺陷的密度可以大于在第二范围中体区与上表面电极相接的接触部位的下方的结晶缺陷的密度。根据这样的结构,也不用使作为MOSFET的特性变化而能够使相对于相同电流密度的体二极管的正向电压在第一范围内比在第二范围内高。

[0030] 在上述的实施方式中,在第一范围的所述的接触部位的下方漂移区包含的结晶缺陷的密度可以大于在第二范围的所述的接触部位的下方漂移区包含的结晶缺陷的密度。即,作为一例,上述的结晶缺陷的密度的差别化可以在漂移区进行。

[0031] 在本技术的一实施方式中,半导体装置可以还具备检测半导体基板的温度的温度传感器。这种情况下,在俯视观察时,温度传感器可以配置于半导体基板的中心或其附近。但是,配置温度传感器的位置可以进行各种变更。根据本技术,由于能改善半导体基板的温

度分布，因此无论温度传感器的位置如何，都能够正确地检测半导体基板的温度。

[0032] 以下，关于本发明的代表性而非限定性的具体例，参照附图进行详细说明。该详细的说明仅是将用于实施本发明的优选例的详情向本领域技术人员展示，没有限定本发明的范围。而且，以下公开的追加性的特征以及发明为了提供进一步改善的半导体装置和其使用及制造方法，可以与其他的特征或发明另行地或一起使用。

[0033] 另外，在以下的详细的说明中公开的特征或工序的组合在最广泛的意思中不是实施本发明时必须的，是仅为了特别说明本发明的代表性的具体例而记载的。此外，在提供本发明的追加性且有用的实施方式中，上述及下述的代表性的具体例的各个特征、以及请求保护的范围所记载的各种特征不是必须如在此记载的具体例那样或者如列举的顺序那样组合。

[0034] 本说明书及/或请求保护的范围所记载的全部的特征意在作为对于原始申请的公开以及主张权利的特定事项的限定而与实施例及/或请求保护的范围所记载的特征的结构另行地单独且相互独立公开。此外，全部的数值范围及组或集团相关的记载作为对于原始申请的公开以及主张权利的特定事项的限定，具有公开它们的非极端的结构的意图。

[0035] (实施例1)

[0036] 参照附图，说明实施例1的半导体装置10。本实施例的半导体装置10是使用于电力供给电路的功率半导体装置。如后所述，半导体装置10具有内置有体二极管(也称为寄生二极管)的MOSFET结构，例如可以采用作为转换器或变换器的开关元件。

[0037] 如图1-图3所示，半导体装置10具备半导体基板12。半导体基板12具有上表面12a和位于上表面12a的相反侧的下表面12b。需要说明的是，在此使用的“上表面”及“下表面”的用语是用于简便地区分相互位于相反侧的两个面的表现，没有限定半导体装置10的制造时或使用时的姿势。而且，在本说明书中“下方”的用语是指从半导体基板12的上表面12a朝向下表面12b的方向。本实施例的半导体基板12是碳化硅(SiC)的基板。但是，构成半导体基板12的半导体材料没有特别限定，例如可以为硅(Si)，也可以为氮化镓(GaN)这样的化合物半导体。需要说明的是，与硅相比，碳化硅或氮化镓这样的宽禁带半导体具有pn结二极管的正向电压高这样的特性。由此，在本说明书中公开的技术在半导体基板12为宽禁带半导体的基板的情况下，能发挥更高的效果。

[0038] 半导体装置10还具备在半导体基板12的上表面12a设置的上表面电极14和在半导体基板12的下表面12b设置的下表面电极16。上表面电极14和下表面电极16是具有导电性的构件。上表面电极14与半导体基板12的上表面12a进行欧姆接触，下表面电极16与半导体基板12的下表面12b进行欧姆接触。上表面电极14及下表面电极16可以使用例如铝(A1)、镍(Ni)、钛(Ti)、金(Au)这样的金属材料形成。关于构成上表面电极14及下表面电极16的具体的材料或结构没有特别限定。

[0039] 在半导体基板12的上表面12a设有多个沟槽12t。多个沟槽12t相互平行且沿图1的上下方向延伸。即，图2、图3示出与多个沟槽12t垂直的截面。在各个沟槽12t内设有栅电极18和栅极绝缘膜20。栅电极18由例如多晶硅这样的导电性材料形成，栅极绝缘膜20由例如氧化硅(SiO<sub>2</sub>)这样的绝缘性材料形成。栅电极18隔着栅极绝缘膜20而与半导体基板12相对。在栅电极18与上表面电极14之间形成有层间绝缘膜22。层间绝缘膜22由例如氧化硅(SiO<sub>2</sub>)这样的绝缘性材料形成，对栅电极18与上表面电极14之间进行电绝缘。

[0040] 在半导体基板12的上表面12a侧设有保护膜24。保护膜24通过例如聚酰亚胺这样的绝缘性材料形成。保护膜24位于上表面电极14上,将上表面电极14的一部分覆盖。保护膜24主要覆盖上表面电极14的外周部分,在保护膜24的中央部分设有使上表面电极14露出的两个开口24a。关于保护膜24的截面结构,例如图7、8所示。需要说明的是,关于保护膜24及其开口24a的位置、大小、形状、个数这样的结构,没有特别限定。

[0041] 而且,在半导体基板12的上表面12a侧设有多个信号电极26、温度传感器28。在多个信号电极26电连接有例如栅电极18、上表面电极14及温度传感器28。温度传感器28配置在半导体基板12的中心(或其附近)。温度传感器28是用于测定半导体基板12的温度的传感器,输出与温度相应的电信号。通常,半导体装置10的动作根据温度传感器28的检测温度而被控制。例如,在温度传感器28的检测温度超过了上限值时,实施将向半导体基板12流动的电流隔断这样的控制。

[0042] 半导体基板12具备漏极区32、漂移区34、体区36及源极区38。漏极区32为n型的半导体区。漏极区32沿着半导体基板12的下表面12b设置,向下表面12b露出。漏极区32遍及半导体基板12的整体而呈层状地扩展。前述的下表面电极16与漏极区32进行欧姆接触。

[0043] 漂移区34是n型的半导体区。漂移区34中的n型杂质的浓度比漏极区32中的n型杂质的浓度低。漂移区34位于漏极区32上,与漏极区32相接。漂移区34遍及半导体基板12的整体而呈层状地扩展。漂移区34中的n型杂质的浓度沿半导体基板12的厚度方向可以恒定,也可以连续地或逐级地变化。而且,在漂移区34内,例如可以沿沟槽12t的底面设置p型的半导体区(所谓漂浮区)。

[0044] 体区36为p型的半导体区。体区36位于漂移区34上,与漂移区34相接。体区36遍及半导体基板12的整体而呈层状地扩展。体区36具有向半导体基板12的上表面12a露出的体接触区36a。体接触区36a的p型杂质的浓度比体区36的其他的部分的p型杂质的浓度高。由此,前述的上表面电极14与体接触区36a进行欧姆接触。在半导体基板12的上表面12a中,多个体接触区36a与多个源极区38一起设置成条纹状。换言之,在半导体基板12的上表面12a中,沿着沟槽12t的长度方向(图1的上下方向)交替形成体接触区36a和源极区38,各个体接触区36a及源极区38与沟槽12t的长度方向垂直地延伸(参照图2、图3)。

[0045] 源极区38为n型的半导体区。源极区38的n型杂质的浓度比漂移区34的n型杂质的浓度高。源极区38位于体区36上,向半导体基板12的上表面12a露出。前述的上表面电极14也与源极区38进行欧姆接触。源极区38经由体区36而被从同样n型的漂移区34及漏极区32分隔。

[0046] 沟槽12t从半导体基板12的上表面12a穿过体区36延伸至漂移区34。栅电极18隔着栅极绝缘膜20而与源极区38、体区36及漂移区34相对。由此,当对于上表面电极14向栅电极18施加正的电压(所谓栅极驱动电压)时,在与栅电极18相对的体区36形成反转层(所谓沟道)。源极区38与漂移区34之间被电连接,上表面电极14与下表面电极16之间进行电导通。

[0047] 如以上所述,在半导体基板12设置具有漏极区32、漂移区34、体区36及源极区38的MOSFET结构。该MOSFET结构如图3正好示出那样内置有体二极管(也称为寄生二极管)。即,在上表面电极14与下表面电极16之间,通过体区36(包含体接触区36a)的p型半导体层和包含漂移区34及漏极区32的n型半导体层,形成pn结型的二极管。该体二极管允许从上表面电极14向下表面电极16流动电流,而另一方面,隔断从下表面电极16向上表面电极14流动的

电流。由此,在采用半导体装置10作为转换器或变换器的开关元件时,能够利用半导体装置10的体二极管作为续流二极管。因此,不必需要另外的二极管元件。

[0048] 然而,MOSFET结构的体二极管的与通电相伴的发热量比较大。由此,如果利用体二极管作为续流二极管,则半导体基板12容易成为高温,而且,温度分布的变动也容易增大。如前所述,半导体基板12的温度由温度传感器28监视,基于温度传感器28的检测温度,来控制半导体装置10的动作。关于这一点,如果半导体基板12的温度分布不均,则温度传感器28的检测温度的可靠性下降。即,即使基于温度传感器28的检测温度来控制半导体装置10的动作,也可能无法避免半导体基板12的过热引起的故障。这样,在半导体装置10中,改善半导体基板12的温度分布的情况至关重要。为此,在本实施例的半导体装置10中,采用下述的结构。

[0049] 如图1-图3所示,在俯视观察时,半导体基板12具有包含半导体基板12的中心的范围A1和位于该范围A1与半导体基板12的外周缘之间的范围A2。在两个范围A1、A2分别设置前述的内置体二极管的MOSFET结构。如图2所示,关于MOSFET结构中的涉及MOSFET的动作的结构,在两个范围A1、A2之间彼此一样。另一方面,如图3所示,关于涉及体二极管的结构,在两个范围A1、A2之间,MOSFET结构互不相同。这是因为,相对于相同电流密度的体二极管的正向电压在范围A1内比范围A2高。

[0050] 根据这样的结构,在电流向半导体基板12的体二极管流动时,范围A1的电流密度比范围A2的电流密度低。其结果是,范围A1的每单位面积的发热量相对于范围A2受到抑制。半导体基板12的包含中心的范围A1与位于其周围的范围A2相比,在散热性方面差。即,本实施例的半导体装置10在散热性差的范围A1中,能抑制半导体基板12的发热量。由此,半导体基板12的温度分布得以改善,温度传感器28的检测温度的可靠性提高。即,通过改善半导体基板12的温度分布,无论配置温度传感器28的位置如何,都能够正确地检测半导体基板12的温度。

[0051] 使相对于相同电流密度的体二极管的正向电压在两个范围A1、A2中不同的手段没有限定为特定的手段。例如图3所示,两个范围A1、A2分别具有体区36与上表面电极14彼此相接的多个体接触部位C。在这样的结构中,可考虑使散热性差的范围A1中的体接触部位C的间隔CP1比其他的范围A2中的体接触部位C的间隔CP2宽。由此,体区36与上表面电极14相接的面积的比例(即,体接触部位C所占的面积的比例)在范围A1中比在范围A2中小。其结果是,相对于相同电流密度的体二极管的正向电压在范围A1中比在范围A2中高,因此能够改善半导体基板12的温度分布。在此,关于MOSFET的动作涉及的结构未受到影响(参照图2),因此半导体装置10的作为MOSFET的特性维持原样。

[0052] 或者,可以如图4所示,使散热性差的范围A1中的体接触部位C的一个的面积CA1比其他的范围A2中的体接触部位C的一个的面积CA2窄。通过这样的结构,体区36与上表面电极14相接的面积的比例(即,体接触部位C所占的面积的比例)在范围A1中也比在范围A2中小。其结果是,相对于相同电流密度的体二极管的正向电压在范围A1中比在范围A2中高,因此能够改善半导体基板12的温度分布。

[0053] 或者,可以如图5所示,使散热性差的范围A1中的体接触部位C的下方的体区36的p型杂质的浓度比其他的范围A2中的体接触部位C的下方的体区36的p型杂质的浓度低。通过这样的结构,也不用使作为MOSFET的特性变化,而能够使相对于相同电流密度的体二极管

的正向电压在范围A1中比在范围A2中高。在此基础上或取代于此,同样如图5所示,可以使散热性差的范围A1中的体接触部位C的下方的结晶缺陷12d的密度比其他的范围A2中的体接触部位C的下方的结晶缺陷(图示省略)的密度大。通过这样的结构,也不用使作为MOSFET的特性变化而能够使相对于相同电流密度的体二极管的正向电压在范围A1中比在范围A2中高。虽然为一例,但是在两个范围A1、A2之间为了实现结晶缺陷12d的密度的差别化,能够在散热性差的范围A1的漂移区34有意地设置结晶缺陷12d。

[0054] 图3-图5所示的若干的结构例分别可以单独采用,并且也可以将它们中的两个以上任意组合地采用。

[0055] (实施例2)

[0056] 接下来,参照图6-8,说明实施例2的半导体装置100。关于与实施例1共通或对应的结构,标注同一标号,在此省略重复的说明。如图6-8所示,在俯视观察时,半导体基板12具有由保护膜24覆盖的范围A3和未由保护膜24覆盖的范围A4。在两个范围A3、A4分别设置内置有实施例1中说明的体二极管的MOSFET结构。

[0057] 在本实施例的半导体装置100中,在由保护膜24覆盖的范围A3与未由保护膜24覆盖的范围A4之间,MOSFET结构互不相同。在这一点上,本实施例的半导体装置100与实施例1中说明的半导体装置10、10a、10b不同。需要说明的是,如图7所示,关于MOSFET结构中的MOSFET的动作涉及的结构,在两个范围A3、A4之间彼此一样。相对于此,如图8所示,关于体二极管涉及的结构,在两个范围A3、A4之间互不相同。这是因为,相对于相同电流密度的体二极管的正向电压在范围A3中比在范围A4中高的缘故。

[0058] 根据这样的结构,在电流向半导体基板12的体二极管流动时,范围A3中的电流密度也比范围A4中的电流密度小。其结果是,范围A3的每单位面积的发热量相对于范围A4受到抑制。由保护膜24覆盖的范围A3与未由保护膜24覆盖的范围A4相比,在散热性方面差。即,本实施例的半导体装置100在散热性差的范围A3中,能抑制半导体基板12的发热量。由此,半导体基板12的温度分布得以改善,温度传感器28的检测温度的可靠性提高。即,通过改善半导体基板12的温度分布,无论配置温度传感器28的位置如何,都能够正确地检测半导体基板12的温度。

[0059] 与实施例1同样,使相对于相同电流密度的体二极管的正向电压在两个范围A3、A4中不同的手段没有限定为特定的手段。例如图8所示,两个范围A3、A4分别具有体区36与上表面电极14彼此相接的多个体接触部位C。在这样的结构中,可考虑使散热性差的范围A3中的体接触部位C的一个的面积CA3比其他的范围A4中的体接触部位C的一个的面积CA4窄。由此,体区36与上表面电极14相接的面积的比例(即,体接触部位C所占的面积的比例)在范围A3中也比在范围A4中小。其结果是,相对于相同电流密度的体二极管的正向电压在范围A3中也比在范围A4中高,因此能够改善半导体基板12的温度分布。在此,关于MOSFET的动作涉及的结构未受到影响(参照图7),因此半导体装置10的作为MOSFET的特性维持原样。

[0060] 或者,可以如实施例1中也说明过的那样,使散热性差的范围A3中的体接触部位C的间隔比其他的范围A2中的体接触部位C的间隔窄(参照图3)。或者,可以使散热性差的范围A3中的体接触部位C的下方的体区36的p型杂质的浓度比其他的范围A4中的上述浓度低。或者,可以使散热性差的范围A3中的体接触部位C的下方的结晶缺陷12d的密度比其他的范围A4中的上述密度大。这些结构例可以分别单独采用,并且也可以将它们中的两个以上任

意组合采用。

[0061] (实施例3)

[0062] 接下来,参照图9、10,说明实施例3的半导体装置110。关于与实施例1、2共通或对应的结构,标注同一标号,在此省略重复的说明。如图9、10所示,本实施例的半导体装置110具有平面栅极结构,在这一点上,与具有沟槽栅极结构的实施例1、2的半导体装置10、10a、10b、100不同。即,在半导体装置110中,沿着半导体基板12的上表面12a设置栅电极18及栅极绝缘膜20,栅电极18隔着栅极绝缘膜20而与半导体基板12的上表面12a相对。

[0063] 如图10所示,在半导体基板12上设置具有漏极区32、漂移区34、体区36及源极区38的MOSFET结构。与实施例1、2中说明的结构相比,体区36(包含体接触区36a)及源极区38的结构被变更。由此,栅电极18隔着栅极绝缘膜20而与源极区38、体区36及漂移区34相对。而且,源极区38及体区36与上表面电极14进行欧姆接触。如果是本领域技术人员则可知,本实施例的MOSFET结构与实施例1、2中说明的MOSFET结构同样内置有能作为续流二极管利用的体二极管。

[0064] 在本实施例的半导体装置110中,与实施例2同样,在由保护膜24覆盖的范围A3与未由保护膜24覆盖的范围A4之间,MOSFET结构互不相同。具体而言,散热性差的范围A3中的体接触部位C的下方的结晶缺陷12d的密度比其他的范围A4中的上述密度大。由此,相对于相同电流密度的体二极管的正向电压在范围A3中比在范围A4中高,在电流向半导体基板12的体二极管流动时,范围A3中的电流密度比在范围A4中的电流密度低。与实施例2同样,在散热性差的范围A3中能抑制半导体基板12的发热量,因此能改善半导体基板12的温度分布。

[0065] 从实施例2、3可知,本说明书公开的技术在沟槽栅极型的MOSFET结构和平面栅极型的MOSFET结构中都可以采用。而且,本说明书公开的技术没有限定为特定的MOSFET结构,可以采用于各种MOSFET结构。这种情况下,MOSFET结构可以具有与上表面电极14相接的n型的源极区38、与下表面电极16相接的n型的漏极区32、介于源极区38与漏极区32之间并与上表面电极14相接的p型的体区36、介于体区36与漏极区32之间的n型的漂移区34。需要说明的是,漏极区32和漂移区34都为n型的半导体区,因此两者之间不需要明确的边界。

[0066] (实施例4)

[0067] 接下来,参照图11-13,说明实施例4的半导体装置120。关于与实施例1-3共通或对应的结构,标注同一标号,在此省略重复的说明。本实施例的半导体装置120与实施例1、2同样具有沟槽栅极结构。半导体装置120通常与例如引线这样的导电性构件122一起向半导体封装体装入。此时,导电性构件122经由例如焊料层124而接合于半导体装置120的上表面电极14的至少一部分。因此,上表面电极14为了提高与焊料层124的亲和性或结合性,可以具有例如基于镍或金的镀敷层14a。

[0068] 在上表面电极14接合有导电性构件122的状态下,在俯视观察下,半导体基板12具有由导电性构件122覆盖的范围A5和未由导电性构件122覆盖的范围A3、A4。半导体基板12的热量通过导电性构件122而能向外部散热。因此,未由导电性构件122覆盖的范围A3、A4与由导电性构件122覆盖的范围A5相比,散热性差,容易成为高温。由此,在本实施例的半导体装置120中,在未由导电性构件122覆盖的范围A3、A4与由导电性构件122覆盖的范围A5之间,MOSFET结构互不相同。此外,在本实施例的半导体装置120中,在由保护膜24覆盖的范围

A3与未由保护膜24覆盖的范围A4之间,MOSFET结构也互不相同。即,在散热性不同的三个范围A1-A3之间,MOSFET结构互不相同。

[0069] 如图13所示,两个范围A3-A5分别具有体区36与上表面电极14彼此相接的多个体接触部位C。将三个范围A3-A5进行比较时,由保护膜24覆盖的范围A3在散热性上最差,由导电性构件122覆盖的范围A5在散热性上最优异。因此,范围A3-A5中的体接触部位C的各面积CA3-CA5满足 $CA3 < CA4 < CA5$ 的关系。由此,相对于相同电流密度的体二极管的正向电压在范围A3中变得最高,在范围A5中变得最低。因此,在电流向半导体基板12的体二极管流动时,电流密度在范围A3中变得最小,在范围A5中变得最大。各范围A3-A5的发热量根据其散热性来调整,因此能改善半导体基板12的温度分布。

[0070] 在其他的实施方式中,可以关于四个以上的范围,以相对于同一电流密度的体二极管的正向电压不同的方式使MOSFET结构互不相同。这种情况下,与实施例1-3同样,在各范围内使体二极管的正向电压不同的手段没有限定为特定的手段,可以采用本说明书记载的一个或多个结构例。

[0071] 在本说明书公开的半导体装置10、10a、10b、100、110、120中,能改善以内置于MOSFET结构的体二极管的发热为起因的温度分布。因此,在将上述的半导体装置10、10a、10b、100、110、120采用于转换器或变换器时,能够利用体二极管作为续流二极管。在此,半导体装置10、10a、10b、100、110、120在实施同步整流控制的转换器或变换器中也能够良好采用。同步整流控制是对应于电流向体二极管流动的期间而驱动栅电极18(即,将MOSFET接通),限制向体二极管流动的电流的控制。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13