(12) 发明专利

(10) 授权公告号 CN 110784666 B

(45) 授权公告日 2022.04.12

(21) 申请号 201911202048.X

(74) 专利代理机构 北京市金杜律师事务所

(22) 申请日 2013.03.28

11256

(65) 同一申请的已公布的文献号

代理人 李文屹

申请公布号 CN 110784666 A

(51) Int.CI.

(43) 申请公布日 2020.02.11

H04N 5/353 (2011.01)

(30) 优先权数据

H04N 5/355 (2011.01)

2012-082158 2012.03.30 JP

H04N 5/369 (2011.01)

2012-104830 2012.05.01 JP

H04N 5/3745 (2011.01)

(62) 分案原申请数据

H04N 5/378 (2011.01)

201380016350.0 2013.03.28

H04N 9/04 (2006.01)

(73) 专利权人 株式会社尼康

H01L 27/146 (2006.01)

地址 日本东京都

(56) 对比文件

US 2010/0214453 A1, 2010.08.26

(72) 发明人 纲井史郎 村田宽信

CN 102007761 A, 2011.04.06

US 2010/0193923 A1, 2010.08.05

审查员 薛梦姣

权利要求书4页 说明书13页 附图15页

(54) 发明名称

拍摄元件以及拍摄装置

(57) 摘要

一种拍摄元件，具有：拍摄部，其形成多个像素组，像素组中的多个像素是输出与入射光对应的像素信号的多个像素，并入射与相互不同图像信息对应的入射光；控制部，其按每个所述像素组对包含在所述像素组中的所述多个像素的电荷的积蓄时间进行控制；读取部，其按每个所述像素组设置，从包含在所述像素组中的所述多个像素读取所述像素信号。

1. 一种拍摄元件, 具有:

多个像素, 具有将光转换为电荷的光电转换部;

第一控制线, 其与所述多个像素中的多个第一像素连接, 输出用于控制所述第一像素的第一控制信号, 所述第一像素具有将来自具有第一分光特性的第一滤光片的光转换为电荷的第一光电转换部; 以及

与所述第一控制线不同的第二控制线, 其与所述多个像素中的多个第二像素连接, 输出用于控制所述第二像素的第二控制信号, 所述第二像素具有将来自第二滤光片的光转换为电荷的第二光电转换部, 所述第二滤光片的分光特性与所述第一分光特性不同,

所述多个第一像素在行方向及列方向上分别配置,

所述多个第二像素在所述行方向及所述列方向上分别配置。

2. 根据权利要求1所述的拍摄元件, 其中,

所述第一像素具有连接于所述第一控制线的第一电路部,

所述第二像素具有连接于所述第二控制线的第二电路部。

3. 根据权利要求2所述的拍摄元件, 其中,

所述第一电路部具有用于通过所述第一控制信号而从所述第一光电转换部传输电荷的第一传输部,

所述第二电路部具有用于通过所述第二控制信号而从所述第二光电转换部传输电荷的第二传输部。

4. 根据权利要求3所述的拍摄元件, 其中,

在与所述第一控制信号被所述第一控制线输出的定时不同的定时, 所述第二控制信号被所述第二控制线输出。

5. 根据权利要求3所述的拍摄元件, 其中,

具有对从所述第一像素输出的第一信号和从所述第二像素输出的第二信号进行信号处理的信号处理部。

6. 根据权利要求5所述的拍摄元件, 其中,

所述信号处理部具有将所述第一信号和所述第二信号放大的放大部。

7. 根据权利要求5所述的拍摄元件, 其中,

所述信号处理部具有为了将所述第一信号和所述第二信号转换为数字信号而使用的转换部。

8. 根据权利要求7所述的拍摄元件, 其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述转换部配置于不同于所述第一半导体芯片的第二半导体芯片。

9. 根据权利要求8所述的拍摄元件, 其中,

所述第一半导体芯片层叠于所述第二半导体芯片。

10. 根据权利要求7所述的拍摄元件, 其中,

所述拍摄元件具备存储部, 所述存储部存储使用所述转换部转换为数字信号的所述第一信号、和使用所述转换部转换为数字信号的所述第二信号。

11. 根据权利要求10所述的拍摄元件, 其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述转换部配置于不同于所述第一半导体芯片的第二半导体芯片，

所述存储部配置于不同于所述第一半导体芯片及所述第二半导体芯片的第三半导体芯片。

12. 根据权利要求11所述的拍摄元件, 其中,

所述第一半导体芯片层叠于所述第三半导体芯片。

13. 根据权利要求5所述的拍摄元件, 其中,

所述信号处理部具有对所述第一信号进行信号处理的第一信号处理电路、和对所述第二信号进行信号处理的第二信号处理电路。

14. 根据权利要求13所述的拍摄元件, 其中,

所述第一信号处理电路具有将所述第一信号放大的第一放大电路,

所述第二信号处理电路具有将所述第二信号放大的第二放大电路。

15. 根据权利要求13所述的拍摄元件, 其中,

所述第一信号处理电路具有为了将所述第一信号转换为数字信号而使用的第一转换电路,

所述第二信号处理电路具有为了将所述第二信号转换为数字信号而使用的第二转换电路。

16. 根据权利要求15所述的拍摄元件, 其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述第一转换电路和所述第二转换电路配置于不同于所述第一半导体芯片的第二半导体芯片。

17. 根据权利要求16所述的拍摄元件, 其中,

所述第一半导体芯片层叠于所述第二半导体芯片。

18. 根据权利要求15所述的拍摄元件, 其中,

所述拍摄元件具备: 存储使用所述第一转换电路转换为数字信号的所述第一信号的第一存储电路、和存储使用所述第二转换电路转换为数字信号的所述第二信号的第二存储电路。

19. 根据权利要求18所述的拍摄元件, 其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述第一转换电路和所述第二转换电路配置于不同于所述第一半导体芯片的第二半导体芯片,

所述第一存储电路和所述第二存储电路配置于不同于所述第一半导体芯片及所述第二半导体芯片的第三半导体芯片。

20. 根据权利要求19所述的拍摄元件, 其中,

所述第一半导体芯片层叠于所述第三半导体芯片。

21. 根据权利要求2所述的拍摄元件, 其中,

所述第一电路部具有第一复位部, 其用于通过所述第一控制信号而将被传输来自所述第一光电转换部的电荷的第一浮动扩散区的电位复位,

所述第二电路部具有第二复位部, 其用于通过所述第二控制信号而将被传输来自所述第二光电转换部的电荷的第二浮动扩散区的电位复位。

22. 根据权利要求21所述的拍摄元件,其中,

在与所述第一控制信号被所述第一控制线输出的定时不同的定时,所述第二控制信号被所述第二控制线输出。

23. 根据权利要求21所述的拍摄元件,其中,

具有对从所述第一像素输出的第一信号和从所述第二像素输出的第二信号进行信号处理的信号处理部。

24. 根据权利要求23所述的拍摄元件,其中,

所述信号处理部具有将所述第一信号和所述第二信号放大的放大部。

25. 根据权利要求23所述的拍摄元件,其中,

所述信号处理部具有为了将所述第一信号和所述第二信号转换为数字信号而使用的转换部。

26. 根据权利要求25所述的拍摄元件,其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述转换部配置于不同于所述第一半导体芯片的第二半导体芯片。

27. 根据权利要求26所述的拍摄元件,其中,

所述第一半导体芯片层叠于所述第二半导体芯片。

28. 根据权利要求25所述的拍摄元件,其中,

所述拍摄元件具备存储部,所述存储部存储使用所述转换部转换为数字信号的所述第一信号、和使用所述转换部转换为数字信号的所述第二信号。

29. 根据权利要求28所述的拍摄元件,其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述转换部配置于不同于所述第一半导体芯片的第二半导体芯片,

所述存储部配置于不同于所述第一半导体芯片及所述第二半导体芯片的第三半导体芯片。

30. 根据权利要求29所述的拍摄元件,其中,

所述第一半导体芯片层叠于所述第三半导体芯片。

31. 根据权利要求23所述的拍摄元件,其中,

所述信号处理部具有对所述第一信号进行信号处理的第一信号处理电路、和对所述第二信号进行信号处理的第二信号处理电路。

32. 根据权利要求31所述的拍摄元件,其中,

所述第一信号处理电路具有将所述第一信号放大的第一放大电路,

所述第二信号处理电路具有将所述第二信号放大的第二放大电路。

33. 根据权利要求31所述的拍摄元件,其中,

所述第一信号处理电路具有为了将所述第一信号转换为数字信号而使用的第一转换电路,

所述第二信号处理电路具有为了将所述第二信号转换为数字信号而使用的第二转换电路。

34. 根据权利要求33所述的拍摄元件,其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述第一转换电路和所述第二转换电路配置于不同于所述第一半导体芯片的第二半导体芯片。

35. 根据权利要求34所述的拍摄元件,其中,

所述第一半导体芯片层叠于所述第二半导体芯片。

36. 根据权利要求33所述的拍摄元件,其中,

所述拍摄元件具备:存储使用所述第一转换电路转换为数字信号的所述第一信号的第一存储电路、和存储使用所述第二转换电路转换为数字信号的所述第二信号的第二存储电路。

37. 根据权利要求36所述的拍摄元件,其中,

所述第一光电转换部和所述第二光电转换部配置于第一半导体芯片,

所述第一转换电路和所述第二转换电路配置于不同于所述第一半导体芯片的第二半导体芯片,

所述第一存储电路和所述第二存储电路配置于不同于所述第一半导体芯片及所述第二半导体芯片的第三半导体芯片。

38. 根据权利要求37所述的拍摄元件,其中,

所述第一半导体芯片层叠于所述第三半导体芯片。

39. 一种电子设备,其具备权利要求1至38中任一项所述的拍摄元件。

## 拍摄元件以及拍摄装置

[0001] 本申请是国际申请号为PCT/JP2013/002119,国家申请号为201380016350.0、申请日为2013年3月28日、发明名称为“拍摄元件以及拍摄装置”的发明专利申请的分案申请。

### 技术领域

[0002] 本发明关于拍摄元件以及拍摄装置。

### 背景技术

[0003] 已知有如下的拍摄单元:按每个集合了多个像素而成的单元(cell)单位经由微型凸块将背面照射型拍摄芯片与信号处理芯片连接。

[0004] 现有技术文献

[0005] 专利文献

[0006] 专利文献1:日本特开2006-49361号公报

### 发明内容

[0007] 在上述拍摄单元中,按每个单元进行电荷的积蓄时间的控制以及像素信号的读取的控制。然而,由于上述单元是将在二维上接近的像素的集合作为单元,所以不能细致地控制在单元内或者单元间的电荷的积蓄时间以及像素信号的读取。

[0008] 用于解决课题的手段

[0009] 在本发明的第1方案中,具有:拍摄部,其形成多个像素组,所述像素组的多个像素是输出与入射光相应的像素信号的多个像素,并入射与互不相同的图像信息对应的入射光;控制部,其按每个所述像素组对向包含在所述像素组中的所述多个像素积蓄电荷的积蓄时间进行控制;读取部,其按每个所述像素组设置,从包含在所述像素组中的所述多个像素读取所述像素信号。

[0010] 本发明的第2方案中,提供使用上述拍摄元件的拍摄装置。

[0011] 另外,上述的发明的概要未列举本发明的全部必要特征。此外,这些特征群的子组合也能够构成发明。

### 附图说明

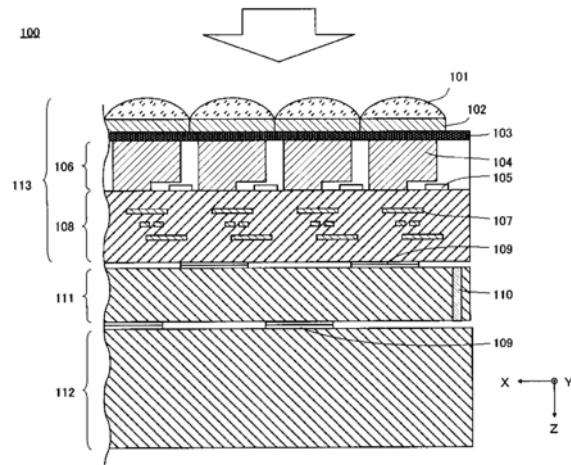

[0012] 图1是本实施方式的背面照射型的MOS型拍摄元件的剖视图。

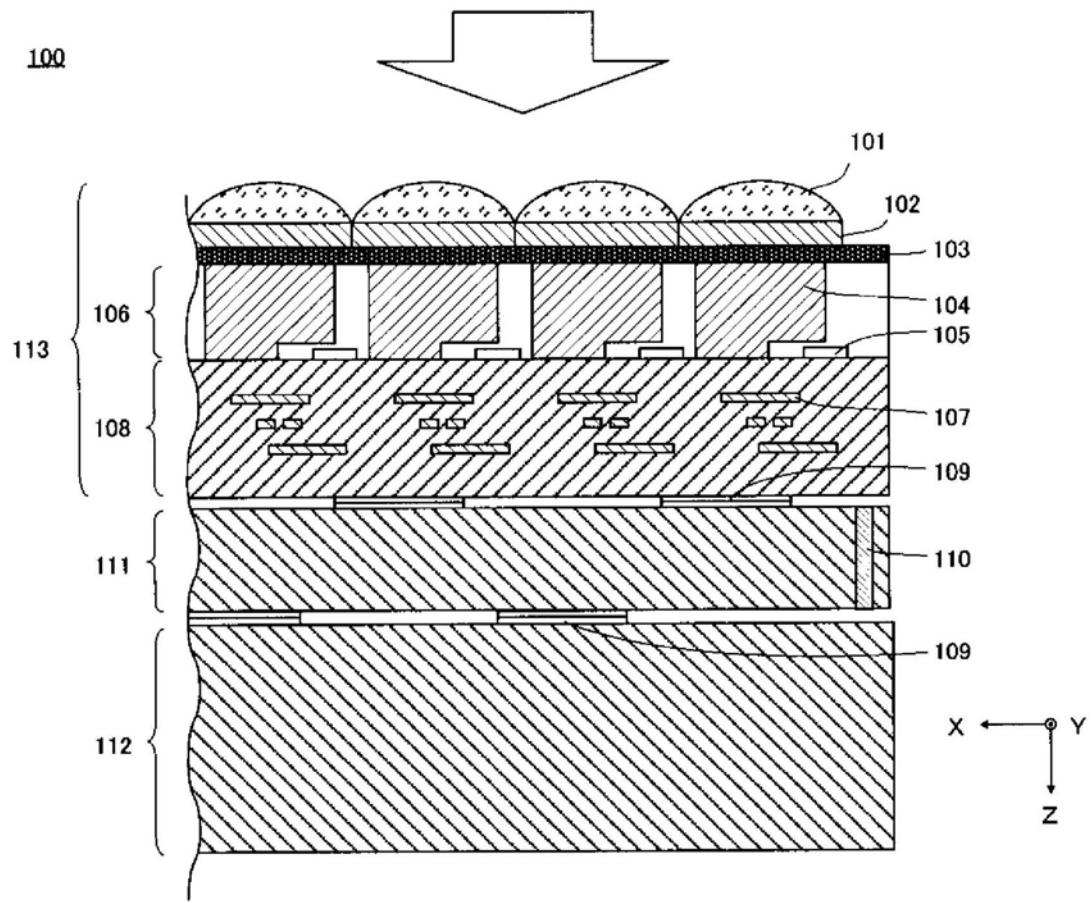

[0013] 图2是说明拍摄芯片的像素排列与单位区块的图。

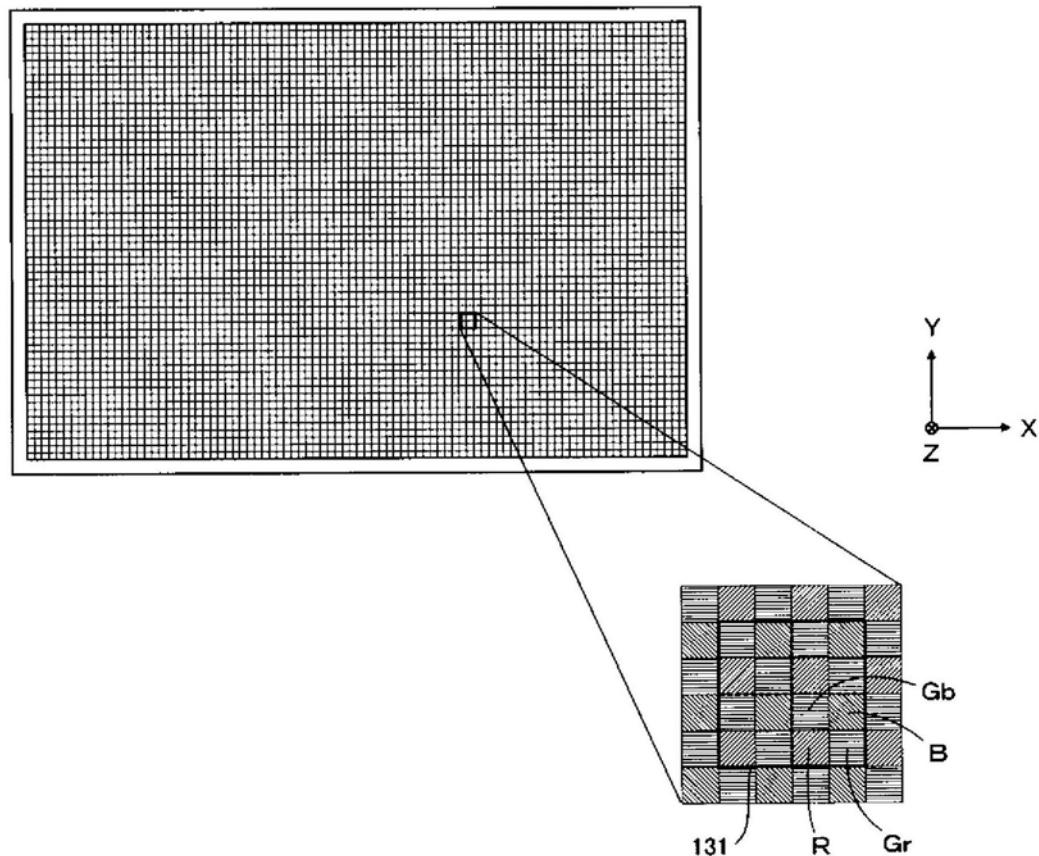

[0014] 图3是表示像素的等价电路图。

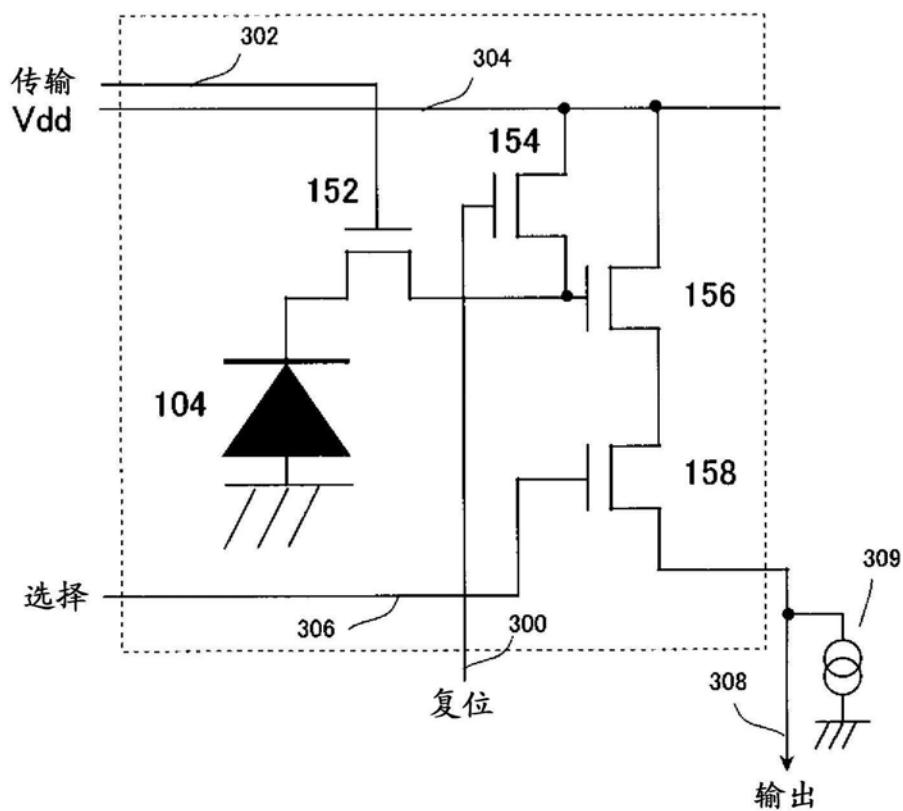

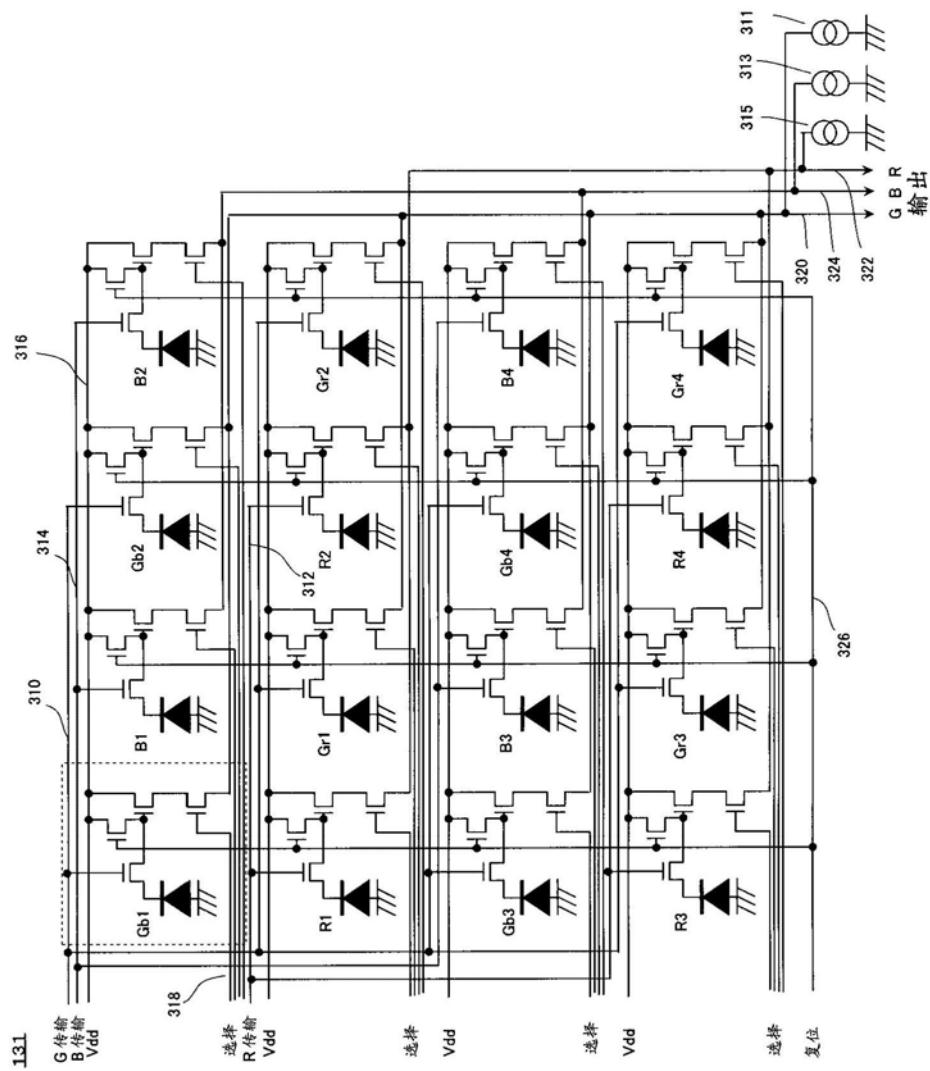

[0015] 图4是表示在单位区块中像素的连接关系的电路图。

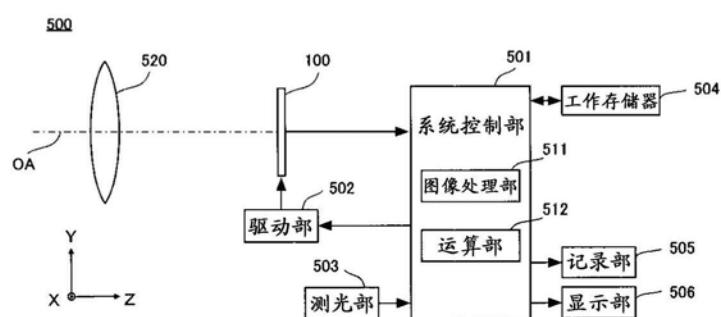

[0016] 图5是表示本实施方式的拍摄装置的构成的框图。

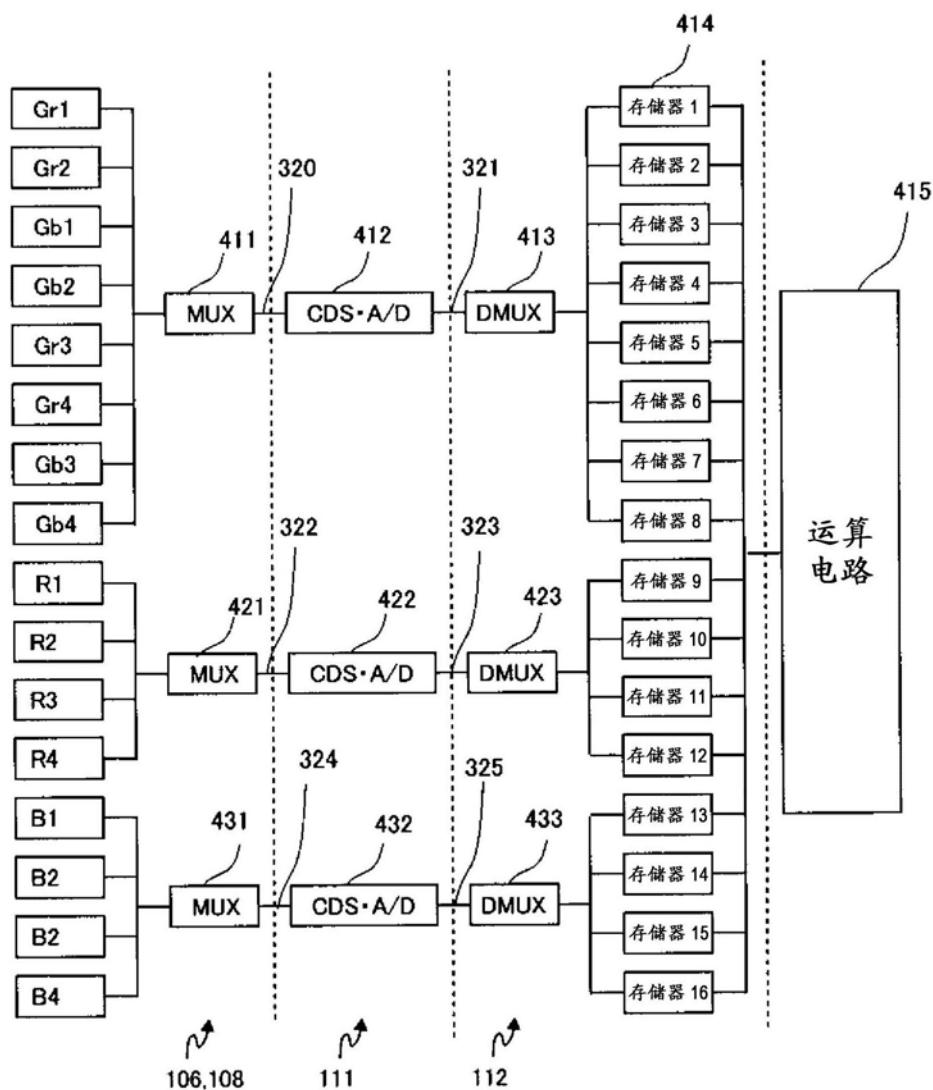

[0017] 图6是表示拍摄元件的功能的构成的框图。

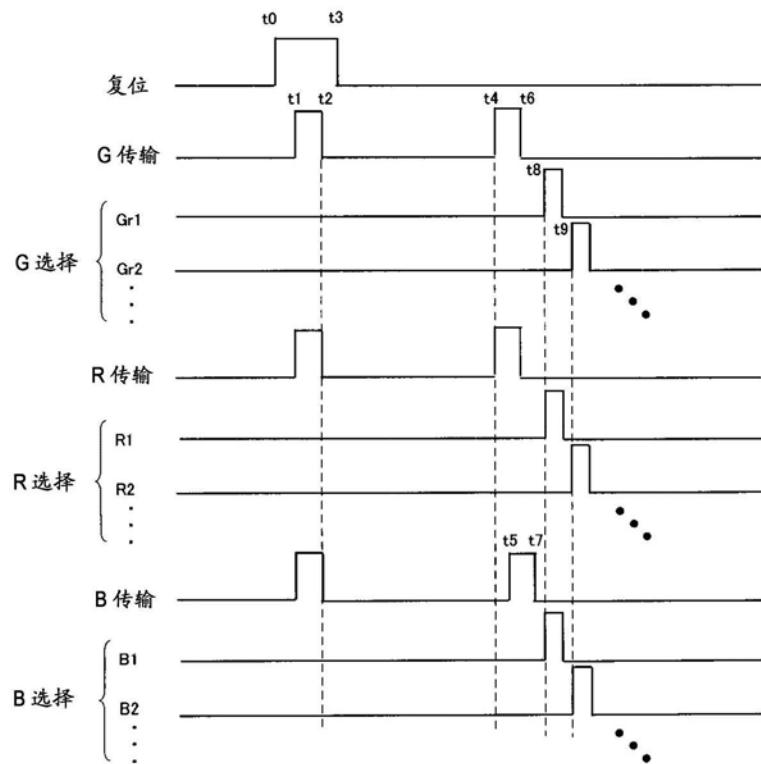

[0018] 图7是表示各像素组的动作的时序图。

[0019] 图8示出了其他单位区块的例子以及各像素的连接关系。

- [0020] 图9是背面照射型的其他的拍摄元件的剖视图。

- [0021] 图10示出了与图9的拍摄元件对应的单位区块的例子以及各像素的连接关系。

- [0022] 图11示出了其他像素的等价电路。

- [0023] 图12示意性地示出了其他拍摄元件的单位区块。

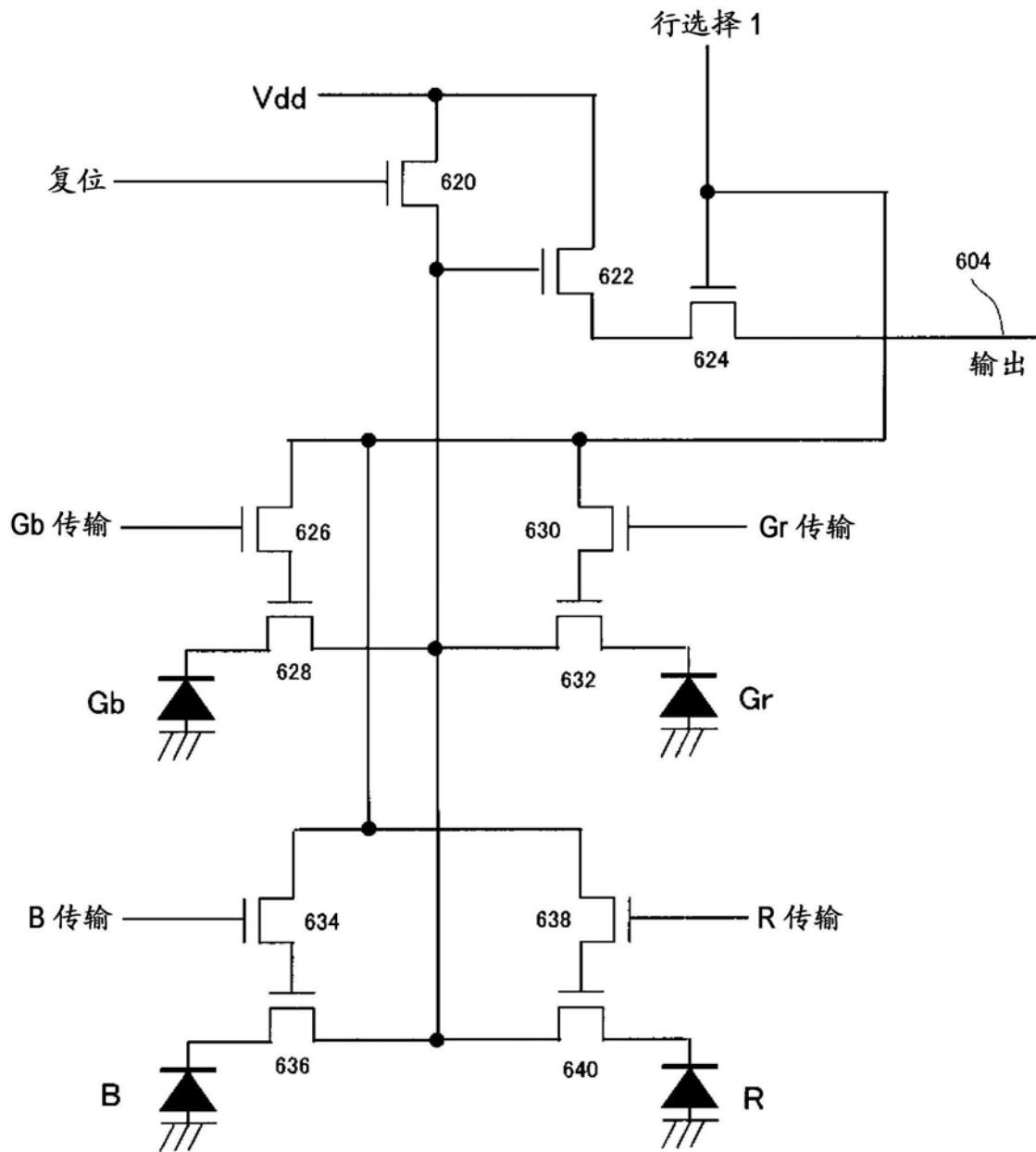

- [0024] 图13是表示单位区块内的像素单元的电路图。

- [0025] 图14进一步示意性地示出了其他拍摄元件的单位区块。

- [0026] 图15是表示单位区块内的像素单元的电路图。

- [0027] 图16示意性地示出了其他拍摄元件的单位区块。

- [0028] 图17是表示单位区块内的像素单元的电路图。

## 具体实施方式

[0029] 以下,通过发明的实施方式说明本发明,但以下的实施方式不限定关于权利要求的范围的发明。此外,在实施方式中说明的特征的全部的组合未必是发明的解决手段中必须的。

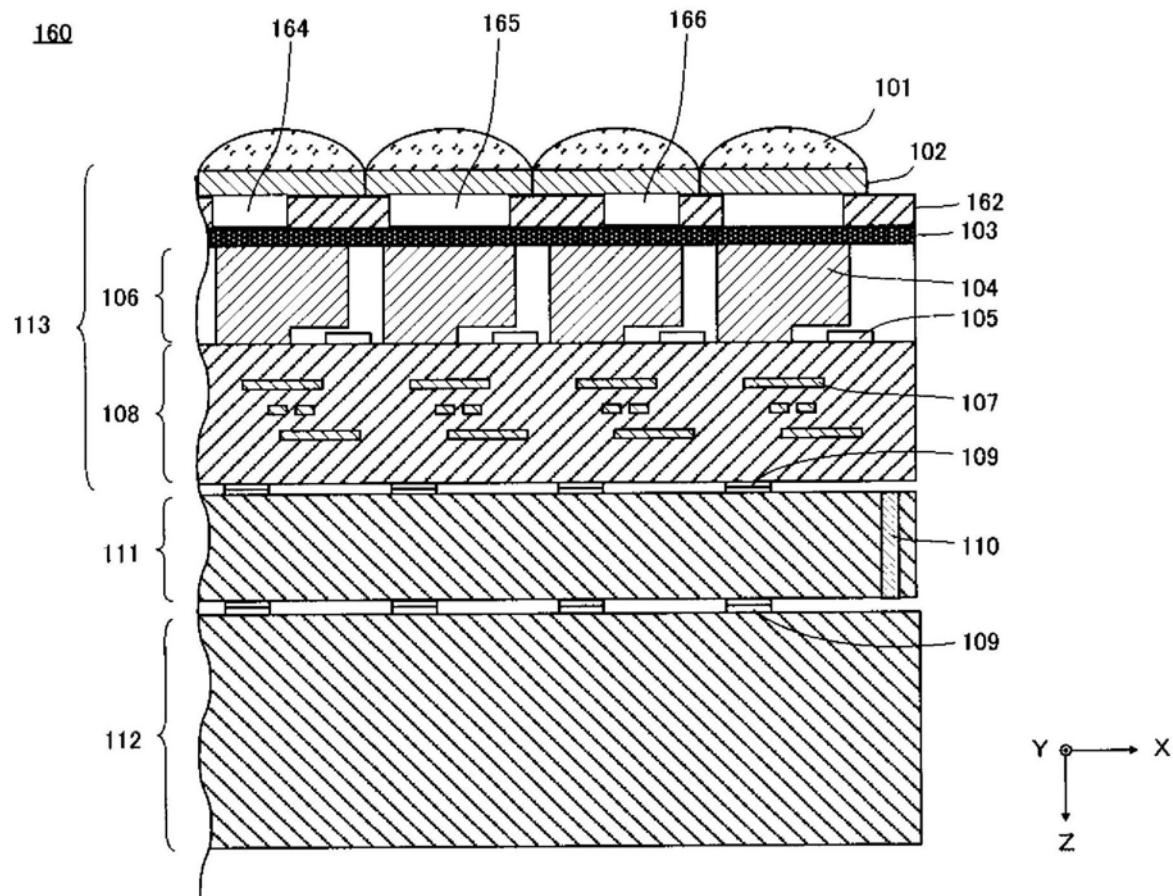

[0030] 图1是本实施方式涉及的背面照射型的拍摄元件100的剖视图。拍摄元件100具有输出与入射光对应的像素信号的拍摄芯片113、处理像素信号的信号处理芯片111、存储像素信号的存储器芯片112。层叠这些拍摄芯片113、信号处理芯片111以及存储器芯片112,通过铜(Cu)等具有导电性的凸块109将它们相互电连接。

[0031] 另外,如图示出那样,入射光主要向用空心箭头表示的Z轴正方向入射。在本实施方式中,在拍摄芯片113中,将入射光入射一侧的面称为背面。此外,如坐标轴所示那样,将与Z轴正交的纸面右方向作为X轴正方向,将与Z轴以及X轴正交的向纸面近前的方向作为Y轴正方向。在以下的几个图中,将图1的坐标轴作为基准,以能够明确各个图的方向的方式表示坐标轴。

[0032] 拍摄芯片113的一个例子是背面照射型的MOS图像传感器。PD层配置在布线层108的背面侧。PD层106具有二维地配置的多个PD(光电二极管)104,以及与PD104对应设置的晶体管105。

[0033] 在PD层106中入射光的入射侧上隔着钝化膜103设置了彩色滤光片102。彩色滤光片102具有透射互不相同的波长区域的多个种类,与PD104分别对应地具有特定的排列。关于彩色滤光片102的排列将后述。彩色滤光片102、PD104以及晶体管105的组形成一个像素。

[0034] 在彩色滤光片102中的入射光的入射侧上与各自的像素对应地设置微型透镜101。微型透镜101使入射光向对应的PD104聚光。

[0035] 布线层108具有将来自PD层106的像素信号向信号处理芯片111传输的布线107。布线107可以有多层,此外,也可以设置无源元件以及有源元件。

[0036] 在布线层108的表面上配置多个凸块109。使该多个凸块109与设置在信号处理芯片111的相对的面上的多个凸块109对准,通过对拍摄芯片113与信号处理芯片111进行加压等,使对准的凸块109彼此接合并电连接。

[0037] 相同地,在信号处理芯片111以及存储器芯片112的彼此相对的面上配置多个凸块109。使这些凸块109相互对准,通过对信号处理芯片111与存储器芯片112进行加压等,使对准的凸块109彼此接合并电连接。

[0038] 另外,在凸块109间的接合中,并不限定于基于固相扩散的Cu凸块接合,也可以采用基于焊锡熔融的微型凸块结合。此外,凸块109例如相对于后述的一个输出布线设置一个左右即可。因此,凸块109的大小也可以比PD104的间距大。此外,也可以在排列有像素的像素区域以外的周边区域中一并设置比与像素区域对应的凸块109大的凸块。

[0039] 信号处理芯片111具有将分别设置在表背面上的电路相互连接的TSV(硅贯通电极)110。TSV110优选设置在周边区域中。此外,TSV110也可以设置在拍摄芯片113的周边区域、存储器芯片112中。

[0040] 图2是说明拍摄芯片113的像素排列与单位区块131的图。特别是示出了从背面侧观察拍摄芯片113的样子。在像素区域中矩阵状地排列2000万个以上的像素。在本实施方式中,相邻的4像素×4像素的16个像素形成一个组。图的格子线示出了相邻的像素分组而形成单位区块131的概念。

[0041] 如像素区域的局部放大图示出那样,单位区块131上下左右地包含4个由绿色像素Gb、Gr、蓝色像素B以及红色像素R这4个像素构成的拜耳排列。绿色像素Gb、Gr具有作为彩色滤光片102的绿色滤色器,接收入射光中的绿色波段的光。相同地,蓝色像素B具有作为彩色滤光片102的蓝色滤色器,接收蓝色波段的光,红色像素R具有作为彩色滤光片102的红色滤色器,接收红色波段的光。

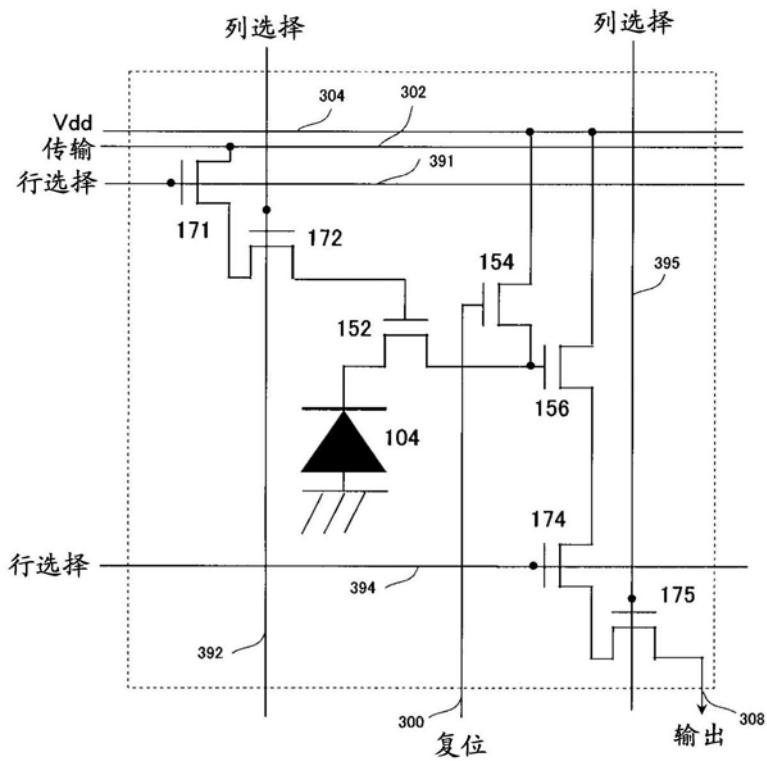

[0042] 图3表示像素150的等价电路图。上述多个像素150分别具有上述PD104、传输晶体管152、复位晶体管154、放大晶体管156以及选择晶体管158。这些晶体管的至少一部分与图1的晶体管105对应。进而,在像素150中,配置有提供复位晶体管154的导通信号的复位布线300、提供传输晶体管152的导通信号的传输布线302、接收来自电源Vdd的电力供给的电源布线304、提供选择晶体管158的导通信号的选择布线306,以及输出像素信号的输出布线308。以下,对将各晶体管作为n沟道型FET的例子进行说明,但晶体管的种类不限于此。

[0043] 传输晶体管152的源极、栅极、漏极分别与PD104的一端、传输布线302、放大晶体管156的栅极连接。此外,复位晶体管154的漏极与电源布线304连接,源极与放大晶体管156的栅极连接。放大晶体管156的漏极与电源布线304连接,源极与选择晶体管158的漏极连接。选择晶体管158的栅极与选择布线306连接,源极与输出布线308连接。负载电流源309向输出布线308提供电流。即,由源极跟随器形成与选择晶体管158对应的输出布线308。另外,负载电流源309可以设置在拍摄芯片113侧,也可以设置在信号处理芯片111侧。

[0044] 图4是表示在单位区块131中上述像素150的连接关系的电路图。另外,虽然出于容易观察附图的目的而省略各晶体管的附图标记,但图4的各像素的各晶体管具有与配置在图3的像素150中对应的位置上的各晶体管相同的构成以及功能。

[0045] 在图4所示的单位区块131内,具有相同颜色的彩色滤光片102的像素150形成像素组。彩色滤光片102如图2所示那样与RGB的三个种类对应,像素Gb1、Gb2、Gb3、Gb4、Gr1、Gr2、Gr3、Gr4这8个像素形成G像素组。相同地,像素R1、R2、R3、R4这4个像素形成R像素组,像素B1、B2、B3、B4这4个像素形成B像素组。即,按每个透射彩色滤光片102的波长区域形成像素组。

[0046] 在此,在包含在各像素组中的多个像素间共通地连接传输晶体管的栅极。由此,在属于像素组的像素中同时地控制传输晶体管的栅极,并且在像素组间独立控制该传输晶体管的栅极。

[0047] 在如图4示出的例子中,包含在G像素组中的像素Gb1、Gb2、Gb3、Gb4、Gr1、Gr2、Gr3、Gr4的传输晶体管的栅极与共通的G传输布线310连接。相同地,R像素组的像素R1、R2、R3、R4的传输晶体管的栅极与共通的R传输布线312连接,B像素组的像素B1、B2、B3、B4的传输晶体管的栅极与共通的B传输布线314连接。

[0048] 此外,在包含在各像素组中的多个像素间共通地连接选择晶体管的源极。G像素组的像素Gb1、Gb2、Gb3、Gb4、Gr1、Gr2、Gr3、Gr4的选择晶体管的源极与共通的G输出布线320连接。相同地,R像素组的像素R1、R2、R3、R4的选择晶体管的源极与共通的R输出布线322连接,B像素组的像素B1、B2、B3、B4的选择晶体管的源极与共通的B输出布线324连接。

[0049] 在G输出布线320中连接负载电流源311。相同地,在R输出布线322中连接负载电流源313,并且在B输出布线324中连接负载电流源315。另外,复位布线326以及电源布线316在单位区块131中共通。此外,选择布线318与各像素一对一地配置16根,与对应的选择晶体管的栅极连接。

[0050] 这样,对一个单位区块131设置多个输出布线。但是,由于拍摄芯片113是背面照射型,所以能够不减少向PD104入射的光量,增加拍摄芯片113的布线107的层数,能够不增加平面方向的大小地拉绕布线。

[0051] 图5是示出了本实施方式涉及的拍摄装置的构成的框图。拍摄装置500包括作为拍摄光学系统的拍摄透镜520,拍摄透镜520将沿着光轴OA入射的被拍摄体光束向拍摄元件100引导。拍摄透镜520也可以是能够相对于拍摄装置500装拆的交换式透镜。拍摄装置500主要具有拍摄元件100、系统控制部501、驱动部502、测光部503、工作存储器504、记录部505、以及显示部506。

[0052] 拍摄透镜520由多个光学透镜组构成,使来自场景的被拍摄体光束在其焦点面附近成像。另外,以在图5中配置在瞳孔附近的虚拟的1枚透镜作为代表表示。驱动部502是按照来自系统控制部501的指令执行拍摄元件100的定时控制、区域控制等的电荷积蓄控制的控制电路。在该意义上驱动部502可以说是承担对拍摄元件100执行电荷积蓄并输出像素信号的拍摄元件控制部的功能。驱动部502与拍摄元件100组合,形成拍摄单元。形成驱动部502的控制电路也可以做成芯片而层叠在拍摄元件100上。

[0053] 拍摄元件100将像素信号引导到系统控制部501的图像处理部511。图像处理部511将工作存储器504作为工作空间实施各种图像处理,生成图像数据。例如,在生成JPEG文件格式的图像数据的情况下,在实施白平衡处理、对比度处理等后执行压缩处理。生成的图像数据记录在记录部505中,并且转换为显示信号,在预先设定的时间期间显示在显示部506中。

[0054] 测光部503在生成图像数据的一系列的拍摄步骤之前检测场景的亮度分布。测光部503包含例如100万个像素左右的AE传感器。系统控制部501的运算部512接受测光部503的输出,计算每个场景区域的亮度。运算部512根据算出的亮度分布决定快门速度、光圈值、ISO灵敏度。另外,可以将在上述AE传感器中使用的像素设置在拍摄元件100内,在这种情况下,也可以不设置与该拍摄元件100相独立的测光部503。

[0055] 图6是表示拍摄元件100的功能构成的框图。模拟信号的多路调制器(multiplexer)411按顺序选择单位区块131的G像素组的8个像素Gb1等,将各个像素信号向G输出布线320等输出。

[0056] 经由多路调制器411输出的像素信号经由G输出布线320,通过进行相关二重取样(CDS)、模/数(A/D)转换的信号处理电路412,进行CDS以及A/D转换。A/D转换的像素信号经由G输出布线321被引导到多路解调器(demultiplexer)413,存储在与各自的像素对应的像素存储器414中。

[0057] 同样地,多路调制器421按顺序选择单位区块131的R像素组的4个像素R1等,向R输出布线322输出各个像素信号。信号处理电路422对向R输出布线322输出的像素信号进行CDS以及A/D转换。A/D转换后的像素信号经由R输出布线323被引导到多路解调器423,存储在与各自的像素对应的像素存储器414中。

[0058] 同样地,多路调制器431按顺序选择单位区块131的B像素组的4个像素B1等,向B输出布线324输出各个像素信号。信号处理电路432对向B输出布线324输出的像素信号进行CDS以及A/D转换。A/D转换后的像素信号经由B输出布线325被引导到多路解调器433,存储在与各自的像素对应的像素存储器414中。

[0059] 多路调制器411、421、431分别由在拍摄芯片113上的图3的选择晶体管158与选择布线306形成。信号处理电路412、422、432形成于信号处理芯片111。另外,在图6的例子中,与G像素组、R像素组以及B像素组对应设置三个信号处理电路412、422、432。多路解调器413以及像素存储器414形成于存储器芯片112。

[0060] 与单位区块131内的G像素组、R像素组以及B像素组对应地设置G输出布线320、321、R输出布线322、323以及B输出布线324、325。由于拍摄元件100中层叠了拍摄芯片113、信号处理芯片111以及存储器芯片112,所以通过这些布线使用了凸块109进行芯片间的电连接,能够不将各芯片向平面方向增大地拉绕布线。

[0061] 运算电路415对存储在像素存储器414中的像素信号进行处理将其引导到后级的图像处理部。运算电路415可以设置在信号处理芯片111上,也可以设置在存储器芯片112上。另外,在图中示出了1组的连接,实际上这些按每个组存在上述连接,并行地进行工作。但是,运算电路415也可以不按每个组存在,例如,一个运算电路415也可以一边按顺序参照与各个组对应的像素存储器414的值一边按序进行处理。

[0062] 图7示出的是图4的各像素组的动作的时序图。驱动部502在时刻t0经由复位布线326将该单位区块131的各像素Gb1等的复位晶体管导通。由此,释放各像素Gb1等的放大晶体管的栅极的电荷,使栅极的电位复位。进而驱动部502使各像素Gb1等的复位晶体管保持导通状态,从时刻t1至t2经由G传输布线310将属于G像素组的各像素Gb1等的传输晶体管导通。由此,释放积蓄在属于G像素组的各像素Gb1等的PD中的电荷。

[0063] 同样地,驱动部502从时刻t1至t2经由R传输布线312以及B传输布线314,将R像素组的各像素R1等的传输晶体管以及B像素组的各像素B1等的晶体管导通。由此,释放积蓄在R像素组的各像素R1等以及B像素组的各像素B1等的PD中的电荷。之后,驱动部502在时刻t3经由复位布线326将该单位区块131的各像素Gb1等的复位晶体管截止。

[0064] 在从上述时刻t2经过了预定的积蓄时间之后的时刻t4,驱动部502经由G传输布线310将属于G像素组的各像素Gb1等的传输晶体管导通,在其后的时刻t6中将传输晶体管截止。由此,在属于G像素组的各像素Gb1等中在从时刻t2至t4之间积蓄在PD中的电荷经由传输晶体管向放大晶体管的栅极同时传输。因此,驱动部502能够统一控制属于G像素组的各像素Gb1的电荷的积蓄时间。另外该积蓄时间与例如曝光时间相同。

[0065] 在图7示出的例子中,在与G像素组相同的从时刻t4至t6中,驱动部502经由R传输布线312,将R像素组的各像素R1等的传输晶体管导通。由此,在R像素组的各像素R1等中从时刻t2至t4之间积蓄在PD中的电荷经由传输晶体管向放大晶体管的栅极同时传输。

[0066] 此外,在如图7所示的例子中,从时刻t4之后的时刻t5至预定时间之后的时刻t7中,驱动部502经由B传输布线314将B像素组的各像素B1等的传输晶体管导通。由此,在B像素组的各像素B1等中从时刻t2至t5之间积蓄在PD中的电荷经由传输晶体管向放大晶体管的栅极同时传输。

[0067] 由此,驱动部502能够在与G像素组的各像素Gr1等不同的积蓄时间中统一控制B像素组的各像素B1等的电荷的积蓄时间。此外,也能够相对于特定的图像组,在与曝光时间不同的积蓄时间积蓄电荷。关于在哪个像素组中设定怎样的积蓄时间,可以从与在正式拍摄(main photographing)前进行试验拍摄(tentative photographing)时的像素组对应的每个图像信息的输出来判断。例如系统控制部501判断基于一个图像信息的图像比基于其他图像信息的图像暗的情况下,系统控制部501也可以针对与该一个图像信息对应的像素组,通过驱动部502将积蓄时间延长得比与该其他图像信息对应的像素组长。

[0068] 在上述时刻t7之后的时刻t8,驱动部502经由选择布线Gr1将G像素组的像素Gr1的选择晶体管导通。由此,在放大晶体管中生成与通过传输晶体管传输的电荷相应的像素信号,该像素信号经由选择晶体管向G输出布线320输出。在时刻t8之后的时刻t9,通过驱动部502经由选择布线Gr2将G像素组的像素Gr2的选择晶体管导通,相同地,像素Gr2的像素信号经由选择晶体管向G输出布线320输出。这样,通过驱动部502经由G像素组的各像素Gr1等的选择布线Gr1等将选择晶体管依次导通,向一个G输出布线320依次输出G像素组的各像素Gr1等的像素信号。

[0069] 与上述时刻t8、t9等同步,驱动部502经由选择布线R1等依次将R像素组的像素R1等的选择晶体管导通,由此向一个R输出布线322依次输出R像素组的各像素R1等的像素信号。相同地,与上述时刻t8、t9等同步,驱动部502经由选择布线B1等将B像素组的像素B1等的选择晶体管依次导通,由此向一个B输出布线324依次输出B像素组的各像素B1等的像素信号。

[0070] 根据以上,在单位区块131所含的各像素的像素信号从各像素组的输出布线输出。另外,优选在像素组内预先设定输出像素信号的像素的顺序,在驱动部502中作为硬件安装或作为软件存储。

[0071] 以上,根据本实施方式,能够统一控制属于与各图像信息对应的各像素组的各像素的电荷的积蓄时间。因此,能够用与各个图像信息适应的积蓄时间积蓄电荷。例如,在拍摄偏向于RGB的任一个的被拍摄体的情况下,通过使与强色对应的像素组和与弱色对应的像素组中的积蓄时间不同,能够扩大每个颜色的动态范围。此外,能够在像素组间独立地读取各像素的像素信号。

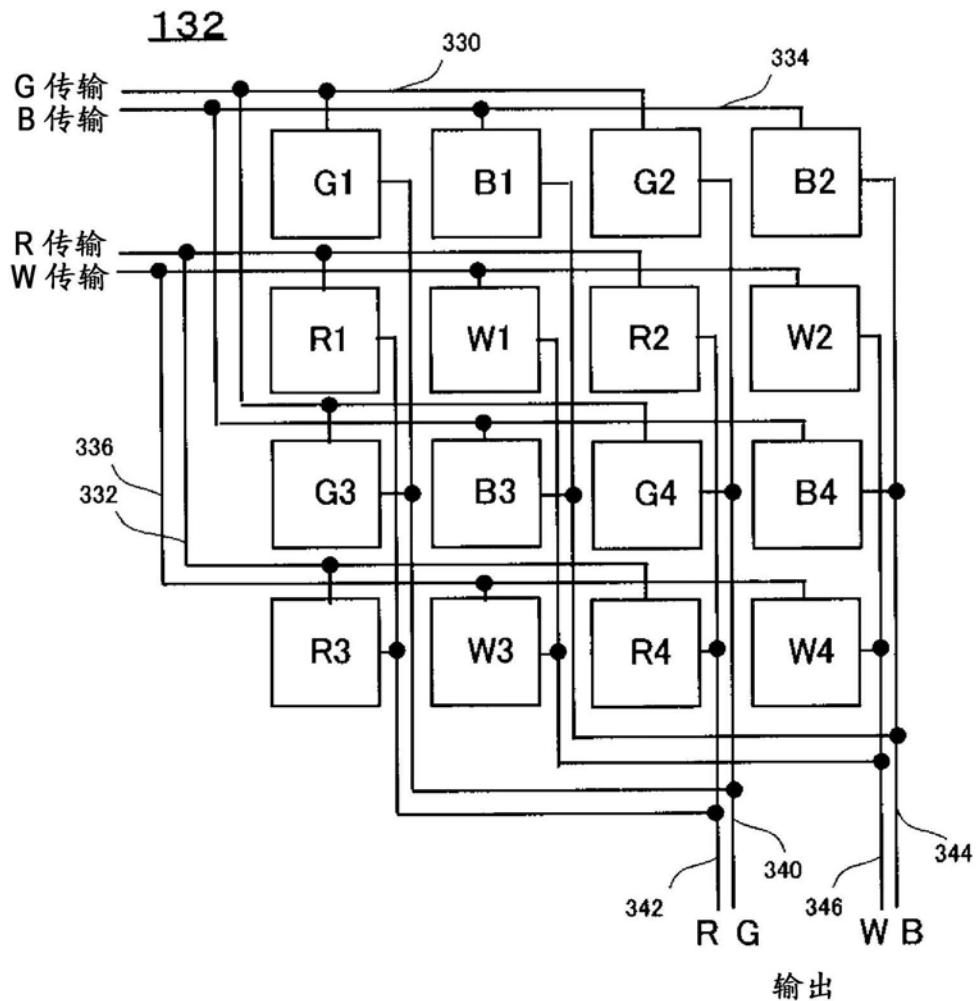

[0072] 图8示出了其他单位区块132的例子以及各像素的连接关系。另外,出于在图8中容易观察图的目的,示出了传输布线以及输出布线,省略各像素的其他构成,用方形表示。

[0073] 在图8示出的例子中,拍摄元件100的像素排列代替图2中的绿色像素Gb,配置白色像素W。在白色像素W中,没有设置对应的彩色滤光片102,此外,设置了透射红色、绿色以及蓝色的无色的滤光器。因此,在绿色像素Gb、蓝色像素B、红色像素R以及白色像素W中,入射

与作为互不相同图像信息的一个例子、即颜色信息对应的入射光。

[0074] 单位区块132分别具有 $4 \times 4$ 的16个像素。另外,与图4的例子相同,包含在每个单位区块132中的像素的数量不限于此。

[0075] 在单位区块132内,具有相同颜色的彩色滤光片102的像素150形成像素组。彩色滤光片102与RGBW四个种类对应,像素G1、G2、G3、G4的4个像素形成G像素组。同样地,像素R1、R2、R3、R4的4个像素形成R像素组,像素B1、B2、B3、B4的4个像素形成B像素组。进而,像素W1、W2、W3、W4的4个像素形成W像素组。即,按每个透射彩色滤光片102的波长区域形成像素组。

[0076] 在此,在包含在各像素组中的多个像素间共通地连接传输晶体管的栅极。由此,驱动部502在像素组内同时地控制传输晶体管的栅极,并且在像素组间独立控制该传输晶体管的栅极。

[0077] 包含在G像素组中的像素G1、G2、G3、G4的传输晶体管的栅极与共通的G传输布线330连接。同样地,R像素组的像素R1、R2、R3、R4的传输晶体管的栅极与共通的R传输布线332连接,B像素组的像素B1、B2、B3、B4的传输晶体管的栅极与共通的B传输布线334连接。进而,W像素组的像素W1、W2、W3、W4的传输晶体管的栅极与共通的W传输布线336连接。

[0078] 此外,在包含在各像素组中的多个像素间共通地连接选择晶体管的输出侧。G像素组的像素G1、G2、G3、G4的选择晶体管的输出侧与共通的G输出布线340连接。同样地,R像素组的像素R1、R2、R3、R4的选择晶体管的输出侧与共通的R输出布线342连接,B像素组的像素B1、B2、B3、B4的选择晶体管的源极与共通的B输出布线344连接。进而,W像素组的像素W1、W2、W3、W4的选择晶体管的输出侧与共通的W输出布线346连接。

[0079] 另外,与图4的例子相同地,复位布线以及电源布线在单位区块132中是共通的。此外,选择布线与各像素一对一地配置16根,与对应的选择晶体管的栅极连接。进而,在输出布线中与图4的例子相同地连接各自的负载电流源。

[0080] 因此,驱动部502能够统一控制属于各像素组的各像素的电荷的积蓄时间。此外,能够相对于特定的图像组,以与其他的像素组不同的积蓄时间积蓄电荷。例如,由于W像素组的彩色滤光片是无色的,所以存在与G像素组等相比光量大的情况。因此,通过将W像素组的各像素的电荷的积蓄时间缩短得比G像素组等各像素的电荷的积蓄时间短,能够得到在W像素组与G像素组等中各自适当的曝光。

[0081] 图9是背面照射型的其他拍摄元件160的剖视图。在拍摄元件160中,关于与图1的拍摄元件100相同的构成赋予相同的附图标记,省略说明。

[0082] 图9的拍摄元件160在钝化膜103与彩色滤光片102之间具有开口掩模162。开口掩模162由例如铝膜形成。

[0083] 开口掩模162与各PD104对应,具有开口164、165、166,该开口部分以外的部分阻断入射光。由此,开口掩模162根据开口位置使成像光学系统中的光束的一部分透射。与配置在如图9所示的例子中图示的4个像素中最靠-X侧的像素对应的开口164相对于PD104向-X侧位移。另一方面,与从4个像素中最靠-X侧起第3个像素对应的开口166相对于PD104向+X侧位移。通过这些步骤,能够在成像光学系统中射出瞳(exit pupil)的向-X及+X位移了的光束入射,获得相位差AF的信息。

[0084] 有时将这些开口相对于PD104位移了的像素称为视差像素。另一方面,开口165不相对于PD104位移。对视差像素配置白色的彩色滤光片102。有时将该像素称为无视差像素。

对无视差像素配置RGB任一个彩色滤光片102。

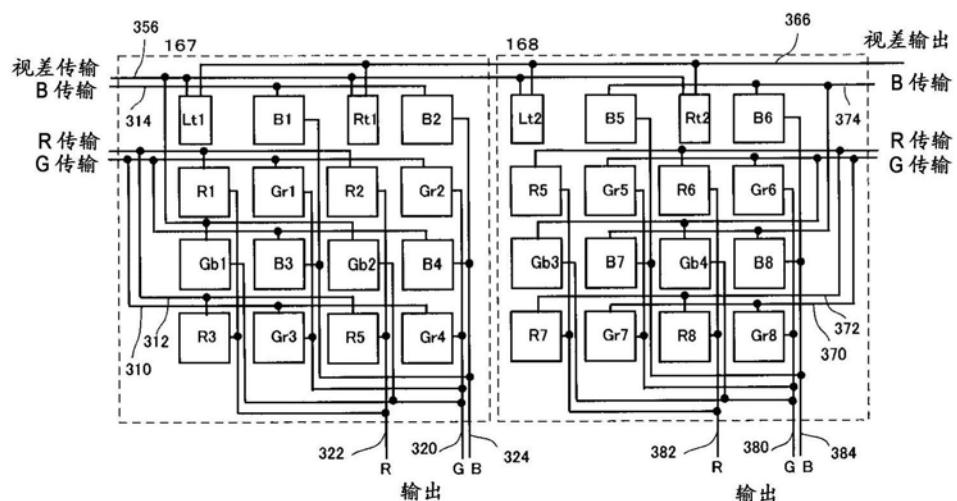

[0085] 图10示出了与拍摄元件160对应的单位区块167、168的例子以及各像素的连接关系。另外,出于在图10中容易观察图的目的,与图8相同地示出了传输布线以及输出布线,省略各像素的其他的构成,用方形表示。

[0086] 在图10所示的例子中,拍摄元件160的像素排列中,关于 $4 \times 4$ 的像素代替在图4中的绿色像素Gr1、Gr2而配置视差像素Lt1、Rt1。视差像素Lt1与在图9中设置了开口164的像素对应,视差像素Rt1与在图9中设置了开口166的像素对应。此外,该 $4 \times 4$ 的16个像素形成单位区块167。

[0087] 在单位区块167内,具有相同颜色的彩色滤光片102的像素150形成像素组。彩色滤光片102与RGB的三个种类对应,与图4同样地形成G像素组、R像素组以及B像素组。关于G像素组、R像素组以及B像素组的构成以及作用与图4相同,所以省略说明。但是,在单位区块167中,与代替在图4中的绿色像素Gr1、Gr2而配置视差像素Lt1、Rt1对应,G像素组以6个像素形成。另外,关于单位区块168,虽然与单位区块167相独立地设置了G传输布线370、R传输布线372、B传输布线374、G输出布线380、R输出布线382、B输出布线384,但其连接关系与单位区块167相同。

[0088] 进而,也按每个开口位置形成像素组。在这种情况下,以跨着多个单位区块167、168的方式形成像素组。在图10的例子中,开口位置位移的视差像素Lt1、Lt2、Rt1、Rt2的4个像素形成视差像素组。

[0089] 包含在视差像素组中的视差像素Lt1、Lt2、Rt1、Rt2的传输晶体管的栅极与共通的视差传输布线356连接。此外,视差像素组的像素Lt1、Lt2、Rt1、Rt2的选择晶体管的输出侧与共通的视差输出布线366连接。

[0090] 由此,驱动部502能够统一控制属于各像素组的各像素的电荷的积蓄时间。此外,能够对特定的图像组,在与其他像素组不同的积蓄时间积蓄电荷。进而,在输出布线中与图4的例子相同地连接各自的负载电流源。

[0091] 例如,在拍摄装置500中半按释放按钮时,驱动视差像素组的各像素Lt1等来获得相位差AF的信息,并且,在该时刻不驱动其他像素组的各像素Gr1等。另一方面,在拍摄装置500中全按释放按钮时,驱动G像素组、R像素组以及B像素组的各像素Gr1等来获得RGB图像的信息,并且,不驱动视差像素组的各像素Lt1等。由此,能够在释放按钮半按的状态下在与相位差AF的信息相适应的积蓄时间中积蓄电荷,并且通过在少量像素中进行图像处理,因此可以在短时间中得到相位差AF的信息。另一方面,能够一边在释放按钮全按的状态下保持高分辨率,一边在与RGB图像的信息相适应的积蓄时间中积蓄电荷。

[0092] 另外,图10中以跨着二个单位区块167、168的方式形成了视差像素组,也可以以跨着单位区块内的视差像素,或者,跨着三个以上的单位区块的方式形成视差像素组。进而,也可以按每个开口位置的位移方向形成视差像素组。即,也可以形成基于开口向-X侧位移了的多个像素Lt1、Lt2等的视差像素组,和基于开口向+X侧位移了的多个像素Rt1、Rt2等的视差像素组。

[0093] 此外,在图4或者图8的排列中,各像素也可以具有位移了的开口。在这种情况下,也可以按每个颜色并且按每个开口位置的位移方向形成像素组。进而,也可以代替图10的视差像素或者不仅如此,还将具有未位移的开口且未设置彩色滤光片102或者具有无色的

彩色滤光片102的像素作为AE像素配置在单位区块167、168内。在这种情况下也通过多个AE像素形成AE像素组，由此驱动部502统一控制属于AE像素组的各像素的电荷的积蓄时间。由此，能够设定与获得作为图像信息的曝光信息相适应的积蓄时间，例如在释放按钮半按时等中与其他的图像组独立地读取像素信息。

[0094] 图11示出了其他的像素170的等价电路。在图11中关于与图3的像素150相同的构成，赋予相同的附图标记，省略说明。另外，与图4的例子相同地，在输出布线308中省略连接了负载电流源的图示。

[0095] 像素170在传输布线302与传输晶体管152的栅极之间设置了行选择晶体管171以及列选择晶体管172。行选择晶体管171的栅极与行选择布线391连接，列选择晶体管172的栅极与列选择布线392连接。在该行选择布线391上例如至少共通地配置了在单位区块131内与该像素170在X方向(即行方向)上并列的像素的行选择晶体管的栅极。同样地，在该列选择布线392上例如至少共通地配置了在单位区块131内与该像素170在Y方向(即列方向)上并列的像素的列选择晶体管的栅极。

[0096] 根据上述构成，能够在行选择布线391与列选择布线392中附加了导通信号的情况下使由该布线特定的像素170的传输晶体管152导通。因此，能够在像素单位中控制传输晶体管的导通截止。

[0097] 进而，像素170中，代替像素150的一个选择晶体管158而设置了行选择晶体管174以及列选择晶体管175。行选择晶体管174的栅极与行选择布线394连接，列选择晶体管175的栅极与列选择布线395连接。在该行选择布线394中例如至少共通地配置了在单位区块131内与该像素170在X方向(即行方向)上并列的像素的行选择晶体管的栅极。同样地，在该列选择布线395中例如至少共通地配置了在单位区块131内与该像素170在Y方向(即列方向)上并列的像素的列选择晶体管的栅极。

[0098] 根据上述构成，能够在将行选择布线394与列选择布线395中附加了导通信号的情况下将由该布线特定的像素170的像素信号向输出布线308输出。因此，同如像素150那样与选择晶体管158一对一地对应的选择布线318相比，能够减少布线数。

[0099] 另外，也可以使与传输晶体管152相对的行选择布线391以及列选择布线392、和与输出布线308相对的行选择布线394以及列选择布线395不成组地使用。也可以对任意一方使用像素150的构成。此外，在不同时进行传输与输出的情况下，可以将行选择布线391、394作为一根而在传输与输出中共通地使用，并且列选择布线392、395也作为一根而在传输与输出中共通地使用。

[0100] 在上述实施方式中的任一个，复位布线326以及电源布线316也在单位区块131中共通。除此之外，复位布线326以及电源布线316也可以在多个单位区块131间共通。此外，代替于此，也可以将复位布线326按每个像素组设为共通，在像素组间另外布线。进而，也可以将复位布线326按每个像素分别布线，与在像素170中的传输晶体管152的控制同样地控制复位晶体管154。

[0101] 以上，根据本实施方式，在单位区块131内或者单位区块131间，将与相同的图像信息对应的多个像素作为像素组来控制电荷积蓄时间以及读取。因此，能够设定与各自的图像信息相适应的电荷积蓄时间以及读取定时。

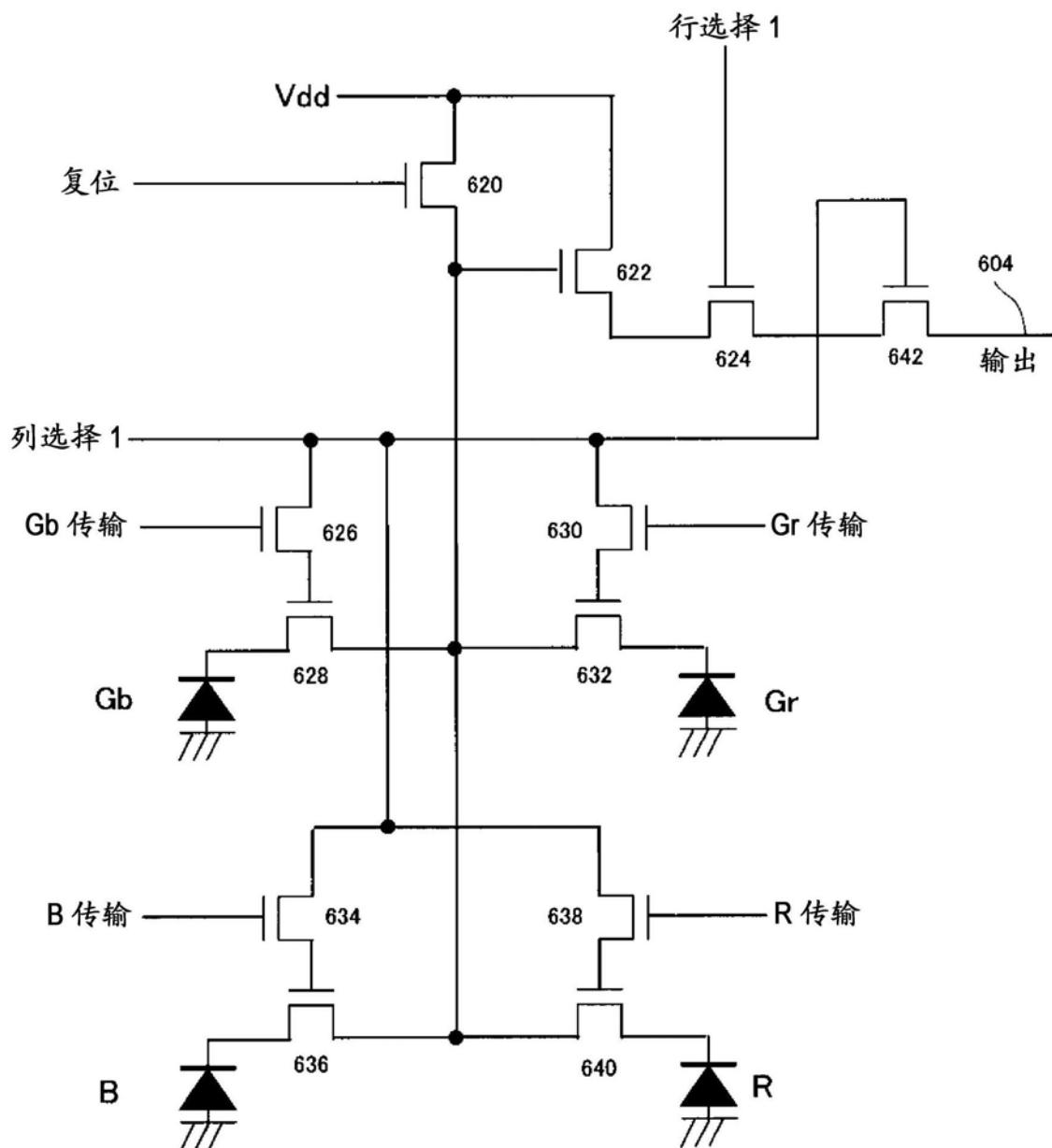

[0102] 图12示意性地示出了其他拍摄元件600的单位区块602。图13示出了单位区块602

内的像素单元603的电路图。

[0103] 拍摄元件600的单位区块602以与图2同样地拜耳排列的方式,二维地排列像素。每2行像素设置一根行选择线,在各行选择线上共通地连接2行像素。每2列像素设置一根输出布线604,在各输出布线604上共通地连接2列像素。输出布线604分别经由电连接拍摄芯片113与信号处理芯片111的凸块606而与CDS电路608一对一地连接。

[0104] 与包含在单位区块602中的多个输出布线604分别地一对一连接的多个CDS电路608的输出向多路调制器610输入。进而来自多路调制器610的输出向A/D转换电路612输入,A/D转换电路612的输出与像素存储器414连接。

[0105] 此外,在拜耳排列中一个单位形成像素单元603。即,像素单元603具有4个像素Gb、Gr、B、R。

[0106] 电源布线Vdd、复位布线在包含在单位区块131中的全体像素中共通地连接。此外,Gb传输布线在单位区块131中的像素Gb中共通地连接。同样地,Gr传输布线在单位区块131中的像素Gr中共通地连接,B传输布线在单位区块131中的像素B中共通地连接,R传输布线在单位区块131中的像素R中共通地连接。进而,在多个单位区块131间另外设置复位布线以及各传输布线。

[0107] 像素单元603的像素Gb、Gr、B、R共享复位晶体管620、放大晶体管622、选择晶体管624。此外,像素Gb具有传输晶体管626、628。同样地,像素Gr具有传输晶体管630、632,像素B具有传输晶体管634、636,像素R具有传输晶体管638、640。

[0108] 着眼于各像素的情况下,该像素与复位晶体管620、放大晶体管622以及选择晶体管624的连接关系与图3相同。另一方面,传输晶体管626等与图3的连接关系不同。像素Gb的传输晶体管626的栅极、漏极、源极分别与Gb传输布线、行选择线1、传输晶体管628的栅极连接。此外,传输晶体管628的源极、漏极分别与像素Gb的PD的一端、放大晶体管622的栅极连接。像素Gr、B、R的连接关系也是相同的。

[0109] 在如图12以及图13所示的方式中,如下述那样读取各像素的图像信号。另外,为了简化说明,省略复位动作的说明。

[0110] 使行选择线的任一个、例如行选择线1导通。在该状态下使任一个传输布线、例如Gb传输布线导通。由此,像素Gb的传输晶体管626、628双方导通,像素Gb的电荷向放大晶体管622的栅极传输。在此,由于行选择线1为导通状态,所以选择晶体管624也为导通,从输出布线604输出与向放大晶体管622的栅极传输的电荷相应地被放大的像素信号。

[0111] 由于行选择线1相对于单位区块602内的2行像素共通,Gb传输布线相对于单位区块602内的像素Gb共通,所以单位区块602的1行的像素Gb的像素信号向各自对应的输出布线604同时输出。在此,由于在输出布线604上一对一地配置了CDS电路608,所以各自的像素信号在除去了噪声的状态下暂时保持在各个CDS电路608中。

[0112] 多路调制器610依次读取保持在该CDS电路608中的像素信号,被引导到A/D转换电路612。A/D转换电路612依次将该像素信号数字化而写入到像素存储器414中。因此,单位区块602的1行的像素Gb的像素信号分别不受其他像素信号的影响地存储于像素存储器414中。

[0113] 接下来,通过在行选择线1导通的状态下使Gr传输布线导通,由此单位区块602的1行的像素Gr的像素信号分别不受其他的像素信号的影响地被依次读取。同样地,通过在行

选择线1导通的状态下使B传输布线导通,由此单位区块602的1行的像素B的像素信号被分别读取而存储在像素存储器414中,通过在行选择线1导通的状态下使R传输布线导通,单位区块602的1行的像素R的像素信号被分别读取而存储在像素存储器414中。通过以上,单位区块602的2行像素的像素信号被读取。

[0114] 接着导通行选择线2,重复进行上述顺序,由此读取单位区块602的接下来2行像素的像素信号。通过对全部的行选择线重复进行上述顺序,读取单位区块602内的全部像素的像素信号。

[0115] 根据图12以及图13所示的方式,关于各单位区块602,只要对2行像素设置一个行选择线即可,所以布线的拉绕变得容易。此外,由于关于各单位区块602对2列像素设置一个输出布线即可,所以布线的拉绕变得容易。

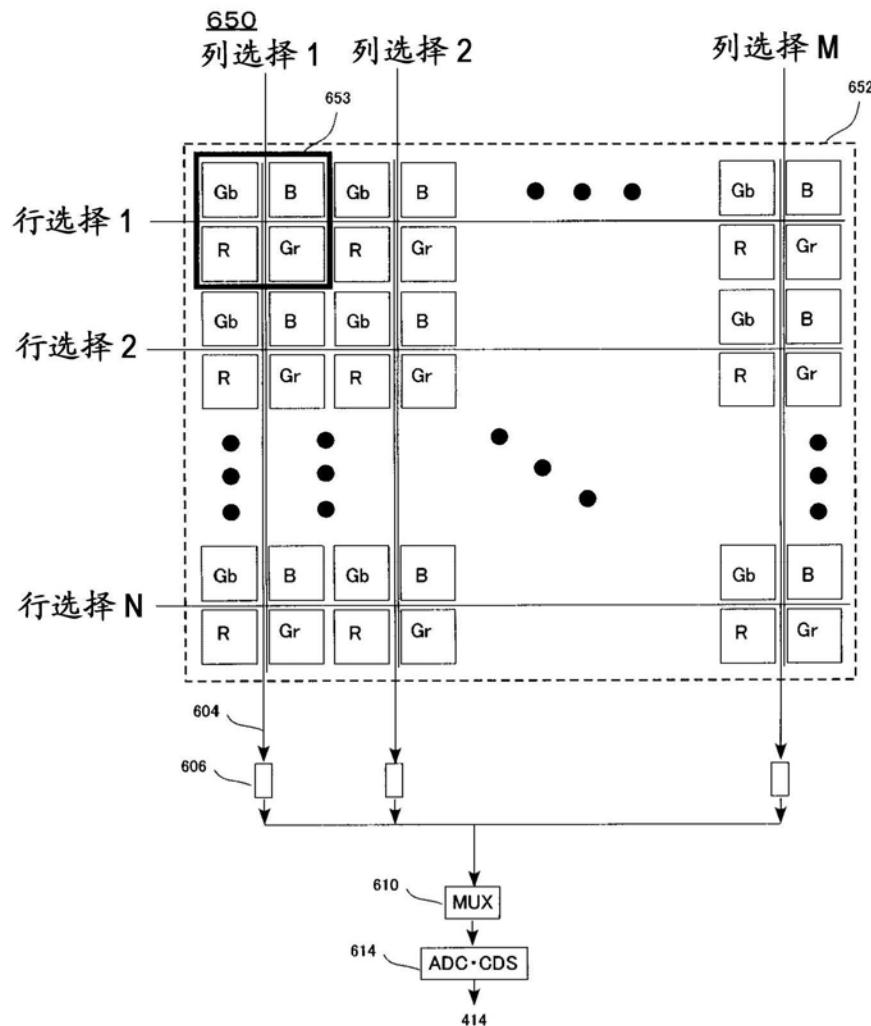

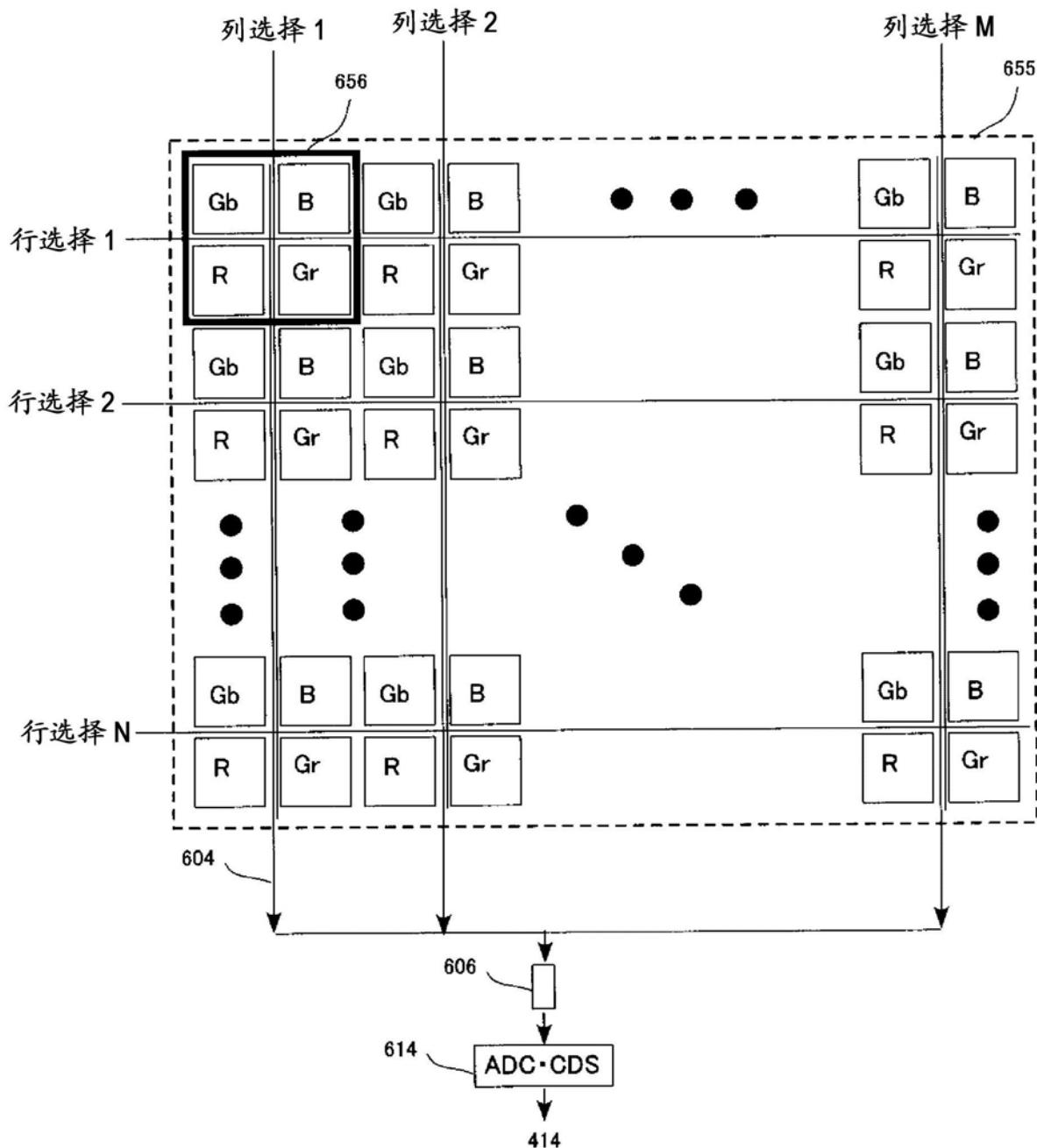

[0116] 图14进而示意性地示出了其他的拍摄元件650的单位区块652。

[0117] 图15是表示单位区块652内的像素单元653的电路图。在图14以及图15中,关于与图12以及图13相同的构成以及功能,赋予相同的附图标记,省略说明。

[0118] 在单位区块652中,每2列像素设置一根列选择线,在各列选择线上共通地连接2列的像素。列选择线与像素单元653的各传输晶体管626、630、634、638的漏极连接。

[0119] 各输出布线604经由凸块606配置在信号处理芯片111上,向与单位区块652对应设置的一个多路调制器610输入。多路调制器610的输出向A/D转换电路614输入。A/D转换电路614不仅具有将像素信号数字化的电路,还具有以数字方式执行CDS的电路。在A/D转换电路614中数字化后并执行了CDS的输出被存储到像素存储器414中。

[0120] 在图14以及图15的方式中,各像素的图像信号如下述那样读取。另外,为了简化说明,省略复位动作的说明。

[0121] 使行选择线的任一个、例如行选择线1导通。在该状态下使任一个传输线路、例如Gb传输布线导通。在该状态下进而使列选择线的任一个、例如列选择线1导通。由此,单位区块652内的一个像素单元653的像素Gb的传输晶体管626、628双方导通,像素Gb的电荷向放大晶体管622的栅极传输。在此,由于行选择线1为导通状态,所以选择晶体管624也为导通,从与该像素单元653对应的输出布线604输出与向放大晶体管622的栅极传输的电荷相应地被放大的像素信号。进而,将行选择线1以及Gb传输布线保持在导通状态,依次切换列选择线的导通状态,由此从各自的输出布线604依次输出1行的像素Gb的像素信号。

[0122] 通过与列选择线的切换同步地多路调制器610切换来自各输出布线604的输入,来自像素Gb的像素信号以每次一个像素量的方式向A/D转换电路614输入。单位区块652的1行的像素Gb的像素信号分别不受其他的像素信号的影响地被读取并存储在像素存储器414中。

[0123] 接下来,在行选择线1以及Gr传输布线导通的状态下,依次切换列选择线的导通状态,由此从各自的输出布线604依次输出1行的像素Gr的像素信号。同样地,通过在行选择线1以及B传输布线导通的状态下依次切换列选择线的导通状态,从各自的输出布线604依次输出1行的像素B的像素信号,通过在行选择线1以及R传输布线导通的状态下依次切换列选择线的导通状态,从各自的输出布线604依次输出1行的像素R的像素信号。根据以上,单位区块652的2行的像素的像素信号被读取。

[0124] 接下来通过导通行选择线2,重复进行上述顺序,读取单位区块652的接下来2行的

像素的像素信号。通过对全部的行选择线重复进行上述顺序,读取单位区块652内的全部像素的像素信号。

[0125] 在图14以及图15所示的方式中,由于关于各单位区块652对2行像素设置一个行选择线即可,所以布线的拉绕变得容易。此外,由于关于各单位区块652对2列像素设置一个输出布线即可,所以布线的拉绕变得容易。此外,能够将CDS电路设置在信号处理芯片111侧。

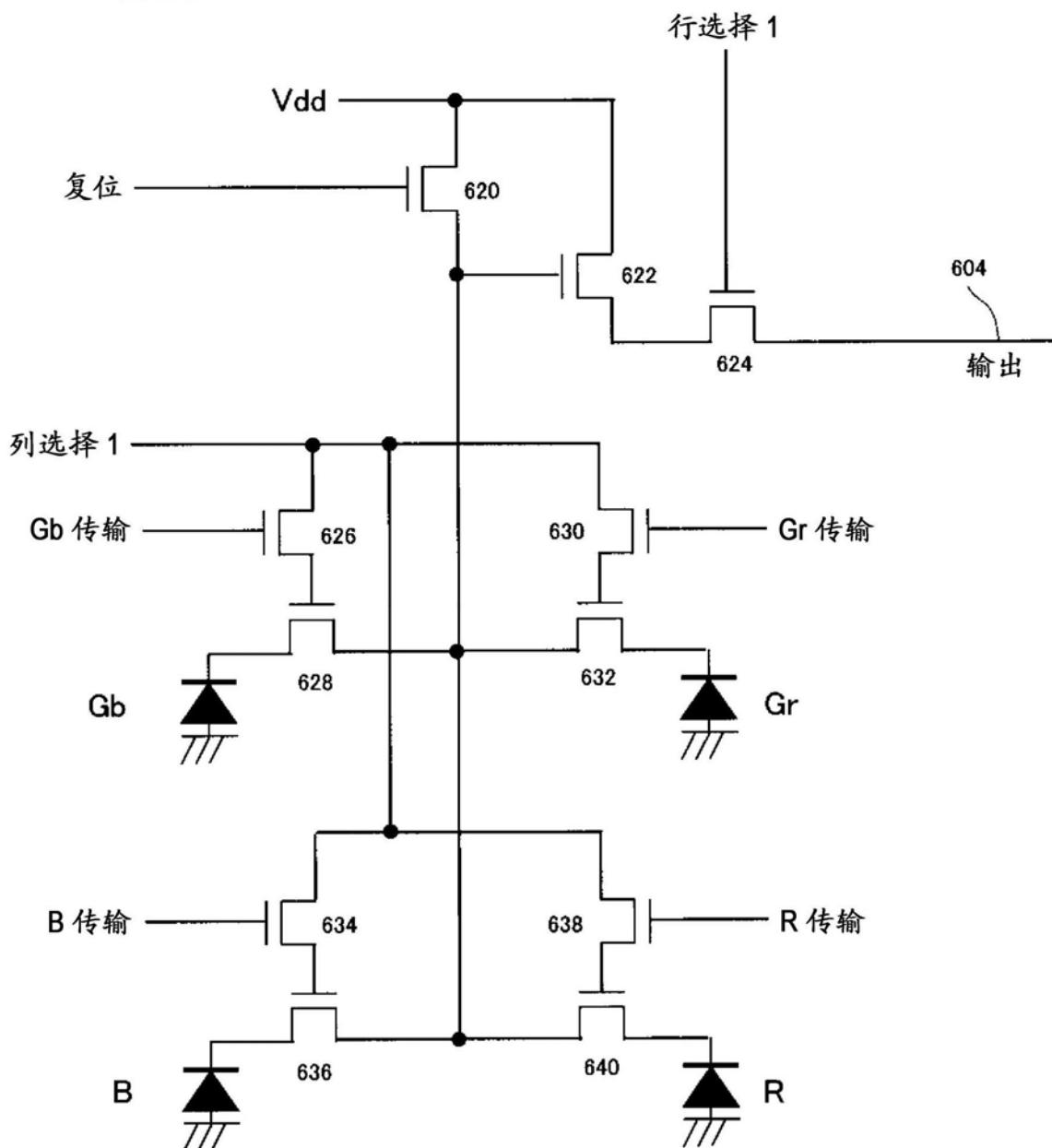

[0126] 图16进而示意性地示出了其他拍摄元件654的单位区块655。图17是表示单位区块655内的像素单元656的电路图。在图16以及图17中,关于与图14以及图15相同的构成以及功能,赋予相同的附图标记,省略说明。

[0127] 在单位区块655中,多个输出布线604与和单位区块652对应设置的一个凸块606共通连接。该凸块606与A/D转换电路614的输入侧连接。此外,在像素单元656的输出布线604上设置栅极与列选择线连接了的选择晶体管642。

[0128] 在图16以及图17的方式中,各像素的图像信号如下述那样读取。此外,为了简化说明,省略复位动作的说明。

[0129] 使行选择线的任一个、例如行选择线1导通。在该状态下使任一个传输线路、例如Gb传输布线导通。在该状态下进而使列选择线的任一个例如列选择线1导通。由此,将单位区块655内的一个像素单元656的像素Gb的传输晶体管626、628双方导通,像素Gb的电荷向放大晶体管622的栅极传输。在此,由于行选择线1为导通状态,所以选择晶体管624也为导通,从与该像素单元653对应的输出布线604输出与向放大晶体管622的栅极传输的电荷相应地被放大的像素信号。

[0130] 进而,将行选择线1以及Gb传输布线保持导通状态,通过依次切换列选择线的导通状态,从各自的输出布线604依次输出1行的像素Gb的像素信号。因此,来自像素Gb的像素信号以每次一个像素量的方式经由凸块606向A/D转换电路614输入。在这种情况下,由于在各像素单元656中配置选择晶体管642,所以阻断来自未在列选择线中选择的像素单元656的像素Gb的输出。因此,单位区块655的1行的像素Gb的像素信号分别不受其他像素信号的影响被读取,并存储在像素存储器414中。

[0131] 接下来,在行选择线1以及Gr传输布线导通的状态下,通过依次切换列选择线的导通状态,从各自的输出布线604依次输出1行的像素Gr的像素信号。同样地,通过在行选择线1以及B传输布线导通的状态下依次切换列选择线的导通状态,从各自的输出布线604依次输出1行的像素B的像素信号,通过在行选择线1以及R传输布线导通的状态下依次切换列选择线的导通状态,从各自的输出布线604依次输出1行的像素R的像素信号。

[0132] 通过以上,单位区块655的2行的像素的像素信号被读取。通过接下来导通行选择线2并重复进行上述顺序,读取单位区块655接下来2行的像素的像素信号。通过对全部的行选择线重复进行上述顺序,读取单位区块655内的全部像素的像素信号。

[0133] 在图16以及图17所示的方式中,由于关于各单位区块655对2行像素设置一个行选择线即可,所以布线的拉绕变得容易。此外,由于关于各单位区块655对2个像素列设置一个输出布线即可,所以布线的拉绕变得容易。此外,能够将CDS电路设置在信号处理芯片111侧。进而,由于也可以不设置多路调制器,所以能够简化信号处理芯片111侧的布线。

[0134] 在从图12至图17所示的方式中,虽然A/D转换电路612、614是相对于单位区块602、652、655一对一地设置,但A/D转换电路612、614的个数不限定于此。也可以对各单位区块

602、652、655设置多个A/D转换电路612、614。在这种情况下,各单位区块602、652、655的多个输出布线604以分别分配给多个A/D转换电路612、614的任一个的方式布线并输入。

[0135] 此外,像素单元由4个像素构成,按每2行像素地配置行选择布线,按每3列像素地配置输出布线,但不限定于此。例如,在像素单元由m行n列构成的情况下,也可以对单位区块按每m行一根地设置行选择布线,按每n列一根地设置输出布线,并且,也可以另外设置m×n根传输布线。另外,各传输布线可以在像素组内共通。

[0136] 上述实施方式涉及的拍摄装置500可以在拍摄静止图像中使用,也可以在拍摄动态图像中使用。在拍摄动态图像的情况下,也可以使每一个像素组的积蓄时间按时间变化。例如,也可以在场景切换前后动态改变每一个像素组的积蓄时间。在这种情况下,也可以基于之前的图像,以与静止图像的情况相同的方式改变积蓄时间。此外,也可以基于之前的数秒期间的图像,例如基于其平均时间,来改变积蓄时间。此外,也可以使用预先登记了拍摄流程与积蓄时间的关系的数据库,根据拍摄流程使积蓄时间变化。

[0137] 此外,在上述实施方式中,层叠拍摄芯片113、信号处理芯片111以及存储器芯片112,也可以不层叠这些。即,也可以在一个芯片上设置这些功能。

[0138] 以上,使用实施本发明的方式进行说明,本发明的技术范围不限定于上述实施方式记载的范围内。在上述实施方式中,本领域技术人员可以加上多样的变更或者改进。从权利要求的记载得以明确,加上多样的变更或者改进的方式也可以包含在本发明的技术范围内。

[0139] 权利要求、说明书、以及附图中所示的装置、系统、程序、以及方法中的动作、顺序、步骤、以及阶段等的各处理的执行顺序没有特别明示“之前”、“首先”,此外,只要在之后的处理中使用之前的处理的输出,就应当留意到能够在任意的顺序中实现。关于权利要求、说明书、以及附图中的动作流程,即使在便利上使用“首先,”、“接下来,”等进行说明,也不意味着必须以该顺序实施。

图1

100

图2

150

图3

图4

图5

图6

图7

图8

图9

图10

170

图11

图12

**603**

图13

图14

**653**

图15

**654**

图16

**656**

图17