(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0037464

(43) 공개일자 2009년04월15일

(51) Int. Cl.

*H01L 21/20* (2006.01)

(21) 출원번호 10-2009-7002676

(22) 출원일자 2009년02월10일

심사청구일자 없음

번역문제출일자 2009년02월10일

(86) 국제출원번호 PCT/US2007/075040

국제출원일자 2007년08월02일

(87) 국제공개번호 WO 2008/019282

국제공개일자 2008년02월14일

(30) 우선권주장

11/764,219 2007년06월17일 미국(US)

60/821,472 2006년08월04일 미국(US)

(71) 출원인

어플라이드 머티어리얼스, 인코포레이티드

미국 95054 캘리포니아 산타 클라라 바우어스 애브뉴 3050

(72) 별명자

올젠, 크리스토퍼

미국 94536 캘리포니아 프레몬트 무어 드라이브 38642

(74) 대리인

남상선

전체 청구항 수 : 총 20 항

(54) 귀 가스를 포함하는 이중 플라즈마 질화에 의해 CMOS SiON 게이트 유전체 성능의 개선

### (57) 요 약

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법이 제공된다. 상기 층은 또한 산소를 포함하며 실리콘 산질화물 게이트 유전체 층으로서 사용될 수 있다. 일면에서, 상기 층을 형성하는 방법은 상기 기판의 상부면 내측에 질소를 결합시키도록 질소와 귀 가스의 플라즈마에 실리콘 기판을 노출시키는 단계를 포함하며, 상기 귀 가스는 아르곤, 네온, 크립톤, 또는 제논이다. 상기 층은 어닐링된 후에 상기 층 내측에 많은 질소를 결합시키도록 질소 플라즈마에 노출된다. 상기 층은 그 후에 추가로 어닐링된다.

### 대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법으로서,

챔버 내측으로 실리콘을 포함하는 기판을 도입하는 단계와,

상기 기판의 상부면 내측에 질소를 결합시키고 상기 기판 상에 실리콘과 질소를 포함하는 층을 형성하도록, 아르곤, 네온, 크립톤과 제논으로 이루어지는 그룹으로부터 선택되는 귀 가스와 질소의 플라즈마에 상기 챔버 내의 기판을 노출시키는 단계와,

실리콘과 질소를 포함하는 상기 층을 어닐링하는 단계와,

실리콘과 질소를 포함하는 상기 층의 내측에 더 많은 질소를 결합시키도록 질소 플라즈마에 실리콘과 질소를 포함하는 상기 층을 노출시키는 단계, 및

실리콘과 질소를 포함하는 상기 층을 추가로 어닐링하는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

### 청구항 2

제 1 항에 있어서,

실리콘과 질소를 포함하는 상기 층을 어닐링하는 단계는 상기 층의 내측에 산소를 유입시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

### 청구항 3

제 1 항에 있어서,

상기 질소는 질소 소오스로서 질소 가스( $N_2$ )에 의해 제공되는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

### 청구항 4

제 1 항에 있어서,

상기 플라즈마는 RF 전력, 마이크로웨이브 전력, 또는 이들의 조합을 사용하여 생성되는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

### 청구항 5

제 1 항에 있어서,

상기 어닐링 및 추가의 어닐링 단계는 각각, 약 800 °C 내지 약 1100 °C 범위의 온도에서 산소 가스( $O_2$ )를 포함하는 가스에 실리콘과 질소를 포함하는 층을 노출시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

### 청구항 6

제 1 항에 있어서,

상기 어닐링 및 추가의 어닐링 단계 중의 하나 또는 그 이상은 약 800 °C 내지 약 1100 °C 범위의 온도에서 불활성 가스에 실리콘과 질소를 포함하는 층을 노출시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

### 청구항 7

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법으로서,

챔버 내측으로 실리콘을 포함하며 상부에 얇은 화학적 산화물 층을 포함하거나 수소-종결반응된 상부면을 가지는 기판을 도입하는 단계와,

상기 기판의 상부면 내측에 질소를 결합시키고 상기 기판 상에 실리콘과 질소를 포함하는 층을 형성하도록, 아르곤, 네온, 크립톤과 제논으로 이루어지는 그룹으로부터 선택되는 귀 가스와 질소의 플라즈마에 상기 챔버 내의 기판을 노출시키는 단계와,

실리콘과 질소를 포함하는 상기 층을 어닐링하는 단계로서, 상기 어닐링 단계 중에 산소가 상기 층 내측으로 유입되는 어닐링 단계와,

실리콘과 질소를 포함하는 상기 층의 내측에 더 많은 질소를 결합시키도록 질소 플라즈마에 실리콘과 질소를 포함하는 상기 층을 노출시키는 단계, 및

실리콘과 질소를 포함하는 상기 층을 추가로 어닐링하는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 8

제 7 항에 있어서,

상기 질소는 질소 소오스로서 질소 가스( $N_2$ )에 의해 제공되는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 9

제 7 항에 있어서,

상기 기판을 상기 챔버 내측으로 유입시키기 이전에 상기 기판을 세정하는 단계를 더 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 10

제 9 항에 있어서,

상기 기판을 세정하는 단계는 습식 세정 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 11

제 10 항에 있어서,

상기 습식 세정 단계는  $H_2O$ ,  $NH_4OH$ , 및  $H_2O_2$ 를 포함하는 용액에 상기 기판을 노출시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 12

제 11 항에 있어서,

상기 기판을 세정하는 단계는 상기 기판을 HF에 노출시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 13

제 7 항에 있어서,

상기 기판은 상부에 약 3 Å 내지 약 5 Å 범위의 두께를 가지는 얇은 화학적 산화물 층을 포함하는 상부면을 가지는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 14

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법으로서,

챔버 내측으로 실리콘을 포함하는 기판을 도입하는 단계와,

상기 기판의 상부면 내측에 질소를 결합시키고 상기 기판 상에 실리콘과 질소를 포함하는 층을 형성하도록 질소와 아르곤의 플라즈마에 상기 챔버 내의 기판을 노출시키는 단계와,

실리콘과 질소를 포함하는 상기 층을 어닐링하는 단계로서, 상기 어닐링 단계 중에 산소가 상기 층 내측으로 유입되는 어닐링 단계와,

실리콘과 질소를 포함하는 상기 층의 내측에 더 많은 질소를 결합시키도록 질소 플라즈마에 실리콘과 질소를 포함하는 상기 층을 노출시키는 단계, 및

실리콘과 질소를 포함하는 상기 층을 추가로 어닐링하는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 15

제 14 항에 있어서,

상기 챔버의 내측으로 상기 기판을 유입시키기 이전에 상기 기판을 세정하는 단계를 더 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 16

제 15 항에 있어서,

상기 세정 단계는 상부에 얇은 화학적 산화물 층을 포함하거나 수소 종결반응된 상기 기판 상부면을 형성하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 17

제 16 항에 있어서,

상기 기판은 상부에 약 3 Å 내지 약 5 Å 범위의 두께를 가지는 얇은 화학적 산화물 층을 포함하는 상부면을 가지는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 18

제 14 항에 있어서,

상기 질소는 질소 소오스로서 질소 가스( $N_2$ )에 의해 제공되는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 19

제 14 항에 있어서,

상기 어닐링 및 추가의 어닐링 단계는 각각, 약 800 °C 내지 약 1100 °C 범위의 온도에서 산소 가스( $O_2$ )를 포함하는 가스에 상기 층을 노출시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

#### 청구항 20

제 14 항에 있어서,

상기 추가의 어닐링 단계는 약 800 °C 내지 약 1100 °C 범위의 온도에서 불활성 가스에 상기 층을 노출시키는 단계를 포함하는,

기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법.

## 명세서

### 기술분야

<1> 본 발명의 실시예들은 일반적으로 게이트 유전체 층을 형성하는 방법에 관한 것이다. 특히, 본 발명의 실시예들은 실리콘 산질화물(SiON) 게이트 유전체 층을 형성하는 방법에 관한 것이다.

### 배경기술

<2> 집적 회로는 트랜지스터, 커패시터, 및 레지스터와 같은 다수의 예를 들어, 수백만 개의 장치로 구성된다. 전계 효과 트랜지스터와 같은 트랜지스터는 통상적으로, 소오스, 드레인, 및 게이트 스택(stack)을 포함한다. 게이트 스택은 통상적으로, 실리콘 기판과 같은 기판, 상기 기판 상에 실리콘 이산화물, SiO<sub>2</sub>과 같은 게이트 유전체, 및 상기 게이트 유전체 상의 다결정질 실리콘과 같은 게이트 전극을 포함한다.

<3> 집적 회로의 크기와 집적 회로 상의 트랜지스터의 크기가 감소됨에 따라, 트랜지스터의 속도를 증가시키는데 필요한 게이트 구동 전류도 증가되었다. 게이트 용량이 증가함에 따라 구동 전류도 증가하고 용량이 게이트 유전체 두께에 반비례하기 때문에, 유전체 두께를 감소시키는 것은 구동 전류를 증가시키는 하나의 방법이다.

<4> 20 Å 이하의 SiO<sub>2</sub> 게이트 유전체의 두께를 감소시키기 위한 시도들이 수행되어 왔다. 그러나, 20 Å 이하의 얇은 SiO<sub>2</sub> 게이트 유전체의 사용은 종종 게이트 성능과 내구성에 바람직하지 않은 결과를 초래하는 것이 발견되었다. 예를 들어, 붕소 도프된 게이트 전극으로부터의 붕소가 얇은 SiO<sub>2</sub> 게이트 유전체를 통해서 하층의 실리콘 기판으로 침투할 수 있다. 또한, 통상적으로 게이트에 소모되는 전력량을 증가시키는 게이트 전류의 누설, 즉 터널링(tunneling)이 증가된다.

<5> 얇은 SiO<sub>2</sub> 게이트 유전체가 갖는 문제점을 처리하는데 사용되어 온 하나의 방법은 실리콘 산질화물(SiON 또는 SiO<sub>x</sub>N<sub>y</sub>) 게이트 유전체를 형성하기 위해 SiO<sub>2</sub> 층 내에 질소를 결합시키는 것이다. SiO<sub>2</sub> 층 내의 질소 결합으로 하층의 실리콘 기판으로 붕소의 침투를 차단하고 게이트 유전체의 유전체 상수를 증가시켜서 보다 두꺼운 유전체 층의 사용을 가능하게 한다.

<6> 선택적으로 후처리 어닐링이 사용될 수 있는 플라즈마 질화법이 실리콘 산질화물 층을 형성시키기 위해 SiO<sub>2</sub> 층 내에 질소를 결합시키는데 필수적인 하나의 공정으로 사용되었다. 그러나, 그와 같은 단일 단계의 질화 공정에 있어서 상기 층의 두께를 통해 원자 질소량과 같은 실리콘 산질화물 층의 농도 프로파일을 제어하는 것이 어렵다. 따라서, 실리콘 산질화물 층을 증착시키기 위한 방법에 그 필요성이 남아 있다.

### 발명의 상세한 설명

<7> 본 발명은 일반적으로 기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법을 제공한다. 실리콘과 질소를 포함하는 층도 산소를 포함할 수 있으며, 따라서 게이트 유전체 층으로서 사용될 수 있는 실리콘 산질화물 층을 제공한다.

<8> 일 실시예에서, 기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법은 챔버 내측으로 실리콘을 포함하는 기판을 도입하고 나서 기판의 상부면에 질소를 결합시키고 기판 상에 실리콘을 포함하는 층을 형성시키도록 질소와 귀 가스의 플라즈마에 챔버 내의 기판을 노출시키는 단계를 포함하며, 귀 가스는 아르곤, 네온, 크립톤, 및 제논으로 이루어지는 그룹으로부터 선택된다. 실리콘과 질소를 포함하는 층은 어닐링된다. 상기 층의 어닐링에는 약 800 °C 내지 약 1100 °C 범위의 온도에서 산소 가스를 포함하는 가스에 상기 층을 노출시키거나 약 800 °C 내지 약 1100 °C 범위의 온도에서 불활성 가스에 상기 층을 노출시키는 단계를 포함할 수 있다. 상기 층은 그 후에 실리콘과 질소를 포함하는 층 내에 많은 질소를 결합시키도록 질소 플라즈마에 노출된다.

<9> 다른 실시예에서 기판 상에 실리콘과 질소를 포함하는 층을 형성하는 방법은 챔버 내측으로 실리콘을 포함하는

기판을 도입하고 나서 기판의 상부면에 질소를 결합시키고 기판 상에 실리콘을 포함하는 층을 형성시키도록 질소와 아르곤 플라즈마에 챔버 내의 기판을 노출시키는 단계를 포함한다. 실리콘과 질소를 포함하는 층은 어닐링되며 산소가 어닐링 중에 상기 층의 내측으로 유입된다. 상기 층은 그 후에 실리콘과 질소를 포함하는 상기 층의 내측에 많은 질소를 결합시키도록 질소 플라즈마에 노출된다. 상기 층은 그 후 추가로 어닐링된다.

<10> 전술한 본 발명의 특징들이 더욱 명확하게 이해될 수 있도록 간략하게 요약된 본 발명에 대해 몇몇 실시예만이 첨부 도면에 도시된 실시예들을 참조하여 더욱 상세히 설명된다. 그러나, 첨부 도면들은 본 발명의 단지 통상적인 실시예일뿐이므로 본 발명의 범주를 한정하는 것이 아니며 다른 균등하고 효과적인 실시예들이 있을 수 있다고 이해해야 한다.

### 실시예

<15> 본 발명의 실시예들은 실리콘과 질소를 포함하는 층을 형성하는 방법을 제공한다. 실리콘과 질소를 포함하는 층은 게이트 유전체 층으로서 사용될 수 있는 실리콘 산질화물(SiON) 층일 수 있다. 본 발명의 실시예에 따른 실리콘 산질화물 층들을 포함하는 게이트 스택은 NMOS 및 PMOS 장치 내에 바람직한 구동 전류를 가진다.

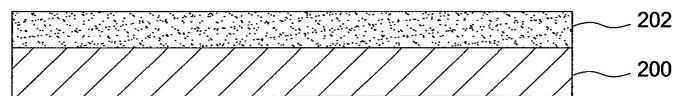

<16> 본 발명의 실시예는 도 1의 흐름도와 관련하여 간단히 설명되며 도 2a 내지 도 2e와 관련하여 이후에 더 상세히 설명된다.

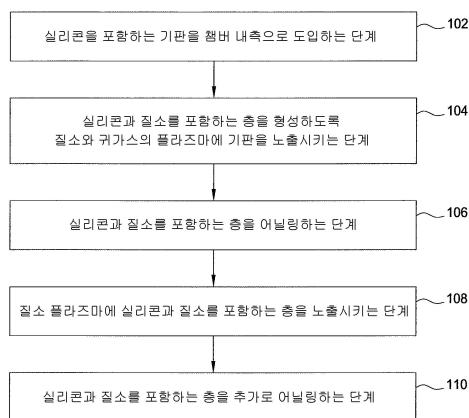

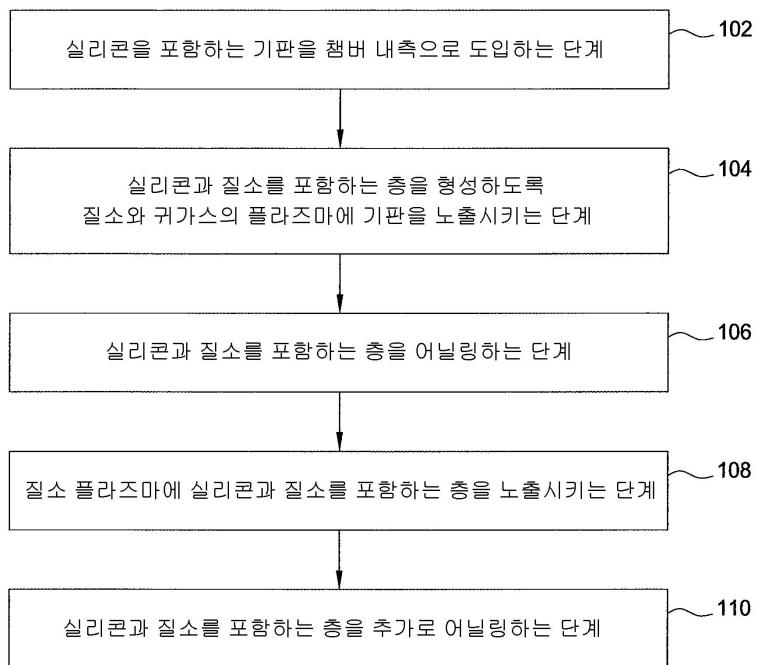

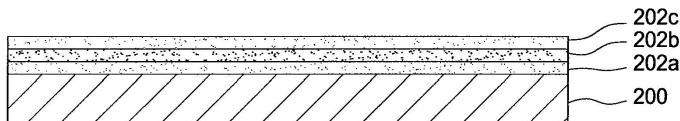

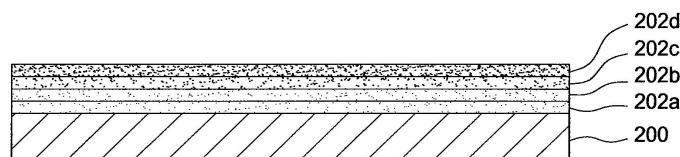

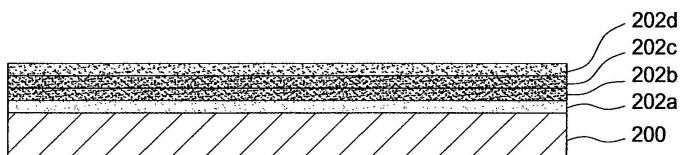

<17> 실리콘을 포함하는 기판이 도 1에 도시한 바와 같이 단계(102)에서 챔버 내측으로 도입된다. 기판은 단계(104)에 나타낸 바와 같이, 기판 상에 실리콘과 질소를 포함하는 층을 형성하도록 질소와 귀 가스의 플라즈마, 즉 질소와 귀 가스 함유 플라즈마에 노출된다. 실리콘과 질소를 포함하는 층이 단계(106)에서 어닐링된다. 그 후 실리콘과 질소를 포함하는 상기 층이 단계(108)에서 질소 플라즈마에 노출된다. 단계(110)에서, 실리콘과 질소를 포함하는 층이 추가로 어닐링된다. 단계(104)와 단계(108)는 플라즈마의 존재 하에서 층 내측에 질소를 결합시키므로, 플라즈마 질화 단계로서 설명될 수 있다. 일련의 다중 플라즈마 질화와 어닐링 단계를 사용함으로써, 실리콘 산질화물 층과 같은 실리콘과 질소를 포함하며 바람직한 농도 프로파일을 가지는 층이 얻어질 수 있다.

<18> 도 2a는 도 1의 단계(102)에서 전술한 바와 같이, 실리콘을 포함하는 기판(200)의 예를 도시한다. 기판(200)은 반도체 또는 평판 디스플레이 처리에 적합한 200 mm 또는 300 mm 또는 다른 기판일 수 있다. 기판은 베어(bare) 실리콘 웨이퍼 또는 기판과 같은 실리콘 기판일 수 있다. 이와는 달리, 기판은 수소-종결반응된 상부면을 가지거나 상부에 얇은 화학적 산화물 층을 포함하는 실리콘 기판일 수 있다. 기판 상부면 상의 얇은 화학적 산화물 층 또는 수소-종결반응된 상부면은 기판이 단계(102)에서 챔버의 내측으로 도입되기 이전에 실리콘 기판 상에 수행되는 세정 공정에 의해 형성될 수 있다. 세정 공정은 추가의 처리 이전에 기판으로부터 네가티브 산화물 층 또는 다른 오염물을 제거하기 위해 수행된다. 세정 공정은 단일 기판 또는 배치 시스템에서 수행될 수 있다. 세정 공정은 초음파 강화 욕 내에서 수행될 수 있다.

<19> 일 실시예에서, 세정 공정은 기판을 습식 세정 공정에 노출시키는 단계를 포함한다. 습식 세정 공정은 기판의 상부면 상에 얇은 화학적 산화물 층을 형성하는,  $H_2O$ ,  $NH_4OH$ , 및  $H_2O_2$ 를 포함하는 용액, 예를 들어 SC-1 용액에 기판을 노출시키는 단계를 포함할 수 있다. 이와는 달리, 습식 세정 공정은 불화수소산 최종 세정을 포함할 수 있으며, 상기 세정 공정의 최종 단계는 불화수소산(HF)의 희석 용액에 기판을 노출시키는 단계를 포함하여 기판 상에 수소 종결 반응된 상부면을 남긴다. 상기 용액은 약 20 °C 내지 약 30 °C의 온도에서 사용되는 약 0.1 내지 약 10.0 중량%의 HF 농도를 가질 수 있다. 예시적인 실시예에서, 상기 용액은 약 25 °C의 사용 온도와 약 0.5 중량%의 농도를 가진다. 상기 용액에의 잠시 노출은 탈이온수 내의 린스 단계가 이어질 수 있다.

<20> 단계(102)로 돌아가서, 기판이 내측으로 도입되는 챔버는 기판을 플라즈마에 노출시킬 수 있는 챔버이다. 플라즈마는 RF 전력(power), 마이크로웨이브 전력, 또는 이들의 조합에 의해 생성될 수 있다. 플라즈마는 준-원격 플라즈마 소오스, 유도 플라즈마, 라디칼 라인 슬롯 안테나(RLSA) 소오스, 다른 플라즈마 소오스를 사용하여 생성될 수 있다. 플라즈마는 연속적 또는 단속적일 수 있다.

<21> 사용될 수 있는 챔버의 예는 감결합 질화(DPN) 챔버이다. DPN 챔버는 진폭 변조식 RF 에너지를 사용하여 게이트 유전체를 플라즈마 질화시키기 위한 방법 및 장치라는 발명의 명칭으로 2004년 12월 2일자로 공개된 미국 출원 공개 번호 2004/0242021호에 추가로 설명되어 있으며, 이는 어플라이드 머티리얼즈, 인코포레이트에 양도되었으며, 모든 내용이 본 발명에 참조되었다. 하나의 적합한 감결합 플라즈마 챔버는 미국 산타 클라라 소재의 어플라이드 머티리얼즈, 인코포레이티드로부터 상업적으로 이용가능한 DPN CENTURA(등록 상표) 챔버이다. DPN

CENTURA(등록 상표) 챔버를 포함할 수 있으며 본 발명의 실시예들을 수행하는데 사용될 수 있는 통합 처리 시스템의 예는 또한, 미국 산타 클라라 소재의 어플라이드 머티리얼즈, 인코포레이티드로부터 이용가능한 게이트 스택 CENTURA(등록 상표) 시스템이다.

<22> 일단 챔버 내에서 기관(200)은 기관의 상부면 내에 질소를 결합시켜 도 2b에 도시한 바와 같이 실리콘과 질소를 포함하는 층(202)을 형성하도록 질소와 귀 가스 플라즈마에 노출된다. 하나의 일면에서, 기관을 질소와 귀 가스의 플라즈마에 노출시키는 것은 플라즈마 질화 공정이다. 플라즈마 내의 질소는 질소 가스( $N_2$ )와 같은 질소 소오스에 의해 제공된다. 귀 가스는 아르곤(Ar), 네온(He), 크립톤(Kr), 또는 제논(Xe)일 수 있다. 일 실시예에서, 질소 소오스는 질소 가스이며, 귀 가스는 아르곤이다. 플라즈마는 약 1 % 내지 약 80 % 범위의 귀 가스이며 나머지는 질소에 의해 제공된다. 사용될 플라즈마 처리 조건의 예로는 약 10 sccm 내지 약 2000 sccm 범위로 챔버의 내측으로 제공되는 질소 소오스, 예를 들어  $N_2$  유동, 약 10 sccm 내지 약 2000 sccm 범위로 챔버의 내측으로 제공되는 귀가스, 예를 들어 Ar 유동, 약 20 °C 내지 약 500 °C 범위의 챔버 기관 지지대 온도, 및 약 5 mTorr 내지 약 1000 mTorr 범위의 챔버 압력이다. RF 전력은 13.56 MHz에서, 약 3 kW 내지 약 5 kW 범위의 연속 파형(CW) 또는 펄스 파형 플라즈마 전력에 의해 제공될 수 있다. 펄싱 중, 피크 RF 전력, 주파수 및 듀티 사이클은 통상적으로, 각각 약 10 W 내지 약 3000 W, 약 2 kHz 내지 약 100 kHz, 및 약 2 내지 약 50 %이다. 플라즈마 질화법은 약 1 내지 약 180 초간 수행될 수 있다. 일 실시예에서, 질소 가스는 약 200 sccm으로 제공되며, 약 1000 W의 RF 전력이 화학적 산화물 표면 상에서 약 15 내지 약 180 초 동안 약 25 °C와 약 20 mTorr에서, 유도 플라즈마 소오스에 인가된 약 5 %의 듀티 사이클로 약 10 kHz에서 펄스된다. 추가의 실시예에서, 질소 가스는 약 200 sccm으로 제공되며, 약 1000 W의 RF 전력이 수소 종결반응된 표면 상에서 약 15 초 동안 약 25 °C와 약 80 mTorr에서, 유도 플라즈마 소오스에 인가된 약 5 %의 듀티 사이클로 약 10 kHz에서 펄스된다.

<23> 실리콘과 질소를 포함하는 층(202)이 형성된 이후에, 층은 어닐링된다. 층(202)의 어닐링으로 도 2c에 도시한 바와 같이, 층(202) 내에 상이한 부분층들을 형성한다. 부분층(202a)은 기관(202)에 인접하며, 부분층(202c)은 기관(202)으로부터 가장 멀리 위치되며, 부분층(202b)은 부분층(202a, 202c)들 사이에 있다. 부분층(202b)은 부분층(202a, 202c)보다 높은 질소 농도를 가지며, 부분층(202a, 202c)은 어닐링 이전에 층(202)의 농도보다 낮은 질소 농도를 가진다. 층(202)의 어닐링으로 또한, 층을 조밀화하여서 질소 함유 플라즈마에 층(202)의 계속된 노출(단계 108)에서 질소가 너무 깊게 층(202)을 침투하지 못하여 하부층(202)을 오염시키는데, 이는 각각 게이트 유전체 층과 하부 실리콘 채널으로서 층(202, 200)을 포함하는 게이트 장치를 훼손할 수 있다. 어닐링은 모두 미국 산타클라라 소재의 어플라이드 머티리얼즈, 인코포레이티드로부터 이용가능한 RADIANCE(등록 상표) 챔버 또는 RADIANCE 플러스 RTP 챔버와 같은 챔버 내에서 수행될 수 있다.

<24> 일 실시예에서, 실리콘과 질소를 포함하는 층의 어닐링은 질소 가스 분위기로 희석되는  $O_2$  또는 저압  $O_2$ 와 같은 저압 산화 분위기의 약간 산화 분위기에 상기 층을 노출시키는 단계를 포함하며, 상기  $O_2$  부분압은 약 1 mTorr 내지 약 100 Torr 범위이다. 상기 층은 약 5 초 내지 약 180 초간 약 800 °C 내지 약 1100 °C 범위의 기관 온도에서 어닐링될 수 있다.  $O_2$ 는 약 500 sccm과 같은 약 2 sccm 내지 약 5000 sccm 범위의 유동률로 챔버 내측으로 유입된다. 일 실시예에서,  $O_2$ 는 약 15 초간 약 1000 °C의 온도와 약 0.1 Torr의 압력을 유지하는 동안에 약 500 sccm으로 제공된다.

<25> 다른 실시예에서, 실리콘과 질소를 포함하는 상기 층을 어닐링하는 것은 약 800 °C 내지 약 1100 °C 범위의 온도에서 질소, 아르곤, 또는 이들의 조합과 같은 불활성 가스에 상기 층을 노출시키는 단계를 포함한다.

<26> 또 다른 실시예에서, 상기 어닐링은 습식 산화 환경을 제공함으로써 수행될 수 있다. 인 시튜 스텀 생성(ISSG)으로서 공지된 이러한 공정은 미국 산타 클라라 소재의 어플라이드 머티리얼즈 인코포레이티드로부터 상업적으로 이용가능하다. ISSG 공정은 500 sccm 내지 5000 sccm의 산소 및 10 sccm 내지 1000 sccm의 수소를 갖는 분위기 및 0.5 내지 18.0 Torr의 압력에서 약 700 °C 내지 약 1000 °C로 기관 표면을 가열하는 단계를 포함한다. 바람직하게, 수소는 산소와 수소 혼합물의 전체 가스 유동의 20 % 미만이다. 가스 혼합물에의 노출 주기는 약 5 내지 약 180초이다. 일 실시예에서, 산소는 980 sccm으로 제공되며, 수소는 20 sccm으로 제공되며, 기관 표면 온도는 800 °C이며, 챔버 압력은 7.5 Torr이며, 노출 주기는 약 15초이다.

<27> 실리콘과 질소를 포함하는 층이 어닐링된 후에, 층은 도 1의 단계(108)에 도시된 바와 같이 질소 플라즈마에 노출된다. 질소 플라즈마에 층을 노출하는 것에 의해 추가 양의 질소가 상기 층 내에 결합하게 함으로써 층 내의 질소 원자비를 증가시킨다. 도 2d에 도시한 바와 같이, 실리콘과 질소를 함유하는 층(202)의 추가의 부분층

(202d)이 실리콘과 질소 함유 층(202)의 표면에 형성되며 부분층(202a-202c)보다 높은 질소 농도를 가진다.

- <28> 질소 플라즈마는 질소 가스(N<sub>2</sub>), 아산화 질소(N<sub>2</sub>O), 또는 산화 질소(NO)와 같은 질소 소오스에 의해 제공될 수 있다. 선택적으로, 질소 플라즈마도 아르곤, 네온, 크립톤, 또는 제논과 같은 귀 가스를 포함할 수 있다. 플라즈마는 RF 전력, 마이크로웨이브 전력, 또는 이들의 조합을 사용하여 생성될 수 있다. 플라즈마는 준-원격 플라즈마 소오스, 유도 플라즈마, 라디칼 라인 슬롯 안테나(RLSA) 소오스, 다른 플라즈마 소오스를 사용하여 생성될 수 있다. 플라즈마는 연속적 또는 단속적일 수 있다. 상기 층은 DPN CENTURA(등록 상표) 챔버와 같은 DPN 챔버 내에서 플라즈마에 노출될 수 있다.

- <29> 사용될 플라즈마 처리 조건의 예로는 약 10 sccm 내지 약 2000 sccm 범위로 챔버의 내측으로 제공되는 질소 소오스, 예를 들어 N<sub>2</sub> 유동, 약 20 °C 내지 약 500 °C 범위의 챔버 기판 온도, 및 약 5 mTorr 내지 약 1000 mTorr 범위의 챔버 압력이다. RF 전력은 13.56 MHz에서, 약 3 kW 내지 약 5 kW 범위의 연속 파형(CW) 또는 펄스 파형 플라즈마 전력에 의해 제공될 수 있다. 펄싱 중, 피크 RF 전력, 주파수 및 듀티 사이클은 통상적으로, 각각 약 10 W 내지 약 3000 W, 약 2 kHz 내지 약 100 kHz, 및 약 2 내지 약 50 %이다. 플라즈마 질화법은 약 1 내지 약 180 초간 수행될 수 있다. 일 실시예에서, 질소 가스는 약 200 sccm으로 제공되며, 약 1000 W의 RF 전력이 약 15 내지 약 180 초 동안 약 25 °C와 약 20 mTorr에서, 유도 플라즈마 소오스에 인가된 약 5 %의 듀티 사이클로 약 10 kHz에서 펄스된다.

- <30> 실리콘과 질소를 포함하는 층(202)이 질소 플라즈마에 노출된 이후에, 상기 층은 단계(110)에 도시된 바와 같이 추가로 어닐링된다. 도 2e에 도시한 바와 같이, 추가의 어닐링은 부분층(202b, 202c)이 부분층(202a, 202d)보다 높은 질소 농도를 갖도록 상기 층(202)의 질소 농도 프로파일을 변경시킨다. 부분층(202a)의 질소 농도를 감소시키는데에 따른 하나의 이득은 상기 층(202)과 실리콘 기판(200) 사이의 경계면에서 질소 농도를 감소시킨다는 점인데, 이는 층(202)이 게이트 유전체이고 상기 실리콘 기판이 게이트 트랜지스터의 실리콘 채널을 포함할 때 바람직한데, 그 이유는 게이트 유전체-실리콘 채널 경계면에서 질소 농도를 감소시키는 것에 의해 일정한 전하 밀도와 경계면 상태 밀도를 감소시키기 때문이다. 추가의 어닐링은 미국 산타클라라 소재의 어플라이드 머티리얼즈, 인코포레이티드로부터 모두 이용가능한 RADIANCE(등록 상표) 챔버 또는 RadiancePlus RTP 챔버와 같은 챔버 내에서 수행될 수 있다.

- <31> 일 실시예에서, 실리콘과 질소를 포함하는 층의 어닐링은 질소 분위기에서 희석된 O<sub>2</sub> 또는 저압 O<sub>2</sub>와 같은 저압 산화 분위기의 약산화 분위기에 상기 층을 노출시키는 단계를 포함하며, O<sub>2</sub> 부분압은 약 1 mTorr 내지 약 100 Torr 범위이다. 상기 층은 약 5 초 내지 약 180 초간 약 800 °C 내지 약 1100 °C 범위의 기판 온도에서 어닐링될 수 있다. O<sub>2</sub>는 약 500 sccm과 같은 약 2 sccm 내지 약 5000 sccm 범위의 유동률로 챔버의 내측으로 유입될 수 있다. 일 실시예에서, O<sub>2</sub>는 약 15 초간 약 0.1 Torr의 압력과 약 1000 °C의 온도에서 유지되는 동안에 약 500 sccm으로 제공된다.

- <32> 다른 실시예에서, 실리콘과 질소를 포함하는 층의 어닐링은 약 800 °C 내지 약 1100 °C 범위의 온도에서 질소, 아르곤, 또는 이들의 조합과 같은 불활성 가스에 상기 층을 노출시키는 단계를 포함한다.

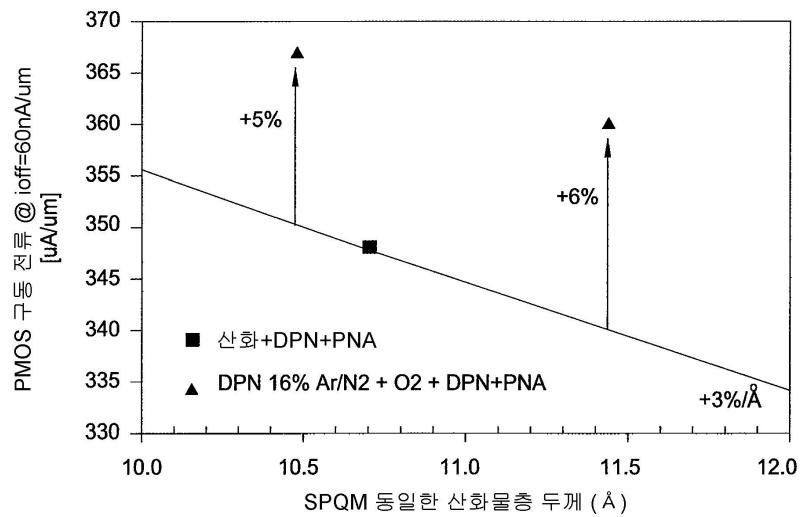

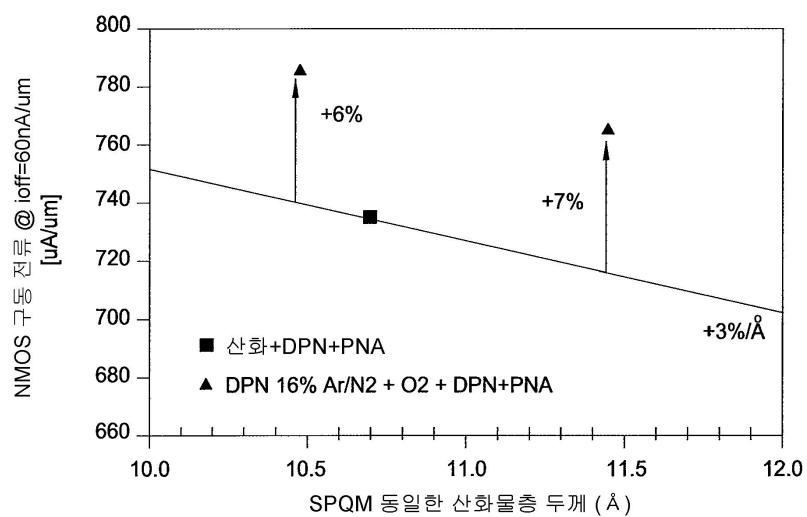

- <33> 도 3 및 도 4는 각각, 본 발명의 실시예에 따라 형성된 실리콘 산질화물 게이트 유전체 층을 포함하는 게이트 스택뿐만 아니라 본 발명의 다른 방법에 따라 형성된 실리콘 산질화물 게이트 유전체 층을 포함하는 게이트 스택을 위한 동일한 산화물 두께의 게이트 유전체 층에 대한 NMOS 구동 전류 및 동일한 산화물 두께의 유전체 층에 대한 PMOS 구동 전류를 나타낸다. 다른 방법에 따라 형성되는 게이트 유전체 층들은 실리콘 기판의 산화, 실리콘 기판의 플라즈마 질화(감결합 플라즈마 질화, DPN), 및 기판의 어닐링(후처리-질화 어닐링, PNA)을 포함하는 공정에 의해 형성된다. 본 발명에 따라 형성되는 게이트 유전체 층은 16% 아르곤/질소 플라즈마 내에서 실리콘 기판의 플라즈마 질화, 산소(O<sub>2</sub>) 존재하의 고온에서 기판의 어닐링, 질소 플라즈마 내에서 기판의 플라즈마 질화, 및 감압 산소 분위기하의 고온에서 기판의 어닐링을 포함하는 공정에 의해 형성된다.

- <34> 도 3 및 도 4는 실리콘 산화물 층의 단일 플라즈마 질화에 의해 형성된 게이트 유전체 층에 비해서, 본 발명의 실시예에 따른 게이트 유전체 층을 포함하는 NMOS 및 PMOS 장치에서 약 6%의 구동 전류가 개선되었음을 나타낸다. 또한, 본 발명에 따라 형성된 게이트 유전체 층은 아르곤 또는 다른 귀 가스를 포함하지 않는 질소 플라즈마 내에서의 실리콘 기판의 플라즈마 질화, 산소(O<sub>2</sub>) 존재하의 고온에서 기판의 어닐링, 질소 플라즈마 내에서 기판의 플라즈마 질화, 및 고온에서 기판의 어닐링을 포함하는 공정에 의해 형성되는 게이트 유전체 층을 포함하는 장치보다 약 3% 개선되었음을 알 수 있다. 기판의 제 1 플라즈마 질화 중에 질소 이외에 네온, 크립톤,

또는 제논과 같은 다른 다른 중불활성 가스 또는 아르곤을 포함하는 플라자를 사용하여 실리콘 기판과 실리콘 사이의 경계면과 그 위에 형성되는 질소 층, 예를 들어 실리콘 산질화물 층을 개선함으로써 구동 전류를 개선하는 것으로 여겨진다.

<35> 전술한 설명은 본 발명의 실시예들에 관한 것이지만, 본 발명의 다른 추가의 실시예들이 본 발명의 기본 범주로부터 이탈함이 없이 창안될 수 있으며, 본 발명의 범주는 이후의 청구의 범위에 의해 결정된다.

### 도면의 간단한 설명

- <11> 도 1은 본 발명의 실시예를 도시하는 흐름도이며,

- <12> 도 2a 내지 도 2e는 본 발명의 실시예에 따른 공정 시퀀스의 상이한 단계에서의 기판 구조를 개략적으로 도시하는 획단면도이며,

- <13> 도 3은 유전체 층의 동일한 산화물 두께(EOT)에 대한 본 발명의 실시예에 따른 유전체의 NMOS 구동 전류를 나타내는 그래프이며,

- <14> 도 4는 유전체 층의 동일한 산화물 두께(EOT)에 대한 본 발명의 실시예에 따른 유전체의 PMOS 구동 전류를 나타내는 그래프이다.

### 도면

#### 도면1

#### 도면2a

## 도면2b

## 도면2c

## 도면2d

## 도면2e

## 도면3

## 도면4