(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5858852号

(P5858852)

(45) 発行日 平成28年2月10日(2016.2.10)

(24) 登録日 平成27年12月25日(2015.12.25)

(51) Int.Cl.

H01L 33/48 (2010.01)

H01L 33/00 (2010.01)

F 1

H01L 33/00 400

H01L 33/00 J

請求項の数 5 (全 10 頁)

(21) 出願番号 特願2012-88287 (P2012-88287)

(22) 出願日 平成24年4月9日 (2012.4.9)

(65) 公開番号 特開2013-219167 (P2013-219167A)

(43) 公開日 平成25年10月24日 (2013.10.24)

審査請求日 平成26年10月30日 (2014.10.30)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(73) 特許権者 000131430

シチズン電子株式会社

山梨県富士吉田市上暮地1丁目23番1号

(74) 代理人 100126583

弁理士 宮島 明

(72) 発明者 荒井 秀和

山梨県富士吉田市上暮地1丁目23番1号

シチズン電子株式会社内

(72) 発明者 渡辺 茂久

山梨県富士吉田市上暮地1丁目23番1号

シチズン電子株式会社内

最終頁に続く

(54) 【発明の名称】 LEDモジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

回路基板上に複数のLEDダイを実装したLEDモジュールにおいて、少なくとも前記LEDダイの実装領域の中央部において前記LEDダイがひし形の格子状に配列し、

前記LEDダイの実装領域及び前記実装領域を囲むダム材が略円形であり、前記LEDダイが直列接続し一本のLED列を形成し、前記LED列が第1部分LED列と第2部分LED列からなり、前記第1部分LED列と前記第2部分LED列の接続点にバイパス回路が接続し、前記実装領域には前記第2部分LED列の一部が実装される実装部と、前記第2部分LED列の他の一部が実装される実装部があり、

前記第2部分LED列の二つの実装部で前記第1部分LED列の実装部を挟み込み、前記第1部分LED列の前記実装部と前記第2部分LED列の前記実装部が共通の対称軸を有する

ことを特徴とするLEDモジュール。

## 【請求項 2】

前記バイパス回路が第1電流入力端子と第2電流入力端子を備え、前記第1部分LED列と前記第2部分LED列の接続点に前記第1電流入力端子が接続し、前記第2部分LED列を流れる電流が前記第2電流入力端子に入力し、前記バイパス回路が前記第2電流入力端子に入力する電流により前記第1電流入力端子に入力する電流を制限していることを

特徴とする請求項1に記載のL E Dモジュール。

**【請求項3】**

前記バイパス回路は、ディプレッション型のFETと抵抗からなり、前記第1電流入力端子には前記FETのドレインが接続し、前記第2電流入力端子には前記FETのソースと前記抵抗の一端が接続し、前記FETのゲートと前記抵抗の他端の接続部から電流が流出することを特徴とする請求項2に記載のL E Dモジュール。

**【請求項4】**

前記バイパス回路に含まれる前記FETがペアチップであり、前記回路基板にダイボンディングされていることを特徴とする請求項3に記載のL E Dモジュール。

**【請求項5】**

前記L E D列に全波整流波形を印加することを特徴とする請求項1から4のいずれか一項に記載のL E Dモジュール。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、複数のL E Dダイを回路基板に実装したL E Dモジュールに関する。

**【背景技術】**

**【0002】**

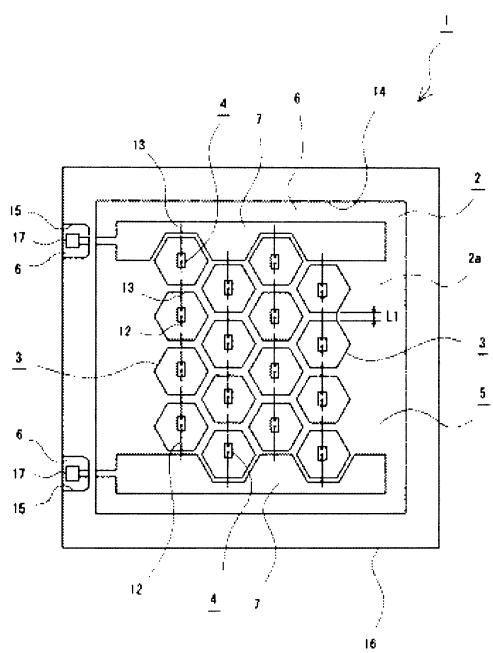

ウェハーから切り出したペアチップの半導体発光素子（以下L E Dダイと呼ぶ）を回路基板上に多数実装したL E Dモジュールが知られている。このL E Dダイは回路基板上において格子状に配列されることが多く、その格子形状は長方形であったり、ひし形であったりする。

**【0003】**

例えば特許文献1の図1にはL E Dダイがひし形の格子状に配列している発光体（L E Dモジュール）が示されている。特許文献1の図1を図5に再掲示し、発光体の構造を説明する。図5は発光体1の概略平面図である。L E Dペアチップ4（L E Dダイ）は図の上下方向に4本の列で配列しており、各列には4個のL E Dペアチップ4が含まれる。また各L E Dペアチップ4は図の横方向で近接しないように配置されている。このようにして各L E Dペアチップ4はひし形の格子を形成する。また各L E Dペアチップ4は、6角形の金属製のパッド3上にダイボンディングされている。このようにして発光体1は、金属製のパッド3により高い発光効率と良好な熱伝導性を備えながら、ひし形の格子配置にすることで高い実装密度を保持している。

**【0004】**

なお発光体1は各列ごとに4個づつワイヤ12, 13で直列接続している。このとき端部のL E Dペアチップ4は配線パターン7と接続している。またL E Dペアチップ4は矩形の被覆板16の収納部14に実装されており、被覆板16の切り欠き部16には電源端子17が形成されている。なお基板2（回路基板）はアルミ板上に絶縁層4を備えたものであり、各L E Dペアチップ4は透明樹脂5で被覆されている。

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】特開2010-238972号公報（図1）**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

図5に示したL E Dモジュール（発光体1）のようにL E Dダイ（各L E Dペアチップ4）の実装領域が略正方形であると、例えば図5の縦及び横方向が明るく、図の斜め方向が暗くなることが確認されている。すなわち図5に示したようなL E Dモジュール（発光体1）には配光ムラがある。

**【0007】**

10

20

30

40

50

そこで本発明は、上記課題に鑑みて為されたものであり、複数のLEDダイを回路基板に実装する際、発光効率を高くしても配光ムラが小さいLEDモジュールを提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明のLEDモジュールは、回路基板上に複数のLEDダイを実装したLEDモジュールにおいて、少なくとも前記LEDダイの実装領域の中央部において前記LEDダイがひし形の格子状に配列し、前記LEDダイの実装領域及び前記実装領域を囲むダム材が略円形であり、前記LEDダイが直列接続し一本のLED列を形成し、前記LED列が第1部分LED列と第2部分LED列からなり、前記第1部分LED列と前記第2部分LED列の接続点にバイパス回路が接続し、前記実装領域には前記第2部分LED列の一部が実装される実装部と、前記第2部分LED列の他の一部が実装される実装部があり、前記第2部分LED列の二つの実装部で前記第1部分LED列の実装部を挟み込み、前記第1部分LED列の前記実装部と前記第2部分LED列の前記実装部が共通の対称軸を有することを特徴とする。10

【0009】

本発明のLEDモジュールは、少なくともLEDダイを実装した領域の中央部においてLEDダイがひし形の格子状に配列している。つまり実装領域の中央部でLEDダイの配列がひし形の格子を形成していれば、実装領域全体にわたりLEDダイの配列が概ねひし形の格子状になる。このようにLEDダイを配置すると、LEDダイの側面から回路基板表面に沿うようにして出射する光線が、隣接するLEDダイの側面にあたりにくくなるため、回路基板面で効率よく反射し、LEDモジュールの発光効率が向上する。20

【0010】

このときLEDダイの実装領域を円形とすると配光ムラが軽減することを確認した。さらに本発明のLEDモジュールではLEDダイを直列接続しLED列を形成させている。このためLED列を折り曲げるようにして配置及び接続させることが可能になり、配置に関する自由度が増すことにより略円形の実装領域であっても実装可能となる。

【0012】

LED列全体に高い電圧を印加する場合、第1部分LED列と第2部分LED列がともに点灯する。これに対しLED列に低い電圧を印加した場合は、第1部分LED列からバイパス回路に電流が流れ、第1部分LED列のみが点灯する。このとき第2部分LED列の実装部が分割されているため、第1部分LED列の実装部をLED列全体の実装領域の中央部に配置できる。すなわちLED列に印加する電圧が低いときであっても発光分布の偏りを少なくできる。30

【0013】

前記バイパス回路が第1電流入力端子と第2電流入力端子を備え、前記第1部分LED列と第2部分LED列の接続点に前記第1電流入力端子が接続し、前記第2部分LED列を流れる電流が前記第2電流入力端子に入力し、前記バイパス回路が前記第2電流入力端子に入力する電流により前記第1電流入力端子に入力する電流を制限しても良い。

【0014】

前記バイパス回路は、ディプレッション型のFETと抵抗からなり、前記第1電流入力端子には前記FETのドレインが接続し、前記第2電流入力端子には前記FETのソースと前記抵抗の一端が接続し、前記FETのゲートと前記抵抗の他端の接続部から電流が流出するようにしても良い。40

【0015】

前記バイパス回路に含まれる前記FETがベアチップであり、前記回路基板にダイボンディングされていても良い。

【0016】

前記LED列に全波整流波形を印加しても良い。

**【発明の効果】****【0017】**

以上のように本発明のLEDモジュールは、複数のLEDダイを略ひし形の格子状に配列することにより発光効率を向上させている。このときLEDダイを直列接続し、これで形成したLED列を折り曲げるようにして各LEDダイを配置及び接続することにより、円形の実装領域にLEDダイを適切に配列し配光ムラを低減させることができる。

**【図面の簡単な説明】****【0018】**

【図1】本発明のLEDモジュールの外形図。

【図2】図1に示すLEDモジュールから蛍光樹脂を除いた状態の平面図。

10

【図3】図1に示すLEDモジュールの実体的な回路図。

【図4】図1に示すLEDモジュールの回路図。

【図5】従来例として示したLEDモジュールの概略平面図。

**【発明を実施するための形態】****【0019】**

以下、添付図1～4を参照しながら本発明の好適な実施形態について詳細に説明する。なお図面の説明において、同一または相当要素には同一の符号を付し、重複する説明は省略する。また説明のため部材の縮尺は適宜変更している。さらに特許請求の範囲に記載した発明特定事項との関係をカッコ内に記載している。

**【0020】**

20

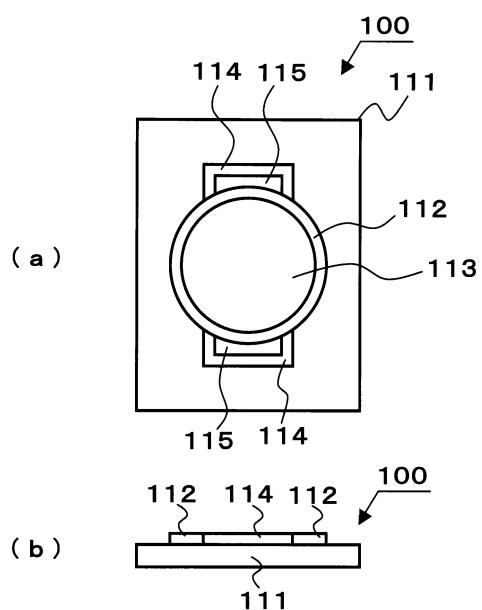

先ず図1によりLEDモジュール100の外観を説明する。図1はLEDモジュール100の外形図であり、(a)が平面図、(b)が正面図である。回路基板111上には円形のダム材112と一辺が欠けた矩形状のダム材114がある。ダム材112の内側の領域には蛍光樹脂113が充填され、ダム材112とダム材114で囲まれた領域には蛍光樹脂115が充填されている。なおダム材112とダム材114で囲まれた領域は図の上下2箇所にある。また回路基板111上の配線パターンは図示していない。

**【0021】**

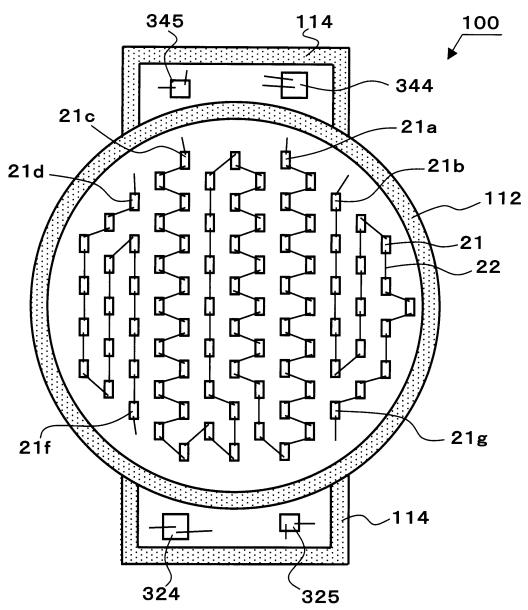

次に図2によりLEDモジュール100の電子部品の配置を説明する。図2は図1に示したLEDモジュール100から蛍光樹脂113, 115をとり除いた状態の平面図であり、ダム材112, 114の内側の領域を示している。なお回路基板111及び回路基板111上の配線パターンは図示していない。

30

**【0022】**

図2において、回路基板111上には83個のLEDダイ21（以下、個別のLEDダイについては必要に応じてサフィックスをつけて区別する）と、2個のFET324, 344（ペアチップ状態のディプレッション型のFET）と、2個の抵抗325, 345が搭載されている。LEDダイ21の実装領域は略円形であり、円形のダム材112により周囲を囲まれている。またFET324, 344と抵抗325, 345を実装した領域はダム材112の円弧とダム材114により囲まれている。なお回路基板111の配線パターン（図示せず）は上面（表面）だけに形成されており、回路基板111にスルーホールはない。

40

**【0023】**

LEDダイ21は $500\mu\text{m} \times 290\mu\text{m}$ 、FET324, 344は $1.5\text{mm} \times 1.5\text{mm}$ 、抵抗325, 345は $500\mu\text{m} \times 500\mu\text{m}$ である。回路基板111は熱伝導性と反射率を考慮してアルミナを使用した。図示していない配線パターンはAg上にNi, Pd, Auを積層している。ダム材112, 114はシリコーン樹脂からなり、太さが $0.7 \sim 1.0\text{mm}$ であり、高さが $0.5 \sim 0.7\text{mm}$ である。図1に示した蛍光樹脂113, 115は蛍光体を含有したシリコーン樹脂であり、厚さが $400 \sim 800\mu\text{m}$ 程度である。なお蛍光樹脂113の厚さはその変動が色度ずれを引き起こすので厳密に管理しなければならないが、これに比べ蛍光樹脂115の厚さは精度を緩くして良い。なおFET324, 344の被覆材を蛍光樹脂115としても光による誤動作はなかった。

50

**【0024】**

次に図1, 2を参照してLEDモジュール100の製造方法を説明する。まず回路基板111上にLEDダイ21、FET324, 344及び抵抗325, 345をダイボンディングし、その後ワイヤボンディングする。次にディスペンサで硬化前のダム材112, 114を配置し、ダム材112, 114を約150で硬化させる。LEDダイ21の実装領域では蛍光樹脂113の厚さを精度良く管理しなければならないためダム材112の外形も高精度に形成する必要がある。これに比べダム材114の精度は緩くて良い。最後にディスペンサでLEDダイ21の実装領域並びにFET324, 344及び抵抗325, 345の実装領域に蛍光樹脂113, 115を塗布する。蛍光樹脂113, 115の焼結温度は約150であり、焼結後の蛍光樹脂113の厚さばらつきは100μm以内が好ましい。10

**【0025】**

LEDダイ21を実装した領域の中央部では、近接しあう4個のLEDダイ21は、それぞれを頂点とし、図の縦方向に潰れたひし形をなすよう配列している。このひし形をセルとする格子配列は、実装領域の周辺部ではLEDダイ21がなくなるため当然周期性はなくなるが、これとは別に寸法調整のため周期性を失うこともある。なお全体的にLEDダイ21の配列がひし形格子を形成していれば、LEDダイ21の側面から回路111の表面に沿うようにして出射する光線が、図の横方向で隣接するLEDダイ21にあたりにくくなっているため、回路基板111(図示せず)の表面で効率よく反射し、LEDモジュール100の発光効率が向上する。このときLEDダイ21の実装領域を円形とすることにより配光ムラが軽減することを確認した。20

**【0026】**

LEDダイ21は回路基板111(図示せず)にダイボンディングされ、ワイヤ22により接続している。なおLEDダイ21a～gは一方のワイヤ22が配線パターン(図示せず)に接続している。LEDダイ21は全体で一本の直列接続したLED列を構成しており、このLED列のアノードはLEDダイ21cの一方のワイヤ22が相当し、カソードはLEDダイ21dの一方のワイヤ22が相当する。このときLEDダイ21fとLEDダイ21gは図示していない配線パターンで接続している。同様にLEDダイ21aとLEDダイ21bも図示していない配線パターンで接続している。30

**【0027】**

FET324は底面がドレインであり、導電性ペーストで配線パターン(図示せず)にダイボンディングされている。この配線パターンによりFET324のドレインはLEDダイ21a, 21bと接続している。FET324のゲートとソースはワイヤ22で図示していない別の配線パターンと接続する。抵抗325も回路基板111にダイボンディングされ、ワイヤ22で図示していない配線パターンと接続する。FET344も底面がドレインであり、導電性ペーストで配線パターン(図示せず)にダイボンディングされている。この配線パターンによりFET344のドレインはLEDダイ21dと接続している。FET344のゲートとソースはワイヤ22で図示していない別の配線パターンと接続する。抵抗345も回路基板111にダイボンディングされ、ワイヤ22で図示していない配線パターンと接続する。なおLEDダイ21及び抵抗325, 345の底面は絶縁されている。40

**【0028】**

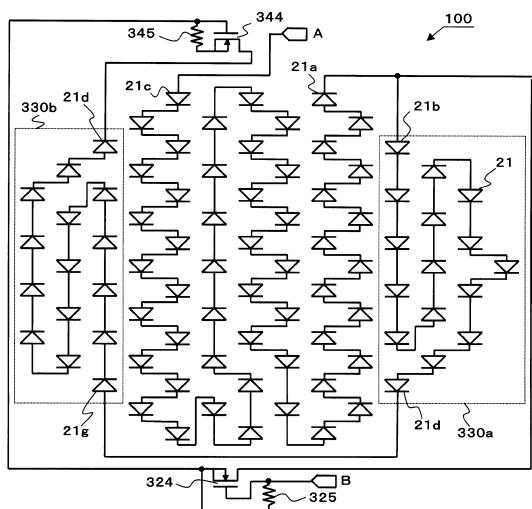

この接続状態を図3により説明する。図3は図1に示すLEDモジュール100の実体的な回路図であり、図2で示した電子部品と図3で示した電子部品は相対的な位置関係が一致している。あわせてLEDダイ21の向きも明示している。LEDダイ21は直列接続しており、LED列は、LEDダイ21cから始まり、途中LEDダイ21a, 21b, 21d, 21gを通り、LEDダイ21dで終わっている。LEDダイ21cからLEDダイ21aに至る部分(第1部分LED列、図4で示す部分LED列310)の実装部は実装領域全体の中央部にあり、LED21bからLED21dに至る部分LED列330a(第2部分LED列の一部、図4で示す部分LED列330の一部分)の実装部とL

50

ED21gからLED21dに至る部分LED列330b（第2部分LED列の他の一部、図4で示す部分LED列330の一部分）の実装部に挟まれている。FET324と抵抗325が図4で後述するバイパス回路320となり、FET344と抵抗345が図4で後述する電流制限回路340となる。端子A, Bはそれぞれ電流が流入及び流出する端子である。また図3において配線が交差していないため、図2の説明のなかで述べたように回路基板111（図1参照）にスルーホールを設けなくても良くなる。

#### 【0029】

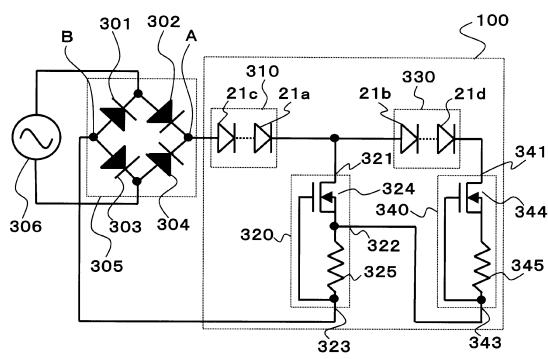

次に図4によりLEDモジュール100の動作について説明する。図4はLEDモジュール100と周辺回路の回路図である。なお図3の回路図と図4に示したLEDモジュール100の回路図は等価であり、各電子部品は共通の符号を用いている。また図4の回路には、LEDモジュール100とともにブリッジ整流回路305と商用交流電源306が書き加えられている。ブリッジ整流回路305は4個のダイオード301, 302, 303, 304からなり、端子Aが全波整流波形の出力端子であり、端子Bが基準電圧を与える端子となる。商用交流電源306はブリッジ整流回路305の入力端子に接続している。

10

#### 【0030】

LEDモジュール100は、部分LED列310（第1部分LED列）、部分LED列330（第2部分LED列）、バイパス回路320、電流制限回路340からなる。部分LED列310と部分LED列330とが直列接続しLEDモジュール100全体のLED列を構成する。部分LED列310内ではLEDダイ21c, 21aを含む多数のLEDダイ21（図2参照）が直列接続しており、同様に部分LED列330内でもLEDダイ21b, 21dを含む多数のLEDダイ21が直列接続している。部分LED列310のアノードはブリッジ整流回路305のA端子に接続している。部分LED列310, 330の接続部はバイパス回路320の電流入力端子321（第1電流入力端子）と接続している。部分LED列330のカソードは電流制限回路340の電流入力端子341に接続している。

20

#### 【0031】

バイパス回路320は、電流入力端子321（第1電流入力端子）、電流入力端子322（第2電流入力端子）、電流出力端子323を備えている。電流入力端子322は電流制限回路340の電流出力端子343と接続している。電流出力端子323はブリッジ整流回路305のB端子に接続している。バイパス回路320は、ディプレッション型のFET324及び抵抗325からなり、電流入力端子321にFET324のドレインが接続し、電流入力端子322にFET324のソースと抵抗325の一端が接続し、電流出力端子323にFET324のゲートと抵抗325の他端が接続している。またバイパス回路320は、電流入力端子322から流入する電流により電流入力端子321から流入する電流を制限する。

30

#### 【0032】

電流制限回路340は、バイパス回路320と略同じ回路構成であり、相違点はバイパス回路320の電流入力端子322に相当するものがないことだけである。FET344、抵抗345の結線もバイパス回路320と等しい。なおLEDダイ21の順方向電圧降下量が3V程度なので、部分LED列310の閾値は約150V、部分LED列330の閾値は約90Vとなり、LEDモジュール100は実効値が240Vとなる商用交流電源306に対応している。また抵抗345は、抵抗325よりも値が小さく、抵抗345と抵抗325の抵抗値の比を1:2にしている。

40

#### 【0033】

次に図4によりLEDモジュール100の点灯状況を説明する。全波整流波形の電圧が上昇し、部分LED列310の閾値を越えると、部分LED列310とバイパス回路320に電流が流れ部分LED列310が点灯する。このとき抵抗325からFET324のソースにフィードバックが掛かり、バイパス回路320は定電流動作する。さらに全波整流波形の電圧が上昇し、部分LED列310の閾値と部分LED列330の閾値の和より

50

も大きくなると、部分LED列330及び電流制限回路340にも電流が流れ始める。電流入力端子322に電流が入力するようになると、FET324はソース電圧が上昇し、ソース - ゲート間の電圧が広がるためカットオフする。このとき抵抗345からFET344にフィードバックがかかり、電流制限回路340は定電流動作する。このようにして部分LED列310と部分LED列330が点灯する。なお全波整流波形の電圧が下降する期間では、全波整流波形の電圧が上昇する期間の逆の過程を辿る。

#### 【0034】

LEDモジュール100は、LEDダイ21が長いLED列を形成しているため、この長いLED列を折り曲げるようにしてLEDダイ21を配置できるので、実装領域が円形であってもLEDダイを過不足なく配置できる。このようにして実装部を円形にしたことで配光ムラを改善していたが、さらにLEDモジュール100は部分LED列310と部分LED列330の実装部の割り振り方で配光分布を改善している。前述のように部分LED列330（図4参照）の実装部が二つに分かれしており（図3において部分LED列330aと部分LED列330bとして示していることに対応する）、部分LED列310（図4参照）の実装部が部分LED列330の二つの実装部に挟まれている。そして部分LED列310と部分LED列330の接続点にバイパス回路220が接続していた。このため全波整流波形の電圧が低いうちはLED列310が点灯し、実装領域全体の中央部が発光する。その後全波整流波形の電圧が上昇すると部分LED列330が点灯し実装領域全体が発光する。すなわち全波整流波形の低電圧位相でも高電圧位相でも配光分布が共通の対称軸をもっているため、LEDモジュール100が長いLED列を折り曲げるようにしてLEDダイ21を配置しても配光分布を劣化させていない。

#### 【0035】

またLEDモジュール100ではバイパス回路320がディプレッション型のFET324と抵抗325からなるだけであった（図4参照）。このため図3の説明のなかで述べたように配線を交差させないで回路図が描けるようになったため、回路基板111（図1参照）表面上の配線パターンとワイヤ22（図1参照）だけで各電子部品を接続でき、さらに電力供給用の端子A, B（図3参照）も確保できた。さらにバイパス回路320はLED列330（図4参照）を流れる電流がバイパス回路320の第2の電流入力端子322（図4参照）に入力し、第1の電流入力端子321（図4参照）から流れ込む電流を制限していたため、バイパス回路320には制御配線が存在しない。このことも回路基板111上の配線パターンを単純化するのに役立っている。

#### 【0036】

またLEDモジュール100ではFET324, 344と抵抗325, 345をダイボンディング及びワイヤボンディングで実装していた。FETや抵抗は表面実装用のチップ部品でも良いが、LEDモジュール100のような実装方式とすることにより、小型化を図ると共にLEDダイ21の実装方法と共に通化させることができる。なおLEDダイをフリップチップ実装しても良い。この場合は接続用のワイヤが不要になるため、ワイヤの影がなくなりLEDモジュールの発光効率が向上する。

#### 【符号の説明】

#### 【0037】

- 100...LEDモジュール、

- 111...回路基板、

- 112, 114...ダム材、

- 113, 115...蛍光樹脂、

- 21, 21a~g...LEDダイ、

- 22...ワイヤ、

- 301, 302, 303, 304...ダイオード、

- 305...ブリッジ整流回路、

- 306...商用交流電源、

- 310...部分LED列（第1部分LED列）、

10

20

30

40

50

3 2 0 … バイパス回路、

3 2 1 … 電流入力端子（第 1 電流入力端子）、

3 2 2 … 電流入力端子（第 2 電流入力端子）、

3 2 3 , 3 4 3 … 電流出力端子、

3 2 4 , 3 4 4 … F E T、

3 2 5 , 3 4 5 … 抵抗、

3 3 0 … 部分 L E D 列（第 2 部分 L E D 列）、

3 3 0 a , 3 3 0 b … 部分 L E D 列（第 2 部分 L E D 列の一部）、

3 4 0 … 電流制限回路、

3 4 1 … 電流入力端子。

10

【図 1】

【図 2】

【図3】

【 図 4 】

【図5】

---

フロントページの続き

審査官 村井 友和

(56)参考文献 特開2010-287657(JP,A)

国際公開第2011/020007(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64