(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4131544号

(P4131544)

(45) 発行日 平成20年8月13日(2008.8.13)

(24) 登録日 平成20年6月6日(2008.6.6)

(51) Int.Cl.

F 1

|             |           |

|-------------|-----------|

| H01L 25/00  | (2006.01) |

| H01L 25/065 | (2006.01) |

| H01L 25/07  | (2006.01) |

| H01L 25/18  | (2006.01) |

|            |

|------------|

| H01L 25/00 |

| H01L 25/08 |

|   |

|---|

| B |

| Z |

請求項の数 4 (全 10 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-37242 (P2004-37242)    |

| (22) 出願日  | 平成16年2月13日 (2004.2.13)        |

| (65) 公開番号 | 特開2005-228981 (P2005-228981A) |

| (43) 公開日  | 平成17年8月25日 (2005.8.25)        |

| 審査請求日     | 平成18年12月12日 (2006.12.12)      |

早期審査対象出願

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 899000079<br>学校法人慶應義塾<br>東京都港区三田2丁目15番45号            |

| (74) 代理人  | 100110191<br>弁理士 中村 和男                               |

| (72) 発明者  | 黒田 忠広<br>神奈川県横浜市港北区日吉3-14-1<br>慶應義塾大学 理工学部内          |

| (72) 発明者  | 溝口 大介<br>神奈川県横浜市港北区日吉3-14-1<br>慶應義塾大学 理工学部内          |

| (72) 発明者  | ユスマラズ ピンティ ユスフ<br>神奈川県横浜市港北区日吉3-14-1<br>慶應義塾大学 理工学部内 |

最終頁に続く

(54) 【発明の名称】電子回路

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上の配線により形成され、送信回路に接続される第1コイルを有する第1基板と、

基板上の配線により前記第1コイルと対応する位置に形成され第1コイルと誘導結合し、

第1受信回路に接続される第2コイルを有する第2基板と、

基板上の配線により前記第1及び第2コイルと対応する位置に形成され第1及び第2コ

イルと誘導結合し、第2受信回路に接続される第3コイルを有する第3基板と

を第1基板から第3基板の順に積層して備え、

前記送信回路は、送信ディジタル信号の0から1への変化に応じて前記第1コイルの一

端を第1電位から第2電位に変化させて所定時間遅れて他端を第1電位から第2電位に変

化させ、送信ディジタル信号の1から0への変化に応じて前記第1コイルの一端を第2電

位から第1電位に変化させて所定時間遅れて他端を第2電位から第1電位に変化させ、

前記送信回路が送信するディジタル信号を前記第1及び第2受信回路が受信することを

特徴とする電子回路。

## 【請求項 2】

基板上の配線により形成され、送信回路に接続される第1コイルを有する第1基板と、

基板上の配線により前記第1コイルと対応する位置に形成され第1コイルと誘導結合し、

第1受信回路に接続される第2コイルを有する第2基板と、

基板上の配線により前記第1及び第2コイルと対応する位置に形成され第1及び第2コ

イルと誘導結合し、第2受信回路に接続される第3コイルを有する第3基板と

を第1基板から第3基板の順に積層して備え、

前記送信回路は、前記第1コイルの一端を送信ディジタル信号に応じて2つの電位に選択的に接続し、他端を該2つの電位の中間の電位に保持し、

前記送信回路が送信するディジタル信号を前記第1及び第2受信回路が受信することを特徴とする電子回路。

【請求項3】

前記第1及び第2受信回路は、前記第2及び第3コイルの両端をそれぞれ所定の1つの電圧源に接続する2つの抵抗を有することを特徴とする請求項1又は2記載の電子回路。

【請求項4】

前記第1コイルは、前記第2及び第3コイルよりも小さいことを特徴とする請求項1乃至3いずれかに記載の電子回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、I C (Integrated Circuit) ベアチップやP C B (プリント基板) などの基板間の通信を好適に行うことができる電子回路に関する。

【背景技術】

【0002】

近年における電子機器は、ますます小型化、高機能化されており、これに伴い、内蔵されるL S I (Large Scale Integration) も小型化、高速化が進行している。小型化、高速化を実現する手段として、1パッケージにシステムの全機能を含めることが望まれ、現在、この実現方法として大まかに2種類の方法がある。

【0003】

第1の方法としては、一つのベアチップにシステム全てを搭載するシステムオンチップ(SoC)と呼ばれる方式である。この方式は、異なるプロセス技術を一つのベアチップ上で実現することと、チップ面積の増大による歩留まりの低下により、コストが高くなる。

【0004】

第2の方法として、1パッケージに複数のベアチップを封入するシステムインパッケージ(SiP)という方法がある。この手法は、異なるプロセスで製造される機能を別チップで実現するため、ベアチップ当たりの歩留まりが高く、低コスト化が期待できる。ただし、異なるチップ間の相互接続をする必要が生じ、接続手法は3種類存在する。

【0005】

SiPにおける相互接続の第1の方法は、従来通り、ワイヤボンディングを用いる方法である。この場合、チップ間の接続本数は従来のパッケージと同じか、それ以下となり、通信バンド幅に問題が生じる。また、実装面積を低減させる際には、3次元実装が不可欠であるが、ワイヤボンディング方式では上に積み上げられるチップを小さくする必要があり、実装面積が制限される上に、1対1の接続が主であるためバスの形成が困難である。

【0006】

SiPにおける相互接続の第2の方法は、チップを3次元実装し、マイクロバンプで接続する方法である。この方法は、2チップの対面実装まではコストが低いが、3チップ以上の実装となると、スルーホールと呼ばれる、チップ自体又はビルトアップ基板を貫通する通信路を物理的に製造する必要があり、専用のプロセス技術と高い加工精度を求められ、コストが高くなる。

【0007】

SiPにおける相互接続の第3の方法は、チップを3次元実装し、チップ間を容量性結合により電気的に接続する方法である。この方法は2チップまでの対面実装ではコストが低く高速通信が可能であるが、3チップ以上では信号の伝送効率が急激に悪化し、消費電力が増大する。

【0008】

このため、アンテナによってチップ間通信を行うことが提案されている(例えば、特許

10

20

30

40

50

文献 1 参照)。

【特許文献 1】特開平 11 - 68033 号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし、このアンテナによる場合でも、3チップ以上を実装してチップをまたがって信号を伝送しようとすると、アンテナによって発生する電界が誘電率の異なる多数の物質(バイアスされたシリコン基板、ドープされたシリコン、酸化膜、窒化膜等)を貫通しなければならず、境界面で反射が生じ、伝送効率が悪化してしまう。

【0010】

本発明は、上記問題点に鑑み、3以上の基板を3次元実装して基板をまたがって信号を伝送する場合でも効率良く信号を伝送することができる電子回路を提供することを目的とする。この基板には I C ベアチップや P C B が含まれる。

【課題を解決するための手段】

【0011】

本発明の電子回路は、基板上の配線により形成され、送信回路に接続される第 1 コイルを有する第 1 基板と、基板上の配線により前記第 1 コイルと対応する位置に形成され第 1 コイルと誘導結合し、第 1 受信回路に接続される第 2 コイルを有する第 2 基板と、基板上の配線により前記第 1 及び第 2 コイルと対応する位置に形成され第 1 及び第 2 コイルと誘導結合し、第 2 受信回路に接続される第 3 コイルを有する第 3 基板とを第 1 基板から第 3 基板の順に積層して備え、前記送信回路は、送信デジタル信号の 0 から 1 への変化に応じて前記第 1 コイルの一端を第 1 電位から第 2 電位に変化させて所定時間遅れて他端を第 1 電位から第 2 電位に変化させ、送信デジタル信号の 1 から 0 への変化に応じて前記第 1 コイルの一端を第 2 電位から第 1 電位に変化させて所定時間遅れて他端を第 2 電位から第 1 電位に変化させ、前記送信回路が送信するデジタル信号を前記第 1 及び第 2 受信回路が受信する。

【0012】

また、本発明の電子回路は、基板上の配線により形成され、送信回路に接続される第 1 コイルを有する第 1 基板と、基板上の配線により前記第 1 コイルと対応する位置に形成され第 1 コイルと誘導結合し、第 1 受信回路に接続される第 2 コイルを有する第 2 基板と、基板上の配線により前記第 1 及び第 2 コイルと対応する位置に形成され第 1 及び第 2 コイルと誘導結合し、第 2 受信回路に接続される第 3 コイルを有する第 3 基板とを第 1 基板から第 3 基板の順に積層して備え、前記送信回路は、前記第 1 コイルの一端を送信デジタル信号に応じて 2 つの電位に選択的に接続し、他端を該 2 つの電位の中間の電位に保持し、前記送信回路が送信するデジタル信号を前記第 1 及び第 2 受信回路が受信する。

【0013】

また、前記第 1 及び第 2 受信回路は、前記第 2 及び第 3 コイルの両端をそれぞれ所定の 1 つの電圧源に接続する 2 つの抵抗を有することで、信号受信時に受信コイル両端に生じる電圧振幅の中心電圧を、信号増幅に最適な電圧値とすることができます。

【0014】

また、前記第 1 コイルは、前記第 2 及び第 3 コイルよりも小さいことを特徴とする。

【発明の効果】

【0016】

本発明によれば、3以上の基板を3次元実装して基板をまたがって信号を伝送する場合でも効率良く信号を伝送できる。

【0017】

また、通信が電流駆動によるものであるので、低電圧駆動の需要が大きい L S I 等に適用して好適である。

【発明を実施するための最良の形態】

【0018】

10

20

30

40

50

以下、添付図面を参照しながら本発明の好適な実施の形態について詳細に説明する。

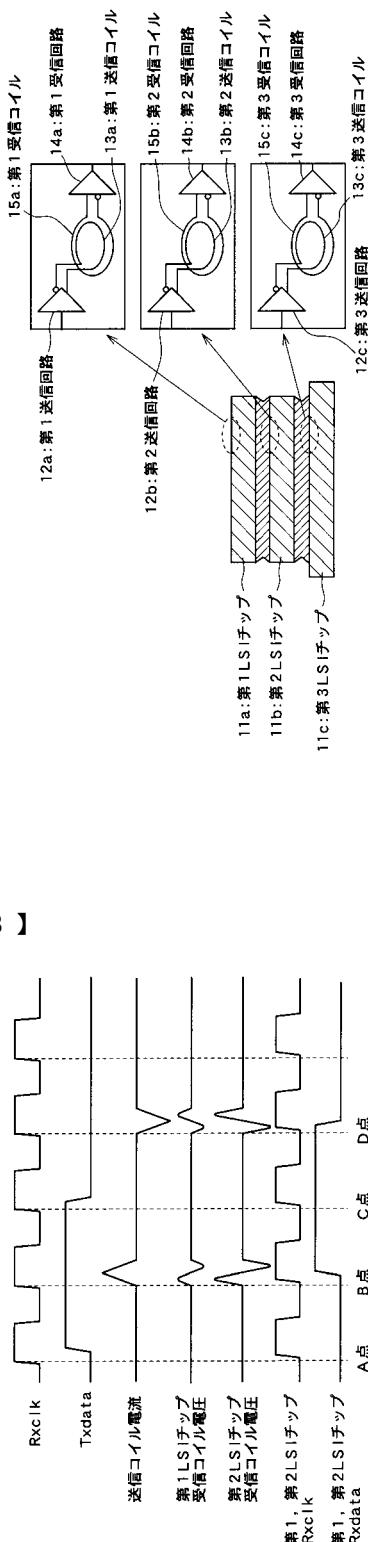

#### 【0019】

図1は、本発明の一実施の形態による電子回路の構成を示す図である。本実施の形態の電子回路は、第1LSIチップ11a、第2LSIチップ11b、及び第3LSIチップ11cから成る。LSIチップが3層にスタックされ、3チップにまたがるバスを形成する例である。第1～第3LSIチップ11a、11b、11cが縦に積まれ、各チップは接着剤で互いに固定されている。第1～第3LSIチップ11a、11b、11c上には、それぞれ、送信に用いる第1～第3送信コイル13a、13b、13cが配線により形成され、また、それぞれ、受信に用いる第1～第3受信コイル15a、15b、15cが配線により形成される。これら3ペアの送受信コイル13、15の開口の中心が一致するように、第1～第3LSIチップ11a、11b、11c上で配置されている。これにより、3ペアの送受信コイル13、15は誘導性結合を形成し、通信が可能となる。第1～第3送信コイル13a、13b、13cにはそれぞれ第1～第3送信回路12a、12b、12cが接続され、第1～第3受信コイル15a、15b、15cにはそれぞれ第1～第3受信回路14a、14b、14cが接続される。送受信コイル13、15は、プロセス技術の多層配線を利用し、通信に許される面積内で、3次元的に1回巻き以上のコイルとして実装される。送受信コイル13、15には、通信に最適な形状が存在し、最適な巻き数、開口、線幅をとる必要がある。一般的に、送信コイル13が受信コイル15より小さい。

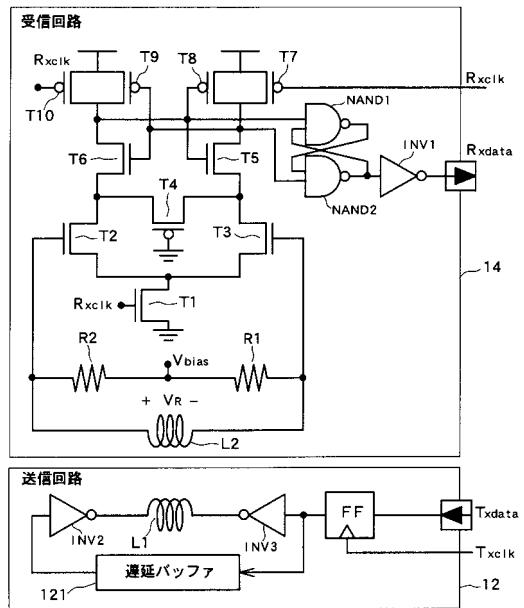

#### 【0020】

図2は、本実施の形態における送信回路及び受信回路の具体的構成を示す図である。本実施の形態の送信回路12は、記憶素子FF、遅延バッファ121、第1送信用バッファINV2、及び第2送信用バッファINV3から成る。L1は送信コイル13である。送信回路12は、入力として送信クロック(同期信号)Txclkと、これに同期した送信データTxdataを取り。入力される送信データTxdataは記憶素子FFに保持され、第1、第2送信用バッファINV2、INV3に入力される。ただし、第1送信用バッファINV2の前には、遅延素子である遅延バッファ121が設けられ、第1送信用バッファINV2と第2送信用バッファINV3への入力時間に差ができるように構成されている。第1送信用バッファINV2と第2送信用バッファINV3の出力は送信コイルL1の両端にそれぞれ接続される。この構成により、送信データに変化が生じた場合のみに、遅延バッファ121の信号伝播遅延時間だけコイルL1へ電流が流れる。受信コイル15の受信電圧が最大となり、かつ、受信タイミングのマージンを大きくするため、送信コイルL1へ流れる電流波形が三角波となるよう、第1、第2送信用バッファINV2、INV3の駆動力を設定する。

#### 【0021】

受信回路14は、トランジスタT1～T10、抵抗R1、R2、 NAND回路NAND1、NAND2、及び受信用バッファINV1から成り、全体としてラッチつき差動アンプを構成している。L2は受信コイル15である。外部から受信クロック(同期信号)Rxclkをとり、受信データRxdataを出力する。トランジスタT2、T3が差動アンプの差動対をなし、受信コイルL2からの信号を受ける。トランジスタT2、T3に接続されている受信コイルL2の両端は抵抗R1、R2を通りバイアス電圧Vbiasに接続されている。これにより、信号受信時に受信コイルL2両端に生じる電圧振幅の中心電圧を、信号増幅に最適な電圧値Vbiasとすることができる。トランジスタT2、T3のソース端子は、テイル電流源発生用トランジスタT1に接続される。トランジスタT1のソース端子は接地され、ゲート端子へは受信クロックRxclkが入力される。トランジスタT2、T3のドレイン側では、トランジスタT5とトランジスタT8、及び、トランジスタT6とトランジスタT9がそれぞれインバータを形成し、この2つのインバータがループ状に接続されている。インバータを繋ぐ配線が、NAND回路NAND1、NAND2へ入力され、NAND回路NAND1、NAND2はラッチを形成している。差動アンプで受信したデータはトランジスタT1へ入力される受信クロックRxclkに同期して値が変化し、NAND回路NAND1、NAND2に

より、値の変化があったときのみ、受信信号をデジタルデータとして値を取り込み、入力値の変化がない間は値を保持する。差動アンプのプリチャージと、受信クロック Rxclk が L (ロー) の期間のラッチの値保持のために、トランジスタ T7、T10 が接続されている。このトランジスタ T7、T10 が発生するノイズの影響で、受信コイル L2 からの受信信号の変化がないにもかかわらず、受信データ Rxdata の値が反転するのを防ぐために、トランジスタ T4 が接続される。

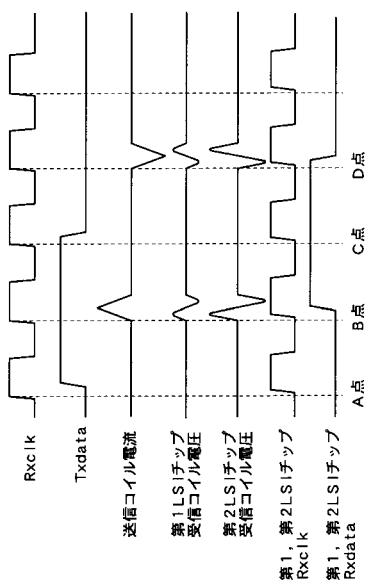

#### 【0022】

図 3 は、本実施の形態の動作を説明する波形を示す図である。図 1 に示す第 3 LSI チップ 11c 上の第 3 送信回路 12c から、この上に存在する第 1、第 2 LSI チップ 11a、11b 上の第 1、第 2 受信回路 14a、14b へデータの送信をする場合の動作説明を行う。例として、送信データ Txdata として「... L L H H L L ...」というデータ送信を行った際の動作について説明する。第 3 LSI チップ 11c 上の第 3 送信回路 12c は、値の送信時に送信クロック Rxclk と、これに同期した送信データ Txdata を入力する。まず、送信データ Txdata として L (ロー) が入力されている状態では、第 1、第 2 送信用バッファ INV2、INV3 の出力は共に H (ハイ) を保持した定常状態となっている。第 1、第 2 LSI チップ 11b、11c 上の第 1、第 2 受信回路 14a、14b は、L が連続されて入力された状態では、受信データ Rxdata に L が出力されている状態で定常状態となっている。

#### 【0023】

この状態から、送信データ Txdata が A 点の時間に L から H に変化する。この信号が B 点で記憶素子 FF に取り込まれ、すぐに第 2 送信用バッファ INV3 に入力される。ここで第 2 送信用バッファ INV3 の出力は L となるが、第 1 送信用バッファ INV2 の出力は H のままであり、電流が第 1 送信用バッファ INV2 から第 2 送信用バッファ INV3 に向かい流れる。この後、遅延バッファ 121 の遅延時間の後、第 2 送信用バッファ INV3 の出力が H となり、第 1 送信用バッファ INV2 と第 2 送信用バッファ INV3 の出力が等電位となり電流の流れが止まる。この際に、電流波形が「送信コイル電流」 B 点に示すような 3 角波となるよう第 1、第 2 送信用バッファ INV2、INV3 の駆動力を設定しておく。

#### 【0024】

「送信コイル電流」の B 点～C 点における電流変化により、第 1、第 2 LSI チップ 11a、11b 上に配置されている受信コイル L2 には「第 1 LSI チップ受信コイル電圧」、「第 2 LSI チップ受信コイル電圧」に示される電圧が生じる。この電圧の振れの中心電圧は Vbias である。第 1 LSI チップ 11a は第 2 LSI チップ 11b より第 3 LSI チップ 11c から遠いため、生じる電圧が低くなる。これらの電圧変化をラッチ付き差動アンプにより増幅し、ラッチで値を保持することにより、「第 1、第 2 LSI チップ Rxdata」 B 点に示すデジタルデータとする。

#### 【0025】

第 3 LSI チップ 11c 上の送信データ Txdata は B 点では H を保持し、変化していない。この場合、C 点における送信コイル L1 への入力は変化せず、第 1、2 LSI チップ 11a、11b 上の受信コイル L2 の電圧も変化を起こさず、出力データ Rxdata は保持される。

#### 【0026】

第 3 LSI チップ 11c 上の送信データ Txdata が C 点のように H から L に遷移した場合、D 点で記憶素子 FF に取り込まれ、直ちに第 2 送信用バッファ INV3 への入力が H から L に変化し、その出力は L から H へと遷移する。このとき、第 1 送信用バッファ INV2 の出力は、遅延バッファ 121 により L から H への変化が遅れ、第 2 送信用バッファ INV3 から第 1 送信用バッファ INV2 へ電流が流れる。この後、遅延バッファ 121 の遅延時間の後、第 1 送信用バッファ INV2 の出力が H となり第 1 送信用バッファ INV2 と第 2 送信用バッファ INV3 の出力電圧が等しくなり、電流がとまる。この一連の送信電流の変化が「送信コイル電流」 D 点のように、B 点における 3 角波形の逆の極性を

10

20

30

40

50

とる3角波となるよう第1、第2送信用バッファIN V2、IN V3の駆動力を設定しておく。

#### 【0027】

第3LSIチップ11c上の送信コイルL1の電流変化により、「第1LSIチップ受信コイル電圧」、「第2LSIチップ受信コイル電圧」のD点の波形が第1、2LSIチップ11a、11b上の受信コイルL2に発生する。この電圧変化を差動アンプで増幅し、ラッチでデジタルデータに変換することにより、「第1、第2LSIチップRxdata」D点のデジタル受信信号を得る。

#### 【0028】

以上、本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。10

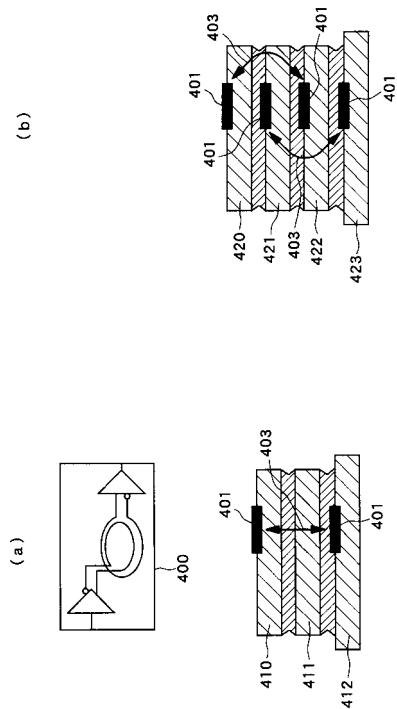

#### 【0029】

例えば、バス接続ではなく1対1接続も可能であり、この場合の接続例を図4(a)に示す。図4(a)は、第1～第3LSIチップ410～412から成るスタックトLSIを横から見た図である。送受信回路401の内容を送受信回路400として示している。矢印403は誘導性結合を表す。

#### 【0030】

また、多対多の接続も可能であり、この場合の接続例を図4(b)に示す。図4(b)は、第1～第4LSIチップ420～423から成るスタックトLSIを横から見た図である。この場合には、第1LSIチップ420と第3LSIチップ422との通信、及び、第2LSIチップ421と第4LSIチップ423との通信と同じ水平位置において行うものである。すなわち、送信回路と受信回路の複数の組合せが同じ空間を使って独立に誘導性結合しているものである。同じ水平位置で誘導性結合させるものであるので、例えば時分割するなどしてそれぞれの通信を漏話なく行う。20

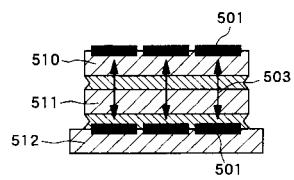

#### 【0031】

これらのように縦方向の接続の拡張だけでなく、横方向も接続を拡張可能であり、並列に通信をしてバンド幅を増やした例を図5に示す。図5は、第1～第3LSIチップ510～512から成るスタックトLSIを横から見た図である。送受信回路501は図4に示す送受信回路400と同じものである。矢印503は誘導性結合を表し、並列に複数の結合を確立している様子を表している。30

#### 【0032】

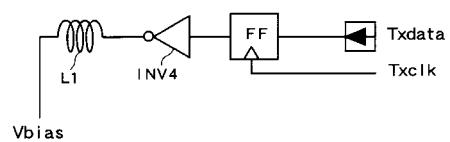

また、接続方式だけではなく、送受信回路も変更可能である。送信回路は、消費電力は増加してしまうが、回路規模を小さくすることを主眼とすると、図6の構成をとることができる。図6に示す送信回路は、記憶素子FF、送信用バッファIN V4、及びバイアス電圧Vbiasの電圧源から成る。送信データTxdataは、記憶素子FFに保持され、送信用バッファIN V4を介して送信コイルL1に入力される。送信コイルL1の他端はバイアス電圧Vbiasに接続される。バイアス電圧Vbiasを送信データのL、Hの中間の電圧にしておくと、送信コイルL1には絶えず正負いずれかの電流が流れているが、送信データTxdataが変化する時に送信コイルL1に流れる電流が反転して、信号が伝送される。40

#### 【0033】

また、受信回路は、受信クロックに同期して受信信号を受けるはずである周期的な所定の期間の信号だけを受信するようにすることで、クロックによる雑音等を除去してS/N比を高くすることができる。

#### 【図面の簡単な説明】

#### 【0034】

【図1】本発明の一実施の形態による電子回路の構成を示す図である。

【図2】本実施の形態における送信回路及び受信回路の具体的構成を示す図である。

【図3】本実施の形態の動作を説明する波形を示す図である。

【図4】本発明の他の実施の形態による電子回路の構成を示す図である。50

【図5】本発明の更に他の実施の形態による電子回路の構成を示す図である。

【図6】本発明の他の実施の形態における送信回路の具体的構成を示す図である。

【符号の説明】

【0035】

1 1 L S I チップ

1 2 送信回路

1 3 送信コイル

1 4 受信回路

1 5 受信コイル

4 0 0、4 0 1 送受信回路

10

4 0 3 誘導性結合

4 1 0、4 1 1、4 1 2、4 2 0、4 2 1、4 2 2、4 2 3 L S I チップ

5 0 1 送受信回路

5 0 3 誘導性結合

5 1 0、5 1 1、5 1 2 L S I チップ

F F 記憶素子

I N V バッファ

N A N D ナンド回路

L コイル

T トランジスタ

20

R xclk 受信クロック

R xdata 受信データ

T xclk 送信クロック

T xdata 送信データ

V bias バイアス電圧

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 三浦 典之

神奈川県横浜市港北区日吉3-14-1 慶應義塾大学 理工学部内

(72)発明者 櫻井 貴康

東京都世田谷区宮坂2-21-15

審査官 今井 拓也

(56)参考文献 特開2002-368118(JP,A)

特開2002-252324(JP,A)

特開2000-124406(JP,A)

特開平11-068033(JP,A)

鬼塚浩平 外1名, チップ間ワイヤレス電源伝送に関する検討, 2003年電子情報通信学会基礎・境界ソサイエティ大会講演論文集, 日本, 2003年 9月18日, p.3

神田浩一 外5名, 1.27Gb/s/pin, 3mW/pin Wireless Superconnect(WSC) Interface Scheme, 電子情報通信学会技術研究報告, 日本, 社団法人電子情報通信学会, 2003年 5月21日, Vol.103, No.88, p.19-22

(58)調査した分野(Int.Cl., DB名)

H01L 25/00

H01L 25/065

H01L 25/07

H01L 25/18