(1) Publication number:

0 347 250 B1

# **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication of patent specification: 29.09.93 (51) Int. Cl. 5 G04C 3/14, G04C 21/00

21) Application number: 89306145.7

② Date of filing: 16.06.89

54 Electronic alarm watch.

Priority: 17.06.88 JP 150862/88

17.06.88 JP 150873/88

14.07.88 JP 176040/88

- Date of publication of application:20.12.89 Bulletin 89/51

- Publication of the grant of the patent:29.09.93 Bulletin 93/39

- Designated Contracting States:

CH DE FR GB LI

- References cited:

EP-A- 0 216 171

US-A- 4 253 172

US-A- 4 470 707

PATENT ABSTRACTS OF JAPAN, vol. 9, no. 157 (P-369)[1880], 2nd July 1985; & JP-A-60 33 081 (SEIKOUSHIYA K.K.) 20-02-1985

Proprietor: SEIKO EPSON CORPORATION 4-1, Nishishinjuku 2-chome Shinjuku-ku Tokyo-to(JP)

Inventor: Kawaguchi, Takashi c/o Seiko Epson Corporation

3-5, Owa 3-chome

Suwa-shi Nagano-ken(JP)

Inventor: Yabe, Hiroshi c/o Seiko Epson Cor-

poration

3-5, Owa 3-chome

Suwa-shi Nagano-ken(JP)

Inventor: Maruyama, Akihiko c/o Seiko Epson

Corporation 3-5, Owa 3-chome

Suwa-shi Nagano-ken(JP)

Inventor: Yoshino, Masato c/o Seiko Epson

Corporation

3-5, Owa 3-chome

Suwa-shi Nagano-ken(JP)

Representative: Miller, Joseph et al J. MILLER & CO. 34 Bedford Row, Holborn London WC1R 4JH (GB)

Note: Within nine months from the publication of the mention of the grant of the European patent, any person may give notice to the European Patent Office of opposition to the European patent granted. Notice of opposition shall be filed in a written reasoned statement. It shall not be deemed to have been filed until the opposition fee has been paid (Art. 99(1) European patent convention).

10

15

20

25

30

35

40

50

55

## **Description**

This invention relates to electronic alarm watches.

A prior art analog electronic watch with alarm such as disclosed in EP-A-0 216 171 includes an alarm ringing mode and an alarm non-ringing mode. In the alarm ringing mode, the alarm set time is retained even after the alarm rings, so that the alarm again rings when a predetermined period of time, usually twelve hours, has passed after the alarm rang and when the alarm set time coincides again with current time.

With such an electronic alarm watch, if the alarm is not to be rung after ringing once, the alarm ringing must be prohibited by external operation of a switch or the like. Then, when setting the alarm again in an alarm ringing prohibited state, that state must be released, thus involving complication in operation.

If a timer like use is desired for ringing the alarm about 10 minutes later, for example, a user must calculate the time by adding 10 minutes to current time and then set the alarm by the time, which is a rather troublesome procedure.

The invention seeks to overcome such problems. Its object is to simplify necessary operation by omitting an operation for prohibiting an alarm from ringing when the alarm is not to be rung again after the alarm rang, and an operation for releasing a ringing prohibited state of the alarm when setting the alarm again. It enables a reduction of one external operating member, ensures a multi-function of the alarm, and simplifies a timer like use of the alarm function.

According to the invention, an electronic alarm watch having a plurality of step motors, at least one pointer or hand driven by each step motor, external operating means, alarm ringing means and alarm controlling means, is characterised in that one or a plurality of pointers or hands indicate current time in the state when an alarm is not set, in that such pointers indicate an alarm set time when and after the alarm is set, and in that after the alarm rings, such pointers or hands are driven to indicate current time again, with the alarm free from being set.

Other aspects of the invention are defined in claims 2 to  $6. \,$

The invention is described further, by way of example, with reference to the accompanying drawings, in which:-

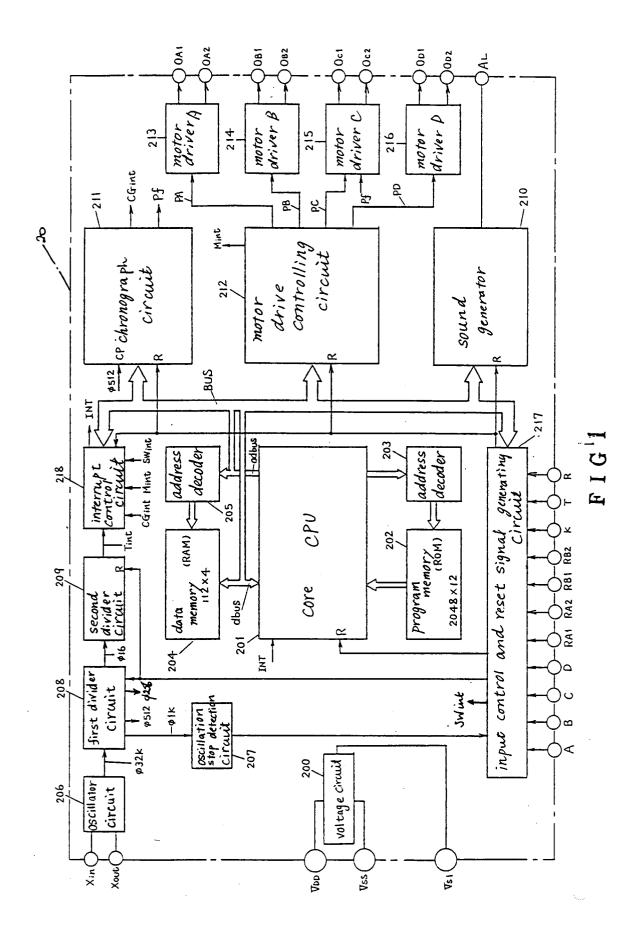

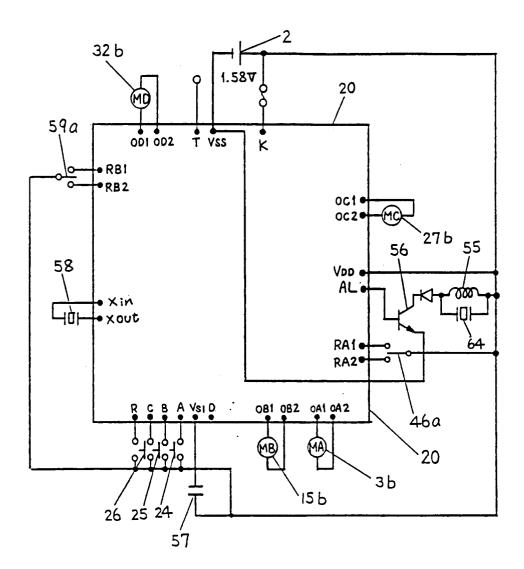

Figure 1 is a block diagram representing an IC chip for an analog electronic watch in one embodiment of the invention;

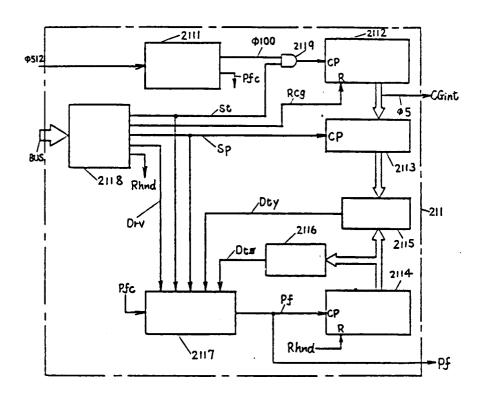

Figure 2 is a block diagram representing a chronograph circuit forming part of the circuit of Figure 1;

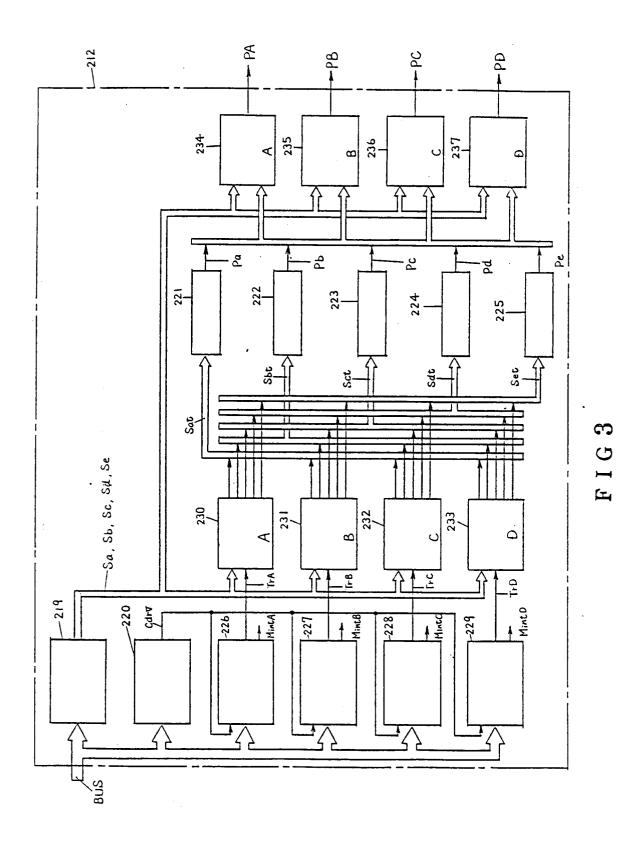

Figure 3 is a block diagram representing a motor drive controlling circuit forming part of the circuit of Figure 1;

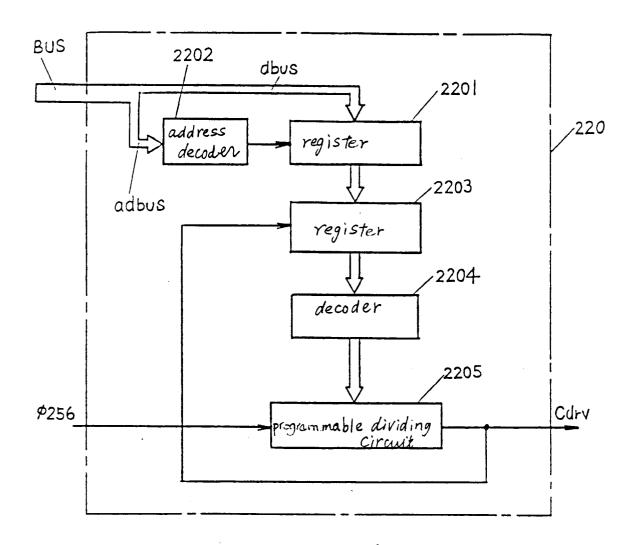

Figure 4 is a block diagram representing a drive reference signal forming circuit forming part of the circuit of Figure 3;

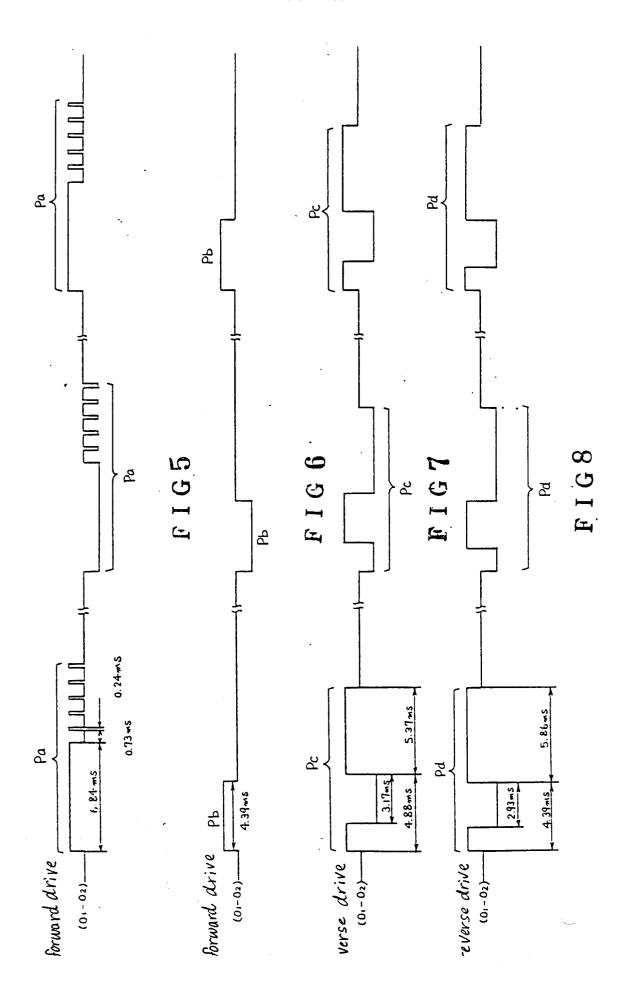

Figures 5, 6, 7 and 8 are timing charts of motor driving pulses generated from first, second, third and fourth driving pulse shaping circuits respectively, forming part of the circuit of Figure 3;

Figure 9 is a block diagram representing one of four motor clock control circuits forming part of the circuit of Figure 3;

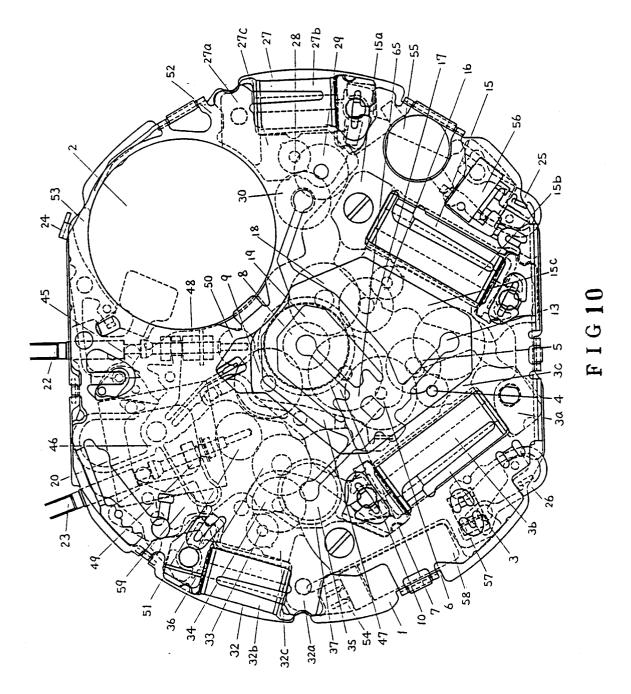

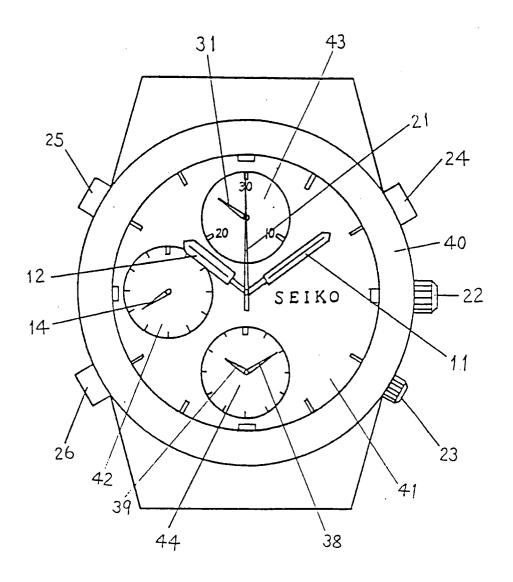

Figure 10 is a plan view of one embodiment of an analog electronic watch according to the invention:

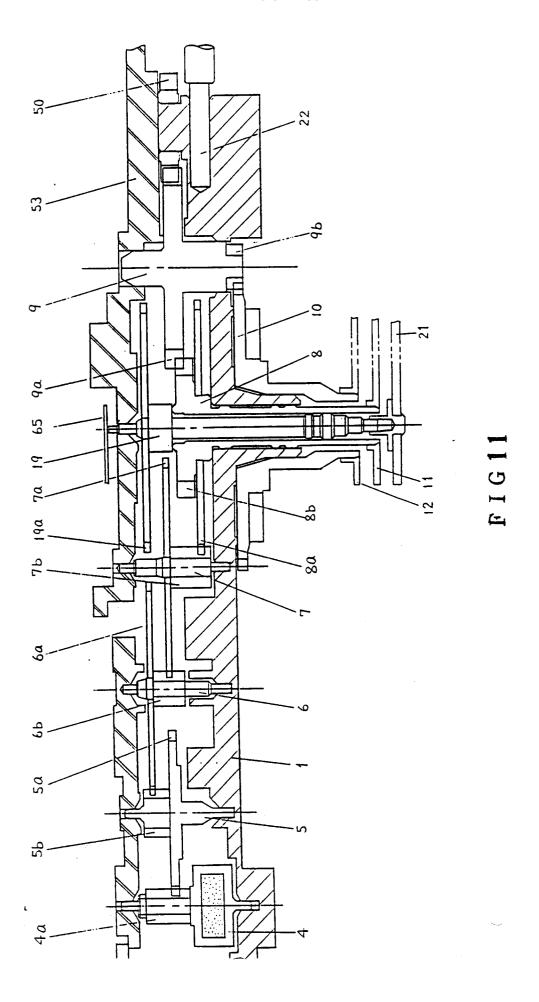

Figure 11 is a sectional view of gear trains in the watch of Figure 10 for driving hands to indicate ordinary time in hours and minutes;

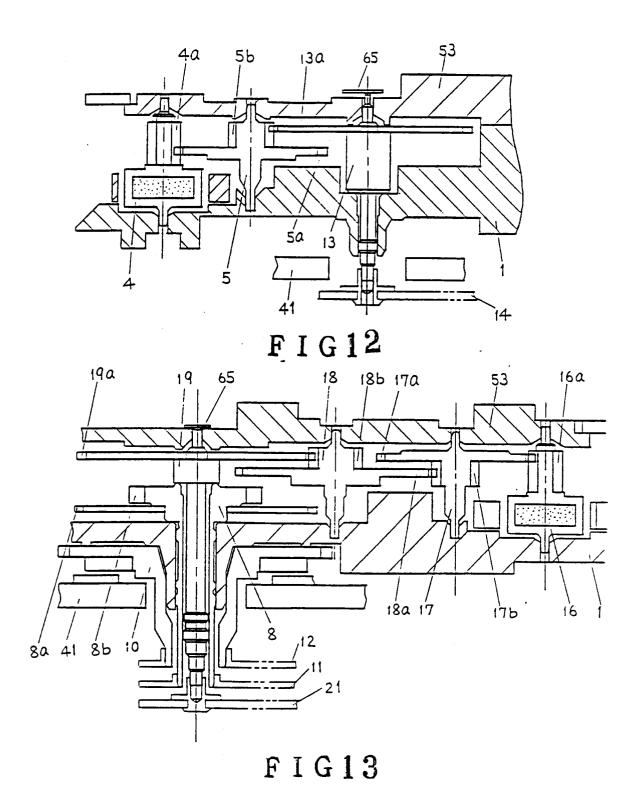

Figure 12 is a sectional view of a gear train in the watch of Figure 10, for driving a hand to indicate ordinary time in seconds;

Figure 13 is a sectional view of a gear train in the watch of Figure 10, for driving a stopwatch second hand:

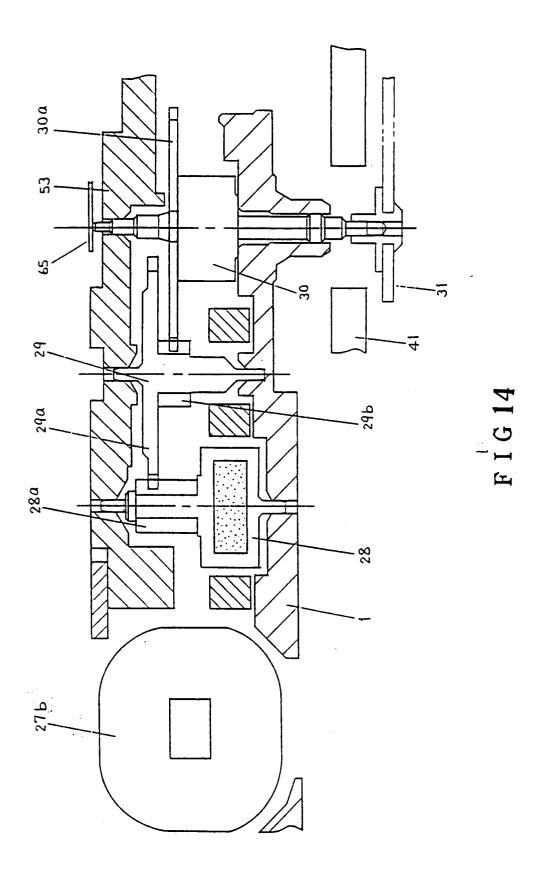

Figure 14 is a sectional view of gear trains in the watch of Figure 10, for driving a hand to indicate a chronograph minute and a timer second;

Figure 15 is a sectional view of a gear train in the watch of Figure 10, for driving hands to indicate an alarm set time;

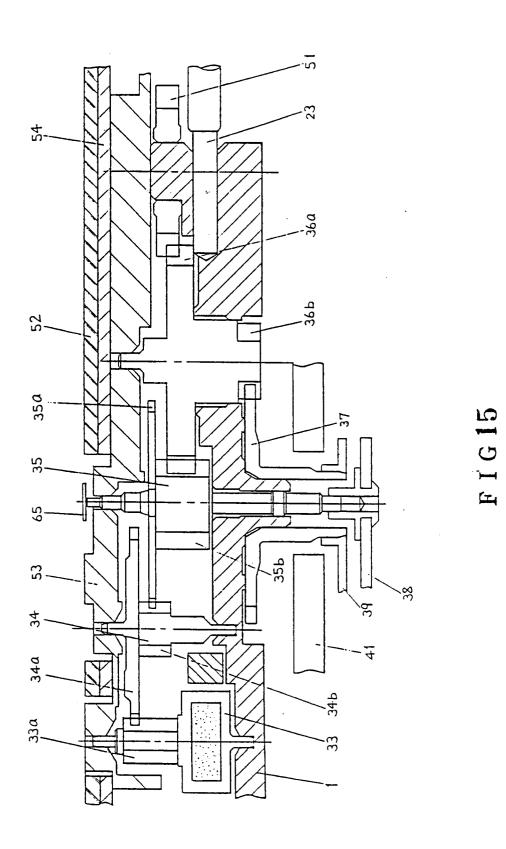

Figure 16 is a circuit connection diagram of the watch of Figure 10;

Figure 17 is a front view of a complete multifunction electronic watch according to one embodiment of the invention;

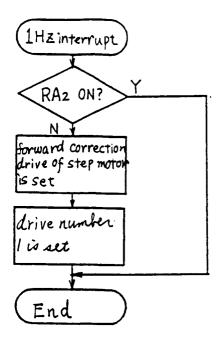

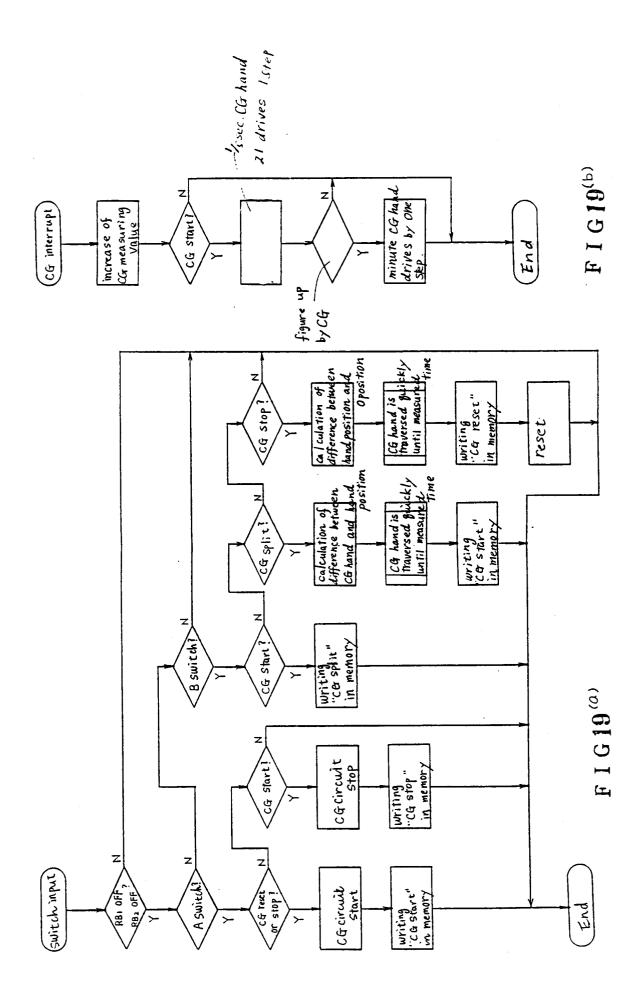

Figures 18 (a) and 18 (b) are flow charts of alternative steps for indicating ordinary time;

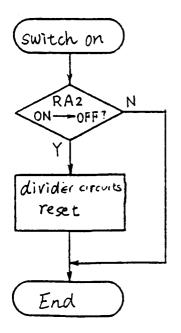

Figures 19 (a) and 19 (b) are flow charts of alternative steps of a chronograph function;

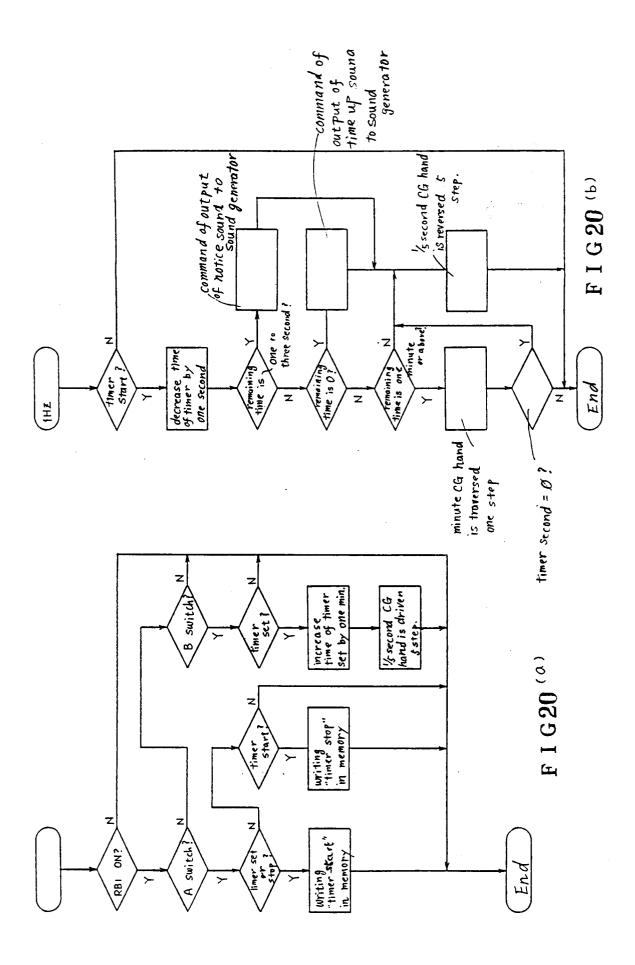

Figures 20 (a) and 20 (b) are flow charts of alternative steps of a timer function;

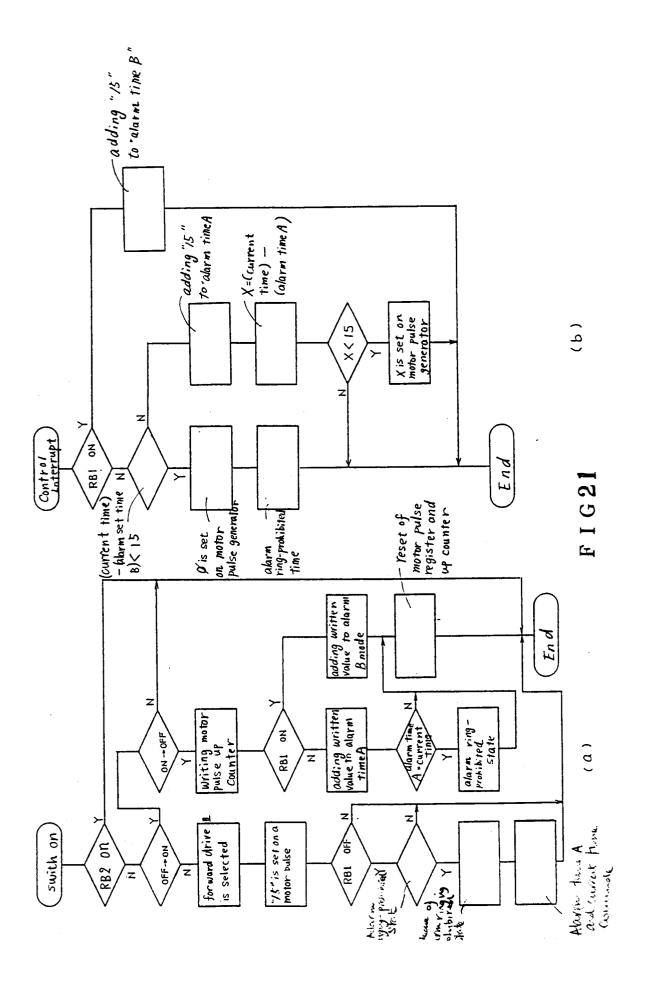

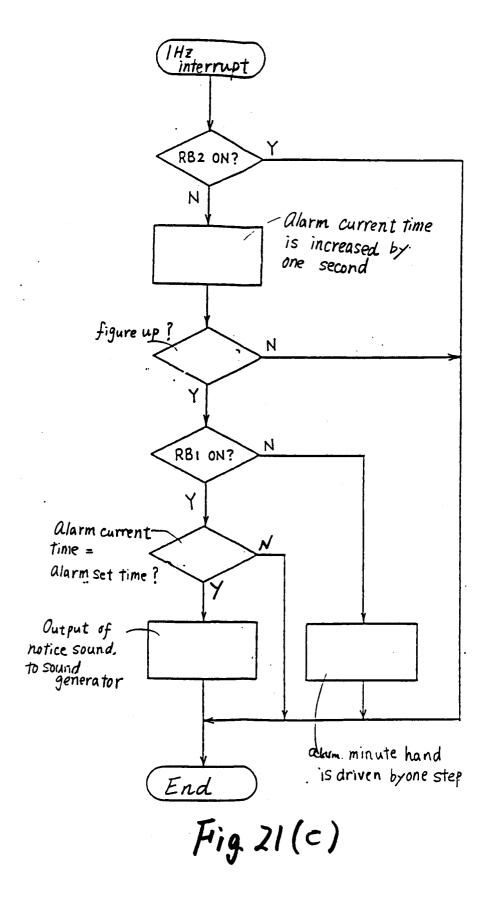

Figures 21 (a), 21 (b) and 21 (c) are flow charts of alternative steps of an alarm function;

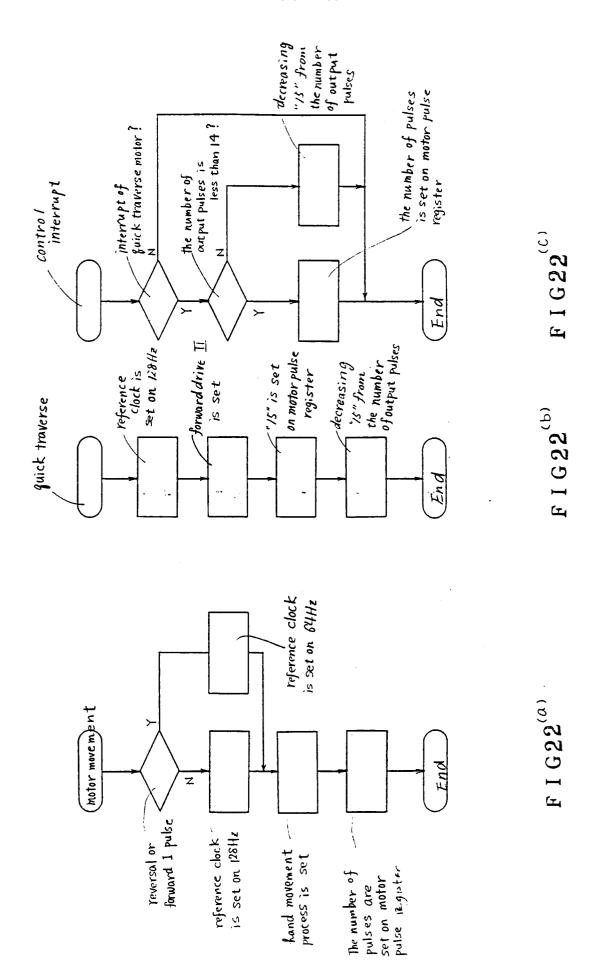

Figures 22 (a), 22 (b) and 22 (c) are flow charts of alternative steps of driving methods of the motor; and

Figure 23 illustrates, in block diagram form, a second embodiment of the invention.

A CMOS-IC chip 20 (Figure 1) is a one chip micro-computer for an analog electronic watch with a program memory 202, a data memory 204, four motor drivers 213, 214, 215 and 216, a motor drive controlling circuit 212, a sound generator 210, an interrupt control circuit 218 and other circuits integrated on one chip around a core CPU 201.

The core CPU 201 comprises an ALU, a register for arithmetic operations, an address controlling

register, a stack pointer, an instruction register, an instruction de-coder and other functional circuits, and is connected to peripheral circuits through an address bus adbus and a data bus dbus according to a memory-mapped I/O system.

The program memory 202 consists of a mask read only memory ROM of 2,048 words x 12 bits, storing software for operating the IC, and has an address decoder 203.

The data memory 204 consists of a random access memory RAM of 112 words x 4 bits which is used for various timers, counters for storing hand position of each pointer and others, and has an address de-coder 205.

An oscillator circuit 206 oscillates at 32,768 Hz with a tuning fork crystal resonator connected to terminals Xin and Xout as an oscillation source.

A first divider circuit 208 divides the 32,768 Hz signal  $\Phi$ 32k generated from the oscillator circuit 206 in sequence and generates a 1 kHz signal  $\Phi$ 1k, a 512 Hz signal  $\Phi$ 512, a 256 Hz signal  $\Phi$ 256, and a 16 Hz signal  $\Phi$ 16. An oscillation stop detection circuit 207 is connected to receive the signal  $\Phi$ 1k and, when a stop of oscillation of the oscillator circuit 206 is detected, applies a re-set to the system.

A second divider circuit 209 divides the signal  $\Phi$ 16 from the first divider circuit 208 in sequence into 8 Hz, 4Hz, 2 Hz and 1 Hz signals, which can be read into the core CPU 201 by the software.

The 16 Hz signal  $\Phi$ 16, 8 Hz signal  $\Phi$ 8, and 1 Hz signal  $\Phi$ 1 are used as a time interrupt (Tint) for processing such as time keeping or the like. The time interrupt (Tint) is generated at the fall of each signal. Read, re-set and mask of each interrupt source are all effected by the software, and re-set and mask are read individually at every source.

The sound generator 210 can generate a buzzer driving signal to a terminal AL. Driving frequency, ON/OFF operation and sound pattern of the buzzer driving signal can be controlled by the software.

The chronograph circuit 211 (Figure 2) provides a 1/100 sec chronograph, though the drive of the 1/100 sec hand is controlled by hardware to lighten the load on the software.

The circuit 211 includes a clock forming circuit 2111 which forms 100 Hz signal  $\Phi$ 100 working as a reference clock for chronography from 512 Hz signal  $\Phi$ 512, and a clock pulse Pfc 100 Hz and 3.91 ms in pulse width for forming 1/100 sec hand driving pulse Pf. A 50-proceeding chronograph counter 2112 counts signals  $\Phi$ 100 passing through an AND gate 2119 and is re-set on a chronograph re-set signal Rcg generated by a control signal forming circuit 2118. A register 2113 holds the contents of the chronograph counter 2112, when a split indication command signal Sp is generated by

the control signal forming circuit 2118. A 50-proceeding hand position counter 2114 stores 1/100 sec hand indication position of the 1/100 sec hand by counting 1/100 sec hand driving pulses Pf from a 1/100 sec hand drive controlling circuit 2117 and is re-set by a signal Rhnd from the control signal forming circuit 2118 to store a zero position on the 1/100 sec hand.

An identity detection circuit 2115 compares the contents of the register 2113 and of the hand position counter 2114 and generates an identity signal Dty when identity is detected. A zero position detection circuit 2116 generates a zero detection signal Dt upon detection of zero in the hand position counter 2114.

The control signal forming circuit 2118 receives instructions over the bus BUS and forms and generates a start signal St, a chronograph re-set signal Rcg, a split signal Sp, a drive signal Drv and the zero position signal Rhnd. The start signal St is passed to AND gate 2119 and to circuit 2117 to command a measurement start or stop according to a command of the software. The split signal Sp is passed to register 2113 and circuit 2117 to command a split indication or split indication release. The chronograph re-set signal Rcg is passed to counter 2112 to command a re-set of measurement. The zero position signal Rhnd is passed to counter 2114 to store a zero position of the 1/100 sec hand. The drive signal Drv is passed to circuit 2117 to command operation or inoperation of the 1/100 sec hand. The 1/100 sec hand drive controlling circuit 2117 receives clock pulses Pfc from circuit 2111 and passes clock pulses Pfc when the contents of the chronograph counter 2112 and the hand position counter 2114 are identical in the state when the 1/100 sec hand operates and also during measuring, that is when signals Dty and Drv or St are up. The circuit 2117 also passes clock pulses Pf when the contents of the register 2113 and the hand position counter 2114 are not identical at the time of split indication and also stop of measuring, that is when signal Dty is down and signal Sp is up or signal St is down. The circuit 2117 also passes clock pulses Pf when the contents of the hand position counter 2114 is other than zero in the state when the 1/100 sec hand is not operating and also during measuring, that is when signal DtΦ is down and signal Drv is down or signal St is up. The clock pulses Pf are supplied to motor driver 215 (Figure 1) so that the 1/100 sec hand is ready for driving only by a step motor C. Further, a chronograph interrupt CGint (Figure 2) is generated on a 5 Hz carry signal Φ5 coming from the chronograph counter 2112, and a measurement after 1/5 seconds is ready for processing by the software.

The motor drive controlling circuit 212 (Figure 3) generates motor driving pulses for each motor driver according to commands from the software.

5

The circuit 212 includes a motor drive system controlling circuit 219 which stores a drive system for each motor and according to commands from the software forms and generates control signals, namely, signal Sa for selecting a forward drive I, signal Sb for selecting a forward drive II, signal Sc for selecting a reverse drive I, signal Sd for selecting a reverse drive II, and signal Se for selecting a forward corrective drive.

The circuit 212 also includes a drive reference signal forming circuit 220 (Figure 4) for forming and generating a drive reference clock signal Cdrv according to commands from the software over the bus BUS. The circuit 220 includes a 3-bit register 2201 which stores data supplied over the data bus dbus for deciding the frequency of the driving reference clock signal Cdrv according to the output signal of an address de-coder 2202 receiving addresses over the address bus adbus from the software. The circuit 220 also includes a 3-bit register 2203 which is loaded with the data in the register 2201 at the fall of the driving reference clock signal Cdrv generated by a programmable dividing circuit 2205. The circuit 220 also includes a de-coder 2204 generating numerals 2, 3, 4, 5, 6, 8, 10 and 16 in binary form corresponding to data stored in the register 2203. The programmable dividing circuit 2205 divides the 256 Hz signal Ф256 generated from the first divider circuit 208 by n, being the numeral generated by the de-coder 204. Accordingly, the drive reference signal forming circuit 220 is capable of selecting the frequency of the drive reference clock signal Cdrv from among eight kinds, namely, 128 Hz., 85.3 Hz, 64 Hz, 51.2 Hz, 42.7 Hz, 32 Hz, 25.6 Hz and 16 Hz. The frequency of the drive reference clock signal Cdrv is changed at the point in time when data is loaded into the register 2203, and the data is loaded into the register 2203 synchronously with the drive reference clock signal Cdrv. Therefore an interval of 1/fa will be secured when the frequency fa is switched to the next frequency fb.

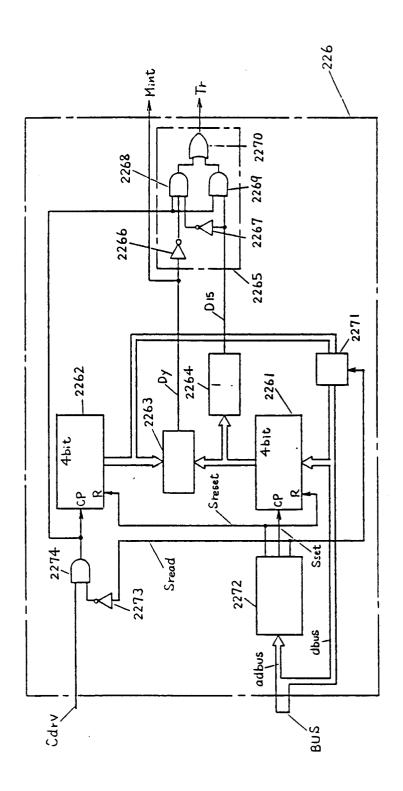

The circuit 212 also includes four motor clock controlling circuits 226, 227, 228, 229 which control driving pulse numbers of step motor A, step motor B, step motor C, step motor D, respectively, according to commands from the software. As the circuits are identical, only one circuit 226 (Figure 9) will be described in detail. The circuit 226 includes a 4-bit register 2261 which stores a driving pulse number commanded by the software. A 4-bit upcounter 2262 counts drive reference clock signals Cdrv passing through AND gate 2274, and is re-set by a control signal. A control signal forming circuit 2272 receives instructions over the address bus

adbus, and forms and generates a signal Sset for setting a driving pulse number on the data bus dbus in the register 2261 according to commands from the software, a signal Sread for reading data of the up-counter 2262, and a signal Sreset for resetting the register 2261 and the up-counter 2262. The signal Sread is supplied to an inverter 2273 whose output is to the AND gate 2274, so that the driving reference clock signals Cdrv are prohibited from passing the AND gate 2274. A two-way switch 2271 is turned to ON when the signal Sread is generated, thus applying data of the up counter 2262 onto the databus dbus. In this case, the register 2261 and up-counter 2262 must be re-set after reading by the signal Sreset.

An identity detection circuit 2263 compares the contents of the register 2261 and the up-counter 2262 and generates an identity signal Dy when the contents are identical. An all-1 detection circuit 2264 generating an all-1 detection signal D15 when the contents of the register 2261 are all 1s. A motor driving pulse forming trigger signal generation circuit 2265 comprises inverters 2266 and 2267, a 3-input AND gate 2268, a 2-input AND gate 2269 and a 2-input OR gate 2270.

The circuit 2265 receives clock signals Cdrv supplied as inputs to AND gates 2268 and 2269, the identity signal Dy as input to inverter 2266 whose output is one input of AND gate 2268, and the all-1 detection signal D15 as input to AND gate 2269 and as input to inverter 2267 whose output is one input to AND gate 2268. The outputs of AND gates 2268 and 2269 are ORed in OR gate 2270 whose output is a motor trigger signal Tr. When a number, other than all 1s, is set in register 2261, which number differs from that in register 2262, trigger signals Tr are generated through AND gate 2268 until the numbers agree, when the identity signal Dy stops such generation. When the register 2261 is set to all 1s, the circuit 2265 generates trigger signals Tr repeatedly through AND gate 2269 even when an identity signal Dy is generated.

When the identity detection circuit 2263 detects identity or when the pulse number is set at zero, a motor control interrupt Mint is generated, which interrupt can be read by the software, and can be re-set after reading.

The circuit 212 (Figure 3) includes four trigger forming circuits 230, 231, 232 and 233, each receiving a signal Sa, Sb, Sc, Sd or Se from circuit 219 and passing a trigger signal Tr generated from the corresponding motor clock controlling circuit as trigger signals Sat, Sbt, Sct, Sdt, Set for drive pulse controlling circuits 221, 222, 223, 224 and 225 to form motor driving pulses Pa, Pb, Pc, Pd, Pe correspondingly to drive system control signals Sa, Sb, Sc, Sd, Se generated from the motor drive system controlling circuit 219.

35

40

50

55

When the forward drive I and the reverse drive are carried out continuously, the frequency of the driving reference clock Cdrv is limited to below 64 Hz. The first drive pulse forming circuit 221 forms and generates the driving pulse Pa for forward drive I (Figure 5). The second drive pulse forming circuit 222 forms and generates the driving pulse Pb for forward drive II (Figure 6). The third drive pulse forming circuit 223 forms and generates the driving pulse Pc for the reverse drive I (Figure 7). The fourth drive pulse forming circuit 224 forms and generates the driving pulse Pd for reverse drive II (Figure 8). The fifth drive pulse forming circuit 225 forms and generates a pulse group Pe for corrective drive, comprising ordinary driving pulse P1, correction driving pulse P2, pulse P3 at the time of AC magnetic field detection, AC magnetic field detecting pulse SP1, rotation detecting pulse SP2, as disclosed in Japanese Laid-Open Patent No. 260883/1985.

Four motor driving pulse selection circuits 234, 235, 236 and 237 (Figure 3), select and generate driving pulses PA, PB, PC and PD, respectively, necessary for a step motor from among the motor driving pulses Pa, Pb, Pc, Pd, Pe generated by the driving pulse forming circuits 221 to 225, corresponding to the drive system control signals Sa, Sb, Sc, Sd or Se received.

The motor drivers 213, 214, 215 and 216, each drive a step motor by passing motor driving pulses PA, PB, PC and PD, respectively, coming from the motor driving pulse selection circuit 212 alternately to two output terminals of each motor driver.

An input control and re-set signal forming circuit 217 receives switched inputs at terminals A, B, C, D, RA1, RA2, RB1 and RB2, and inputs at terminals K, T and R. The circuit 217 also receives data and instructions on bus BUS and any re-set input from the oscillation stop detection circuit 207.

The interrupt control circuit 218 operates to give precedence to each switch interrupt SWint, chronograph interrupt CGint, motor control interrupt Mint, storage before reading, and re-set R after reading, by issuing a signal INT. A constant voltage circuit 200 provides a low constant voltage of about 1.2 V at terminal VS1 from a battery voltage of about 1.58 V impressed across terminals VDD and VSS. If there is a switched input at any one of the terminals A, B, C, D, RA1, RA2, RB1 or RB2, a switch interrupt signal SWint is generated. In this case, read and re-set of the interrupt source are carried out by the software. Then, each input terminal is pulled down to the level of terminal VSS representing data 0, where data 1 is represented by the level of terminal VDD.

The terminal K is that for switching specifications, and two kinds of specifications can be selected according to the data on terminal K. Then, the data on the terminal K is read by the software.

The terminal R is that for system re-setting, and when the terminal R is at the level of terminal VDD, the core CPU 201, the divider circuits 208 and 209 and other peripheral circuits are initialised by the hardware.

The terminal T is that for converting the test modes, and by inputting a clock pulse to the terminal T with the terminal RA2 at the level of terminal VDD, sixteen test modes for testing peripheral circuits can be changed. The main test mode comes in a forward drive I ensuring mode, a forward drive II ensuring mode, a reverse drive I ensuring mode, a reverse drive II ensuring mode, a corrective drive ensuring mode, a chronograph 1/100 sec ensuring mode and others, and in these ensuring modes, the motor driving pulse is generated automatically to each motor driving pulse output terminal.

The system can be re-set by connecting the terminal R to the level of terminal VDD and also by closing the switches concurrently otherwise. In the IC, the system will be re-set forcibly by hardware when A or C, and B and RA2 are closed concurrently, and also when one of A, B and C, and RA2 and RB2 are closed concurrently.

Then, functions to re-set the divider circuit and other peripheral circuits are available by the software, and when the peripheral circuits are re-set, the divider circuits will also be re-set.

Thus, the CMOS-IC 20 has the following features for the drive of step motors, and is extremely effective as IC chip for multi-hand type multi-functional analog electronic watches:-

- 1. the motor drivers 213, 214, 215 and 216, so that the four step motors can be driven concurrently;

- 2. the motor drive system controlling circuit 219, the drive pulse forming circuits 221 to 225 and the motor drive pulse selection circuits 234 to 237, so that three kinds of forward drive and two kinds of reverse drive on each of the four step motors can be effected by the software;

- 3. the drive reference signal forming circuit 220, so that the drive speed of each step motor can be arbitrarily changed by the software; and

- 4. the motor clock controlling circuits 226 to 229 each corresponding to a step motor, so that a driving pulse number can be set arbitrarily for each step motor.

An embodiment of a multi-functional analog electronic watch (Figure 10) according to the invention incorporates a CMOS-IC 20 as hereinbefore described. The watch includes a base plate 1 formed of a plastics resin material, and a silver oxide battery 2 (SR927W). There are four step motors A, B, C, and D, referenced in Figure 10 as 3, 15, 27 and 32. The step motor 3 for indicating ordinary time, comprises a magnetic core 3a of

15

20

40

high permeability material, a coil block 3b consisting of a coil wound on the magnetic core 3a, a coil lead substrate having the opposite ends processed to be conductive and a coil frame, a stator 3c formed of high permeability material, and a rotor 4 consisting of a rotor magnet and a pinion 4a (Figure 11).

A fifth wheel 5 has a gear 5a engaged with the pinion 4a, and a pinion 5b engaged by a gear 6a of a fourth wheel 6. The wheel 6 has a pinion 6b engaged by a gear 7a of a third wheel 7 which also has a pinion 7b engaged by a gear 8a of a minute wheel 8. The wheel 8 has a pinion 8b engaged by a gear 9a of an intermediate wheel 9 having a pinion 9b engaged by a gear 10a of an hour wheel 10. The minute wheel 8 and hour wheel 10 have their axes disposed centrally of the watch face and have noses projecting therethrough carrying minute and hour hands 11 and 12, respectively. The various pinions, gears and wheels of the gear trains are mounted on bearings in the base plate 1 and a spaced plate 53 (Figures 11 to 15). The plate 53 (Figure 15) is recessed to receive a circuit substrate 54 held in place by a plate 52.

The reduction ratio between the rotor pinion 4b and the minute wheel gear 8a is 1/1800, so that the minute wheel 8 and hand 11 rotate once for every 1800 rotations of the rotor 4. If the rotor 4 rotates once in two seconds, that produces a single revolution of the wheel 8 per 3600 seconds or 60 minutes or one hour. The reduction ratio between the minute pinion 8b and the hour wheel gear 10a is 1/12, so that with the rotor 4 rotating once in two seconds, the hour wheel rotates once in twelve hours.

The pinion 5b of the fifth wheel 5 (Figure 12) is also engaged by a gear 13a of a small second wheel 13 whose axis of rotation is disposed eccentrically of the watch face and along the position of the hour hand at 9 o'clock (Figure 17). The wheel 13 has a nose projecting through the watch face 41 (Figure 12) and carrying a small second hand 14. The reduction gear ratio between the rotor pinion 4a and the small second gear 13a is 1/30, and thus the small second wheel 13 turns once per 60 seconds when the rotor 4 rotates once per two seconds, thereby indicating seconds of ordinary time.

The step motor 15 (Figure 10) for chronograph second hand indication, comprises a magnetic core 15a of high permeability material, a coil block 15b consisting of a coil wound on the magnetic core 15a, a coil lead substrate with the opposite ends processed to be conductive and a coil frame, a stator 15c consisting of high permeability material, and a rotor 16 consisting of a rotor magnet and a rotor pinion 16a (Figure 13).

The rotor pinion 16a is engaged by a gear 17a of a chronograph first intermediate wheel 17 having a pinion 17b engaged by a gear 18a of a chronograph second intermediate wheel 18. The wheel 18 has a pinion 18b engaged by a gear 19a of a chronograph wheel 19. The chronograph wheel 19 is disposed centrally of the watch and has a nose projecting through the noses of the minute and hour wheels 8 and 10, and carries a hand 21. The wheel 19 is urged into contact with the wheel 8 by a spring 65 (Figures 11 to 15) pressing on a bearing portion projecting through the plate 53. The reduction gear ratio between the rotor pinion 16a and the chronograph gear 19a is 1/150. The rotor 16 rotates two and a half times or 900° per second on electrical signals from CMOS-IC 20, so that the chronograph wheel 19 rotates 6° per second, or five steps of 1.2°, thereby indicating 60 chronograph seconds per revolution. The hand 21 functions as a timer set hand for timer setting at the same time in a timer operation described hereinafter.

The step motor 27 (Figure 10) for minute indication of the chronograph and second indication of an elapsed time of the timer, comprises a magnetic core 27a of high permeability material, a coil block 27b consisting of a coil wound on the magnetic core 27a, a coil lead substrate with the opposite ends processed to be conductive and a coil frame, a stator 27c consisting of high permeability material, and a rotor 28 consisting of a rotor magnet and a rotor pinion 28a (Figure 14). The rotor pinion 28a is engaged by a gear 29a of a chronograph minute intermediate wheel 29 having a pinion 29b engaged by a gear 30a of a chronograph minute wheel 30. The chronograph minute wheel 30 is disposed to rotate on an axis eccentric to the watch face and along the position of the hour hand at 12 o'clock. A minute indication of the chronograph and a second indication of an elapsed time of the timer are made on that axis. The reduction gear ratio between the rotor pinion 28a and the chronograph minute gear 30a is 1/30. In the chronograph mode, the rotor 28 rotates once per minute on electrical signals from CMOS-IC 20. Accordingly, the chronograph minute wheel 30 rotates 12° per minute, or once every half hour, thus realising a chronograph minute indication of 30 minutes. The wheel 30 has a nose projecting through the watch face 41 and carrying a chronograph minute hand 31 for chronograph minute indication. By combining the indications of the chronograph hands 21 and 31, a chronograph indication is realised with 1/5 seconds as minimum reading unit and 30 minutes as maximum.

In the timer mode, the rotor 28 rotates counter to that of chronograph mode once every two seconds on electrical signals from CMOS-IC 20. Thus the chronograph minute hand 31 rotates once

counter-clockwise every 60 seconds in steps of one second, thus indicating seconds of an elapsed time of the timer in a 60 seconds rotation. At the same time, the rotor 16 rotates two and a half times per minute counter to that of chronograph mode on electrical signals from the CMOS-IC 20. Accordingly, the central chronograph hand 21 turns counter clockwise at 6° per minute, thus indicating minutes of elapsed time of the timer. The CG minute hand 31 driven by the step motor 27 acts as the 1/100 second had referred to in connection with Figure 2 as controlled by software.

11

The watch has first and second manually operable stems 22 and 23 (Figure 17) and three switch operating buttons 24, 25 and 26. In setting the timer, the second stem 23 is placed in a first state and the rotor 16 rotates through 180° in five steps whenever a button 25 is pushed once to close the switch connected to terminal B, so that the chronograph hand 31 turns 6° representing one minute. Thus a timer set time as long as 60 minutes can be shown.

The step motor 32 (Figure 10) comprises a magnetic core 32a of high permeability material, a coil block 32b consisting of a coil wound on the magnetic core 32a, a coil lead substrate with the opposite ends processed to be conductive and a coil frame, a stator 32c consisting of high permeability material, and a rotor 33 consisting of a rotor magnet and a rotor pinion 33a (Figure 15). The rotor pinion 33a is engaged by a gear 34a of an alarm intermediate wheel 34 having a pinion 34b engaged by a gear 35a of an alarm minute wheel 35. The wheel 35 has a pinion 35b engaged by a gear 36a of a third alarm wheel 36 having a pinion 36b engaged by an alarm hour wheel 37. The reduction ratio between the rotor pinion 33a and the alarm minute gear 35a is 1/30, and the reduction ratio between the alarm minute pinion 35b and the alarm hour wheel 37 is 1/12. The wheels 35 and 37 rotate about a common axis disposed eccentrically of the watch face along the position of the hour hand at 6 o'clock. The wheel 35 carries an alarm minute hand 38 and the wheel 37 carries an alarm hand 39.

When the second stem 23 is in the first state to select a timer set or alarm mode, the rotor 33 is rotated through 180° on an electrical signal from the CMOS-IC 20 by pushing the button 26 once to close the switch connected to terminal C. The alarm minute hand 38 turns through 6° representing 1 minute, and the alarm hour hand 39 turns through 0.5°. Thus the alarm time can be set at minute intervals up to 12 hours. For this, if the button 26 is pressed continuously, the alarm minute hand 38 and the alarm hour hand 39 rotate rapidly, thus setting the alarm time in a short time. When the set alarm time and the ordinary time

coincide, an alarm rings.

When the second stem 23 is placed in the zero state, an alarm off mode is selected, and the alarm minute hand 38 and the alarm hour hand 39 indicate ordinary time. In this case, the rotor 33 is rotated in steps of 180° at every minute on an electrical signal from CMOS-IC 20.

The CMOS-IC 20 is connected with other electric elements as shown in the circuit diagram of Figure 16. These other elements include buzzer driving elements consisting of a boosting coil 55, a mini-mold, or small sized surface coupling, transistor 56 with protective diode and a piezo-electric buzzer 64 applied to a back cover of the watch case. A 1uF chip capacitor 57 suppresses voltage fluctuations of the constant voltage circuit 200. A micro tuning fork type crystal oscillator 58 is the source for the oscillator circuit 206 through terminals Xin and Xout. A three position switch 46a can be closed on terminal RA1 or on terminal RA2 or be open. A similar three position switch 59a can be closed on terminal RB1 or on terminal RB2 or be

The buttons 24, 25 and 26 are spring-biased and can only close their switches when pushed. The switch 46a is on a yoke 46 engaged with the first stem 22, so as to close with terminal RA1 in a first state of the first stem 22, to close with terminal RA2 in a second state and to open normally. Likewise, the switch 59a is on a lever 59 engaged with the second stem 23, so as to close with terminal RB1 in a first state of the second stem 23, to close with terminal RB2 in a second state, and to open normally.

The watch (Figure 17) has a case 40. On the watch face 41 are indicia 42 for ordinary second time, indicia 43 for a chronograph minute and timer elapsed time second indication, and indicia 44 for an alarm set time indication.

Ordinary time is indicated by the small second hand 14 stepping at every second, whilst the minute hand 11 and the hour hand 12 rotate more slowly. For correcting the time, the first stem 22 is pulled out to the second state. The first stem 22 engages a lever 45 and yoke 46 to move a setting lever 47 which engages and stops the fourth wheel 6. The first stem 22 is then rotated and through a clutch wheel 48 rotates a setting pinion 50 in either direction. The pinion 50 (Figure 11) is engaged with the gear 9a of the intermediate wheel 9. Rotation of the wheel 9 is transferred to the minute wheel 8 and the hour wheel 10. The gear 8a of the minute wheel 8 is coupled to the wheel 8 and pinion 8b with constant sliding torque, so that relative rotation can occur under the torque applied manually through the stem 22 because the stopping of the fourth wheel 6 also stops the third wheel 7 and gear 8a. The rotor 4 also stops and

55

35

15

20

25

the second wheel 13 (Figure 12) also stops. When the minute and hour hands 11 and 12 have been set to the desired time, the stem 22 is returned from its second state to its normal position and the rotor 4 re-starts rotation to drive the hands 11, 12 and 13.

If a 1 Hz interrupt (Figure 18 (a)) is input, it is first determined whether or not the switch 46a is connected to terminal RA2. If not, then a forward correction drive of the step motor A is set on the motor drive system controlling circuit 219 (Figure 3) and a drive number 1 is set on a motor clock controlling circuit 226. If the switch 46a is connected to the terminal RA2, a time corrected state (Figure 18 (a)), the motor drive is stopped, and divider circuits 208 and 209 are re-set instantaneously so as to drive the motor one second later at the point in time when the switch 46a is turned off

In the flow chart of the chronograph function (Figures 19 (a) and 19 (b)), CG is used as an abbreviation for chronograph. When a switch input to the circuit 217 occurs, it is first determined whether the second stem 23 is not in the first or second state, so that the switch 59a is not on the terminal RB1 or RB2. If the switch 59a is not on either terminal, then it is determined whether the switch input comes from pushing the button 24 to connect to terminal A. If so, the data memory is read to determine if CGreset or CGstop is stored therein. If so, then the CG circuit is started and CGstart is written into the memory in place of CGreset or CGStop. CGstart causes the CG second hand 21 to be driven five steps per second from the zero position from which it starts. The number of seconds is counted in both the counter 2113 and the counter 2114 and after 60 seconds, a carry causes the CG minute hand 31 to be stepped to indicate the passage of one minute of time.

This continues until another switch input occurs and is found to be from the terminal A due to a push on the button 24. It is first determined whether CGstart has occurred and because CGstart is written in the memory, the CG circuit is stopped and CGStop is written into the memory in place of CGstart. Thus the CG second hand 21 and the CG minute hand 31 are both stopped and the elapsed time can be read off the watch face. If, whilst CGstart is in the memory, a switch input is found not to be from terminal A, it is determined whether it is from terminal B. If so, then it arises from a push on the button 25 and CG split is started and CGsplit is written into the memory in place of CGstart. This stops the rotation of the CG second hand 21 and the CG minute hand 31, but continues the counting of the seconds passing in counter 2113. Thus a split time can be read from the hands 21 and 31 off the watch face.

If a further push on button 25 occurs thereafter, and it is determined that <u>CGsplit</u> is in the memory, then a calculation occurs as to the difference between the CG hand position as it is recorded in counter 2114 and the CG hand position as it ought to be as recorded in counter 2113. The difference in circuit 2115 causes the CG hands to be driven quickly until it is eliminated when they continue to rotate at normal forward speed. At the same time, <u>CGstart</u> is re-written into the memory in place of <u>CGsplit</u>.

If, after the button 24 has been pushed to stop the chronograph indication and CGstop has been written into the memory, the button 25 is pushed, then after a determination that CGstart and CGsplit are not in the memory and that CGstop is in the memory, the difference between the hand position and the zero hand position is calculated and the hands rapidly returned to the zero position as indicated in the circuit 2116, whilst CGreset is written into the memory in place of CGstop.

If, after the button 25 has been pushed and CGsplit written into the memory, the button 24 is pushed to close the switch upon terminal A, then the hand is already stopped at the split time. The counting of seconds is stopped and the accumulated value retained in memory. If the button 25 is again pushed to close the switch upon terminal A, counting is re-started, but the hand remains stopped.

If the second stem 23 is moved to the first state, the switch 59a engages the terminal RB1 and the flow chart of Figures 20 (a) and 20 (b) indicates the resultant steps in the timer set mode. If a switch input to circuit 217 is detected, it is first determined whether the terminal RB1 is connected. If so, it is determined whether the terminal A is connected due to the button 24 being pushed. If so, it is determined whether timerset or timerstop is written in the memory. There is no need to write timerset into memory, if it is assumed that timerset is so written when it is determined that neither timerstart nor timerstop is written in memory. If so, the timer is started as described in relation to Figure 20 (b) and timerstart is written into the memory. If in the previous deter- mination, it is found that timerstart is written in the memory, then the timer is stopped and timerstop written in the memory. A further push on button 24 re-starts the timer.

If in the initial determination, it is found that the button 25 has been pushed so that the terminal B is connected, it is determined whether timerset is written in the memory. If so, then this indicates that neither timerstart nor timerstop is written in the memory and that a timer operation is not in progress. Accordingly, the timer set time is increased by one minute and this is indicated by

45

50

clockwise stepping of the CG second hand 21 by five steps representing 6° on the watch face 41. Repeated pushing of the button 25 causes repeated increases and stepping until the CG second hand 21 indicates the desired timer set time. The maximum time that can be set is 60 minutes. When the timer is started by pushing the button 24, the 1 Hz interrupt signal with timerstart written in the memory causes a decrease of one second in the time set each second and the CG minute hand 31 is driven counter clockwise. Every minute, the CG minute hand completes a full circle and the CG second hand 21 is stepped five steps counter clockwise until only one minute remains. Then the CG minute hand 31 stops and the CG second hand 21 is stepped five steps for each second. At each decrease of timer time by one second, it is determined (Figure 20 (b)) whether the time remaining is one to three seconds. If not, then it is determined whether no time remains. If not, then it is determined whether the time remaining is one minute or more. If so, the CG minute hand 31 is stepped by one second counter clockwise and it is determined if the timer second = 0. If so, then the CG second hand 21 is stepped counter clockwise by five steps. If the remaining time is found to be one to three seconds, a command is issued to the sound generator to output a notice sound. If the remaining time is zero, a command is issued to the sound generator to output a time-is-up sound. If the remaining time is less than one minute, the CG second hand 21 is stepped counter clockwise by five steps. If a time of one minute only is set, the elapse of time is only indicated by counter clockwise movement of the CG second hand 21. Otherwise, time elapsed is shown by both hands 21 and 31 until only one minute remains. It will be appreciated that when the remaining time is zero, the CG minute hand 31 is already in a zero position and the CG second hand 21 is stepped through five steps back to the zero position.

As shown in the flow chart of an alarm function in Figure 21 (a), when the button 26 is pushed with the second stem 23 in the normal or in the first state, that is with switch 59a off the terminal RB2, a forward drive II is selected for the motor driving pulse selecting circuit 237 according to an instruction from the CPU, "15" is set on a register of the trigger forming circuit 233 (hereinafter called "motor pulse register") and a correction for quick traverse of the alarm hour/minute hands is commenced. In the alarm A mode, the second stem 23 is kept in the zero state, the switch 59a is off the terminal RB1 and the alarm is not set; thus alarm ringing is prohibited. The time when correction is commenced is fixed as an alarm set time, and the alarm ringing prohibited state is cleared to an alarm set state. When the motor pulse is generated 15

times, a control interrupt is generated by the trigger forming circuit 233. When the control interrupt is generated, as shown in Figure 21 (b), "15" is added to an alarm time B and "15" is re-loaded in the motor pulse register at the time of alarm B mode, thus continuing the correction. In the alarm A mode, when a difference between the current time and the alarm time A is 15 or over, "15" is added to the alarm time A, and where the difference between the current time and the alarm time A becomes less than 15 in result, the difference is set on the motor pulse register. In this case, since the alarm hour/minute hands indicate the current time when the next control interrupt is generated, "0" is set on the motor pulse register, the correction is interrupted, alarm ringing is prohibited, and the alarm set state is cleared. When the button 26 is released, the up counter 2262 (hereinafter called "motor pulse up counter") operates as shown in Figure 21 (a), and a quick traverse of alarm minute hand 38 stops. In this case the alarm minute hand 38 has advanced by a read value from the time when the previous control interrupt was generated, therefore a correction will be made for the advance. Then, in the alarm A mode, when the alarm time and the current time coincide at this point in time, alarm ringing is prohibited in the state where the alarm is not set. As shown in Figure 21 (c), the alarm is rung when a 1 Hz interrupt is counted and the alarm time and the current time coincide. However, in the case where the alarm ringing is prohibited in the alarm A mode, the alarm is not rung, and the alarm minute hand 38 is driven every minute. Thus, in the alarm A mode, alarm ringing is prohibited and an alarm set state is cleared after the alarm is rung.

In the embodiment, the alarm controlling means has the current time, the alarm set time A, and the alarm set time B as absolute values, however, relative values may be given to control the difference between the alarm set time A and the current time and the difference between the alarm set time B and the current time.

Whilst in the embodiment control is by the CPU, it may be realised by a logic circuit instead thereof.

Then, a correction of the ordinary time is carried out by turning the second stem on the second state through the clutch wheel 49 and a setting wheel 51 (Figure 10).

Various motor driving methods are illustrated in Figures 22 (a), 22 (b) and 22 (c). When motor movement is called for (Figure 22 (a)), it is first determined if the pulses required are for reverse I or forward I drives. If so, then the reference clock is set to 64 Hz, whereas if not, it is set to 128 Hz. The selection of the correct motor to drive the hands requiring movement is then made and the number

50

15

20

25

30

35

40

of pulses set in the motor pulse register 2261 (Figure 9). If the drive called for is reverse I or forward I, then the necessary pulses are issued to the selected motor until the contgents of the up counter 2262 counting incoming pulses is found to be equal to the contents of the register 2261 by the circuit 2263. The clock signals Cdrv arrive at 64 Hz.

If a quick traverse drive is called for, then the reference clock having been set on 128 Hz, the motor pulse register 2261 is set at 15, if there are 15 or more pulses to be issued, and forward II drive is set, 15 is then deducted from the number of output pulses.

If a control interrupt occurs, it is first determined if it is an interrupt of a quick traverse motor. If so, then it is determined whether the number of output pulses is less than 14. If so, then that number of pulses is set into register 2261 by the switch 2271. If not, then 15 is deducted from the number of output pulses.

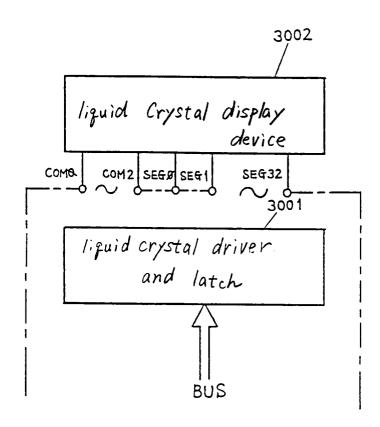

In a second embodiment of the invention, a liquid crystal driver and latch 3001 (Figure 23) is added in the body of the first embodiment and receives input from the CPU on the BUS. The driver and latch 3001 control a 33 segment liquid crystal display panel 3002 so that current time, second time separate from the current time, a calendar, alarm time, timer time, mode, chronograph time and other indications are given in digital representation by the liquid crystal display panel 3002 according to instructions from software. The panel 3002 is visible through the face 41 of the watch.

As described above, one or more pointers or hands indicate current time when an alarm is not set by the alarm controlling means. The pointers or hands indicate an alarm set time when and after the alarm is set. After the alarm rings, the pointers or hands are driven to indicate current time again with the alarm free from being set. Therefore an operation for prohibiting an alarm ring when the alarm is not to be rung again after the ring, and an operation for releasing a ring prohibited state of the alarm may be omitted, thus simplifying the operation. As the operation is thus simplified, wear of the switches will be reduced, improving the long term reliability of the watch.

An alarm time is indicated in the state when the alarm has been set, and current time is indicated in the state when the alarm is not set. Accordingly, it is readily perceivable whether or not the alarm is set without special mode indicating means. Thus, a user is free from being concerned about what to do or not to do next without observing the indication.

The alarm sound can be varied according to the mode to enable the mode to be identified

simply from the alarm sound. Further, the alarm ring tone may be changed according to the purpose for which the alarm is used.

When alarm set time and current time coincide after setting, the alarm set state is released, correction of the alarm set time is interrupted, and the alarm set state is ready for release without particular operating or ensuring an indicated state.

#### Claims

- 1. An electronic alarm watch having a plurality of step motors (3, 4; 32, 33), at least one pointer or hand (11, 12; 38, 39) driven by each step motor, external operating means (22, 23, 26), alarm ringing means (210) and alarm controlling means (20), characterised in that one or more pointers or hands (38, 39) indicate current time in the state when an alarm is not set, in that such pointers or hands (38, 39) indicate an alarm set time when and after the alarm is set, and in that after the alarm rings, such pointers or hands (38, 39) are driven to indicate current time again, with the alarm free from being set.

- 2. A watch as claimed in claim 1, comprising means whereby the alarm is released from being set when the time set on the alarm by the alarm controlling means coincides with the current time.

- 3. A watch as claimed in claim 1 or 2, comprising means whereby quick traverse set of the alarm set time is omitted when the alarm set time and the current time coincide although such quick traverse is called for by the alarm controlling means.

- 4. A watch as claimed in claim 1, 2 or 3 comprising selecting means whereby the alarm set time is retained even after the alarm rings by the alarm controlling means, and when the alarm set time and the current time coincide again the alarm rings.

- 5. A watch as claimed in claim 4 comprising means for differentiating an alarm ring when the alarm set time is so retained, from another alarm ring when the alarm is released from being set after the alarm rings.

- **6.** A watch as claimed in any preceding claim, including an additional digital indicator.

55

50

20

25

30

40

45

50

55

## Patentansprüche

- 1. Elektronische Weckuhr mit mehreren Schrittmotoren (3, 4; 32, 33), mindestens einem von jedem Schrittmotor angetriebenen Zeiger oder einer Nadel (11, 12; 38, 39), einer externen Betriebseinrichtung (22, 23, 26), einer Wecktongebereinrichtung (210) und einer Wecksteuereinrichtung (20), dadurch gekennzeichnet, daß einer oder mehrere Zeiger oder Nadeln (38, 39) die laufende Zeit in dem Zustand anzeigen, in welchem ein Weckvorgang nicht eingestellt ist, daß diese Zeiger oder Nadeln (38, 39) eine eingestellte Weckzeit angeben, wenn und nachdem der Weckvorgang eingestellt ist, und daß nach dem Ertönen des Wecktons diese Zeiger oder Nadeln (38, 39) derart angetrieben werden, daß sie erneut die laufende Zeit anzeigen, wobei der Weckvorgang dann nicht mehr eingestellt ist.

- Uhr nach Anspruch 1, gekennzeichnet durch eine Einrichtung, durch die der Weckvorgang aus dem eingestellten Zustand gelöst wird, wenn die durch die Wecksteuereinrichtung eingestellte Weckzeit mit der laufenden Zeit übereinstimmt.

- 3. Uhr nach Anspruch 1 oder 2, gekennzeichnet durch eine Einrichtung, durch ein Eilgang von der eingestellten Weckzeit aus entfällt, wenn die eingestellte Weckzeit mit der laufenden Zeit übereinstimmt, obschon ein solcher Eilgang durch die Wecksteuereinrichtung aufgerufen wird.

- 4. Uhr nach Anspruch 1, 2 oder 3, umfassend eine Auswahleinrichtung, durch die die eingestellte Weckzeit auch nach dem Ertönen des Weckrufs von der Wecksteuereinrichtung aufrechterhalten wird, so daß bei Übereinstimmung der eingestellten Weckzeit und der laufenden Zeit der Weckruf erneut ertönt.

- 5. Uhr nach Anspruch 4, gekennzeichnet durch eine Einrichtung zum Unterscheiden eines Weckrufs bei in dieser Weise erhaltener eingestellter Weckzeit von einem anderen Weckruf, wenn der eingestellte Weckvorgang, nachdem der Weckruf ertönt ist, freigegeben wird.

- **6.** Uhr nach irgendeinem vorhergehenden Anspruch, umfassend eine zusätzliche digitale Anzeige.

### Revendications

- 1. Une montre réveil électronique munie d'une pluralité de moteurs pas-à-pas (3, 4; 32, 33), d'au moins un indicateur ou aiguille (11, 12; 38, 39) entraîné par chaque moteur pas-à-pas, de movens d'actionnement externe (22, 23, 26), de moyens d'émission d'un signal d'alarme ou de réveil (210) ainsi que de moyens de commande d'alarme ou de réveil (20), caractérisé en ce qu un ou plusieurs indicateurs ou aiguilles (38, 39) indiquent l'heure exacte dans l'état ou le réveil ou l'alarme n'est pas activé, et en ce que de tels indicateurs ou aiguilles (38, 39) indiquent une heure prédéterminée d'émission d'un signal d'alarme ou de réveil pendant et après l'activation de la fonction alarme, et en ce qu'après l'émission du signal d'alarme, lesdits indicateurs ou aiguilles (38, 39) sont entraînés afin d'indiquer à nouveau l'heure exacte, l'état d'activation de l'alarme étant annulé.

- 2. Une montre selon la revendication 1, comprenant des moyens permettant de libérer l'état d'activation de l'alarme quand l'heure prédéterminée pour l'émission du signal d'alarme par les moyens de commande d'alarme coïncident avec l'heure exacte.

- 3. Une montre selon la revendication 1 ou 2, comprenant des moyens permettant d'omettre une détermination de l'heure de l'émission d'un signal d'alarme au moyen d'un passage rapide, lors de la coïncidence de l'heure exacte et de l'heure prédéterminée pour l'émission du signal d'alarme bien qu'un tel passage rapide soit exigé par les moyens de commande d'alarme.

- 4. Une montre selon la revendication 1, 2 ou 3, comprenant des moyens de sélection permettant de maintenir l'heure prédéterminée d'émission du signal d'alarme même après l'émission de ce signal d'alarme par les moyens de commande d'alarme, et pour permettre l'émission de ce signal d'alarme lors de la coïncidence renouvelée de l'heure exacte et de l'heure prédéterminée pour l'émission de ce signal d'alarme.

- 5. Une montre selon la revendication 4, comprenant des moyens permettant de différencier le signal d'alarme quand l'heure prédéterminée d'émission du signal d'alarme est ainsi maintenue, d'un autre signal d'alarme après l'annulation de l'activation de l'alarme, après l'émission du signal d'alarme.

6. Une montre selon l'une quelconque des revendications précédentes comprenant un moyen d'affichage numérique supplémentaire.

FIG2

F I G 4

F I G 9

21

23

F I G 16

F I G 17

F I G 18 (b)

F I G 18 (a)

F I G 23