(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5281448号

(P5281448)

(45) 発行日 平成25年9月4日(2013.9.4)

(24) 登録日 平成25年5月31日(2013.5.31)

(51) Int.Cl.

F 1

G06F 11/30 (2006.01)

G06F 15/78 (2006.01)G06F 11/30 310B

G06F 15/78 510K

請求項の数 9 (全 18 頁)

(21) 出願番号 特願2009-69908 (P2009-69908)

(22) 出願日 平成21年3月23日 (2009.3.23)

(65) 公開番号 特開2010-224759 (P2010-224759A)

(43) 公開日 平成22年10月7日 (2010.10.7)

審査請求日 平成24年2月20日 (2012.2.20)

(73) 特許権者 000237592

富士通テン株式会社

兵庫県神戸市兵庫区御所通1丁目2番28

号

(74) 代理人 100107478

弁理士 橋本 眞

(72) 発明者 嘉藤 智幸

兵庫県神戸市兵庫区御所通1丁目2番28

号 富士通テン株式会社内

審査官 多賀 実

最終頁に続く

(54) 【発明の名称】電子制御装置、異常監視方法

## (57) 【特許請求の範囲】

## 【請求項 1】

マイクロコンピュータと、前記マイクロコンピュータから出力される異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、前記マイクロコンピュータから出力されるパルス信号に基づいて前記マイクロコンピュータの異常を検出する異常監視回路とを備えている電子制御装置であって、

前記マイクロコンピュータは、前記パルス信号の出力制御を行なうとともに、入力されるC P Uクロックを停止させることで自身をストップ状態に移行させるための制御信号の出力制御を行なうC P Uと、前記制御信号の出力状態に応じて前記監視制御信号の出力状態を切り替える監視制御回路とを備えていることを特徴とする電子制御装置。

## 【請求項 2】

前記制御信号が前記C P Uによりストップ命令が実行されたときに切り替わる信号であり、前記監視制御回路は当該信号の切り替わりに応じて異常監視を禁止するように前記監視制御信号を切り替えることを特徴とする請求項1記載の電子制御装置。

## 【請求項 3】

前記C P Uによるストップ命令の実行時に生成される前記制御信号に基づいてC P Uクロックを停止し、前記C P Uをストップモードから動作モードに切り替えるウェイクアップ信号に基づいて前記C P Uクロックを出力するように制御するクロック制御回路を備えることを特徴とする請求項1または2記載の電子制御装置。

## 【請求項 4】

10

20

前記制御信号が前記 C P U により低消費電力駆動命令が実行されたときに切り替わる信号であり、前記監視制御回路は当該信号の切り替わりに応じて異常監視を禁止するよう前に記監視制御信号を切り替えることを特徴とする請求項 1 から 3の何れかに記載の電子制御装置。

【請求項 5】

前記監視制御信号が出力されるポートがポートモードを設定するモード設定レジスタを備えた汎用入出力ポートで構成され、前記マイクロコンピュータのリセット時に前記モード設定レジスタによるポートモードが設定されるまでの間、ハイインピーダンスとなるよう<sup>10</sup>に設定されていることを特徴とする請求項 1 から 4の何れかに記載の電子制御装置。

【請求項 6】

前記モード設定レジスタの値の変更を禁止するプロテクトレジスタを備えている請求項 5 記載の電子制御装置。

【請求項 7】

前記監視制御信号が出力されるポートの信号レベルを入力する入力回路を前記ポートに設けていることを特徴とする請求項 5 または 6 記載の電子制御装置。

【請求項 8】

前記監視制御信号が禁止状態から許可状態に切り替わるときに、前記監視制御信号を遅延させる遅延回路を、前記監視制御信号の信号線に設けていることを特徴とする請求項 1 から 7の何れかに記載の電子制御装置。

【請求項 9】

マイクロコンピュータから出力される異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、前記マイクロコンピュータから出力されるパルス信号に基づいて前記マイクロコンピュータの異常を検出する異常監視方法であって、

前記マイクロコンピュータの C P U から出力され、入力される C P U クロックを停止させることで自身をストップ状態に移行させるための制御信号の出力状態に連動して前記監視制御信号の出力状態を切り替える異常監視方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロコンピュータと、異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、前記マイクロコンピュータから出力されるパルス信号に基づいて前記マイクロコンピュータの異常を検出する異常監視回路とを備えている電子制御装置、及び異常監視方法に関する。

【背景技術】

【0002】

一般に、電子機器はマイクロコンピュータにより制御されている。そして、高い安全性が要求される電子機器、例えば車両に搭載される電子制御装置（以下、E C U (Electric Control Unit) と記す。）では、ノイズ等の影響によりマイクロコンピュータが暴走したり回路が破損して正常に動作しなくなる万一の事態に備えて、通常、マイクロコンピュータの外部にマイクロコンピュータの異常監視装置を設けていることが多い。

【0003】

異常監視装置は、マイクロコンピュータから出力されるパルス信号をモニタしておき、当該パルス信号の異常監視装置への入力が所定期間途切れると、マイクロコンピュータにソフトウェア暴走等の異常が発生していると判断して、マイクロコンピュータに対してリセット信号を出力する。

【0004】

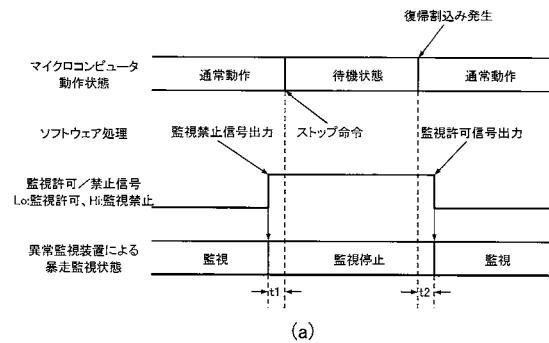

ところで、車両には複数の E C U が搭載されており、これら E C U には、イグニッションスイッチがオンの場合にのみ給電される E C U と、イグニッションスイッチのオンオフにかかわらず常時給電される E C U がある。これら E C U は、単数または複数のネットワ

10

20

30

40

50

ーク、例えばCAN (Controller Area Network) バスやLIN (Local Interconnect Network) バス等で相互接続されている。

【0005】

イグニッションスイッチがオンの場合にのみ給電されるECUとしては、エンジンを制御するECUやブレーキを制御するECU等があり、イグニッションスイッチのオンオフにかかわらず常時給電されているECUとしては、複数のネットワーク同士を接続するために各ネットワークで異なるプロトコルの変換を行なうゲートウェイECU、ドアロック制御用のECU、及び盗難防止等のセキュリティを管理するECU等がある。

【0006】

そして、イグニッションスイッチのオンオフにかかわらず常時給電されているECUは、イグニッションスイッチがオフの場合には、マイクロコンピュータを待機状態へ移行させ、イグニッションスイッチがオンになった場合やCANバスを介してフレームの受信があった等の割込み発生時等にのみ、マイクロコンピュータをウェイクアップして動作させることが、省電力化のために有効である。

10

【0007】

マイクロコンピュータが移行する待機状態にはいくつかの種類があり、例えば、CPUの動作クロックを停止させるモードがある。このようなモードに移行した場合、マイクロコンピュータはパルス信号を出力できなくなる。すると、異常監視装置は、待機状態のマイクロコンピュータからのパルス信号が所定期間途切れたことによって、マイクロコンピュータに異常が発生したと誤判断してしまう虞がある。

20

【0008】

このような誤判断を防止するため、マイクロコンピュータは、待機状態へ移行する際、異常監視装置に対してマイクロコンピュータの異常監視を禁止する信号（監視禁止信号）を出力した後で、待機状態への移行処理を実行していた。ここで、待機状態への移行処理は、例えば、マイクロコンピュータに備えられた発振回路を停止させる命令の実行である。

【0009】

また、マイクロコンピュータは、待機状態から復帰する際、待機状態からの復帰処理を実行した後で、異常監視装置に対してマイクロコンピュータの異常監視を許可する信号（監視許可信号）を出力していた。ここで、待機状態からの復帰処理は、例えば、復帰後の割込みを禁止する処理や、クロックが正常に発振するまでの遅延期間を設ける処理である。

30

【0010】

尚、特許文献1には、マイクロコンピュータからのパルス出力が所定の時間条件を満たさない時にマイクロコンピュータの異常として検出するウォッチドッグタイマ方式の異常監視装置が開示されている。当該異常監視装置は、監視動作の動作／停止を制御するWDT監視部を備えており、マイクロコンピュータをスタンバイ状態に移行させるスタンバイ信号を、マイクロコンピュータの監視動作の動作／停止を指示する異常監視指示信号としてWDT監視部に入力し、WDT監視部はこの異常監視指示信号によりその動作／停止を制御する。

40

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2004-326629号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

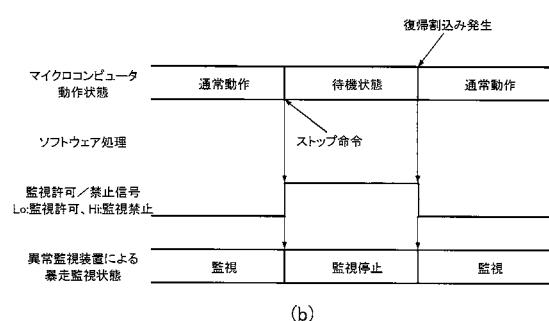

しかし、マイクロコンピュータは、監視禁止信号の出力や待機状態への移行処理、及び、待機状態の復帰や監視許可信号の出力処理を、CPUがメモリに記憶された制御プログラムを実行することで、つまりソフトウェアで行っていた。よって、図1(a)に示すよ

50

うに、監視禁止信号の出力から待機状態への移行まで、及び、待機状態からの復帰から監視許可信号の出力までに、所定期間のタイムラグ  $t_1$ 、 $t_2$  が生じてしまう虞があった。

【0013】

そして、所定期間  $t_1$ 、 $t_2$  にマイクロコンピュータに異常が生じた場合、所定期間  $t_1$ 、 $t_2$  では異常監視装置は異常監視を禁止されているため、マイクロコンピュータに異常が発生していると判断することができなかつた。つまり、従来の異常監視装置では、マイクロコンピュータの異常を監視することができない期間が存在していた。

【0014】

また、特許文献 1 に記載された異常監視装置では、異常監視指示信号はマイクロコンピュータを介すことなく WDT 監視部に入力されているが、監視動作の停止を指示する異常監視指示信号が WDT 監視部に入力すると同時に CPU が停止するわけではないため、CPU が動作しているにもかかわらずマイクロコンピュータの異常を監視することができない期間が存在することは変わらない。

【0015】

尚、特許文献 1 には、スタンバイ状態であってもマイクロコンピュータの異常動作を監視できる異常監視装置も開示されているが、このような異常監視装置では、マイクロコンピュータが異常動作する可能性が極めて少ないスタンバイ状態であっても、電力消費を考慮しているとはいえ異常監視は実行されているため、異常監視を禁止することに比べると省電力化を図ることができない。

【0016】

本発明の目的は、上述した従来の問題点に鑑み、マイクロコンピュータの CPU が動作している間のマイクロコンピュータの異常を確実に監視することのできる電子制御装置、及び異常監視方法を提供する点にある。

【課題を解決するための手段】

【0017】

上述の目的を達成するため、本発明による電子制御装置の特徴構成は、マイクロコンピュータと、前記マイクロコンピュータから出力される異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、前記マイクロコンピュータから出力されるパルス信号に基づいて前記マイクロコンピュータの異常を検出する異常監視回路とを備えている電子制御装置であって、前記マイクロコンピュータは、前記パルス信号の出力制御を行なうとともに、入力される CPU クロックを停止させることで自身をストップ状態に移行させるための制御信号の出力制御を行なう CPU と、前記制御信号の出力状態に応じて前記監視制御信号の出力状態を切り替える監視制御回路とを備えている点にある。

【0018】

上述の構成によれば、監視制御回路は、制御信号の出力状態が CPU の停止を示す状態となったときに、監視制御信号の出力状態を異常監視を禁止する状態とすることによって、CPU の動作及び停止と監視制御信号の出力状態とを同時に切り替えることができるので、図 1 (b) に示すように、監視禁止信号の出力と待機状態への移行まで、及び、待機状態からの復帰と監視許可信号の出力までに、タイムラグが生じることがない。

【発明の効果】

【0019】

以上説明した通り、本発明によれば、マイクロコンピュータの CPU が動作している間のマイクロコンピュータの異常を確実に監視することのできる電子制御装置を提供することができるようになった。

【図面の簡単な説明】

【0020】

【図 1】(a) は従来のマイクロコンピュータの動作状態及び監視禁止 / 許可信号の出力並びに異常監視装置の監視状態を示すタイミングチャート、(b) は本発明によるマイクロコンピュータの動作状態及び監視禁止 / 許可信号の出力並びに異常監視装置の監視状態を示すタイミングチャート

10

20

30

40

50

【図2】車両に備えられた複数の電子制御装置のブロック構成図

【図3】電子制御装置のブロック構成図

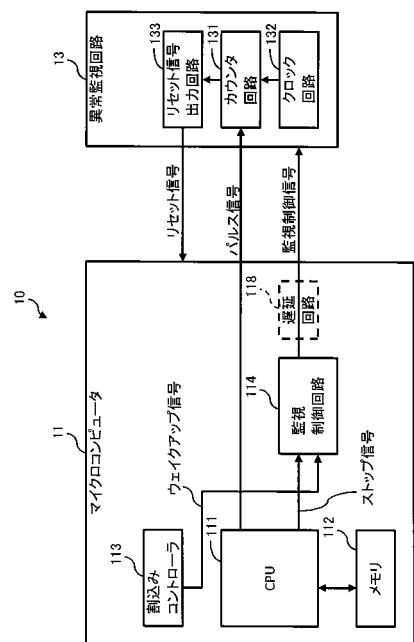

【図4】マイクロコンピュータと異常監視回路のブロック構成図

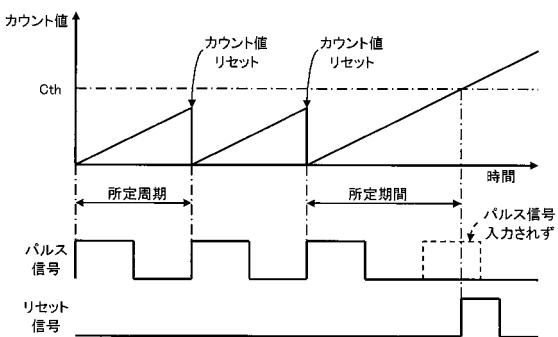

【図5】異常監視回路の動作について説明するためのタイミングチャート

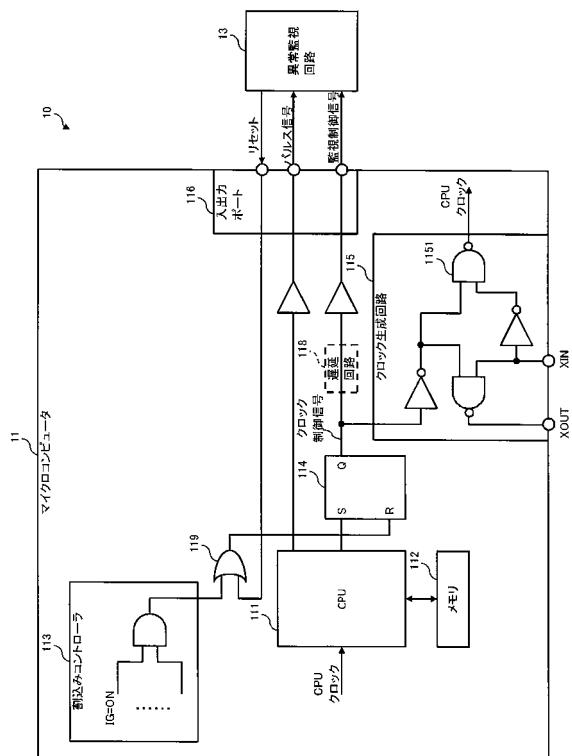

【図6】マイクロコンピュータの回路図

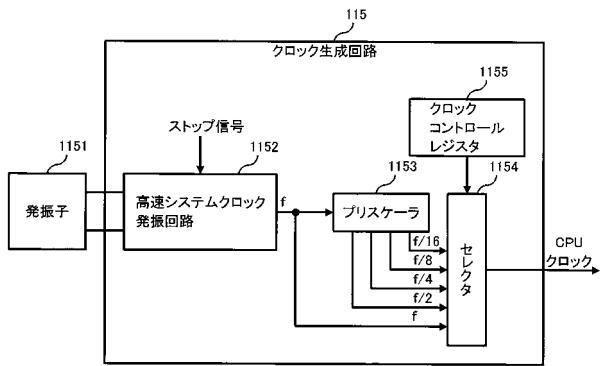

【図7】クロック生成回路のブロック構成図

【図8】(a)は遅延回路の回路図、(b)はRSフリップフロップの回路図、(c)はRSフリップフロップの真理値表

【図9】汎用入出力ポートの回路図

【図10】入力回路を備えた汎用入出力ポートの回路図

10

【図11】マイクロコンピュータの処理について説明するためのフローチャート

【図12】異常監視回路の処理について説明するためのフローチャート

【図13】電子制御装置の処理について説明するためのタイミングチャート

【発明を実施するための形態】

【0021】

以下に、本発明による電子制御装置（以下、ECUと記す。）及び異常監視方法を車両に適用した場合の実施形態について説明する。

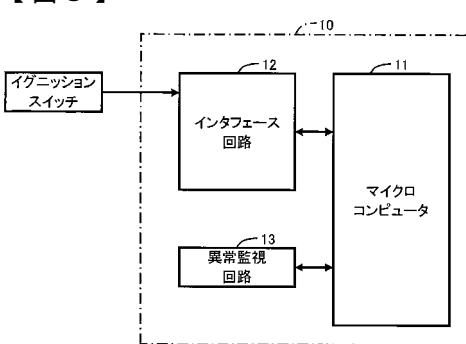

【0022】

ECUは、図2に示すように、イグニッションスイッチがオンされた場合にバッテリから給電される群と、イグニッションスイッチがオフされている場合でもバッテリから給電される群で構成されている。前者には高速のCANバスで接続されたエンジンECU、ミッションECU、及びブレーキECU等が含まれ、後者には低速のCANバスやLINバスで接続されたセキュリティ管理用のECU、ドアロック制御用のECU、及び高速と低速のバスの相互を接続してデータを中継するゲートウェイECU等が含まれる。

20

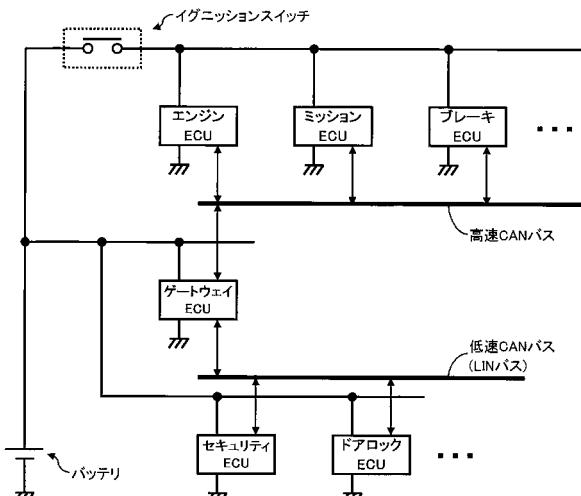

【0023】

本発明によるECUは、後者のECUに具現化されており、図3に示すように、マイクロコンピュータ11、インターフェース回路12、及び異常監視回路13等を備えている。

【0024】

インターフェース回路12は、CANバスやLINバス等のネットワークを介して他のECU等とデータの送受信を実行する通信回路と、各種センサ等からデータを入力してマイクロコンピュータ11が入力可能な信号に変換してマイクロコンピュータ11に出力する入力回路と、マイクロコンピュータ11から出力された制御信号を受け取って制御対象（例えばドアロックスイッチ）等を駆動する信号に変換して当該スタータリレー等に出力する出力回路等とを備えている。

30

【0025】

マイクロコンピュータ11は、図4に示すように、CPU111と、RAMやROM等のメモリ112と、割込みコントローラ113等を備えて構成されており、CPU111がROMに記憶された制御プログラムを実行することでECU10としての定常処理を行なう。

【0026】

40

定常処理は、例えば、ECU10がセキュリティ管理用のECUである場合はセキュリティ管理、ECU10がドアロック用ECUの場合はドアロック制御、ECU10がゲートウェイECUの場合はプロトコル変換処理等である。

【0027】

割込みコントローラ113について詳述する。マイクロコンピュータ11には、単数または複数ビットで構成される割込みレジスタや優先順位設定レジスタ等が割込み要因毎に設けられている。

【0028】

割込みレジスタには、イグニッションスイッチがオンされた場合等に起動される外部割込みや、所定の時間間隔で起動されるタイマ割込み等の割込み要因が発生すると、夫々に

50

対応するタスクを起動するための割込み要求フラグがセットされる。優先順位設定レジスタには、複数の割込みレジスタに同時に割込み要求フラグがセットされたときに優先的に処理すべきタスクを起動するように優先順位が設定される。

【0029】

そして、割込みコントローラ113は、マイクロコンピュータ11に入力された各種信号（例えばイグニッションスイッチがオンされた旨の信号）等に基づいて、これらレジスタにフラグをセットまたはリセットし、各レジスタのフラグの状態に基づいた割込み信号をCPU111等に出力することによって、マイクロコンピュータ11に対する割込み処理を制御する。

【0030】

また、マイクロコンピュータ11は、複数の動作モードを有している。例えば、マイクロコンピュータ11は、通常動作時に高速のクロックで動作するモード（以下、動作モードと記す。）と、クロックを完全に停止させて、ウェイクアップ信号入力等の割込み要因に対する起動処理の実行機能以外の全ての機能を停止するモード（以下、ストップモードと記す。）とを有している。

【0031】

また、マイクロコンピュータ11は、現在のモードが動作モードである場合、所定周期のパルス信号を以下で説明する異常監視回路13へ出力する。また、マイクロコンピュータ11は、異常監視回路13のマイクロコンピュータ11に対する異常監視を許可または禁止する監視制御信号を、後述する監視制御回路114を介して異常監視回路13へ出力する。

【0032】

異常監視回路13は、異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、マイクロコンピュータ11から出力されるパルス信号に基づいてマイクロコンピュータ11の異常を検出する。

【0033】

図4及び図5に示すように、異常監視回路13は、クロック回路132から出力されるクロック信号の立上りエッジ（または立下りエッジ）でカウントアップされ、CPU111から出力されるパルス信号の立上りエッジ（または立下りエッジ）でリセットされ、リセット後にカウントを再起動するカウンタ回路131と、カウンタ回路131にクロック信号を出力するクロック回路132と、リセット信号出力回路133等を備えている。

【0034】

リセット信号出力回路133は、パルス信号が適正な周期（所定周期）でカウンタ回路に入力されないためにカウント値が所定閾値Cthを超える場合、つまりパルス信号の直近の立上りエッジ（または立下りエッジ）から所定期間を超えてパルス信号の立上りエッジ（または立下りエッジ）の入力がない場合、マイクロコンピュータ11にリセット信号を出力する。

【0035】

つまり、異常監視回路13は、パルス信号が所定期間入力されない場合に、マイクロコンピュータ11に異常が発生したと判断して、マイクロコンピュータ11をリセットする回路である。

【0036】

また、異常監視回路13は、異常監視を許可する旨の監視制御信号が入力されると動作（カウンタ回路131によるカウントアップ処理、クロック回路132によるクロック信号出力処理、及びリセット信号出力回路133によるリセット信号出力処理）を開始し、異常開始を禁止する旨の監視制御信号が入力されると当該動作を停止（カウンタ回路131によるカウントアップ停止及びカウント値リセット、クロック回路132によるクロック信号出力停止、及びリセット信号出力回路133によるリセット信号出力停止）する。

【0037】

マイクロコンピュータ11の説明に戻る。図4に示すように、マイクロコンピュータ1

10

20

30

40

50

1は、CPU111の動作を停止させる制御信号の出力状態に応じて監視制御信号の出力状態を切り替える監視制御回路114を備えている。

【0038】

例えば、制御信号がCPU111によりストップ命令が実行されたときに切り替わる信号であり、監視制御回路114は当該信号の切り替わりに応じて異常監視を禁止するように監視制御信号を切り替える。また、制御信号がCPU111をストップモードから動作モードに切り替えるウェイクアップ信号に基づいて切り替わる信号であり、監視制御回路114は当該信号の切り替わりに応じて異常監視を許可するように監視制御信号を切り替える。

【0039】

ストップ命令とは、マイクロコンピュータ11に備えられた発振回路（例えば、高速システムクロック発振回路、高速内蔵発振回路、低速内蔵発振回路、及びサブシステムクロック発振回路等）を停止させ、マイクロコンピュータ11を停止させる命令であり、CPU111によって実行される。そして、ストップ命令の実行を示す信号であるストップ信号が、CPU111から監視制御回路114へ出力される。CPU111は、ストップ命令を実行することによって動作モードからストップモードへ移行する。

【0040】

ストップ命令が実行されたときに切り替わる信号とは、例えば、監視制御回路114にストップ信号が入力されると、それまでの信号レベルに関係なくローレベルに切り替わる信号である。

【0041】

ウェイクアップ信号は、イグニッションスイッチがオンになった場合や異常監視回路13からリセット信号が入力された場合等に、CPU111等に入力される割込み信号であり、CPU111は当該割込み信号を受け取ると、ストップモードから動作モードへ移行する。また、ウェイクアップ信号は、監視制御回路114へも入力される。

【0042】

ウェイクアップ信号に基づいて切り替わる信号とは、例えば、監視制御回路114にウェイクアップ信号が入力されると、それまでの信号レベルに関係なくハイレベルに切り替わる信号である。

【0043】

以下に、監視制御回路114について、図6に基づいて詳述する。尚、図6に示すマイクロコンピュータ11では、ストップ信号とウェイクアップ信号はハイアクティブの信号であるとする。つまり、ストップ信号は、ストップ命令が実行された場合にハイレベルのパルスを出力するが、その他の場合はローレベルを維持している。また、ウェイクアップ信号は、割込みコントローラ113からアクティブレベル（ハイレベル）の割込み信号が入力された場合や異常監視回路13からアクティブレベル（ハイレベル）のリセット信号が入力された場合にOR回路119からハイレベルのパルスを出力するが、割込み信号やリセット信号が入力されない場合はローレベルを維持している。

【0044】

図6では、マイクロコンピュータ11は、CPUクロックを生成して出力するクロック生成回路115を備えている。ここで、CPUクロックは、CPUの動作クロックである。クロック生成回路115は、例えば、図6に示すように、各二個のインバータとNAND回路で構成されており、XIN端子に接続された発振子からの入力信号を、監視制御回路114の出力信号に基づいて、CPU111へ出力し、また、XOUT端子からマイクロコンピュータ11の外部へ出力する回路である。

【0045】

尚、クロック生成回路115は、図6に示すような構成に限らず、例えば、図7に示すような構成であってもよい。図7に示すクロック生成回路115は、発振子1151に接続された高速システムクロック発振回路1152から出力された所定周波数のクロックがプリスケーラ1153で分周されセレクタ1154に入力され、単数または複数ビットで

10

20

30

40

50

構成されたクロックコントロールレジスタ 1155 の設定値に基づいた周波数のクロックが C P U クロックとしてセレクタ 1154 から出力される回路である。図 7 に示すクロック生成回路 115 は、ストップ信号が高速システムクロック発振回路 1152 に入力し、高速システムクロック発振回路 1152 が停止することで停止する。

【 0046 】

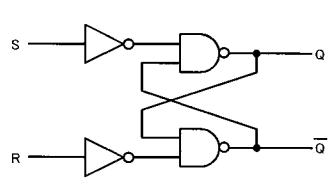

また、図 6 では、監視制御回路 114 は、クロック生成回路 115 を制御するクロック制御回路 114 で構成されている。図 6 で使用される R S フリップフロップ 114 の回路を図 8 ( b ) に示し、図 8 ( b ) の回路の真理値表を図 8 ( c ) に示す。尚、図 6 では、クロック制御回路 114 は、 R S フリップフロップで構成されているが、以下で説明するような機能を有するならば、 R S フリップフロップに限らない。

10

【 0047 】

クロック制御回路 114 は、 C P U 111 からアクティブルベル ( ハイレベル ) のストップ信号が入力されると、つまり R S フリップフロップのセット端子 S にハイレベルの信号が入力されると、クロック生成回路 115 にハイレベルのクロック制御信号を出力し、割込みコントローラ 113 または異常監視回路 13 からアクティブルベル ( ハイレベル ) のウェイクアップ信号が入力されると、つまり R S フリップフロップのリセット端子 R にハイレベルの信号が入力されると、クロック生成回路 115 にローレベルのクロック制御信号を出力する。

【 0048 】

クロック生成回路 115 は、クロック制御回路 114 からローレベルのクロック制御信号が入力されると、 X I N 端子から入力された信号の論理が反転された信号を N A N D 回路 1151 から C P U クロックとして出力するが、クロック制御回路 114 からハイレベルのクロック制御信号が入力されると、 X I N 端子から入力される信号のレベルにかかわらず、 N A N D 回路 1151 からハイレベルの信号を出力する。つまり、ハイレベルの信号が入力された場合には、 C P U クロックは出力されない。

20

【 0049 】

以上より、クロック制御回路 114 は、 C P U 111 によるストップ命令の実行時に生成されるストップ信号に基づいて C P U クロックを停止し、 C P U 111 をストップモードから動作モードに切り替えるウェイクアップ信号に基づいて C P U クロックを出力するように制御する。

30

【 0050 】

そして、マイクロコンピュータ 11 が図 6 の構成である場合の制御信号は、クロック制御信号である。つまり、本発明による E C U 10 のマイクロコンピュータ 11 は、図 6 に示すように、クロック制御回路 114 の出力を入出力ポート 116 と接続することで、クロック制御回路 114 から出力されるクロック制御信号を、クロック生成回路 115 へ出力するだけでなく、入出力ポート 116 を介して監視制御信号として異常監視回路 13 へも出力するように構成されている。尚、以上の説明より、図 6 の場合、監視制御信号は、ハイレベルで異常監視の禁止で、ローレベルで異常監視の許可である。

【 0051 】

上述の構成によれば、制御信号が、 C P U 111 により C P U クロックを停止させるストップ命令が実行されたときに切り替わり、 C P U クロックを出力させるウェイクアップ信号に基づいて切り替わる信号、つまりクロック制御回路から出力されるクロック制御信号である。

40

【 0052 】

従って、制御信号の出力状態に応じて出力状態を切り換えられる監視制御信号の異常監視回路 13 への出力タイミングを、 C P U クロックの停止タイミング及び出力タイミングと同時とすることができます、監視禁止信号の出力と待機状態への移行まで、及び、待機状態からの復帰と監視許可信号の出力までに、タイムラグが生じることはない。

【 0053 】

つまり、本発明による E C U 10 は、マイクロコンピュータと、マイクロコンピュータ

50

から出力される異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、前記マイクロコンピュータから出力されるパルス信号に基づいて前記マイクロコンピュータの異常を検出する異常監視回路とを備え、マイクロコンピュータは、パルス信号の出力制御を行なうとともに、自身をストップ状態に移行させるための制御信号の出力制御を行なうCPUと、制御信号の出力状態に応じて前記監視制御信号の出力状態を切り替える監視制御回路とを備えている。

【0054】

また、図6に示すように、監視制御信号として出力する制御信号と、クロック生成回路115へ出力する制御信号とを、共通の信号であるクロック制御信号とすることにより、一致している必要がある両制御信号に不一致が生じることを防止することができる。

10

【0055】

監視制御信号が禁止状態から許可状態に切り替わるときに、監視制御信号を遅延させる遅延回路を、監視制御信号の信号線に設けてもよい。

【0056】

例えば、図4及び図6に破線で示すように、監視制御信号が禁止状態から許可状態に切り替わる場合にのみ入力信号を所定時間遅延させて出力する遅延回路118を、監視制御回路114の後段に設けておき、マイクロコンピュータ11は、監視制御回路114から出力された制御信号を所定時間遅延させて、監視制御信号として異常監視回路13へ出力する。

【0057】

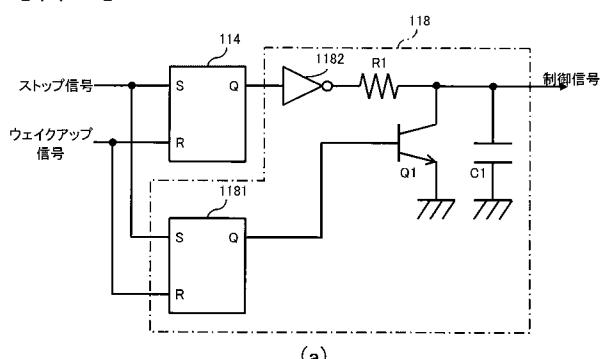

遅延回路118の一例を図8(a)に示し、図8(a)で使用されるRSフリップフロップ114、1181の回路を図8(b)に示し、図8(b)の回路の真理値表を図8(c)に示す。

20

【0058】

図8では、遅延回路118は、クロック制御回路114の出力Qと直列接続されたインバータ1182と、インバータ1182と直列接続された抵抗R1と、一方を抵抗R1と接続され他方を接地されたコンデンサC1と、コレクタを抵抗R1と接続されエミッタを接地されたトランジスタQ1と、クロック制御回路114と同様にストップ信号及びウェイクアップ信号が夫々セットS、リセットRに入力され、出力QがトランジスタQ1のベースに接続されたRSフリップフロップ1181とを備えている。

30

【0059】

クロック制御回路114及びRSフリップフロップ1181のセットSにアクティブルレベル(ハイレベル)のストップ信号が入力されると、クロック制御回路114の出力Q(ハイレベル)はインバータ1182で論理反転することでローレベルとなる。また、RSフリップフロップ1181の出力(ハイレベル)がトランジスタQ1のベースに入力することでトランジスタQ1はオンとなる。その結果、クロック制御回路114にストップ信号が入力された場合には、コンデンサC1に電荷が蓄積されていても、クロック制御回路114から出力されインバータ1182で論理反転された制御信号(ローレベル)は、遅延することなく監視制御信号として後段(入出力ポート116)へ出力される。つまり、遅延回路118は、監視制御信号が許可状態から禁止状態に切り替わるときは、監視制御信号を遅延させない。

40

【0060】

一方、クロック制御回路114及びRSフリップフロップ1181のリセットRにアクティブルレベル(ハイレベル)のウェイクアップ信号が入力されると、クロック制御回路114の出力Q(ローレベル)はインバータで論理反転することでハイレベルとなる。また、RSフリップフロップ1181の出力(ローレベル)がトランジスタQ1のベースに入力することでトランジスタQ1はオフとなる。その結果、クロック制御回路114にウェイクアップ信号が入力された場合には、クロック制御回路114から出力されインバータ1182で論理反転された制御信号(ハイレベル)は、コンデンサC1に電荷が蓄積されるまでの時間だけ遅延して監視制御信号として後段(入出力ポート116)へ出力される

50

。つまり、遅延回路 118 は、監視制御信号が禁止状態から許可状態に切り替わるときは、監視制御信号を遅延させる。

【0061】

尚、図 8 (a) に示す遅延回路 118 を使用する場合、監視制御信号は、ハイレベルで許可状態であり、ローレベルで禁止状態であるが、論理を逆にする場合は、例えば遅延回路 118 の後段にインバータを設ければよい。

【0062】

マイクロコンピュータ 11 は、ウェイクアップ信号が入力されることで異常監視を許可するように監視制御信号を切り替えてからパルス信号が異常監視回路 13 へ出力されるまでに所定時間がかかる場合がある。その理由は、例えば以下の通りである。つまり、マイクロコンピュータ 11 は、ウェイクアップした直後には、CPU 111 の動作が安定するまでの間、CPUクロックの周波数を低くするよう設定されている場合があるため、パルス信号が出力される命令が実行されるまでに遅延が生じてしまうのである。

10

【0063】

その結果、異常監視回路 13 には、監視制御信号によって異常監視を許可されてから所定時間、パルス信号が入力されず、カウンタ回路 131 のカウント値が所定閾値 Cth を超えてしまい、異常監視回路 13 は、マイクロコンピュータ 11 の異常であると誤って判断してしまう虞がある。

【0064】

しかし、上述の構成によれば、監視制御信号の切替時期を遅延する遅延回路 118 を設けることで、上記のような誤った判断が異常監視回路 13 によってなされることを防止することができる。

20

【0065】

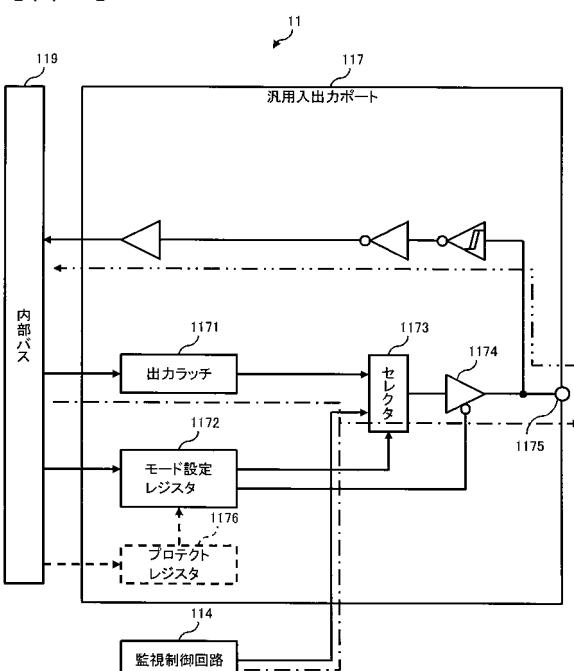

以上の説明では、監視制御信号が出力されるポートは、入出力ポート 116 に備えられた監視制御信号の出力専用のポートである場合について説明したが、図 9 に示すように、監視制御信号が出力されるポートがポートモードを設定するモード設定レジスタ 1172 を備えた汎用入出力ポート 117 で構成され、マイクロコンピュータ 11 のリセット時にモード設定レジスタ 1172 によるポートモードが設定されるまでの間、ハイインピーダンスとなるように設定されていてもよい。

30

【0066】

以下に詳述する。汎用入出力ポート 117 は、例えば、マイクロコンピュータ 11 の内部バス 119 と接続されており、出力データを保持する出力ラッチ 1171 と、ポートモード（入力モードと出力モード）の指定及び入出力するデータの種類の指定を行なうための単数または複数ビットで構成されたモード設定レジスタ 1172 と、モード設定レジスタ 1172 の保持内容に基づいて出力ラッチ 1171 から出力されたデータと監視制御回路 114 から出力された制御信号の何れかを選択して出力するセレクタ 1173 と、モード設定レジスタ 1172 の保持内容に基づいて、入力をそのまま出力するかハイインピーダンスとするかを切り替え可能なスリーステートバッファ 1174 とを備えている。

【0067】

汎用入出力ポート 117 では、モード設定レジスタ 1172 によって出力モードに設定されている場合、スリーステートバッファ 1174 は入力をそのまま出力するように切り替えられる。その結果、データ（出力ラッチ 1171 から出力されたデータまたは監視制御回路 114 から出力された制御信号）は、図 9 に一点鎖線矢印で示す経路で端子 1175 より出力される。

40

【0068】

一方、モード設定レジスタ 1172 によって入力モードに設定されている場合、スリーステートバッファ 1174 はハイインピーダンスに切り替えられる。その結果、データ（外部から端子 1175 を介して入力されたデータ）は、図 9 に二点鎖線矢印で示す経路で内部バス 119 へ出力される。

【0069】

50

また、モード設定レジスタ 1172 は、マイクロコンピュータ 11 のリセット時に、モード設定レジスタ 1172 の設定が可能となった瞬間に、スリーステートバッファ 1174 をハイインピーダンスとするように設定される。

【0070】

上述の構成によれば、監視制御信号の出力専用ポートを余分に設ける必要がないので、ポートを節約することができる。

【0071】

また、マイクロコンピュータ 11 側でポートをハイインピーダンスとなるように設定すると、異常監視回路 13 側で監視制御信号の初期値を設定することができる。つまり、初期値をハイレベルとしたい場合には異常監視回路 13 の監視制御信号が入力されるポートにプルアップ抵抗を設け、初期値をローレベルとしたい場合には当該ポートにプルダウン抵抗を設ければよい。

10

【0072】

また、マイクロコンピュータ 11 のリセット時に、モード設定レジスタ 1172 の設定が可能となった瞬間にポートをハイインピーダンスとなるように設定することで、モード設定レジスタ 1172 にポートモードが設定されるまでの間に、

不適切なレベルの信号が汎用入出力ポート 117 から異常監視回路 13 へ出力されることを防止することができる。その結果、異常監視回路 13 の誤動作の発生可能性を低減することができる。

【0073】

20

ECU 10 は、図 9 に破線で示すように、モード設定レジスタの値の変更を禁止するプロテクトレジスタ 1176 を備えていてもよい。

【0074】

例えば、CPU 111 は、モード設定レジスタの値を変更する際、まず、プロテクトレジスタ 1176 の値を所定値（例えばハイレベル）に設定してモード設定レジスタの値の変更の禁止を解除してから、モード設定レジスタの値を設定する。そして、CPU 111 は、モード設定レジスタの値の設定後、プロテクトレジスタの値を上記とは異なる所定値（例えばローレベル）に設定してモード設定レジスタの値の変更を禁止する。

【0075】

上述の構成によれば、ソフトウェアの暴走等によりモード設定レジスタが不適切な値に書き換えられる危険性を低減することができる。

30

【0076】

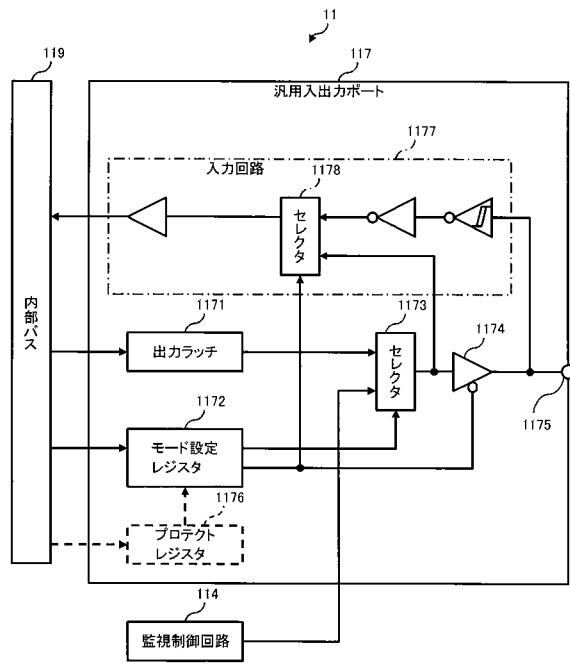

ECU 10 は、監視制御信号が出力されるポートの信号レベルを入力する入力回路をポートに設けていてもよい。

【0077】

例えば、図 10 に示すように、モード設定レジスタ 1172 に保持されている値に基づいて、セレクタ 1173 から出力されたデータと端子 1175 を介して外部より入力されたデータの何れかを選択して内部バス 119 に出力するセレクタ 1178 を備えた入力回路 1177 を設けておく。

【0078】

40

セレクタ 1173 は監視制御回路 114 から出力された制御信号を選択し、セレクタ 1178 はセレクタ 1173 から出力されたデータを選択するように、モード設定レジスタ 1172 を設定することで、監視制御信号が出力されるポートの信号レベルを入力する。

【0079】

上述の構成によれば、監視制御回路 114 や入出力ポート 116 の異常等によって、マイクロコンピュータ 11 が output したつもりの監視制御信号の内容と、実際に出力された監視制御信号の内容が異なるものである場合でも、その事実を早期に発見して適切な対応をことができる。

【0080】

例えば、マイクロコンピュータ 11 は自身に異常があると判断して、即座に全ての動作

50

を停止してストップモードに入るといった対応や、ダイアグノーシスコード等を出力してマイクロコンピュータ11の異常をユーザに知らせるといった対応をとることができる。ユーザに知らせる方法としては、例えば、車両に搭載されたナビゲーション装置の液晶パネル等の表示部への警告メッセージの表示や、スピーカーからの音声メッセージの出力等がある。

#### 【0081】

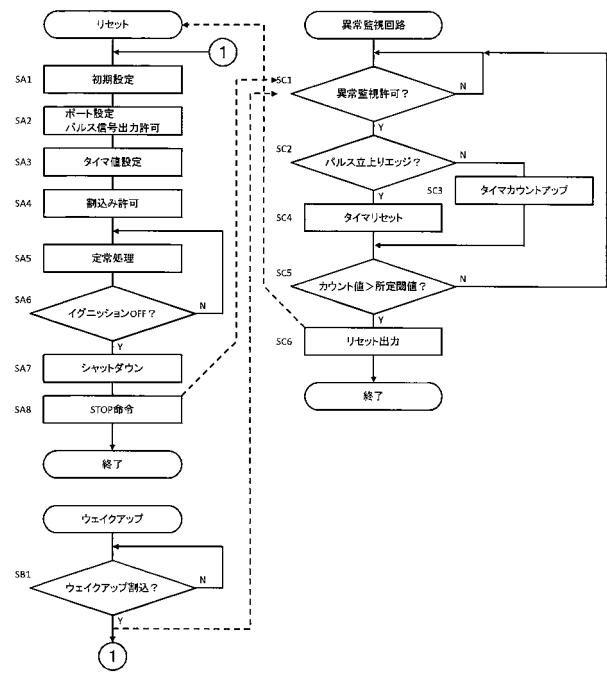

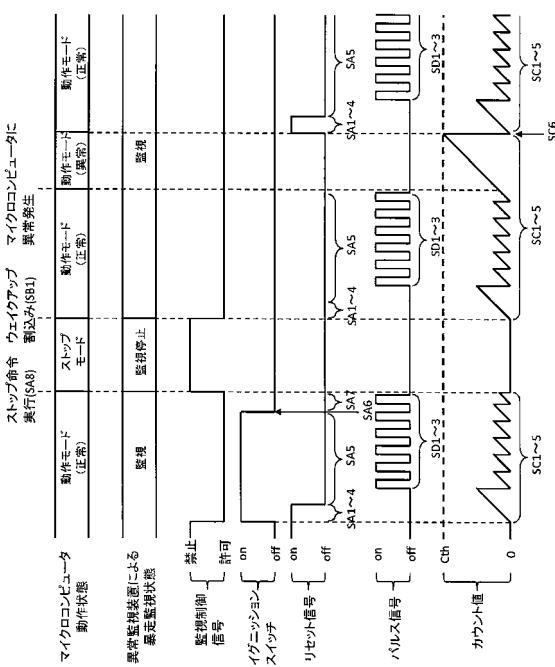

以下、本発明によるECU10の処理について、図11及び図12に示すフローチャート並びに図13に示すタイミングチャートに基づいて説明する。

#### 【0082】

リセットされたECU10のマイクロコンピュータ11は、CPU111が安定すると10、初期設定を実行する(SA1)。初期設定は、例えば、RAMのチェック処理及びクリア処理や、入力ポートへの初期データの入力処理の他、モード設定レジスタに所定値を保持することにより所定のポートモード(例えば動作モード)に設定するポート設定(SA2)、パルス信号の出力許可(SA2)、タイマ割込処理を開始するタイミング設定、換言するとパルス信号の周期設定のための割込タイマ値を単数または複数ビットで構成されるタイマレジスタに設定するタイマ値設定(SA3)、及び割込み許可(SA4)等がある。

#### 【0083】

初期設定が完了すると、ECU10では、マイクロコンピュータ11等によって定常処理が実行される(SA5)。ここで、定常処理は、例えば、ECU10がセキュリティ管理用ECUの場合、セキュリティ管理であり、ECU10がドアロック用ECUの場合、ドアロック制御であり、ECU10がゲートウェイECUの場合、プロトコル変換処理である。尚、これら定常処理は、イグニッションスイッチのオフ時であっても、CPU111が動作モードである場合に実行される。

#### 【0084】

定常処理中に、車両の運転者等によってイグニッションスイッチがオフされると(SA6)、マイクロコンピュータ11は、シャットダウン処理を実行する(SA7)。シャットダウン処理とは、例えば、RAMに記憶されているデータのEEPROM等の不揮発性メモリへの退避である。

#### 【0085】

シャットダウン処理が完了すると、CPU111はストップ命令を実行する(SA8)。CPU111によってストップ命令が実行されると、制御信号の出力状態が異常監視の許可から禁止に切り替わり、状態の切り替わった制御信号は監視制御信号としてマイクロコンピュータ11によって異常監視回路13に出力される。つまり、マイクロコンピュータ11のストップモードへの移行と、異常監視回路13の異常監視の実行状態から停止状態への移行とが略同時に実行される。

#### 【0086】

マイクロコンピュータ11では、ストップモード時に、ウェイクアップ信号が入力される割込みが発生すると(SB1)、制御信号の出力状態が異常監視の禁止から許可に切り替わり、状態の切り替わった制御信号は監視制御信号としてマイクロコンピュータ11によって異常監視回路13に出力される。つまり、マイクロコンピュータ11の動作モードへの移行と、異常監視回路13の異常監視の停止状態から実行状態への移行とは略同時に実行される。

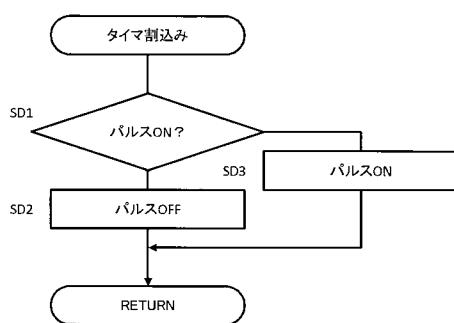

#### 【0087】

また、マイクロコンピュータ11は、タイマ割込みが発生すると、出力しているパルス信号の論理を反転させる。つまり、出力しているパルス信号がオン(例えばハイレベル)の場合は(SD1)、オフ(例えばローレベル)に切り替え(SD2)、出力しているパルス信号がオフの場合は(SD1)、オンに切り替える(SD3)。

#### 【0088】

異常監視回路13は、CPU111によるストップ命令の実行によって(SA8)、マ

10

20

30

40

50

イクロコンピュータ 11 から異常監視回路 13 へ異常監視を禁止する旨の監視制御信号が出力されている場合、動作しない (S C 1)。

【0089】

一方、異常監視回路 13 は、ウェイクアップ信号が入力される割込みによって (S B 1)、マイクロコンピュータ 11 から異常監視回路 13 へ異常監視を許可する旨の監視制御信号が出力されている場合 (S C 1)、マイクロコンピュータ 11 から異常監視回路 13 へ出力されるパルス信号を参照する。

【0090】

異常監視回路 13 は、パルス信号の立上りエッジが入力されていない場合 (S C 2)、カウント回路 131 をカウントアップし (S C 3)、パルス信号の立上りエッジが入力されると (S C 2)、カウンタ回路 131 をリセットする (S C 4)。 10

【0091】

異常監視回路 13 のリセット信号出力回路 133 は、マイクロコンピュータ 11 の異常発生等でマイクロコンピュータ 11 からパルス信号が入力しないことにより、ステップ S C 3 または S C 4 の処理後のカウンタ回路 131 のカウント値が所定閾値 C t h を超えている場合には (S C 5)、マイクロコンピュータ 11 に異常が発生したと判断して、マイクロコンピュータ 11 を再起動させるためのリセット信号をマイクロコンピュータ 11 に出力する (S C 6)。

【0092】

リセット信号を受け取ったマイクロコンピュータ 11 は、リセットされ、ステップ S A 1 で説明した初期設定以降の処理を実行する。 20

【0093】

以上説明した通り、本発明による異常監視方法は、マイクロコンピュータから出力される異常監視を許可または禁止する監視制御信号により異常監視が許可されているときに、マイクロコンピュータから出力されるパルス信号に基づいてマイクロコンピュータの異常を検出する異常監視方法であって、マイクロコンピュータの C P U の動作を停止させる制御信号の出力状態に連動して監視制御信号の出力状態を切り替える方法、つまり、マイクロコンピュータの C P U から出力され、自身をストップ状態に移行させるための制御信号の出力状態に連動して監視制御信号の出力状態を切り替える方法である。

【0094】

以下、別実施形態について説明する。上述の実施形態では、制御信号が C P U 111 によりストップ命令が実行されたときに切り替わる信号である場合について説明したが、制御信号が C P U 111 により低消費電力駆動命令が実行されたときに切り替わる信号であり、監視制御回路 114 は当該信号の切り替わりに応じて異常監視を禁止するように監視制御信号を切り替えてよい。 30

【0095】

低消費電力駆動命令は、例えば、マイクロコンピュータ 11 に複数の発振回路が搭載されている場合に、C P U 111 のモードをストップモードでも動作モードでもないモード、つまり一部の発振回路 (C P U 111 の動作クロック) には発振を停止させるが当該一部の発振回路以外の発振回路には発振を継続させることで消費電力を低減させるモード (低消費電力駆動モード) へ移行させる命令である。 40

【0096】

低消費電力駆動モードは、システム全体を停止させるストップモード程には消費電力を低減させることはできない。しかし、例えば、通常動作時の C P U クロックを生成するための高速内蔵発振回路の発振は停止させるが、所定インターバルで C P U 111 を駆動させて低速クロックで動作させるためのクロック (間欠動作時の C P U クロック) を生成するための低速内蔵発振回路の発振は継続させるようにすると、間欠動作時の処理の再開を迅速に行なうことができる。

【0097】

尚、間欠動作のインターバルは、例えば、上述のタイマ割込処理とは別のタイマ割込処理

50

を開始するタイミング設定のための割込タイマ値を上述のタイマレジスタとは別に設けられた単数または複数ビットで構成されるタイマレジスタに設定することで決定される。具体的には、間欠動作のインターバルは、例えば1時間等に設定される。

#### 【0098】

制御信号を、C P U 1 1 1 によりストップ命令が実行されたときに切り替わる信号とするか、C P U 1 1 1 により低消費電力駆動命令が実行されたときに切り替わる信号とするか、C P U 1 1 1 によりストップ命令または低消費電力駆動の命令の何れかが実行されたときに切り替わる信号とするかといった選択は、マイクロコンピュータの初期設定時（例えば図11のステップS A 1）に、当該選択を行なうために設けられた単数または複数ビットで構成されるレジスタに各選択に対応した値を設定することによって実行する。

10

#### 【0099】

このような低消費電力駆動モードでは、C P U 1 1 1 の動作クロックは停止しておりC P U 1 1 1 は動作しておらず、C P U 1 1 1 に異常が発生することは稀であるため、異常監視回路13によるマイクロコンピュータ11の異常監視を禁止しておくことが、省電力化の観点等から好ましい。

#### 【0100】

よって、上述の構成によれば、マイクロコンピュータ11の消費電力を低減することができる。

#### 【0101】

また、上述の構成によれば、制御信号が、C P U 1 1 1 により低消費電力駆動命令が実行されたときに切り替わる信号である。よって、制御信号の出力状態に応じて出力状態を切り換えられる監視制御信号の異常監視回路13への出力タイミングを、低消費電力駆動モードへの移行タイミングと同時とすることができる。従って、上述の構成によれば、監視禁止信号の出力と待機状態への移行までに、タイムラグが生じることはない。

20

#### 【0102】

上述の実施形態では、本発明によるE C U 1 0 及び異常監視方法を車両に適用した場合について説明したが、異常監視回路を備えており、異常監視回路によるマイクロコンピュータの異常監視の許可と禁止を切り替える必要がある装置を搭載する機器、或いは、マイクロコンピュータの異常監視の許可と禁止を切り替える必要がある異常監視方法を使用する機器であれば、車両以外、例えば船舶や航空機等に適用してもよい。

30

#### 【0103】

また、上述したマイクロコンピュータに備えた監視制御回路の出力信号は、外部に備えた異常監視回路に出力するばかりでなく、C P U の動作が停止するときに、同期して他の外部回路の動作を停止させるために用いることも可能である。

#### 【0104】

尚、上述の実施形態は、本発明の一例に過ぎず、本発明の作用効果を奏する範囲において各ブロックの具体的構成等は適宜変更設計できる（例えば論理レベルのアクティブレベルをハイレベルとローレベルに変える場合の設計変更ができる）ことは言うまでもない。

#### 【符号の説明】

#### 【0105】

1 0 : 電子制御装置

40

1 1 : マイクロコンピュータ

1 3 : 異常監視回路

1 1 1 : C P U

1 1 4 : 監視制御回路

1 1 7 : 汎用入出力ポート

1 1 8 : 遅延回路

1 1 7 2 : モード設定レジスタ

1 1 7 6 : プロテクトレジスタ

1 1 7 7 : 入力回路

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(c)

| 入力 | 出力 |    |  |  |

|----|----|----|--|--|

| S  | R  | Q  |  |  |

| 0  | 0  | 保持 |  |  |

| 0  | 1  | 0  |  |  |

| 1  | 0  | 1  |  |  |

| 1  | 1  | 不定 |  |  |

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開2008-276360(JP, A)

実開平05-079648(JP, U)

特開昭63-313247(JP, A)

特開平11-203173(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11 / 30

G 06 F 15 / 78