(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2024-68760

(P2024-68760A)

(43)公開日 令和6年5月21日(2024.5.21)

## (51)国際特許分類

|        |                  |        |       |         |

|--------|------------------|--------|-------|---------|

| H 01 L | 29/06 (2006.01)  | H 01 L | 29/78 | 6 5 2 P |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 29/739 (2006.01) | H 01 L | 29/06 | 3 0 1 G |

| H 01 L | 29/12 (2006.01)  | H 01 L | 29/06 | 3 0 1 S |

H 01 L 29/78 6 5 2 N 審査請求 未請求 請求項の数 10 O L (全12頁) 最終頁に続く

(21)出願番号

特願2022-179333(P2022-179333)

(22)出願日

令和4年11月9日(2022.11.9)

(71)出願人

000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

100088672

弁理士 吉竹 英俊

100088845

弁理士 有田 貴弘

西 康一

東京都千代田区丸の内二丁目7番3号

三菱電機株式会社内

新田 哲也

東京都千代田区丸の内二丁目7番3号

三菱電機株式会社内

## (54)【発明の名称】 半導体装置

## (57)【要約】

【課題】VLD構造の電界緩和層の上に配置される電極の幅を広く保ちつつ、半導体装置の耐圧を向上させる。

【解決手段】半導体装置を構成する半導体基板50には、第1導電型のドリフト層1が形成されており、終端領域20の半導体基板50の表層部に、不純物濃度が半導体基板50の外側へ向かって減少する第2導電型のウェル層2と、チャネルストップ層としての第1導電型のエミッタ層3が形成されている。終端領域20は、ウェル層2が深く形成された緩和領域21と、緩和領域21の外側に位置し、ウェル層2が浅く形成されたリサーフ領域22と、チャネルストップ層が形成されたチャネルストップ領域23とを備える。緩和領域21上にはゲート配線電極11が形成され、チャネルストップ領域23上にはチャネルストップ電極13が形成される。ゲート配線電極11およびチャネルストップ電極13は、それらの間を電気的に接続する半絶縁膜14で覆われる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1導電型のドリフト層が形成された半導体基板と、

前記半導体基板において半導体素子が形成された活性領域と、

前記半導体基板における前記活性領域の外側の領域である終端領域と、

前記終端領域の前記半導体基板の表層部に形成され、第2導電型の不純物濃度が前記半導体基板の外側へ向かって減少する第2導電型のウェル層と、

前記ウェル層よりも外側の前記半導体基板の表層部に形成された第1導電型のチャネルストップ層と、

を備え、

前記終端領域は、

前記活性領域に隣接し、前記ウェル層が形成された緩和領域と、

前記緩和領域の外側に位置し、前記緩和領域よりも前記ウェル層が浅く形成されたリサーフ領域と、

前記リサーフ領域の外側に位置し、前記チャネルストップ層が形成されたチャネルストップ領域と、

前記緩和領域上に層間絶縁膜を介して形成された電極と、

前記チャネルストップ層に接続するチャネルストップ電極と、

前記電極および前記チャネルストップ電極を覆い、前記電極と前記チャネルストップ電極との間を電気的に接続する半絶縁膜と、

を備える、

半導体装置。

**【請求項 2】**

前記終端領域は、前記リサーフ領域上に前記層間絶縁膜を介して形成された少なくとも1つのフィールドプレート電極をさらに備え、

前記半絶縁膜は、前記電極、前記フィールドプレート電極および前記チャネルストップ電極を覆い、前記電極、前記フィールドプレート電極および前記チャネルストップ電極の間を電気的に接続する、

請求項1に記載の半導体装置。

**【請求項 3】**

前記半絶縁膜は、前記電極、前記フィールドプレート電極および前記チャネルストップ電極の間隔は均一である、

請求項2に記載の半導体装置。

**【請求項 4】**

前記フィールドプレート電極は複数であり、複数の前記フィールドプレート電極の幅は均一である、

請求項2または請求項3に記載の半導体装置。

**【請求項 5】**

前記電極、前記フィールドプレート電極および前記チャネルストップ電極は、同一の導電体材料で形成されている、

請求項2または請求項3に記載の半導体装置。

**【請求項 6】**

前記電極の外端部は前記リサーフ領域へ張り出しており、

前記電極が前記リサーフ領域へ張り出した長さは、0 μm以上30 μm以下である、

請求項1から請求項3のいずれか一項に記載の半導体装置。

**【請求項 7】**

前記チャネルストップ電極の内端部は前記リサーフ領域へ張り出しており、

前記チャネルストップ電極が前記リサーフ領域へ張り出した長さは、0 μm以上30 μm以下である、

請求項1から請求項3のいずれか一項に記載の半導体装置。

10

20

30

40

50

**【請求項 8】**

前記半絶縁膜の抵抗率は、 $1 \times 10^{12}$  ~ cm以下である、

請求項 1 から請求項 3 のいずれか一項に記載の半導体装置。

**【請求項 9】**

前記半絶縁膜の上に形成された絶縁膜をさらに備える、

請求項 1 から請求項 3 のいずれか一項に記載の半導体装置。

**【請求項 10】**

前記半絶縁膜の上面の凹凸を埋めるように前記半絶縁膜を覆う表面保護膜をさらに備える、

請求項 1 から請求項 3 のいずれか一項に記載の半導体装置。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は半導体装置に関するものである。

**【背景技術】****【0002】**

縦型半導体素子の終端構造として、電界緩和層の不純物濃度を半導体基板の外側へ向けて減少させた VLD (Variation of Lateral Doping) 構造が知られている（例えば下記の特許文献 1）。

20

**【先行技術文献】****【特許文献】****【0003】**

【特許文献 1】国際公開第 2015/104900 号

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

特許文献 1 では、VLD 構造の上にフィールドプレート電極を設け、フィールドプレート電極の幅 (W) と間隔 (D) との比率 (W / D) を、半導体基板の外側へ向けて減少させることが提案されている。この構造は、フィールドプレート電極の電位分布を電界緩和層の電位分布に近くして、半導体装置の耐圧を向上させることができる。しかし、この構造では、半導体基板の周縁部でフィールドプレート電極幅が狭くなるため、応力によるフィールドプレート電極のスライド等が生じやすく、信頼性の低下を招く要因となる。

30

**【0005】**

本開示は以上のような課題を解決するためになされたものであり、VLD 構造の電界緩和層の上に配置される電極の幅を広く保ちつつ、半導体装置の耐圧を向上させることを目的とする。

**【課題を解決するための手段】****【0006】**

本開示に係る半導体装置は、第 1 導電型のドリフト層が形成された半導体基板と、前記半導体基板において半導体素子が形成された活性領域と、前記半導体基板における前記活性領域の外側の領域である終端領域と、前記終端領域の前記半導体基板の表層部に形成され、第 2 導電型の不純物濃度が前記半導体基板の外側へ向かって減少する第 2 導電型のウェル層と、前記ウェル層よりも外側の前記半導体基板の表層部に形成された第 1 導電型のチャネルストップ層と、を備え、前記終端領域は、前記活性領域に隣接し、前記ウェル層が形成された緩和領域と、前記緩和領域の外側に位置し、前記緩和領域よりも前記ウェル層が浅く形成されたリサーフ領域と、前記リサーフ領域の外側に位置し、前記チャネルストップ層が形成されたチャネルストップ領域と、前記緩和領域上に層間絶縁膜を介して形成された電極と、前記チャネルストップ層に接続するチャネルストップ電極と、前記電極および前記チャネルストップ電極を覆い、前記電極と前記チャネルストップ電極との間を電気的に接続する半絶縁膜と、を備える、半導体装置。

40

50

## 【発明の効果】

## 【0007】

本開示によれば、配線電極とチャネルトップ電極との間が半絶縁膜により電気的に接続されることで、配線電極とチャネルトップ電極との間の電位分布がウェル層の電位分布に近くなり、半導体装置の耐圧が向上する。また、ウェル層上に幅の狭い電極を設ける必要がないため、応力による電極のスライド等の発生を抑制でき、信頼性の向上にも寄与できる。

## 【図面の簡単な説明】

## 【0008】

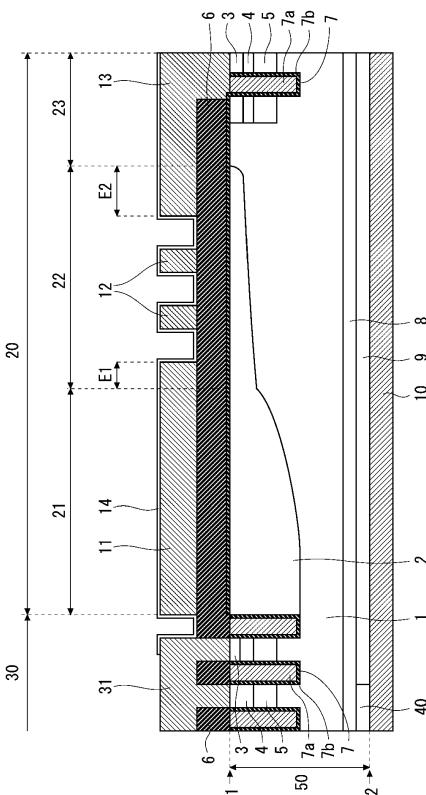

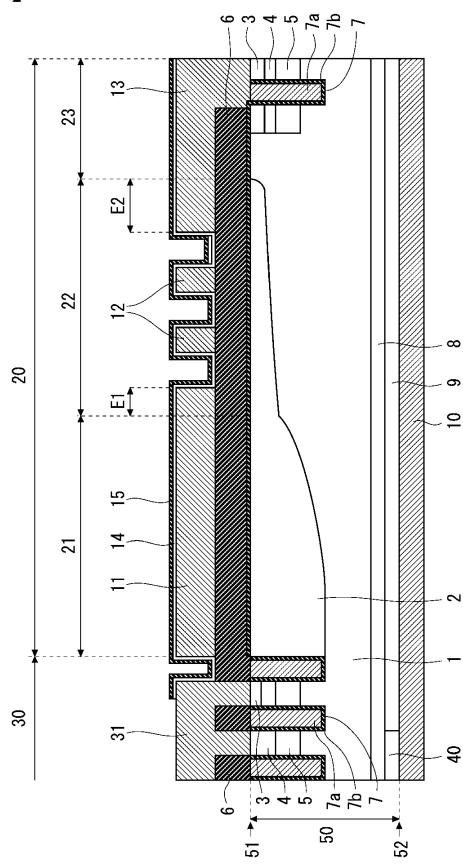

【図1】実施の形態1に係る半導体装置の断面図である。

10

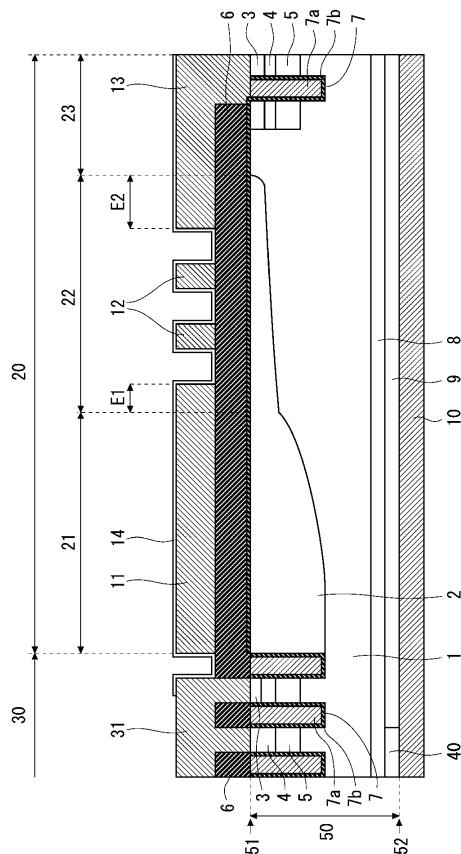

【図2】ゲート配線がリサーフ領域へ張り出した長さ(E1)と半導体装置の耐圧との関係を示すグラフである。

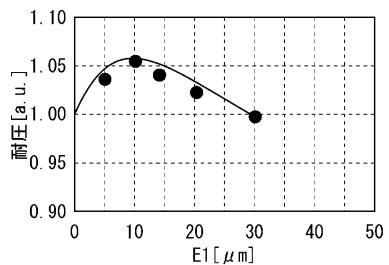

【図3】チャネルトップ電極がリサーフ領域へ張り出した長さ(E2)と半導体装置の耐圧との関係を示すグラフである。

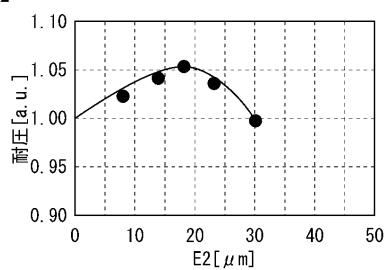

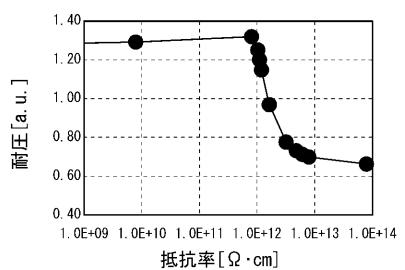

【図4】半絶縁膜の抵抗率と半導体装置の耐圧との関係を示すグラフである。

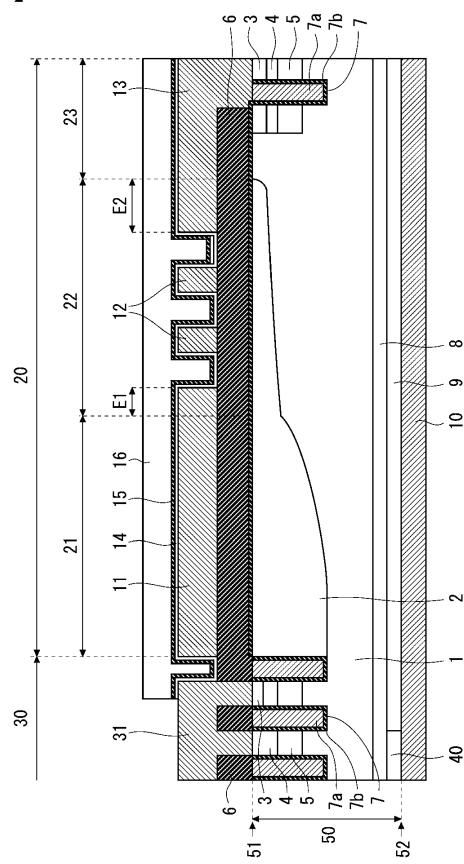

【図5】実施の形態5に係る半導体装置の断面図である。

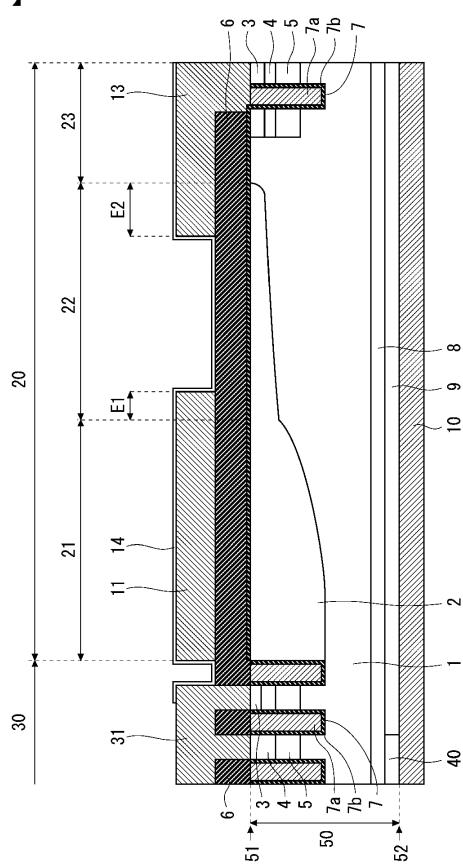

【図6】実施の形態6に係る半導体装置の断面図である。

【図7】実施の形態7に係る半導体装置の断面図である。

## 【発明を実施するための形態】

## 【0009】

20

## &lt;実施の形態1&gt;

図1は、実施の形態1に係る半導体装置の断面図を示す。本実施の形態では、半導体装置として、IGBT (Insulated Gate Bipolar Transistor) とFWD (Free Wheeling Diode) とを1チップで構成したRC-IGBT (Reverse Conducting IGBT) を示すが、半導体装置は、例えばMOSFET (Metal Oxide Semiconductor Field Effect Transistor) やSBD (Schottky Barrier Diode) などでもよい。また、以下の説明では、第1導電型をN型、第2導電型をP型として説明するが、それとは逆に、第1導電型をP型、第2導電型をN型としてもよい。

## 【0010】

図1に示すように、実施の形態1に係る半導体装置は、半導体基板50を用いて形成されている。ここで、図1における半導体基板50の上側の主面を第1主面51、半導体基板50の下側の主面を第2主面52と定義する。

30

## 【0011】

半導体基板50の材料は、シリコン(Si)の他、炭化珪素(SiC)、窒化ガリウム(GaN)、ダイヤモンドなどのワイドバンドギャップ半導体でもよい。半導体基板50の材料としてワイドバンドギャップ半導体を用いた場合、シリコンを用いた半導体装置と比較して、高電圧、大電流、高温での動作に優れた特性が得られる。また、半導体基板50は、FZ (Floating Zone) 法で形成されるFZ基板、MCZ (Magneticfield applied Czochralski) で形成される基板、エピタキシャル成長法によって形成されるエピタキシャル基板のいずれでもよい。

40

## 【0012】

半導体基板50の第1主面51と第2主面52との間には、第1導電型のドリフト層1が形成されている。また、半導体基板50には、半導体素子としてのRC-IGBTが形成された活性領域30と、活性領域30を取り囲む終端領域20とが規定されている。

## 【0013】

まず、活性領域30の構成を説明する。

## 【0014】

活性領域30には、半導体基板50の第1主面51側の表層部に第2導電型のベース層4が形成されており、ベース層4の表層部にエミッタ層3が選択的に形成されている。また、本実施の形態では、ベース層4とドリフト層1との間に、ドリフト層1よりも不純物

50

のピーク濃度が高い第1導電型のキャリア蓄積層5を形成している。

【0015】

半導体基板50の第1正面51には、エミッタ層3に隣接し、ベース層4およびキャリア蓄積層5を貫通してドリフト層1に達するトレンチ7が形成されている。トレンチ7の側面および底面にはゲート絶縁膜7bが形成されている。また、トレンチ7内に埋め込まれるように、ゲート電極7aがゲート絶縁膜7b上に形成されている。

【0016】

半導体基板50の第1正面51上には、ゲート電極7aを覆うように層間絶縁膜6が形成されている。層間絶縁膜6の上には、エミッタ電極31が形成されている。エミッタ電極31は、層間絶縁膜6に形成されたコンタクトホールを介してエミッタ層3およびベース層4と電気的に接続されている。

【0017】

半導体基板50の第2正面52側の表層部には、第2導電型のコレクタ層9と第1導電型のカソード層40とが、それぞれ選択的に形成されている。また、本実施の形態では、コレクタ層9およびカソード層40とドリフト層1との間に、ドリフト層1よりも不純物のピーク濃度が高い第1導電型のバッファ層8を形成している。半導体基板50の第2正面52上には、コレクタ層9およびカソード層40と電気的に接続するコレクタ電極10が形成されている。

【0018】

次に、終端領域20の構成を説明する。

10

【0019】

図1に示すように、上述したドリフト層1、バッファ層8、コレクタ層9、コレクタ電極10および層間絶縁膜6は、活性領域30だけでなく終端領域20にも形成されている。

20

【0020】

終端領域20には、半導体基板50の第1正面51側の表層部に、電界緩和層として、第2導電型のウェル層2が形成されている。終端領域20は、半導体基板50の内側から順に、活性領域30に隣接し、ウェル層2が比較的深く形成された緩和領域21と、緩和領域21の外側に位置し、緩和領域21よりもウェル層2が浅く形成されたリサーフ領域22と、リサーフ領域22よりも外側に位置するチャネルストップ領域23とに分けられる。本実施の形態では、緩和領域21のウェル層2における第2導電型の不純物濃度のピークの位置を、リサーフ領域22のウェル層2における第2導電型の不純物濃度のピークの位置よりも深い位置（第1正面51から遠い位置）にすることによって、緩和領域21のウェル層2をリサーフ領域22のウェル層2よりも深くしている。ただし、ウェル層2の深さは不純物濃度によっても調整できるため、例えば、リサーフ領域22のウェル層2における第2導電型の不純物濃度を、緩和領域21のウェル層2における第2導電型の不純物濃度をよりも下げることで、リサーフ領域22のウェル層2を緩和領域21のウェル層2よりも浅くすることができる。よって、緩和領域21のウェル層2における第2導電型の不純物濃度のピークの位置と、リサーフ領域22のウェル層2における第2導電型の不純物濃度のピークの位置とは同じ深さでもよい。

30

【0021】

ウェル層2は、第2導電型の不純物濃度が半導体基板50の外側へ向かって減少する、いわゆるVLD構造の不純物領域である。すなわち、緩和領域21では、ウェル層2の第2導電型の不純物濃度が、活性領域30の外周部から緩和領域21の外周部へ向かって減少する。また、リサーフ領域22では、ウェル層2の第2導電型の不純物濃度が、緩和領域21の外周部からリサーフ領域22の外周部に向かって減少する。

40

【0022】

チャネルストップ領域23には、活性領域30と同様に、半導体基板50の第1正面51側の表層部に第1導電型のエミッタ層3が形成されており、このエミッタ層3はチャネルストップ層として機能する。また、本実施の形態では、図1のように、ベース層4、キ

50

ヤリア蓄積層 5、トレンチ 7、ゲート電極 7 a およびゲート絶縁膜 7 b も、チャネルストップ領域 2 3 に設けている。ただし、これらは省略されてもよい。

【 0 0 2 3 】

終端領域 2 0 の層間絶縁膜 6 の上には、ゲート配線電極 1 1、フィールドプレート電極 1 2 およびチャネルストップ電極 1 3 が形成されている。ゲート配線電極 1 1 は、不図示の領域でゲート電極 7 a と接続しており、緩和領域 2 1 に形成され、且つ、その外端部はリサーフ領域 2 2 に張り出している。フィールドプレート電極 1 2 は、リサーフ領域 2 2 に 1 つ以上（図 1 では 2 つ）形成されている。チャネルストップ電極 1 3 は、チャネルストップ領域 2 3 に形成され、且つ、その内端部はリサーフ領域 2 2 に張り出している。また、チャネルストップ電極 1 3 は、層間絶縁膜 6 に形成されたコンタクトホールを通してチャネルストップ層であるチャネルストップ領域 2 3 のエミッタ層 3 と電気的に接続されている。

【 0 0 2 4 】

ゲート配線電極 1 1、フィールドプレート電極 1 2 およびチャネルストップ電極 1 3 は、半絶縁膜 1 4 で覆われている。よって、ゲート配線電極 1 1、フィールドプレート電極 1 2 およびチャネルストップ電極 1 3 は、それぞれ離間しているが、半絶縁膜 1 4 を通して電気的に繋がる。この構成により、フィールドプレート電極 1 2 の幅を広く保ちながら、フィールドプレート電極 1 2 の電位分布を電界緩和層であるウェル層 2 の電位分布に近くでき、半導体装置の耐圧を向上させることができる。また、フィールドプレート電極 1 2 の幅が広く保たれることで、半導体装置のチップを封止する封止材（例えば樹脂など）からの応力によってフィールドプレート電極 1 2 のスライドが発生することが防止され、半導体装置の信頼性が向上する。フィールドプレート電極 1 2 のアスペクト比（高さ／幅）は、1 以下であることが望ましい。

【 0 0 2 5 】

さらに、上記の構成により、フィールドプレート電極 1 2 を単層にすることができ、終端構造の形成にかかる製造コストを低減することができる。なお、ゲート配線電極 1 1、フィールドプレート電極 1 2 およびチャネルストップ電極 1 3 は、エミッタ電極 3 1 と同一の導電体材料で形成することができ、そうすることにより製造コストの低減に寄与できる。

【 0 0 2 6 】

ゲート配線電極 1 1、フィールドプレート電極 1 2 およびチャネルストップ電極 1 3 の各電極の間隔は均一であることが好ましい。そうすることにより、半導体装置の耐圧が安定化する。また、フィールドプレート電極 1 2 を複数設ける場合、複数のフィールドプレート電極 1 2 の幅は均一であることが好ましい。そうすることにより、フィールドプレート電極 1 2 のスライドの発生を防止することができる。

【 0 0 2 7 】

< 実施の形態 2 >

実施の形態 1 に係る半導体装置（図 1）における、ゲート配線電極 1 1 がリサーフ領域 2 2 へ張り出した長さ、すなわち、緩和領域 2 1 とリサーフ領域 2 2 との境界からゲート配線電極 1 1 の外端までの長さ（E 1）と、半導体装置の耐圧との関係を図 2 に示す。なお、ゲート配線電極 1 1 の外端が、緩和領域 2 1 とリサーフ領域 2 2 との境界よりも内側に位置する場合、E 1 は負の値となる。

【 0 0 2 8 】

図 2 のように、半導体装置の耐圧は E 1 に対して極大値を有する。その理由は、E 1 を小さくすると緩和領域 2 1 とリサーフ領域 2 2 との境界に電界が集中して耐圧が低下し、E 1 を大きくするとリサーフ領域 2 2 上に配置できるフィールドプレート電極 1 2 の個数が少なくなつて耐圧が低下するためである。そこで実施の形態 2 では、E 1 を 0  $\mu\text{m}$  以上 30  $\mu\text{m}$  以下とすることで、半導体装置の耐圧を向上させる。

【 0 0 2 9 】

< 実施の形態 3 >

10

20

30

40

50

実施の形態 1 に係る半導体装置（図 1）における、チャネルトップ電極 13 がリサーフ領域 22 へ張り出した長さ、すなわち、リサーフ領域 22 とチャネルトップ領域 23 との境界からチャネルトップ電極 13 の外端までの長さ（E2）と、半導体装置の耐圧との関係を図 3 に示す。なお、チャネルトップ電極 13 の内端が、リサーフ領域 22 とチャネルトップ領域 23 との境界よりも外側に位置する場合、E2 は負の値となる。

【0030】

図 3 のように、半導体装置の耐圧は E2 に対して極大値を有する。その理由は、E2 を小さくするとリサーフ領域 22 とチャネルトップ領域 23 との境界に電界が集中して耐圧が低下し、E2 を大きくするとリサーフ領域 22 上に配置できるフィールドプレート電極 12 の個数が少なくなつて耐圧が低下するためである。そこで実施の形態 2 では、E2 10 を 0 μm 以上 30 μm 以下とすることで、半導体装置の耐圧を向上させる。

【0031】

< 実施の形態 4 >

実施の形態 1 に係る半導体装置（図 1）における、半絶縁膜 14 の抵抗率と半導体装置の耐圧との関係を図 4 に示す。

【0032】

図 4 のように、半絶縁膜 14 の抵抗率が一定値を超えると、半導体装置の耐圧が低下する。その理由は、半絶縁膜 14 の抵抗率を高くすると、ゲート配線電極 11、フィールドプレート電極 12 およびチャネルトップ電極 13 の各電極の間の電位分布が不安定になり、耐圧が低下するためである。そこで実施の形態 4 では、半絶縁膜 14 の抵抗率を 1 × 20 10<sup>12</sup> ~ cm 以下とすることで、半導体装置の耐圧を向上させる。

【0033】

< 実施の形態 5 >

図 5 は、実施の形態 5 に係る半導体装置の断面図である。図 5 の構成は、図 1 の構成に対し、半絶縁膜 14 の上に絶縁膜 15 を設けたものである。絶縁膜 15 は、半絶縁膜 14 の形成工程よりも後の製造プロセスや、半導体装置のチップを封止する封止材から、半絶縁膜 14 を保護し、半導体装置の信頼性を向上させることができる。

【0034】

< 実施の形態 6 >

図 6 は、実施の形態 6 に係る半導体装置の断面図である。図 6 の構成は、図 5 の構成に対し、絶縁膜 15 の上に表面保護膜 16 を設けたものである。なお、表面保護膜 16 は、図 1 の構成に対して設けられてもよい。すなわち、表面保護膜 16 は、半絶縁膜 14 上に設けられてもよい。

【0035】

実施の形態 7 に係る半導体装置では、ゲート配線電極 11、フィールドプレート電極 12、チャネルトップ電極 13 の形状に応じて半絶縁膜 14 の上面に生じた凹凸が表面保護膜 16 によって埋められる。そのため、ゲート配線電極 11、フィールドプレート電極 12、チャネルトップ電極 13 の各電極の間は、表面保護膜 16 によって埋められる。表面保護膜 16 は、半導体装置のチップを封止する封止材からフィールドプレート電極 12 に加わる応力を緩和し、半導体装置の信頼性を向上させることができる。

【0036】

< 実施の形態 7 >

図 7 は、実施の形態 7 に係る半導体装置の断面図である。図 7 の構成は、図 1 の構成からフィールドプレート電極 12 を省略したものである。よって、本実施の形態では、半絶縁膜 14 は、ゲート配線電極 11 およびチャネルトップ電極 13 を覆い、ゲート配線電極 11 とチャネルトップ電極 13 との間を電気的に接続する。なお、図 5 または図 6 の構成から、フィールドプレート電極 12 を省略してもよい。

【0037】

実施の形態 7 に係る半導体装置では、終端領域 20 の半導体装置ゲート配線電極 11 とチャネルトップ電極 13 との間が、離散的に配置されたフィールドプレート電極 12 を

10

20

30

40

50

介することなく、連続的に配置された半絶縁膜 14 によって電気的に接続される。よって、半導体装置ゲート配線電極 11 とチャネルストップ電極 13 との間の電位分布が滑らかになり、半導体装置の耐圧の向上に寄与できる。

【0038】

なお、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略したりすることが可能である。

【0039】

<付記>

以下、本開示の諸態様を付記としてまとめて記載する。

【0040】

(付記1)

第1導電型のドリフト層が形成された半導体基板と、

前記半導体基板において半導体素子が形成された活性領域と、

前記半導体基板における前記活性領域の外側の領域である終端領域と、

前記終端領域の前記半導体基板の表層部に形成され、第2導電型の不純物濃度が前記半導体基板の外側へ向かって減少する第2導電型のウェル層と、

前記ウェル層よりも外側の前記半導体基板の表層部に形成された第1導電型のチャネルストップ層と、

を備え、

前記終端領域は、

前記活性領域に隣接し、前記ウェル層が形成された緩和領域と、

前記緩和領域の外側に位置し、前記緩和領域よりも前記ウェル層が浅く形成されたリサーフ領域と、

前記リサーフ領域の外側に位置し、前記チャネルストップ層が形成されたチャネルストップ領域と、

前記緩和領域上に層間絶縁膜を介して形成された電極と、

前記チャネルストップ層に接続するチャネルストップ電極と、

前記電極および前記チャネルストップ電極を覆い、前記電極と前記チャネルストップ電極との間を電気的に接続する半絶縁膜と、

を備える、

半導体装置。

【0041】

(付記2)

前記終端領域は、前記リサーフ領域上に前記層間絶縁膜を介して形成された少なくとも1つのフィールドプレート電極をさらに備え、

前記半絶縁膜は、前記電極、前記フィールドプレート電極および前記チャネルストップ電極を覆い、前記電極、前記フィールドプレート電極および前記チャネルストップ電極の間を電気的に接続する、

付記1に記載の半導体装置。

【0042】

(付記3)

前記半絶縁膜は、前記電極、前記フィールドプレート電極および前記チャネルストップ電極の間隔は均一である、

付記2に記載の半導体装置。

【0043】

(付記4)

前記フィールドプレート電極は複数であり、複数の前記フィールドプレート電極の幅は均一である、

付記2または付記3に記載の半導体装置。

【0044】

10

20

30

40

50

## (付記 5 )

前記電極、前記フィールドプレート電極および前記チャネルストッパ電極は、同一の導電体材料で形成されている、

付記 2 から付記 4 のいずれか一つに記載の半導体装置。

## 【0045】

## (付記 6 )

前記電極の外端部は前記リサーフ領域へ張り出しており、

前記電極が前記リサーフ領域へ張り出した長さは、0  $\mu\text{m}$  以上 30  $\mu\text{m}$  以下である、

付記 1 から付記 5 のいずれか一つに記載の半導体装置。

## 【0046】

10

## (付記 7 )

前記チャネルストッパ電極の内端部は前記リサーフ領域へ張り出しており、

前記チャネルストッパ電極が前記リサーフ領域へ張り出した長さは、0  $\mu\text{m}$  以上 30  $\mu\text{m}$  以下である、

付記 1 から付記 6 のいずれか一つに記載の半導体装置。

## 【0047】

## (付記 8 )

前記半絶縁膜の抵抗率は、 $1 \times 10^{12} \text{ } \cdot \text{cm}$  以下である、

付記 1 から付記 7 のいずれか一つに記載の半導体装置。

## 【0048】

20

## (付記 9 )

前記半絶縁膜の上に形成された絶縁膜をさらに備える、

付記 1 から付記 8 のいずれか一つに記載の半導体装置。

## 【0049】

## (付記 10 )

前記半絶縁膜の上面の凹凸を埋めるように前記半絶縁膜を覆う表面保護膜をさらに備える、

付記 1 から付記 9 のいずれか一つに記載の半導体装置。

## 【符号の説明】

## 【0050】

30

1 ドリフト層、2 ウェル層、3 エミッタ層、4 ベース層、5 キャリア蓄積層、

6 層間絶縁膜、7 トレンチ、7 a ゲート電極、7 b ゲート絶縁膜、8 バッファ層、

9 コレクタ層、10 コレクタ電極、11 ゲート配線電極、12 フィールド

プレート電極、13 チャネルストッパ電極、14 半絶縁膜、15 絶縁膜、16 表

面保護膜、20 終端領域、21 緩和領域、22 リサーフ領域、23 チャネルスト

ッパ領域、30 活性領域、31 エミッタ電極、40 カソード層、50 半導体基板

、51 第1主面、52 第2主面。

40

50

【図面】

【図1】

【図2】

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

【図7】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

| F      | I     |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 3 A |

| H 01 L | 29/78 | 6 5 5 B |

| H 01 L | 29/78 | 6 5 5 D |

| H 01 L | 29/78 | 6 5 5 F |

| H 01 L | 29/78 | 6 5 7 D |

| H 01 L | 29/06 | 3 0 1 F |

| H 01 L | 29/78 | 6 5 2 J |

| H 01 L | 29/78 | 6 5 2 T |