(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6418757号

(P6418757)

(45) 発行日 平成30年11月7日(2018.11.7)

(24) 登録日 平成30年10月19日(2018.10.19)

|              |                                                                  |

|--------------|------------------------------------------------------------------|

| (51) Int.Cl. | F 1                                                              |

| HO 1 L 23/12 | (2006.01)                                                        |

| HO 1 L 25/10 | (2006.01)                                                        |

| HO 1 L 25/11 | (2006.01)                                                        |

| HO 1 L 25/18 | (2006.01)                                                        |

| HO 1 L 21/60 | (2006.01)                                                        |

|              | HO 1 L 23/12 HO 1 L 23/12 HO 1 L 23/12 HO 1 L 25/14 HO 1 L 21/60 |

|              | Q 501B N Z 311S                                                  |

請求項の数 10 (全 23 頁)

(21) 出願番号 特願2014-40092(P2014-40092)

(22) 出願日 平成26年3月3日(2014.3.3)

(65) 公開番号 特開2015-165533(P2015-165533A)

(43) 公開日 平成27年9月17日(2015.9.17)

審査請求日 平成28年11月28日(2016.11.28)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100087480

弁理士 片山 修平

(74) 代理人 100180459

弁理士 二階堂 裕

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 大井 淳

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 栗原 孝

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法と半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁層が非感光性樹脂からなる第1の多層配線層と、

前記第1の多層配線層内の上面側に備えられ、前記第1の多層配線層の周縁部に配置された複数の外部接続パッドを含む第1配線層と、

前記第1の多層配線層の上に形成され、絶縁層が感光性樹脂からなる第2の多層配線層と、

前記第2の多層配線層に備えられ、前記第1配線層に接続され、かつ前記第1配線層よりも配線ピッチが狭い第2配線層と、

を有し、

前記第2の多層配線層の絶縁層は前記外部接続パッドを露出するように形成され、

前記第1の多層配線層の外部接続パッドの厚みは、前記第2の多層配線層の第2配線層の厚みよりも厚く、

前記第1配線層は、前記第1配線層の上面と前記第1の多層配線層の絶縁層の上面とが同一面となるように、前記第1の多層配線層の前記絶縁層に埋め込まれ、

前記第2の多層配線層は、前記第1の多層配線層の前記絶縁層の上面に接して形成されると共に、前記第2配線層は前記第1配線層の上面にビアを介さずに直接接続されたことを特徴とする配線基板。

## 【請求項 2】

前記第1配線層の上面と前記第1の多層配線層の絶縁層の上面とは研磨面であることを

10

20

特徴とする請求項1に記載の配線基板。

**【請求項 3】**

絶縁層が非感光性樹脂からなる第1の多層配線層と、

前記第1の多層配線層内の上面側に備えられ、複数の外部接続パッドを含む第1配線層と、

前記第1の多層配線層の上に形成され、絶縁層が感光性樹脂からなり、前記第1の多層配線層よりも配線ピッチが狭い第2の多層配線層とを有し、

前記第2の多層配線層の絶縁層は、各々の前記外部接続パッドに対応する複数の接続ホールを備え、前記接続ホールの底面に前記外部接続パッドが露出していることを特徴とする配線基板。

10

**【請求項 4】**

絶縁層が非感光性樹脂からなる第1の多層配線層と、

前記第1の多層配線層内の上面側に備えられ、前記第1の多層配線層の周縁部に配置された複数の外部接続パッドを含む第1配線層と、

前記第1の多層配線層の上に形成され、絶縁層が感光性樹脂からなる第2の多層配線層と、

前記第2の多層配線層に備えられ、前記第1配線層に接続され、かつ前記第1配線層よりも配線ピッチが狭い第2配線層と

を有し、

前記第2の多層配線層の絶縁層は前記外部接続パッドを露出するように形成され、

20

前記第1の多層配線層の外部接続パッドの厚みは、前記第2の多層配線層の第2配線層の厚みよりも厚く、

前記第1配線層は、前記第1配線層の上面と前記第1の多層配線層の絶縁層の上面とが同一面となるように、前記第1の多層配線層の前記絶縁層に埋め込まれ、

前記第2の多層配線層は、前記第1の多層配線層の前記絶縁層の上面に接して形成されると共に、前記第2配線層は前記第1配線層の上面にビアを介さずに直接接続された配線基板と、

前記第2の多層配線層の上にフリップチップ接続された半導体チップとを有することを特徴とする半導体装置。

**【請求項 5】**

30

前記配線基板及び前記半導体チップの上に配置され、前記第1の多層配線層の外部接続パッドにバンプ電極を介して接続された上側配線基板を有することを特徴とする請求項4に記載の半導体装置。

**【請求項 6】**

複数の前記半導体チップが前記第2の多層配線層の上に並んで配置されていることを特徴とする請求項4又は5に記載の半導体装置。

**【請求項 7】**

非感光性樹脂から形成された第1絶縁層にレーザによって第1ビアホールを形成する手法を含む方法により、周縁部に配置された外部接続パッドを含む第1配線層を上面側に備えた第1の多層配線層を形成する工程と、

40

感光性樹脂をフォトリソグラフィでパターニングすることによって、第2ビアホールを備えた第2絶縁層を形成する手法を含む方法により、前記第1の多層配線層の上に、前記第2絶縁層から前記外部接続パッドが露出するように、前記第1配線層に接続される第2配線層を備えた第2の多層配線層を形成する工程と

を有し、

前記第2の多層配線層の配線ピッチが前記第1の多層配線層の配線ピッチよりも狭く設定され、

前記第1の多層配線層の外部接続パッドの厚みは、前記第2の多層配線層の第2配線層の厚みよりも厚く設定され、

前記第1配線層は、前記第1配線層の上面と前記第1絶縁層の上面とが同一面となるよ

50

うに、前記第1絶縁層に埋め込まれ、

前記第2の多層配線層は、前記第1絶縁層の上面に接して形成されると共に、前記第2配線層は前記第1配線層の上面にビアを介さずに直接接続されたことを特徴とする配線基板の製造方法。

【請求項8】

前記第1の多層配線層を形成する工程において、前記第2の多層配線層を形成する工程の前に、

前記第1の多層配線層の第1絶縁層の上面を研磨することにより、前記第1配線層は、前記第1配線層の上面と前記第1絶縁層の上面とが同一面となるように、前記第1絶縁層に埋め込まれて形成されることを特徴とする請求項7に記載の配線基板の製造方法。 10

【請求項9】

前記第2の多層配線層を形成する工程において、

前記第2配線層を形成する工程は、

前記第2の多層配線層の前記第2絶縁層の上及び前記第2ビアホールの内面にシード層を形成する工程と、

前記第2ビアホールを含む領域に開口部が設けられためっきレジスト層を前記シード層の上に形成する工程と、

前記シード層をめっき給電経路に利用する電解めっきにより、前記第2ビアホール及び前記めっきレジスト層の開口部に金属めっき層を形成する工程と、

前記めっきレジスト層を除去する工程と、 20

前記金属めっき層をマスクにして前記シード層を異方性ドライエッティングにより除去する工程とを含むことを特徴とする請求項7又は請求項8に記載の配線基板の製造方法。

【請求項10】

非感光性樹脂から形成された第1絶縁層にレーザによって第1ビアホールを形成する手法を含む方法により、上面側に外部接続パッドを含む第1配線層を備えた第1の多層配線層を形成する工程と、

感光性樹脂をフォトリソグラフィでパターニングすることによって、第2ビアホールを備えた第2絶縁層を形成する手法を含む方法により、前記第1の多層配線層の上に、前記外部接続パッドの上の前記第2絶縁層に接続ホールが配置された第2の多層配線層を形成する工程とを有し、 30

前記第2の多層配線層の配線ピッチが前記第1の多層配線層の配線ピッチよりも狭く設定されることを特徴とする配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板及びその製造方法と半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置の高性能化に伴って実装技術の高密度化が進められている。半導体チップを配線基板に接続する技術としてフリップチップ接続が広く使用されている。フリップチップ接続では、配線基板の電極に半導体チップのバンプ電極がはんだを介して接続される。 40

【0003】

さらには、配線基板上の半導体チップを収容するように、配線基板の上にバンプ電極を介して上側配線基板が接続された半導体装置が開発されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008-85373号公報

【特許文献2】特開2008-166438号公報 50

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

後述する予備的事項の欄で説明するように、図1に示すような積層型の半導体装置では、下側配線基板100は通常のビルドアップ工法を使用して製造されたため、第2配線層320のライン(幅)：スペース(間隔)は $10\mu m : 10\mu m$ 程度が限界である。このため、狭ピッチの接続端子を備えた高性能な半導体チップを横方向に並べてフリップチップ接続する要求に容易には対応できない。

**【0006】**

また、下側配線基板100に薄膜の微細配線を形成できるとしても、外部接続パッドPも微細配線と同一層から形成されるため、外部接続パッドPの十分な機械強度が得られない課題がある。10

**【0007】**

半導体チップを高密度にフリップチップ接続できると共に、信頼性よく上側配線基板を積層できる構造の配線基板及びその製造方法と半導体装置を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

以下の開示の一観点によれば、絶縁層が非感光性樹脂からなる第1の多層配線層と、前記第1の多層配線層内の上面側に備えられ、前記第1の多層配線層の周縁部に配置された複数の外部接続パッドを含む第1配線層と、前記第1の多層配線層の上に形成され、絶縁層が感光性樹脂からなる第2の多層配線層と、前記第2の多層配線層に備えられ、前記第1配線層に接続され、かつ前記第1配線層よりも配線ピッチが狭い第2配線層とを有し、前記第2の多層配線層の絶縁層は前記外部接続パッドを露出するように形成され、前記第1の多層配線層の外部接続パッドの厚みは、前記第2の多層配線層の第2配線層の厚みよりも厚く、前記第1配線層は、前記第1配線層の上面と前記第1の多層配線層の絶縁層の上面とが同一面となるように、前記第1の多層配線層の前記絶縁層に埋め込まれ、前記第2の多層配線層は、前記第1の多層配線層の前記絶縁層の上面に接して形成されると共に、前記第2配線層は前記第1配線層の上面にビアを介さずに直接接続された配線基板が提供される。20

**【0009】**

また、その開示の他の観点によれば、非感光性樹脂から形成された第1絶縁層にレーザによって第1ビアホールを形成する手法を含む方法により、周縁部に配置された外部接続パッドを含む第1配線層を上面側に備えた第1の多層配線層を形成する工程と、感光性樹脂をフォトリソグラフィでパターニングすることによって、第2ビアホールを備えた第2絶縁層を形成する手法を含む方法により、前記第1の多層配線層の上に、前記第2絶縁層から前記外部接続パッドが露出するように、前記第1配線層に接続される第2配線層を備えた第2の多層配線層を形成する工程とを有し、前記第2の多層配線層の配線ピッチが前記第1の多層配線層の配線ピッチよりも狭く設定され、前記第1の多層配線層の外部接続パッドの厚みは、前記第2の多層配線層の第2配線層の厚みよりも厚く設定され、前記第1配線層は、前記第1配線層の上面と前記第1絶縁層の上面とが同一面となるように、前記第1絶縁層に埋め込まれ、前記第2の多層配線層は、前記第1絶縁層の上面に接して形成されると共に、前記第2配線層は前記第1配線層の上面にビアを介さずに直接接続された配線基板の製造方法が提供される。40

**【発明の効果】****【0010】**

以下の開示によれば、第1の多層配線層では、絶縁層が非感光性樹脂から形成され、上面側の周縁部に外部接続パッドが形成されている。

**【0011】**

また、第1の多層配線層の上に外部接続パッドが露出するように第2の多層配線層が配置され、第2の多層配線層の絶縁層は感光性樹脂から形成される。そして、第1の多層配50

線層の配線ピッチは第2の多層配線層の配線ピッチよりも狭く設定されている。

**【0012】**

このようにして、第2の多層配線層は第1の多層配線層よりも微細化されて形成されるため、第2の多層配線層の上に狭ピッチの接続端子を備えた半導体チップを高密度にフリップチップ接続することができる。

**【0013】**

また、第1の多層配線層の外部接続パッドは、配線ピッチの緩い厚膜の配線層と同じ設計ルールで形成できるため、十分な機械強度を有する。これにより、第1の多層配線層の外部接続パッドにバンプ電極を介して上側配線基板を信頼性よく接続することができる。

**【図面の簡単な説明】**

10

**【0014】**

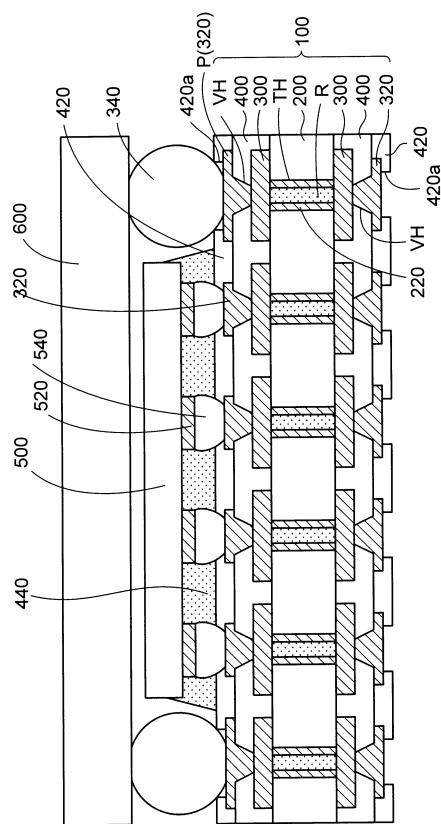

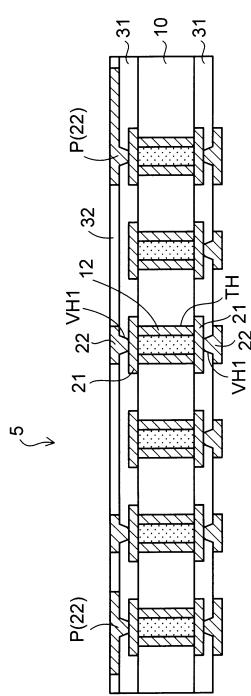

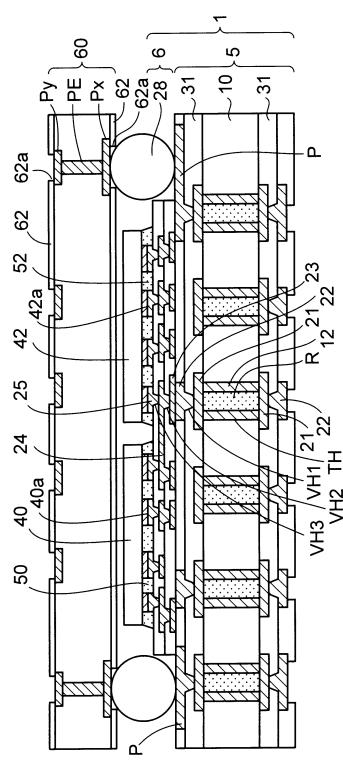

【図1】図1は予備的事項に係る半導体装置を示す断面図である。

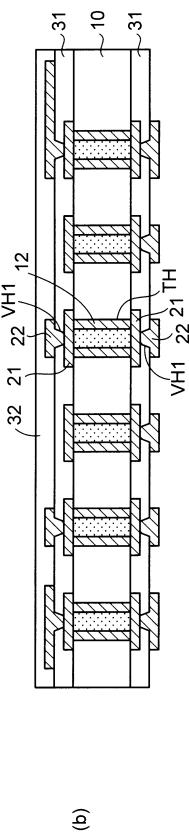

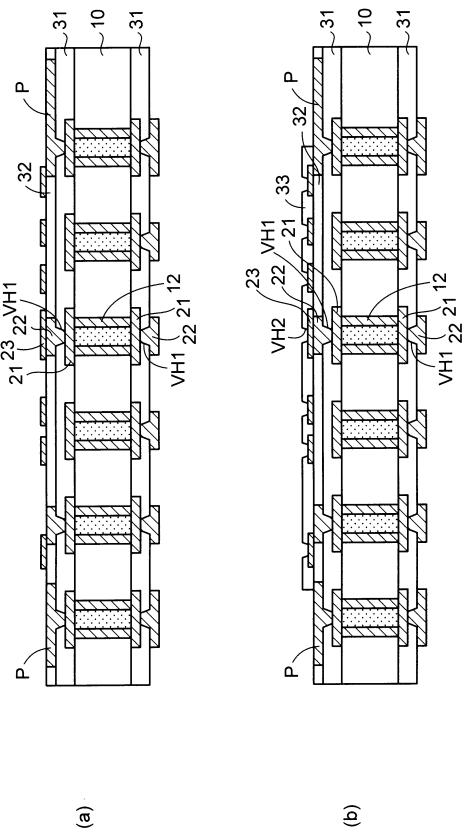

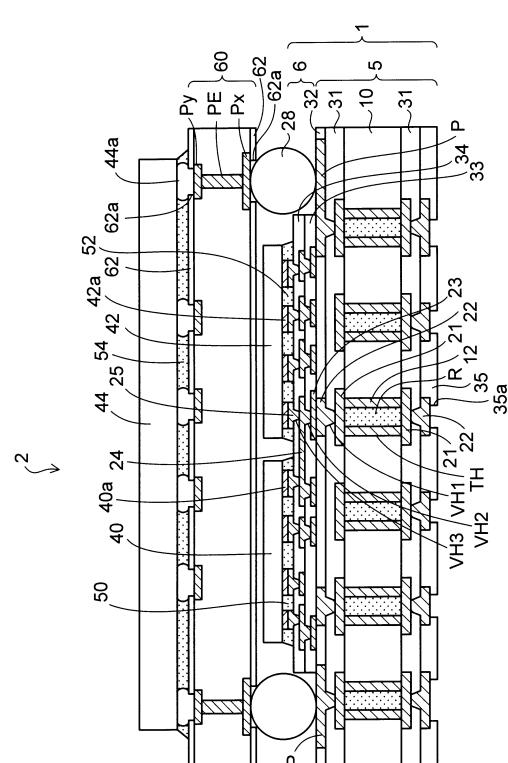

【図2】図2(a)及び(b)は実施形態の配線基板の製造方法を示す断面図(その1)である。

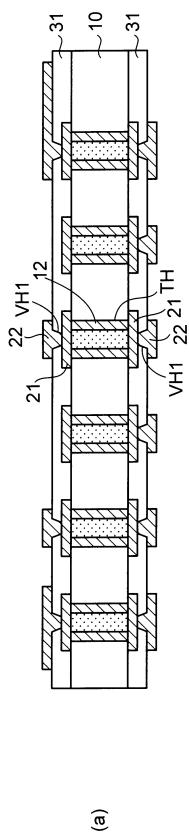

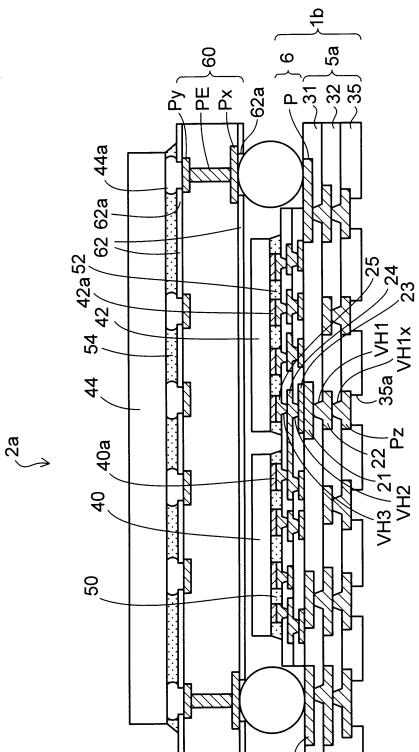

【図3】図3(a)及び(b)は実施形態の配線基板の製造方法を示す断面図(その2)である。

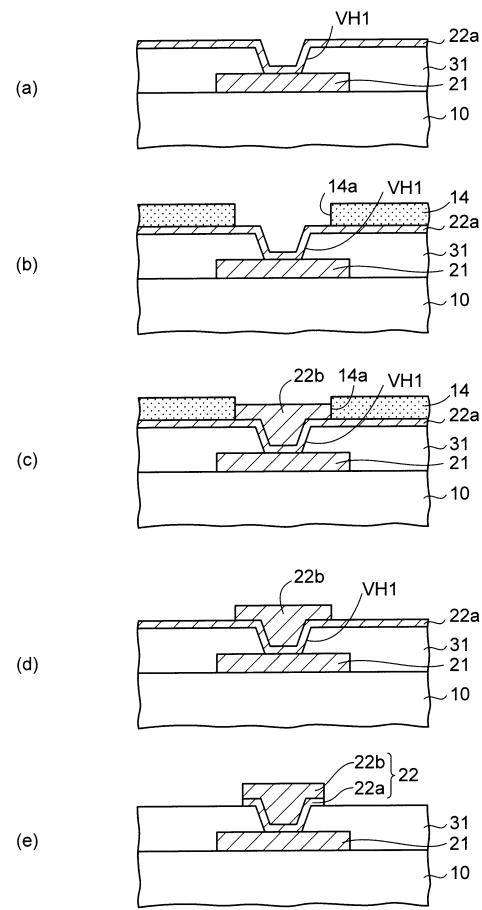

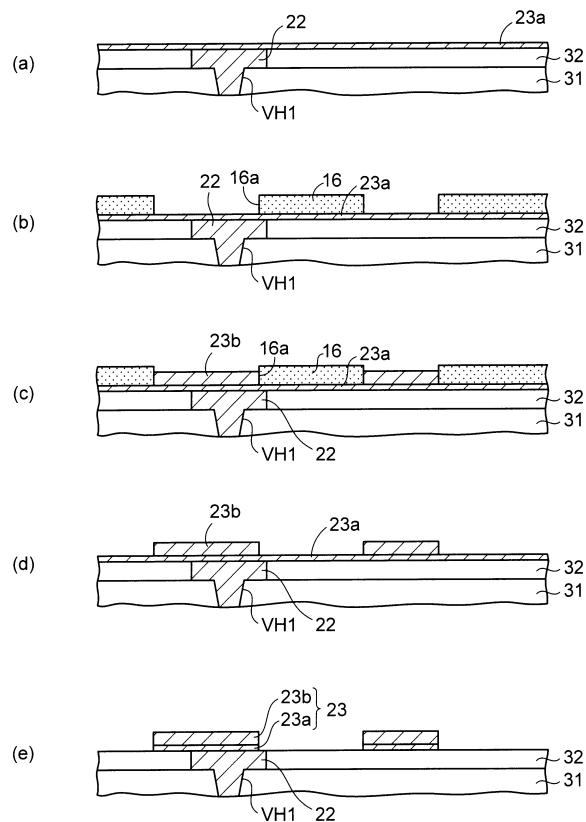

【図4】図4(a)～(e)は実施形態の配線基板の製造方法を示す断面図(その3)である。

【図5】図5は実施形態の配線基板の製造方法を示す断面図(その4)である。

【図6】図6(a)及び(b)は実施形態の配線基板の製造方法を示す断面図(その5)である。

20

【図7】図7(a)～(e)は実施形態の配線基板の製造方法を示す断面図(その6)である。

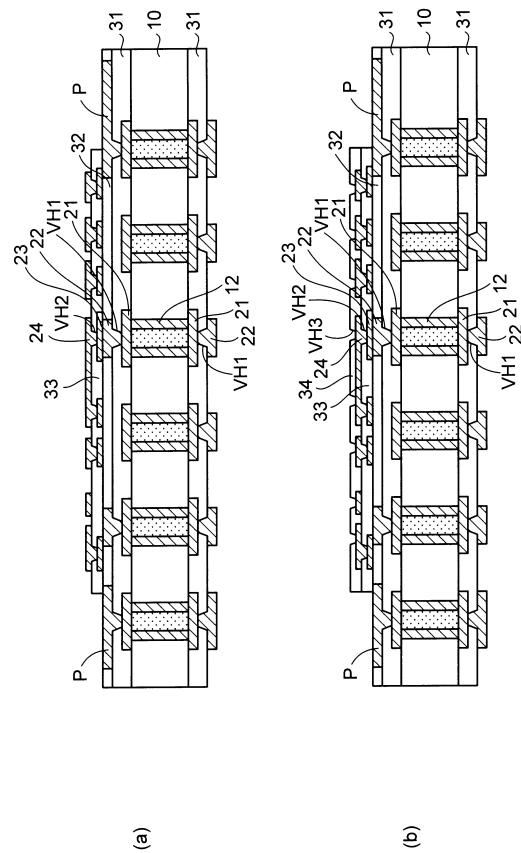

【図8】図8(a)及び(b)は実施形態の配線基板の製造方法を示す断面図(その7)である。

【図9】図9(a)～(e)は実施形態の配線基板の製造方法を示す断面図(その8)である。

【図10】図10は実施形態の配線基板を示す断面図である。

【図11】図11は実施形態の配線基板を使用して半導体装置を製造する方法を示す断面図(その1)である。

30

【図12】図12は図11の構造体を平面からみた縮小平面図である。

【図13】図13は図12において2つの半導体チップの間の領域にも外部接続パッドが配置された形態を示す平面図である。

【図14】図14は実施形態の配線基板を使用して半導体装置を製造する方法を示す断面図(その2)である

【図15】図15は図14の構造体を平面からみた縮小平面図である。

【図16】図16は図15において2つの半導体チップの間の領域にも外部接続パッドが配置された形態を示す平面図である。

【図17】図17は実施形態の配線基板を使用して半導体装置を製造する方法を示す断面図(その3)である。

40

【図18】図18は実施形態の半導体装置を示す断面図である。

【図19】図19は実施形態の第1変形例の半導体装置を示す断面図である。

【図20】図20は実施形態の第2変形例の半導体装置を示す断面図である。

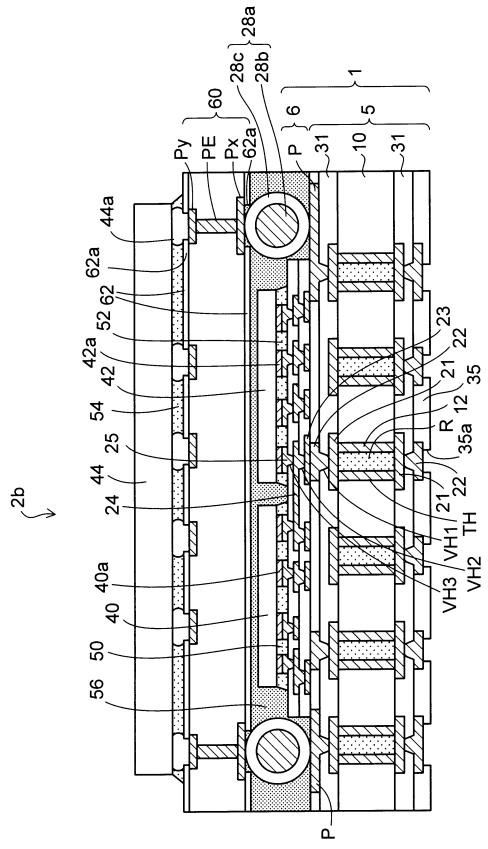

【図21】図21は実施形態の第3変形例の半導体装置を示す断面図である。

**【発明を実施するための形態】**

**【0015】**

以下、実施の形態について、添付の図面を参照して説明する。

**【0016】**

実施形態を説明する前に、基礎となる予備的事項について説明する。図1は予備的事項に係る半導体装置を示す断面図である。

50

**【0017】**

図1に示すように、予備的事項に係る半導体装置の下側配線基板100は、厚み方向の中央部にコア基板200を備え、コア基板200の両面には第1配線層300がそれぞれ形成されている。

**【0018】**

コア基板200にはスルーホールTHが形成されており、スルーホールTHの内壁にはスルーホールめっき層220が形成されている。コア基板200の両面側の第1配線層300はスルーホールめっき層220を介して相互接続されている。また、スルーホールTHの残りの孔には樹脂体Rが充填されている。

**【0019】**

コア基板200の両面側には、第1配線層300に到達するビアホールVHを備えた層間絶縁層400がそれぞれ形成されている。さらに、両面側の層間絶縁層400の上にはビアホールVHを介して第1配線層300に接続される第2配線層320がそれぞれ形成されている。第2配線層320は、下側配線基板100の周縁部に配置された外部接続パッドPを含んで形成される。

**【0020】**

また、両面側の層間絶縁層400の上には、両面側の第2配線層320の接続部及び上面側の外部接続パッドPの上に開口部420aが設けられたソルダレジスト層420がそれぞれ形成されている。

**【0021】**

そして、コア基板200の上面側の第2配線層320の接続部に半導体チップ500の接続端子520がはんだ層540を介してフリップチップ接続されている。半導体チップ500と下側配線基板100との間にアンダーフィル樹脂440が充填されている。

**【0022】**

さらに、下側配線基板100の周縁に配置された外部接続パッドPにバンプ電極340を介して上側配線基板600が接続されている。このようにして、下側配線基板100及び半導体チップ500の上に上側配線基板600が積層され、上側配線基板600の下側領域に半導体チップ500が収容される。

**【0023】**

予備的事項の半導体装置の下側配線基板100は、通常のビルトアップ配線を形成する方法によって製造される。このため、第2配線層320は、ライン(幅) : スペース(間隔)が $10\mu m : 10\mu m$ 程度が限界であり、比較的緩い設計ルールで形成される。

**【0024】**

近年では、半導体チップの高性能化により、半導体チップの接続端子の狭ピッチ化が進められている。そして、図1の半導体チップ500が実装された領域に、高密度な接続端子を備えた半導体チップを実装する要求がある。さらには、高密度な接続端子を備えた2つの半導体チップを並べて実装し、それらを相互接続する要求がある。

**【0025】**

しかし、予備的事項の半導体装置の下側配線基板100の製造方法では、配線層をこれ以上微細化することが困難であるため、高密度な接続端子を備えた半導体チップを実装する要求に対応できない課題がある。

**【0026】**

また、下側配線基板100に薄膜の微細配線を形成できるとしても、下側配線基板100の外部接続パッドPも微細配線と同一層から形成されるため、外部接続パッドPが薄膜のパッドとして形成される。このため、下側配線基板100の外部接続パッドPにバンプ電極340を介して上側配線基板600を接続する際に、外部接続パッドPの機械強度が弱いためクラックなどが発生しやすく、接続の信頼性が低下する課題がある。

**【0027】**

以下に説明する実施形態の配線基板及びその製造方法では、前述した課題を解決することができる。

10

20

30

40

50

**【0028】**

(実施形態)

図2～図9は実施形態の配線基板の製造方法を示す図、図10は実施形態の配線基板を示す図、図11～図18は図10の配線基板を使用する半導体装置を説明するための図である。

**【0029】**

以下、配線基板及び半導体装置の製造方法を説明しながら、配線基板及び半導体装置の構造について説明する。

**【0030】**

最初に、本実施形態の配線基板のベース基板となる第1の多層配線層を形成する方法について説明する。本実施形態では、第1の多層配線層は、ビルドアップ配線基板から形成される。10

**【0031】**

まず、図2(a)に示すような構造のコア基板10を用意する。コア基板10には厚み方向に貫通するスルーホールTHが形成されており、スルーホールTHの内壁にはスルーホールめっき層12が形成されている。コア基板10はガラスエポキシ樹脂などの絶縁材料から形成される。

**【0032】**

また、コア基板10の両面側には第1配線層21がそれぞれ形成されている。両面側の第1配線層21はスルーホールめっき層12を介して相互接続されている、スルーホールTHの残りの孔には樹脂体Rが充填されている。20

**【0033】**

コア基板10のスルーホールTHはドリルなどによって形成される。また、コア基板10に形成されるスルーホールめっき層12及び第1配線層21は、めっき法及びフォトリソグラフィなどを使用して形成される。

**【0034】**

次いで、図2(b)に示すように、コア基板10の両面側に未硬化の樹脂フィルムを貼付し、加熱処理して硬化させることにより、第1層間絶縁層31をそれぞれ形成する。

**【0035】**

その後に、両面側の第1層間絶縁層31をレーザで加工することにより、両面側の第1配線層21の接続部に到達する第1ビアホールVH1をそれぞれ形成する。30

**【0036】**

この手法では、第1ビアホールVH1をレーザで形成するため、第1層間絶縁層31は非感光性樹脂から形成される。樹脂材料としては、エポキシ樹脂又はポリイミド樹脂などが使用される。例えば、第1層間絶縁層31の厚みは10μm～20μm程度であり、第1ビアホールVH1の直径は30μm～50μm程度となる。

**【0037】**

さらに、過マンガン酸法などによって第1ビアホールVH1内をデスマニア処理することにより、樹脂スミアを除去してクリーニングする。

**【0038】**

次いで、図3(a)に示すように、両面側の第1層間絶縁層31の上に、第1ビアホールVH1内のビア導体を介して第1配線層21に接続される第2配線層22を形成する。第2配線層22はセミアディティブ法によって形成される。40

**【0039】**

詳しく説明すると、図4(a)に示すように、第1層間絶縁層31上及び第1ビアホールVH1の内面に無電解めっきにより、厚みが1μm程度の銅などからなるシード層22aを形成する。

**【0040】**

次いで、図4(b)に示すように、第2配線層22が配置される部分に開口部14aが設けられためっきレジスト層14を形成する。50

**【0041】**

続いて、図4(c)に示すように、シード層22aをめっき給電経路に利用する電解めっきにより、めっきレジスト層14の開口部14aに厚みが10μm程度の銅などからなる金属めっき層22bを形成する。その後に、図4(d)に示すように、めっきレジスト層14を除去する。

**【0042】**

さらに、図4(e)に示すように、金属めっき層22bをマスクにしてシード層22aをウェットエッティングにより除去する。これにより、シード層22a及び金属めっき層22bから第2配線層22が形成される。

**【0043】**

次いで、図3(b)に戻って説明すると、コア基板10の上面側の第1層間絶縁層31及び第2配線層22の上に、未硬化の樹脂フィルム貼付し、加熱処理を行って硬化させることにより第2層間絶縁層32を形成する。

**【0044】**

続いて、図5に示すように、第2層間絶縁層32をCMP(Chemical Mechanical Polishing)によって第2配線層22の上面が露出するまで研磨する。これにより、第2配線層22の上面と第2層間絶縁層32の上面とが同一面となる。

**【0045】**

以上により、本実施形態の半導体装置のベース基板となるビルドアップ配線基板から形成される第1の多層配線層5が得られる。第1の多層配線層5の周縁部の第2配線層22が外部接続パッドPとして形成される。このようにして、第1の多層配線層5の上面側の環状の周縁部に複数の外部接続パッドPが並んで配置される。

**【0046】**

第1の多層配線層5として、多面取りの大型基板を使用する場合は、第1の多層配線層5に複数のチップ搭載領域が画定される。図5では、第1の多層配線層5の1つのチップ搭載領域が示されており、外部接続パッドPよりも内側領域がチップ搭載領域となる。

**【0047】**

次に、第1の多層配線層5の上に第2配線層22よりも配線ピッチの狭い第2の多層配線層を形成する方法について説明する。

**【0048】**

図6(a)に示すように、まず、第1の多層配線層5の第2層間絶縁層32の上に、第2配線層22に接続される第3配線層23を形成する。第3配線層23はセミアディティブ法によって形成される。詳しく説明すると、図7(a)に示すように、第2層間絶縁層32及び第2配線層22の上に、スパッタ法によりシード層23aを形成する。

**【0049】**

シード層23aの一例としては、下から順に、厚みが0.05μmのチタン(Ti)層/厚みが0.5μmの銅(Cu)層を形成する。

**【0050】**

次いで、図7(b)に示すように、第3配線層23が配置される部分に開口部16aが設けられためっきレジスト層16をシード層23aの上に形成する。

**【0051】**

続いて、図7(c)に示すように、シード層23aをめっき給電経路に利用する電解めっきにより、めっきレジスト層16の開口部16aに銅などからなる金属めっき層23bを形成する。その後に、図7(d)に示すように、めっきレジスト層16を除去する。

**【0052】**

さらに、図7(e)に示すように、金属めっき層23bをマスクにしてシード層23aを異方性ドライエッティングにより除去する。

**【0053】**

異方性ドライエッティングは、RIE(Reactive Ion Etching)装置、又はICP(Inductively Coupled Plasma)装置などのドライエッティング装置によって行われる。

## 【0054】

異方性ドライエッティングを採用することにより、金属めっき層23bの細りを微小に抑えることができると共に、シード層23aが金属めっき層23bの下端から内側にサイドエッティングすることができない。しかも、スパッタ法を採用することにより、シード層23aを薄膜化できるため、微細化に有利になる。

## 【0055】

以上により、シード層23a及び金属めっき層23bから第3配線層23が形成される。

## 【0056】

このようにして、ライン(幅)：スペース(間隔)が $2\text{ }\mu\text{m} : 2\text{ }\mu\text{m} \sim 3\text{ }\mu\text{m} : 3\text{ }\mu\text{m}$ の微細な第3配線層23を設計スペック内で歩留りよく形成することができる。第3配線層23の厚みは、 $1\text{ }\mu\text{m} \sim 5\text{ }\mu\text{m}$ の範囲、好適には $2\text{ }\mu\text{m} \sim 3\text{ }\mu\text{m}$ の薄膜に設定される。10

## 【0057】

シード層23aが銅から形成される場合は、ドライエッティング時に発生する銅の塩化物は揮発性が低いため、エッティング装置のステージの温度を $100 \sim 200$ に設定して高温雰囲気でエッティングすることが好ましい。

## 【0058】

このように、微細な第3配線層23を形成するには、シード層23aを異方性ドライエッティングで除去することが好ましい。しかし、枚葉式のスピニエッティング装置などを使用することにより、ウェットエッティングであってもシード層23aをある程度精度よく除去することも可能である。20

## 【0059】

このようにして、第3配線層23の配線ピッチを第1の多層配線層5の第1、第2配線層21, 22の配線ピッチよりも狭く設定することができる。

## 【0060】

また、第3配線層23を形成する際にシード層23aを異方性ドライエッティングにより除去する場合は、シード層23aの幅は金属めっき層23bの幅と同一又はそれより広くなる。図7(e)の例では、シード層23aの幅が金属めっき層23bの幅と同一になっている。

## 【0061】

次いで、図6(b)に戻って説明すると、図6(a)の構造体の上面に、感光性樹脂(不図示)を形成し、フォトリソグラフィに基づいて露光・現像を行った後に、加熱処理して硬化させる。感光性樹脂の形成は、液状樹脂を塗布してもよいし、薄膜の樹脂フィルムを貼付してもよい。

## 【0062】

これにより、第3配線層23の上に第2ビアホールVH2が配置された第3層間絶縁層33を形成する。このとき、第3層間絶縁層33は第1の多層配線層5上の外部接続パッドPが配置された周縁部が一括して露出するよう開口されて形成される。

## 【0063】

ネガ型の感光性樹脂を使用する場合は、第1の多層配線層5の周縁部を非露光部とすればよい。また、ポジ型の感光性樹脂を使用する場合は、第1の多層配線層5の周縁部を露光部とすればよい

シリカなどの無機フィラーを含まない感光性樹脂をフォトリソグラフィによってパターニングすることにより、微細な第2ビアホールVH2を備えた薄膜の第3層間絶縁層33を形成することができる。第3層間絶縁層33の厚みは、 $1\text{ }\mu\text{m} \sim 5\text{ }\mu\text{m}$ の範囲、好適には $2\text{ }\mu\text{m} \sim 3\text{ }\mu\text{m}$ に設定される。

## 【0064】

また、第3層間絶縁層33に形成される第2ビアホールVH2の直径は、例えば $70\text{ }\mu\text{m}$ で形成される。

## 【0065】

10

20

30

40

50

第3層間絶縁層33の好適な一例としては、感光性を有するフェノール系樹脂から形成される永久レジスト層が使用される。以下の他の層間絶縁層を形成する際にも同様な樹脂材料及び形成方法が採用される。

#### 【0066】

このように、感光性樹脂をフォトリソグラフィでパターニングすることにより、樹脂層をレーザで加工する手法よりも、層間絶縁層の薄膜化及びビアホールの狭小化を図ることができ、微細な多層配線層用の層間絶縁層を形成することができる。

#### 【0067】

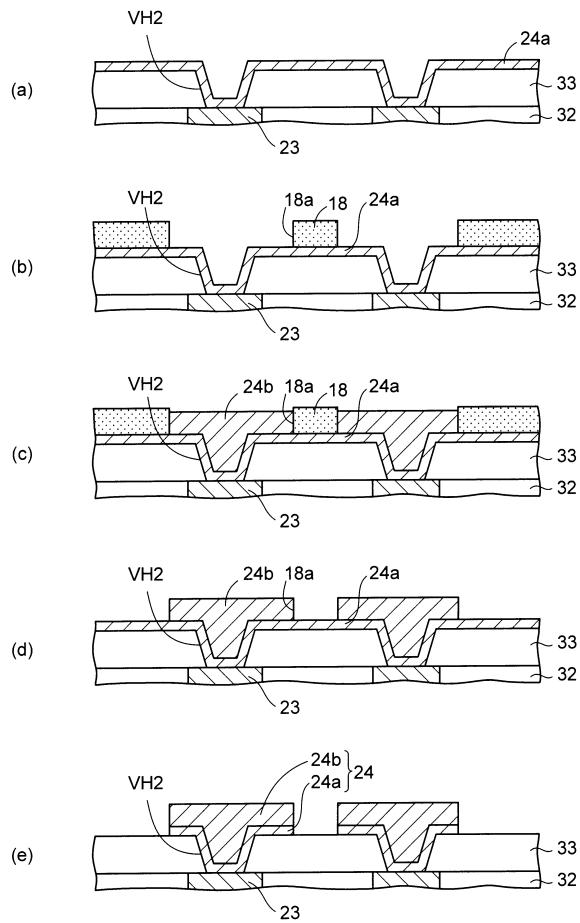

次いで、図8(a)に示すように、第3層間絶縁層33の上に、第2ビアホールVH2内のビア導体を介して第3配線層23に接続される第4配線層24を形成する。第4配線層24においてもセミアディティブ法によって形成される。

10

#### 【0068】

詳しく説明すると、図9(a)に示すように、前述した図7(a)の工程と同様な方法により、第3層間絶縁層33及び第2ビアホールVH2の内面にスパッタ法によりシード層24aを形成する。

#### 【0069】

次いで、図9(b)に示すように、前述した図7(b)の工程と同様に、第4配線層24が配置される部分に開口部18aが設けられためっきレジスト層18を形成する。

#### 【0070】

続いて、図9(c)に示すように、前述した図7(c)の工程と同様に、シード層24aをめっき給電経路に利用する電解めっきにより、めっきレジスト層18の開口部18aに金属めっき層24bを形成する。その後に、図9(d)に示すように、めっきレジスト層18を除去する。

20

#### 【0071】

さらに、図9(e)に示すように、前述した図7(e)の工程と同様に、金属めっき層24bをマスクにしてシード層24aを異方性ドライエッティングにより除去する。

#### 【0072】

以上により、シード層24b及び金属めっき層24aにより第4配線層24が形成される。第4配線層24は、前述した第3配線層23の形成方法と同様なセミアディティブ法で形成されるため、ライン(幅)：スペース(間隔)が2μm:2μm~3μm:3μm程度の微細配線として形成される。

30

#### 【0073】

次に、図8(b)に戻って説明すると、第4配線層24の接続部上に第3ビアホールVH3が配置された第4層間絶縁層34を第3層間絶縁層33の上に形成する。第4層間絶縁層34は、前述した図6(b)の工程と同様に、感光性樹脂をフォトリソグラフィに基づいてパターニングすることにより形成される。

#### 【0074】

第4層間絶縁層34においても、第3層間絶縁層33と同様に、第1の多層配線層5上の外部接続パッドPが配置された周縁部が一括して露出するように開口されて形成される。

40

#### 【0075】

次いで、図10に示すように、第4層間絶縁層34の上に、第3ビアホールVH3内のビア導体を介して第4配線層24に接続される第5配線層25を形成する。第5配線層25においても、第3、第4配線層23, 24と同様なセミアディティブ法によって微細配線として形成される。

#### 【0076】

これにより、第1の多層配線層5の上に、第3~第5配線層23, 24, 25が第3、第4層間絶縁層33, 34を介して積層された第2の多層配線層6が作り込まれる。

#### 【0077】

さらに、第1の多層配線層5の下面側の第1層間絶縁層31の上に、第2配線層22の

50

接続部上に開口部 35a が設けられたソルダレジスト層 35 を形成する。

【0078】

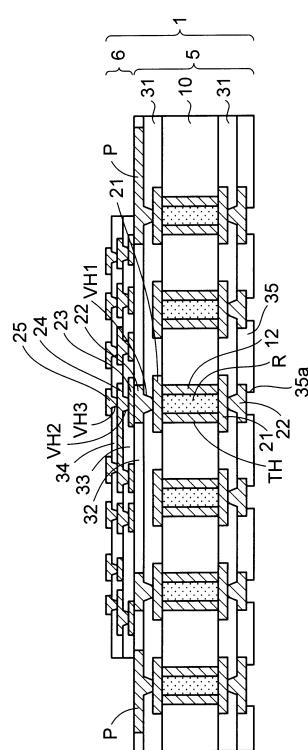

以上により、図 10 に示すように、実施形態の配線基板 1 が製造される。配線基板 1 は、前述した図 5 の第 1 の多層配線層 5 とその上に積層された第 2 の多層配線層 6 とを有する。第 1 の多層配線層 5 では、前述した図 2 のコア基板 10 の両面側に第 1 配線層 21 に到達する第 1 ビアホール VH1 が配置された第 1 層間絶縁層 31 がそれぞれ形成されている。

【0079】

両面側の第 1 層間絶縁層 31 の上には、第 1 ビアホール VH1 を介して第 1 配線層 21 に接続される第 2 配線層 22 がそれぞれ形成されている。上面側の第 1 層間絶縁層 31 上の周縁部には、第 2 配線層 22 と同一層から形成された外部接続パッド P が配置されている。

10

【0080】

上面側の第 2 配線層 22 及び外部接続パッド P の横方向に第 2 層間絶縁層 32 が形成されており、第 2 配線層 22 及び外部接続パッド P は第 2 層間絶縁層 32 に埋め込まれている。

【0081】

第 2 配線層 22 及び外部接続パッド P の各側面の全体及び各下面が第 2 層間絶縁層 32 に接触しており、第 2 配線層 22 及び外部接続パッド P の各上面が第 2 層間絶縁層 32 から露出している。このようにして、第 2 配線層 22 及び外部接続パッド P の各上面と第 2 層間絶縁層 32 の上面とが同一面となっている。

20

【0082】

また、コア基板 10 の下面側の第 1 層間絶縁層 31 の上には、第 2 配線層 22 の接続部上に開口部 35a が設けられたソルダレジスト層 35 が形成されている。

【0083】

前述した製造方法で説明したように、第 1 の多層配線層 5 を製造する際には、一般的なビルドアップ工法が採用される。つまり、非感光性樹脂からなる層間絶縁層にレーザでビアホールを形成し、配線層を形成するセミアディティブ法においてシード層を無電解めっきで形成し、シード層の除去をウェットエッティングで行っている。

【0084】

30

このため、第 1 の多層配線層 5 の配線層の設計ルールとしては、ライン（幅）：スペース（間隔）が  $10 \mu m : 10 \mu m$  程度が限界であり、狭ピッチの接続端子を備えた半導体チップの接続は困難である。

【0085】

そこで、微細配線を形成できる手法により、第 1 の多層配線層 5 の上に第 2 の多層配線層 6 を形成している。第 2 の多層配線層 6 を製造する際には、感光性樹脂をフォトリソグラフィでパターニングすることにより、微細なビアホールを備えた層間絶縁層を形成している。

【0086】

また、配線層を形成するセミアディティブ法において、シード層をスパッタ法により薄膜で形成し、シード層の除去を異方性ドライエッティングで行っている。

40

【0087】

これにより、第 2 の多層配線層 6 の配線層の設計ルールとしては、ライン（幅）：スペース（間隔）を  $2 \mu m : 2 \mu m \sim 3 \mu m : 3 \mu m$  程度に微細化することができ、狭ピッチの接続端子を備えた半導体チップの接続に対応させることができる。

【0088】

第 2 の多層配線層 6 では、第 3 配線層 23、第 4 配線層 25 及び第 5 配線層 25 が第 3 層間絶縁層 33 及び第 4 層間絶縁層 34 を介して積層されている。第 2 の多層配線層 6 の最下の第 3 配線層 23 が第 1 の多層配線層 5 の最上の第 2 配線層 22 にビアホールを介さずに直接接続されている。

50

**【0089】**

また、第4配線層24は第3層間絶縁層33の第2ビアホールVH2を介して第3配線層23に接続されている。さらに、第5配線層25は第4層間絶縁層34の第3ビアホールVH3を介して第4配線層24に接続されている。

**【0090】**

このようにして、第2の多層配線層6は、その最下の第3配線層23が第1の多層配線層5の第2配線層22に接続された状態で第1の多層配線層5の第2層間絶縁層32の上に配置されている。

**【0091】**

また、第2の多層配線層6の第3層間絶縁層33及び第4層間絶縁層34は、第1の多層配線層5の外部接続パッドPが配置された周縁部が一括で露出するように開口されている。10

**【0092】**

次に、本実施形態の配線基板1の第2の多層配線層6に半導体チップをフリップチップ接続する方法について説明する。

**【0093】**

前述したように、第2の多層配線層6の第3～第5配線層23, 24, 25は、第1の多層配線層5の第1、第2配線層21, 22よりも狭ピッチで形成されている。このため、狭ピッチの接続端子を備えた高性能な半導体チップを実装することができる。

**【0094】**

例えば、第1の多層配線層5には、接続端子の配置ピッチが130μm程度以上の半導体チップしか実装できない。これに対して第1の多層配線層5の上に微細配線を備えた第2の多層配線層6を形成することにより、接続端子の配置ピッチが40μm程度の半導体チップを実装することができる。20

**【0095】**

また、CPUチップなどのロジックLSIは高性能化によりそのサイズも小型化されるため、第1の多層配線層5上で一つの半導体チップを実装した領域に2つの半導体チップを並べて実装することができる。

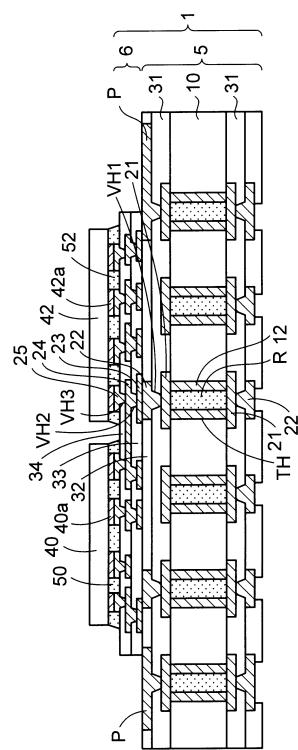

**【0096】**

図11に示すように、実施形態の配線基板1の第2の多層配線層6の第5配線層25の接続部に第1半導体チップ40の接続端子40aをはんだ層を介してフリップチップ接続する。また同様に、配線基板1の第2の多層配線層6の第5配線層25の接続部に第2半導体チップ42の接続端子42aをはんだ層を介してフリップチップ接続する。30

**【0097】**

第1半導体チップ40及び第2半導体チップ42は第2の多層配線層6の上に横方向に並んで配置される。そして、第1半導体チップ40と第2半導体チップ42とが第2の多層配線層6の第5配線層25及び第4配線層24を介して電気的に接続される。

**【0098】**

さらに、第1半導体チップ40と第2の多層配線層6との間に第1アンダーフィル樹脂50を充填する。また同様に、第2半導体チップ42と第2の多層配線層6との間に第2アンダーフィル樹脂52を充填する。40

**【0099】**

本実施形態では、第2の多層配線層6の上に2つの半導体チップを並べてフリップチップ接続しているが、第2の多層配線層6の上に一つの半導体チップを実装してもよいし、任意の数の複数の半導体チップを並べて配置してもよい。

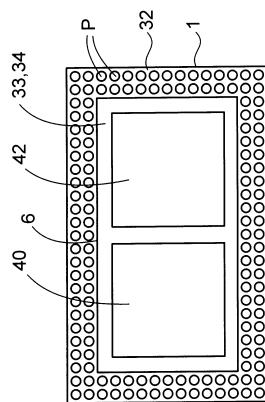

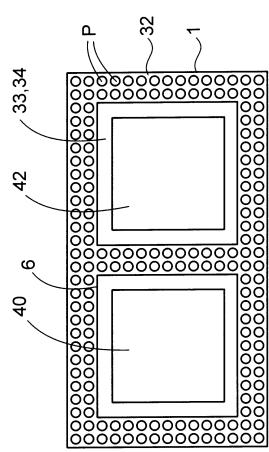

**【0100】**

図12は図11の構造体を平面からみた模式的な縮小平面図である。図12では、第1の多層配線層5の外部接続パッドPが2列になって並んで配置された例が示されており、図11とは異なっている。

**【0101】**50

図12に示すように、配線基板1の第2の多層配線層6の上に第1半導体チップ40及び第2半導体チップ42が並んで配置されている。

#### 【0102】

第2の多層配線層6の第3、第4層間絶縁層33, 34は第1の多層配線層5の周縁部上で一括して開口されており、第1の多層配線層5の周縁部の全体が第2の多層配線層6から露出している。

#### 【0103】

これにより、第1の多層配線層5の周縁部に並んで配置された複数の外部接続パッドPが第2の多層配線層6の第3、第4層間絶縁層33, 34から露出した状態となっている。

10

#### 【0104】

第1の多層配線層5には微細配線が形成されないため、外部接続パッドPは配線ピッチの広い第2配線層22と同一層から形成され、10μm程度の厚膜で形成される。このため、外部接続パッドPを強い機械強度を有するパッドとして形成することができる。

#### 【0105】

本実施形態と違って、第2の多層配線層6の配線層の形成と同時に外部接続パッドを形成すると、2μm～3μmの薄膜のパッドとなるため、外部接続パッドPとして使用するには、機械強度が弱くなってしまう。

#### 【0106】

このため、はんだバンプを介して上側配線基板を外部接続パッドに接続する際に、クラックなどが発生しやすくなり、接続の信頼性が得られなくなる。

20

#### 【0107】

また、第1の多層配線層5では、外部接続パッドPが第2層間絶縁層32に埋め込まれており、外部接続パッドPの上面と第2層間絶縁層32の上面とが同一面となっている。

#### 【0108】

外部接続パッドP上にはんだボールなどを介して上側配線基板を接続する際に、第2層間絶縁層32（樹脂）は、はんだの濡れ性が悪いため、外部接続パッドPの上面から周囲にはんだが流出するおそれがない。

#### 【0109】

このため、外部接続パッドPの上に、はんだをせき止めるための開口部が配置されたソルダレジスト層を設ける必要がなく、簡易な構造とすることができます。

30

#### 【0110】

また、図13に示すように、図12において、第1半導体チップ40と第2半導体チップ42との間の領域にも外部接続パッドPを配置してもよい。そして、図12と同様に、第1半導体チップ40及び第2半導体チップ42の周りの外部接続パッドPが第2の多層配線層6から一括で露出するようにしてもよい。

#### 【0111】

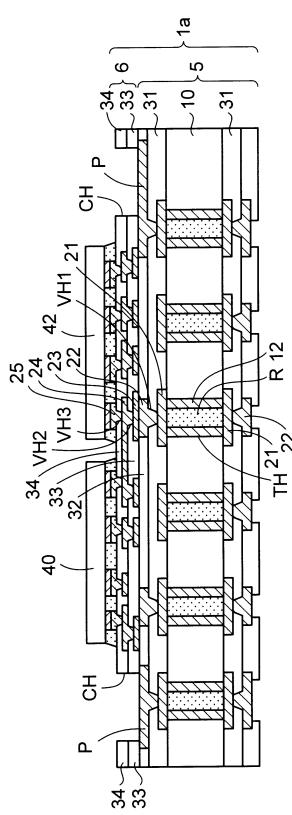

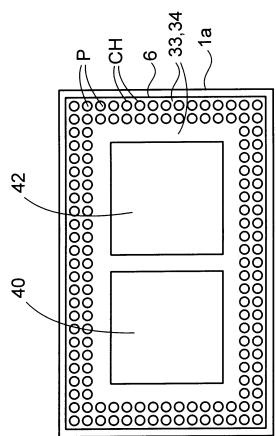

図14には、実施形態の変形例の配線基板1aに同様に2つの半導体チップがフリップチップ接続された様子が示されている。図15は図14の構造体を平面からみた模式的な縮小平面図である。

40

#### 【0112】

図14及び図15に示すように、変形例の配線基板1aでは、第1の多層配線層5の各々の外部接続パッドPに対応するように第3層間絶縁層33及び第4層間絶縁層34に複数の接続ホールCHがそれぞれ配置されている。各接続ホールCHの底面に外部接続パッドPが露出している。

#### 【0113】

変形例の配線基板1aでは、図11の配線基板1と違って、隣り合う外部接続パッドPの間の領域及び最外周部に第2の多層配線層6の第3層間絶縁層33及び第4層間絶縁層34が残されている。

#### 【0114】

50

このようにして、変形例の配線基板 1 aにおいても、第 1 の多層配線層 5 の外部接続パッド P が第 2 の多層配線層 6 の第 3 、第 4 層間絶縁層 3 3 , 3 4 から露出している。

#### 【 0 1 1 5 】

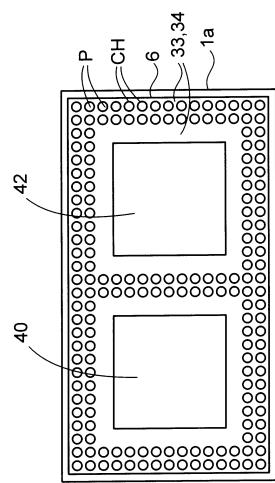

各外部接続パッド P 上に接続ホール C H を配置することで、外部接続パッド P が狭ピッチ化され、かつ大きなはんだボールを採用する場合であっても、接続ホール C H 内にはんだをせき止めることができるので、外部接続パッド P 間の短絡を防止することができる。

#### 【 0 1 1 6 】

また、図 1 6 に示すように、図 1 5 において、第 1 半導体チップ 4 0 と第 2 半導体チップ 4 2 との間の領域にも外部接続パッド P を配置してもよい。そして、図 1 5 と同様に、第 1 半導体チップ 4 0 及び第 2 半導体チップ 4 2 の周りの各々の外部接続パッド P の上に第 2 の多層配線層 2 の接続ホール C H をそれぞれ配置してもよい。10

#### 【 0 1 1 7 】

次に、前述した図 1 1 の配線基板 1 の上に上側配線基板及び第 3 半導体チップを接続する方法について説明する。上側配線基板は第 3 の多層配線層として製造される。

#### 【 0 1 1 8 】

まず、図 1 7 に示すように、上側配線基板 6 0 を用意する。上側配線基板 6 0 では、下側接続パッド P x と上側接続パッド P y が形成され、厚み方向に貫通電極 P E が形成されている。

#### 【 0 1 1 9 】

下側接続パッド P x と上側接続パッド P y とは貫通電極 P E を介して相互接続されている。上側配線基板 6 0 は、内部に多層配線を備えていてもよいし、上下側が導通可能な構造であればよい。20

#### 【 0 1 2 0 】

さらに、上側配線基板 6 0 では、両面側に最外層として、下側接続パッド P x 及び上側接続パッド P y の上に開口部 6 2 a が設けられたソルダレジスト層 6 2 がそれぞれ形成されている。

#### 【 0 1 2 1 】

そして、上側配線基板 6 0 の下側接続パッド P x にはんだボール 2 8 を搭載する。続いて、第 1 の多層配線層 5 の外部接続パッド P 上に上側配線基板 6 0 のはんだボール 2 8 が配置されるようにして、配線基板 1 及び第 1 、第 2 半導体チップ 4 0 , 4 2 の上に上側配線基板 6 0 を配置する。30

#### 【 0 1 2 2 】

さらに、リフロー加熱することにより、上側配線基板 6 0 の下側接続パッド P x をはんだボール 2 8 を介して第 1 の多層配線層 5 の外部接続パッド P に接続する。

#### 【 0 1 2 3 】

はんだボール 2 8 は第 1 の多層配線層 5 の外部接続パッド P の上に搭載してもよいし、はんだボール 2 8 の代わりに、はんだバンプを印刷などによって形成してもよい。

#### 【 0 1 2 4 】

これにより、上側配線基板 6 0 の下側の領域に第 1 、第 2 半導体チップ 4 0 , 4 2 が収容された状態となる。第 1 、第 2 半導体チップ 4 0 , 4 2 の上面と、上側配線基板 6 0 下面との間に間隔が設けられる。バンプ電極の好適な例としてははんだボール 2 8 を挙げるが、各種の導電材料を使用することができる。40

#### 【 0 1 2 5 】

続いて、図 1 8 に示すように、図 1 7 の上側配線基板 6 0 の上側接続パッド P y に第 3 半導体チップ 4 4 の接続端子 4 4 a をはんだ層を介してフリップチップ接続する。その後に、第 3 半導体チップ 4 4 と上側配線基板 6 0 との間に第 3 アンダーフィル樹脂 5 4 を充填する。第 3 半導体チップ 4 4 として、第 1 、第 2 半導体チップ 4 0 , 4 2 が C P U チップの場合は、メモリチップが使用される。

#### 【 0 1 2 6 】

以上により、実施形態の半導体装置 2 が得られる。第 1 の多層配線層 5 として、多面取50

りの大型基板を使用する場合は、上側配線基板 6 0 及び第 1 の多層配線層 5 が切断されて個々の半導体装置 2 が得られる。あるいは、前述した図 1 1 の工程の後に、第 1 、第 2 半導体チップ 4 0 , 4 2 が搭載された配線基板 1 を切断してもよい。

#### 【 0 1 2 7 】

図 1 8 に示すように、半導体装置 2 では、図 1 0 で説明した配線基板 1 の第 2 の多層配線層 6 の上に第 1 半導体チップ 4 0 及び第 2 半導体チップ 4 2 が並んでフリップチップ接続されている。

#### 【 0 1 2 8 】

第 1 半導体チップ 4 0 と第 2 半導体チップ 4 2 とは、第 2 の多層配線層 6 の第 5 配線層 2 5 及び第 4 配線層 2 4 を介して相互接続されている。第 1 半導体チップ 4 0 と第 2 の多層配線層 6 との間に第 1 アンダーフィル樹脂 5 0 が充填されている。

10

#### 【 0 1 2 9 】

また同様に、第 2 半導体チップ 4 2 と第 2 の多層配線層 6 との間に第 2 アンダーフィル樹脂 5 2 が充填されている。

#### 【 0 1 3 0 】

配線基板 1 及び第 1 、第 2 半導体チップ 4 0 , 4 2 の上には、はんだボール 2 8 を介して上側配線基板 6 0 が配置されている。上側配線基板 6 0 の上側接続パッド P y に第 3 半導体チップ 4 4 の接続端子 4 4 a がフリップチップ接続されている。第 3 半導体チップ 4 4 と上側配線基板 6 0 との間に第 3 アンダーフィル樹脂 5 4 が充填されている。

20

#### 【 0 1 3 1 】

第 1 半導体チップ 4 0 及び第 2 半導体チップ 4 2 は、第 2 の多層配線層 6 、第 1 の多層配線層 5 、はんだボール 2 8 、及び上側配線基板 6 0 を介して第 3 半導体チップ 4 4 に電気的に接続されている。

#### 【 0 1 3 2 】

図 1 9 には、実施形態の第 1 変形例の半導体装置 2 a が示されている。第 1 変形例の半導体装置 2 a が図 1 8 の半導体装置 2 と異なる点は、コア基板 1 0 を有するビルドアップ配線基板からなる第 1 の多層配線層 5 を使用する代わりに、コア基板 1 0 を有さないコアレスタイプの第 1 の多層配線層 5 a を使用することにある。

#### 【 0 1 3 3 】

このように、第 1 変形例の半導体装置 2 a では、第 1 の多層配線層 5 a として、コアレス配線基板が使用される。そして、コアレスタイプの第 1 の多層配線層 5 a の上に同様な第 2 の多層配線層 6 が積層されている。

30

#### 【 0 1 3 4 】

図 1 9 のコアレスタイプの第 1 の多層配線層 5 a は、仮基板の上に多層配線層を形成し、仮基板を除去することにより製造される。図 1 9 では、多層配線層の仮基板から分離された面に第 2 の多層配線層 6 が積層されている。

#### 【 0 1 3 5 】

図 1 9 のコアレスタイプの第 1 の多層配線層 5 a では、図 1 8 の第 1 の多層配線層 5 と同様に、最上の第 1 層間絶縁層 3 1 に第 1 配線層 2 1 及び外部接続パッド P が埋め込まれている。第 1 配線層 2 1 及び外部接続パッド P の各上面と第 1 層間絶縁層 3 1 の上面とが同一面となっている。

40

#### 【 0 1 3 6 】

第 1 層間絶縁層 3 1 には第 1 配線層 2 1 に到達する上側第 1 ビアホール V H 1 が形成されている。第 1 層間絶縁層 3 1 の下には上側第 1 ビアホール V H 1 を介して第 1 配線層 2 1 に接続される第 2 配線層 2 2 が形成されている。

#### 【 0 1 3 7 】

また、第 1 層間絶縁層 3 1 の下には、第 2 配線層 2 2 に到達する下側第 1 ビアホール V H 1 x を備えた第 2 層間絶縁層 3 2 が形成されている。第 2 層間絶縁層 3 2 の下には、下側第 1 ビアホール V H 1 x を介して第 2 配線層 2 2 に接される接続パッド P z が形成されている。

50

**【0138】**

第2層間絶縁層32の下には接続パッドPzを露出させる開口部35aを備えたソルダレジスト層35が形成されている。

**【0139】**

そして、コアレスタイプの第1の多層配線層5aの最上の第1配線層21に第2の多層配線層6の最下の第3配線層23が接続されて、配線基板1bが形成されている。図19の他の要素は図18と同一であるため、その説明は省略する。

**【0140】**

図20には、実施形態の第2変形例の半導体装置2bが示されている。図20に示すように、第2変形例の半導体装置2bでは、図18の半導体装置2において、配線基板1及び第1、第2半導体チップ40, 42と、上側配線基板60との間にモールド樹脂56が充填されている。

10

**【0141】**

また、配線基板1と上側配線基板60とを接続するはんだボールとして、銅コア部28bの外面にはんだ層28cが被覆された銅コアはんだボール28aが採用される。銅コアはんだボール28aを採用することにより、リフロー加熱して接続する際に、銅コア部64bはリフローしない。

**【0142】**

このため、第1、第2半導体チップ40, 42と上側配線基板60との間隔を狭くして薄型化する場合であっても、確実にその間隔を確保し、モールド樹脂56で封止することができる。図20の他の要素は図18と同一であるため、その説明を省略する。

20

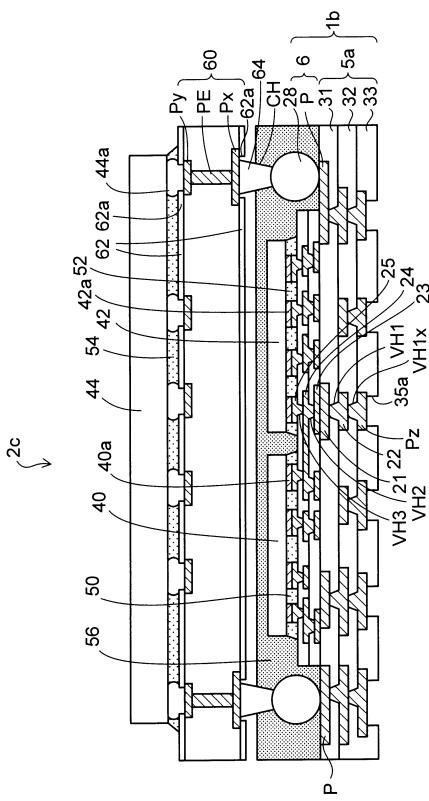

**【0143】**

また、図21には、実施形態の第3変形例の半導体装置2cが示されている。図21の第3変形例の半導体装置2cでは、前述した図19の半導体装置2aにおいて、配線基板1b、第1、第2半導体チップ40, 42、及びはんだボール28がモールド樹脂56で封止されている。そして、はんだボール28の上のモールド樹脂56に接続ホールCHが設けられている。

**【0144】**

さらに、上側配線基板60の下側接続パッドPxに形成されたはんだバンプ64が配線基板1bの接続ホールCH内のはんだボール28に接続されている。モールド樹脂56の上面と上側配線基板60の下面との間に間隔が設けられている。図21の他の要素は図18と同一であるため、その説明を省略する。

30

**【0145】**

図21の第3変形例の半導体装置2cを製造する際には、まず、前述した図19の配線基板1bの外部接続パッドPの上にはんだボール28を搭載する。さらに、配線基板1b、第1、第2半導体チップ40, 42及びはんだボール28をモールド樹脂56で封止する。続いて、はんだボール28の上のモールド樹脂56をレーザで加工して接続ホールCHを形成する。

**【0146】**

次いで、上側配線基板60のはんだバンプ64を配線基板1bの接続ホールCH内のはんだボール28の上に配置する。さらに、リフロー加熱することにより、配線基板1bと上側配線基板60とをはんだボール28及びはんだバンプ64を介して接続する。

40

**【0147】**

図19～図21の実施形態の第1～第3変形例の半導体装置2a, 2b, 2cは、図18の実施形態の半導体装置2と同様な効果を奏する。

**【符号の説明】****【0148】**

1, 1a, 1b…配線基板、2, 2a, 2b, 2c…半導体装置、5…第1の多層配線層、5a…コアレスタイプの第1の多層配線層、6…第2の多層配線層、10…コア基板、12…スルーホールめっき層、14, 16, 18…めっきレジスト層、14a, 16a,

50

18a, 35a, 62a...開口部、21...第1配線層、22...第2配線層、22a, 23a, 24a...シード層、22b, 23b, 24b...金属めっき層、23...第3配線層、24...第4配線層、25...第5配線層、28...はんだボール、28a...銅コアはんだボール、28b...銅コア部、28c...はんだ層、31...第1層間絶縁層、32...第2層間絶縁層、33...第3層間絶縁層、34...第4層間絶縁層、35, 62...ソルダレジスト層、40...第1半導体チップ、42...第2半導体チップ、44...第3半導体チップ、40a, 42a, 44a...接続端子、50, 52, 54...アンダーフィル樹脂、56...モールド樹脂、60...上側配線基板、64...はんだバンプ、P...外部接続パッド、PE...貫通電極、Px...下側接続パッド、Py...上側接続パッド、Pz...接続パッド、R...樹脂体、TH...スルーホール、VH1, VH1x, VH2, VH3...ビアホール。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

審査官 鈴木 駿平

(56)参考文献 特開2004-146602(JP,A)

特開2010-141204(JP,A)

特開2002-171048(JP,A)

特開2010-123708(JP,A)

特開2000-156564(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 25/04

H01L 25/065

H01L 25/07

H01L 25/10

H01L 25/11

H01L 25/18

H01L 21/60

H05K 3/46