(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-78479

(P2006-78479A)

(43) 公開日 平成18年3月23日(2006.3.23)

(51) Int.CI.

GO1R 35/00 (2006.01)

GO1R 27/28 (2006.01)

F1

GO1R 35/00

GO1R 27/28ZABA

Z

テーマコード(参考)

2GO28

審査請求 未請求 請求項の数 10 O L (全 12 頁)

(21) 出願番号 特願2005-237480 (P2005-237480)

(22) 出願日 平成17年8月18日 (2005.8.18)

(31) 優先権主張番号 939670

(32) 優先日 平成16年9月13日 (2004.9.13)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100105913

弁理士 加藤 公久

(72) 発明者 ジョエル・ダンスモア

アメリカ合衆国カリフォルニア州、セバス

トポル、グリーン・バレー・ロード 135

01

最終頁に続く

(54) 【発明の名称】自動ポート延長校正を含むネットワークアナライザ及び動作方法

## (57) 【要約】

【課題】テストフィクスチャに対する様々なポート接続によって生じる遅延の算出精度を向上させる

【解決手段】テストフィクスチャを使用して被測定物(DUT)を計測するネットワークアナライザを自動的に校正する方法であって、テストフィクスチャに接続された個々のポート上において、刺激信号を生成する段階(103)と、前記個々のポート上において前記刺激信号の反射を計測し、計測データを生成する段階であって前記計測データが前記テストフィクスチャの位相応答を反映している段階(104)と、前記計測データを処理して前記ネットワークアナライザと前記テストフィクスチャに関連する結合におけるインピーダンスの不整合によって生成されるリップルを補償する段階と、前記処理段階に基づいて、前記ネットワークアナライザのポート延長の設定内容を調節する段階とを有する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

テストフィクスチャを使用して被測定物を計測するネットワークアナライザを自動的に校正する方法であって、

前記テストフィクスチャに接続された個々のポート上において、刺激信号を生成する段階と、

前記個々のポート上において前記刺激信号の反射を計測し、計測データを生成する段階であって、前記計測データが前記テストフィクスチャの位相応答を反映している段階と、

前記計測データを処理して、前記ネットワークアナライザと前記テストフィクスチャに関連する結合におけるインピーダンスの不整合によって生成されるリップルを補償する段階と、

前記処理段階に基づいて、前記ネットワークアナライザのポート延長の設定内容を調節する段階と、

を有することを特徴とする方法。

**【請求項 2】**

前記処理段階が、複数の基準と関連する反射計測から得られた計測データと共に前記計測データを平均化する段階を有していることを特徴とする請求項 1 に記載の方法。

**【請求項 3】**

前記処理段階が、周波数範囲にわたる平均群遅延値を算出する段階を有していることを特徴とする請求項 1 に記載の方法。

**【請求項 4】**

前記処理段階が、前記計測データから得られた位相値に対してラインをフィッティングする段階を有していることを特徴とする請求項 1 に記載の方法。

**【請求項 5】**

前記フィッティングされたラインの傾きから遅延値を判定する段階を更に有することを特徴とする請求項 4 に記載の方法。

**【請求項 6】**

前記遅延値からオフセット値を判定する段階であって段階を更に有し、

前記ポート延長の設定内容を調節する前記段階が、最低周波数においてはゼロ補償が提供されるように、中間点周波数においては前記フィッティングされたラインの Y 切片値の半分の補償が適用されるように、最高周波数においては前記 Y 切片値の 2 倍の補償が適用されるように、前記オフセット値を適用することを特徴とする請求項 4 に記載の方法。

**【請求項 7】**

現在の遅延値が以前の遅延値と実質的に同一になるまで、前記計測データに対してラインをフィッティングすることにより、前記テストフィクスチャと関連する遅延値を反復的に算出する段階を更に有し、前記反復的な算出段階が、前記計測データに関連するポイント密度の連続的な増大と関連して実行されることを特徴とする請求項 1 に記載の方法。

**【請求項 8】**

被測定物に対して刺激信号を印加し、前記 D U T からの信号を計測する複数のポートと、

前記複数のポート上において実行される計測のスペクトル分析を実行する信号処理ロジックであって、前記スペクトル分析によって生成された位相データに対してポート延長補償を適用する信号処理ロジックと、

前記ネットワークアナライザの校正モードにおいて、反射計測データを処理し、前記複数のポートから、D U T を保持するべく使用されているテストフィクスチャへの遅延の推定値を生成するロジックと、

前記処理ロジックに応答して、ポート延長の設定内容を調節するロジックと、

を有することを特徴とするネットワークアナライザ。

**【請求項 9】**

反射計測データを処理する前記ロジックが、ラインフィッティング操作を実行して前記

10

20

30

40

50

遅延の推定値を生成することを特徴とする請求項 8 に記載のネットワークアナライザ。

【請求項 10】

前記処理ロジックが、前記計測データと関連するポイント密度を同時に増大させつつ、現在の遅延値が以前の遅延値と実質的に同一になるまで、前記テストフィクスチャと関連する遅延値を反復的に算出するべく動作可能であることを特徴とする請求項 8 に記載のネットワークアナライザ。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、一般に、テストフィクスチャを使用して計測を実行するネットワークアナライザの校正に関するものである。 10

【背景技術】

【0002】

ネットワークアナライザは、様々な被測定物 (Device Under Test : D U T ) の高周波 (Radio Frequency : R F ) 特性を判定するのに使用する装置である。多くの場合に、D U T は、プリント回路基板 (Printed Circuit Board : P C B ) 上のトレース接点とインターフェイスするべく設計された相対的に小さなコンポーネントである。多くのネットワークアナライザは、通常、同軸結合を受け入れるべく適合されたインターフェイスを利用している。P C B 上で使用するべく設計されたD U T をネットワークアナライザを使用して試験するために、しばしば、テストフィクスチャが使用されている。テストフィクスチャは、一般に、D U T を容易に嵌め込むべく適合され、D U T をネットワークアナライザの 1 つ又は複数のポートに電気的に接続する専用装置である。 20

【0003】

多くのD U T (平衡型フィルタ、バラン、及び平衡型増幅器など)においては、適切な性能の計測は、それぞれのポートにおいて印加及び受信する信号の大きさと位相の両方に依存している。そして、平衡型装置の場合には、それぞれのテストフィクスチャポートの遅延の位相が、均衡したポート対間ににおいて同一であることが非常に重要である。しかしながら、このようなネットワークアナライザ及びテストフィクスチャを使用して実行する計測は、問題点を有している。具体的には、テストフィクスチャ / ネットワークアナライザの構成を使用すると、通常、ポートごとに、経路長が異なってくるのである。このばらつきは、P C B レイアウトの制約、製造プロセスの制限、又はその他の理由によってもたらされるものである。 30

【0004】

このようなネットワークアナライザのポート間における経路長の違いに対処するべく、ネットワークアナライザ用の「ポート延長 (Port Extension)」が開発されている。ポート延長とは、個々のポート上の計測結果に数学的な遅延を提供するものである。この数学的な遅延は、試験セットアップの電気的な長さの違いによってもたらされる位相応答の線形部分をモデル化したものである。

【0005】

具体的には、ポート延長機能は、通常、それぞれのポートごとに個別の遅延値を定義することによって動作する。即ち、計測を実行した後に、ネットワークアナライザは、関係するポートに応じて定義されている遅延値を使用し、計測データに対して位相補償を適用する。例えば、反射計測を実行する際には、所与のポートに定義されている遅延の 2 倍を使用することにより、入射信号と反射信号における遅延を補償する。一方、透過計測の場合には、入射ポートの遅延と応答ポートの遅延を使用することにより、2 つの異なるポート間における電気的な経路の遅延を補償する。そして、合計遅延に位相補償値の個々の周波数を乗算することにより、その周波数範囲の様々な周波数におけるそれぞれの位相補償値を算出する。このようにして、位相補償値を適切に適用することにより、ネットワークアナライザによって提供されるデータにおいて、テストフィクスチャによって生じる遅延 40

50

を補償することができる。

【発明の開示】

【発明が解決しようとする課題】

【0006】

既存のネットワークアナライザは、いくつかの有利な特徴を提供しているが、既存のネットワークアナライザは、制限を有している。具体的には、既存のネットワークアナライザにおいては、ポート延長によって適用する適切な値をユーザーが判定する必要がある。従って、テストフィクスチャを使用して試験を実施するネットワークアナライザの校正には、時間を要すると共に、ある程度の誤りが混入する可能性をも有している。

【課題を解決するための手段】

【0007】

いくつかの代表的な実施例は、テストフィクスチャを使用して計測動作を実施するネットワークアナライザを自動的に校正するシステム及び方法に関するものである。具体的には、既知の反射のS11計測を実行し、これから位相基準を生成することができる。尚、「S11計測」とは、散乱パラメータモデルを使用するネットワークアナライザによって実行する計測を意味しており、この場合に、「S11」とは、同一ポート上における入射信号に対する反射信号の比率を意味している。又、この既知の反射は、オープン回路（例：テストフィクスチャからDUTを除去する）又は短絡回路の結果として得られるいずれのものであってよい。この計測データを処理することにより、その試験セットアップの不良なソース-PWB整合の結果として生じる位相応答の誤差を明らかにすることができます。そして、この処理により、テストフィクスチャに対する様々なポート接続によって生じる遅延の算出精度を大幅に向上させることができる。

【発明を実施するための最良の形態】

【0008】

いくつかの代表的な実施例においては、ネットワークアナライザの複数のポートに刺激信号を連続的に供給し、複数のポートのそれぞれにおいて反射計測を実行する。そして、これらの反射計測値を使用することにより、それぞれのポートを通じたテストフィクスチャに関連する遅延を推定する。更には、テストフィクスチャの同軸-PWB接続が、しばしば、相対的に不良なインピーダンス整合を有している。オープン基準を使用して反射計測値を取得する場合には、インピーダンスの不整合により、結果的に、大きなリップルが生じることになる。又、カプラまたはブリッジの指向性によっても、反射計測値にリップルが混入する可能性がある。従って、いくつかの代表的な実施例においては、複数の周波数に関連する位相応答値を適切に処理することにより、テストフィクスチャに接続されたネットワークアナライザの複数のポートに関連する遅延を推定している。

【0009】

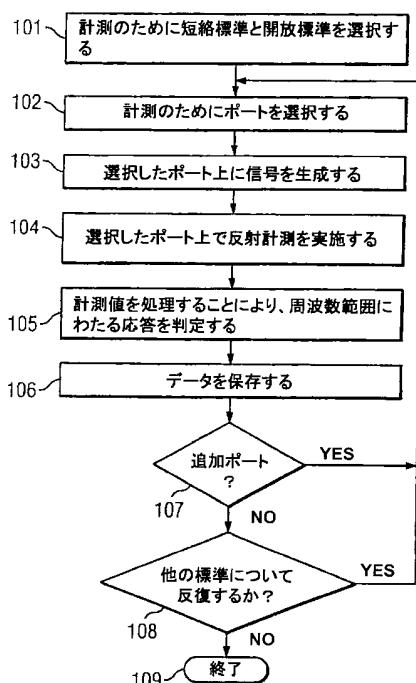

次に、図面を参照すれば、図1は、代表的な一実施例によるネットワークアナライザの動作フローチャートを示している。尚、このフローチャートは、代表的な一実施例においては、ネットワークアナライザのプロセッサによって実行される適切なソフトウェア命令又はコードを使用して実装されている。或いは、この代わりに（又は、これに加えて）、他の実施例においては、集積回路を使用することにより、このフローチャートの一部又は全体を実装可能である。

【0010】

まず、段階101において、後続の計測のために、短絡基準(Short Standard)又はオープン基準(Open Standard)を選択する。尚、短絡基準とは、180度の位相シフトを有する单一の反射を具備する理想的な電気的接続を意味しており、短絡基準の計測においては、通常、適切なテストキットコンポーネントをテストフィクスチャ内に挿入した状態で、そのテストフィクスチャのセットアップの応答を取得する。一方、オープン基準とは、終端されていない伝送ラインを意味するものであり、オープン基準は、テストフィクスチャ内のいずれかの要素の配置を除外することによって計測され、従って、回路経路が「オープン」になっている。この基準の選択は、グラフィカル

10

20

30

40

50

ユーザーインターフェイス (G r a p h i c a l U s e r I n t e r f a c e : G U I ) 又はその他のインターフェイスを通じて、ネットワークアナライザのユーザーから適切な入力を受信することによって実行することができる。又、基準の位相対周波数応答が判明しているか、或いは、仮定可能である場合には、その他の適切な反射基準を使用することも可能である。

#### 【 0 0 1 1 】

段階 102において、校正対象のネットワークアナライザのポートを選択する。代表的な一実施例においては、適切なソフトウェアループにより、その装置上に提供されているそれぞれのポートを反復的にチェックすることによって個々のポートを選択する。或いは、この代わりに、G U I 又はその他のインターフェイスを通じて、ユーザーがポートを手作業で選択することも可能である。

#### 【 0 0 1 2 】

段階 103において、その選択したポート上に信号を生成する。段階 104において、その選択したポート上において反射計測を実行する。段階 105において、それらの計測値を処理することにより、周波数範囲にわたる応答を判定する。尚、この処理には、ベクトル誤差補正 (V e c t o r E r r o r C o r r e c t i o n) を含むことができる。一般的には、テストフィクスチャを接続する前に、同軸ポートにおいてベクトル誤差補正を実行する。この結果、テストフィクスチャ自体の誤差のみが計測値に含まれることになる。そして、段階 106において、後続の処理のために、この応答データを保存する。

#### 【 0 0 1 3 】

段階 107において、論理比較を実行し、試験を要する更なるポートが存在しているかどうかを判定する。そして、存在している場合には、プロセスフローは、段階 102に戻る。段階 108において、論理比較を実行し、その他の基準について、処理を反復するかどうかを判定する。そして、この論理比較が真である場合には、プロセスフローは、段階 102に戻り、その他の基準を使用してプロセスを実行する。そして、段階 109において、この計測プロセスは終了する。

#### 【 0 0 1 4 】

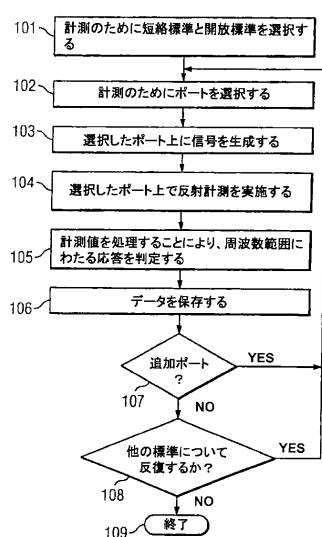

図 2 は、代表的な 1 実施例によるオープン基準を使用したテストフィクスチャの反射計測に関連する振幅応答 201、位相応答 202、及び遅延応答 203 を示している。D U T の試験を実施する際には、正しいトレースを有向正規化 (D i r e c t e d N o r m a l i z a t i o n) するために、このオープン基準と関連する応答を使用することができる。しかしながら、図 2 に示されているように、これらの応答 201 ~ 203 は、リップルを有している。この応答 201 ~ 203 におけるリップルは、計測システムとオープン応答の不良なソース整合 (同軸 - P C B 接続) によって発生した誤差を示すものである。前述のように、ポート延長機能においては、計測データに対する位相補償の適用を制御する単一の遅延値を選択している。しかしながら、遅延応答 203 がリップルを有しているため、個々のポートを特徴付けるために、遅延応答 203 の周波数範囲におけるどの値が適切であるのかが、即座に明らかではない。又、遅延を抽出するための一般的な手動による方法においては、ポートをオープン状態とし、位相応答を参照して、トレースが平坦になるまで、様々なポート延長値を適用している。この方法は、時間を要し、解釈が混入すると共に、熟練したオペレータを必要としている。又、計測値のリップルのために、結果を正しく解釈することが困難な場合がある。

#### 【 0 0 1 5 】

オープン基準と短絡基準の平均値を使用することにより、ソース整合の寄与度を大幅に緩和することが可能である。この場合には、オープン及び短絡基準の平均応答を、正規化として、テストフィクスチャを使用する D U T の計測値に適用すればよい。しかしながら、いくつかの試験環境においては、短絡基準を使用した計測を実行することが、実際には容易ではなく、オープン基準の計測のみが実行されている。従って、いくつかの代表的な実施例においては、オープン基準から取得した計測データを処理することより、試験システムの不良なソース整合によって生じる誤差を緩和している。

10

20

30

40

50

## 【0016】

代表的な一実施例においては、周波数範囲にわたる複数の周波数に関連する群遅延値の平均を使用することにより、試験システムの不良なソース整合に関連する誤差に対処している。又、別の実施例においては、ラッピングされていない位相値に対してラインフィッティングアルゴリズムを適用することにより、試験システムの不良なソース整合と関連する誤差に対処している。

## 【0017】

実際には、この平均法と線形フィッティング法の値は、しばしば、略同一の結果を生成する。但し、平均化の操作と関連する数学は、周波数範囲の最初と最後の周波数に関連する位相値の破壊の影響を受けやすい。即ち、周波数範囲内の個々の周波数の群遅延は、個々の周波数に隣接する周波数に関連する位相値の差を使用して算出される。具体的には、個々の群遅延値は、 $g d_i = - (f_i - f_{i+1}) / (f_{i+1} - f_{i-1})$  と表すことができる。平均群遅延は、 $(1/N) g d_i$  である（ここで、 $i = 1 \sim N$  である）。そして、「 $f_i - f_{i+1}$ 」項は、通常、その周波数範囲にわたって一定であって（ $f$ ）、この加算の外に移動する可能性があり、この結果、平均群遅延として、 $(-1/N) f$

$(f_i - f_{i+1})$  が与えられる（ここで、 $i = 1 \sim N$  である）。従って、中間の位相値は、単純に相殺され、周波数範囲にわたる平均群遅延には、最初と最後の位相値のみが寄与することになる。例えば、この加算には、 $-d_2$  ( $i = 1$  の場合) と  $d_2$  ( $i = 2$  の場合) が含まれている。従って、加算の完了後には、最初と最後の位相値 ( $d_1 - d_{N+1}$ ) のみが残ることになり、最初と最後の位相値が（例えば、雑音によって）破壊された場合には、平均群遅延値も破壊されることになる。

10

20

30

40

## 【0018】

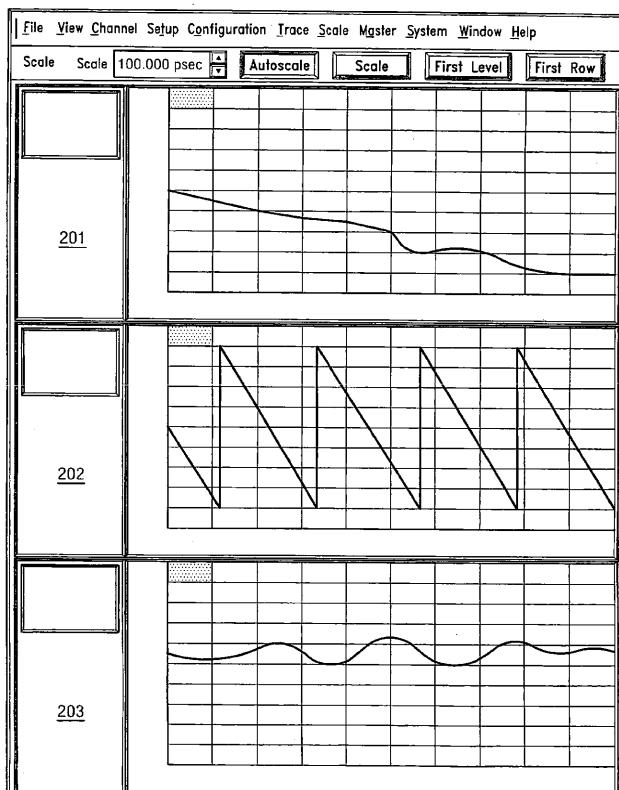

図2の位相応答202には、ラッピングされた位相値が示されている。これらのラッピングされた位相値は、 $-d_1 \sim d_N$  の間に制約されている。ラッピングされた位相値は、この範囲内に制約されているため、通常は、これらのラッピングされた値に対してライン（直線）をフィッティングしても、個々のポートと関連する遅延の正確な推定値は生成されない。と等しい又はこれを上回る絶対位相変化を検出し、その位相変化の値に応じて $d_2$  を加算又は減算することにより、ラッピングされていない位相値を算出可能である。図3には、ラップされていない位相値が示されており、これらは、 $-d_1 \sim d_N$  の間に制約されてはいない。ラッピングされていない位相値を使用することにより、ラインフィッティングアルゴリズムによって、テストフィクスチャセットアップの遅延を正確に推定することができる。

## 【0019】

図3は、ラッピングされていない位相データと、このラッピングされていない位相データに対する線形フィッティングを含むグラフ300を示している。このグラフ300からわかるように、ポイント301は、雑音やなんらかのその他の影響によって破壊されている。尚、一実施例においては、最小二乗法を使用することにより、ラッピングされていない位相データに対して、ラインをフィッティング可能であるが、適切な任意のラインフィッティング法を使用することができる。この図3からわかるように、フィッティングされたラインの終点であるポイント302は、その基礎となっている位相データのポイント301の破壊によって破壊されてはいない。

## 【0020】

従って、代表的な一実施例においては、このフィッティングされたラインから遅延を算出している（従って、この遅延も、雑音又はその他の信号破壊の影響を受けにくい）。具体的には、群遅延は、位相応答の傾きの尺度である。フィッティングされたラインを使用して位相応答の線形部分をモデル化しているため、フィッティングされたラインの傾きを使用して、ポート延長の遅延値を算出することが好ましい。前述のように、ポート延長機能は、DCにおいては、ゼロ位相補償を適用している。しかしながら、フィッティングアルゴリズムを使用する場合には、非ゼロのY切片ポイント（DCにおいて、非ゼロの値）が生成される可能性が高い。ここで、Y軸は、ラッピングされていない位相を示す軸であ

50

る。そして、このような非ゼロのY切片は、遅延に基づいた位相（これは、ゼロのY切片を具備している）からオフセットされた位相を結果的にもたらすことになる。一実施例においては、周波数範囲の半分において、この位相オフセットを付与する値を有するオフセット遅延を加算することにより、非ゼロのY切片について、遅延を補償している。この結果、一実施例によれば、フィッティングされたラインの傾きと適切な位相オフセットを使用することにより、位相応答は、最低周波数においては、ゼロ補償を、中間点においては、Y切片の半分を、そして、最高周波数においては、Y切片の2倍を具備している。

#### 【0021】

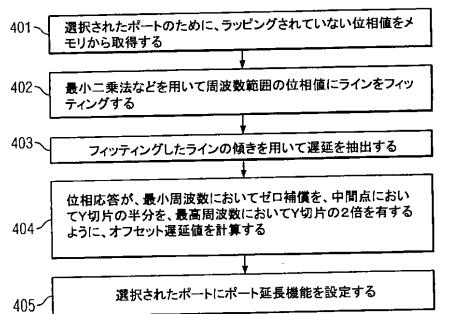

図4は、代表的な一実施例によるデータを処理してポート延長機能を校正するフローチャートを示している。尚、代表的な一実施例においては、このフローチャートは、ネットワークアナライザのプロセッサによって実行される適切なソフトウェア命令又はコードを使用して実装されている。或いは、この代わりに（又は、これに加えて）、その他の実施例においては、集積回路を使用することにより、このフローチャートの一部又は全体を実装可能である。

#### 【0022】

段階401において、校正対象のポートのラッピングされていない位相値をメモリから取得する。段階402において、例えば、最小二乗法を使用することにより、周波数範囲にわたる位相値に対してラインをフィッティングする。段階403において、そのフィッティングしたラインの傾きを使用して遅延を抽出する。そして、段階404において、位相応答が、最低周波数においては、ゼロ補償を、中間点においては、Y切片の半分を、そして、最高周波数においては、Y切片の2倍を有するように、オフセット遅延を算出する。次いで、段階405において、選択されているポートのポート延長機能を適切な設定内容に適切に設定する。尚、反射計測を使用して初期計測を実行しているため、ラッピングされていない位相値は、個々のポート上においてテストフィックスチャによって発生する遅延の2倍を表している。従って、そのポートの遅延を正確に表すべく、好ましくは、遅延算出プロセスにおいて、2による除算を実行する。

#### 【0023】

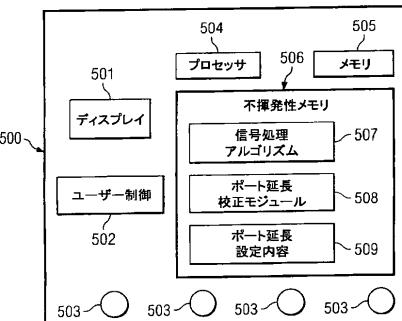

図5は、代表的な一実施例によるネットワークアナライザ500のブロックダイアグラムを示している。このネットワークアナライザ500は、ネットワークアナライザに共通的な一般的な要素を含んでいる。例えば、このネットワークアナライザ500は、ネットワークアナライザ500の動作を制御するプロセッサ504を含んでいる。又、ネットワークアナライザ500には、処理のために計測データを保存するメモリ505も含まれている。更には、このネットワークアナライザ500には、計測データ、ユーザーインターフェイス、又はこれらに類似のものを表示するためのディスプレイ501と、ネットワークアナライザ500の動作のユーザーによる制御を実現するユーザー制御手段502も含まれている。そして、ネットワークアナライザ500は、DUTに対して印加するべく信号を生成すると共に、試験動作の際にDUTから信号を受信する複数の同軸又はその他のポート503を含んでいる。

#### 【0024】

このネットワークアナライザ500は、好ましくは、ポート延長機能の自動校正を実行するロジック（ソフトウェア命令、集積回路、又はこれらに類似するもの）を含んでいる。例えば、図5に示されているように、不揮発性メモリ506を使用することにより、ネットワークアナライザ500の動作を定義するソフトウェア命令又はコードを保存している。この不揮発性メモリ506には、計測データの一般的なスペクトル分析を実行する信号処理アルゴリズム507が含まれている。そして、この信号処理アルゴリズム507には、テストフィックスチャとポート503間ににおける電気的な長さの差に対処するためのポート延長機能が含まれている。又、この不揮発性メモリ506には、ポート503からの反射信号を計測し、計測データを処理した後に、ポート延長の設定内容509を算出するポート延長校正モジュール508も含まれている。

#### 【0025】

10

20

30

40

50

適切なポート延長の校正を判定するための位相応答の抽出は、ポイント間隔が十分に密であって、計測ポイント間に180度未満の間隔が存在していることを前提としている。そして、計測の際には、必要に応じて、補間誤差補正を使用し、データポイント密度を増大させ、サーチを実行して、遅延利得を再算出し、この再算出した遅延を、低いポイント密度における遅延と比較することができる。そして、その遅延が実質的に同一に留まっている場合には、それらのポイントは、エイリアシングされていない。一方、その遅延が実質的に異なっている場合には、遅延が実質的に同一になるまで、データポイント密度を増大させる方法を反復する。このようにして遅延を抽出することにより、不良なフィクスチャ・ソース整合の影響を大幅に低減し、ユーザーによる解釈を必要とすることなしに、電気的に長いフィクスチャについて、適切な遅延を確実に判定することが可能となる。

10

#### 【0026】

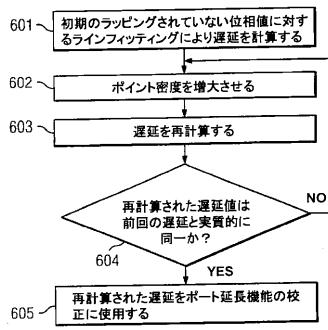

図6は、代表的な一実施例によるデータを処理してポート延長値を自動的に抽出するフローチャートを示している。尚、代表的な一実施例においては、このフローチャートは、ネットワークアナライザのプロセッサによって実行される適切なソフトウェア命令又はコード（例：図5のポート延長校正モジュール508）を使用して実装されている。或いは、この代わりに（又は、これに加えて）、その他の実施例においては、集積回路を使用することにより、このフローチャートの一部又は全体を実装可能である。

#### 【0027】

段階601において、初期のラッピングされていない位相値に対してラインをフィッティングすることにより、ポートのポート延長値を算出する。段階602において、ポイント密度を増大させる。段階603において、その増大させたポイント密度と関連するラッピングされていない位相値に対してラインをフィッティングすることにより、そのポートの遅延を再算出する。段階604において、論理比較を実行し、その再算出した遅延が以前の遅延と実質的に同一であるかどうかを判定する。そして、同一ではない場合には、プロセスフローは、段階602に戻り、ポイント密度を再度増大させて、遅延を再算出する。一方、再算出された遅延が実質的に同一である場合には、プロセスフローは、段階605に進み、その再算出した遅延を使用して、ポート延長機能を校正する。

20

#### 【0028】

ネットワークアナライザの掃引においてセグメント化掃引を使用しており（それぞれのセグメント内のポイント密度が同一ではなく、それらのセグメントが均等に分散していないてもよい）、それぞれのセグメントが十分なポイント密度を具備している場合には、それぞれのセグメントのラッピングされていない位相を使用することにより、個々のセグメントの遅延を判定する。そして、それぞれのセグメントの最初と最後の位相ポイントを判定し、抽出したセグメントの遅延に対して、最初と最後の周波数を適用することにより、セグメントデルタ位相とセグメントデルタ周波数を取得する。そして、デルタ位相の合計を算出し、すべてのデルタ周波数の合計によって除算することにより、全体遅延を判定する。

30

#### 【0029】

いくつかの代表的な実施例においては、ポート延長機能を校正することにより、ネットワークアナライザによる計測の正確且効率的な実行が可能となる。複数の手動による校正操作の実行は、必ずしも必要ではない。又、ポート延長機能の校正のための複数の基準を使用した計測の実行も、必ずしも必要ではない。更には、計測データを適切に処理することにより、不良なソース整合特性に起因する応答データ内のリップルにも拘らず、テストフィクスチャによって生じる遅延の相対的に正確な推定値を判定することができる。

40

#### 【0030】

本発明の実施態様は、上記の説明により明らかに理解されるものと思量するが、念のため以下に本発明の実施態様を列挙する。

##### (実施態様1)

テストフィクスチャを使用して被測定物（DUT）を計測するネットワークアナライザを自動的に校正する方法であって、

50

前記テストフィクスチャに接続された個々のポート上において、刺激信号を生成する段階（103）と、

前記個々のポート上において前記刺激信号の反射を計測し、計測データを生成する段階であって、前記計測データが前記テストフィクスチャの位相応答を反映している段階（104）と、

前記計測データを処理して、前記ネットワークアナライザと前記テストフィクスチャに関連する結合におけるインピーダンスの不整合によって生成されるリップルを補償する段階と、

前記処理段階に基づいて、前記ネットワークアナライザのポート延長の設定内容を調節する段階（405）と、

を有することを特徴とする方法。

（実施態様2）

前記処理段階が、複数の基準と関連する反射計測から得られた計測データと共に前記計測データを平均化する段階を有していることを特徴とする実施態様1に記載の方法。

（実施態様3）

前記処理段階が、周波数範囲にわたる平均群遅延値を算出する段階を有していることを特徴とする実施態様1に記載の方法。

（実施態様4）

前記処理段階が、前記計測データから得られた位相値に対してラインをフィッティングする段階（402）を有していることを特徴とする実施態様1に記載の方法。

（実施態様5）

前記フィッティングされたラインの傾きから遅延値を判定する段階（403）を更に有することを特徴とする実施態様4に記載の方法。

（実施態様6）

前記遅延値からオフセット値を判定する段階であって段階（404）を更に有し、

前記ポート延長の設定内容を調節する前記段階が、最低周波数においてはゼロ補償が提供されるように、中間点周波数においては前記フィッティングされたラインのY切片値の半分の補償が適用されるように、最高周波数においては前記Y切片値の2倍の補償が適用されるように、前記オフセット値を適用することを特徴とする実施態様4に記載の方法。

（実施態様7）

現在の遅延値が以前の遅延値と実質的に同一になるまで、前記計測データに対してラインをフィッティングすることにより、前記テストフィクスチャと関連する遅延値を反復的に算出する段階を更に有し、前記反復的な算出段階が、前記計測データに関連するポイント密度の連続的な増大と関連して実行されることを特徴とする実施態様1に記載の方法。

（実施態様8）

被測定物（DUT）に対して刺激信号を印加し、前記DUTからの信号を計測する複数のポート（503）と、

前記複数のポート上において実行される計測のスペクトル分析を実行する信号処理ロジック（507）であって、前記スペクトル分析によって生成された位相データに対してポート延長補償を適用する信号処理ロジックと、

前記ネットワークアナライザの校正モードにおいて、反射計測データを処理し、前記複数のポートから、DUTを保持するべく使用されているテストフィクスチャへの遅延の推定値を生成するロジック（508）と、

前記処理ロジックに応答して、ポート延長の設定内容を調節するロジックと、

を有することを特徴とするネットワークアナライザ。

（実施態様9）

反射計測データを処理する前記ロジックが、ラインフィッティング操作を実行して前記遅延の推定値を生成することを特徴とする実施態様8に記載のネットワークアナライザ。

（実施態様10）

前記処理ロジックが、前記計測データと関連するポイント密度を同時に増大させつつ、

10

20

30

40

50

現在の遅延値が以前の遅延値と実質的に同一になるまで、前記テストフィクスチャと関連する遅延値を反復的に算出するべく動作可能であることを特徴とする実施態様8に記載のネットワークアナライザ。

**【図面の簡単な説明】**

**【0031】**

【図1】代表的な一実施例によるフローチャートを示す図である。

【図2】代表的な一実施例によるオーブン基準を使用したテストフィクスチャの振幅応答、ラッピングされた位相応答（-～+ ラジアンの範囲に制限されている）、及び遅延応答を示す図である。

【図3】代表的な一実施例によるラッピングされていない位相データ（位相の絶対値がラジアンを上回ることが許容されている）にフィッティングされたラインを示す図である。

10

【図4】代表的な一実施例による別のフローチャートを示す図である。

【図5】代表的な一実施例によるネットワークアナライザを示す図である。

【図6】代表的な一実施例によるデータを処理してポート延長機能を校正するフローチャートを示す図である。

**【符号の説明】**

**【0032】**

503 ポート

507 信号処理ロジック

508 遅延推定値生成ロジック

10

20

**【図1】**

**【図2】**

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

F ターム(参考) 2G028 AA01 BB10 CG15 CG17 CG18 CG25 MS02