(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-165598

(P2004-165598A)

(43) 公開日 平成16年6月10日(2004.6.10)

(51) Int.Cl.<sup>7</sup>

**H01L 21/336**

**G02F 1/1368**

**H01L 21/20**

**H01L 21/268**

**H01L 29/786**

F 1

H01L 29/78 627G

G02F 1/1368

H01L 21/20

H01L 21/268

H01L 29/786

テーマコード(参考)

2 H092

5 F052

5 F110

審査請求 未請求 請求項の数 21 O L (全 28 頁) 最終頁に続く

(21) 出願番号 特願2003-63044 (P2003-63044)

(22) 出願日 平成15年3月10日 (2003.3.10)

(31) 優先権主張番号 特願2002-164134 (P2002-164134)

(32) 優先日 平成14年6月5日 (2002.6.5)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2002-274774 (P2002-274774)

(32) 優先日 平成14年9月20日 (2002.9.20)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人 100093506

弁理士 小野寺 洋二

(72) 発明者 菊池 廣

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所生産技術研究所内

(72) 発明者 本郷 幹雄

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所生産技術研究所内

(72) 発明者 波多野 睦子

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】アクティブ・マトリクス型表示装置とその製造方法

## (57) 【要約】

【課題】高性能の薄膜トランジスタ回路を有するアクティブ・マトリクス基板を備えた表示装置を経済的に提供する。

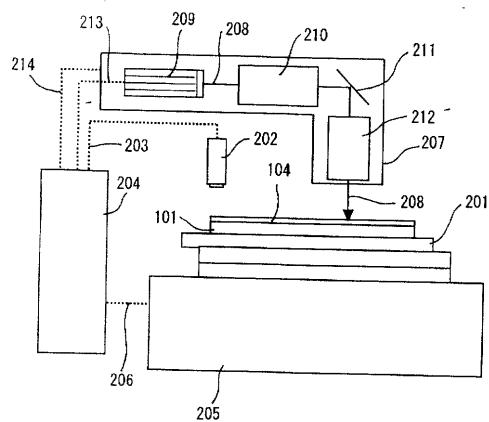

【解決手段】表示装置を構成するアクティブ・マトリクス基板101の画素部のアモルファスシリコン膜104に選択的にレーザビーム208を照射してポリシリコン膜105に改質する。改質されたポリシリコン膜105に薄膜トランジスタ等の画素回路を形成する。

【選択図】図5

図5

**【特許請求の範囲】****【請求項 1】**

絶縁基板上に成膜したシリコン膜に選択的にレーザ光を照射して改質された改質領域を有し、当該改質領域にアクティブ回路を有するアクティブ・マトリクス基板を具備したことを特徴とするアクティブ・マトリクス型表示装置。

**【請求項 2】**

前記アクティブ回路が前記アクティブ・マトリクス基板の表示領域に有する画素回路であることを特徴とする請求項 1 に記載のアクティブ・マトリクス型表示装置。

**【請求項 3】**

前記アクティブ回路が前記アクティブ・マトリクス基板の周辺領域に有する駆動回路であることを特徴とする請求項 1 または 2 に記載のアクティブ・マトリクス型表示装置。 10

**【請求項 4】**

前記アクティブ回路がボトムゲート型薄膜トランジスタで形成されたことを特徴とする請求項 1 乃至 3 の何れかに記載のアクティブ・マトリクス型表示装置。

**【請求項 5】**

前記アクティブ回路が薄膜トランジスタであり、当該薄膜トランジスタのゲートがタングステンまたはモリブデンを主成分とする配線材料で形成されたことを特徴とする請求項 1 乃至 4 の何れかに記載のアクティブ・マトリクス型表示装置。

**【請求項 6】**

前記画素回路の配置ピッチが画素ピッチに等しいことを特徴とする請求項 2 乃至 5 の何れかに記載のアクティブ・マトリクス型表示装置。 20

**【請求項 7】**

前記画素回路の配置ピッチが画素ピッチの 2 倍に等しいことを特徴とする請求項 6 に記載のアクティブ・マトリクス型表示装置。

**【請求項 8】**

前記画素回路の配置ピッチと周辺回路の配置ピッチが等しいことを特徴とする請求項 7 に記載のアクティブ・マトリクス型表示装置。

**【請求項 9】**

絶縁基板上に成膜したシリコン膜に選択的にレーザ光を照射して改質された改質領域を有し、当該改質領域に画素回路部を有するアクティブ・マトリクス基板を具備したアクティブ・マトリクス型表示装置の製造方法であって、 30

前記画素回路部を前記アクティブ・マトリクス基板に集約して配置し、当該集約して配置した部分に往復走査を用いて前記画素回路部のシリコン膜に選択的にレーザ光を照射して改質し、改質されたシリコン膜に画素回路を形成することを特徴とするアクティブ・マトリクス型表示装置の製造方法。

**【請求項 10】**

前記画素回路部のシリコン膜が CVD 法で形成されたアモルファスシリコン膜であり、前記改質されたシリコン膜がポリシリコン膜であることを特徴とする請求項 9 に記載のアクティブ・マトリクス型表示装置の製造方法。

**【請求項 11】**

前記画素回路部のシリコン膜がアモルファスシリコン膜から改質されたポリシリコン膜であり、改質されたシリコン膜がより改質されたポリシリコン膜であることを特徴とする請求項 9 に記載のアクティブ・マトリクス型表示装置の製造方法。 40

**【請求項 12】**

前記画素回路部のシリコン膜がスパッタ法で形成されたポリシリコン膜であり、改質されたシリコン膜がより改質されたポリシリコン膜であることを特徴とする請求項 9 に記載のアクティブ・マトリクス型表示装置の製造方法。

**【請求項 13】**

前記画素回路部のシリコン膜が CVD 法で形成されたポリシリコン膜であり、改質されたシリコン膜がより改質されたポリシリコン膜であることを特徴とする請求項 9 に記載のア 50

クティブ・マトリクス型表示装置の製造方法。

【請求項 14】

前記選択的にレーザ光が照射される領域を、前記アクティブ・マトリクス基板上にストライプ状に形成することを特徴とする請求項 9 乃至 13 の何れかに記載のアクティブ・マトリクス型表示装置の製造方法。

【請求項 15】

前記アクティブ・マトリクス基板に成膜したシリコン膜に対して、往復動作を用いて前記画素回路部のシリコン膜に選択的にレーザ光を照射して改質し、当該改質されたシリコン膜に画素回路を形成することを特徴とする請求項 9 乃至 14 の何れかに記載のアクティブ・マトリクス型表示装置の製造方法。 10

【請求項 16】

前記レーザ光の波長が 400 nm 乃至 2000 nm の固体レーザであることを特徴とする請求項 9 乃至 15 の何れかに記載のアクティブ・マトリクス型表示装置の製造方法。

【請求項 17】

前記レーザ光を生成するレーザがエキシマレーザであることを特徴とする請求項 9 乃至 16 の何れかに記載のアクティブ・マトリクス型表示装置の製造方法。

【請求項 18】

前記アクティブ・マトリクス基板上を走査する前記レーザ光の照射幅が 20 μm 乃至 100 μm であることを特徴とする請求項 9 乃至 17 の何れかに記載のアクティブ・マトリクス型表示装置の製造方法。 20

【請求項 19】

前記レーザ光の走査速度が 1 mm / s 乃至 1000 mm / s であることを特徴とする請求項 18 に記載のアクティブ・マトリクス型表示装置の製造方法。

【請求項 20】

前記アクティブ・マトリクス基板上を走査するレーザ光が単一のレーザ光を分割した複数のレーザ光であり、前記複数のレーザ光を用いて並列に走査することを特徴とする請求項 18 または 19 に記載のアクティブ・マトリクス型表示装置の製造方法。 30

【請求項 21】

前記アクティブ・マトリクス基板上を走査するレーザ光が複数のレーザ発振機の並列動作させた複数のレーザ光であり、前記複数のレーザ光を用いて並列に走査することを特徴とする請求項 18 または 19 に記載のアクティブ・マトリクス型表示装置の製造方法。 30

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、表示装置に係り、特に絶縁基板上に形成された半導体膜の膜質をレーザ光で改質し、改質された半導体膜でアクティブ素子を構成したアクティブ・マトリクス型表示装置とその製造方法に関する。なお、以下では、表示装置をディスプレイ装置あるいは単にディスプレイと称する場合もある。

【0002】

【従来の技術】

マトリクス配列された画素の駆動素子として薄膜トランジスタ等のアクティブ素子を用いたアクティブ・マトリクス型表示装置（またはアクティブ・マトリクス型駆動方式の表示装置、あるいはディスプレイ装置とも称する）が広く使用されている。当該業者によく知られているように、現在、この種のアクティブ・マトリクス型表示装置の多くは、半導体膜としてシリコン膜を用いて形成された薄膜トランジスタ等のアクティブ素子で構成された多数の画素回路を基板上に配置することで良質の画像を表示することができる。ここでは、上記アクティブ素子として、その典型例である薄膜トランジスタを例として説明する。

【0003】

しかし、半導体膜としてこれまで一般的に用いられてきたアモルファスシリコン半導体膜 50

(以下、シリコン半導体膜を単にシリコン膜とも称する)を用いた薄膜トランジスタでは、その移動度に代表される薄膜トランジスタの性能に限界があるために、高速、高機能が要求される回路を構成することは困難であった。より優れた画像品質を提供するのに必要な高移動度薄膜トランジスタの実現にはアモルファスシリコン膜をあらかじめポリシリコン膜に改質(結晶化)し、結晶化したポリシリコン膜を用いて薄膜トランジスタを形成するのが有効である。

#### 【0004】

この改質(結晶化)およびこの結晶性を改善するためにはエキシマレーザ光(または、レーザビーム、あるいは単にレーザ光とも称する)を照射してアモルファスシリコン膜をポリシリコン膜に改質する手法が用いられている。かかる手法については、例えば、「非特許文献1」、あるいは「非特許文献2」などに詳細に述べられている。10

#### 【0005】

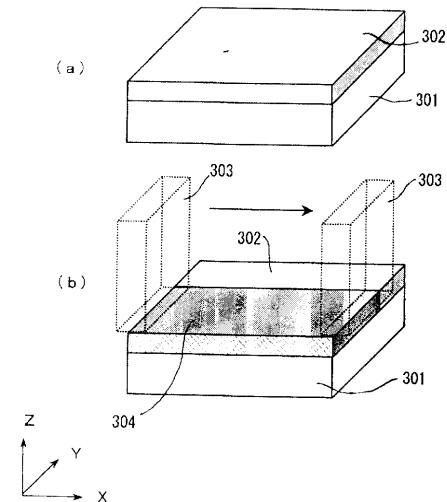

エキシマレーザ光照射を使用するアモルファスシリコン膜の結晶化による改質方法を図26で説明する。図26は最も一般的なエキシマパルスレーザ光照射を走査することによる結晶化方法の説明図であり、図26(a)は照射される半導体層を形成したガラス基板の構成、同(b)はレーザ光の照射で改質される状態を示す。この基板にはガラスやセラミックが用いられるが、ここではガラス基板を用いたものとして説明する。ガラス基板301上に下地膜(SiN等、図示せず)を介して堆積したアモルファスシリコン膜302に幅が数mm乃至数100mm程度の線状のエキシマレーザビーム303を照射し、矢印で示したように一方向(x方向)に沿って1乃至数パルス毎に照射位置を移動する走査を行うことにより、基板301全体のアモルファスシリコン膜302をポリシリコン膜304に改質する。この方法で改質したポリシリコン膜にエッチング、配線形成、イオン打ち込み等の種々の加工を施して、各々の画素部に駆動用の薄膜トランジスタ回路を配置したアクティブ・マトリクス基板を作成する。この基板を用いて液晶ディスプレイや有機EL等のアクティブ・マトリクス方式のディスプレイを製造するのである。20

#### 【0006】

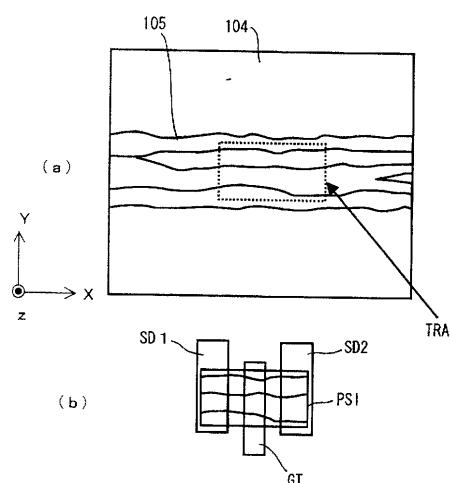

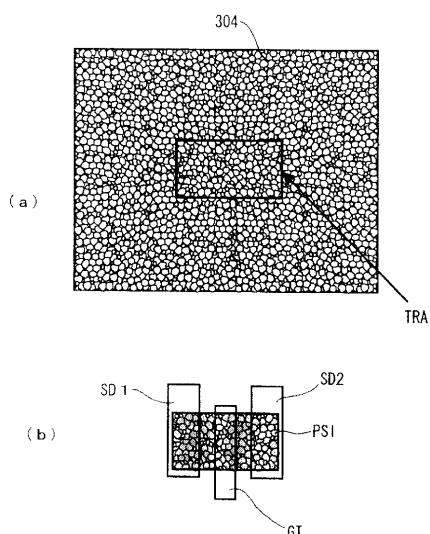

図27は図26におけるレーザ光照射部の部分平面図と薄膜トランジスタ部の構成例を説明する要部平面図である。図27(a)に示したように、レーザ光照射部には0.05μm乃至0.5μm程度の結晶化したシリコン粒子の多数が面内に均一に成長する。各シリコン粒子(すなわちシリコン結晶)の粒界はそれぞれが閉じている。図27(a)にて囲んだ部分を個々の薄膜トランジスタの半導体膜となるトランジスタ部TRAとなる。従来のシリコン膜の改質はこのような結晶化を指しており、本発明の改質とは内容が異なることは強調されるべきである。30

#### 【0007】

上記の改質されたシリコン膜304を利用して画素回路を形成するには図27(b)に示すように結晶化したシリコンの一部をトランジスタ部として利用するために図27(a)のトランジスタ部TRAとなる部分を除く不要部をエッチングで除去してアイランド状のシリコン膜の部分を形成し、このアイランドPSI上にゲート絶縁膜(図示せず)、ゲート電極(同)、ソース電極SD1、ドレイン電極SD2を配置してMISトランジスタを製造するのである。かかるトランジスタの形成技術は当該業者には周知である。従来の技術では結晶化のための改質操作を画素部全面に施すために改質の効率が劣るものであった。40

#### 【0008】

##### 【非特許文献1】

T.C.Angelis et al; Effect of Excimer Laser Annealing on the Structural and Electrical Properties of Polycrystalline Silicon Thin-Film Transistor, J. Appl. Phys., Vol.86, pp4600-4606, 1999。

##### 【非特許文献2】

H. Kuriyama et al; Lateral Grain Growth of Poly-Si Films with a Specific Orientation by an Eximer Laser Annealing Method, Jpn. J. Appl. Phys., Vol.32, pp6190-61950

5,1993あるいは K.Suzuki et al; Correlation between Power Density Fluctuation and Grain Size Distribution of Laser annealed Poly-Crystalline Silicon, SPIE Conference, Vol.3618, pp310-319, 1999。

#### 【0009】

##### 【発明が解決しようとする課題】

上記の従来技術においては、基板上に改質されたシリコン膜を形成して性能のよい薄膜トランジスタを配置したアクティブ・マトリクス基板を製造できる利点はあるものの、シリコン膜を改質するための経済費用が多大なものとなり、上記利点を十分に活用できない問題を抱えていた。かかる問題は、高額なエキシマレーザ装置を使用する必要性に加え、エキシマレーザパルスの強度、パルス間隔が不足するために基板全面のシリコン膜を改質するためには要する時間も多大となることから生じるものである。10

#### 【0010】

この問題は大形の表示装置を構成するための基板を多面取りすることでディスプレイ装置を安価に提供しようとする場合には著しいものとなる。基板サイズを大形化してシリコン膜を改質する場合には極めて高額な設備でかつ不十分なスループットしか得られないでの、かかる問題は到底、許容できるものではなかった。したがって、大サイズの基板であっても安価な設備で高速、かつ高効率にシリコン膜の改質が実現できる新規な技術の提供が強く求められていた。20

#### 【0011】

上記した課題を考慮してなされた本発明の第一の目的は、マトリクス状に配置された画素部に高性能の薄膜トランジスタ回路を有するアクティブ・マトリクス基板を備えた表示装置を経済的に提供することにあり、さらに、本発明の第二の目的は、これらの課題を解決するための具体的な製造技術を提供することにある。なお、本発明は、表示装置のためのガラス基板等に形成された半導体膜の改質に限るものではなく、他の基板例えはシリコンウエハ上に形成された半導体膜の改質等にも同様に適用できる。30

#### 【0012】

##### 【課題を解決するための手段】

上記の課題を解決するための手段として、本発明は画素部のシリコン膜に選択的にレーザビーム（以下、レーザ光とも称する）を照射し、該画素部の改質されたシリコン膜に画素回路を形成する。この画素回路は、主として薄膜トランジスタである。また、本発明によるアクティブ・マトリクス型表示装置の製造では、好ましくは、往復動作を用いて画素部のシリコン膜に選択的にレーザビームを照射し、該画素部の改質されたシリコン膜に画素回路を形成する。さらに好ましくは、画素回路部を集約して配置し、該集約部分に往復動作を用いて画素部のシリコン膜に選択的にレーザビームを照射し、該画素部の改質されたシリコン膜に画素回路を形成する。30

#### 【0013】

本発明によるシリコン膜の改質と従来技術でのシリコン膜の改質とはその内容が異なっており、ちがいについて説明すると以下のようになる。すなわち、本発明のシリコン膜の改質では、改質により結晶化したシリコン膜は幅 $0.1\text{ }\mu\text{m}$ 乃至 $10\text{ }\mu\text{m}$ 、長さ $1\text{ }\mu\text{m}$ 乃至 $100\text{ }\mu\text{m}$ 程度の単結晶の集合体となり、良好なキャリア移動度を確保できる。その値は、電子移動度としておよそ $300\text{ cm}^2/\text{V}\cdot\text{s}$ 以上、望ましくは $500\text{ cm}^2/\text{V}\cdot\text{s}$ 以上にもなる。40

#### 【0014】

一方、従来のエキシマレーザを用いたシリコン膜の改質では、レーザ光照射部には $0.05\text{ }\mu\text{m}$ 乃至 $0.5\text{ }\mu\text{m}$ 程度の結晶化したシリコン粒子の多数が均一に成長する。電子移動度としてはおよそ $100\text{ cm}^2/\text{V}\cdot\text{s}$ 以下、平均的には $50\text{ cm}^2/\text{V}\cdot\text{s}$ 程度のシリコン膜が得られる。かかる従来のシリコン膜の改質は、アモルファスシリコン膜の電子移動度である $1\text{ cm}^2/\text{V}\cdot\text{s}$ 以下に比べれば性能は向上しているが、本発明ではかかる従来の改質より優れた改質を用いるのが特長であり、本発明の改質と従来技術の改質は内容が異なることは強調されるべきである。50

## 【0015】

本発明による表示装置を構成するアクティブ・マトリクス基板に有する画素部のシリコン膜はCVD法で形成されたアモルファスシリコン膜（非晶質シリコン膜）であり、画素部の改質されたシリコン膜がポリシリコン膜（多結晶シリコン膜）であるのが好ましい。しかし、本発明はこれに限定されることなく、該画素部のシリコン膜がアモルファスシリコン膜から改質されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であることも可能である。ここで言う「改質されたポリシリコン膜」とは、非晶質シリコンが結晶化したシリコン膜に変化したものと意味し、各々の結晶の粒界は基本的には閉じている状態にある。また、「より改質されたポリシリコン膜」とは、その粒界が所定方向に連続している結晶構造を有するものに変化した状態を意味する。

10

## 【0016】

さらに、本発明は、該画素部のシリコン膜がスパッタ法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるようにすることもできる。さらに該画素部のシリコン膜がCVD法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるような組み合わせも可能なのである。

## 【0017】

本発明では基板上の画素部のシリコン膜に選択的にレーザビームを照射するので、選択的に照射される領域、すなわち改質されたシリコンの領域が、基板面に沿ってストライプ状に形成されるのを特徴とする。かかる形状を積極的に採用することで、薄膜トランジスタを形成する過程でエッチングで除去してしまう画素部以外の領域にはレーザビームを照射する必要がなくなり、不要な作業を大幅に低減できる。

20

## 【0018】

本発明で使用するレーザは発振波長400nm乃至2000nmの連続発振固体レーザであることが好ましい。連続発振レーザ光はアニール対象である非晶質あるいは多結晶シリコン薄膜に対して吸収のある波長、即ち紫外波長から可視波長が望ましく、より具体的にはArレーザあるいはKrレーザとその第二高調波、Nd:YAGレーザ、Nd:YVO<sub>4</sub>レーザ、Nd:YLFレーザの第二高調波及び第三高調波などが適用可能である。しかし、出力の大きさ及び安定性を考慮すると、LD（レーザダイオード）励起Nd:YAGレーザの第二高調波（波長532nm）あるいはNd:YVO<sub>4</sub>レーザの第二高調波（波長532nm）が最も望ましい。このレーザ波長の上限および下限はシリコン膜の光吸収が効率よく生じる範囲と経済的に入手できる安定なレーザ光源の兼ね合いから定まるものである。

30

## 【0019】

本発明の固体レーザはシリコン膜に吸収するレーザ光を安定に供給できるとともに、ガスレーザに特有なガス交換作業や発信部の劣化等の経済負担が少ないので特徴であり、経済的にシリコン膜を改質する手段として好ましい。しかし、本発明では該レーザが波長150nm乃至400nmのエキシマレーザであることを積極的に排除するものではない。

## 【0020】

本発明ではレーザ光を光学的に調整し、強度の空間分布を均一化したうえでレンズ系を用いて集光して照射するのが望ましく、さらに、改質されたシリコン膜の結晶性を調整するためには、連続発振レーザ光を光学的に成形してパルス化したうえで照射するのが好ましい。かかる場合のレーザのパルス幅は100ナノ秒(ns)以上、1ミリ秒(ms)以下の範囲から選択されることが望ましい。

40

## 【0021】

本発明では基板にストライプ状にレーザ光を照射する時の照射幅が20μm乃至1000μmの幅であることが好ましい。かかる幅は画素部回路に必要な領域の幅と該幅が画素ピッチに占める割合の両者から経済性を勘案して定まるものである。照射部の長さは基板のサイズ、画素領域のサイズを勘案して定まるものである。本発明ではステージの走査に同期してレーザ光の照射を断続的に行うことも可能であり、かかる場合にも本発明の効果が

50

失われることはない。

【0022】

本発明では該レーザ光照射が $1\text{ mm/s}$ 乃至 $1000\text{ mm/s}$ の速度で走査することを特徴とする。かかる走査速度の下限は基板内の所定領域を走査するのに要する時間と経済負担の兼ね合いから定まるものであり、上限は走査に必要な機械設備の能力から制限されるものである。

【0023】

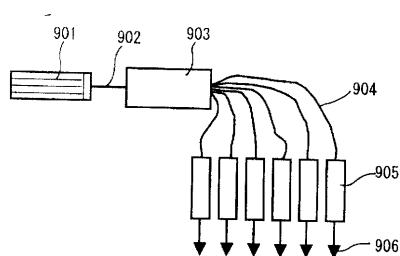

本発明では該レーザ照射がレーザ光を光学系で収束したビームを走査することでなされることを特徴とするが、このとき、単一のレーザ光を単一のビームに収束する光学系を使用してもよい。しかし、単一のレーザ光を複数に分割して照射することにより、複数の画素部の列に同時走査で照射することができるため、レーザ光の照射の効率は著しく向上する。レーザ光を複数に分割して照射するのは本発明の好ましい形態である。このようなレーザ光の走査形態は大形サイズの基板を短時間で処理する場合には特に好ましい。

【0024】

また、本発明では該レーザ光照射が複数のレーザ発振機を並列動作して照射された場合にレーザ照射の効率が著しく向上する。かかる形態も大形サイズの基板を短時間で処理する場合には特に好ましい。

【0025】

さらに本発明では、選択的に走査されるレーザ光照射領域が画素回路部に止まらず、周辺回路部を形成することも可能である。レーザ光を周辺回路の形成領域まで照射する選択は画素回路部に形成する薄膜トランジスタの性能が周辺回路に必要な性能を満たす場合には推奨される。かかる場合にはディスプレイの駆動に必要な駆動回路チップ（LSIドライバ、ドライバIC）の数を大幅に低減できるので、経済効果も多大である。

【0026】

さらに本発明では改質されたシリコン膜から形成される回路が一般的なトップゲート型薄膜トランジスタ回路に限定されることなく、ボトムゲート型薄膜トランジスタ回路とすることも可能である。NチャンネルMISもしくはPチャンネルMISのみの单チャンネル回路を必要とする場合には製造工程の簡略化からボトムゲート型がむしろ好ましい場合もある。かかる場合にはゲート配線上に絶縁膜を介したシリコン膜をレーザ照射で改質するので、ゲート配線材料には高融点金属の採用が好ましく、タンゲステン（W）もしくはモリブデン（Mo）を主成分とするゲート配線材料の使用が本発明の特徴の1つとなる。

【0027】

以上に述べた本発明の手段を用いて製造することにより、レーザ光照射の効率を大幅に改善した結果として、画素回路の配置ピッチが画素ピッチに等しいアクティブ・マトリクス基板が得られる。

【0028】

ところが画素回路の配置を工夫すると、驚くべき効果としてレーザ光照射の効率をさらに大幅に改善することが可能となる。かかる改良された画素回路の配置では、等間隔に配置された2列分の画素の回路部分を列の中央部分に集約配置し、かかる集約配置した画素領域のみに選択的にレーザ光照射してシリコン膜を改質することで、レーザ光照射の効率を約2倍にも高められる。かかる本発明では画素回路の配置ピッチが画素ピッチの2倍に等しいことが特徴となる。

【0029】

本発明の画素回路、あるいは周辺回路の半導体構造を有するアクティブ・マトリクス基板を使用することで優れた画質の液晶表示装置を安価に提供できる。また、本発明のアクティブ・マトリクス基板を使用することで優れた画質の有機ELディスプレイ装置をも安価に提供できる。さらに本発明では液晶ディスプレイ装置、有機ELディスプレイ装置にとどまることなく、同様の半導体構造を画素回路や周辺回路に有する他の方式のアクティブ・マトリクス型ディスプレイ装置にも適用可能である。

【0030】

10

20

30

40

50

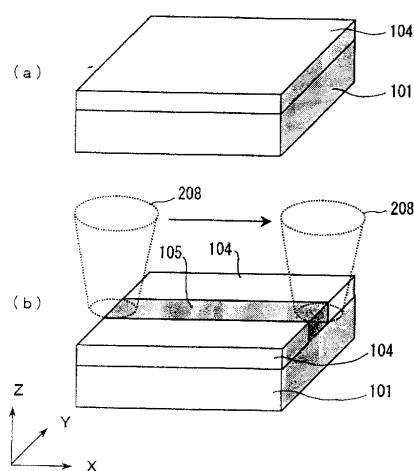

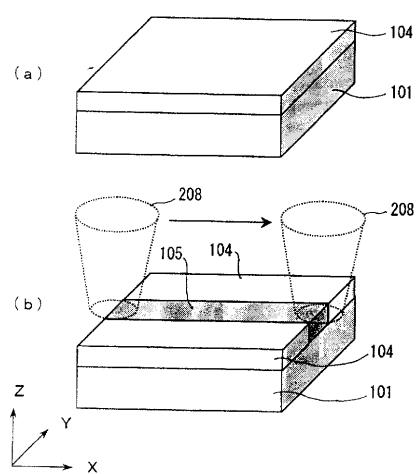

本発明の概要を図1～図7を参照して説明する。なお、これらの図面の説明は後述の実施の形態における実施例の記述と重複する部分もある。先ず、ガラスを好適とする基板（以下、ガラス基板と称する）101上にバリア膜として機能するSiN膜102およびSiO膜103をCVD等の手段により薄く堆積し、その上にアモルファスシリコン膜104を50nm程度の厚さにCVD法で堆積する（図1の（a））。上記したバリア膜の層構成、膜厚およびシリコン膜の膜厚等は一例であり、この記述が本発明を制限するものではないことは強調されるべきである。その後、本発明のレーザ照射法で画素部のみに照射し、画素回路を形成すべき部分のシリコン膜を改質する（図1（b））。

### 【0031】

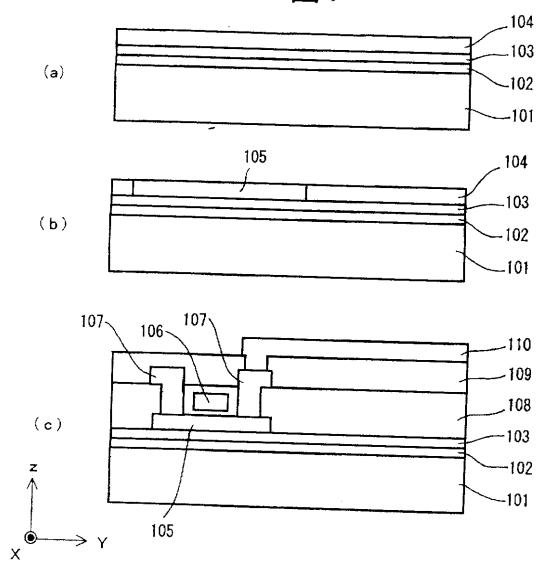

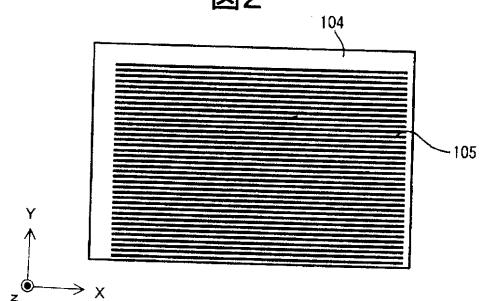

上記基板内の照射部分の平面を図2に模式的に示してある。本発明では、改質されたシリコン膜105が所定の方向に並行するストライプ状に形成できることを示している。かかるレーザ光照射を実施するための装置の一例を図3に示す。本発明のアモルファスシリコン膜104を堆積したガラス基板101をXY方向に移動する駆動ステージ201に設置し、基準位置測定用カメラ202を用いて位置合わせを行う。基準位置測定用カメラ202からの基準位置測定信号203は制御装置204に入力される。駆動設備205は制御装置204から入力された制御信号206に基づいて照射位置の微調整を行い、所定の速度で駆動ステージ201を移動させ、ガラス基板を一方向に走査する。この走査に同期して照射設備207からのレーザ光208をアモルファスシリコン膜104に照射して、当該シリコン膜104をポリシリコン膜105に改質する。

### 【0032】

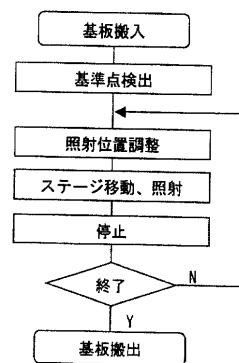

照射設備207内にはレーザ光源209、ホモジナイザ等の光学系210、反射ミラー211、集光レンズ系212を配置することで所望の照射ビームを形成できる。レーザ光の照射時間、照射強度などは制御装置204からのオン・オフ（以下、ON-OFF）信号213、制御信号214で調整する。このような照射シーケンスをフローチャートで示したのが図4である。本発明では、上記走査を並列に行う複数の照射設備207を並列動作させることで照射の速度を大幅に向上できることは強調されてよい。

### 【0033】

本発明では上記の動作で基板上を一方向（x方向）に走査しながら照射した後、照射設備207とガラス基板の相対位置を上記一方向に交差する他方向（y方向）に若干移動させて逆方向に走査しながら照射する往復動作する照射法を用いるのが望ましい。この往復動作はステージの走査時間を照射に有効に利用できるので、ガラス基板上の全ての画素部を照射するのに必要な時間を大幅に低減する効果がある。

### 【0034】

本発明のレーザ光照射をさらに詳細に示すと図5のようになる。本発明では図5（a）に示すガラス基板101上に下地膜（図示せず）を介して形成したアモルファスシリコン膜104に図5（b）に示すように集光したレーザ光208を照射しながら照射部をx方向に走査する。その結果、改質されたシリコン膜105が狭い帯状（ストライプ状）に形成できるのである。図6は本発明のレーザ光の照射部と薄膜トランジスタの構成を模式的説明図であり、同図（a）はレーザ光照射部の平面図、同図（b）は薄膜トランジスタの構成を例を示す平面図である。

### 【0035】

図6の（a）に示したように、ガラス基板101上のアモルファスシリコン膜104にレーザ光を走査して照射することで、当該レーザ光照射部には結晶化したシリコンがレーザ光の走査方向（同図のx方向）に沿って帯状に成長する。この結晶化したシリコンの成長領域すなわちポリシリコン膜の領域に点線で示したトランジスタ部TRAが形成される。

### 【0036】

本発明のシリコン膜の改質はかかる結晶化を指しており、結晶化した部分は上記帯状の幅が0.1μm乃至10μmで長さが1μm乃至100μm程度の単結晶の集合体となる。かかる改質されたシリコン膜105を利用して画素回路を形成することで、改質の効率が大幅に向上する。具体的には結晶化したシリコン膜の一部を図6（a）に示したトランジ

10

20

30

40

50

スラブ T R A として利用するために不要部をエッティングで除去して図 6 ( b ) に示すようにシリコン膜のアイランド P S I を形成し、このアイランド P S I 上にゲート絶縁膜(図示せず)、ゲート電極 G T 、ソース電極 S D 1 、ドレイン電極 S D 2 を配置して M I S トランジスタを製造するのである。なお、このようなトランジスタの形成技術は当該業者には周知である。また、ガラス基板上でのレーザ光照射のスポット形状は円形に成形する以外にも橢円形、矩形、長方形等の形状に成形することも可能である。かかる形状は光学系で調整可能の範囲である。

### 【 0 0 3 7 】

本発明では、上記のように形成した改質されたシリコン膜 1 0 5 を図 1 ( c ) に示すように、所定の回路になるようにエッティングし、ゲート絶縁膜(図示せず)、ゲート電極(またはゲート配線) 1 0 6 、層間絶縁膜 1 0 7 、ソース / ドレイン配線 1 0 8 、パシベーション膜 1 0 9 、画素電極となる透明電極 1 1 0 を順次、形成する。これにより、改質されたシリコン膜 1 0 5 を用いたトランジスタ回路を画素に配置したアクティブ・マトリクス基板が形成できる。このトランジスタ回路、および電極の形成にかかる加工技術の詳細は当該業者には周知である。また工程の途中にイオン打ち込み、活性化アニール等の工程の追加が必要であることも周知である。

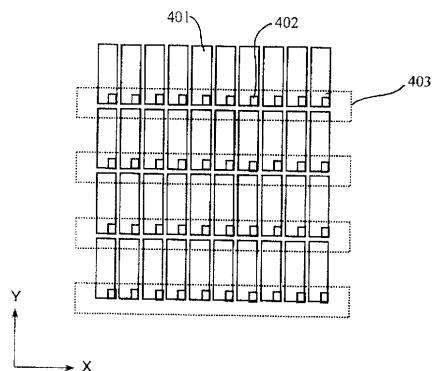

### 【 0 0 3 8 】

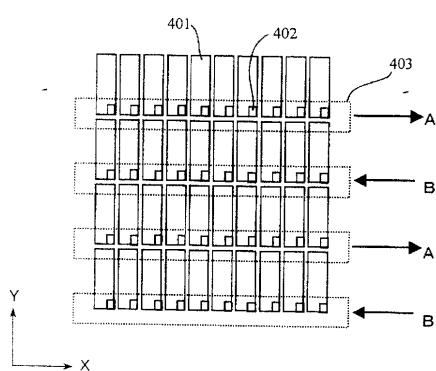

図 7 は本発明のアクティブマトリクス基板の画素部とレーザ光照射領域の関係を説明する平面図である。図 7 は必ずしも実寸法とは対応しないが、模式的に画素 4 0 1 と画素回路部 4 0 2 とレーザ光照射部 4 0 3 の関係を示している。本発明では、レーザ照射部 4 0 3 の面積が画素部全体の面積の 1 / 2 から 1 / 5 程度にできることがわかる。

### 【 0 0 3 9 】

#### 【 発明の実施の形態 】

以下、本発明の実施の形態について、実施例の図面を参照して詳細に説明する。

### 【 0 0 4 0 】

#### [ 第 1 実施例 ]

本発明の第 1 実施例を図 1 ~ 図 5 、および図 8 を参照して説明する。図 1 は本発明による表示装置の第 1 実施例におけるアクティブ・マトリクス基板の構成手順を模式的に示す断面図、図 2 は本発明による表示装置の第 1 実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射パターンを模式的に説明する平面図、図 3 は本発明による表示装置の第 1 実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射装置の模式的構造図、図 4 は本発明による表示装置の第 1 実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射作業の手順を説明するフロー・チャート、図 5 は本発明による表示装置の第 1 実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射の立体的な説明図である。そして、図 8 は本発明の第 1 実施例におけるアクティブマトリクス基板の画素部とレーザ光照射領域の関係を説明する平面図である。

### 【 0 0 4 1 】

先ず、図 1 の ( a ) に示したように、厚さが 0 . 3 m m 乃至 1 . 0 m m 程度で、好ましくは 4 0 0 ° C 乃至 6 0 0 ° C の熱処理で変形や収縮の少ない耐熱性のガラス基板 1 0 1 を準備する。このガラス基板 1 0 1 の上に熱的、化学的なバリア膜として機能するおよそ 5 0 n m 厚の S i N 膜 1 0 2 および約 5 0 n m 厚の S i O 膜 1 0 3 を C V D 法で連続かつ均一に堆積し、該バリア膜上にアモルファスシリコン膜 1 0 4 を 5 0 n m 程度の厚さに C V D 法で堆積する。かかる C V D 法を用いたバリア膜およびアモルファスシリコン膜の堆積方法については当該業者には周知である。その後、本発明のレーザ光照射法で画素部のみに照射し、画素回路を形成すべき部分のシリコン膜をレーザ光照射によりアモルファスシリコン膜からポリシリコン膜 1 0 5 に改質する。

### 【 0 0 4 2 】

図 1 の ( b ) はレーザ光の照射により所要の部分のアモルファスシリコン膜をポリシリコン膜に改質した状態を示す断面図である。図 1 の ( b ) に示したレーザ光照射を実施する

10

20

30

40

50

ための装置として図3に示す装置を用いることができる。この照射装置を用いるレーザ光照射の概要については前記の解決手段の項での説明と重複するが、本実施例ではアモルファスシリコン膜104を堆積したガラス基板101はx-y方向の駆動ステージ201上に設置され、基準位置測定用カメラ202を用いて位置合わせを行う。基準位置測定信号203は制御装置204に入力され、駆動設備205に入力された制御信号206に基づいて照射位置の微調整を行い、所定の速度でステージ201を移動させて一方向(図1のx方向)に走査する。かかる走査に同期して照射設備207からのレーザ光208をアモルファスシリコン膜104に照射して、シリコン膜を改質する。

#### 【0043】

前記したように、照射設備207内には一例としてLD(レーザダイオード)励起のNd:YVO<sub>4</sub>レーザの第二高調波(波長532nm)からなる1Wのレーザ光源209、ホモジナイザ等の光学系210、反射ミラー211、集光レンズ系212を配置することによって所望の照射ビームを形成できる。レーザ光の照射時間、照射強度などは制御装置204からのON-OFF信号213、制御信号214で調整する。

#### 【0044】

図4は図3の照射設備を用いたレーザ光の照射シーケンスを説明するフローチャートである。本実施例では、レーザ光を光学的に調整し、強度の空間分布を均一化したうえでレンズ系を用いて集光して照射するのが望ましい。さらに、改質されたシリコン膜の結晶性を調整するためには、連続発振レーザ光を光学的に成形してパルス化したうえで照射するのが好ましい。かかる場合のレーザのパルス幅は100ナノ秒(ns)以上、1ミリ秒(ms)以下の範囲から選択されることが望ましく、たとえば、5ミクロン(μm)の粒径を得るために最適なレーザ条件として、パルス幅が10マイクロ秒(μs)が選択される。

#### 【0045】

図2では基板内の照射部分を平面図で模式的に示しており、本実施例では改質されたシリコン膜105がストライプ状に形成できることを示している。レーザ光の照射ビーム径は画素部の回路領域の幅より大であることが要求されるので、一例として30μmが選択される。

#### 【0046】

本実施例では図8に示すように、上記の動作で基板上をx方向(A方向=前記一方向)に照射した後、y方向に若干シフトさせて上記x方向に沿って逆方向(B方向)に走査しながら照射する往復動作での基板面を二次元に照射する方法を用いるのが望ましい。走査速度の一例として300ミリ/秒(ms)が選択される。この往復動作を繰り返すことによって、全ての画素部のシリコン膜を良質なポリシリコン膜に改質できる。改質されたポリシリコン膜はレーザ光の照射方向に沿って単結晶領域は図6に示したように、非対称に一方向に成長した特徴ある結晶形態となる。

#### 【0047】

上記のように形成した改質されたシリコン膜105を図1(c)に示すような所定の回路になるようにエッチング処理し、ゲート絶縁膜(図示せず)、ゲート電極(図6(b))のゲート電極GT)106、層間絶縁膜107、ソース/ドレイン配線108、パシベーション膜109、画素電極となる透明電極110を順次、形成することで、改質されたシリコン膜105を用いたトランジスタ回路を画素回路に配置したアクティブ・マトリクス基板が形成される。

#### 【0048】

かかるトランジスタ回路の形成ではゲート部の電子もしくはホールの移動方向が結晶の成長方向に並行して一致する配置とすることが望ましい。並行して一致するとは、ポリシリコン膜の結晶成長方向に対する角度が0度もしくは180度を指す。この角度に許容される誤差はおよそ30度以内である。この理由を表1に示す。

#### 【0049】

#### 【表1】

表1

| 方向(deg) | 電子移動度(cm <sup>2</sup> /Vs) |

|---------|----------------------------|

| 0       | 520                        |

| 30      | 500                        |

| 60      | 260                        |

| 90      | 150                        |

| 120     | 220                        |

| 150     | 510                        |

| 180     | 580                        |

10

20

30

40

50

表1は電子移動の方向とレーザ光照射の走査方向(角度: deg)と電子移動度( $\text{cm}^2/\text{Vs}$ )の関係を検証した結果を示す。表1に示されたように、レーザ光照射の走査方向で定義する結晶成長の方向がなす角度(絶対値)と電子移動度の関係は、0度もしくは180度に対し約30度以下のずれの場合には約 $300\text{ cm}^2/\text{V}\cdot\text{s}$ 以上を充分に確保できる。これに対し、上記結晶成長の方向との誤差が30度を超えると電子移動度は低下し、直角な方向(90度)では電子移動度は極端に低下することが分かった。本実施例はこの知見に基づくものである。なお、このことは後述する他の実施例でも同様である。

#### 【0050】

かかる配置の特長は、本実施例(後述する他の実施例も含めた本発明全体)がレーザ光照射の往復動作を許容することから生じるものである。画素回路のレイアウトが同じ場合には往路から形成したレーザ光照射部403に形成される画素回路部(図8のA方向の走査部)と復路から形成したレーザ照射部403に形成される画素回路部(図8のB方向の走査部)ではキャリアの移動方向と結晶の成長方向に0度もしくは180度の違いが生じる。本実施例を含む本発明では、このような違いがトランジスタ特性にほとんど影響しないことを見い出したために、0度と180度の2種の配置が許容できるようになったのである。かかる自明でない結果に基づいて往復照射が可能になったことは強調されるべきである。

#### 【0051】

上記の如き積極的な結晶方向の配置によりキャリアが結晶粒界を横切る確率を低減できるので、粒界散乱に起因する特性劣化を最小限に抑制することができ、最良のトランジスタ回路を得ることが可能となる。この種のトランジスタ回路、および電極形成にかかる加工技術の詳細は当該業者には周知である。また工程の途中にイオン打ち込み、活性化アニール等の工程の追加が必要であることも周知である。

#### 【0052】

かかる手法によって画素部にポリシリコン半導体膜を用いた薄膜トランジスタ回路を配置することができる。本実施例で得られる薄膜トランジスタの性能は、例えばNチャンネルMISトランジスタを作成する場合に、電界効果移動度が約 $300\text{ cm}^2/\text{V}\cdot\text{s}$ 以上でかつ、閾値電圧のバラツキを±0.2V以下に抑制することができ、高性能、高信頼で動作し、デバイス間の均一性が優れたアクティブ・マトリクス基板を用いた表示装置を製造することができる。

**【 0 0 5 3 】**

また本実施例では、電子キャリアを付与するリンのイオン打ち込みに代えてホールキャリアを付与するボロン打ち込みによりPチャンネルMISトランジスタを製造することもできるし、ホトマスクの配置を代えN型とP型を同一基板に形成し、いわゆるCMOS型の回路を形成することも可能である。CMOS型の回路では周波数特性の向上が期待でき、高速動作に適している。しかし反面、マスク数が増加することによる製造工程の増加が背反する要因となる。かかる半導体製造技術および半導体回路技術の詳細については当該業者には周知であり、どのような半導体装置を構成するかは表示装置に必要な特性と製造するためのコストを勘案したうえで最適化することが求められる。

**【 0 0 5 4 】**

本実施例のアクティブ・マトリクス基板を用いて液晶表示装置を製造するための技術手法は当該業者には周知である。具体的には、アクティブ・マトリクス基板上に液晶配向膜層を形成し、これにラビング等の手法で配向規制力を付与し、画素部の周辺にシール剤を形成した後、同様に配向膜層を形成したカラーフィルタ基板を所定のギャップで対向配置し、このギャップ内に液晶を封入し、シール剤の封入口を封止材で閉鎖することで液晶セルを形成する。

**【 0 0 5 5 】**

その後、この液晶セルの周辺部にゲートドライバLSIおよびソースドライバLSIを実装搭載することで液晶表示モジュールとする。この液晶表示モジュールに偏光板、導光板、バックライト等を実装することで液晶表示装置を製造することができる。

**【 0 0 5 6 】**

本実施例のアクティブ・マトリクス基板を使用した液晶表示装置は、その画素回路に上記した優れたポリシリコン薄膜トランジスタ回路を配置することで、電流駆動能力に優れることから高速動作に適している。さらに、閾値電圧のバラツキが小さいために画質の均一性に優れ液晶表示装置を安価に提供できるのが特長である。

**【 0 0 5 7 】**

また、本実施例のアクティブ・マトリクス基板を用いて有機EL表示装置を製造する有機EL技術手法は当該業者には周知である。具体的には、アクティブ・マトリクス基板上有機EL素子分離のためのバンクパターンを形成し、透明電極表面から順次、ホール輸送層、発光層、電子輸送層、陰極金属層などを蒸着して積層体を構成する。かかる積層層を形成した基板の画素部の周囲にシール材を配置し、封止缶で封止する。かかる封止技術は画素部の有機ELを水分などから保護する。有機ELを水分などから保護することは画像品質の劣化を抑制するために必要であり、封止缶内に乾燥剤を設置することが推奨される。

**【 0 0 5 8 】**

有機EL表示装置用のアクティブマトリクス駆動では、有機EL素子が電流駆動発光方式であるために高性能の画素回路の採用が良質な画像の提供には必須であり、特にCMOS型の画素回路を用いるのが望ましい。本実施例のアクティブ・マトリクス基板は、このような要求にこたえる高性能のアクティブ・マトリクス基板として好適であり、本実施例のアクティブ・マトリクス基板を用いた有機EL表示装置は本実施例の特長を最大限に發揮する表示装置の1つであることも強調されるべきである。

**【 0 0 5 9 】****[ 第2実施例 ]**

本実施例ではレーザ光を照射して改質する対象となるシリコン膜はアモルファスシリコン膜に限定されることはなく、アモルファスシリコン膜から改質されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であることも可能である。さらに、本実施例は、該画素部のシリコン膜がスパッタ法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるようにすることもできる。さらに該画素部のシリコン膜がCVD法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるような

10

20

30

40

50

組み合わせも可能なのである。前記した第1実施例とは異なるシリコン膜に対して改質した本発明の実施形態を前記した各図を参照して説明する。

#### 【0060】

第1実施例と同様に、厚さが0.3mm乃至1.0mm程度で、好ましくは400°C乃至600°Cの熱処理で変形、収縮の少ない耐熱性のガラス基板101を準備する。このガラス基板上に熱的、化学的なバリア膜として機能するおよそ50nm厚のSiN膜102および、約50nm厚のSiO膜103をCVD法で連続かつ均一に堆積し、該バリア膜上にアモルファスシリコン膜104を50nm程度の厚さにCVD法で堆積する（図1の（a）参照）。

#### 【0061】

このアモルファスシリコン膜に対し、エキシマパルスレーザ光照射を走査する結晶化方法を前記の図26も参照して説明する。図26（a）のように、ガラス基板301上に下地膜（図示せず）を介して堆積したアモルファスシリコン膜302に幅が数mm乃至数100mm程度の線状のエキシマレーザビーム303を照射し、1乃至数パルス枚に照射位置を移動する走査により、広い領域のアモルファスシリコン膜302が改質されたシリコン膜304となる。かかる広域照射を基板全面に施すことでアモルファスシリコン膜をポリシリコン膜に改質することができる。

#### 【0062】

かかるエキシマパルスレーザ光で改質されたシリコン膜に対して本実施例のレーザ光照射による改質を第1実施例と同様に施してポリシリコンの結晶性をより向上させることができ。本実施例の実施形態では本実施例のレーザ光照射による改質の後、第1実施例と全く同様の手順で本発明のアクティブ・マトリクス基板とこれを用いた液晶表示装置を作成することができる。

#### 【0063】

本実施例の特に留意すべき特徴点は、あらかじめエキシマパルスレーザ光照射による微細結晶が生成しているシリコン膜を用いたにもかかわらず、レーザ光照射で生成したポリシリコン膜はアモルファスシリコン膜から出発して生成したポリシリコン膜と異なることがないという点である。すなわち、エキシマパルスレーザ光照射を施した場合でも、本実施例で得られたポリシリコン膜を用いた薄膜トランジスタでは、例えばNチャンネルMISトランジスタを作成する場合に、電界効果移動度が約 $300\text{ cm}^2/\text{V}\cdot\text{s}$ 以上でかつ、閾値電圧のバラツキを±0.2V以下に抑制することができ、高性能、高信頼で動作し、デバイス間の均一性が優れたアクティブ・マトリクス基板を製造することができ、またこの基板を用いることで高品質の表示装置を得ることができる。

#### 【0064】

当該技術分野における周知の知見ではエキシマパルスレーザ光照射を用いてアモルファスシリコン膜を結晶化できる。かかる結晶化では約 $1\mu\text{m}$ 以下の微細結晶からなるポリシリコン膜が得られ、このポリシリコン膜で形成した薄膜トランジスタでは、例えばNチャンネルMISトランジスタを作成する場合に、電界効果移動度が約 $100\text{ cm}^2/\text{V}\cdot\text{s}$ 程度以下でかつ、閾値電圧のバラツキも大きい。このような周知の知見と比較しても、本実施例の優れた効果の一端を知ることができる。

#### 【0065】

##### [第3実施例]

本実施例では、レーザ光を照射して改質する対象となるシリコン膜はアモルファスシリコン膜に限定されることはない。前記の第2実施例で説明した実施形態にも示されたように、本実施例のシリコン膜はアモルファスシリコン膜から改質されたポリシリコン膜、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であることも可能である。さらに、本実施例は、該画素部のシリコン膜がスパッタ法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるようにすることもできる。さらに該画素部のシリコン膜がCVD法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるような組み合

10

20

30

40

50

せも可能なのである。前記実施例とは異なるシリコン膜に対して改質した本発明の他の実施形態を図9にしたがって以下に説明する。

#### 【0066】

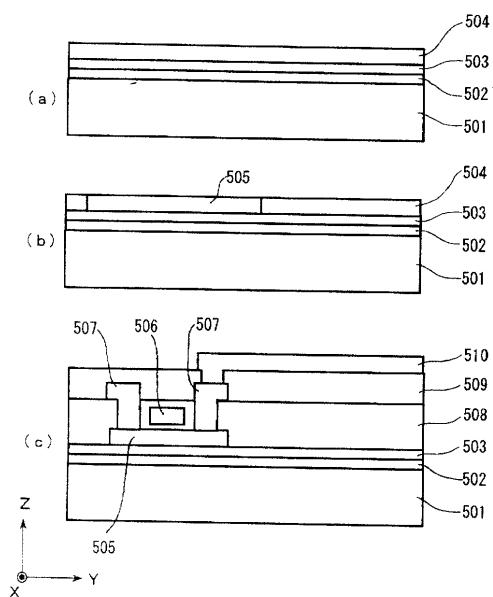

図9は本発明による表示装置の第3実施例におけるアクティブ・マトリクス基板の構成手順を模式的に示す断面図である。第1実施例と同様に、厚さが0.3mm乃至1.0mm程度で、好ましくは400°C乃至600°Cの熱処理で変形、収縮の少ない耐熱性のガラス基板501を準備する。このガラス基板501上に熱的、化学的なバリア膜として機能するおよそ50nm厚のSiN膜502および約50nm厚のSiO膜503をCVD法で連続かつ均一に堆積する。該バリア膜上にスパッタ法でシリコン膜504を50nm程度の厚さにCVD法で堆積する(図9(a)参照)。

10

#### 【0067】

その後、前記第1実施例で説明したものと同様の装置を用いたレーザ光照射法で画素部のみに照射し、画素回路を形成すべき部分のシリコン膜をレーザ光照射によりアモルファスシリコン膜504からポリシリコン膜505に改質する(図9(b)参照)。このようにして改質されたシリコン膜505を図9(c)に示すように、所定の回路になるようにエッチング処理し、ゲート絶縁膜(図示せず)、ゲート配線(ゲート電極となる)506、層間絶縁膜507、ソース/ドレイン配線508、パシベーション膜509、画素電極となる透明電極510を順次形成する。これにより、改質されたシリコン膜505を用いたトランジスタ回路を画素に配置したアクティブ・マトリクス基板が形成される。

20

#### 【0068】

かかるトランジスタ回路の形成では、ゲート部の電子もしくはホールの移動方向がシリコン膜の結晶の成長方向に並行して一致する配置とすることが望ましいことも第1実施例と同様である。

#### 【0069】

本実施例でもレーザ光照射の往復動作に基づく結晶成長方向の違いにより、画素部の薄膜トランジスタのキャリアの移動方向と結晶の成長方向に0度もしくは180度の違いが生じる。特筆すべきこに、この場合にも、かかる違いがトランジスタ特性にはほとんど影響しない。電子移動の方向と本発明のレーザ走査方向で定義する結晶成長の方向がなす角度(絶対値)と電子移動度との関係は、第1実施例で表1を用いて説明したとおりである。

30

#### 【0070】

本実施例で得られるアクティブ・マトリクス基板に有する薄膜トランジスタの性能は、第1実施例や第2実施例と同様に優れたものとなる。例えば、NチャンネルMISトランジスタを作成する場合に、電界効果移動度が約300cm<sup>2</sup>/V·s以上でかつ、閾値電圧のバラツキを±0.2V以下に抑制することができる。

#### 【0071】

本実施例によるアクティブ・マトリクス基板を用いて液晶表示装置を製造する手法は、前記第1実施例および第2実施例で説明したものと同様に周知であり、液晶表示装置に用いることでその高速表示動作が得られ、画質の均一性に優れた表示装置を安価に提供できる。

40

#### 【0072】

##### [第4実施例]

本実施例では、レーザ光を照射して改質する対象となるシリコン膜はアモルファスシリコン膜に限定されることはなく、前記実施例の実施形態で説明したように、アモルファスシリコン膜から改質されたポリシリコン膜、また画素部の改質されたシリコン膜がより改質されたポリシリコン膜であることも可能である。さらに、本実施例は、該画素部のシリコン膜がスパッタ法で形成されたポリシリコン膜、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるようにすることもできる。さらに、該画素部のシリコン膜がCVD法で形成されたポリシリコン膜であり、画素部の改質されたシリコン膜がより改質されたポリシリコン膜であるような組み合わせも可能である。

50

#### 【0073】

第1実施例と同様に、厚さが0.3mm乃至1.0mm程度で、好ましくは400°C乃至600°Cの熱処理で変形、収縮の少ない耐熱性のガラス基板を準備する。このガラス基板上に熱的、化学的なバリア膜として機能するおよそ50nm厚のSiN膜502および約50nm厚のSiO膜503をCVD法で連続かつ均一に堆積する。該バリア膜上にCVD法でポリシリコン膜を50nm程度の厚さに堆積する。

#### 【0074】

CVD法でポリシリコン膜を堆積する技術についても当該業者には周知であり、本実施例の方法を採用することで、CVD法で得られたポリシリコン膜の結晶性を大幅に改善することができる。本実施例の効果はレーザ光を照射する対象となるシリコン膜の膜質に依存することなく、照射後に安定したポリシリコン膜が得られることを示しており、これが本実施例の特徴でもある。10

#### 【0075】

本実施例によるアクティブ・マトリクス基板を用いて液晶表示装置を製造する手法は、前記第1実施例乃至第3実施例で説明したものと同様に周知であり、液晶表示装置に用いることでその高速表示動作が得られ、画質の均一性に優れた表示装置を安価に提供できる。

#### 【0076】

##### [第5実施例]

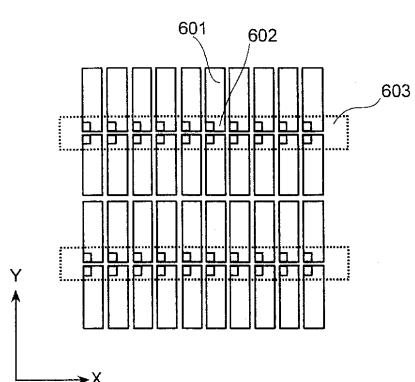

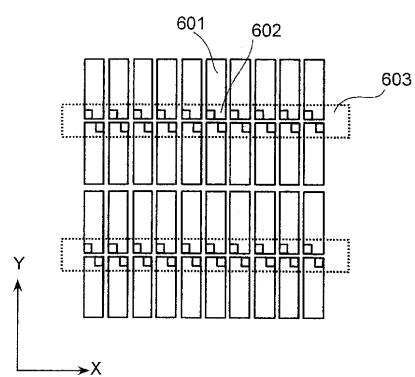

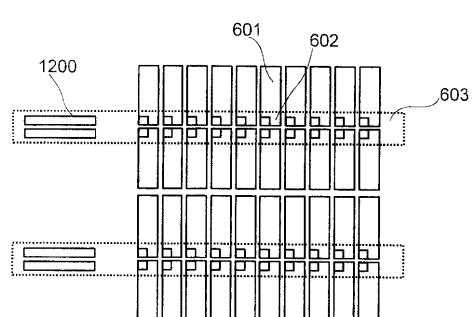

本実施例を図10、図11、図12、図13、図14および図15を参照して説明する。本実施例は、本発明の実施形態の一つとしてアクティブ・マトリクス基板上の画素回路の配置を工夫したものであり、本発明のレーザ照射の効率をさらに大幅に改善することを可能としたものである。20

#### 【0077】

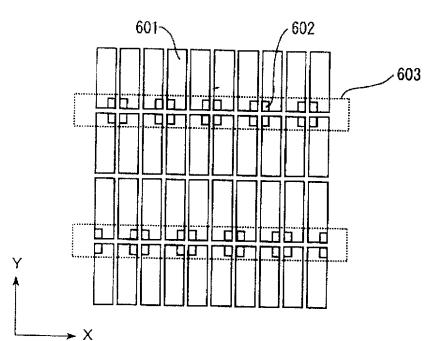

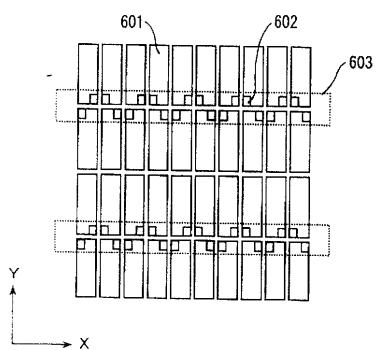

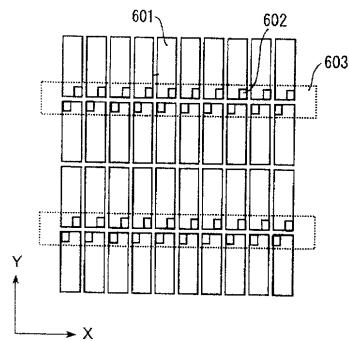

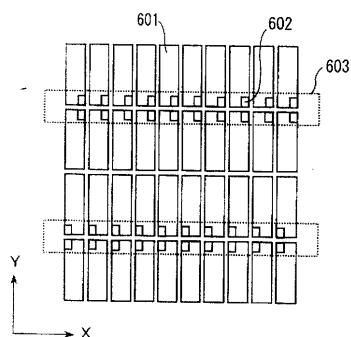

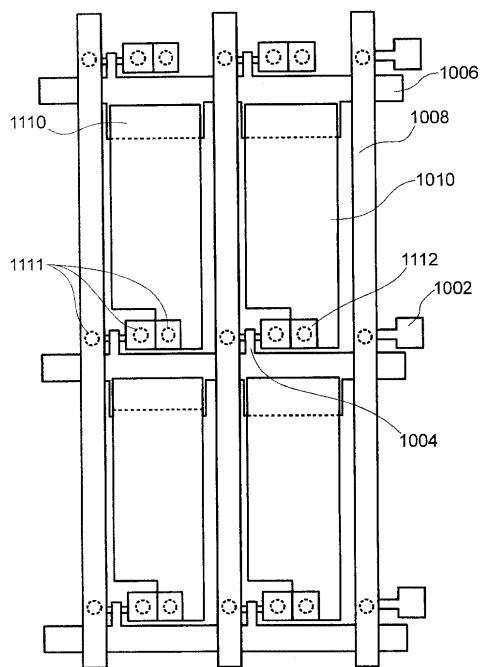

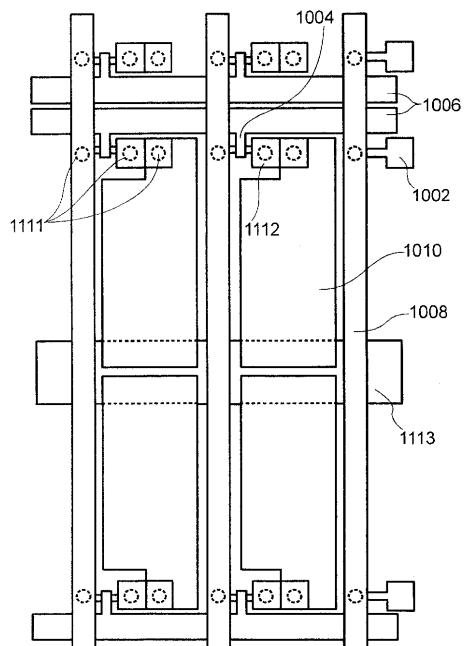

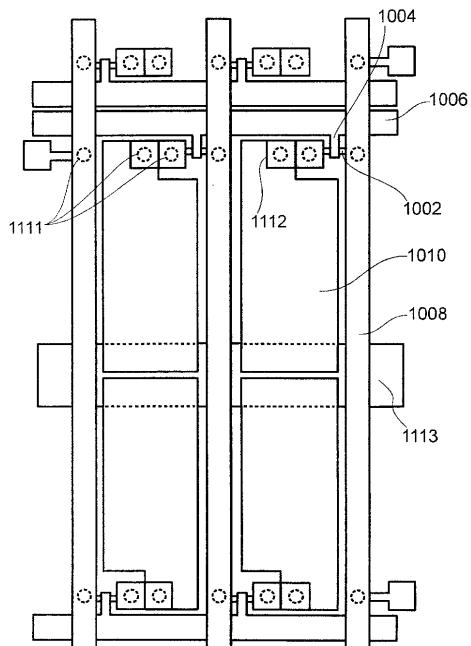

図10は本発明の第5実施例を説明するレーザ光照射部の一パターン例の平面図、図11は本発明の第5実施例を説明するレーザ光照射部の他のパターン例の平面図、図12は本発明の第5実施例を説明するレーザ光照射部の他のパターン例の平面図、図13は本発明の第5実施例を説明するレーザ光照射部の他のパターン例の平面図、図14は本発明の第5実施例を説明するレーザ光照射部のさらに他のパターン例の平面図、図15は本発明の第5実施例を説明するレーザ光照射部のさらにまた他のパターン例の平面図である。

#### 【0078】

図10、図11、図12、図13、図14および図15に示したレーザ光照射部のパターンにおいては、画素回路の配置のいずれもx方向に等間隔に配置された2列分の画素601の回路部分602からなる画素領域の列がy方向で隣接する中央部分に集約配置されている。30

#### 【0079】

そして、集約配置した画素領域のみを選択的なレーザ照射領域603として、レーザ照射の効率を約2倍にも高められたものである。これらのレーザ光照射部のパターンは画素回路の配置ピッチが画素ピッチの2倍に等しいことが特徴となる。

#### 【0080】

画素配置の方法には上記の図10、図11、図12、図13、図14および図15に示した例以外もあるが、画素回路の配置ピッチが画素ピッチの2倍に等しい配置はいずれも本実施例に含まれることは強調されるべきである。また、これらの配置のなかからどのような配置を選択するかは、形成する薄膜トランジスタのゲート側およびソース側の配線設計と画素回路のレイアウト（画素配置）、画素回路の駆動法を考慮して最適化されるべきである。40

#### 【0081】

なお、具体的なアクティブ・マトリクス基板の製造方法は第1実施例で説明した方法と同様であればよく、レーザ光照射幅を画素の集約配置に合わせて例えば約70μmを選択することで照射効率を第1実施例の場合の約2倍にも高められる。かかる配置の場合にもレーザ照射は往復走査が適用できることも強調されて良い。

#### 【0082】

次に、本実施例を具体的に液晶表示装置に適用する場合の画素部の配置（レイアウト）について図16、図17、図18、図19、図20、図21を参照して説明する。図16は本発明の第5実施例を比較説明するための従来のTN型液晶表示装置の画素部の画素配置の平面図、図17は本発明の第5実施例の一例を示すTN型液晶表示装置の画素部の画素配置の平面図、図18は本発明の第5実施例の他の例を説明するためのTN型液晶表示装置の画素部の画素配置の平面図、図19は本発明の第5実施例を比較説明するための従来のIPS型液晶表示装置の画素部の画素配置の平面図、図20は本発明の第5実施例の一例を示すIPS型液晶表示装置の画素部の画素配置の平面図、図21は本発明の第5実施例を説明する表示装置の画素部と周辺回路部を含むレーザ光照射部のパターン例の平面図である。

10

### 【0083】

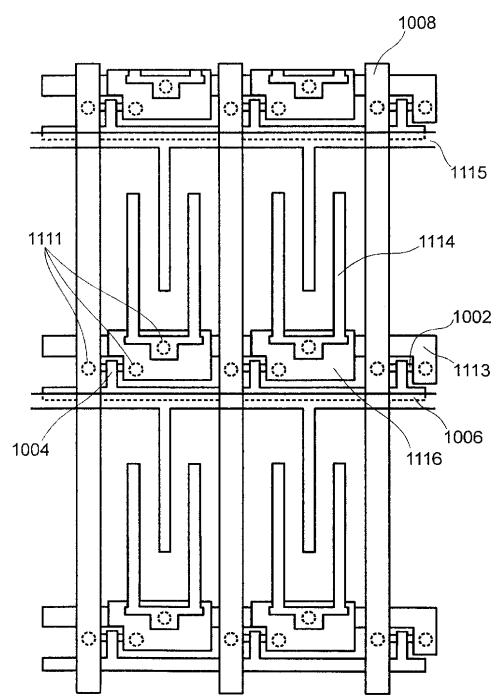

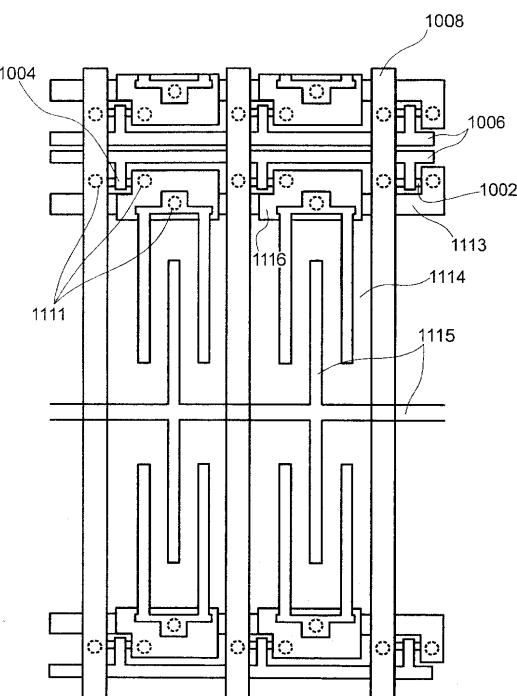

従来のTN（ツイストネマティック）型液晶表示装置の画素配置は、代表的に図16に示すようなものであり、前記した図7と等価な配置である。図16に示した画素配置では、格子状に配置したゲート配線1006とデータ配線1008の交差部にポリシリコン1002を備えたゲート1004を有する駆動トランジスタを配置しコンタクトホール1111を介して接続をとり、画素電極である透明電極1010の電圧を制御する。表示電圧を保持するためのストレージ（容量）部1110は透明電極1010と前段のゲート配線1006との重なり部に構成するのが一般的である。

### 【0084】

本発明のTN型液晶ディスプレイの画素配置は代表的に図17に示すようなものであり、図16と等価な配置である。すなわち、等間隔のデータ配線1008に対し、2画素分のゲート配線1006を集約して配置することで集約した薄膜トランジスタの配置を実現することが可能である。ただし、図16に示した従来の画素配置のように、前段のゲート配線の一部を利用してストレージ部を構成するのはできない。そのため、別途、ストレージ配線1113を設け、透明電極1010との重なり部にストレージ部を構成する必要がある。かかる画素配置を用いた場合には、露光マスクのレイアウトを変更するだけで、開口率も低下することなく、従来の製造工程と同様の工程数でTN型の液晶表示装置製造することができる。

20

### 【0085】

本発明の他のTN型液晶ディスプレイの代表的な画素配置を図18に示す。この画素配置は前記図15に示したものと等価な配置である。かかる画素配置においても、露光マスクのレイアウトを変更するだけで、開口率も低下することなく、従来の製造工程と同様の工程数でTN型液晶表示装置を製造することができる。

30

### 【0086】

さらに、従来のインプレーンスイッチング（IPS）型液晶表示装置の画素配置は代表的に図19に示すようなものである。これは図7と等価な画素配置である。図19に示した画素配置では、格子状に配置したゲート配線1006とデータ配線1008の交差部にポリシリコン1002を備えたゲート1004を有する薄膜トランジスタを配置し、画素電極1114をコンタクトホール1111を介して薄膜トランジスタのソース電極と接続をとりコモン電極（対向電極）115と画素電極1114の間の電圧を制御する。この電圧を保持するためのストレージ（容量）はゲート配線1006と並行して配置したストレージ配線113にストレージ電極1115設けて構成するのが一般的である。

40

### 【0087】

本発明のIPS型液晶表示装置の画素配置は代表的に図20に示すようなものであり、図10と等価な画素配置である。等間隔のデータ配線1008に対し、2画素分のゲート配線1006を集約して配置することで集約した薄膜トランジスタの配置を実現することができる。この場合にも、ゲート配線1006と並行してストレージ配線1113を設け、ストレージ部を構成する必要がある。かかる画素配置を用いた場合にも、露光マスクのレイアウトを変更するだけで、開口率も低下することなく、従来の製造工程と同様の工程数でIPS型液晶表示装置を製造することができる。

50

**【 0 0 8 8 】**

上記の実施例に示したように、本発明を用いて容易に液晶表示装置を製造することができる。また、同様にして有機 E L 表示装置も製造できる。

**【 0 0 8 9 】**

さらに、上記の実施例では、全てシングルゲートの薄膜トランジスタを用いた例を示したが、本発明はこれに限定されることは言うまでもない。すなわち、所謂ダブルゲートの薄膜トランジスタを用いた場合にも全く同様の画素配置で表示装置を製造することができる。かかる場合には薄膜トランジスタ部分の面積はわずかに増加する反面、オフリーグ電流の抑制や耐圧の向上効果などの利点が大きいために製造歩留まりを向上することが可能であり、実際の製品に採用することはより好ましい。

10

**【 0 0 9 0 】**

なお、本発明による画素配置では、画素領域の周辺に設ける周辺回路部（駆動回路部）のゲート駆動回路の配置も画素部の薄膜トランジスタの配置ピッチと同等として画素部と周辺回路部を本発明の方法で同時に作り込むことができる。すなわち、図 2 1 に示すように、画素 6 0 1 を形成する画素部のレーザ照射領域 6 0 3 を周辺回路部であるゲート駆動回路部 1 2 0 0 にまで延長し、該延長領域内に周辺回路を作り込むことでアクティブ・マトリクス基板の生産性を大幅に向かうことができる。このレーザ照射領域 6 0 3 の延長領域にゲート駆動回路 1 2 0 0 を配置する場合には、本発明の改質されたシリコン膜で作り込んだ薄膜トランジスタを利用して電圧変換、インピーダンス変換、シフトレジスタ、各種スイッチ、保護回路などを含むゲート駆動回路部 1 2 0 0 が実現できる。かかる配置の場合には、画素回路部の配置ピッチと周辺回路部の配置ピッチが等しくなるのが本発明の大きな特徴である。

20

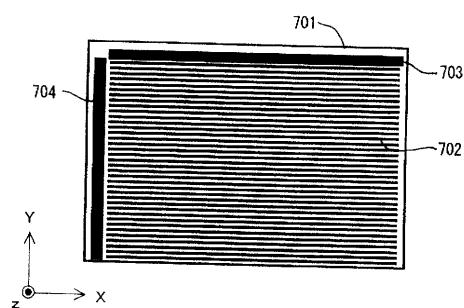

**【 0 0 9 1 】****[ 第 6 実施例 ]**

本実施例のレーザ光の照射は、アクティブ・マトリクス基板上の画素部にレーザ光を照射し、画素回路を形成すべき部分のシリコン膜をレーザ光照射により良質なポリシリコン膜に改質するのと同じ方法で画素部の周辺に配置した周辺回路部のシリコン膜をも改質し、周辺回路を画素部と同様の薄膜トランジスタで形成するようにしたものである。

**【 0 0 9 2 】**

図 2 2 は本発明の第 6 実施例を説明するアクティブ・マトリクス基板の平面図である。本実施例は第 1 実施例と同様にガラス基板上に堆積したアモルファスシリコン膜 7 0 1 の画素部のみに x 方向に沿ってストライプ状にレーザ光を照射してポリシリコン膜 7 0 2 に改質した領域を形成する。さらに、画素部の周辺に配置した周辺回路部 7 0 3 と 7 0 4 にも第 1 実施例で説明した方法でレーザ光を照射した領域を形成するものである。図 2 2 では、周辺回路部 7 0 3 の領域はソース側の周辺回路部、周辺回路部 7 0 4 はゲート側の周辺回路部としている。

30

**【 0 0 9 3 】**

その後に第 1 実施例と同様の方法で画素回路と同時に周辺回路に薄膜トランジスタを形成する。本実施例によれば、表示装置の駆動に必要な駆動用集積回路（ドライバ I C : L S I ）を大幅に低減することができる。大形表示装置（大形パネル）として代表的な S X G A パネル（1 2 8 0 × 1 0 2 4 ）を例にすれば、市販パネルのドライバ I C 数が約 1 4 ケであるのに対し、本発明を用いた場合には I C 数を少くとも 2 ケ以下、好ましくは 0 ケにも低減できるのである。そして、本実施例により液晶表示装置を製造すると、ドライバ I C の低減に加え当該 I C の実装にともなう製造プロセスの負担も低減できるので、良質かつ安価な液晶ディスプレイを提供することができる。このような実施形態が可能になるのは、本実施例で得られたアクティブ・マトリクス基板の性能が周辺回路の駆動に必要な高い性能を満たしている結果である。

40

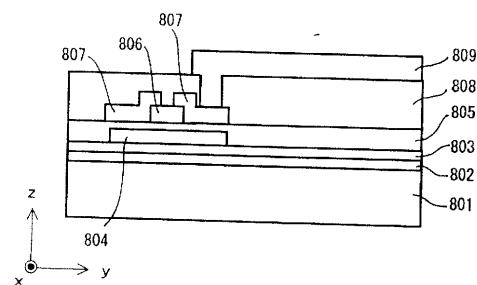

**【 0 0 9 4 】****[ 第 7 実施例 ]**

本実施例は、改質されたシリコン膜から形成される回路が一般的なトップゲート型薄膜ト

50

ランジスタ回路に限定されることなく、ボトムゲート型薄膜トランジスタ回路とすることも可能としたものである。NチャンネルMISもしくはPチャンネルMISのみの単チャンネル回路を必要とする場合には製造工程の簡略化からボトムゲート型がむしろ好ましい場合もある。本実施例について、本発明をボトムゲート型薄膜トランジスタ回路に適用する場合の実施態様を図23に従って以下に説明する。

#### 【0095】

図23は本発明の第7実施例のアクティブ・マトリクス基板に有する薄膜トランジスタの構造を模式的に説明する断面図である。図23において、ガラス基板801上にバリア膜として機能するSiN膜802およびSiO膜803をCVD等の手段により薄く堆積する。その上にゲート電極804を所定の形状に形成する。そして、ゲート電極804を被服するようにゲート絶縁膜805を形成する。次いで、アモルファスシリコン膜を100nm程度の厚さにCVD法で堆積する。このアモルファスシリコン膜の成膜ではN型のMISトランジスタを構成するためにシランガスと共に所定量のフォスフィンを共存することでN型のアモルファスシリコン膜を堆積するとよい。

#### 【0096】

その後、前記したレーザ光照射法でゲート電極806上のみにレーザ光を照射し、画素回路を形成すべき部分をポリシリコン膜に改質する。次いでシリコン膜上にフォスフィン量を増加したCVD法でN+層を20nm程度の厚さに堆積し、積層膜を形成する。これのように形成した積層膜を所定位置で所定形状になるようにドライエッチングし、アイランド806を形成する。形成したアイランド806にソース/ドレイン配線807を形成し、ソースとドレイン配線部以外に露出したN+層をドライエッチングで除去する。

#### 【0097】

次に、パシベーション膜808、透明電極809を順次形成することでアモルファスシリコンからポリシリコンに改質されたシリコン膜を用いたトランジスタ回路を画素に配置したアクティブ・マトリクス基板が製作される。このような回路形成、電極形成にかかる加工技術の概要は当該業者には周知である。また、製造工程の途中に活性化アニール等の工程の追加が必要であることも周知である。

#### 【0098】

上記した製造工程ではCVDによる成膜の際に不純物キャリアをドープできるので、高価、かつ煩雑なイオン打ち込みを省略することができ、極めて経済的である。さらに、P型のキャリアとなるようにボランガスを用いたドープによりP型のMISを製造することもできる。したがって、ボトムゲート型の採用は単チャンネル型の半導体装置を経済的に提供するのに優れた方法となる。

#### 【0099】

本実施例のように、本発明によりボトムゲート型薄膜トランジスタを製造する場合にはゲート配線上で、絶縁膜を介してシリコン膜にレーザ光を照射するので、ゲート配線材料には高融点金属を採用することが好ましい。したがって、本実施例の特徴の一つは、ゲート配線材料としてタンクステン(W)もしくはモリブデン(Mo)を主成分とする配線材料を使用する点にある。

#### 【0100】

##### [第8実施例]

図24は本発明の製造方法を実現するためのレーザ光照射設備のより改良された構成例の説明図である。本発明では画素部のシリコン膜に選択的にレーザビームを照射し、該画素部の改質されたシリコン膜に画素回路を形成するのでレーザビームを複数化して並列動作で照射することが生産性を向上する要因となる。このようなレーザ光照射の並列化には前記図3に示したようなレーザ照射装置の複数台を並列配置するのが有効である。しかし、以下に述べるように1台のレーザ光源から発振したビームを複数に分割して並列化することも極めて有効な方法である。ちなみに、レーザ光照射装置の並列設置ではその台数をmとすると照射時間は1台のときに比較しおよそ $1/m$ に短縮できる。

#### 【0101】

10

20

30

40

50

レーザ光の複数分割は、図24に示すように、レーザ光源901から発振したレーザビーム902をホモジナイザ等の光学系903の内部で分割する。分割したレーザビームを光ファイバ904等の複数の導光路を通して複数の集光レンズ系905に導入して複数の照射ビーム906とするのが有効である。かかるビーム分割、導光路の作成技術自体は光学技術の範囲内であるが、本発明にかかる技術を利用するとシリコン膜の改質に要する時間が驚くほど短縮できることは強調されるべきである。レーザ光の分割数をnとすると、照射時間は1台のときに比較し、およそ $1/n$ に短縮できる。さらに、レーザビーム分割と並列設置を併用すると照射時間はおよそ $1/n^m$ にも短縮でき、この種のアクティブ・マトリクス基板の生産性を飛躍的に向上でき、またこのようなアクティブ・マトリクス基板に限らず、各種の半導体装置の製造に適用すればその生産性を格段に向上することができる。10

#### 【0102】

図25は本発明による表示装置を用いた電子機器一例を示す外観図である。この電子機器はテレビ受像機であり、その表示部に前記実施例の何れかの構成を有するパネルPNLを実装し、スタンド部で直立させている。パネルPNLは液晶表示装置でも、あるいは有機EL表示装置、もしくは他のアクティブ・マトリクス型の表示装置である。なお、スタンド部は着脱可能とすることもできる。

#### 【0103】

なお、本発明は特許請求の範囲に記載の構成および実施例に記載の構成に限定されるものではなく、本発明の技術思想を逸脱することなく種々の変形が可能であることは言うまでもない。20

#### 【0104】

##### 【発明の効果】

以上説明したように、本発明は画素部のシリコン膜に選択的にかつ効率的にレーザビームを照射してシリコン膜を改質し、改質されたシリコン膜に画素回路を形成してアクティブ・マトリクス基板を得、これを用いて表示装置を構成するものであるため、著しく高性能の表示装置を安価に提供でき、その技術的、経済的効果を大幅に高めることができる。

##### 【画面の簡単な説明】

【図1】本発明による表示装置の第1実施例におけるアクティブ・マトリクス基板の構成手順を模式的に示す断面図である。30

【図2】本発明による表示装置の第1実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射パターンを模式的に説明する平面図である。

【図3】本発明による表示装置の第1実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射装置の模式的構造図である。

【図4】本発明による表示装置の第1実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射作業の手順を説明するフローチャートである。

【図5】本発明による表示装置の第1実施例におけるアクティブ・マトリクス基板のシリコン膜を改質するためのレーザ光照射の立体的な説明図である。

##### 【図6】本発明のレーザ光の照射部と薄膜トランジスタの構成を模式的説明図である。

【図7】本発明のアクティブマトリクス基板の画素部とレーザ光照射領域の関係を説明する平面図である。40

【図8】本発明の第1実施例におけるアクティブマトリクス基板の画素部とレーザ光照射領域の関係を説明する平面図である。

【図9】本発明による表示装置の第3実施例におけるアクティブ・マトリクス基板の構成手順を模式的に示す断面図である。

【図10】本発明の第5実施例を説明するレーザ光照射部の一パターン例の平面図である。

【図11】本発明の第5実施例を説明するレーザ光照射部の他のパターン例の平面図である。

##### 【図12】本発明の第5実施例を説明するレーザ光照射部の他のパターン例の平面図である。50

る。

【図13】本発明の第5実施例を説明するレーザ光照射部の他のパターン例の平面図である。

【図14】本発明の第5実施例を説明するレーザ光照射部のさらに他のパターン例の平面図である。

【図15】本発明の第5実施例を説明するレーザ光照射部のさらにまた他のパターン例の平面図である。

【図16】本発明の第5実施例に比較する、従来のTN液晶の画素部のレイアウトを説明する平面図である。

【図17】本発明の第5実施例の一例を示す、本発明のTN液晶の画素部のレイアウトを説明する平面図である。 10

【図18】本発明の第5実施例の他の例を示す、本発明のTN液晶の画素部のレイアウトを説明する平面図である。

【図19】本発明の第5実施例に比較する、従来のIPS液晶の画素部のレイアウトを説明する平面図である。

【図20】本発明の第5実施例の一例を示す、本発明のIPS液晶の画素部のレイアウトを説明する平面図である。

【図21】本発明の第5実施例を説明する、画素部と周辺回路部を含むレーザ光照射部のパターン例の平面図である。

【図22】本発明の第6実施例を説明するアクティブ・マトリクス基板の平面図である。 20

【図23】本発明の第7実施例のアクティブ・マトリクス基板に有する薄膜トランジスタの構造を模式的に説明する断面図である。

【図24】本発明の製造方法を実現するためのレーザ光照射設備のより改良された構成例の説明図である。

【図25】本発明による表示装置を用いた電子機器一例を示す外観図である。

【図26】一般的なエキシマパルスレーザ光照射を走査することによる結晶化方法の説明図である。

【図27】図26におけるレーザ光照射部の部分平面図と薄膜トランジスタ部の構成例を説明する要部平面図である。

【符号の説明】 30

101・・・ガラス基板、102・・・SiN膜 103・・・SiO膜、104・・・アモルファスシリコン膜 105・・・ポリシリコン膜、106・・・ゲート電極、10

7・・・層間絶縁膜、108・・・ソース／ドレイン配線、109・・・パシベーション膜、110・・・透明電極、201・・・駆動ステージ、202・・・基準位置測定用カメラ、203・・・基準位置測定信号、204・・・制御装置、205・・・駆動設備、206・・・制御信号、207・・・照射設備、208・・・レーザ光、209・・・レ

ーザ光源、210・・・光学系、211・・・反射ミラー、212・・・集光レンズ系、213・・・ON-OFF信号、214・・・制御信号、301・・・ガラス基板、30

2・・・アモルファスシリコン膜、303・・・エキシマレーザビーム、304・・・改質されたシリコン膜、401・・・画素、402・・・画素回路部、403・・・レーザ照射部、501・・・ガラス基板、502・・・SiN膜、503・・・SiO膜、50

4・・・シリコン膜、505・・・ポリシリコン膜、506・・・ゲート配線、507・・・層間絶縁膜、508・・・ソース／ドレイン配線、509・・・パシベーション膜、510・・・透明電極、601・・・画素、602・・・画素回路部分、603・・・レ

ーザ照射領域、701・・・アモルファスシリコン膜、702・・・ポリシリコン領域、703・・・ソース側の周辺回路部、704・・・ゲート側の周辺回路部、801・・・ガラス基板、802・・・SiN膜、803・・・SiO膜、804・・・ゲート電極、805・・・ゲート絶縁膜、806・・・アイランド、807・・・ソース／ドレイン配線、808・・・パシベーション膜、809・・・透明電極、901・・・レーザ光源、902・・・ビーム、903・・・光学系、904・・・光ファイバ、905・・・集光

40

50

レンズ系、906…照射ビーム、1002…ポリシリコン、1004…ゲート、1006…ゲート配線、1008…データ配線、1010…透明電極、1110…ストレージ(容量)部、1111…コントラクトホール、1112…コントラクト領域、1113…ストレージ配線、1114…画素電極、1115…コモン電極(対向電極)、1200…ゲート駆動回路部。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図23】

図23

【図22】

図22

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

図27

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 01 L 29/78 612B

(72)発明者 大倉 理

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

F ターム(参考) 2H092 GA59 JA25 JA26 JA28 JA37 JA41 JB41 JB61 KA04 KA18

MA05 MA07 MA12 MA27 MA30 MA37 NA21 NA27 QA07 QA09

5F052 AA02 BA11 BB01 BB02 BB04 BB07 DA01 DA02 DB01 DB07

FA19 JA02 JA04

5F110 AA30 BB02 BB04 CC02 CC07 DD02 DD13 DD14 DD17 EE04

EE28 GG02 GG13 GG25 GG32 GG43 GG44 HJ23 NN02 NN72

NN77 PP03 PP04 PP05 PP06 PP24