(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5419525号

(P5419525)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

(51) Int.Cl.

F 1

**H01L 21/3205 (2006.01)**

**H01L 21/768 (2006.01)**

**H01L 23/522 (2006.01)**

**H01L 21/329 (2006.01)**

**H01L 29/866 (2006.01)**

H01L 21/88

H01L 29/90J

D

請求項の数 10 (全 18 頁)

(21) 出願番号

特願2009-92014 (P2009-92014)

(22) 出願日

平成21年4月6日(2009.4.6)

(65) 公開番号

特開2010-245263 (P2010-245263A)

(43) 公開日

平成22年10月28日(2010.10.28)

審査請求日

平成24年2月15日(2012.2.15)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 村山 啓

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 安田 雅彦

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板に形成された素子と、

前記半導体基板を貫通して形成されたスルーホールと、

前記半導体基板の両面側及び前記スルーホールの内面に形成された絶縁層と、

前記スルーホール内に形成された銅からなる貫通電極と、

前記絶縁層に形成され、前記素子の接続部に到達するコンタクトホールと、

前記半導体基板の両面側において、前記素子が形成された領域を除く領域に形成され、

前記貫通電極を被覆して前記貫通電極からの銅の拡散を防止する第1バリア金属パターン層と、

前記半導体基板の少なくとも上面側に形成され、前記第1バリア金属パターン層に接続される第1配線層と、

前記半導体基板の少なくとも上面側に形成され、前記コンタクトホールを通して前記素子の接続部に接続されて前記第1配線層と同一層からなる第2配線層とを有することを特徴とする半導体装置。

## 【請求項 2】

前記第1配線層は、前記第1バリア金属パターン層の上に形成された第2バリア金属パターン層とその上に形成された導電パターン層とから形成され、

第2配線層は、前記素子の接続部の上に形成された第2バリア金属パターン層とその上

10

20

に形成された導電パターン層とから形成されることを特徴とする請求項 1 に記載の半導体装置。

**【請求項 3】**

前記素子は、ツェナーダイオード、トランジスタ又はキャパシタであることを特徴とする請求項 1 又は 2 に記載の半導体装置。

**【請求項 4】**

前記素子は、前記半導体基板の表層部に前記半導体基板と反対導電型の不純物拡散領域が形成されて構成されるツェナーダイオードであり、前記不純物拡散領域及び前記半導体基板の下面が前記接続部となっており、

前記コンタクトホールは前記半導体基板の両面側の前記絶縁層に形成されていることを特徴とする請求項 3 に記載の半導体装置。 10

**【請求項 5】**

前記第 1 バリア金属パターン層は、チタン層、下から順にチタン層 / 室化チタン層、アルミニウム層、及びアルミニウム合金層のいずれかよりなることを特徴とする請求項 1 乃至 4 のいずれか一項に記載の半導体装置。

**【請求項 6】**

半導体基板と、前記半導体基板に形成された素子と、前記半導体基板を貫通するスルーホールと、前記半導体基板の両面側及び前記スルーホールの内面に形成されて、前記素子を被覆する絶縁層とを備えた構造体を用意する工程と、

前記スルーホール内に銅からなる貫通電極を形成する工程と、 20

前記半導体基板の両面側において、前記素子が形成された領域を除く領域に、前記貫通電極を被覆して前記貫通電極からの銅の拡散を防止する第 1 バリア金属パターン層をそれぞれ形成する工程と、

前記第 1 バリア金属パターン層を形成する工程の後に、前記絶縁層に、前記素子の接続部に到達するコンタクトホールを形成する工程と、

前記コンタクトホール内の前記素子の接続部の自然酸化膜をウェット処理によって除去する工程と、

前記半導体基板の少なくとも上面側に、前記第 1 バリア金属パターン層に接続されると共に、前記コンタクトホールを通して前記素子の接続部に接続される配線層を形成する工程とを有することを特徴とする半導体装置の製造方法。 30

**【請求項 7】**

前記配線層を形成する工程において、

前記第 1 バリア金属パターン層及び前記素子の接続部に接続される第 2 バリア金属パターン層を形成する工程と、

めっきにより、前記第 2 バリア金属パターン層の上に導電パターン層を形成する工程とを含むことを特徴とする請求項 6 に記載の半導体装置の製造方法。

**【請求項 8】**

前記素子は、ツェナーダイオード、トランジスタ又はキャパシタであることを特徴とする請求項 6 又は 7 に記載の半導体装置の製造方法。

**【請求項 9】**

前記素子は、前記半導体基板の表層部に前記半導体基板と反対導電型の不純物拡散領域が形成されて構成されるツェナーダイオードであって、前記不純物拡散領域及び前記半導体基板の下面が前記接続部となっており、

前記コンタクトホールを形成する工程において、

前記コンタクトホールは前記半導体基板の両面側の前記絶縁層に形成されることを特徴とする請求項 8 に記載の半導体装置の製造方法。

**【請求項 10】**

前記第 1 バリア金属パターン層は、チタン層、下から順にチタン層 / 室化チタン層、アルミニウム層、及びアルミニウム合金層のいずれかよりなることを特徴とする請求項 6 乃至 9 のいずれか一項に記載の半導体装置の製造方法。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置及びその製造方法に係り、さらに詳しくは、半導体基板にダイオードなどの素子と貫通電極とが形成された構造を有する半導体装置及びその製造方法に関する。

**【背景技術】****【0002】**

従来、半導体基板にダイオードなどの素子と貫通電極とが形成された構造を有する半導体装置がある。

10

**【0003】**

特許文献1には、ツェナーダイオードと貫通電極が形成されたシリコン基板の上面側に発光素子が実装され、シリコン基板の下面側の配線層がマザーボードに接続される半導体装置が開示されている。

**【0004】**

特許文献2には、薄膜トランジスタ基板において、銅配線からシリコン層への銅の拡散を防止するために、銅配線の下に窒化チタンなどのバリア導電膜を配置することが記載されている。

**【先行技術文献】****【特許文献】**

20

**【0005】**

【特許文献1】特開2008-21987号公報

【特許文献2】特開2005-68494号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

後述する関連技術の欄で説明するように、シリコン基板にツェナーダイオードと貫通電極とが形成された半導体装置を製造する場合、貫通電極の上下面が露出した状態で、ツェナーダイオードの接続部に到達するコンタクトホールが絶縁層に形成される。ツェナーダイオードの接続部には自然酸化膜が形成されており、配線層を形成する前に自然酸化膜をウェット処理によって除去する必要がある。

30

**【0007】**

しかしながら、貫通電極(銅)が露出している状態で、シリコン基板をエッティング槽に浸漬させると、エッティング槽の処理液に貫通電極から銅が拡散し、ツェナーダイオードが銅によって汚染されてしまう。このため、ツェナーダイオードの特性劣化が生じ、半導体装置の歩留り低下の要因になる。

**【0008】**

本発明は以上の課題を鑑みて創作されたものであり、半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できて歩留りよく製造できる半導体装置の製造方法及び半導体装置を提供することを目的とする。

40

**【課題を解決するための手段】****【0009】**

上記課題を解決するため、本発明は半導体装置の製造方法に係り、半導体基板と、前記半導体基板に形成された素子と、前記半導体基板を貫通するスルーホールと、前記半導体基板の両面側及び前記スルーホールの内面に形成されて、前記素子を被覆する絶縁層とを備えた構造体を用意する工程と、前記スルーホール内に銅からなる貫通電極を形成する工程と、前記半導体基板の両面側において、前記素子が形成された領域を除く領域に、前記貫通電極を被覆して前記貫通電極からの銅の拡散を防止する第1バリア金属パターン層をそれぞれ形成する工程と、前記第1バリア金属パターン層を形成する工程の後に、前記絶

50

縁層に、前記素子の接続部に到達するコンタクトホールを形成する工程と、前記コンタクトホール内の前記素子の接続部の自然酸化膜をウェット処理によって除去する工程と、前記半導体基板の少なくとも上面側に、前記第1バリア金属パターン層に接続されると共に、前記コンタクトホールを通して前記素子の接続部に接続される配線層を形成する工程とを有することを特徴とする。

#### 【0010】

本発明では、まず、半導体基板と、それに形成された素子（ツエナーダイオード、トランジスタ又はキャパシタなど）と、半導体基板を貫通するスルーホールと、半導体基板の両面側及びスルーホールの内面に形成されて、素子を被覆する絶縁層とを備えた構造体が用意される。

10

#### 【0011】

素子がツエナーダイオードの場合は、上面側又は両面側に絶縁層が形成された半導体基板に、絶縁層を介して半導体基板と反対導電型の不純物が導入されてツエナーダイオードが形成される。続いて、絶縁層及び半導体基板にスルーホールが形成された後に、スルーホールの側面を含む全体面に絶縁層が形成される。

#### 【0012】

次いで、スルーホールに貫通電極が形成された後に、半導体基板の両面側に貫通電極の上下面を被覆する第1バリア金属パターン層がそれぞれ形成される。さらに、素子の接続部に到達するコンタクトホールが絶縁層に形成された後に、コンタクトホール内の素子の接続部の自然酸化膜がウェット処理によって除去される。

20

#### 【0013】

このとき、貫通電極（銅）は第1バリア金属パターン層でキャップされて保護されているので、貫通電極から銅がエッチング槽の処理液に拡散しないので、素子が銅で汚染されるおそれがない。

#### 【0014】

その後に、第1バリア金属パターン層に接続されると共に、コンタクトホールを通して素子に接続される配線層が形成される。

#### 【0015】

これにより、所望の特性を有する素子が得られると共に、配線層は低いコンタクト抵抗で素子に接続されるので、半導体装置の製造歩留りを向上させることができる。

30

#### 【0016】

このような製造方法で製造される半導体装置では、貫通電極に接続される配線構造は、素子に接続される配線構造と異なっている。つまり、貫通電極と配線層との間にはウェット処理から貫通電極を保護するための第1バリア金属パターン層が介在しており、素子は第1バリア金属パターン層を介さないで配線層と直接接続される。

#### 【発明の効果】

#### 【0017】

以上説明したように、本発明では、製造過程において貫通電極からの銅の拡散によって素子が汚染されることを防止することができる。

#### 【図面の簡単な説明】

#### 【0018】

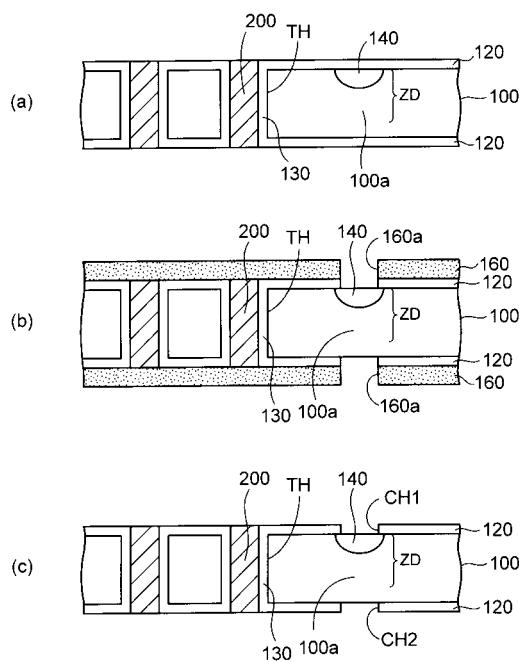

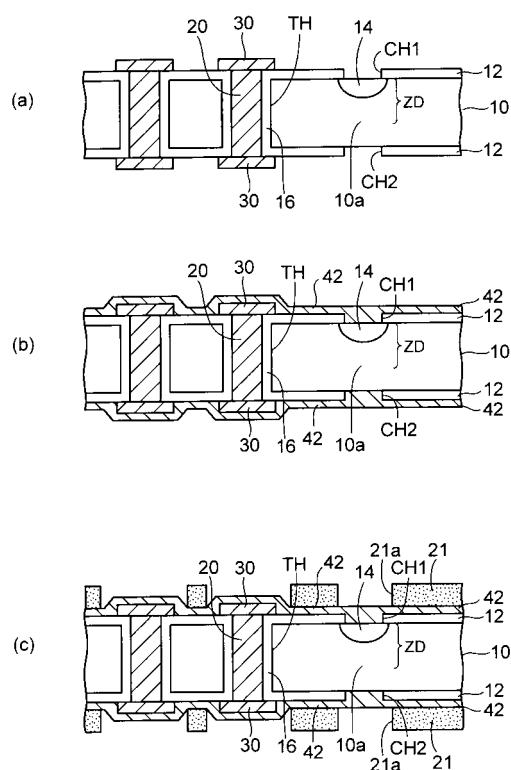

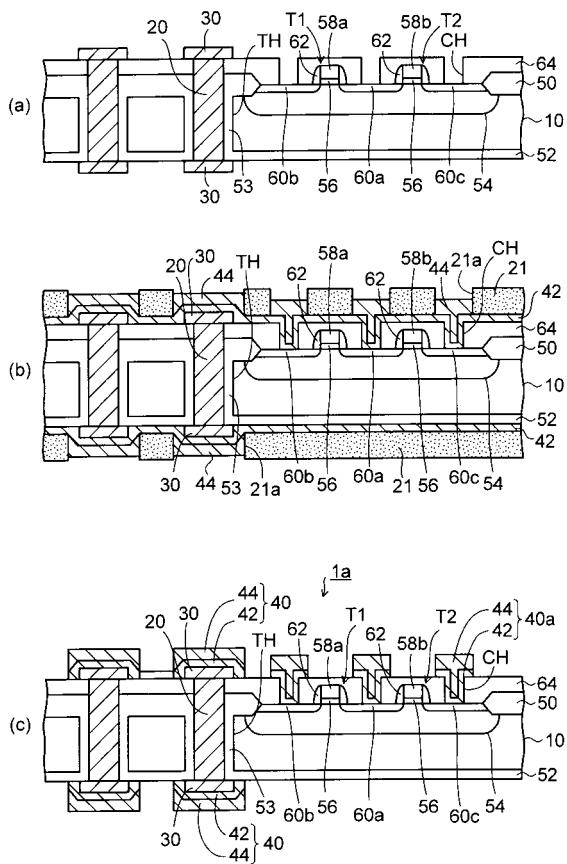

【図1】図1(a)～(c)は本発明に関連する関連技術の半導体装置の製造方法を示す断面図(その1)である。

40

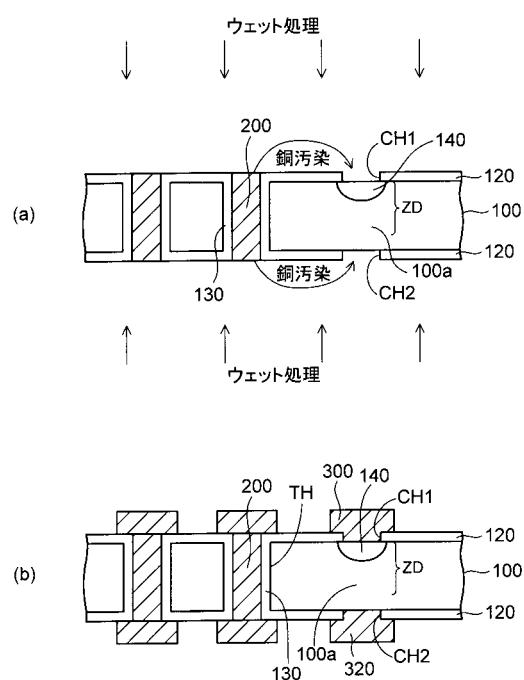

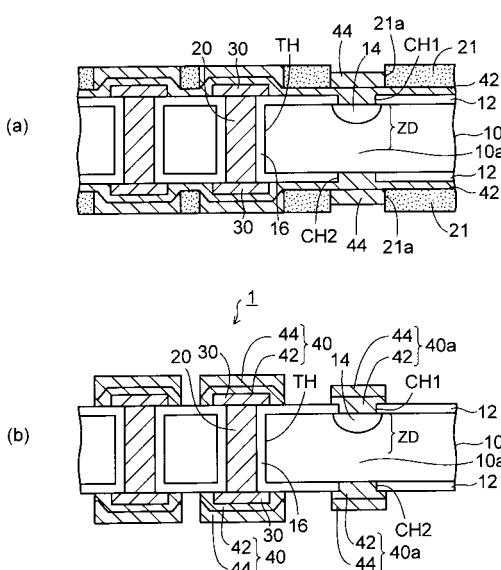

【図2】図2(a)及び(b)は本発明に関連する関連技術の半導体装置の製造方法を示す断面図(その2)である。

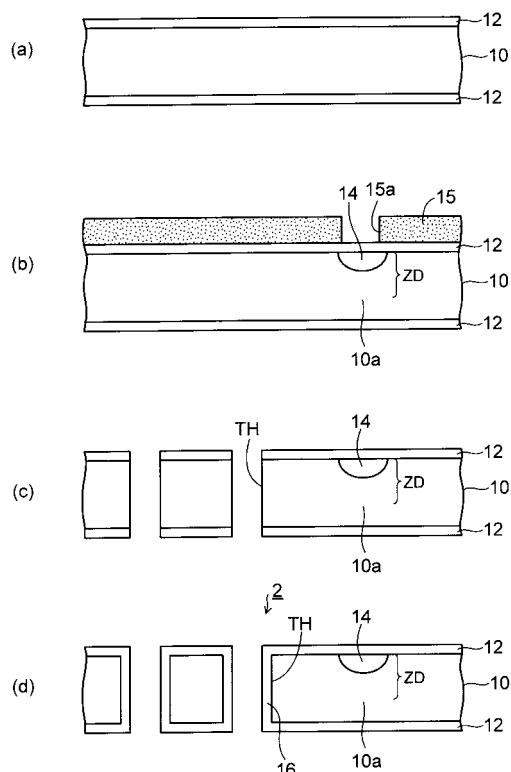

【図3】図3(a)～(d)は本発明の第1実施形態の半導体装置の製造方法を示す断面図(その1)である。

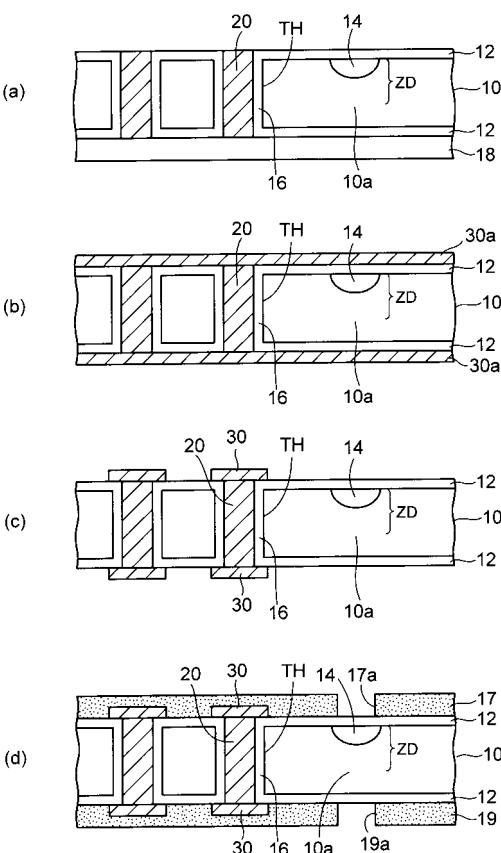

【図4】図4(a)～(d)は本発明の第1実施形態の半導体装置の製造方法を示す断面図(その2)である。

#### 【図5】図5(a)～(c)は本発明の第1実施形態の半導体装置の製造方法を示す断面

50

図(その3)である。

【図6】図6(a)及び(b)は本発明の第1実施形態の半導体装置の製造方法を示す断面図(その4)である。

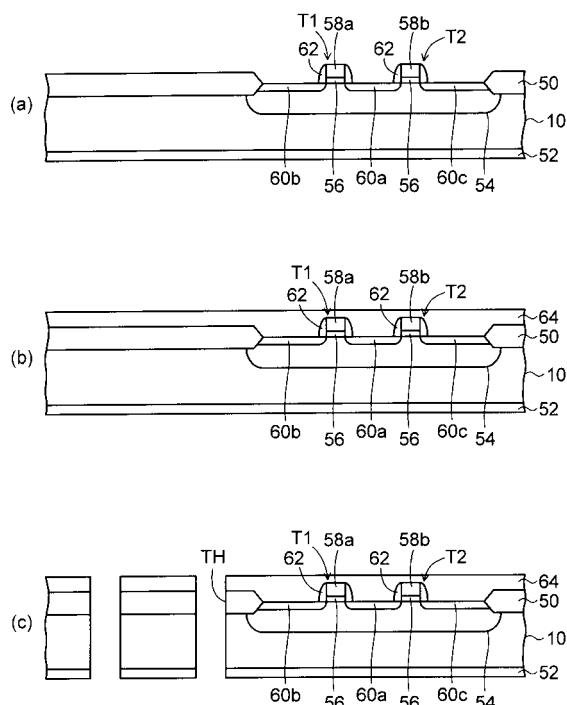

【図7】図7(a)~(c)は本発明の第2実施形態の半導体装置の製造方法を示す断面図(その1)である。

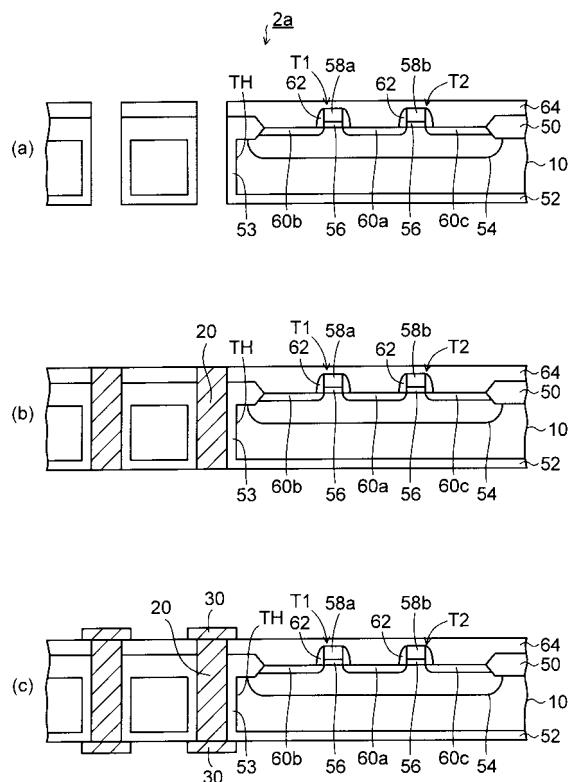

【図8】図8(a)~(c)は本発明の第2実施形態の半導体装置の製造方法を示す断面図(その2)である。

【図9】図9(a)~(c)は本発明の第2実施形態の半導体装置の製造方法を示す断面図(その3)である。

【発明を実施するための形態】

10

【0019】

以下、本発明の実施の形態について、添付の図面を参照して説明する。

【0020】

(関連技術)

本発明の実施形態を説明する前に、本発明に関連する関連技術の問題点について説明する。図1及び図2は関連技術の半導体装置の製造方法を示す断面図である。

【0021】

まず、図1(a)の断面構造を得るまでの方法について説明する。図1(a)に示すように、p型のシリコン基板100の両面側に熱酸化によって絶縁層120を形成する。さらに、レジスト(不図示)をマスクにして、絶縁層120を介してシリコン基板100にイオン注入することによりn型不純物拡散領域140を形成する。これにより、n型不純物拡散領域140とp型シリコン部100aとによってツェナーダイオードZDが構成される。

20

【0022】

次いで、両面側の絶縁層120及びシリコン基板100にその厚み方向に貫通するスルーホールTHを形成する。その後に、シリコン基板100を熱酸化することにより、スルーホールTHの側面に絶縁層130を得る。続いて、めっき法によってスルーホールTH内に銅からなる貫通電極200を充填する。

【0023】

次いで、図1(b)に示すように、シリコン基板100の両面側の絶縁層120の上に、ツェナーダイオードZDに対応する部分に開口部160aが設けられたレジスト160をそれぞれ形成する。

30

【0024】

続いて、シリコン基板100の両面側において、レジスト160をマスクにしてその開口部160aを通して絶縁層120をエッチングする。その後に、レジスト160が除去される。

【0025】

これにより、図1(c)に示すように、シリコン基板100の上面側では、ツェナーダイオードZDのn型不純物拡散領域140に到達するコンタクトホールCH1が絶縁層120に形成される。また、シリコン基板100の下面側では、ツェナーダイオードZDのp型シリコン部100aの下面に到達するコンタクトホールCH2が絶縁層120に形成される。

40

【0026】

このとき、コンタクトホールCH1, CH2内にそれぞれ露出するツェナーダイオードZDのn型不純物拡散領域140及びp型シリコン部100aの下面是、大気に曝されることで極薄の自然酸化膜(SiO<sub>2</sub>)が形成される。あるいは、レジスト160が酸素を使用するドライアッティングで除去される場合は、自然酸化膜より厚い酸化膜が形成されることがある。

【0027】

コンタクトホールCH1, CH2内のn型不純物拡散領域140及びp型シリコン部1

50

00aの下面に自然酸化膜が形成されると、ツェナーダイオードZDに接続される配線層を形成する際にコンタクト抵抗が高くなるため、ツェナーダイオードZDの特性を十分に引き出せなくなる。このため、配線層を形成する前処理としてそれらの自然酸化膜を除去する必要がある。

#### 【0028】

自然酸化膜を除去する方法としては、図2(a)に示すように、希HFなど処理液が入ったエッティング槽(不図示)にシリコン基板100を浸漬させてウェット処理(ライトエッティング)する方法が採用される。

#### 【0029】

このとき、シリコン基板100の両面側には貫通電極200(銅)の上下面が露出しているので、貫通電極200から銅がエッティング槽の処理液に拡散し、コンタクトホールCH1, CH2に露出するシリコン基板100に銅が付着する。つまり、シリコン基板100が銅によって汚染(コンタミネーション)されてしまう。

#### 【0030】

次いで、図2(b)に示すように、シリコン基板100の上面側の絶縁層120の上に、貫通電極200に接続されると共に、コンタクトホールCH1を通してツェナーダイオードZDのn型不純物拡散領域140に接続される配線層300を形成する。

#### 【0031】

また、シリコン基板100の下面側の絶縁層120の上に、貫通電極200に接続されると共に、コンタクトホールCH2を通してツェナーダイオードZDのp型シリコン部100aの下面に接続される配線層320を形成する。

#### 【0032】

n型不純物拡散領域140に接続された配線層300がマイナス(-)電極となり、p型シリコン部100aの下面に接続される配線層320がプラス(+)電極となって、ツェナーダイオードZDの整流特性が得られる。

#### 【0033】

上記したように、シリコン基板100は銅で汚染されており、銅はシリコン中を拡散しやすい特性があるため、ツェナーダイオードZDの特性が銅によって劣化し、歩留り低下の要因になる。

#### 【0034】

以下に説明する本実施形態の半導体装置の製造方法は、前述した不具合を解消することができる。

#### 【0035】

(第1の実施の形態)

図3～図6は本発明の第1実施形態の半導体装置の製造方法を示す断面図である。

#### 【0036】

第1実施形態の半導体装置の製造方法では、図3(a)に示すように、まず、p型のシリコン基板10(半導体基板)を用意し、その両面側に熱酸化によってシリコン酸化層からなる絶縁層12を形成する。CVD法によってシリコン基板10の上面側のみにシリコン酸化層などの絶縁層12を形成してもよい。

#### 【0037】

次いで、図3(b)に示すように、シリコン基板10の上面側の絶縁層12の上に、開口部15aが設けられたレジスト15をフォトリソグラフィによって形成する。さらに、レジスト15をマスクにしてその開口部15aから絶縁層12を介して、アンチモン、ヒ素又はリンなどのn型の導電型不純物をシリコン基板10にイオン注入する。

#### 【0038】

これにより、シリコン基板10の表層部にn型不純物拡散領域14が形成される。このようにして、n型不純物拡散領域14とp型シリコン部10aとによってツェナーダイオードZD(素子)が構成される。その後に、レジスト15が除去される。

#### 【0039】

10

20

30

40

50

なお、n型のシリコン基板にp型の導電型不純物をイオン注入することによりツェナーダイオードZDを構成してもよい。つまり、シリコン基板にそれと反対導電型の導電型不純物を導入すればよい。

#### 【0040】

このようにして、ツェナーダイオードZD(素子)は絶縁層12で被覆された状態でシリコン基板10に形成される。

#### 【0041】

次いで、図3(c)に示すように、シリコン基板10の上面側に、開口部が設けられたレジストなどのマスク(不図示)を形成する。さらに、マスクの開口部を通して、上面側の絶縁層12、シリコン基板10、及び下面側の絶縁層12をドライエッチングによって貫通加工する。その後に、マスクが除去される。これにより、両面側の絶縁層12及びシリコン基板10にそれらの厚み方向に貫通するスルーホールTHが形成される。

10

#### 【0042】

続いて、図3(d)に示すように、シリコン基板10を熱酸化することにより、スルーホールTHの内面にシリコン酸化層からなる絶縁層16を形成する。前述した図3(a)において、シリコン基板10の下面に絶縁層12を形成しない場合は、スルーホールTHの内面とシリコン基板10の下面に熱酸化によって絶縁層16が同時に形成される。

#### 【0043】

あるいは、CVD法によってシリコン基板10の両面側及びスルーホールTHの内面にシリコン酸化層を形成して絶縁層16を得てもよい。

20

#### 【0044】

このようにして、シリコン基板10と、それに形成されたツェナーダイオードZDと、シリコン基板10を貫通するスルーホールTHと、シリコン基板10の両面側及びスルーホールTHの内面に形成されてツェナーダイオードZDを被覆する絶縁層12,16とを備えた構造体2を得る。

#### 【0045】

次いで、図4(a)に示すように、シリコン基板10の下に銅箔などのめっき給電部材18を配置する。さらに、めっき給電部材18をめっき給電経路に利用する電解めっきによって、スルーホールTHの下部から上部にかけて銅めっきを施すことにより、貫通電極20をスルーホールTH内に充填して形成する。その後に、めっき給電部材18がシリコン基板10から取り外される。

30

#### 【0046】

スルーホールTH上に貫通電極20が突出して形成される場合は、CMPなどによって貫通電極20の上部が研磨される。これによって、貫通電極20の上面と絶縁層12の上面とが同一面となって平坦化される。

#### 【0047】

続いて、図4(b)に示すように、シリコン基板10の両面側の絶縁層12の上に、スパッタ法によりバリア金属層30aを形成する。バリア金属層30aとしては、膜厚が100nmのチタン(Ti)層が使用される。又は、Ti層の上に窒化チタン(TiN)層を形成してバリア金属層30aを構成してもよい。あるいは、アルミニウム(A1)層又はアルミニウム合金層からバリア金属層30aを形成してもよい。

40

#### 【0048】

次いで、図4(c)に示すように、シリコン基板10の両面側において、フォトリソグラフィ及びエッチングにより、バリア金属層30aをパターニングして貫通電極20の上下面に接続される第1バリア金属パターン層30をそれぞれ形成する。これにより、貫通電極20の上下面が第1バリア金属パターン層30によってそれぞれ被覆される。

#### 【0049】

第1バリア金属パターン層30は、島状の電極として貫通電極20を被覆していてよいし、あるいは配線状に貫通電極20から外側に延在していてよい。

#### 【0050】

10

20

30

40

50

第1バリア金属パターン層30は、後述するように、シリコン基板10に対してウェット処理を行う際に、貫通電極20から銅が処理液に拡散することを防止する銅拡散防止層として機能する。

#### 【0051】

次いで、図4(d)に示すように、シリコン基板10の上面側の絶縁層12の上に、ツエナーダイオードZDのn型不純物拡散領域14上に開口部17aが設けられたレジスト17を形成する。さらに、シリコン基板10の下面側の絶縁層12の上に、ツエナーダイオードZDに対応する部分に開口部19aが設けられたレジスト19を形成する。

#### 【0052】

そして、レジスト17, 19をマスクにしてこれらの開口部17a, 19aを通して、シリコン基板10の両面側の絶縁層12をエッティングする。その後に、レジスト17, 19が除去される。

#### 【0053】

これにより、図5(a)に示すように、シリコン基板10の上面側において、ツエナーダイオードZDのn型不純物拡散領域14(接続部)に到達するコンタクトホールCH1が絶縁層12に形成される。また、シリコン基板10の下面側において、ツエナーダイオードZDのp型シリコン部10aの下面(接続部)に到達するコンタクトホールCH2が形成される。

#### 【0054】

このとき、前述した関連技術と同様に、コンタクトホールCH1, CH2内に露出するツエナーダイオードZDのn型不純物拡散領域14及びp型シリコン部10aの下面是、大気に曝されることによって自然酸化膜(SiO<sub>2</sub>)が形成された状態となる。

#### 【0055】

次いで、希HFなどの処理液が入ったエッティング槽(不図示)にシリコン基板10を浸漬させることにより、コンタクトホールCH1, CH2内のn型不純物拡散領域14及びp型シリコン部10aの下面の自然酸化膜を除去する。

#### 【0056】

このとき、貫通電極20の上下面是第1バリア金属パターン層30でキャップされて保護されているので、エッティング槽の処理液に貫通電極20から銅が拡散するおそれがない。従って、コンタクトホールCH1, CH2内に露出するツエナーダイオードZDが銅で汚染されなくなるので、所望の特性を有するツエナーダイオードZDが得られる。

#### 【0057】

また、ツエナーダイオードZDの接続部の自然酸化膜が除去されるので、後述する配線層が低いコンタクト抵抗で信頼性よくツエナーダイオードZDに接続される。

#### 【0058】

次いで、図5(b)に示すように、シリコン基板10の両面側に、スパッタ法によってシード層42を形成する。シード層42としては、電解めっきのめっき給電経路として機能する他に、バリア金属層として機能する金属材料が使用される。

#### 【0059】

例えば、シード層42は、下から順に、Ti層(膜厚: 50nm) / Cu層(膜厚: 300nm)から形成される。あるいは、シード層42は、下から順に、Ti層 / TiN層、又はTi層 / TiN層 / Cu層から形成されてもよい。

#### 【0060】

続いて、図5(c)に示すように、シリコン基板10の両面側のシード層42の上に、配線層が配置される部分に開口部21aが設けられためっきレジスト21をそれぞれ形成する。

#### 【0061】

次いで、図6(a)に示すように、シリコン基板10の両面側において、シード層42をめっき給電経路に利用する電解めっきにより、めっきレジスト21の開口部21aに導電パターン層44を形成する。例えば、導電パターン層44は、下から順に、Cu層(膜

10

20

30

40

50

厚：500nm）/Ni層（膜厚：300nm）/Au層（膜厚：100nm）から構成される。

#### 【0062】

次いで、図6(b)に示すように、シリコン基板10の両面側において、めっきレジスト21を除去した後に、導電パターン層44をマスクにしてシード層42をエッチングする。これにより、シリコン基板10の両面側に、シード層42と導電パターン層44とから構成されて第1バリア金属パターン層30に接続される第1配線層40がそれぞれ形成される。

#### 【0063】

また、シリコン基板10の両面側に、シード層42と導電パターン層44とから構成されてコンタクトホールCH1, CH2を通してツェナーダイオードZDのn型不純物拡散領域14及びp型シリコン部10aに接続される第2配線層40aがそれぞれ形成される。第1、第2配線層40, 40aにおいて、シード層42は第2バリア金属パターン層として機能し、導電パターン層44は配線部として機能する。

#### 【0064】

以上により、第1実施形態の半導体装置1が得られる。

#### 【0065】

図6(b)に示すように、第1実施形態の半導体装置1では、p型のシリコン基板10の両面側に絶縁層12がそれぞれ形成されている。シリコン基板10の表層部にはn型不純物拡散領域14が形成されており、n型不純物拡散領域14とp型シリコン部10aによってツェナーダイオードZD(素子)が構成されている。

#### 【0066】

シリコン基板10にはその厚み方向に貫通するスルーホールTHが形成されており、シリコン基板10の両面側及びスルーホールTHの内面には絶縁層16が形成されている。スルーホールTH内には銅からなる貫通電極20が充填されて形成されている。

#### 【0067】

さらに、シリコン基板10の両面側には、貫通電極20の上下面を被覆する第1バリア金属パターン層30が形成されている。シリコン基板10の両面側の絶縁層12の上には、第1バリア金属パターン層30に接続される第1配線層40がそれぞれ形成されている。

#### 【0068】

また、シリコン基板10の両面側の絶縁層12には、ツェナーダイオードZDのn型不純物拡散領域14(接続部)及びp型シリコン部10aの下面(接続部)に到達するコンタクトホールCH1がそれぞれ形成されている。

#### 【0069】

そして、シリコン基板10の上面側の絶縁層12上には、コンタクトホールCH1を通してn型不純物拡散領域14に接続される第2配線層40aが形成されている。また、下面側の絶縁層12上には、コンタクトホールCH2を通してツェナーダイオードZDのp型シリコン部10aの下面に接続される第2配線層40aが形成されている。

#### 【0070】

第1、第2配線層40, 40aは、第2バリア金属パターン層として機能するシード層42とその上に形成された導電パターン層44とによってそれぞれ構成される。つまり、第1、第2配線層40, 40aは、最下に第2バリア金属パターン層(シード層42)を含んで形成される。これにより、第2配線層40aの導電パターン層44に含まれる銅がツェナーダイオードZDに拡散することが防止される。

#### 【0071】

また、シリコン基板10の両面側において、第1バリア金属パターン層30に接続される第1配線層40と、ツェナーダイオードZDに接続される第2配線層40aとは同一層から形成される。

#### 【0072】

10

20

30

40

50

前述したように、第1実施形態の半導体装置1の製造方法では、貫通電極20が第1バリア金属パターン層30で被覆された後に、絶縁層12に、ツェナーダイオードZDのn型不純物拡散領域14及びp型シリコン部10aを露出させるコンタクトホールCH1, CH2が形成される。

#### 【0073】

次いで、第1、第2配線層40, 40aを形成する前処理として、ウェット処理によってツェナーダイオードZDのn型不純物拡散領域14及びp型シリコン部10aの下面の自然酸化膜が除去される。

#### 【0074】

このとき、貫通電極20は第1バリア金属パターン層30でキャップされて保護されていることから、ウェット処理時に貫通電極30の銅がエッティング液に拡散しないので、ツェナーダイオードZDが銅で汚染されるおそれがない。その後に、貫通電極20及びツェナーダイオードZDに接続される第1、第2配線層40, 40aが同時に形成される。10

#### 【0075】

第1実施形態の半導体装置1は、そのような製造方法によって製造されるので、貫通電極20に接続される配線構造は、ツェナーダイオードZDに接続される配線構造と異なっている。

#### 【0076】

つまり、貫通電極20と第1配線層40との間にはウェット処理から貫通電極20を保護するための第1バリア金属パターン層30が介在しており、ツェナーダイオードZDは第1バリア金属パターン層30を介さずに第2配線層40aに直接接続されている。20

#### 【0077】

このように、第1実施形態の半導体装置1では、シリコン基板10に形成されたツェナーダイオードZDは製造過程において貫通電極20からの銅の汚染を受けるおそれがないので、所望の特性のツェナーダイオードZDが得られ、半導体装置が歩留りよく製造される。

#### 【0078】

第1実施形態の半導体装置1では、ツェナーダイオードZDのn型不純物拡散領域14に接続された第2配線層40aがマイナス(-)電極となり、p型シリコン部10aの下面に接続される第2配線層40aがプラス(+)電極となって、ツェナーダイオードZDの整流特性が得られる。30

#### 【0079】

そして、シリコン基板10の上面側にLEDなどの発光素子(不図示)が第1、第2配線層40, 40aに接続されて実装され、ツェナーダイオードZDは、電源ラインにおいて発光素子と電気的に並列になるように接続されて電源レギュレータとして機能する。そして、シリコン基板10の下面側の第1、第2配線層40, 40aが配線基板(マザーボード)に接続される。

#### 【0080】

なお、図6(b)の半導体装置1の例では、ツェナーダイオードZDのp型シリコン部10aの下面を接続部としているが、n型不純物拡散領域14の外側のp型シリコン部10aの上面を接続部とし、上面側の絶縁層12にp型シリコン部10aの上面に到達するコンタクトホールを形成してもよい。40

#### 【0081】

また、下面側に素子用のコンタクトホールを形成しない場合は、必ずしも下面側に配線層40, 40aを形成する必要はなく、下面側の第1バリア金属パターン層30に接続電極を設けてもよい。

#### 【0082】

また、シリコン基板10から複数の半導体装置1を得る場合は、発光素子を実装する前又は後にシリコン基板10が切断される。

#### 【0083】

50

(第2の実施の形態)

図7～図9は本発明の第2実施形態の半導体装置の製造方法を示す断面図である。第2実施形態では、ツェナーダイオードの代わりにトランジスタがシリコン基板に形成される。

【0084】

第2実施形態では、第1実施形態と同一工程についてはその詳しい説明を省略する。

【0085】

まず、図7(a)の断面構造を得るまでの方法について説明する。図7(a)に示すように、n型又はp型のシリコン基板10(半導体基板)のトランジスタ形成領域の周囲にシリコン酸化層からなる素子分離絶縁層50を形成する。素子分離絶縁層50は、シリコン窒素層(SiN)をマスクにしてシリコン基板10を選択的に酸化することにより形成される。あるいは、シリコン基板10に素子分離溝を形成し、その中に絶縁層を埋め込んでもよい。

【0086】

さらに、シリコン基板10の下面側にシリコン酸化層からなる絶縁層52を形成する。シリコン基板10の下面側の絶縁層52は素子分離絶縁層50と同時に形成してもよい。あるいは、シリコン基板10の下面側の絶縁層52は後の工程で形成してもよい。

【0087】

続いて、シリコン基板10のトランジスタ形成領域にp型不純物を導入してpウェル54を形成する。さらに、シリコン基板10のトランジスタ形成領域の表面を熱酸化して、シリコン酸化層からなるゲート絶縁膜56を形成する。

【0088】

次いで、シリコン基板10の上側全面に非晶質又は多結晶シリコン層を形成し、これをフォトリソグラフィ及びドライエッティングによりパターニングすることにより、ゲート電極58a, 58bを形成する。

【0089】

次いで、pウェル54のうちゲート電極58a, 58bの両側にn型不純物をイオン注入してソース/ドレインとなる第1～第3のn型不純物拡散領域60a, 60b, 60cを形成する。

【0090】

さらに、CVD法によりシリコン酸化層などの絶縁層をシリコン基板10の全面に形成した後に、その絶縁層をエッチバックしてゲート電極58a, 58bの両側部分に絶縁性のサイドウォールスペーサ62として残す。

【0091】

続いて、ゲート電極58a, 58bとサイドウォールスペーサ62をマスクに使用して、第1～第3のn型不純物拡散領域60a, 60b, 60cに再びn型不純物をイオン注入することにより、第1～第3のn型不純物拡散領域60a, 60b, 60cをLDD(Lightly Doped Drain)構造にする。

【0092】

以上の工程により、pウェル54には、LDD構造のn型不純物拡散領域60a, 60b, 60c、ゲート絶縁層56及びゲート電極58a, 58bを有する2つのnチャネル型のMOSトランジスタT1, T2(素子)がそれぞれ形成される。

【0093】

なお、特に図示しないが、シリコン基板10にはnウェルが形成されており、nウェル領域には、pチャネル型のMOSトランジスタ(素子)が形成される。

【0094】

次いで、図7(b)に示すように、MOSトランジスタT1, T2の上にCVD法によりシリコン酸化層を層間絶縁膜64として形成する。その後に、層間絶縁膜64の上面をCMPにより平坦化する。これにより、シリコン基板10に形成されたMOSトランジスタT1, T2が層間絶縁膜64で被覆された状態となる。

10

20

30

40

50

**【 0 0 9 5 】**

続いて、層間絶縁膜 6 4 の上に、開口部が設けられたレジストなどのマスク（不図示）を形成する。さらに、マスクの開口部を通して層間絶縁層 6 4 、素子分離絶縁層 5 0 、シリコン基板 1 0 、及びその下の絶縁層 5 2 をドライエッチングによって貫通加工する。その後に、マスクが除去される。

**【 0 0 9 6 】**

これにより、図 7 ( c ) に示すように、層間絶縁層 6 4 、素子分離絶縁層 5 0 、シリコン基板 1 0 及び絶縁層 5 2 に、それらの厚み方向に貫通するスルーホール TH が形成される。

**【 0 0 9 7 】**

さらに、図 8 ( a ) に示すように、シリコン基板 1 0 を熱酸化することにより、スルーホール TH の内面に絶縁層 5 3 を形成する。なお、熱酸化時の加熱処理が MOS トランジスタ T 1 , T 2 の特性に影響を及ぼす場合は、 CVD 法によってスルーホール TH の内面及びシリコン基板 1 0 の両面側に絶縁層 5 3 を形成してもよい。また、前述した図 7 ( a ) において、シリコン基板 1 0 の下面に絶縁層 5 2 を形成しない場合は、スルーホール TH の内面とシリコン基板 1 0 の下面に絶縁層 5 2 が同時に形成される。

**【 0 0 9 8 】**

このようにして、シリコン基板 1 0 と、それに形成された MOS トランジスタ T 1 , T 2 と、シリコン基板 1 0 を貫通するスルーホール TH と、シリコン基板 1 0 の両面側及びスルーホール TH の内面に形成されて MOS トランジスタ T 1 , T 2 を被覆する絶縁層（層間絶縁層 6 4 、絶縁層 5 2 , 5 3 ）とを備えた構造体 2 a を得る。

**【 0 0 9 9 】**

次いで、図 8 ( b ) に示すように、第 1 実施形態と同様な電解めっきにより、シリコン基板 1 0 のスルーホール TH に銅からなる貫通電極 2 0 を形成する。

**【 0 1 0 0 】**

さらに、図 8 ( c ) に示すように、第 1 実施形態の図 4 ( b ) 及び ( c ) で説明した方法により、シリコン基板 1 0 の両面側に、貫通電極 2 0 の上下面を被覆する第 1 バリア金属パターン層 3 0 をそれぞれ形成する。

**【 0 1 0 1 】**

続いて、図 9 ( a ) に示すように、フォトリソグラフィ及びドライエッチングにより層間絶縁層 6 4 をパターニングすることにより、第 1 ~ 第 3 の n 型不純物拡散領域 6 0 a , 6 0 b 、 6 0 c に到達するコンタクトホール CH をそれぞれ形成する。

**【 0 1 0 2 】**

第 2 実施形態においても、コンタクトホール CH 内に露出する第 1 ~ 第 3 の n 型不純物拡散領域 6 0 a , 6 0 b 、 6 0 c の表面に自然酸化膜が形成された状態となっている。このため、第 1 実施形態と同様なウェット処置によって、コンタクトホール CH 内の自然酸化膜を除去する。

**【 0 1 0 3 】**

このとき、第 1 実施形態と同様に、貫通電極 2 0 は第 1 バリア金属パターン層 3 0 でキヤップされて保護されているので、ウェット処理において貫通電極 2 0 の銅がコンタクトホール CH 内の第 1 ~ 第 3 の n 型不純物拡散領域 6 0 a , 6 0 b 、 6 0 c に侵入するおそれがない。従って、 MOS トランジスタ T 1 , T 2 の特性劣化が防止され、所望のトランジスタ特性が得られる。

**【 0 1 0 4 】**

また、 MOS トランジスタ T 1 , T 2 の接続部の自然酸化膜が除去されるので、後述する配線層が MOS トランジスタ T 1 , T 2 に低いコンタクト抵抗で信頼性よく接続される。

**【 0 1 0 5 】**

次いで、図 9 ( b ) に示すように、シリコン基板 1 0 の上面側において、層間絶縁層 6 4 上及びコンタクトホール CH の内面にシード層 4 2 を形成する。シリコン基板 1 0 の

10

20

30

40

50

下面側の絶縁層 5 2 及び第 1 バリア金属パターン層 3 0 の上にもシード層 4 2 が形成される。シード層 4 2 は、第 1 実施形態と同様に、バリア金属層として機能する金属材料が使用される。

#### 【 0 1 0 6 】

さらに、第 1 実施形態と同様に、シリコン基板 1 0 の両面側において、配線層が配置される部分に開口部 2 1 a が設けられためっきレジスト 2 1 をそれぞれ形成する。その後に、シリコン基板 1 0 の両面側において、シード層 4 2 をめっき給電経路に利用する電解めつきにより、めっきレジスト 2 1 の開口部 2 1 a に導電パターン層 4 4 をそれぞれ形成する。導電パターン層 4 4 はコンタクトホール CH を埋め込んで形成される。

#### 【 0 1 0 7 】

次いで、シリコン基板 1 0 の両面側において、めっきレジスト 2 1 を除去した後に、導電パターン層 4 4 をマスクにしてシード層 4 2 をエッチングする。

#### 【 0 1 0 8 】

これにより、図 9 ( c ) に示すように、シリコン基板 1 0 の上面側の層間絶縁層 6 4 の上に、第 1 バリア金属パターン層 3 0 に接続される第 1 配線層 4 0 と、コンタクトホール CH 1 を通して MOS トランジスタ T 1 , T 2 の n 型不純物拡散領域 6 0 a , 6 0 b 、 6 0 c に接続される第 2 配線層 4 0 a とが形成される。

#### 【 0 1 0 9 】

また、同時に、シリコン基板 1 0 の下面側の絶縁層 5 2 の上には、第 1 バリア金属パターン層 3 0 に接続される第 1 配線層 4 0 が形成される。

#### 【 0 1 1 0 】

以上により、第 2 実施形態の半導体装置 1 a が得られる。

#### 【 0 1 1 1 】

図 9 ( c ) に示すように、第 2 実施形態の半導体装置 1 a では、シリコン基板 1 0 の上面側にトランジスタ形成領域を取り囲むように素子分離絶縁層 5 0 が形成されている。トランジスタ形成領域には MOS トランジスタ T 1 , T 2 ( 素子 ) が形成されている。

#### 【 0 1 1 2 】

素子分離絶縁層 5 0 及び MOS トランジスタ T 1 , T 2 の上には層間絶縁層 6 4 が形成されている。また、シリコン基板 1 0 の下面側には絶縁層 5 2 が形成されている。

#### 【 0 1 1 3 】

層間絶縁層 6 4 、シリコン基板 1 0 及び絶縁層 5 2 には、それらの厚み方向に貫通するスルーホール TH が形成されている。さらに、スルーホール TH の内面には絶縁層 5 3 が形成されている。

#### 【 0 1 1 4 】

スルーホール TH 内には銅からなる貫通電極 2 0 が形成されている。さらに、シリコン基板 1 0 の両面側には、貫通電極 2 0 を被覆する第 1 バリア金属パターン層 3 0 がそれぞれ形成されている。

#### 【 0 1 1 5 】

シリコン基板 1 0 の上面側の層間絶縁層 6 4 及び下面側の絶縁層 5 2 の上には、第 1 バリア金属パターン層 3 0 に接続される第 1 配線層 4 0 がそれぞれ形成されている。

#### 【 0 1 1 6 】

また、層間絶縁層 6 4 には、MOS トランジスタ T 1 , T 2 の第 1 ~ 第 3 の n 型不純物拡散領域 6 0 a , 6 0 b 、 6 0 c に到達するコンタクトホール CH が形成されている。さらに、層間絶縁層 6 4 の上には、コンタクトホール CH を通して MOS トランジスタ T 1 , T 2 の第 1 ~ 第 3 の n 型不純物拡散領域 6 0 a , 6 0 b 、 6 0 c に接続される第 2 配線層 4 0 a が形成されている。第 2 配線層 4 0 a は第 1 配線層 4 0 と同一層から形成される。

#### 【 0 1 1 7 】

第 1 、第 2 配線層 4 0 , 4 0 a は、第 1 実施形態と同様に、第 2 バリア金属パターン層として機能するシード層 4 2 とその上に形成された導電パターン層 4 4 とによってそれぞ

れ構成されている。つまり、第1、第2配線層40, 40aは、最下に第2バリア金属パターン層を含んで形成される。これにより、第2配線層40aの導電パターン層44の銅がMOSトランジスタT1, T2に拡散することが防止される。

#### 【0118】

第2実施形態の半導体装置1aでは、第1実施形態と同様に、貫通電極20が第1バリア金属パターン層30で被覆された後に、層間絶縁層64に、MOSトランジスタT1, T2の第1～第3のn型不純物拡散領域60a, 60b, 60cを露出させるコンタクトホールCH1, CH2が形成される。

#### 【0119】

次いで、第1、第2配線層40, 40aを形成する前処理として、ウェット処理によって第1～第3のn型不純物拡散領域60a, 60b, 60cの表面の自然酸化膜が除去される。

10

#### 【0120】

このとき、貫通電極20は第1バリア金属パターン層30でキャップされて保護されているので、ウェット処理時に貫通電極20から第1～第3のn型不純物拡散領域60a, 60b, 60cに銅が侵入するおそれがない。その後に、第1バリア金属パターン層30及びMOSトランジスタT1, T2に接続される第1、第2配線層40, 40aが同時に形成される。

#### 【0121】

このように、第2実施形態の半導体装置1aでは、シリコン基板10に形成されたMOSトランジスタT1, T2は製造過程において貫通電極20からの銅の汚染を受けるおそれがないので、所望の特性のMOSトランジスタT1, T2が得られ、半導体装置が歩留りよく製造される。

20

#### 【0122】

第2実施形態の半導体装置1aでは、シリコン基板10の上面側に、加速度センサなどのMEMS素子(不図示)が第1、第2配線層40, 40aに接続されて実装される。MOSトランジスタT1, T2は、MEMS素子のドライバICとして機能する。

#### 【0123】

さらに、シリコン基板10の下面側の第1配線層40が配線基板(マザーボード)に接続されて実装される。

30

#### 【0124】

なお、シリコン基板10の下面側には必ずしも第1配線層40を形成する必要はなく、下面側の第1バリア金属パターン層30に接続電極を設けてよい。

#### 【0125】

また、シリコン基板10から複数の半導体装置1aを得る場合は、MEMS素子を実装する前又は後にシリコン基板10が切断される。

#### 【0126】

##### (その他の形態)

第1、2実施形態では、シリコン基板10に素子としてツェナーダイオードZDやMOSトランジスタT1, T2を形成する例を説明したが、シリコン基板10に絶縁層を介してキャパシタを形成してもよい。キャパシタは、上部電極と下部電極によって誘電体層が挟まれ構造を有し、薄膜プロセスによって形成される。そして、上部電極の上面と下部電極の延在部の上面とが接続部となる。

40

#### 【0127】

この場合も同様に、貫通電極20が第1バリア金属パターン層30で被覆された状態で、絶縁層にキャパシタの接続部に到達するコンタクトホールが形成される。これにより、配線層を形成する前に行われるウェット処理の際に、貫通電極20の銅がキャパシタに拡散することが防止される。特に、銅汚染によって特性が変動しやすい材料を使用するキャパシタにおいて信頼性を向上させることができる。

#### 【0128】

50

また、半導体基板としてシリコン基板 10 を例示したが、ガリウムヒ素 (G a A s) 基板などを使用して各種の半導体素子などを形成する製造方法に適用してもよい。

【符号の説明】

【0129】

1, 1 a ... 半導体装置、10 ... シリコン基板、10 a ... p型シリコン部、12, 16, 5

2, 53 ... 絶縁層、14, 60 a, 60 b, 60 c ... n型不純物拡散領域、15, 17,

19, 21 ... レジスト、15 a, 17 a, 19 a, 21 a ... 開口部、18 ... めっき給電部

材、20 ... 貫通電極、30 ... 第1バリア金属パターン層、30 a ... バリア金属層、40 ...

第1配線層、40 a ... 第2配線層、42 ... シード層（第2バリア金属パターン層）、44

... 導電パターン層、50 ... 素子分離絶縁層、54 ... pウェル、56 ... ゲート絶縁層、58

a, 58 b ... ゲート電極、62 ... サイドウォールスペーサ、64 ... 層間絶縁層、C H ...

コンタクトホール、T H ... スルーホール、T 1, T 2 ... M O Sトランジスタ、Z D ... ツェナ

ダイオード。 10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2005-294582(JP,A)

特開2006-278646(JP,A)

特開2008-021987(JP,A)

特開2004-047626(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/768

H01L 21/3205

H01L 23/52

H01L 21/28

H01L 29/45

H01L 29/861

H01L 21/329

H01L 29/78

H01L 21/336

H01L 27/04

H01L 21/822