(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7547575号

(P7547575)

(45)発行日 令和6年9月9日(2024.9.9)

(24)登録日 令和6年8月30日(2024.8.30)

|                         |               |

|-------------------------|---------------|

| (51)国際特許分類              | F I           |

| H 04 N 25/773 (2023.01) | H 04 N 25/773 |

| H 04 N 25/76 (2023.01)  | H 04 N 25/76  |

| H 04 N 25/77 (2023.01)  | H 04 N 25/77  |

| H 01 L 31/107 (2006.01) | H 01 L 31/10  |

| H 01 L 31/10 (2006.01)  | H 01 L 31/10  |

請求項の数 13 (全17頁)

|           |                               |          |                                       |

|-----------|-------------------------------|----------|---------------------------------------|

| (21)出願番号  | 特願2023-121793(P2023-121793)   | (73)特許権者 | 000001007                             |

| (22)出願日   | 令和5年7月26日(2023.7.26)          |          | キヤノン株式会社                              |

| (62)分割の表示 | 特願2019-14728(P2019-14728)の分割  |          | 東京都大田区下丸子3丁目30番2号                     |

| 原出願日      | 平成31年1月30日(2019.1.30)         | (74)代理人  | 100126240<br>弁理士 阿部 琢磨                |

| (65)公開番号  | 特開2023-155231(P2023-155231 A) | (74)代理人  | 100223941<br>弁理士 高橋 佳子                |

| (43)公開日   | 令和5年10月20日(2023.10.20)        | (74)代理人  | 100159695<br>弁理士 中辻 七朗                |

| 審査請求日     | 令和5年8月24日(2023.8.24)          | (74)代理人  | 100172476<br>弁理士 富田 一史                |

|           |                               | (74)代理人  | 100126974<br>弁理士 大朋 靖尚                |

|           |                               | (72)発明者  | 森本 和浩<br>東京都大田区下丸子3丁目30番2号キ<br>最終頁に続く |

(54)【発明の名称】 光電変換装置、撮像システム、移動体

## (57)【特許請求の範囲】

## 【請求項1】

アバランシェ増倍を行うフォトダイオードと、

前記フォトダイオードに接続され、制御信号がゲートに入力されるトランジスタと、

前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号とが入力され、

前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号との論理演算結果

に応じた信号を出力する論理回路と、

前記論理回路に接続されたカウンタと、を有し、

前記カウンタは前記論理回路から出力される前記信号のパルス数をカウントすることを特徴とする光電変換装置。

## 【請求項2】

前記制御信号は、前記カウンタのカウント値をリセットしてから次に前記カウント値をリセットするまでの期間に周期的に入力されることを特徴とする請求項1に記載の光電変換装置。

## 【請求項3】

前記フォトダイオードの出力に基づく信号は前記フォトダイオードへの光子の入射に応じて第1レベルから第2レベルへ遷移し、

前記フォトダイオードの出力に基づく信号が前記第2レベルの場合に、前記制御信号に基づく信号の第3レベルから第4レベルへの切り替えに応じて前記論理演算結果のレベルが遷移することを特徴とする請求項1または2に記載の光電変換装置。

**【請求項 4】**

アバランシェ増倍を行うフォトダイオードと、

前記フォトダイオードに接続され、制御信号がゲートに入力されるトランジスタと、

前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号とが入力され、前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号との論理演算結果に応じた信号を出力する論理回路と、

前記論理回路に接続されたカウンタと、を有し、

前記カウンタは前記論理回路から出力される前記信号のパルス数をカウントし、

前記フォトダイオードの出力に基づく信号は前記フォトダイオードへの光子の入射に応じて第1レベルから第2レベルへ遷移し、

前記フォトダイオードの出力に基づく信号が前記第2レベルの場合に、前記制御信号に基づく信号の第3レベルから第4レベルへの切り替えに応じて前記論理演算結果のレベルが遷移することを特徴とする光電変換装置。

10

**【請求項 5】**

アバランシェ増倍を行うフォトダイオードと、

前記フォトダイオードに接続され、制御信号がゲートに入力されるトランジスタと、

前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号とが入力され、前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号との論理演算結果に応じた信号を出力する論理回路と、を有し、

前記制御信号は前記フォトダイオードがアバランシェ増倍を起こしうる期間に周期的に入力されるパルス信号であることを特徴とする光電変換装置。

20

**【請求項 6】**

前記制御信号はクロック信号であることを特徴とする請求項2または5に記載の光電変換装置。

**【請求項 7】**

前記論理回路に接続されたカウンタを有し、

前記カウンタは、前記論理回路から前記論理演算結果に応じた信号のパルス数をカウントすることを特徴とする請求項5または6に記載の光電変換装置。

**【請求項 8】**

前記トランジスタは、前記制御信号に基づく信号が前記第3レベルにある場合にはオフ状態、前記制御信号に基づく信号が前記第4レベルにある場合にはオン状態であることを特徴とする請求項3または4に記載の光電変換装置。

30

**【請求項 9】**

請求項1から8までのいずれか1項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理部と

を有することを特徴とする撮像システム。

**【請求項 10】**

移動体であって、

請求項1から8までのいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号に基づいて、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と、

を有することを特徴とする移動体。

40

**【請求項 11】**

アバランシェ増倍を行うフォトダイオードを有する光電変換装置の制御方法であって、

前記フォトダイオードに接続されたトランジスタのゲートに制御信号を入力し、

前記フォトダイオードの出力に基づく信号と前記制御信号に基づく信号との論理演算結果を出力し、出力された前記論理演算結果に応じた信号のパルス数をカウントすることを特徴とする制御方法。

**【請求項 12】**

50

前記フォトダイオードの出力に基づく信号は前記フォトダイオードへの光子の入射に応じて第1レベルから第2レベルへ遷移し、

前記フォトダイオードの出力に基づく信号が前記第2レベルの場合に、前記制御信号に基づく信号の第3レベルから第4レベルへの切り替えに応じて前記論理演算結果のレベルが遷移することを特徴とする請求項1\_1に記載の制御方法。

【請求項13】

前記トランジスタは、前記制御信号に基づく信号が前記第3レベルにある場合にはオフ状態、前記制御信号に基づく信号が前記第4レベルにある場合にはオン状態であることを特徴とする請求項1\_2に記載の制御方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、光電変換装置、撮像システム、移動体に関する。

【背景技術】

【0002】

アバランシェ増倍を行う受光部に入射する光子の数をデジタル的に計数し、その計数値をデジタル信号として画素から出力するフォトンカウント型の光電変換装置が知られている。特許文献1には、周期的に繰り返されるリセットパルスの間の期間に、フォトダイオードから信号が入力される増幅器が出力するパルスを検出することによって、フォトダイオードに光子が入射したか否かを検出する装置が記載されている。この装置では、入射した結果が得られた回数を積算することによって、画素に入射した光子の数に対応した計数値を得るとしている。

20

【0003】

具体的には、特許文献1に記載の装置は、リセットパルスがリセットトランジスタに入力されるとフォトダイオードの電位がリチャージされ、次のアバランシェ増倍の待機状態となる。リセットパルスが入力されることで、計数値保持手段の入力部の電位はリセットされる。そして、再びフォトダイオードに光子が入射すると、アバランシェ増倍によって計数値保持手段の入力部の電位が変化する。この電位の変化を受けて、計数値保持手段は保持している計数値に1を加算する。このようにして、アバランシェ増倍の待機状態にある複数の期間のうち、アバランシェ増倍が生じた期間の数が計数される。

30

【先行技術文献】

【特許文献】

【0004】

【文献】特開平7-67043号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

例えば高輝度の光がフォトダイオードに入射する場合など、フォトダイオードをリチャージするタイミング、あるいはその後の近傍のタイミングに、フォトダイオードに光子が入射する場合がある。この場合、計数値保持手段の入力部の電位は光子が検出された状態が維持されて変化しない。これにより、当該期間が、光子が得られた期間としてカウントされないこととなる。よって、入射光の輝度に対応する計数値よりも実際の計数値が小さくなるため、画像の輝度が本来の輝度よりも低いものとなる。

40

【0006】

本発明は、上記の課題を鑑みて為されたものであり、アバランシェ増倍の待機状態にある複数の期間のうち、アバランシェ増倍が生じた期間の数を好適に検出する光電変換装置を提供する。

【課題を解決するための手段】

【0007】

本発明は上記の課題を鑑みて為されたものであり、一の態様は、アバランシェ増倍を行

50

うフォトダイオードと、前記フォトダイオードに接続され、制御信号がゲートに入力されるトランジスタと、前記制御信号に基づく信号と前記フォトダイオードの出力に基づく信号とが入力される論理回路と、を有し、前記論理回路は、前記フォトダイオードの出力に基づく信号と前記制御信号に基づく信号との論理演算結果を出力することを特徴とする光電変換装置である。

【発明の効果】

【0008】

本発明により、アバランシェ増倍の待機状態にある複数の期間のうち、アバランシェ増倍が生じた期間の数を好適に検出する光電変換装置を提供することができる。

【図面の簡単な説明】

【0009】

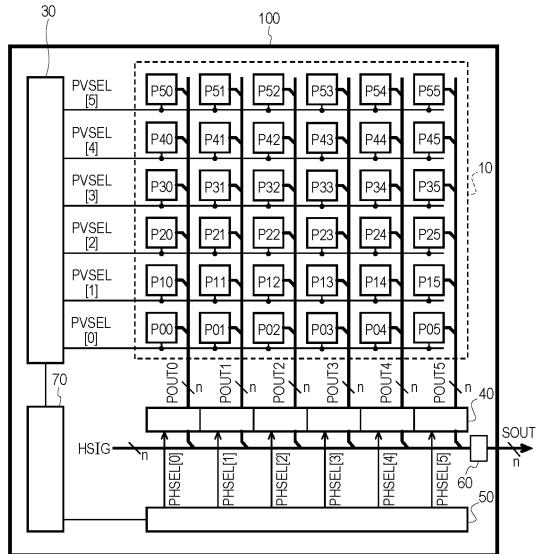

【図1】光電変換装置の概略構成を示すブロック図

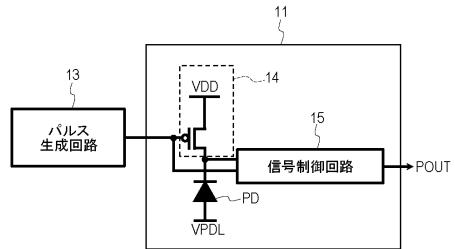

【図2】画素の概略構成を示す図

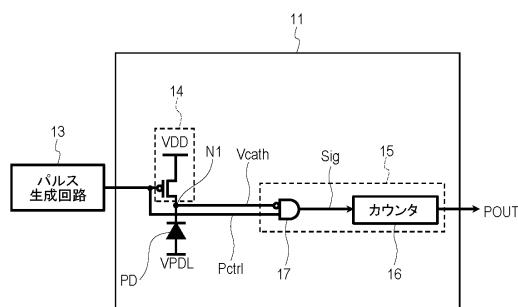

【図3】画素の構成例を示す図

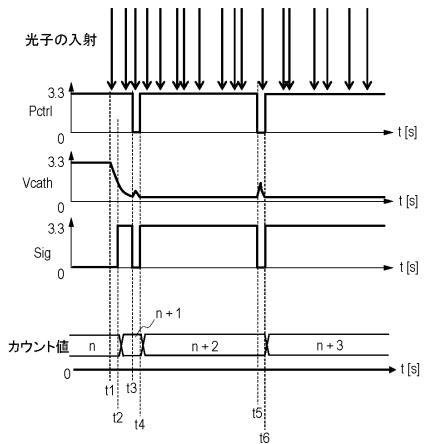

【図4】画素の動作を示すタイミング図

【図5】画素の構成例（比較例）を示す図

【図6】画素の動作（比較例）を示すタイミング図

【図7】画素の構成例を示す図

【図8】画素の構成例を示す図

【図9】画素の構成例を示す図

【図10】画素の動作を示すタイミング図

【図11】画素の構成例を示す図

【図12】撮像システムの概略構成を示すブロック図

【図13】撮像システム及び移動体の構成例を示す図

【発明を実施するための形態】

【0010】

[第1実施形態]

本発明の第1実施形態による光電変換装置及びその駆動方法について、図1乃至図3を用いて説明する。

【0011】

図1は、本実施形態による光電変換装置の概略構成を示すブロック図である。

【0012】

本実施形態による光電変換装置100は、図1に示すように、画素領域10と、垂直選択回路30と、信号処理回路40と、水平選択回路50と、出力回路60と、制御回路70と、を含む。

【0013】

画素領域10には、複数行及び列方向に渡ってマトリクス状に配された複数の画素Pが設けられている。図1には、第0行から第5行までの6行と、第0列から第5列までの6列に配された36個の画素Pを、行番号及び列番号を示す符号とともに示している。例えば、第1行、第4列に配された画素Pには、「P14」の符号を付している。

【0014】

なお、画素領域10を構成する画素アレイの行数及び列数は、特に限定されるものではない。また、画素領域10には、必ずしも画素Pが2次元状に配されている必要はない。例えば、画素領域10は1つの画素Pにより構成されていてもよいし、画素領域10に画素Pが行方向又は列方向に1次元状に配されていてもよい。

【0015】

画素領域10の画素アレイの各行には、第1の方向（図1において横方向）に延在して、制御線PVS ELが配されている。制御線PVS ELは、第1の方向に並ぶ画素Pにそれぞれ接続され、これら画素Pに共通の信号線をなしている。制御線PVS ELの延在する第1の方向は、行方向或いは水平方向と表記することがある。なお、図1には、制御線

10

20

30

40

50

P V S E L を、行番号を示す符号とともに表している。例えば、第 1 行の制御線には、「P V S E L [ 1 ]」の符号を付している。

#### 【 0 0 1 6 】

各行の制御線 P V S E L は、垂直選択回路 3 0 に接続されている。垂直選択回路 3 0 は、画素 P 内の信号生成回路（図示せず）を駆動するための制御信号を、制御線 P V S E L を介して画素 P に供給する回路部である。

#### 【 0 0 1 7 】

画素領域 1 0 の画素アレイの各列には、第 1 の方向と交差する第 2 の方向（図 1 において縦方向）に延在して、出力線 P O U T が配されている。出力線 P O U T は、第 2 の方向に並ぶ画素 P にそれぞれ接続され、これら画素 P に共通の信号線をなしている。出力線 P O U T の延在する第 2 の方向は、列方向或いは垂直方向と表記することがある。なお、図 1 には、出力線 P O U T を、列番号を示す符号とともに表している。例えば、第 4 列の出力線には、「P O U T 4」の符号を付している。出力線 P O U T の各々は、n ビットのデジタル信号を出力するための n 本の信号線を備えている。

10

#### 【 0 0 1 8 】

出力線 P O U T は、信号処理回路 4 0 に接続されている。信号処理回路 4 0 は、画素領域 1 0 の画素アレイの各列に対応してそれぞれ設けられており、対応する列の出力線 P O U T に接続されている。信号処理回路 4 0 は、対応する列の出力線 P O U T を介して画素 P から出力される信号を保持する機能を備える。画素 P から出力される信号は、出力線 P O U T の n 本の信号線を介して入力される n ビットの信号であるため、信号処理回路 4 0 の各々は各ビットの信号を保持するため少なくとも n 個の保持部を有する。

20

#### 【 0 0 1 9 】

水平選択回路 5 0 は、信号処理回路 4 0 から信号を読み出すための制御信号を信号処理回路 4 0 に供給する回路部である。水平選択回路 5 0 は、各列の信号処理回路 4 0 に、制御線 P H S E L を介して制御信号を供給する。水平選択回路 5 0 から制御信号を受信した信号処理回路 4 0 は、保持部に保持している信号を、水平出力線 H S I G を介して出力回路 6 0 へと出力する。なお、図 1 には、制御線 P H S E L を、列番号を示す符号とともに表している。例えば、第 4 列の制御線には、「P H S E L [ 4 ]」の符号を付している。水平出力線 H S I G は、n ビットのデジタル信号を出力するための n 本の信号線を備えている。

30

#### 【 0 0 2 0 】

出力回路 6 0 は、水平出力線 H S I G を介して供給された信号を、出力信号 S O U T として光電変換装置 1 0 0 の外部へ出力するための回路部である。制御回路 7 0 は、垂直選択回路 3 0 、信号処理回路 4 0 、水平選択回路 5 0 、出力回路 6 0 の動作やそのタイミングを制御する制御信号を供給するための回路部である。なお、垂直選択回路 3 0 、信号処理回路 4 0 、水平選択回路 5 0 、出力回路 6 0 の動作やそのタイミングを制御する制御信号の少なくとも一部は、光電変換装置 1 0 0 の外部から供給してもよい。

#### 【 0 0 2 1 】

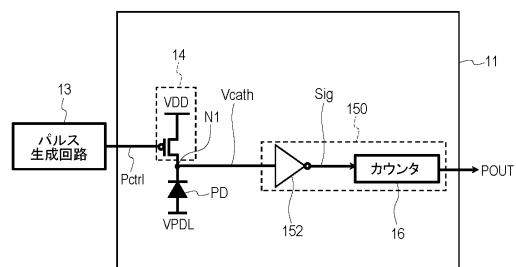

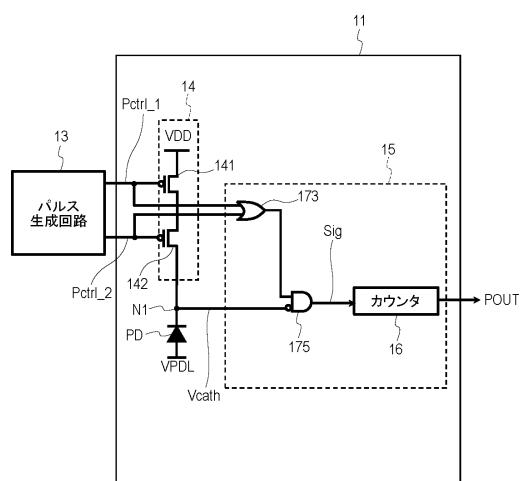

図 2 は、本実施例の光電変換装置の画素 1 1 の構成を示した図である。

#### 【 0 0 2 2 】

画素 1 1 は、フォトダイオード P D と、フォトダイオード P D に接続された、P D 制御回路 1 4（第 1 制御回路）と、信号制御回路 1 5（第 2 制御回路）を有する。フォトダイオード P D には、電圧 V P D L が与えられる。画素 1 1 の外部に設けられたパルス生成回路 1 3（生成回路）は、P D 制御回路 1 4 と、信号制御回路 1 5 に接続される。P D 制御回路 1 4 は、P M O S トランジスタを有する。この P M O S トランジスタのゲートは、パルス生成回路 1 3 に接続される。また、P M O S トランジスタのソース、ドレインの一方には電圧 V D D が与えられ、ソース、ドレインの他方にはフォトダイオード P D 、信号制御回路 1 5 が接続される。本実施例では、電圧 V D D は約 3 . 3 V であり、電圧 V P D L は約 - 2 0 V の負電圧としている。信号制御回路 1 5 は、信号 P O U T を画素 1 1 の外部に出力する。P M O S トランジスタがオンすると、フォトダイオード P D には電圧 V D D と

40

50

電圧 V P D L による逆バイアス電圧が印加される。この逆バイアス電圧を降伏電圧よりも大きい電圧としているため、フォトダイオード PD はガイガーモードのアバランシェフォトダイオードとして動作する。

#### 【 0 0 2 3 】

図 3 は、図 2 に示した画素 1 1 の信号制御回路 1 5 の詳細を示した図である。信号制御回路 1 5 は、カウンタ 1 6、AND 回路 1 7（論理回路）を有する。AND 回路 1 7 には、フォトダイオード PD と PD 制御回路 1 4 が接続されたノード N 1（第 1 ノード）の信号 V c a t h を反転させた信号が入力される。信号 V c a t h はフォトダイオード PD の出力である。AND 回路 1 7 に入力される信号 V c a t h を反転させた信号は、フォトダイオード PD の出力に対応した信号である。AND 回路 1 7 には、パルス生成回路 1 3 からの制御信号である信号 P c t r 1 が入力される。AND 回路 1 7 は、信号 V c a t h を反転させた信号と、信号 P c t r 1 の論理積である信号 S i g をカウンタ 1 6 に出力する。信号 S i g はパルス波形の信号である。

#### 【 0 0 2 4 】

カウンタ 1 6 は、AND 回路 1 7 が output する信号 S i g が Low レベルから High レベルに遷移する回数のカウントを行う。これにより、カウンタ 1 6 は、フォトダイオード PD への光子の入射に対応したカウント値を備えるカウント信号を生成する。

#### 【 0 0 2 5 】

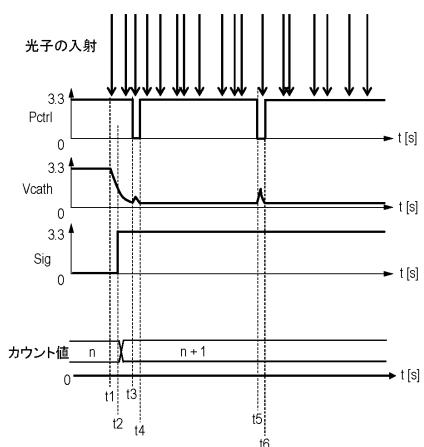

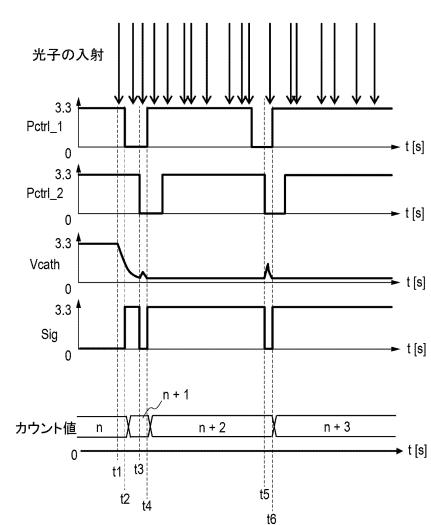

図 4 は、図 3 に示した画素 1 1 の動作を示したタイミング図である。図 4 に示した各信号は、図 3 に示した各信号に対応している。光子がフォトダイオード PD に入射するタイミングを矢印で示している。

#### 【 0 0 2 6 】

時刻 t 1 よりも前の期間、信号 P c t r 1 は High レベル (3.3 V) にある。このため、PD 制御回路 1 4 の PMOS トランジスタはオフしている。したがって、第 1 制御回路である PD 制御回路 1 4 と、フォトダイオード PD が接続されたノード N 1 はフローティングとなっている。信号 V c a t h が High レベルにある期間は、フォトダイオード PD のリチャージが完了している。信号 V c a t h が High レベルにある期間は、PD 制御回路 1 4 が、フォトダイオード PD をアバランシェ増倍可能な待機状態に制御している期間である。

#### 【 0 0 2 7 】

時刻 t 1 に、光子がフォトダイオード PD に入射する。これにより、フォトダイオード PD でアバランシェ増倍が生じ、信号 V c a t h は High レベル (3.3 V) から Low レベル (0 V) に遷移する。

#### 【 0 0 2 8 】

時刻 t 2 に、信号 V c a t h を反転させた信号は、AND 回路 1 7 の論理閾値を上回る。これにより、信号 S i g は、Low レベル (0 V) から High レベル (3.3 V) に遷移する。信号 S i g の Low レベルから High レベルへの遷移によってカウンタ 1 6 のカウント信号のカウント値が 1 LSB 分、増加する。

#### 【 0 0 2 9 】

時刻 t 3 に、パルス生成回路 1 3 は信号 P c t r 1 を Low レベルに変化させる。これにより、PD 制御回路 1 4 の PMOS トランジスタがオンし、信号 V c a t h を電圧 V D D に戻すリチャージ動作が行われる。この期間は、PD 制御回路 1 4 が、フォトダイオード PD を再びアバランシェ増倍が可能な状態に戻すリチャージ状態にある期間である。しかし、図 4 では、このリチャージ動作を行う期間に、光子がフォトダイオード PD に入射する場合を示している。このリチャージ動作中に再びアバランシェ増倍が生じる結果、信号 V c a t h は電圧 V D D には戻らず、0 V 近傍の値で推移する。

#### 【 0 0 3 0 】

また、信号 P c t r 1 が Low レベルに変化するのと同時に、AND 回路 1 7 が output する信号 S i g もまた High レベルから Low レベルに遷移する。つまり、信号制御回路 1 5 (第 2 制御回路) の入力部の電位が初期状態にリセットされる。

10

20

30

40

50

## 【0031】

時刻  $t_4$  に、パルス生成回路 13 は信号  $P_{ctrl}$  を  $High$  レベルに変化させる。これにより、PD 制御回路 14 の PMOS トランジスタがオフし、信号  $V_{cath}$  のリチャージ動作が終了する。図 4 に示した動作では、上述したように、リチャージ動作による信号  $V_{cath}$  の電圧  $V_{DD}$  への復帰が行われず、0V 近傍の値となっている。

## 【0032】

また、時刻  $t_4$  に信号  $P_{ctrl}$  が  $High$  レベルに遷移することにより、信号  $Sig$  もまた  $Low$  レベルから  $High$  レベルに遷移する。よって、信号  $Sig$  の  $Low$  レベルから  $High$  レベルへの遷移によってカウンタ 16 のカウント信号のカウント値が 1LSB 分、増加する。

10

## 【0033】

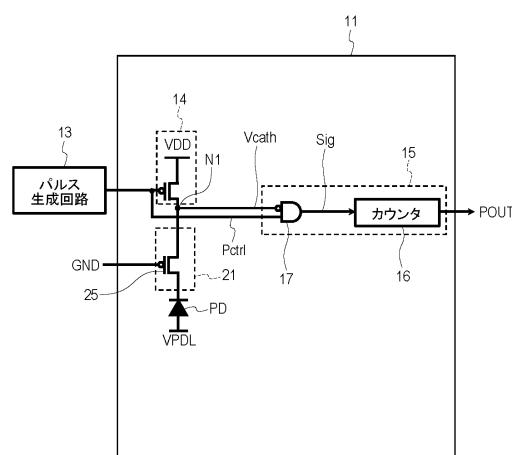

本実施形態では、パルス生成回路 13 が output する信号  $P_{ctrl}$  と信号  $V_{cath}$  を反転した信号との論理積を取る AND 回路 17 が設けられている。ここで、AND 回路 17 が設けられていない場合（比較例）を説明する。図 5 は、AND 回路 17 が設けられていない代わりに、信号  $V_{cath}$  がインバータ 152 に入力される構成を有する比較例である。インバータ 152 は、信号  $V_{cath}$  が閾値よりも電圧が低くなると  $High$  レベルに電位が変化する信号  $Sig$  をカウンタ 16 に出力する。つまり、信号  $V_{cath}$  に基づいて波形を成形し、反転した信号  $Sig$  をカウンタ 16 に出力する。

## 【0034】

図 6 は、図 5 の比較例の動作を示した図である。図 6 に示した各信号は、図 5 に対応している。光子の入射、信号  $P_{ctrl}$  の信号変化のタイミングは、図 4 と同じとしている。

20

## 【0035】

時刻  $t_2$  に信号  $Sig$  が  $High$  レベルに変化する。その後、時刻  $t_3$  に信号  $P_{ctrl}$  が  $Low$  レベルに変化する。しかし、時刻  $t_3$  から時刻  $t_4$  の間に入射する光子によってアバランシェ増倍が生じている。よって、信号  $V_{cath}$  は、リチャージ動作による信号  $V_{cath}$  の電圧  $V_{DD}$  への復帰が行われず、0V 近傍の値となっている。

## 【0036】

この結果、比較例の回路では、時刻  $t_3$  に信号  $P_{ctrl}$  が  $Low$  レベルに変化しても、時刻  $t_3$  以降、信号  $Sig$  は  $High$  レベルのまま推移する。

## 【0037】

その結果、時刻  $t_4 \sim t_5$  のアバランシェ増倍の待機期間、時刻  $t_6$  以降のアバランシェ増倍の待機期間のいずれも、アバランシェ増倍が生じた期間としてカウントされないこととなる。したがって、カウント値は、 $n + 1$  のまま推移する。

30

## 【0038】

一方、本実施形態の画素 11 は、パルス生成回路 13 の制御信号  $P_{ctrl}$  が入力される信号制御回路 15 を有する。これにより、フォトダイオード PD がアバランシェ増倍の待機状態にある期間において、アバランシェ増倍が生じたか否かを好適に検出することができる。これにより、高輝度の光が入射しているような場合においても、フォトダイオード PD がアバランシェ増倍の待機状態にある期間において、アバランシェ増倍が生じたか否かを好適に検出することができる。

40

## 【0039】

なお、本実施形態では、図 1 に示したように、1 つの半導体基板に画素 11 の構成の全てが設けられた構成として説明した。この例に限定されるものでは無く、第 1 の半導体基板にフォトダイオード PD を設け、別の第 2 の半導体基板に、信号制御回路 15 を設ける。そして、第 1 の半導体基板と第 2 の半導体基板とを積層した積層センサとしても良い。なお、パルス生成回路 13、PD 制御回路 14 は、第 1 の半導体基板、第 2 の半導体基板のいずれかに設けるようにすればよい。

## 【0040】

別の一例としては、フォトダイオード PD が第 1 の半導体基板に設けられ、パルス生成回路 13、PD 制御回路 14、信号制御回路 15 が第 2 の半導体基板に設けられる。この

50

場合には、第1ノードであるノードN1を介して、第1の半導体基板のフォトダイオードPDと、第2の半導体基板のPD制御回路14とが接続される。また、第2ノードを介して、第1の半導体基板のフォトダイオードPDと、第2の半導体基板の信号制御回路15とが接続される。

#### 【0041】

なお、本実施形態は、図3に示した構成に限定されるものでは無い。例えば、図7に示したように、フォトダイオードPDと、ノードN1との間に、レベルシフト回路21を有しても良い。レベルシフト回路21は、ゲートに接地電圧が入力されるPMOSトランジスタ25を有する。PMOSトランジスタ25は、接地電圧がゲートに入力されることにより、オン状態にある。レベルシフト回路21の出力部は、PD制御回路14、信号制御回路15に接続されている。

10

#### 【0042】

レベルシフト回路21を設けることにより、フォトダイオードPDの逆バイアス電圧を図3の構成と同じ電圧にした場合でも、信号V<sub>cat h</sub>の振幅を、図3の構成に比べて小さいものとすることができる。これにより、AND回路17の入力部の耐圧マージンの確保を行うことができる。また、アバランシェフォトダイオードには、ブレイクダウン電圧よりも大きい過剰電圧を印加することがある。この過剰電圧は、画素11ごとのブレイクダウン電圧のばらつきを考慮したうえで、全てのフォトダイオードPDが、ガイガーモードで動作できる電圧以上のバイアスをかける必要がある。また、過剰電圧はアバランシェ増倍とその後のリチャージ動作における信号V<sub>cat h</sub>の振幅に相当するため、信号制御回路15の入力電圧として論理閾値よりも振幅の大きい電圧である必要がある。レベルシフト回路21を設けることによって、電源電圧V<sub>DD</sub>を図3の構成よりも小さなものとしても、フォトダイオードPDに充分な過剰電圧を印加することができる。図7の構成では、電源電圧V<sub>DD</sub>を、AND回路17の電源電圧と同じ電圧とすることもできる。この場合には、電源電圧V<sub>DD</sub>と、AND回路17の電源電圧とを共通の電源電圧生成回路が生成することができるため、電源電圧生成回路の回路面積を低減することができる。なお、図3の構成では、電源電圧V<sub>DD</sub>と、AND回路17の電源電圧とを異ならせる場合がある。

20

#### 【0043】

なお、本実施形態では、PD制御回路14が待機状態からリチャージ状態に遷移するタイミングと、カウンタ16の入力部の電位を初期状態にリセットするタイミングとを同時としていた。本実施形態は、この例に限定されるものでは無い。例えば、PD制御回路14が待機状態からリチャージ状態に遷移するタイミングから、所定の期間遅延させて（クロックパルスの数周期分等）、カウンタ16の入力部の電位を初期状態にリセットするようにしてもよい。

30

#### 【0044】

##### 【第2実施形態】

本実施形態の光電変換装置について、第1実施形態と異なる点を中心に説明する。

#### 【0045】

本実施形態の光電変換装置は、画素11の信号制御回路15の構成が第1実施形態と異なる。

40

#### 【0046】

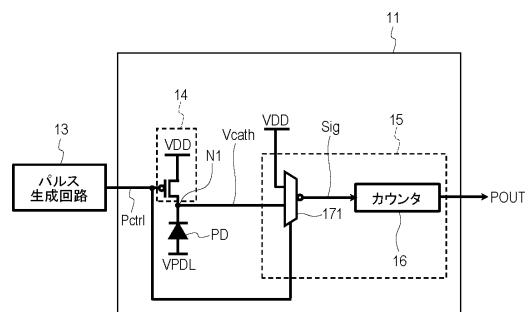

図8は、本実施形態の画素11の構成を示した図である。

#### 【0047】

本実施形態の画素11の信号制御回路15は、選択回路171を有する。選択回路171には、信号V<sub>cat h</sub>、電源電圧V<sub>DD</sub>が入力される。また、選択回路171はパルス生成回路13に接続され、制御信号である信号P<sub>ctr1</sub>が入力される。

#### 【0048】

選択回路171は、信号P<sub>ctr1</sub>の信号レベルに基づいて、信号V<sub>cat h</sub>と電源電圧V<sub>DD</sub>の一方を選択する論理回路である。そして選択回路171は、選択した信号を反

50

転させた信号を信号 *Sig* としてカウンタ 16 に出力する。

【0049】

選択回路 171 は、信号 *Pctr1* が *High* レベル（アバランシェ増倍の待機状態）の場合には、信号 *Vcath* を選択する。そして、選択回路 171 は、信号 *Vcath* を反転させた信号をカウンタ 16 に出力する。

【0050】

一方、選択回路 171 は、信号 *Pctr1* が *Low* レベル（リチャージ状態）の場合には、電源電圧 *VDD* を選択する。そして、選択回路 171 は、電源電圧 *VDD* を反転させた信号（すなわち接地電圧レベルの信号）をカウンタ 16 に出力する。

【0051】

選択回路 171 は、典型的には波形整形回路を備える。つまり、信号 *Pctr1* が *Low* レベルの場合において、信号 *Vcath* が所定の電圧を下回るまでは選択回路 171 の波形整形回路は信号 *Sig* を *Low* レベルとする。そして、信号 *Vcath* が所定の電圧を下回ると、選択回路 171 の波形整形回路は信号 *Sig* を *High* レベルとする。

【0052】

本実施形態の画素 11 の動作は、図 4 と同じとすることができる。これにより、本実施形態においても、第 1 実施形態の光電変換装置と同じ効果を得ることができる。

【0053】

なお、本実施形態においても、図 7 に示したレベルシフト回路 21 を設けるようにしても良い。

【0054】

〔第 3 実施形態〕

本実施形態の光電変換装置について、第 1 実施形態と異なる点を中心に説明する。

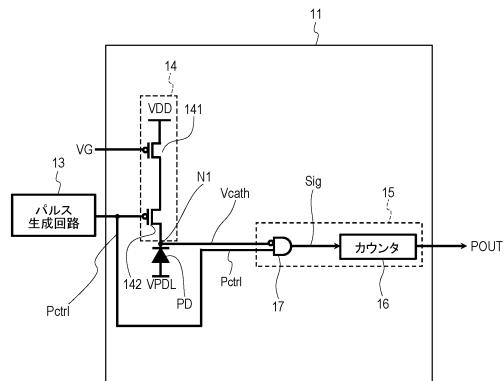

【0055】

本実施形態の光電変換装置の画素 11 は、PD 制御回路 14、信号制御回路 15 の構成が第 1 実施形態と異なる。また、パルス生成回路 13 が複数の制御信号である信号 *Pctr1\_1*、*Pctr1\_2* を出力する。

【0056】

図 9 は、本実施形態の画素 11 の構成を示した図である。PD 制御回路 14 は、PMOS トランジスタ 141、PMOS トランジスタ 142 を有する。

【0057】

パルス生成回路 13 は、信号 *Pctr1\_1* を PMOS トランジスタ 141 のゲートに出力する。また、パルス生成回路 13 は、信号 *Pctr1\_2* を PMOS トランジスタ 142 のゲートに出力する。

【0058】

信号制御回路 15 は、OR 回路 173、AND 回路 175 を有する。OR 回路 173 の入力部はパルス生成回路 13 に接続され、信号 *Pctr1\_1*、*Pctr1\_2* が入力される。OR 回路 173 は信号 *Pctr1\_1*、*Pctr1\_2* の論理和を、AND 回路 175 に出力する。

【0059】

AND 回路 175 の入力部は、ノード N1 と、OR 回路 173 に接続され、信号 *Vcath* を反転した信号と、OR 回路 173 の出力とが入力される。AND 回路 175 は、信号 *Vcath* を反転した信号と、OR 回路 173 の出力との論理積を信号 *Sig* としてカウンタ 16 に出力する。

【0060】

図 10 は、図 9 に示した画素 11 の動作を示した図である。図 10 に示した信号は、図 9 に示した信号に対応している。

【0061】

信号 *Pctr1\_1*、*Pctr1\_2* は、互いに周期が等しい。そして、信号 *Pctr1\_1* と信号 *Pctr1\_2* は位相が互いに異なる信号である。

10

20

30

40

50

## 【0062】

信号 P c t r 1\_1 と信号 P c t r 1\_2 が互いに L o w レベルである期間においてのみ、リチャージすることができる。そのため、図 6 の信号 P c t r 1 に対して、信号 P c t r 1\_1 および信号 P c t r 1\_2 の L o w レベルの期間が長くても、位相差を利用して同様のリチャージ期間を設けることができる。その結果、例えば、図 6 のように単一の信号 P c t r 1 で駆動する場合に比べて、信号伝送経路における波形なまりの影響でリチャージ期間が変動する影響を少なくすることができる。本実施形態では、複数の制御信号である信号 P c t r 1\_1、P c t r 1\_2 によって、アバランシェ増倍の待機状態とリチャージ状態とを制御することができる。そして、複数の制御信号である信号 P c t r 1\_1、P c t r 1\_2 が信号制御回路 15 に入力されることによって、リチャージ状態時に、信号 S i g が H i g h レベルから L o w レベルに遷移する。これにより、次のアバランシェ増倍の待機状態の期間にアバランシェ増倍が生じたか否かを好適に検出することができる。

10

## 【0063】

このように、本実施形態の光電変換装置においても、第 1 実施形態と同じ効果を得ることができる。

## 【0064】

なお、本実施形態の思想は、他の実施形態と組み合わせることが可能である。例えば、第 2 実施形態で説明した図 8 の画素 11 においても、P D 制御回路 14 の構成を、本実施形態の構成とすることができます。この場合、選択回路 171 に、図 8 の信号 P c t r 1 の代わりに、本実施形態の複数の制御信号である信号 P c t r 1\_1、P c t r 1\_2 が入力されるようにすればよい。そして、選択回路 171 が、信号 P c t r 1\_1、P c t r 1\_2 に基づいて、電源電圧 V D D と、信号 V c a t h のいずれかの信号を選択するようにはすればよい。

20

## 【0065】

## [第4実施形態]

本実施形態の光電変換装置について、第 1 実施形態と異なる点を中心に説明する。

## 【0066】

本実施形態の光電変換装置の画素 11 は、P D 制御回路 14 の構成が第 1 実施形態と異なる。

30

## 【0067】

図 11 は、本実施形態の画素 11 の構成を示した図である。P D 制御回路 14 は P M O S トランジスタ 141 と P M O S トランジスタ 142 を有する。P M O S トランジスタ 141 は定電圧 V G がゲートに与えられており、抵抗の役割を果たす。この構成によれば、P M O S トランジスタ 142 のゲート面積は、図 5 の構成のように単一の P M O S トランジスタで構成する場合に対して小さくすることができるため、信号 P c t r 1 の接続先のゲート容量を小さくすることができる。その結果、信号 P c t r 1 の波形なまりの影響を抑制することができる。また、ノード N 1 に対する P M O S トランジスタ 142 の寄生容量が、図 5 の P M O S トランジスタのノード N 1 に対する寄生容量より小さければ、アバランシェ増幅時の消費電荷量が減るため、より好ましい。

40

## 【0068】

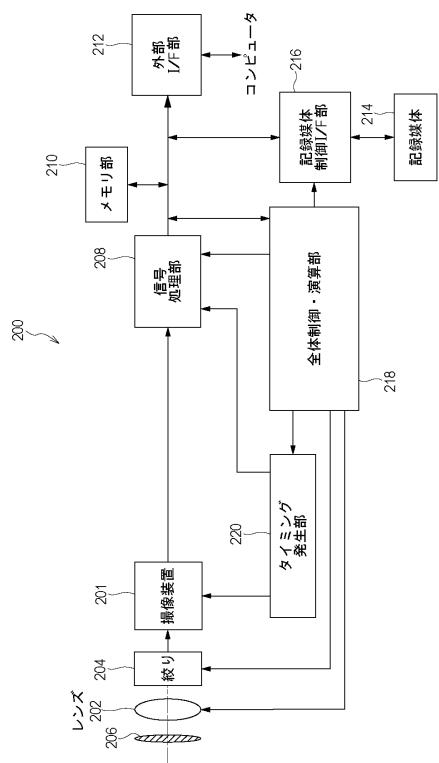

## [第5実施形態]

本発明の第 5 実施形態による撮像システムについて、図 12 を用いて説明する。図 12 は、本実施形態による撮像システムの概略構成を示すブロック図である。

## 【0069】

上記第 1 乃至第 4 実施形態で述べた光電変換装置 100 は、種々の撮像システムに適用可能である。適用可能な撮像システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。図 12 には、これらのうちの一例として、デジタルスチルカメラのプロ

50

ツク図を例示している。

【0070】

図12に例示した撮像システム200は、撮像装置201、被写体の光学像を撮像装置201に結像させるレンズ202、レンズ202を通過する光量を可変にするための絞り204、レンズ202の保護のためのバリア206を有する。レンズ202及び絞り204は、撮像装置201に光を集光する光学系である。撮像装置201は、第1乃至第4実施形態のいずれかで説明した光電変換装置100であって、レンズ202により結像された光学像を画像データに変換する。

【0071】

撮像システム200は、また、撮像装置201より出力される出力信号の処理を行う信号処理部208を有する。信号処理部208は、撮像装置201が出力するアナログ信号をデジタル信号に変換するAD変換を行う。また、信号処理部208はその他、必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。信号処理部208の一部であるAD変換部は、撮像装置201が設けられた半導体基板に形成されていてもよいし、撮像装置201とは別の半導体基板に形成されていてもよい。また、撮像装置201と信号処理部208とが同一の半導体基板に形成されていてもよい。

10

【0072】

撮像システム200は、更に、画像データを一時的に記憶するためのメモリ部210、外部コンピュータ等と通信するための外部インターフェース部(外部I/F部)212を有する。更に撮像システム200は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体214、記録媒体214に記録又は読み出しを行うための記録媒体制御インターフェース部(記録媒体制御I/F部)216を有する。なお、記録媒体214は、撮像システム200に内蔵されていてもよく、着脱可能であってもよい。

20

【0073】

更に撮像システム200は、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部218、撮像装置201と信号処理部208に各種タイミング信号を出力するタイミング発生部220を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システム200は少なくとも撮像装置201と、撮像装置201から出力された出力信号を処理する信号処理部208とを有すればよい。

【0074】

30

撮像装置201は、撮像信号を信号処理部208に出力する。信号処理部208は、撮像装置201から出力される撮像信号に対して所定の信号処理を実施し、画像データを出力する。信号処理部208は、撮像信号を用いて、画像を生成する。

【0075】

このように、本実施形態によれば、第1乃至第4実施形態による光電変換装置100を適用した撮像システムを実現することができる。

【0076】

[第6実施形態]

本発明の第6実施形態による撮像システム及び移動体について、図13を用いて説明する。図13は、本実施形態による撮像システム及び移動体の構成を示す図である。

40

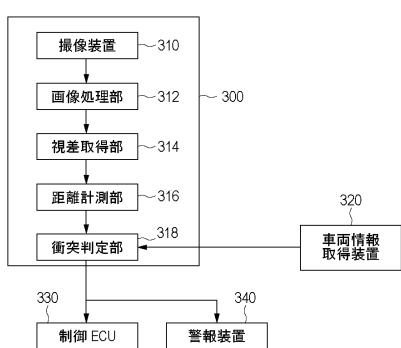

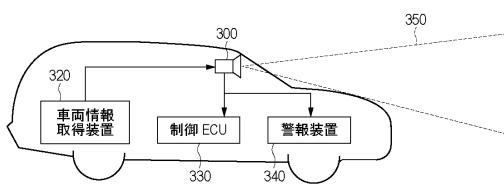

【0077】

図13(a)は、車載カメラに関する撮像システムの一例を示したものである。撮像システム300は、撮像装置310を有する。撮像装置310は、上記第1乃至第4実施形態のいずれかに記載の光電変換装置100である。撮像システム300は、撮像装置310により取得された複数の画像データに対し、画像処理を行う画像処理部312と、撮像システム300により取得された複数の画像データから視差(視差画像の位相差)の算出を行う視差取得部314を有する。また、撮像システム300は、算出された視差に基づいて対象物までの距離を算出する距離取得部316と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部318と、を有する。ここで、視差取得部314や距離取得部316は、対象物までの距離情報を取得する距離情報取得手段の一例である

50

。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) やASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

#### 【0078】

撮像システム 300 は車両情報取得装置 320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 330 が接続されている。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、ドライバーへ警報を発する警報装置 340 とも接続されている。例えば、衝突判定部 318 の判定結果として衝突可能性が高い場合、制御 ECU 330 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 340 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0079】

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム 300 で撮像する。図 13 (b) に、車両前方 (撮像範囲 350) を撮像する場合の撮像システムを示した。車両情報取得装置 320 が、撮像システム 300 ないしは撮像装置 310 に指示を送る。このような構成により、測距の精度をより向上させることができる。

#### 【0080】

上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体 (移動装置) に適用することができる。加えて、移動体に限らず、高度道路交通システム (ITS) 等、広く物体認識を利用する機器に適用することができる。

#### 【0081】

##### [変形実施形態]

本発明は、上記実施形態に限らず種々の変形が可能である。

#### 【0082】

例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

#### 【0083】

また、上記第 5 及び第 6 実施形態に示した撮像システムは、本発明の光電変換装置を適用しうる撮像システム例を示したものであり、本発明の光電変換装置を適用可能な撮像システムは図 12 及び図 13 に示した構成に限定されるものではない。

#### 【0084】

なお、上記実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0085】

11 画素

13 パルス生成回路 (生成回路)

14 P D 制御回路 (第 1 制御回路)

10

20

30

40

50

## 1 5 信号制御回路 (第 2 制御回路)

## 1 6 カウンタ

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

【図 1 1】

【図 1 2】

10

20

【図 1 3】

(a)

30

(b)

40

50

---

フロントページの続き

ヤノン株式会社内

審査官 うし 田 真悟

(56)参考文献 国際公開第2016/042734 (WO, A1)

特表2008-538606 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79

H01L 31/10