**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                                                   |                             |

|---------------------------------------------------------------------------------------------------|-----------------------------|

| (51) Int. Cl. <sup>6</sup><br>G11C 11/40                                                          | (45) 공고일자<br>2001년06월01일    |

| (21) 출원번호<br>10-1992-0007616                                                                      | (11) 등록번호<br>10-0292552     |

| (22) 출원일자<br>1992년05월06일                                                                          | (24) 등록일자<br>2001년03월24일    |

| (30) 우선권주장<br>P4114744.8 1991년05월06일 독일(DE)                                                       | (65) 공개번호<br>특 1992-0022290 |

| (73) 특허권자<br>지멘스 액티엔게젤샤프트<br>독일연방공화국 문현 80333 비델스파하프라즈 2                                          | (43) 공개일자<br>1992년12월19일    |

| (72) 발명자<br>좀머 디터<br>독일연방공화국 데-8000 문현 5 베스터월슈트라쎄 23<br>사비냑 도미니끄<br>독일연방공화국 데-8045 이스마닝 반호프슈트라쎄 2 |                             |

| (74) 대리인<br>남상선                                                                                   |                             |

**심사관 : 이승한**

---

**(54) 데이터 전송방법 및 반도체 메모리**

---

**요약**

다수의 메모리 셀과 반도체 메모리의 입출력 단자중 적어도 하나 사이에서 데이터 전송을 위한 방법 및 상기 방법을 수행하기위한 반도체 메모리에서, 메모리 셀 어드레스는 데이터 전송용 제어 신호에 의해 규정된다. 메모리 셀들간의 데이터 전송 작동은, 어드레스 제어 신호 및 출력인에이블 제어 신호중 하나로 메모리 셀 어드레스를 규정하기 위해 상기 두 신호로 제어된다.

데이터 전송 작용은 두개의 제어 신호의 주어진 논리 연결로 연속해서 시작된다. 계속해서 일어나는 데 이타 전송은 상기 두 제어 신호중 다른 것으로 제어된다.

**대표도**

**도1**

**형세서**

[발명의 명칭]

데이터 전송방법 및 반도체 메모리

[도면의 간단한 설명]

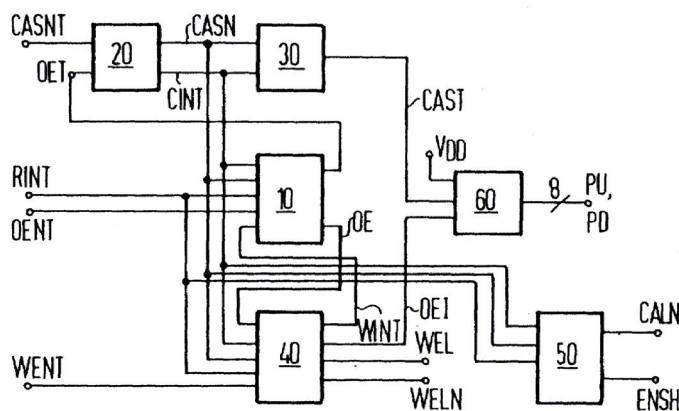

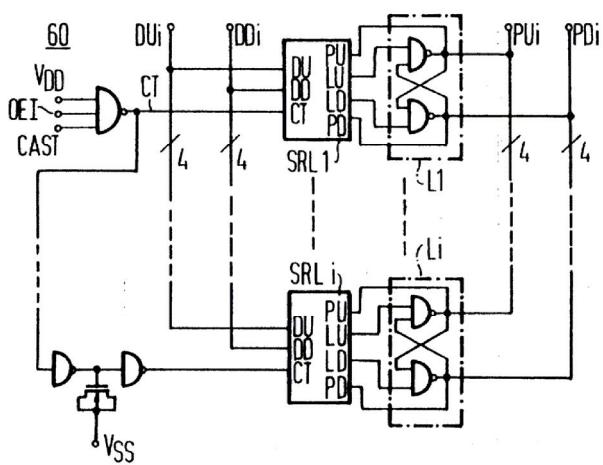

제1도는 본 발명을 설명하기 위해 사용된 장치의 블록 회로도.

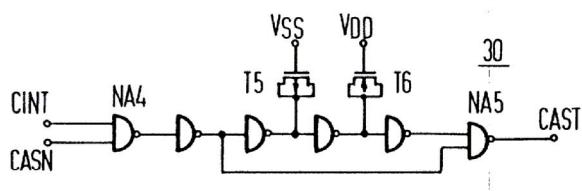

제2도는 출력 인에이블 제어신호로부터 내부 제어신호를 발생하기 위한 장치의 기본 회로도.

제3도는 내부 어드레스 제어신호를 발생하기 위한 기본 회로도.

제4도는 니블-페이지 모드를 설명하기 위한 장치의 기본 회로도.

제5도는 출력 제어에 대한 내부 신호를 발생하기 위한 장치의 기본 회로도.

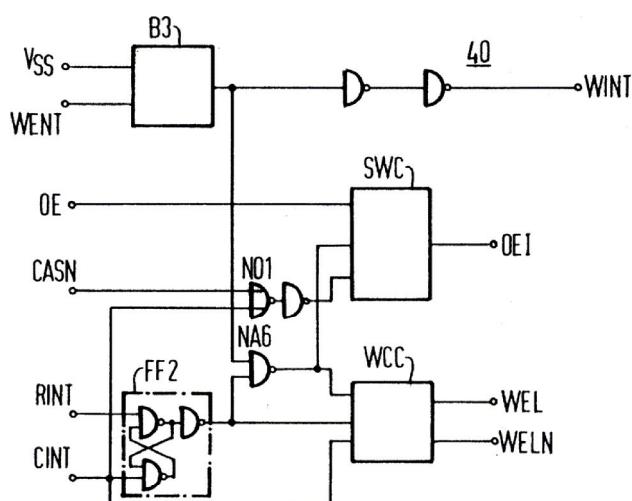

제6도는 내부 기록 제어신호를 발생하기 위한 장치의 기본 회로도.

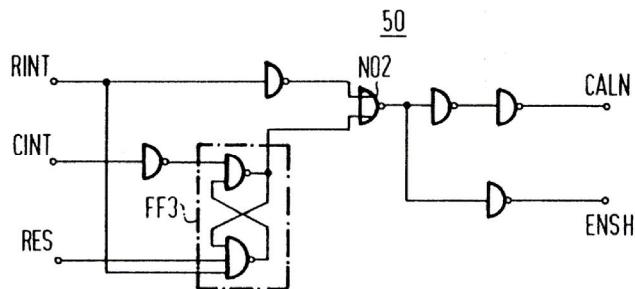

제7도는 어드레스 제어신호를 발생하기 위한 장치의 기본 회로도.

제8도는 출력 제어신호의 기본 회로도.

제9(a)도는 출력 제어신호의 랫치회로에 대한 기본 회로도.

제9(b)도는 버퍼 회로의 기본 회로도.

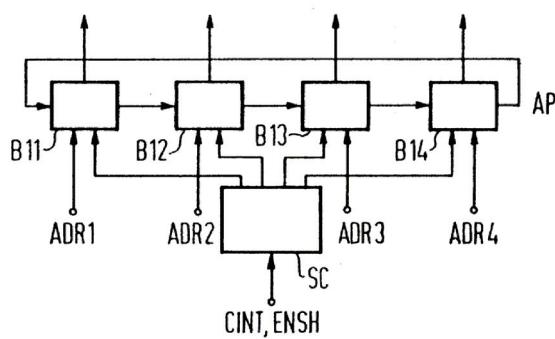

제10도는 본 발명에 따른 신호를 갖는 니블 모드를 설명하기 위한 장치의 기본 회로도.

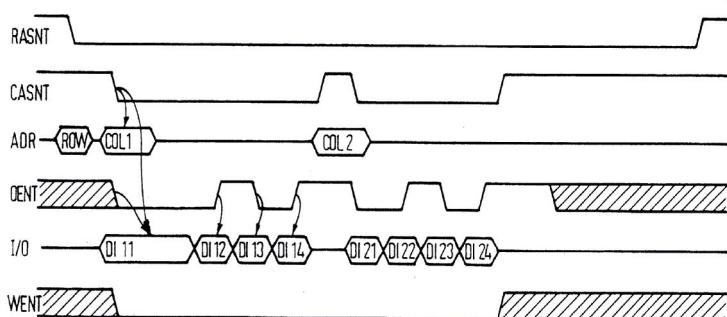

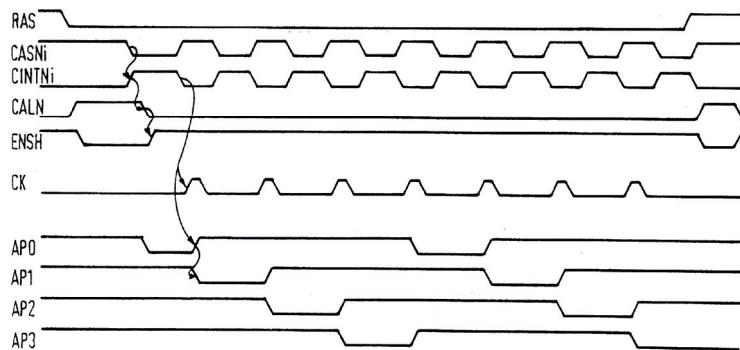

제11도는 니블-페이지 모드를 설명하기 위해 사용된 신호도.

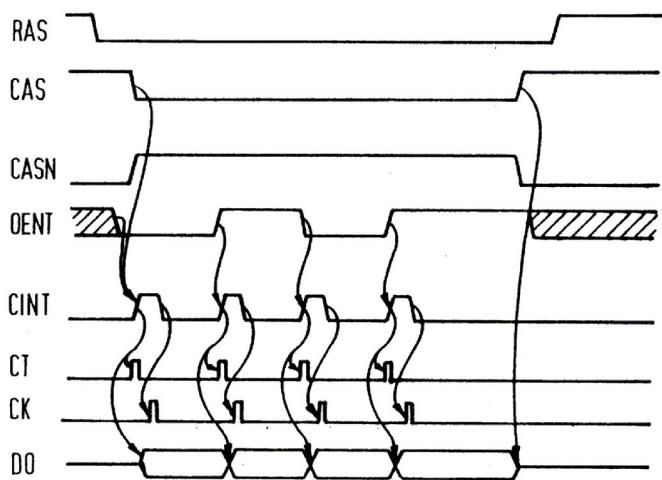

제12도는 판독 사이클에서 본 발명에 따른 방법을 설명하기 위해 사용된 신호도.

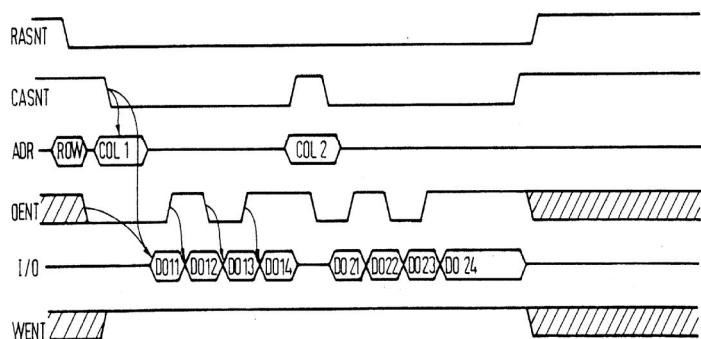

제13도는 판독 사이클에서 니블-페이지 모드를 설명하기 위해 사용된 신호도.

제14도는 기록 사이클에서 니블-페이지 모드를 설명하기 위해 사용된 신호도.

#### \* 도면의 주요부분에 대한 부호의 설명

MUX1, MUX2 : 멀티플렉서

RB : 판독 버스

WB : 기록 버스

MA : 메모리 셀 어레이

DI : 연결핀

TC : 시간제어회로

#### [발명의 상세한 설명]

본 발명은 다수의 메모리 셀과, 데이터 전송을 위해 제어신호에 의해 하나의 메모리 셀 어드레스가 규정되는 반도체 메모리의 입출력 단자중 적어도 하나 사이에서 데이터 전송을 위한 방법과, 어드레스를 위한 수단과 메모리 셀을 규정하기 위한 수단 및 메모리 셀들간의 데이터 전송을 제어하기 위한 수단을 갖고 상기 방법을 수행하기 위한 반도체 메모리에 관한 것이다.

집적 반도체 메모리의 메모리 밀도가 증가되고, 데이터 워드 폭이 증가됨에 따라, 메모리 셀들간에 가능한 최고의 속도를 구현하는 데이터 전송이 요구된다. 전형적인 반도체 메모리는 매트릭스 어레이로 조직된다. 각각의 개별 메모리 셀은 워드라인 및 비트라인으로 한정된다. 그러한 하나의 메모리 셀을 액세스하는 것은 상기 메모리 셀에 지정된 어드레스를 반도체 메모리에 인가하고, 동시에 로우 어드레스 스트로브 신호(RAS) 및 칼럼 어드레스 스트로브 신호(CAS)를 인가하므로 수행된다. 전형적으로, 메모리 셀의 로우 또는 워드 어드레스는 RAS 신호로 어드레스되고 선택된다. 계속해서, 칼럼 어드레스는 CAS 신호에 의해 작동되며, 메모리 셀은 그와 같이 하여 한정된다.

종래 기술에는, 소위 페이지 모드 또는 니블 모드라고 하는 메모리 셀 액세스를 위한 여러가지 기능 모드가 있다. 상기 페이지 모드에서, 상기 로우는 워드라인을 따라서 메모리 셀로 선택되며, 이러한 방법에 따라서, 선택 칼럼 어드레스에 대한 새로운 액세스가 칼럼 어드레스 스트로브 신호 CAS의 두 클럭에 지정 하나에 의해 수행될 수 있다. 그러한 모드에서 개별 셀 액세스를 위해 단지 로우 어드레스만이 변화될 필요가 있으므로, 칼럼 및 로우 어드레스가 불규칙하게 재규정되는 모드와 비교할 때 속도에서 우위를 차지한다.

페이지 모드와 비교할 때, 니블 모드는 데이터 전송 속도에서 상당한 증가를 가져온다. 미합중국 특허 제4,344,156호에 기술된 니블 모드에서는, 네개의 메모리 셀에 대한 액세스가 하나의 어드레스 규정에 의해 수행된다. 상기 네개의 메모리 셀은 상기 규정된 어드레스 중 두 어드레스 인덱스의 가능한 조합이다. 상기 네개의 메모리 셀 즉, 하나의 규정된 어드레스로 주소가 정해지는 네개의 메모리 셀은 버퍼 메모리로 그 저장된 데이터를 출력시키는데, 상기 버퍼 메모리로부터 데이터가 외부로, 입/출력 단자로 또는 반도체 메모리 단자로 전달된다.

전형적으로, 하강 CAS 신호에 있는 니블 펄스에 대한, 다시 말해, 상기 네개의 메모리 셀의 네 비트의 판독 또는 기록에 대해 칼럼 어드레스를 규정하며, 한편 메모리 셀에 대한 새로운 액세스가 RAS에지에서 발생한다. 페이지 모드에서처럼, 그에 대응하는 제1 칼럼 어드레스는 전형적으로 상승 CAS에지에서 채택되며, 데이터는 하강 CAS에지로 그 칼럼 어드레스 또는 메모리 셀로부터 취할 수 있다. 니블 모드에서, 다음 세개의 메모리 셀 액세스를 위해서 어드레스의 새로운 변화는 필요하지 않게 된다. 따라서, 근본적으로 그것들을 규정할 필요가 없다.

데이터 속도를 증가시키기 위한 또 다른 조건은 고체상태 회로에 대한 IEEE 저널, 1989년 8월호, 제24권, 제4호 900 내지 940면의 케이 수마타 등의 명칭 “고밀도 DRAM의 새로운 니블-페이지 구조”에 공지되어 있다. 그러한 니블-페이지 구조에서, 8비트로 된 유니트의 메모리 어드레스에 대한 액세스는 선택된 워드라인 또는 메모리 셀을 따라서 수행될 수 있다. 각 유니트의 8비트에 대한 액세스는 하나의 어드레스를 규정하므로 수행된다. 제1 어드레스가 규정되고 저장된 셀 정보 데이터가 출력된 후, 제1 어드레스에 지정된 메모리 셀의 데이터는, 짧은 간격동안 서로 교번되는, CAS 신호 각각의 다음부의 에지에서 판독된다. 판독 사이클에 대해서도 동일하다. 데이터 출력 또는 입력의 제어는 CAS 신호 및 기록-인에이블(WE) 신호의 도움으로 수행된다. 내부적으로, 상기 8비트에 지정된 메모리 셀은 두 개의 셀 영역으로 분할된다. 즉, 그 각각은 4비트 크기의 데이터 레지스터로 지정된다. 이 정도로, 이것은 공지된 형태의 더블 니블 모드이다. 그러한 빠른 액세스가 갖는 불리한 점은 그처럼 구성되는 메모리 모듈이 그 사이클 액세스에서만 사용될 수 있고, 다른 작동 모드는 수행될 수 없거나 어렵게 수행될 수 있다는 것이다.

미합중국 특허 제4,758,995호에서는 8비트가 하나의 어드레스 규정에 의해 연속해서 판독될 수 있게 하는 데이터 전송방법에 대해 설명한다. 어드레스가 취해지고 첫번째가 관련된 메모리 셀을 판독한 후에, 다른 7비트가 두개의 메모리 셀 영역으로부터 연속해서 판독된다. 카운터는, 다음 네개의 메모리 셀이 어드레스되고 제1 메모리 셀의 판독이 끝나기 전에 충분한 시간을 갖고 판독되는 방식으로 데이터 출력을 제어한다. 기록에 대해서도 그와 동일 방법이 사용된다. 이러한 방법은 빠른 니블 사이클로 고려될 수 있는데, 이것은 그러한 형태의 모듈에 대해서만 사용된다.

따라서, 본 발명의 목적은, 반도체 메모리 액세스 및 반도체 메모리에 데이터를 전송하는 방법을 제공하고 상기 방법을 수행하기 위한 반도체 메모리를 제공하는 것으로서, 이에 따라 전술된 공지방법 및 이러한 종래 형태의 장치에서의 단점을 극복할 수 있으며, 반도체 메모리의 기본적인 기능에 실제적인 제한을 가하지 않고도 메모리 셀을 빨리 액세스하는 것이 가능하게 한다.

전술된 그리고 다른 목적들을 고찰해 볼 때, 본 발명에 따라 다수의 메모리 셀과 반도체 메모리의 적어도 하나의 입/출력 단자 사이에 데이터 전송을 위한 방법이 제공되는데, 여기서 메모리 셀 어드레스는 데이터 전송을 위한 제어 신호에 의해 규정되며, 어드레스 제어신호 및 출력 인에이블 제어신호 중 하나

로 메모리 셀 어드레스를 규정하기 위해 상기 두 신호로 메모리 셀로부터 또는 메모리 셀로 데이터 전송 작동을 제어하며, 상기 두 제어신호의 주어진 논리 연결로 데이터 전송 작동을 계속해서 개시하며, 두 제어신호 중 다른 하나로 계속되는 데이터 전송을 제어하는 것을 포함하는 개선점을 제공한다.

본 발명의 또 다른 모드에 따라, 각각의 규정된 메모리 셀 어드레스에서 다수의 메모리 셀에 하나의 데이터를 액세스시키는 것을 포함하는 방법이 제공된다.

본 발명의 또 다른 모드에 따라, 어드레스 제어신호중 하나의 신호 에지로 메모리 셀 어드레스를 규정하고, 출력 인에이블 제어신호중 하나의 신호 에지로 데이터 전송을 제어하는 것을 포함하는 방법이 제공된다.

본 발명의 부가된 모드에 따라서, 어드레스 제어신호중 각각의 신호에지로 메모리 셀 어드레스를 규정하며, 출력 인에이블 제어신호중 각각의 신호 에지로 데이터 전송을 제어하는 것을 포함하는 방법이 제공된다.

본 발명의 부가적인 모드에 따라서, 어드레스 제어신호의 한 펄스 에지로, 규정된 메모리 셀 어드레스와 관련된 데이터 전송 작동을 종결시키는 것을 포함하는 방법이 제공된다.

본 발명의 목적을 고찰할 때, 어드레스를 위한 수단과 메모리 셀 규정 수단과 메모리 셀들간의 데이터 전송을 제어하는 수단을 포함하며, 다수의 메모리 셀과 적어도 하나의 입/출력 단자를 갖는 반도체 메모리가 제공되며, 어드레스 제어신호 및 출력 인에이블 제어신호로 데이터 전송 작동을 제어하기 위한 수단과, 상기 두개의 신호중 하나로 메모리 셀 어드레스를 규정하기 위한 수단과, 상기 두 신호중 다른 것으로 데이터 전송을 제어하며 상기 두 제어신호중 주어진 논리 연결에서 데이터 전송 작동을 개시하기 위한 수단을 포함하는 개선점이 제공된다.

본 발명의 또 다른 특징에 따라, 메모리 셀을 액세스하기 위한 수단은 각각의 규정된 메모리 셀 어드레스로 다수의 메모리 셀을 액세스한다.

본 발명의 또 다른 특징에 따라, 어드레스 제어신호는 메모리 셀 어드레스를 규정하며, 출력 인에이블 제어신호는 한번에 두 신호 에지중 하나로 데이터 전송을 제어한다.

본 발명의 부가된 특징에 따라, 어드레스 제어신호는 메모리 셀 어드레스를 규정하고, 출력 인에이블 제어신호는 신호 에지 각각으로 데이터 전송을 제어한다.

본 발명의 부수적인 특징에 따라, 규정된 메모리 셀 어드레스와 관련된 데이터 전송 작동은 어드레스 제어신호의 한 클럭 에지로 차단될 수 있다.

본 발명의 장점은, 양자의 작동 모드에서 반도체 메모리의 표준화된 기술 기능을 근본적으로 손상시키지 않고도 메모리 셀간에 높은 데이터 전송 속도를 가능하게 한다는 것이다. 데이터 전송을 제어하기 위해, 어드레스 스트로브 신호 CAS 및 출력 인에이블 제어신호 OE가 사용된다. 출력인에이블 신호는 외부 접속핀을 통해 반도체 메모리에 인가될 수 있으며, 상기 접속핀은 4매가비트 이상의 메모리 용량을 갖으며 ×4 조직을 갖는 반도체 메모리에서 표준 양식이다. 국제적으로 공인된 사양에 따라, 데이터 출력 및 입력은 전송되는 데이터가 없는한 트라이 스테이트(tri-state) 상태로 스위치된다. 본 발명에 대한 특징으로 고려되는 다른 특징이 첨부된 청구범위에 설명되어 있다.

본 발명이 반도체 메모리용 데이터 전송방법 및 상기 방법을 수행하기 위한 반도체 메모리의 실시예로서 설명 및 기술되었지만, 본 발명은 예시된 세부점에 제한되도록 의도된 것은 아니다. 왜냐하면, 여러가지 수정 및 구조적인 변경이 본 발명의 청구범위내에서 이루어질 수 있기 때문이다.

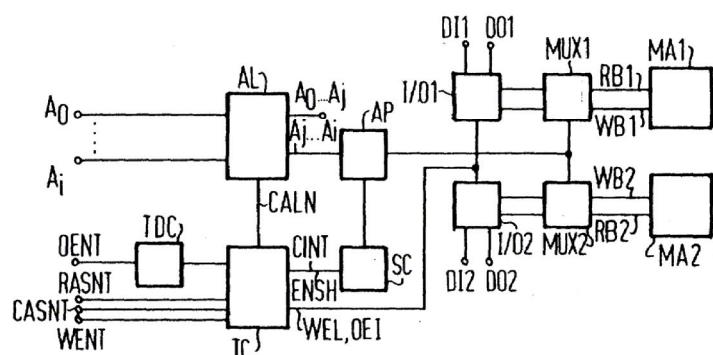

그러나 부가적인 목적 및 장점과 함께 본 발명의 작용방법 및 그 구조는 첨부된 도면을 참조하여 고려할 때 특정 실시예의 설명으로부터 가장 잘 이해할 수 있다. 도면을 자세히 참조하여 보면, 동일한 참조번호는 동일한 요소에 속하며, 특히 제1도에서, 니블 페이지 모드를 갖는 구성의 블록 회로도가 도시되어 있는데, 이것은 예시적인 실시예로서 본 발명에 따른 방법을 설명하는데 사용된다. 본 발명의 전술된 목적에 따라 설정된 조건은, 메모리의 기본적인 기능이 본 발명에 따른 구성 및 방법에 의해 가능한 적게 손상을 받도록 한 것으로서, 표준 사이클이 변동되지 않도록 하므로 보장된다. 다시 말해서, 그 어드레스에 따라 규정된 메모리 셀의 액세스는 RAS 또는 CAS 신호로 수행된다.

본원에서, “RAS 및 CAS 신호”는 외부에서 메모리의 연결핀으로 인가되는 형태의 신호를 말한다. 이것은, TTL 신호 RAS, CAS, WE 및 OE가 핀에 반전 형태로 인가됨을 의미한다. 이것은 참조부호 RASNT, CASNT, WENT 및 OENT로 표시된다. 제1도에서, 이 네개의 신호는 반도체 메모리에 대한 입력제어신호를 형성한다. 하나의 메모리 셀에 대한 어드레스는 RASNT 및 CASNT 신호에 의해 규정되며, 신호 WENT는 메모리가 판독되어야 하는지 기록되어야 하는지를 규정하며, 신호 OENT는 데이터 출력에 대한 출력 버퍼를 인에이블시킨다. 공지된 메모리에서 데이터 입력은 분리된 제어신호에 의해 규정된다.

본 발명의 근본 개념은 공지된 메모리에서와 같이, 메모리 셀이 RAS 및 CAS 신호에 의해 어드레스되고 상기 어드레스는 하강 CAS 신호 에지에서 채택된다. 이미 설명된 바와같이, 그러한 주 펄스의 빠른 연속 동작은 불가능하다. 그 주된 이유는 어드레스 채택이 비교적 긴 시간을 차지하기 때문이다. 따라서, 본 발명을 신호 RAS 및 CAS 사이에서 규정된 두개의 주 펄스 사이에서 부가적인 데이터가 판독될 수 있게 한다. 이러한 목적을 위해서, 제어신호는 신호 CASNT 및 OENT의 도움으로 발생된다. 니블 페이지 모드에서, 주 펄스는 페이지 모드의 주펄스와 일치하는 것으로서, 각각의 주 펄스후에 세개의 부가적인 데이터 펄스로 니블 모드를 형성한다. 이러한 방식으로, 공지된 니블 및 페이지 또는 빠른 페이지 DRAM 모드는 서로 결합될 수 있다. 매 비트당 기록과 같이 또다른 조합이 역시 가능하다. 주로, 대응하는 표준 기능이 손상되지는 않는다. 데이터 전송이 외부 핀에 인가되는 신호 CASNT 및 OENT로 제어되어야 하므로, 이것을 제어하는데는 두가지 기본 조건이 있다. 첫째, 실제의 데이터 전송이 신호 CASNT에 의해 제어될 수 있으며, 둘째, 그것이 신호 OENT에 의해서 제어될 수 있다. 빠른 데이터 전송에도 불구하고, 신호 CASNT로 데이터 전송을 제어하는 것은, CAS 신호에 따라 새로운 칼럼 어드레스의 채택이 어떤 니블 펄스에서

만 가능하다는 단점이 있다. 더욱이, 데이터 출력 버스가 CAS 신호를 통해 트라이 스테йт 상태로 스위치될 수 없으므로, 이 트라이 스테йт 상태는 신호 OENT에 의해 규정될 수 있어야 한다. 공지된 작동 모드와 호환되는 요구조건이 없어지면, 데이터 출력버스는 트라이 스테йт 변이 없이도 작동이 가능하다.

신호 OENT로 데이터 전송을 제어하는 것이, 출력 인에이블 신호를 위한 접속이 ×1 조직 및 4메가비트 이하의 메모리 용량을 갖도록 제공되어야 한다는 단점을 갖는다 할지라도, 빠른 데이터 전송시에 어떤 시간에도 새로운 칼럼 어드레스를 채택하는 것이 가능하다는 장점이 있다. 왜냐하면, CAS 신호는 메모리 셀을 규정하는데 사용되기 때문이다. 신호 CASNT로, 계속되는 니블 순서가 차단될 수 있고 어드레스가 새로운 니블 사이클 동안에 채택될 수 있다. 어드레스 제어신호 CASNT가 메모리 셀 어드레스를 규정하며 출력 인에이블 신호 OENT가 데이터 전송을 제어하는 이러한 제2의 경우는 제1도와 관련하여 후술된다. 상기 상태는 본 발명의 한 특징에 따라, 설명되는데, 여기서 데이터 전송 속도를 더 증가시키기 위해서 신호 OENT의 두 신호 애지중 하나는 물론 신호 OENT의 두 신호 애지 각각이 데이터를 기록 또는 판독한다. 각각의 니블 순서의 제1 데이터는, 신호CASNT의 부의 애지로 어드레스를 채택한 후, 어드레스가 규정되고 데이터 입력 또는 출력이 시작될 때마다 적용 메모리 셀에 기록 또는 판독된다. 이것은 데이터 판독 또는 데이터 기록 작동이 신호 CASNT 및 신호 OENT가 모두 논리 0일 때마다 시작될 수 있다. 데이터 전송을 위하여, 다시 말해서 데이터 기록 또는 판독을 위해서, OENT 신호에 의한 제어가 제공되며, CASNT 신호는 새로운 어드레스가 채택되도록 의도될 때까지 논리 0로 남아 있게 된다.

본 발명의 방법의 흐름을 제어하기 위해서, 시간제어회로 TC가 제1도에 제공되는데, 여기서 신호 RASNT, CASNT 및 WENT는 입력 신호로서 직접 전달된다. 본 발명에 따라 결합하여 결정되는 인에이블 제어신호 OENT는 데이터 전송 인식 TDC용 회로를 통해 시간 제어회로 TC와 통신한다. 회로 TC는 어드레스 랜치 회로 AC에 접속되며, 이 어드레스에서 신호 A0-Ai가 존재한다. 니블 모드가 전형적으로 네개의 데이터 셋트를 포함하므로, 상기 네개의 연관된 메모리 셀은 두개의 어드레스 인덱스의 도움으로 규정될 수 있다. 그러나, 본 발명은 두 개의 주 펄스 사이에 네개의 데이터로 니블 모드를 전송하는데 제한되지는 않으며, 필요로하는 더 많은 데이터, 예를들면 8 또는 16 데이터가 수정된 니블 모드에서 전송될 수 있다. 제1도는 어드레스 Aj-Ai가 어드레스 포인터 AP로 전달됨을 표시한다. 다른 어드레스 A0-Aj는 도시되지는 않았지만, 선택적으로는 다른 기능그룹의 삽입으로 대응하는 디코더로 전달되며, 상기 다른 기능 그룹은 여기서 중요하지 않다. 어드레스 포인터 AP의 작업은 실제의 니블 모드를 제어하기 위한 것이다. 어드레스 포인터 AP 및 시간제어회로 TC는 쉬프트 제어회로 SC를 통해서 서로 통신한다. 실제의 메모리 셀 어레이에 대해서, 어드레스 포인터 AP는 멀티플렉서 MUX1과 통신하며, 상기 멀티플렉서 MUX1은 실제의 메모리 셀 어레이 MA1과 입/출력 회로 I/O1 사이에 배치된다. 이러한 종류의 메모리 셀 어레이 MA1은 다수의 메모리 셀 블록으로 분할되며 각각의 메모리 셀 블록은 여러가지 메모리 셀 필드를 갖는다. 상기 메모리 셀 어레이 MA1 및 멀티플렉서 MUX1을 통해 입/출력 회로 I/O1으로 접속된다. 상기 입/출력회로는 각각의 외부적으로 액세스가 가능한 접속핀 D11 및 D01으로 접속되며, 상기 핀들은 자연히 데이터 입력 및 출력용 신호단자로서 구성될 수 있다. 메모리 셀 어레이, 멀티플렉서 및 입/출력 회로는 제1도에 도시된 바와같이, 더블 또는 4종과 같은 리던더시가 될 수도 있다. 이 경우에, 여러 접속 및 제어는 동일하다. 예를들어, 제1도에서, 멀티플렉서 MUX1 및 MUX2는 버스 RB1, WB1 및 RB2, WB2 위에서 실제의 메모리 셀 어레이 MA1 및 MA2로 연결되고 어드레스 포인터 AP로도 접속된다. 분리된 기록제어 및, 데이터 출력버스 또는 데이터 출력단자의 인에이블먼트를 통해서, 입/출력 회로 I/O1 및 I/O2는 시간제어회로 TC에 접속된다.

제1도에 도시되었지만 설명되지는 않은 신호가 다른 도면과 관련하여 후술된다. 단자에 연결된 라인 및 라인에서 전달된 신호는 물론 그 단자 및 신호가, 설명을 간단히 하기 위해서 동일 참조번호로 확인된다.

데이터 전송 제어가 신호 CASNT 및 OENT로 수행되므로, 나머지 회로의 전체적으로 동일한 설정을 통해서, 회로 TDC와 같은 회로는 신호 CASNT용 접속핀과 시간제어회로 TC 사이에 연결될 수 있으며, 그 경우에 신호 OENT는 시간제어회로로 직접 전달될 수 있다. 본 기술에 숙련된 사람이라면 본 발명이 예시된 실시예에 제한되지 않음을 쉽게 알 수 있다. 개인의 직업적 능력을 사용하여, 본 기술에 숙련된 사람이라면, 본 발명의 기술을 사용하므로 다른 예시 실시예를 제공할 수 있다.

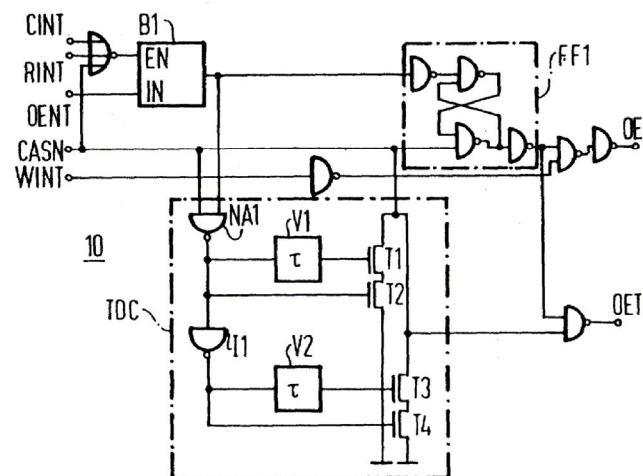

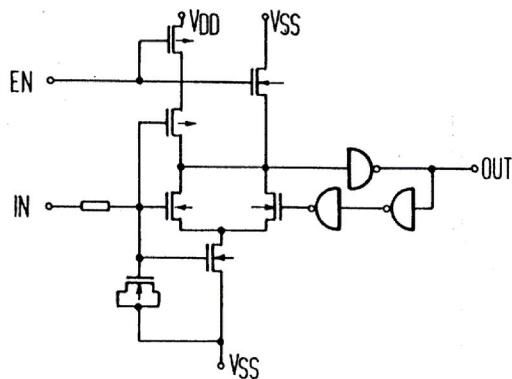

제2도는 이 신호 OENT에서 신호전송을 인식하기 위한 회로 TDC를 구비하는 회로(10)를 도시한다. 상기 회로의 입력 신호는 신호 OENT로서, 반도체 메모리의 외부 연결핀에 인가된 TTL CMOS 레벨을 갖는다. 이 신호는 버퍼 B1에서 내부 신호 레벨로 변환된다. 버퍼 B1은, 외부 제어신호로부터 나오는 내부적으로 발생된 제어신호의 도움으로 인에이블된다. 이러한 내부 제어신호 CINT, RINT 및 CASN의 발생은 후술된다. 버퍼 B1의 출력은, 플립플롭의 도움으로, 각 경우의 다음 신호전송까지 저장된다. 내부신호 OE는 플립플롭 FF1의 출력에 존재한다.

회로 TDC는 버퍼 B1의 출력신호에 의해서, 다시말하면 입력신호 OENT 및 내부 제어신호 CASN에 의해 제어된다. 상기 두 신호는 NAND 게이트 NA1에서 함께 연결된다. 이러한 게이트 NA1의 출력신호는 지연된 소자 V1에 의해 지연된 형태로 한번 사용되고 두개의 트랜지스터 T1 및 T2를 트리거시키기 위해 지연되지 않은 형태로 한번 사용된다. 게이트 NA1의 출력신호는 인버터 I1의 도움으로 반전되며, 동일한 방법으로 사용되는 출력신호를 갖는데, 한번은 지연소자 V2에 의해 지연되고, 한번은 두개의 트랜지스터 T3 및 T4를 트리거시키기 위해 지연되지 않는다. 두개의 트랜지스터 그룹이 상호연결된 OR 연결을 형성한다.

이러한 연결의 출력은 예시되지 않은 또다른 NAND 게이트의 한 입력을 형성하며, 신호 OE에 의해 형성되는 또다른 입력을 갖는다. 이러한 게이트의 형성되는 또다른 입력을 갖는다. 이러한 게이트의 출력측에서, 신호 OET가 사용되는데, 상기 신호는 발생되는 내부 제어신호 CINT를 트리거시키기 위해 제공된다. 완성하기 위해 플립플롭 FF1이 내부 제어신호 CASN에 의해 리셋될 수 있다. 내부 신호 WINT는 데이터 출력 또는 신호 OE를 차단하는데 사용된다.

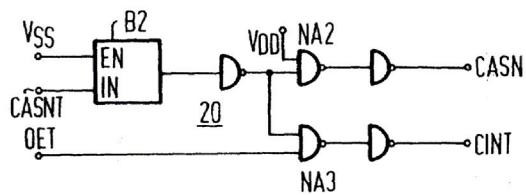

제3도는 외부 TTL 신호 CASNT로부터 내부 칼럼 어드레스 스트로브 신호 CASN을 발생시키기 위한

회로(20)를 도시한다. 외부 신호는 버퍼 B2로 전달되는데, 상기 버퍼 B2는 상기 신호를 내부 전압 레벨 신호로 변환하여, NAND 게이트 NA2를 포함하는 또 다른 논리 소자의 출력에서 내부 신호 CASN으로서 상기 내부 전압 레벨신호를 공급한다. 여기서 NAND 게이트 NA2는 본 발명에서는 별로 중요치 않다. 동시에, 제3도는 내부 제어신호 CINT의 발생을 도시하는 것으로, 상기 신호 CINT는 본 발명에서 필요요소로서, 신호 OET 및 제어신호 CASNT로부터 발생된다. 버퍼 B2후에, 내부 제어신호 CINT를 발생하기 위해서 신호 CASNT에 대응하는 신호가 NAND 게이트 NA3와 논리적으로 연결된다. 이 내부 제어신호 CINT는 데이터 전송을 위한 결정 신호이다. 제2도 및 제3도의 이 신호를 발생시키고나서 명백해지겠지만, 신호 CINT는 신호 펄스 신호 나타내며, 여기서 신호 CASN이 선정된 논리 상태라고 가정되며 신호 OENT의 논리상태 신호 변화가 발생될 때마다 하나의 펄스가 발생된다. 이 접속은 제12도와 관련하여 후술될 것이다. 워드라인 이 신호 RAS에 의해 선택되고, 칼럼 어드레스 스트로브 신호 CAS가 메모리 셀 엑세스를 인에이블시킬때, 신호 CAS는 물론이고 신호 OENT도 논리적 제로이자 마자 신호 CINT의 제1 펄스가 발생된다. 이러한 논리 상태의 연결은 제1 시간동안 CINT 펄스를 발생시키기 위해 필요하다. 신호 OENT의 논리상태의 각 연속신호가 변화할때, 신호 CINT의 또 다른 펄스가 발생된다. 신호 CINT의 두 신호 에지중 하나는 한번에 데이터 전송을 제어한다. 상기 데이터는, 신호 CINT의 일정한 에지에서 다음 데이터가 채택되거나 사이클이 신호 CAS의 도움으로 파괴될 때까지 존재한다.

본 발명의 기본 개념은 이후 기술되는 특징으로부터 명백해진다. 메모리 셀 어드레스를 채택 및 결정으로 인해, 반도체 메모리용 데이터 전송이 외부 신호로 충분히 빨리 토글될 수 없으므로, 내부 제어 펄스 CINT가 발생되며, 외부 OENT 신호와 결합하여 외부 칼럼 어드레스 스트로브 신호 CAS에 의해 제어된다. 이러한 방식으로, 이미 알려졌고 더 설명되는 내부 에어의 표준 기능이 무효된다. 신호 CINT의 도움으로 내부 제어는 신호 CAS의 시간 제한에 무관하며 빠른 데이터 전송을 가능하게 한다.

제4도는 제1도에 따른 니블-페이지 모드를 수행하기 위한 또 다른 세부점을 도시한다. 회로(10,20)은 제2도 및 제3도와 관련하여 이미 설명되었다. 신호 RINT가 버퍼의 도움으로 외부 신호 레벨을 내부 신호 레벨로 변환시키므로 신호 RASNT로부터 발생됨을 유의할 수 있다. 내부 신호 CASN 및 CINT로부터 회로(30)는 출력신호 CAST를 발생하며, 상기 신호 CAST는 데이터 버스를 제어하는데 사용된다. 회로(60)는 내부 데이터 버스를 출력단과 연결시킨다. 회로(40)는 기록 제어를 구비하는데, 상기 기록제어는 외부신호 WENT로부터 내부 신호 WINT를 발생하며 버스 제어 모듈(60)을 위한 제어신호 OEI와 제어신호 WEL(기록 인에이블 랫치)를 발생하거나, 그 반전된 신호 WEIN을 발생한다. 회로(50)는 어드레스 랫치 AL 및 어드레스 포인터 AP용 제어신호를 발생한다. 신호 WINT와 함께, 내부 신호 RINT, CASN 및 CINT는 전체 데이터 전송을 제어하기 위한 일정한 신호이다.

제5도는 신호 CAST를 발생하기 위한 회로(30)의 상세회로 다이어그램이다. 두개의 제어신호 CINT 및 CASN은 게이트 NA4에서 서로 논리적으로 연결되고, 트랜지스터 T5 및 T6로 연결된 게이트를 통해 한번 지연되며, 한번 지연되지 않으면 신호 CAST인 출력신호를 갖는 또 다른 게이트 NA5로 전달된다. 제5도의 회로는, 신호 CINT의 단일신호 에지만을 유효 에지로서 선택하기 위해 사용된다.

제6도는 기록제어회로(40)를 도시한다. 외부 기록제어신호 WENT는 버퍼 B3에 의해 내부 신호 WINT로 변환된다. 버퍼 B3의 출력신호는, 실제의 기록제어회로 WCC를 제어하기 위한 플립플롭 FF2와 NAND 게이트 NA6를 통과하는 신호 RINT 및 CINT와 함께 사용되며, 상기 제어회로 WCC는 기록제어신호를 발생한다. 상기 회로 WCC를 구성하는 것은 본 기술에 속련된 사람이라면 쉬운 일이다. 버퍼 B3의 출력신호는 회로 SWC를 제어하기 위해 사용되며, 상기 회로 SWC는, 기록 인에이블 신호의 기능으로서 데이터 버스를 제어하기 위한 신호 OEI를 발생한다. NOR 게이트 N01은 신호 CASN 및 CINT를 회로 SWC에 연결시킨다.

제7도는 어드레스 제어신호 CALN 및 ENSH를 발생시키는 회로(50)를 도시한다. 신호 RINT 및 CINT는 NOR 게이트 N02에서 서로 논리적으로 연결되며, 신호 CALN을 발생하는데, 상기 신호 CALN은 어드레스 랫치회로 AL 및 제어회로 ENSH를 제어하며, 신호 CALN에 대해서 반전되며, 쉬프트 제어회로 SC를 제어하며, 상기 쉬프트 제어회로 SC는 다시 어드레스 포인터 AP의 도움으로 니블 순서를 규정한다. 플립플롭 FF3를 위한 신호 RES는 리셋트 신호로서, 내부 제어신호에 의존한다.

제8도는 회로(60)를 도시하는데, 상기 회로는 외부 버스 PUi 또는 PD<sub>i</sub>에 대한 내부 데이터 버스 DU<sub>i</sub> 또는 DDi를 제어한다. 예시된 실시예에서 버스 각각은 데이터 업, 데이터 다운, 풀업 및 풀다운을 위한 네 개의 데이터 라인을 구비한다. 내부 데이터 버스는 논리적 하이로 프리차지된다. 신호 CINT의 유효 에지에 따라 선택되는 신호 CAST 및 신호 OEI는 신호 CT를 형성하기 위해 서로 논리적으로 연결된다. 이 신호 CT는 데이터 버스와 함께 셋트/리셋트 랫치 소자 SRL1-SRL<sub>i</sub>에 대한 입력신호로서 사용된다. 이 랫치의 수는 I/O 그룹 및 데이터 라인 그룹의 수와 일치하거나, 또는 다시 말해서 예시된 실시예에서는 네개에 해당한다. 신호 OEI는 이론 기록상태가 존재하는지에 의존한다. 여기서 신호 WENT의 유효 에지는 신호 CASNT의 유효에지전에 존재한다. 이 경우에, 입/출력 라인은 트라이-스테이트 상태에 있으며, 데이터 입력 또는 출력은 허용되지 않는다. 역으로, 기록 인에이블 신호의 유효에지가 신호 CASNT의 유효 에지 후에 발생되면, 데이터 입출력이 인에이블 된다.

신호 CT가 논리 하이 포텐셜에 있으면, 접속 LU 및 출력 랫치에 대한 입력신호는 논리적 로우 포텐셜에 있으며, 그에 따라서 버스 PUi 및 PD<sub>i</sub>의 라인은 논리적 하이 포텐셜 또는 다시 말해서 프라이-스테이트 상태에 있다. 신호 CT가 논리적 로우 포텐셜에 있으면, 데이터 버스 DU 또는 DD의 신호 변화시에, 랫치 SRL<sub>i</sub> 또는 Li 중 하나가 셋트될 수 있으며, 따라서 데이터 신호는 출력 버스로 전송된다. 신호 CINT의 다음 유효 에지는, 내부데이터 버스 DU 및 DD로부터 랫치로 새로운 데이터의 채택을 가능하게 한다.

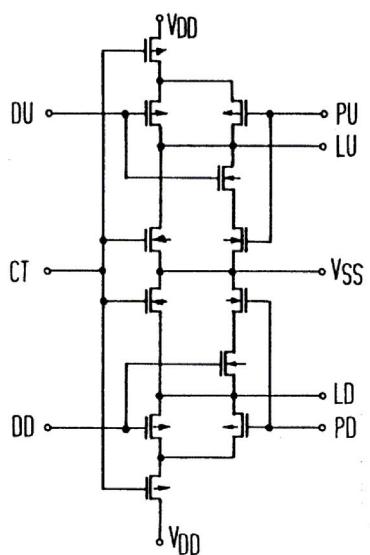

제9(a)도는 셋트/리셋트의 더 상세한 회로도를 도시한다. 제9(b)도는 어드레스 랫치의 더 상세한 회로도를 도시한다.

제10도는 종래 기술의 니블 모드를 설명하기 위해 사용되는 블록회로도를 도시한다. 하나의 니블 순서에 속하는 어드레스 ADR1-ADR4는 어드레스 포인터 AP의 버퍼 B11-B14에 존재한다. 이 버퍼는 링 회로에서 서로 연결된다. 쉬프트 제어 회로 SC는 신호 CINT 및 ENSH에 의해 제어되고 제어 신호를 버퍼로 전달한다. 니블 순서에서 네개의 결합된 메모리 셀은 동시에 버퍼 메모리로 먼저 기록되고 그후 링 제어에 따

라 연속적으로 직접 판독되는 버퍼를 통과하거나, 개별 메모리 셀은 연속적으로 직접 기록되며 상기 데이타가 출력된다.

제11도의 신호도는 이러한 공지된 니블 모드를 설명한다. 상술의 모드의 신호 CASNi 하강 신호 에지에서, 어드레스 포인터 API는 신호 CINTNi 및 ENSH의 도움으로 셋트되며, 신호 CINTNi의 하강 신호 에지에서, 클럭 신호 CK가 발생되며, 이미 셋트된 어드레스 포인터는 리셋트되며 다음 어드레스 포인터가 셋트된다. 이러한 과정은 하나의 니블 순서에 대해 네번씩 일어난다. 본 발명에 따라서, 이러한 과정은 임의의 시간 길이에 대해 순환하여 연속될 수 있다.

제13도는 니블 페이지 모드에서 판독 사이클에서의 신호를 도시하는데, 상기 신호는 출력 인에이블 신호 OE의 신호 변환에 의해 제어된다. 신호 CAS의 하강 신호 에지에서, 제1 칼럼 어드레스가 채택되거나, 신호 OE가 논리적 로우 포텐셜이므로 대응하는 메모리 셀이 규정되며 동시에 입/출력 회로가 인에이블된다. 신호 CAS 및 OE의 두 하강 신호 에지는 판독작동을 개시한다. 두개의 에지가 함께 연결되며, 이 경우에 D011에 대한 제1 판독 작용은 신호 CAS의 부의 에지에 의해 제어된다. 세개의 다음 데이터가 신호 OE의 한 에지에 의해 각각 제어된다. 이 니블 순서가 경과된 후에, 다음 칼럼 어드레스 COL2가 신호 CAS의 상승 에지에서 채택되며, 하나의 니블 순서의 결합된 데이터는 다음 하강 에지에서 판독된다. 신호 CAS는 페이지 모드를 제어하며, 각각의 페이지 간격내 니블 모드는 신호 OE에 의해 제어된다.

제14도의 기록 사이클은 제13도에서 설명된 것과 유사하게 진행된다.

제13도 및 제14도로부터, 신호 CAS로 페이지 모드를 제어하고 신호 OE의 각 신호 에지로 니블 모드를 제어하므로, 데이터 전송 속도는 자동으로 2배가 될 수 있다. 단일 니블 모드는 예시된 실시예에서 선택되었지만, 각 페이지에서 8, 16 또는 그 이상의 니블로 데이터 전송이 가능하다. 이것은 두개, 네개 또는 그 이상의 니블 순서에 해당한다.

본 발명에 따른 방법 및 메모리의 장점은 신호 CAS가, 칼럼 어드레스 스트로브 신호로서 그 원래의 결정을 위해 그리고, 데이터 출력을 트라이-스테йт 상태에 넣으므로 직렬 데이터 흐름을 파괴시키기 위해 그 표준화된 사양으로 사용될 수 있다는 것이다. 자연히, 기술된 모드는 X4조직에서의 어려움이 없이도 채택될 수 있으며, 비트 기능당 하나의 기록과 결합이 어려움없이 가능하다. 본 발명의 개념에 대한 또 다른 실시예가 본 기술에 숙련된 사람이라면 쉽게 이해할 수 있다. 신호 OE에 의해 제어되는 직렬 페이지 모드가 자연히 가능해진다. OE 신호의 두 신호 에지중 하나는 그 경우에 항상 일정하다. 증가된 데이터 속도를 갖는 증가된 페이지 길이를 얻을 수 있으며, 여기서 직렬 데이터 사이클이 CA 신호에 의해 차단될 수 있다. 상술된 예시 실시예에서와 같이, 신호 CAS는 칼럼 어드레스 채택을 제어하고, 데이터 출력은 신호 OE에 의해 제어된다. 한편, 데이터 전송이 신호 CAS 자체에 의해 제어되는 직렬 페이지 모드도 가능하다. 데이터 출력의 트라이-스테йт 상태는 신호 OE에 의해 셋트된다. 이때, 표준-페이지 모드는 사용되지 못한다. 왜냐하면, 데이터 전송이 신호 CAS에 의해 제어되고, 따라서 어드레스 채택이 어떤 시각에서만, 다시말해서 일정수의 CAS 신호가 변화된 후에만 발생할 수 있다. 그러한 목적으로 카운터가 적당히 제공된다. 니블 사이클의 차단시에 어드레스 변화를 인식하는 것이 가능하다. 마지막으로, 분리된 필스가 발생될 수 있는데, 이 필스로 새로운 어드레스가 채택될 수 있다.

## (57) 청구의 범위

### 청구항 1

메모리 셀 어드레스가 데이터 전송용 제 1 어드레스 제어 신호로 규정되는, 다수의 메모리 셀과 반도체 메모리중 적어도 하나의 입/출력 단자 사이의 데이터 전송 방법에 있어서, 메모리 셀(MA)로부터 또는 메모리 셀로의 데이터 전송 과정이 제 2 어드레스 제어 신호(CASNT) 및 출력 인에이블 제어 신호(OENT)에 의해, 두 신호중 하나가 메모리 셀 어드레스를 규정하도록 제어되는 단계, 상기 데이터 전송 과정이 두 신호의 주어진 논리 접속이 존재하는 경우에 시작되는 단계, 및 후속하는 데이터 전송이 두 신호 중 다른 하나에 의해 제어되는 단계를 포함하는 것을 특징으로 하는 데이터 전송 방법.

### 청구항 2

제1항에 있어서, 상기 규정된 메모리 셀 어드레스에서 다수의 메모리 셀에 하나의 데이터 엑세스를 수행하는 단계를 포함하는 것을 특징으로 하는 데이터 전송방법.

### 청구항 3

제1항에 있어서, 상기 제 2 어드레스 제어 신호(CASNT)의 한 신호 에지로 메모리 셀 어드레스를 규정하며, 상기 출력 인에이블 제어 신호(OENT)의 한 신호 에지로 데이터 전송을 제어하는 단계를 포함하는 것을 특징으로 하는 데이터 전송방법.

### 청구항 4

제1항에 있어서, 상기 제 2 어드레스 제어 신호(CASNT)의 각 신호 에지로 상기 메모리 셀 어드레스를 규정하며, 상기 출력 인에이블 제어 신호(OENT)의 각 신호 에지로 데이터 전송을 제어하는 단계를 포함하는 것을 특징으로 하는 데이터 전송방법.

### 청구항 5

제1항에 있어서, 상기 제 2 어드레스 제어 신호의 한 펄스 에지로, 규정된 메모리 셀 어드레스와 관련된 데이터 전송 작용을 종결시키는 단계를 포함하는 것을 특징으로 하는 데이터 전송방법.

### 청구항 6

다수의 메모리 셀, 적어도 하나의 입출력 단자, 어드레싱을 위한 수단, 제 1 어드레스 제어 신호에 의해

메모리 셀을 규정하기 위한 수단, 및 메모리 셀로부터 그리고 메모리셀로의 데이터 전송을 제어하기 위한 수단을 포함하는 반도체 메모리에 있어서, 제 2 어드레스 제어 신호(CASNT) 및 출력 인에이블 신호(OENT)가 제공되고, 상기 두 신호는 공동으로 데이터 전송 과정을 제어하며, 두 신호중 하나가 메모리 셀 어드레스를 규정하기 위하여 사용되며, 두 신호의 주어진 논리 접속 존재시 데이터 전송이 시작된 후에 이 두 신호 중 다른 하나가 데이터 전송을 제어하도록 데이터 전송 과정을 제어하는 것을 특징으로 하는 반도체 메모리.

#### 청구항 7

제6항에 있어서, 메모리 셀을 어드레스하기 위한 상기 수단은 각각의 규정된 메모리 셀 어드레스로 다수의 메모리 셀을 액세스하는 것을 특징으로 하는 반도체 메모리.

#### 청구항 8

제6항에 있어서, 상기 제 2 어드레스 제어 신호(CASNT)는 메모리 셀 어드레스를 규정하고, 상기 출력 인에이블 제어 신호(OENT)는 한번에 두개의 신호 에지중 하나로 데이터 전송을 제어하는 것을 특징으로 하는 반도체 메모리.

#### 청구항 9

제6항에 있어서, 상기 제 2 어드레스 제어 신호(CASNT)는 메모리 셀 어드레스를 규정하며, 상기 출력 인에이블 제어 신호(OENT)는 각각의 신호 에지로 데이터 전송을 제어하는 것을 특징으로 하는 반도체 메모리.

#### 청구항 10

제6항에 있어서, 규정된 메모리 셀 어드레스와 관련된 데이터 전송 작용은 상기 제 2 어드레스 제어 신호(CASNT)중 하나의 클럭 에지로 인터럽트 될 수 있는 것을 특징으로 하는 반도체 메모리.

#### 도면

##### 도면1

##### 도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9a

도면9b

도면10

도면11

도면 12

도면 13

도면 14