(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-530299

(P2005-530299A)

(43) 公表日 平成17年10月6日(2005.10.6)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

G 11 C 29/00

G 11 C 29/00

6 5 1 E

5 B 0 1 5

G 11 C 11/41

G 11 C 11/34

3 4 1 D

5 L 1 0 6

G 11 C 11/413

G 11 C 11/40

Z

審査請求 未請求 予備審査請求 未請求 (全 16 頁)

(21) 出願番号 特願2004-514085 (P2004-514085)

(86) (22) 出願日 平成15年5月7日 (2003.5.7)

(85) 翻訳文提出日 平成16年12月15日 (2004.12.15)

(86) 國際出願番号 PCT/US2003/014107

(87) 國際公開番号 WO2003/107355

(87) 國際公開日 平成15年12月24日 (2003.12.24)

(31) 優先権主張番号 10/173,229

(32) 優先日 平成14年6月17日 (2002.6.17)

(33) 優先権主張国 米国(US)

(71) 出願人 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノンド

ライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 リストン、トーマス ダブリュ.

アメリカ合衆国 78758 テキサス州

オースティン ビターン ホロー 11

916

最終頁に続く

(54) 【発明の名称】メモリにおけるソフト欠陥検出のための方法及び装置

## (57) 【要約】

S R A Mにおけるソフト欠陥を検出するための方法。メモリは、メモリアレイを形成する複数のメモリセルを含み、各メモリセルは、ビット線、相補ビット線及びワード線に接続されている。各メモリセルは、複数のトランジスタを含む。本方法は、次の段階を含む。即ち、メモリアレイを書き込む段階と、複数のビット線及び相補ビット線を所定電圧に充電することによってそれらをコンディショニングする段階であって、これらの電圧は、完全に機能するメモリセルのビット状態を変化させない段階と、所定のワード線を活性化してメモリセル行を選択する段階と、選択されたメモリセルを読み出す段階と、この読み出しの結果をメモリセルに書き込まれたビット値と比較して、いずれかのメモリセルビット状態が修正されたかどうか判断する段階と、修正されたメモリセルが試験に不合格であると特定する段階とを含む。

**【特許請求の範囲】****【請求項 1】**

メモリアレイ(10)を試験するための方法において、

複数のメモリセルで前記メモリアレイを実装する段階であって、前記メモリセルは各々複数のトランジスタを含む段階と、

前記メモリアレイを書き込む段階と、

前記メモリアレイにある複数のビット線及び相補ビット線を、前記複数のビット線及び相補ビット線各々をそれぞれ所定の第1電圧及び所定の第2電圧に充電することによって、コンディショニングする段階であって、前記所定の第1電圧及び前記所定の第2電圧は、前記メモリアレイの完全に機能するビットのビット状態を、前記完全に機能するビットがアドレス指定される時、変更しない値を有する前記段階と、

所定のワード線を活性化する段階であって、前記所定のワード線は、メモリセル行を選択し、また、前記メモリセル行にある各メモリセルの前記複数のトランジスタ全てを電気的導通状態にする前記段階と、

前記所定のワード線を読み出す段階と、

前記所定のワード線を読み出す前記段階からの結果を、前記所定のワード線に書き込まれたビット値と比較し、前記所定のワード線における何れかのメモリセルビット状態が修正されたかどうかを判断する段階と、

修正されたメモリセルが前記試験に不合格であると特定する段階と、

からなる方法。

**【請求項 2】**

請求項1に記載の方法において、更に、

同じ電圧電位を前記第1所定電圧及び前記第2所定電圧に用いる段階が含まれる方法。

**【請求項 3】**

請求項1に記載の方法において、更に、

前記所定のワード線の活性化に先立ち、前記複数のビット線各々にそのそれぞれの相補ビット線を電気的に直接接続する段階であって、前記電気的に直接接続する段階は、前記所定の第1電圧及び前記所定の第2電圧を調整してほぼ等しくする段階が含まれる方法。

**【請求項 4】**

請求項1に記載の方法において、更に、

前記各メモリセルにある前記複数のトランジスタは6つであり、2つのトランジスタが第1導電タイプであり、4つのトランジスタが第2導電タイプであるように前記メモリアレイを実装する段階が含まれる方法。

**【請求項 5】**

ビット機能試験回路を有するメモリアレイ(10)において、

複数のメモリセル(例えば、12)であって、前記メモリセルは、各々複数のトランジスタ(例えば、70、74、78、80)を含む前記複数のメモリセルと、

前記複数のメモリセルに接続され、前記メモリアレイに書き込むための回路(14、16)と、

前記メモリアレイにある複数のビット線及び相補ビット線を、前記各複数のビット線及び相補ビット線各々をそれぞれ所定の第1電圧及び所定の第2電圧に充電することによって、コンディショニングするための試験回路(18、20、21、22)であって、前記所定の第1電圧及び前記所定の第2電圧は、前記メモリアレイの完全に機能するビットのビット状態を、前記完全に機能するビットがアドレス指定される時、変更しない値を有し、前記試験回路は、また、所定のワード線を活性化し、前記所定のワード線は、メモリセル行を選択し、また、前記メモリセル行にある各メモリセルの前記複数のトランジスタ全てを電気的導通状態にし、あらゆる不良メモリセルは、前記活性化する段階に応答してビット状態を変更する前記試験回路と、

前記複数のメモリセルに接続された前記メモリセルのビット状態を出力するための手段(16)と、

10

20

30

40

50

が含まれるメモリアレイ。

【請求項 6】

請求項 5 に記載のメモリにおいて、更に、

前記出力するための手段に接続された比較手段(8)であって、書き込まれた前記所定のワード線を読み出し、また、前記所定のワード線において、いずれかのメモリセルビット状態が修正されたかどうかを判断する前記比較手段が含まれるメモリ。

【請求項 7】

請求項 5 に記載のメモリにおいて、

前記各複数のビット線及び相補ビット線をそれぞれ所定の第 1 電圧及び所定の第 2 電圧に充電する前記試験回路は、各ビット線及び相補ビット線に対して、

第 1 ビット線に接続された第 1 電流電極、第 1 制御信号を受信するための制御電極、及び第 1 基準電圧端子に接続された第 2 電流電極、を有する第 1 導電タイプの第 1 トランジスタ(30)と、

第 2 基準電圧端子に接続された第 1 電流電極、前記第 1 制御信号の相補信号を受信するための制御電極、及び前記第 1 ビット線の相補線に接続された第 2 電流電極、を有する第 2 導電タイプの第 2 トランジスタ(38)と、

前記第 1 ビット線と前記第 1 ビット線の前記相補線との間に接続され、第 2 制御信号に応答して、前記第 1 ビット線及び前記第 1 ビット線の前記相補線を選択的に電気的に接続するためのスイッチング手段(34、36)と、

からなるメモリ。

【請求項 8】

メモリアレイの欠陥を検出する方法において、

現試験状態で前記メモリアレイを書き込む段階であって、前記メモリアレイはメモリセルの行及び列を有する前記段階と、

前記メモリアレイの一部のビット線、及び前記各一部のビット線用の対応するその相補ビット線を、前記各一部のビット線をそれぞれ所定電圧に充電することによって、コンディショニングする段階と、

前記一部のビット線の各ビット線をその対応する相補ビット線に接続する段階であって、前記一部のビット線の各ビット線及びその対応する相補ビット線上の合成電圧は、前記メモリアレイの欠陥がないメモリセルのいかなるメモリ状態も修正しない前記段階と、

前記メモリの所定のワード線を活性化する段階であって、前記活性化する段階は、所定行のメモリセルにある各メモリセルの複数のトランジスタ全てを電気的導通状態にする前記段階と、

前記所定のワード線内に含まれるいずれかのビットのメモリ状態を変えさせる段階であって、このようなビットは、メモリ状態の変化の結果として欠陥がある前記段階と、が含まれる方法。

【請求項 9】

請求項 8 に記載の方法において、更に、

前記所定のワード線の活性化に先立ち、前記一部のビット線各自にそのそれぞれの相補ビット線を電気的に直接接続する段階であって、前記電気的に直接接続する段階は、前記所定の電圧を調整してほぼ等しくする前記段階が含まれる方法。

【請求項 10】

請求項 8 に記載の方法において、更に、

前記メモリアレイにある複数の所定のワード線を順次活性化して、前記複数のメモリセル各自を順次試験する段階と、

前記一部のビット線及び対応する相補ビット線を、所定のワード線に沿って同時に前記一部のビット線及び対応する相補ビット線全てに前記所定電圧を印加することによって、コンディショニングする段階と、が含まれ、

前記複数の所定のワード線を順次活性化する段階は、前記メモリが試験されていない場合の前記メモリの通常動作速度にほぼ等しい速度である方法。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、一般的に、メモリに関し、特に、メモリにおけるソフト欠陥誤り検出に関する。

## 【背景技術】

## 【0002】

メモリには、製品の出荷に先立ち、機能が適切であることを保証する試験が必要である。例えば、メモリは、ソフト欠陥の有無について試験される。ソフト欠陥とは、一般的に、ある条件下で現れ、他の条件下では現れない欠陥を指す。例えば、ソフト欠陥は、特定の電圧、温度、及び時間でのみ現れることがある。これらのソフト欠陥は、したがって、検出が困難である。ソフト欠陥を検出するための1つの既知の方法は、S R A M (静的ランダムアクセスメモリ) セルを試験する場合、それらに所定のデータを書き込み、ある待機期間の後、それらを読み出すことによって試験を行う。しかしながら、全ての異常なメモリセルを確実に不合格にするために、この待機期間は、相対的に長くなければならず、このことによって試験時間が長くなる。したがって、試験のために長い待機期間を要するいずれの試験手法も、試験コストが大きくなる。更に、上述の方法は、全てのソフト欠陥を捕らえることができない。したがって、試験コストを低減し、試験時間を改善するソフト欠陥検出手法の改善に対するニーズが存在する。

10

## 【発明を実施するための最良の形態】

20

## 【0003】

本発明は、付随する図によって、一例として例示するものであって、これらによって限定されるものではない。図では、同様な参照符号は、同様な要素を示す。

図の要素は簡単明瞭に示されており、必ずしも縮尺通りに描かれていないことを当業者は認識されたい。例えば、図の要素の寸法には、本発明の実施形態の理解を改善する一助とするために、他の要素と比較して誇張したものがある。

## 【0004】

本明細書で用いる用語“バス”は、データ、アドレス、制御、又は状態等の1つ以上の様々な種類の情報を伝達するために用い得る複数の信号又は配線を指すために用いられる。本明細書で述べる配線は、単一の配線、複数の配線、单方向の配線、又は双方向の配線であることを参考して図示又は記述し得る。しかしながら、異なる実施形態では、配線の実装が変わることがある。例えば、双方向の配線よりむしろ個別の单方向の配線を用いることがあり、また逆の場合もある。また、多数の信号を直列に又は時分割多重方式で伝達する単一の配線で複数の配線を置き換えることもある。同様に、多数の信号を搬送する単一の配線を分離して、これらの信号の一部を搬送する様々な異なる配線にすることがある。したがって、信号を伝達するための数多くのオプションが存在する。

30

## 【0005】

用語“アサート”及び“ネゲート”(又は“ディアサート”)は、それぞれ、信号、状態ビット、又は同様な装置をその論理的に真(true)の又は論理的に偽(false)の状態にすることを指す場合に用いられる。論理的に真の状態が論理レベル1であれば、論理的に偽の状態は、論理レベル0である。また、論理的に真の状態が論理レベル0であれば、論理的に偽の状態は、論理レベル1である。また、本明細書に述べる実施形態では、信号が“ハイ”(high)状態であることによって論理レベル1を指し、信号が“ロー”(low)状態であることによって論理レベル0を指す。

40

## 【0006】

括弧は、バスの配線又はある値のビット位置を示すために用いられる。例えば、“バス60[0-7]”又は“バス60の配線[0-7]”は、バス60の8つの下位配線を示し、“アドレスビット[0-7]”又は“アドレス[0-7]”は、アドレス値の8つの下位ビットを示す。数字の前にある記号“\$”は、その数字が16進数又は16を基数とする形式で表現されていることを示す。数字の前にある記号“%”は、その数字が2進数

50

又は2を基數とする形式で表現されていることを示す。

【0007】

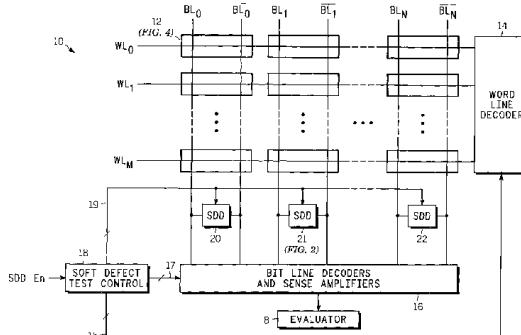

図1は、本発明の一実施形態に基づくメモリ10をブロック図形式で示す。例えば、一実施形態において、メモリ10(メモリアレイ10とも呼ぶ)は、SRAMである。しかしながら、他の実施形態では、本明細書で議論するソフト欠陥検出(SDD)手法は、あらゆる種類のメモリに適用し得る。更に、メモリ10は、組み込み式メモリ又はスタンダードアロン式メモリのいずれをも指し得る。メモリ10には、M+1のワード線WL<sub>0</sub>乃至WL<sub>M</sub>及びN+1対のビット線BL<sub>0</sub>、BL<sub>0</sub>バー乃至BL<sub>N</sub>、BL<sub>N</sub>バーが含まれる。(図面では、相補ビット線BL<sub>x</sub>バーは、BL<sub>x</sub>の上に横棒を付けて表記することに留意されたい)。したがって、メモリ10は、M+1行及びN+1列を有する(M+1)×(N+1)メモリである。各ビット線対及びワード線の交点には、メモリセル12のようなメモリセル(又はビットセル)がある。メモリ10は、したがって、任意の数の行及び列を含み得る。

【0008】

ワード線WL<sub>0</sub>乃至WL<sub>M</sub>は、各ワード線に接続されたワード線デコーダ14によって選択される。例えば、ワード線デコーダは、アドレスビットを受信してワード線の1つを選択し得る。ビット線対は、ビット線デコーダ・センス増幅器16に接続される。また、ビット線デコーダ・センス増幅器16は、静的に又は動的にビット線対を所定の電圧にプリチャージし得るビット線プリチャージ回路を含み得る。例えば、各ビット線は、Vddにプリチャージでき、また、各相補ビット線(ビット線バー)も、Vddにプリチャージし得る。通常動作モードでの読み出し時、ワード線が活性化されると、選択された各ビットセルに記憶された値は、対応するビット線対に印加される。対応するビット線対に接続されたセンス増幅器は、選択されたビットセル内における値を検出するために用いられる。一実施形態において、センス増幅器は、メモリ10の各ビット線対に接続し得る。しかしながら、他の実施形態では、一群のビット線対が、マルチブレクサ等のスイッチング回路を用いることによって、単一のセンス増幅器を共有し得る。通常動作モードでの書き込み時、ワード線が活性化されると、ビット線デコーダ・センス増幅器16内の書き込み回路によって、選択されたビット線及びその相補線のデータ状態は、反対になり、こうして対応するビットセルが、値を記憶する。

【0009】

また、メモリ10には、SDDモードで動作するための回路が含まれる。また、メモリ10には、各対のビット線の間にSDDビット線コンディショニング回路20、21、及び22が含まれる。即ち、SDDビット線コンディショニング回路20は、BL<sub>0</sub>とBL<sub>0</sub>バーとの間に接続され、SDDビット線コンディショニング回路21は、BL<sub>1</sub>とBL<sub>1</sub>バーとの間に接続され、SDDビット線コンディショニング回路22は、BL<sub>N</sub>とBL<sub>N</sub>バーとの間に接続される。(各ビット線対には、ビット線及び相補ビット線が含まれ、この場合、ビット線がBL<sub>x</sub>を指す場合、相補ビット線は、BL<sub>x</sub>バーを指し、ビット線がBL<sub>x</sub>バーを指す場合、相補ビット線は、BL<sub>x</sub>を指すことに留意されたい)。メモリ10には、SDDイネーブル信号SDD\_Enを受信し、また、制御信号を、配線15を介してワード線デコーダ14に、配線17を介してビット線デコーダ・センス増幅器16に、配線19を介して(コンディション回路20、21、及び22を含む)各SDDビット線コンディショニング回路に供給するソフト欠陥試験制御装置18が含まれる。SDDモードで動作する場合、SDD\_Enがアサートされる。SDDモード時、ビット線プリチャージ回路16は、ディスエーブル状態にされる。SDDモード時、マルチブレクサは、ビット線デコーダ・センス増幅器16内に存在する場合、ディスエーブル状態にされたりされなかつたりする。また、SDDモード時、ワード線デコーダ14の機能は、ソフト欠陥試験制御装置18によって制御される。

【0010】

一実施形態において、SDDモードには、充電段階、短絡段階、及びワード線活性化段階が含まれる。充電段階及び短絡段階は、組合せて、ビット線コンディショニング段階と

10

20

30

40

50

称し得ることに留意されたい。充電段階時、ソフト欠陥試験制御装置 18 は、(配線 19 を介して) コンディショニング回路 20、21、及び 22 に SDD\_充電信号を供給する。SDD\_充電信号に応答して、各コンディショニング回路 20、21、及び 22 は、その対応するビット線を第 1 所定電圧に、その相補ビット線を第 2 所定電圧に接続する。例えば、一実施形態において、(図 2 を参照して詳細に述べるように)、対応するビット線は Vss に、相補ビット線は Vdd に接続される。他の選択肢として、ビット線は Vdd に、相補ビット線は Vss に接続し得る。更に他の実施形態において、第 1 及び第 2 所定電圧として任意の電圧を用い得る。(本明細書で用いる Vdd は Vss より大きく、この場合、一実施形態において、Vss は接地を指し、Vdd は電源電圧を指す。したがって、Vdd 及び Vss は、各々、電源電圧とも称し得ることに留意されたい)。

10

## 【0011】

充電段階に続く短絡段階時、各コンディショニング回路 20、21、及び 22 は、対応するワード線の活性化の際、ビット線と相補ビット線との間の電圧レベルを平均化するために、配線 19 を介してソフト検出試験制御装置 18 から受信される SDD\_短絡信号に応答して、その対応するビット線をその対応する相補ビット線に接続する。一実施形態において、その結果得られるビット線及び相補ビット線の平均電圧レベルは、VDD/2 である。その結果得られた平均電圧レベルによって、活性化されたビットセル内の各トランジスタは、ワード線が活性化されると(即ち、アドレス指定されると)、電気的導通状態になる。各トランジスタが電気的導通状態であれば、任意のトランジスタ内におけるソフト欠陥を検出し得る。一例について、図 4 に示す SRAM\_6T セルを参照して説明する。

20

## 【0012】

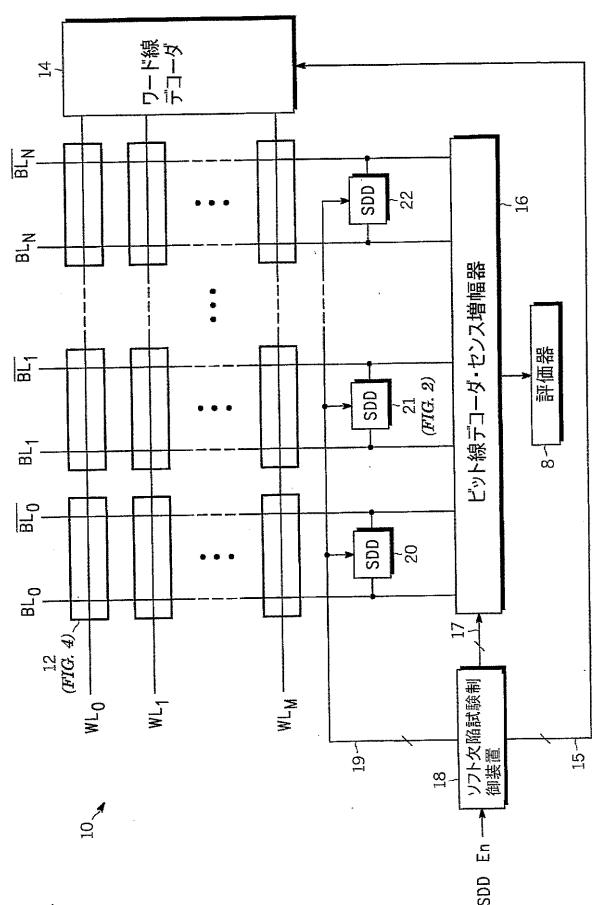

上述したように、充電及び短絡段階は、コンディショニング回路 20、21、及び 22 によって行われる。図 2 は、本発明の一実施形態に基づくコンディショニング回路 21 を示す。(コンディショニング回路 21 に関してここで与えられた同じ説明がコンディショニング回路 20 及び 22 に適用されることに留意されたい)。図 2 のコンディショニング回路 21 には、BL<sub>1</sub> と BL<sub>1</sub> バーとの間に接続された伝達ゲート 37 が含まれ、この場合、伝達ゲートには、N MOS トランジスタ 34 に接続された PMOS トランジスタ 36 が含まれる。即ち、トランジスタ 36 の第 1 電流電極は、ノード 31 において、トランジスタ 34 の第 1 電流電極及び BL<sub>1</sub> に接続される。トランジスタ 36 の第 2 電流電極は、ノード 35 において、トランジスタ 34 の第 2 電流電極及び BL<sub>1</sub> バーに接続される。トランジスタ 34 の制御電極は、ソフト欠陥試験制御装置 18 から SDD\_短絡を受信するために接続され、また、インバータ 33 の入力に接続される。インバータ 33 の出力は、トランジスタ 36 の制御電極に接続される。また、コンディショニング回路 21 には、ノード 31 に接続される第 1 電流電極と、Vss に接続される第 2 電流電極と、ソフト欠陥試験制御装置 18 から SDD\_充電を受信するために接続される制御電極とを有する NMOS トランジスタ 30 が含まれる。また、トランジスタ 30 の制御電極は、インバータ 40 の入力に接続される。また、コンディショニング回路 21 には、Vdd に接続される第 1 電流電極と、ノード 35 に接続される第 2 電流電極とを有する PMOS トランジスタ 38 が含まれる。インバータ 40 の出力は、トランジスタ 38 の制御電極に接続される。

30

## 【0013】

動作時、トランジスタ 30 及び 38 は、SDD\_充電がアサートされることに応答して、Vss を BL<sub>1</sub> に、また、Vdd を BL<sub>1</sub> バーに接続することによって充電段階を行う。SDD\_充電がディアサートされた後、トランジスタ 36 及び 34 を介して、BL<sub>1</sub> と BL<sub>1</sub> バーとの間の電荷を等しくするために、SDD\_短絡がアサートされる。電荷が等しくなった後、SDD\_短絡は、ディアサートし得る。しかしながら、他の実施形態では、ワード線活性化段階時、SDD\_短絡は、アサートされた状態に維持し得るが、これについて後述する。また、様々な異なる回路を用いて、図 2 の例と同じ又は同様な機能を実現し得ることに留意されたい。

40

## 【0014】

50

充電段階に続くワード線活性化段階時、選択されたワード線（例えば、 $WL_0$ ）が、活性化される（即ち、アドレス指定される）。即ち、ソフト欠陥試験制御装置18は、制御信号をワード線デコーダ14に供給して、選択されたワード線を活性化する。選択されたワード線の活性化の際、完全に機能するピットセル（即ち、ソフト欠陥が全くないピットセル）は、状態が変わらない。しかしながら、活性化されたワード線に沿う好適な状態でない欠陥ピットセルは、いずれも状態が変わる。例えば、図1のピットセル12の好適な状態が1であり（ピットセル12はソフト欠陥を含むと仮定して）、また、（ $WL_0$ の活性化に先立ち）0が書き込まれて試験を行う場合、 $WL_0$ を活性化すると、（0から1への）状態変化が起こる。しかしながら、ピットセル12に1が書き込まれて試験を行う場合、 $WL_0$ を活性化すると、状態変化は起こり得ない。したがって、幾つかの実施形態において、ピットセル12の試験を完全に行うために、充電、短絡、及び活性化は、状態0及び1の双方を用いて行うべきであり、これについては、図3のフロー図を参照して更に詳細に説明する。上述したように、ワード線活性化段階時、 $BL_0$ 及び $BL_0$ バーは、実施形態に依存して、互いにまだ接続していてもそうでなくてもよい。

10

20

30

40

50

## 【0015】

ワード線活性化段階後、更にワード線の試験を行う必要がある場合、充電、短絡、及びワード線活性化段階は繰り返してよく、この場合、ワード線活性化段階では、新しいワード線が選択され活性化される。一実施形態において、状態機械を用いて、様々な段階間での遷移を実現し得る。他の選択肢として、メモリ12のピットセルを循環するために用いられる外部アドレスが、様々な段階を循環するために用い得る。例えば、外部アドレスの2つの最下位ピットは、3段階を循環するために用い得る。

## 【0016】

上述したように、充電及び短絡段階は、一括してコンディショニング段階と称し得る。他の実施形態は、したがって、様々な異なる方法でコンディショニング段階を実施でき、また、上述した充電及び短絡段階に限定されない。例えば、他の実施形態において、上述した充電及び短絡段階を行うことよりもむしろ、各ピット線及び相補ピット線は、同じ電圧電位に接続し得る。即ち、コンディショニング段階時、ワード線活性化段階に先立ち、各ピット線及び相補ピット線は、異なる所定電圧に各々接続して互いに短絡するよりもむしろ、同じ電圧電位に接続し得る。したがって、コンディショニング段階時、ピット線及び相補ピット線は、活性化されたピットセル内の各トランジスタが電気的導通状態になる電圧電位に設定される。しかしながら、各ピットセルは、値を記憶するためのトランジスタ並びに記憶された値をアクセスするためのトランジスタを含み得ることに留意されたい。ソフト欠陥は、SDDモード時、値を記憶するためのトランジスタ全てが電気的導通状態であると、値を記憶するためのあらゆるトランジスタにおいて検出し得る。

## 【0017】

また、図1には、メモリ10のピット線デコーダ・センス増幅器16から情報を受信するために、また、その結果を分析して、いずれか欠陥ピットセルが存在するかどうか判断するために、接続された評価器8が含まれる。評価器8は、メモリ10付きチップの上に配置してよく、又は外部分析器もしくはテスタであってよい。例えば、評価器8は、備付けのセルフテスタ（BIST）、機能パターン、又は外部のプログラム可能なテスタであってよい。また、評価器8は、専用分析器又は非専用分析器であってよい。動作時、評価器8は、（コンディショニング及びワード線活性化段階後）メモリアレイ10内の値を（コンディショニング及びワード線活性化段階に先立ち）メモリアレイ10に元々書き込まれた値と比較して、欠陥があるピットセルの存在を判断する。例えば、この比較での不整合は、欠陥があるピットセルを示す。

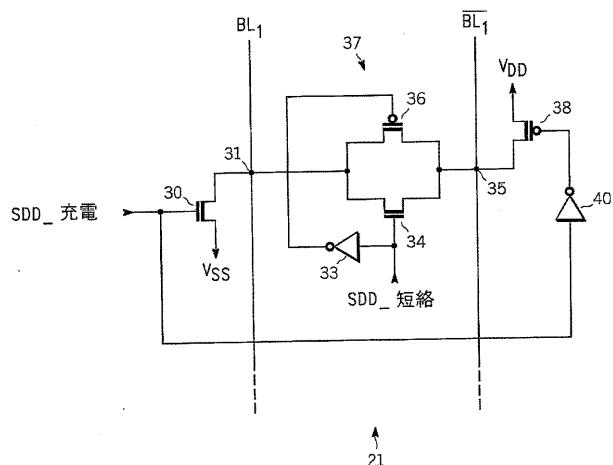

## 【0018】

図3は、SDD法の一実施形態をフロー図形式で示す。図3のフローは、40で始まり、ブロック42に進み、ここで、メモリアレイ10には、現在の試験状態が書き込まれる。例えば、メモリアレイ10には、全て1もしくは全てゼロを、又は任意の試験パターンを書き込み得る。フローは、ブロック44に進み、ここで、選択されたピット線がコンデ

イショニングされる（即ち、コンディショニング段階）。例えば、上述したように、S R A Mセルを用いる実施形態において、選択されたビット線対（各々ビット線及び相補ビット線を有する）は、このステップでコンディショニングされる。一実施形態において、1つのビット線又はビット線対をコンディショニングしてもよく、又は（例えば、同じワード線に沿う一群のビット線対等の）一群のビット線もしくはビット線対をコンディショニングしてもよい。一実施形態において、上述したように、ビット線のコンディショニングには、それぞれ、各ビット線及びその対応する相補ビット線を第1及び第2所定電圧に充電することが含まれる（即ち、充電段階）。例えば、上記例において、ビット線はV<sub>ss</sub>に、相補ビット線はV<sub>dd</sub>に充電し得る。また、本実施形態では、ビット線のコンディショニングには、各ビット線をその対応する相補ビット線に接続すること（即ち、短絡段階）が含まれる。これによって、ビット線と相補ビット線との間の電荷が等しくなる。しかしながら、上述したように、様々な異なる方法を用いて、コンディショニング段階を行うことができる。

#### 【0019】

次に、フローは、ブロック46に進み、ここで、所定のワード線が活性化され（即ち、ワード線活性化段階）、これによって、存在する場合、欠陥があるビットセルは状態が変化する。次に、フローは、判断ひし形48に進み、ここで、活性化すべきワード線が更に存在するかどうか判断する。そうである場合、フローは、ブロック44に戻り、ここで、（異なるワード線に沿う一群のビット線等の）他のビット線又は一群のビット線がコンディショニングされ、ブロック46では、新しいワード線が活性化される。したがって、一実施形態において、ワード線は、順次循環され、この場合、ループ（即ち、ブロック44及び46）を一巡する度に、現ワード線に沿う全てのビット線がコンディショニングされる。

#### 【0020】

判断ひし形48において、活性化すべきワード線が更に残っていない場合、フローは、ブロック50に進み、ここで、メモリアレイ10が読み出され、現在の試験状態と比較され、メモリアレイ10の機能が判断される。例えば、評価器8は、メモリアレイ10を読み出して、メモリアレイ10の新しい内容を判断し得る。次に、これらの新しい内容は、メモリアレイ10に元々書き込まれていた現試験状態と比較される。不整合が存在する場合、欠陥があるビットセルが示される。次に、フローは、判断ひし形52に進み、ここで、試験すべき試験状態が更に存在するかどうか判断される。そうである場合、フローは、ブロック54に進み、ここで、試験すべき次の試験状態が現在の試験状態として与えられ、そして、フローは、ブロック42に進む。例えば、最初の現試験状態が全てゼロであった場合、次の試験状態は、全てのビットセルが論理1及び論理ゼロで完全に評価されるように、メモリアレイ10に全て1を書き込むことに対応し得る。他の選択肢として、3つ以上の試験状態を用いてもよく、この場合、図3のフローは、3回以上実行される。他の選択肢として、1つの試験状態だけを用いてもよい。（判断ひし形52において）一旦全ての試験状態が試験されると、フローは、終了56で終わる。

#### 【0021】

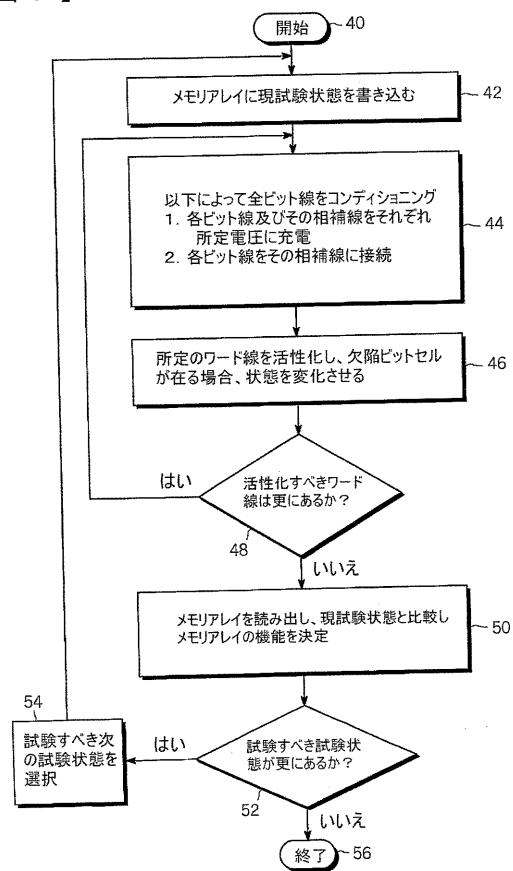

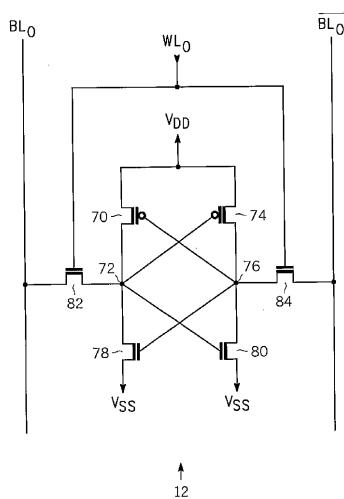

図4は、図1のビットセル12の一例を概略図形式で示す。図4の例において、ビットセル12は、本発明の一実施形態に基づく6T\_S R A Mセルである。ビットセル12には、トランジスタ70、74、78、及び80、並びにアクセストランジスタ82及び84が含まれる。アクセストランジスタ82の第1電流電極はB<sub>L</sub>に接続され、アクセストランジスタ82の第2電流電極はノード72に接続される。アクセストランジスタ82の制御電極は、W<sub>L</sub>に接続される。トランジスタ70の第1電流電極及びトランジスタ74の第1電流電極はV<sub>dd</sub>に接続され、トランジスタ70の第2電流電極及びトランジスタ74の制御電極はノード72に接続される。トランジスタ74の第2電流電極及びトランジスタ70の制御電極は、ノード76に接続される。トランジスタ78の第1電流電極はノード72に接続され、トランジスタ78の第2電流電極はV<sub>ss</sub>に接続され、トランジスタ78の制御電極はノード76に接続される。トランジスタ80の第1電流電極は

10

20

30

40

50

ノード 7 6 に接続され、トランジスタ 8 0 の第 2 電流電極は  $V_{SS}$  に接続され、トランジスタ 8 0 の制御電極はノード 7 2 に接続される。アクセストランジスタ 8 4 の第 1 電流電極はノード 7 6 に接続され、アクセストランジスタ 8 4 の第 2 電流電極は  $BL_0$  バーに接続され、アクセストランジスタ 8 4 の制御電極は  $WL_0$  に接続される。一実施形態において、トランジスタ 7 0 及び 7 4 は、PMOSトランジスタであり、トランジスタ 7 8、8 0、8 2、及び 8 4 は、NMOSトランジスタである。

#### 【0022】

動作時、6T-SRAMセルは、当分野で知られているように動作する。即ち、ノード 7 2 及び 7 6 は、ビットセル用の対応するワード線を介して活性化されるアクセストランジスタ 8 2 及び 8 4 を介してアクセスし得る（読み出し又は書き込み得る）値を記憶する。したがって、トランジスタ 7 0、7 4、7 8、及び 8 0 は、値を記憶するように動作し、一方、トランジスタ 8 2 及び 8 4 は、記憶された値をアクセスするために用いられる。しかしながら、アクセストランジスタ 8 2 及び 8 4 は、アクティブ状態である場合、記憶された値の記憶を支援するようにも動作することに留意されたい。更に、アクセストランジスタ 8 2 及び 8 4 がアクティブ状態である場合、トランジスタ 7 0 及び 7 4 は、必要でないことがある。

#### 【0023】

上述したように、SDDモードのコンディショニング段階の間、 $WL_0$  の活性化時、トランジスタ 7 0、7 4、7 8、及び 8 0 を確実に電気的導通状態にするために、 $BL_0$  及び  $BL_0$  バー上の電荷は、（充電及び短絡段階を介して）等しくするか同じ電圧に設定される。例えば、ビット線及び相補ビット線上の電荷を等しくする一実施形態において、平均電圧レベルは、全てのトランジスタ 7 0、7 4、7 8、及び 8 0 を電気的導通状態にする  $V_{DD}/2$  である。したがって、 $WL_0$  の活性化時、直列接続されたトランジスタ 7 0 及び 7 8 並びに直列接続されたトランジスタ 7 4 及び 8 0 は、導通状態である（この場合、説明例では、トランジスタ 7 0 及び 7 8 並びにトランジスタ 7 4 及び 8 0 の導電タイプは、反対である）。

#### 【0024】

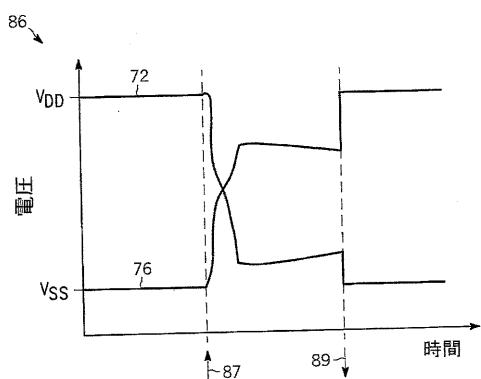

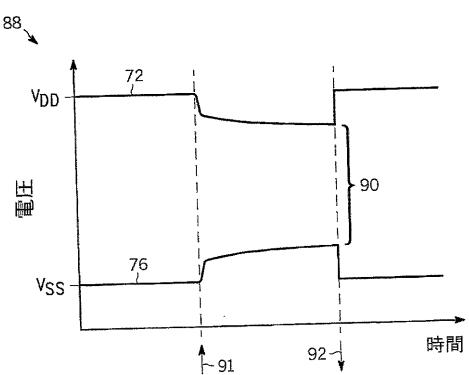

ビットセル 1 2 に欠陥が存在しない場合、ビット線のコンディショニング及び対応するワード線の活性化によって、記憶された値の状態は変化しない。例えば、図 6 は、ノード 7 2 の電圧及びノード 7 6 の電圧に対応する波形を示す。ノード 7 2 の電圧が元々高く（ $V_{DD}$  に対応）、またノード 7 6 の電圧が元々低い（ $V_{SS}$  に対応）場合、ビットセル 1 2 は、論理レベル 1 を記憶する。図 6 において矢印 9 1 で示す  $WL_0$  の活性化の際、アクセストランジスタ 8 2 及び 8 4 が活性化され、トランジスタ 8 4 及び 8 0 を介して電流が流れるにつれて、トランジスタ 8 0 の電圧が高くなるため、ノード 7 6 の電圧が上昇する。 $BL_0$  が  $V_{DD}/2$  である場合、トランジスタ 7 0 及び 8 2 を介して、 $V_{DD}$  から電流がプルされるため、ノード 7 2 の電圧は降下する。ノード 7 2 及び 7 6 の電圧は、最終的には、定常状態値に達する。対応するワード線が非活性化されると（図 6 において矢印 9 2 で示す）、ノード 7 2 及び 7 6 の電圧は、ワード線の活性化に先立ち記憶された状態と同じ状態に対応する元の値にそのまま戻る。即ち、ビットセル 1 2 の状態は変化しない。また、図 6 の電圧 9 0 の差異は、堅牢な動作を保証するのに充分な程大きいままであるべきことに留意されたい。即ち、差異 9 0 が小さくなり過ぎると、ビットセル 1 2 は、プロセス変動に敏感になり過ぎることがある。

#### 【0025】

しかしながら、トランジスタ 7 0、7 4、7 8、及び 8 0 のいずれかが欠陥を含む場合、ビット線のコンディショニング、及び対応するワード線の後続の活性化によって、状態変化が起こり、図 5 を参照して後述するように、欠陥の存在が示される。図 5 は、ビットセル 1 2 に欠陥があると仮定（本例では、トランジスタ 7 0 に欠陥があると仮定）して、ノード 7 2 の電圧及びノード 7 6 の電圧に対応する波形を示す。図 6 のように、ノード 7 2 の電圧が、元々高く（ $V_{DD}$  に対応し）、また、ノード 7 6 の電圧が元々低い（ $V_{SS}$  に対応する）場合、ビットセル 1 2 は、論理レベル 1 を記憶する。図 5 の矢印 8 7 で示す

10

20

30

40

50

W L<sub>0</sub> の活性化時、アクセストランジスタ 8 2 及び 8 4 が活性化される。本例では、トランジスタ 7 0 に欠陥があると見なされることから（抵抗性の欠陥又はオープン状態）、ノード 7 2 の電圧は、ビットセル 1 2 が不安定になることによって状態が変化するのに充分な程大きい量だけ降下する。例えば、ノード 7 2 の電圧の降下が大き過ぎる場合、トランジスタ 8 0 の導通電流は、減少し始め、トランジスタ 7 4 の導通電流は大きくなる。これによって、トランジスタ 7 8 の導通電流は更に大きくなり、この電流は、ビットセル 1 2 に記憶された値を最終的に破壊することがある。また、ノード 7 6 の電圧は、前述したように、トランジスタ 7 4 の導通電流が大きくなるため、上昇する。図 5 で分かるように、欠陥があるトランジスタ 7 0 は、状態が変化する。したがって、（図 5 で矢印 8 9 によって示す）対応するワード線の非活性化時、ビットセル 1 2 は、異なる状態（例えば、論理レベル 0）を記憶する。

10

#### 【0026】

いずれか 1 つ又は複数のトランジスタ 7 0、7 4、7 8、及び 8 0 における何らかの欠陥は、欠陥がある 1 つの又は複数のトランジスタに起因するビットセルにおける不安定性により、ビットセル 1 2 の状態変化をもたらすことに留意されたい。また、対応するワード線の活性化時、この状態変化が起こり、これによって、ソフト欠陥の有無に対するアットスピード試験が可能になることに留意されたい。（アットスピード試験とは、メモリ 1 0 の通常動作速度とほぼ同じ速度での試験を意味する）。即ち、（欠陥が存在すると仮定して）状態変化は、ワード線活性化に応答して即座に発生することから、ワード線の活性化後の長い待機時間は、不要である。また、波形が論理レベル 1 よりもむしろ論理レベル 0 を初期的に記憶することに対応するように、活性化矢印 8 7 及び 9 1 の前に、ノード 7 2 の電圧が低く、また、ノード 7 6 の電圧が高くなるように、図 5 及び 6 の波形を反転し得ることに留意されたい。この場合、図 6 では、無欠陥のビットセルを仮定すると、非活性化矢印 9 2 後の波形は、依然として論理レベル 0 に対応し、また、図 5 では、欠陥があるビットセルを仮定すると、非活性化矢印 8 9 後の波形は、変化した状態、即ち、論理レベル 1 に対応する。

20

#### 【0027】

本明細書で述べた S D D 法は、多数のビットセルに並列に用い得ることに留意されたい。例えば、選択されたワード線に沿う全てのビットセルは、並列にコンディショニングして、後続のワード線活性化を行い得る。このようにして、単一のワード線の活性化は、多数のビットセルに影響を及ぼし、これによって更に試験時間が低減される。幾つかの実施形態では、ピーク（又は動的）電流は、メモリの通常動作時引き出される電流よりも大きい電流をコンディショニング段階で引き出さないように制御し得る。

30

#### 【0028】

本発明について、特定の導電タイプ又は電位極性に関して説明したが、当業者は、導電タイプ及び電位極性を反対にしてもよいことを理解されたであろう。更に、例示したものとは異なる回路要素を用いてもよい。また、異なるトランジスタタイプを様々な回路に用いてもよい。本明細書で述べた方法は、ハードウェアもしくはソフトウェアで、又はハードウェア及びソフトウェアの組合せで実施してもよい。また、上述した方法の一部は、ファームウェアで実現してもよい。また、本明細書で述べた方法は、単一の集積回路内で又は集積回路の組合せで実施してもよい。例えば、メモリアレイは、集積回路に配置でき、また、評価器 8 は、同じ集積回路内に、又は異なる集積回路内に配置し得る。また、図 3 のフロー図内のブロックは、異なる順番で実施してもよく、あるいは、含まれるステップは例示したものよりも多く又は少なくてもよい。

40

#### 【0029】

前述の明細書では、特定の実施形態を参照して、本発明について説明した。しかしながら、当業者は、以下の請求項に記載した本発明の範囲から逸脱することなく、様々な修正及び変更をなし得ることを理解されるであろう。したがって、明細書及び図は、限定的でなく例示的であると見なすものとし、また、このような全ての修正は、本発明の範囲内に含まれるものとする。

50

【 0 0 3 0 】

恩恵、他の利点、及び問題に対する解決策について、特定の実施形態に関して上述してきた。しかしながら、恩恵、他の利点、問題に対する解決策、及び何らかの恩恵、利点、又は解決策を生じるもしくはより顕著にするあらゆる要素（1つ又は複数）は、全ての請求項の決定的な、必要な、もしくは不可欠な特徴又は要素と解釈してはならない。本明細書において用いられる用語“含む”、“含んでいる”又は他のあらゆるその派生語は、非排他的な包括を網羅し、したがって要素の一覧を含むプロセス、方法、品目、又は装置は、それらの要素だけを含むのではなく、明確に一覧化されていない他の要素又はこのようなプロセス、方法、品目、もしくは装置に固有な他の要素も含むことを意図する。

### 【図面の簡単な説明】

〔 0 0 3 1 〕

【図1】本発明の一実施形態に基づくメモリをブロック図形式で示す図。

【図2】本明発の一実施形態に基づく図1の短絡及び充電回路を概略図形式で示す図。

【図3】本発明の一実施形態に基づくソフト欠陥検出方法を図3-1図形式示す図。

【図4】本発明の一実施形態に基づくSRAMセルを概略図形式で示す図。

【図5】本発明の様々な実施形態に基づく図4のSRAMセルに対応する電圧波形をグラフ形式で示す図。

【図6】本発明の様々な実施形態に基づく図4のSRAMセルに対応する電圧波形をグラフ形式で示す図。

〔 図 1 〕

【図2】

【図3】

【図4】

FIG. 4

【図5】

【図6】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                    | Inte<br>nal Application No<br>PCT/US 03/14107                                  |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------|------|---|--------------------------------------------------------------------------------------------------------------|-------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 G11C29/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G11C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="text-align: left; padding: 2px;">US 5 255 230 A (CHAN JAMES ET AL)<br/>19 October 1993 (1993-10-19)<br/>column 5, line 48 -column 6, line 23;<br/>figures 1,3<br/>-----</td> <td style="text-align: center; padding: 2px;">1-10</td> </tr> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="text-align: left; padding: 2px;">US 2001/053102 A1 (SALTERS ROELOF HERMAN WILLEM) 20 December 2001 (2001-12-20)<br/>abstract; claim 1<br/>-----</td> <td style="text-align: center; padding: 2px;">1-10<br/>-/-</td> </tr> </tbody> </table> |                                                                                                                                    |                                                                                | Category | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 5 255 230 A (CHAN JAMES ET AL)<br>19 October 1993 (1993-10-19)<br>column 5, line 48 -column 6, line 23;<br>figures 1,3<br>----- | 1-10 | X | US 2001/053102 A1 (SALTERS ROELOF HERMAN WILLEM) 20 December 2001 (2001-12-20)<br>abstract; claim 1<br>----- | 1-10<br>-/- |

| Category                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Citation of document, with indication, where appropriate, of the relevant passages                                                 | Relevant to claim No.                                                          |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 5 255 230 A (CHAN JAMES ET AL)<br>19 October 1993 (1993-10-19)<br>column 5, line 48 -column 6, line 23;<br>figures 1,3<br>----- | 1-10                                                                           |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 2001/053102 A1 (SALTERS ROELOF HERMAN WILLEM) 20 December 2001 (2001-12-20)<br>abstract; claim 1<br>-----                       | 1-10<br>-/-                                                                    |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    | <input checked="" type="checkbox"/> Patent family members are listed in annex. |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| * Special categories of cited documents :<br>*A* document defining the general state of the art which is not considered to be of particular relevance<br>*E* earlier document but published on or after the international filing date<br>*L* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>*O* document referring to an oral disclosure, use, exhibition or other means<br>*P* document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.<br>*8* document member of the same patent family                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |                                                                                |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| Date of the actual completion of the international search<br><br>21 August 2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    | Date of mailing of the international search report<br><br>11/09/2003           |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

| Name and mailing address of the ISA<br><br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel: (+31-70) 340-2040, Tx. 31 651 epo nl<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    | Authorized officer<br><br>Ríos Báez, A                                         |          |                                                                                    |                       |   |                                                                                                                                    |      |   |                                                                                                              |             |

## INTERNATIONAL SEARCH REPORT

Int. Application No.

PCT/US 03/14107

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                                                    |                       |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                 | Relevant to claim No. |

| X                                                    | <p>MEIXNER A ET AL: "WEAK WRITE TEST MODE: AN SRAM CELL STABILITY DESIGN FOR TEST TECHNIQUE"<br/>           PROCEEDINGS OF THE INTERNATIONAL TEST CONFERENCE. WASHINGTON, OCT. 20 -24, 1996, NEW YORK, IEEE, US,<br/>           20 October 1996 (1996-10-20), pages 309-318, XP000799923<br/>           ISBN: 0-7803-3541-4<br/>           Page 311, right column</p> <p>-----</p> | 1, 4-6                |

| A                                                    | <p>US 6 108 257 A (DAVIES THOMAS J)<br/>           22 August 2000 (2000-08-22)<br/>           abstract; figure 3</p> <p>-----</p>                                                                                                                                                                                                                                                  | 1-10                  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

|                 |                          |

|-----------------|--------------------------|

| Int'l           | onational Application No |

| PCT/US 03/14107 |                          |

| Patent document cited in search report |    | Publication date |                | Patent family member(s)                  |  | Publication date                       |

|----------------------------------------|----|------------------|----------------|------------------------------------------|--|----------------------------------------|

| US 5255230                             | A  | 19-10-1993       | JP             | 5304266 A                                |  | 16-11-1993                             |

| US 2001053102                          | A1 | 20-12-2001       | CN<br>WO<br>EP | 1386283 T<br>0186660 A1<br>1285443 A1    |  | 18-12-2002<br>15-11-2001<br>26-02-2003 |

| US 6108257                             | A  | 22-08-2000       | WO<br>EP<br>JP | 0124189 A1<br>1133770 A1<br>2003510754 T |  | 05-04-2001<br>19-09-2001<br>18-03-2003 |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT, BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA, GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ, EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,M W,MX,MZ,NI,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 ハー、ローレンス エヌ.

アメリカ合衆国 7 8 6 1 5 テキサス州 クーブランド シーアール 4 7 2 1 4 0 1

F ターム(参考) 5B015 KB03 MM07 RR05

5L106 AA02 DD11 DD35 FF05