(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6228459号

(P6228459)

(45) 発行日 平成29年11月8日(2017.11.8)

(24) 登録日 平成29年10月20日(2017.10.20)

(51) Int.Cl.

G06F 9/54 (2006.01)

F 1

G 06 F 9/46 4 8 O B

請求項の数 20 (全 21 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-544736 (P2013-544736)  |

| (86) (22) 出願日 | 平成23年12月14日 (2011.12.14)      |

| (65) 公表番号     | 特表2013-546105 (P2013-546105A) |

| (43) 公表日      | 平成25年12月26日 (2013.12.26)      |

| (86) 國際出願番号   | PCT/US2011/064859             |

| (87) 國際公開番号   | W02012/082867                 |

| (87) 國際公開日    | 平成24年6月21日 (2012.6.21)        |

| 審査請求日         | 平成26年12月15日 (2014.12.15)      |

| 審判番号          | 不服2015-21973 (P2015-21973/J1) |

| 審判請求日         | 平成27年12月11日 (2015.12.11)      |

| (31) 優先権主張番号  | 61/422,953                    |

| (32) 優先日      | 平成22年12月14日 (2010.12.14)      |

| (33) 優先権主張国   | 米国 (US)                       |

| (31) 優先権主張番号  | 13/307,505                    |

| (32) 優先日      | 平成23年11月30日 (2011.11.30)      |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 591016172<br>アドバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド<br>ADVANCED MICRO DEVICES INCORPORATED<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サンディベイル、ビィ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・ブレイス、メイル・ストップ<br>・68 (番地なし) |

| (74) 代理人  | 100108833<br>弁理士 早川 裕司                                                                                                                                                                          |

| (74) 代理人  | 100111615<br>弁理士 佐野 良太                                                                                                                                                                          |

最終頁に続く

(54) 【発明の名称】システムコール要求の通信の最適化

## (57) 【特許請求の範囲】

## 【請求項 1】

ウェーブフロント内のワークアイテムごとにシステムコール要求を処理するために、対応する単一命令複数データ(SIMD)エレメントに情報を記憶するステップと、前記SIMDエレメントをSIMDベクトルとしてまとめるステップと、前記SIMDベクトルを、実行対象としてプロセッサに送信するステップと、各ワークアイテムについての結果を受信するステップと、を含む、方法。

## 【請求項 2】

前記SIMDベクトルを、中央処理装置(CPU)が認識することが可能な高優先度キュー内にエンキューするステップをさらに含む、

請求項1の方法。

## 【請求項 3】

各SIMDエレメントは、関数セレクタと、引数リストと、前記結果用のメモリ空間とを含む、

請求項1の方法。

## 【請求項 4】

前記SIMDベクトルは、複数のウェーブフロントからのシステムコール要求を含む、

請求項1の方法。

## 【請求項 5】

10

20

少なくとも 1 つのプロセッサを有するコンピュータシステムで実行される方法であって、

ウェーブフロント内の各ワークアイテムからのシステムコール要求に対応する单一命令複数データ ( SIMD ) エレメントを含む SIMD ベクトルを受信するステップと、各 SIMD エレメントの各システムコール要求を実行するステップと、各システムコールの結果を、前記 SIMD ベクトルを用いて、前記ウェーブフロント内の各ワークアイテムに送信するステップと、

を含む、方法。

【請求項 6】

前記受信するステップは、前記コンピュータシステム内のグラフィックス処理デバイスが認識することが可能な高優先度キュー内の前記 SIMD ベクトルを受信するステップを含む、

請求項 5 の方法。

【請求項 7】

ウェーブフロント内のワークアイテムごとのシステムコール要求を処理するために、対応する单一命令複数データ ( SIMD ) エレメントに情報を記憶するように構成されたメモリと、

CPU を含み、

前記 SIMD エレメントは、 SIMD ベクトルとしてまとめられ、

前記 CPU は、

前記 SIMD エレメントに記憶された各システムコール要求を実行することと、各システムコール要求の結果を、前記ウェーブフロント内の各ワークアイテムに送信することと、

を行うように構成されている、

システム。

【請求項 8】

前記メモリは、前記 SIMD ベクトルをエンキューするように構成された高優先度キューであり、前記高優先度キューは、 CPU によって認識可能である、

請求項 7 のシステム。

【請求項 9】

各 SIMD エレメントは、関数セレクタと、引数リストと、前記結果用のメモリ空間とを含む、

請求項 7 のシステム。

【請求項 10】

前記 SIMD ベクトルは、複数のウェーブフロントからのシステムコール要求を含む、請求項 8 のシステム。

【請求項 11】

メモリと、

CPU を含み、

前記 CPU は、

情報を含む单一命令複数データ ( SIMD ) エレメントを含む SIMD ベクトルを受信して、対応するシステムコール要求をウェーブフロント内の各ワークアイテムごとに処理することと、

前記 SIMD ベクトルに記憶された各システムコールを実行することと、

各システムコールの結果を、前記ウェーブフロント内の各ワークアイテムに送信することと、

を行うように構成されている、

システム。

【請求項 12】

前記 CPU は、

10

20

30

40

50

高優先度キューから前記 SIMD ベクトルを受信すること、を行うように構成されている。

請求項 1 1 のシステム。

【請求項 1 3】

コンピュータ記憶デバイスに記憶された命令であって、前記命令がコンピューティングデバイスによって実行されると、

対応する単一命令複数データ (SIMD) エレメントに情報を記憶して、ウェーブフロント内のワークアイテムごとにシステムコール要求を処理することと、

前記 SIMD エレメントを SIMD ベクトルとしてまとめて、システムコール要求データ構造を生成することと、

前記 SIMD ベクトルを、実行対象として前記コンピューティングデバイス内のプロセッサに送信することと、

前記ウェーブフロント内の各ワークアイテムについての結果を受信することと、

を前記コンピューティングデバイスに実行させる、

命令。

【請求項 1 4】

前記 SIMD ベクトルを、前記プロセッサが認識することが可能な高優先度キュー内にエンキューすることをさらに含む、

請求項 1 3 の命令。

【請求項 1 5】

コンピュータ記憶デバイスに記憶された命令であって、前記命令がコンピューティングデバイスによって実行されると、

ウェーブフロント内の各ワークアイテムからのシステムコール要求に対応する単一命令複数データ (SIMD) エレメントを含む SIMD ベクトルを受信することと、

前記 SIMD ベクトルからの各システムコール要求を実行することと、

各システムコールの結果を、前記ウェーブフロント内の各ワークアイテムに送信することと、

を前記コンピューティングデバイスに実行させる、

命令。

【請求項 1 6】

前記受信することは、グラフィックス処理デバイスが認識することが可能な高優先度キュー内の前記 SIMD ベクトルを受信することを含む、

請求項 1 5 の命令。

【請求項 1 7】

コンピュータ記憶デバイスであって、前記デバイスには命令が記憶されており、前記命令がコンピューティングデバイスによって実行されると、

対応する単一命令複数データ (SIMD) エレメントに情報を記憶して、ウェーブフロント内のワークアイテムごとにシステムコール要求を処理することと、

前記記憶されたシステムコールを、SIMD ベクトルを用いて、実行対象として前記コンピューティングデバイス内のプロセッサに送信することであって、前記 SIMD ベクトルは、單一データ構造としてまとめられた前記 SIMD エレメントを含むことと、

前記送信に応じて、前記ウェーブフロント内の各ワークアイテムについての結果を受信することと、

を前記コンピューティングデバイスに実行させる、

コンピュータ記憶デバイス。

【請求項 1 8】

前記 SIMD ベクトルを、前記プロセッサが認識することが可能な高優先度キュー内にエンキューすることをさらに含む、

請求項 1 7 のコンピュータ記憶デバイス。

【請求項 1 9】

10

20

30

40

50

コンピュータ記憶デバイスであって、前記デバイスには命令が記憶されており、前記命令がコンピューティングデバイスによって実行されると、

ウェーブフロント内の各ワークアイテムからのシステムコール要求に対応する单一命令複数データ( SIMD )エレメントを含む SIMD ベクトルを受信することと、

前記 SIMD ベクトルからの各システムコール要求を実行することと、

各システムコールの結果を、前記ウェーブフロント内の各ワークアイテムに送信することと、

を前記コンピューティングデバイスに実行させる、

コンピュータ記憶デバイス。

【請求項 20】

10

前記 SIMD ベクトルは、グラフィックス処理デバイスが認識することが可能な高優先度キューから受信される、

請求項 19 のコンピュータ記憶デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して、コンピュータシステムを対象とする。さらに詳細には、本発明は、コンピューティングシステム内のコンピュータコンポーネントの統一のためのアーキテクチャに関する。

【背景技術】

20

【0002】

グラフィックス処理ユニット( GPU : graphics processing unit )を一般的な演算に用いる要請は、 GPU の単位電力および / またはコストあたりの能力が優れることから、最近ではより顕著となってきている。 GPU の計算能力は、対応する中央処理装置( CPU : central processing unit )の計算能力の成長速度を超える速度で成長してきた。モバイルコンピューティング市場( 例えば、ノートブック、モバイルスマートフォン、タブレット、その他 )およびその必要な支援サーバ / 企業システムの爆発的な成長と組み合わされたこの成長は、特定品質の所望のユーザ経験を提供するために用いられてきている。したがって、並列データの内容を有する作業負荷を実行するために CPU と GPU を併用することはボリュームテクノロジとなりつつある。

30

【0003】

しかし、 GPU は、従来、主にグラフィックの高速化のために利用可能な制約されたプログラミング環境で動作する。これらの制約は、 GPU が、 CPU と同程度に豊かなプログラミングエコシステムを有さないという事実に起因するものである。したがって、 GPU の使用は、主に、グラフィックスおよびビデオのアプリケーションプログラミングインターフェース( API : application programming interface )を処理することに既に順応した、 2 次元( 2D )グラフィックスと、 3 次元( 3D )グラフィックスと、少数の最先端マルチメディアアプリケーションとに限られていた。

40

【0004】

マルチベンダにサポートされる OpenCL ( 登録商標 ) 、 DirectCompute ( 登録商標 ) 、標準的な API およびサポート用ツールの出現とともに、従来の用途における GPU の限界は、従来のグラフィックスを越えて拡張されてきている。 OpenCL ( 登録商標 ) および DirectCompute ( 登録商標 ) は将来性のあるスタートではあるが、大部分のプログラミングタスクに対して、 CPU と同程度に流動的に CPU と GPU との組合せが用いられることを可能にする環境およびエコシステムを作成するには、多数のハードルが残されている。

【0005】

既存のコンピューティングシステムは、大抵、複数の処理装置を含む。例えば、いくつ

50

かのコンピューティングシステムは、CPUおよびGPUの両方を、別個のチップ上（例えば、CPUはマザーボード上に、GPUはグラフィックカード上に配置され得る）または单一チップパッケージ上に有し得る。これらの構成の両方は、(i)別個のメモリシステム、(ii)効率的なスケジューリング、(iii)プロセス間のサービス品質(QoS)の保証、(iv)プログラミングモデルおよび(v)複数のターゲット命令セットアーキテクチャ(ISA:instruction set architecture)へのコンパイル、の全項目を、電力消費を最小化しながら満足することに関して顕著な問題点を依然として含む。

#### 【0006】

例えば、個別チップ構成においては、各プロセッサがメモリにアクセスするためには、システムアーキテクチャおよびソフトウェアアーキテクチャは、チップ間インターフェースを利用する余儀なくされる。これらの外部インターフェース（例えばチップ間インターフェース）においては、異機種環境のプロセッサを協働させるために、メモリレイテンシおよび電力消費に弊害がもたらされる一方で、別個のメモリシステム（すなわち、別個のアドレス空間）およびドライバに管理される共有メモリにおいては、きめ細かな負荷軽減に対しては許容されないオーバーヘッドが生成されてしまうこととなる。

#### 【0007】

別の例において、いくつかのコマンドは、GPUにて効率的に実行できない場合がある。例えば、GPUは、オペレーティングシステム(OS)を用いたコマンドを効率的に実行できない場合がある（例えば、メモリまたは印刷データを、コンピュータ画面に割り当てる命令は、CPUでしか処理することができない）。このように、GPUは、これらのタスクを実行することができないため、CPUに対して、これらのタスクを実行するよう要求する。これらの要求は、システムコール（シスコール）として知られている。

#### 【0008】

シスコールは、CPUによる処理対象としては高コストである。すなわち、シスコールは、高優先度コマンドであるため、CPUに送信に対応してもらわなくてはならない場合が多い。CPUは、シスコール要求を受信するたびに、現在のプロセス処理を停止して、OSを呼び出し、当該シスコールを処理した後に処理作業に戻る。

#### 【0009】

GPUがウェーブフロントを処理する場合には、各ワークアイテムは、メモリ割り当てまたはGPUによる処理が不可能（若しくは処理が容易ではない）な他の命令のために、シスコールを必要とし得る。従来のシステムでは、GPUは、ワークアイテムごとに別個のシスコール要求をCPUに発行する。各ワークアイテムは並列に実行するため、同一のシスコール要求が、各ワークアイテムからCPUへ発行される。

#### 【0010】

CPUにシスコール要求が到着するたびに、CPUは、処理作業を停止し、OSを呼び出し、GPUからの要求を処理した後に元の処理作業に戻る。複数のワークアイテムから別個のシスコール要求が同時に発行された場合には、CPUの処理時間の無駄が発生する。なぜならば、CPUは、自身の処理作業を繰り返して一時停止し、OSを呼び出し、GPUからのシスコール要求を処理するからである。

#### 【発明の概要】

#### 【0011】

したがって、必要とされるのは、CPUとGPUとの間のシスコールに関連する通信を最適化する（すなわち、向上させる）ためのシステムおよび方法である。

#### 【0012】

GPUと、アクセラレーテッドプロセッシングユニット(APU)と、GPUによる汎目的計算(GPGPU)とは、この分野において一般に用いられる用語であるが、「アクセラレーテッド処理デバイス」(APD)は、より広い表現とみなされる。例えば、APDは、従来のCPU、従来のGPU、ソフトウェアおよび/またはこれらの組合せと比較して高速化された方法で行われる、グラフィックス処理タスク、データ並列タスク、また

10

20

30

40

50

はネスト化されたデータ並列タスクの高速化に関連する機能および演算を実行する任意のハードウェアおよび／またはソフトウェアの協働的集合体を指す。

#### 【0013】

本発明の実施形態は、システムコールの通信を最適化するためのシステム、方法および製品を含む。上記方法は、ウェーブフロント内のワークアイテムごとのシステムコールを記憶するステップと、前記記憶されたシステムコールを実行対象としてプロセッサに送信するステップとを含む。また、上記方法は、前記送信に応じて、前記ウェーブフロント内のワークアイテムごとの結果を受信するステップを含む。

#### 【0014】

本発明の追加的な特徴および利点、ならびに本発明の様々な実施形態の構造および動作は、添付の図面を参照して以下で詳細に説明される。本発明は本明細書において説明される特定の実施形態に制限されないことに注意すべきである。係る実施形態は、例示目的のみのために本明細書において提示される。追加的実施形態は、本明細書に含まれる教示に基づいて当業者に明らかとなるであろう。

10

#### 【0015】

添付の図面は、本明細書に組み込まれ本明細書の一部を構成するものであって、本発明を例示し、説明とともに、本発明の原理を説明し、当業者が本発明を実施することを可能にするように、さらに機能する。本発明の様々な実施形態は、添付の図面を参照して以下で説明される。なお、添付の図面の全体を通じて、同様の参照番号は同様の構成要素を参考するために用いられる。

20

#### 【図面の簡単な説明】

#### 【0016】

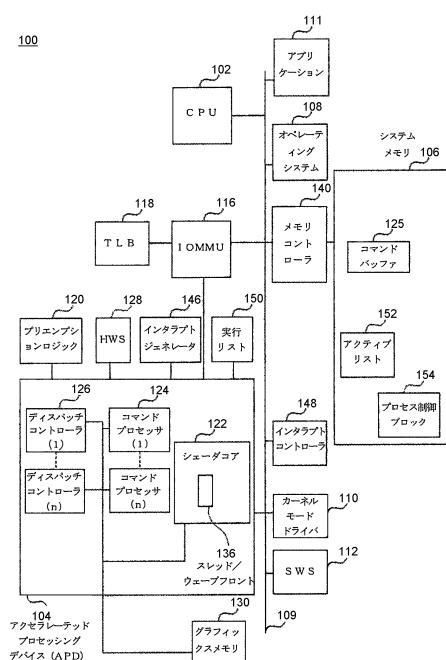

【図1A】本発明の実施形態に係る処理システムの例示的プロック図である。

【図1B】図1Aに示されたAPDの例示的プロック図である。

【図2】CPUとAPDとの間の最適化された通信処理の例示的プロック図200である。

【図3】シスコール要求をCPUに通信するための単一命令複数データ(SIMD)ベクトルを用いたAPDの例示的フローチャート300である。

#### 【発明を実施するための形態】

#### 【0017】

30

以下の詳細な説明においては、「1つの実施形態」、「ある実施形態」、「例示的実施形態」またはその他を参照することは、本明細書において説明される実施形態が、特定の特徴、構造または特性を有することを示すが、全ての実施形態がその特定の特徴、構造または特性を必ずしも含むとは限らない。さらに、係る語句は、同一の実施形態を参照するとは限らない。さらに、特定の特徴、構造または特性が1つの実施形態に関連して説明されるとき、係る特長、構造または特性を他の実施形態との関連で実施することは、明示されているか否かによらず、当業者の知識の範囲内であることが提起される。

#### 【0018】

「本発明の実施形態」という用語は、本発明の実施形態の全部が検討の対象である特徴、特長または操作モードを含むことを必ずしも要求しない。代替的な実施形態が本発明の範囲から逸脱することなく考案され、本発明の既知の構成要素は、本発明の関連する詳細を不明瞭化しないために、必ずしも詳細に説明されるとは限らず、または省略され得る。加えて、本明細書において用いられる用語は、特定の実施形態を説明することのみを目的とし、本発明を制限することを意図するものではない。例えば、本明細書において用いられる単数形の「1つの」および「その」は、内容的に明らかに単数のみを指す場合を除き、複数形をも含むことを意図するものである。本明細書において用いられる場合、「含む」、「備える」、「包含する」および／または「有する」という用語は、述べられた特徴、整数、ステップ、操作、構成要素および／またはコンポーネントが存在することを指定するが、1つまたは複数の他の特徴、整数、ステップ、操作、構成要素、コンポーネントおよび／またはこれらの群の存在または追加を除外しない。

40

50

## 【0019】

図1Aは、CPU102およびAPD104を含む統合化されたコンピューティングシステム100の例示的な図である。CPU102は、1つ以上のシングルコアまたはマルチコアCPUを含み得る。本発明の一実施形態において、システム100は、統合化されたプログラミング環境および実行環境を提供するために、CPU102およびAPD104を組み合わせた単一のシリコンダイまたはパッケージ上に形成される。この環境は、APD104が、いくつかのプログラミングタスクに対して、CPU102と同程度に流動的に用いられることを可能にする。しかし、CPU102およびAPD104が単一のシリコンダイ上に形成されることとは、本発明の絶対的な要件ではない。いくつかの実施形態において、CPU102およびAPD104は別個に形成され、同一の基板または異なる基板上に搭載されることが可能である。10

## 【0020】

1つの例において、システム100は、メモリ106、オペレーティングシステム108および通信インフラストラクチャ109を含む。オペレーティングシステム108および通信インフラストラクチャ109は、以下でより詳細に説明される。

## 【0021】

システム100は、カーネルモードドライバ(KMD: kernel mode driver)110と、ソフトウェアスケジューラ(SWS: software scheduler)112と、例えば入出力メモリ管理ユニット(IOMMU: input/output memory management unit)等のメモリ管理ユニット116とを含む。システム100の構成品は、ハードウェア、ファームウェア、ソフトウェアまたはこれらの任意の組合せとして実装され得る。当業者は、システム100が図1Aに示される実施形態において示されるものに加えて、またはこれらとは異なる、1つ以上のソフトウェアコンポーネント、ハードウェアコンポーネントおよびファームウェアコンポーネントを含み得ることを理解するであろう。20

## 【0022】

1つの例において、KMD110等のドライバは、通常、ハードウェアが接続されたコンピュータバスまたは通信サブシステムを通してデバイスと通信する。呼び出しプログラムがドライバにおいてルーチンを呼び出すと、ドライバは、デバイスに対してコマンドを発行する。デバイスがドライバに対してデータを戻すと、ドライバは、元の呼び出しプログラムにおいてルーチンを呼び出し得る。1つの例において、ドライバは、ハードウェア依存的であり、オペレーティングシステム固有である。ドライバは、通常、任意の必要な非同期的時間依存性のハードウェアインターフェースに対して要求されるインタラプトハンドリングを提供する。デバイスドライバは、特に現代のWindows(登録商標)プラットフォームにおいては、カーネルモード(リング0)またはユーザモード(リング3)において実行され得る。30

## 【0023】

ドライバをユーザモードにおいて実行することの利益は、安定性が改善されることである。なぜなら、不完全な形で書かれたユーザモードデバイスドライバは、カーネルメモリを上書きすることによってシステムをクラッシュさせることができないためである。一方、ユーザモード/カーネルモードの遷移は、通常、顕著な性能オーバーヘッドを与え、それにより、低レイテンシおよび高スループット要件目的のユーザモードドライバを阻害する。カーネルスペースは、システムコールの使用を通してのみ、ユーザモジュールからのアクセスが可能である。UNIX(登録商標)シェルまたは他のGUIベースのアプリケーションなどのエンドユーザプログラムは、ユーザスペースの一部である。これらのアプリケーションは、カーネルにサポートされた機能を通してハードウェアと相互作用する。40

## 【0024】

CPU102は、制御プロセッサ、フィールド・プログラマブル・ゲートアレイ(FPGA: field programmable gate array)、特定用途集積回路(ASIC: application specific integrated circuit)等の機能を備え得る。50

circuit) またはデジタル・シグナル・プロセッサ (DSP : digital signal processor) のうち1つ以上を含み得る(図示せず)。CPU102は、例えば、コンピューティングシステム100の動作を制御する、オペレーティングシステム108、KMD110、SWS112およびアプリケーション111を含む制御ロジックを実行する。この例示的な実施形態において、CPU102は、1つの実施形態によれば、アプリケーション111の実行の起動および制御を、例えばそのアプリケーションに関連する処理をCPU102とAPD104等の他の処理リソースとの間に分散させることにより行う。

#### 【0025】

APD104は、とりわけ、グラフィックス演算や、例えば特に並列処理に好適となり得る他の演算等の、選択された機能のためのコマンドおよびプログラムを実行する。一般に、APD104は、ピクセル処理、幾何学演算およびディスプレイに対する画像のレンダリング等のグラフィックスパイプライン処理を実行するために、しばしば用いられ得る。本発明の様々な実施形態において、APD104は、CPU102から受信したコマンドまたは命令に基づいて、計算処理演算も実行し得る。

#### 【0026】

例えば、コマンドは、ISAに定義されない特殊な命令であるとみなすことができ、所与のISAまたは独特なハードウェアからの1組の命令によって大抵得られる。コマンドは、例えばディスパッチプロセッサ、コマンドプロセッサまたはネットワークコントローラ等の特殊なプロセッサにより実行され得る。一方、命令は、例えばコンピューターアーキテクチャ内のプロセッサの単一の演算であるとみなされ得る。1つの例において、2セットのISAが用いられる場合には、いくつかの命令は、x86プログラムを実行するために用いられ、いくつかの命令は、APD計算ユニット上でカーネルを実行するために用いられる。

#### 【0027】

例示的な実施形態において、CPU102は、選択されたコマンドをAPD104に伝達する。これらの選択されたコマンドは、並列実行に適したグラフィックスコマンドと、並列実行に適した他のコマンドとを含み得る。計算処理コマンドを含み得るこれらの選択されたコマンドは、実質的にCPU102から独立して実行され得る。

#### 【0028】

APD104は、例えば1つ以上の単一命令複数データ (SIMD : single instruction multiple data) 処理コア等ではあるがこれに制限されない、自身の計算ユニット(図示せず)を含み得る。本明細書で参照されるSIMDは、数学パイプライン、すなわち、それぞれが自身のデータおよび共有プログラムカウンタを有する複数の処理エレメント上でカーネルが同時に実行されるプログラミングモデルである。全ての処理エレメントは、完全に同一の1組の命令を実行する。プレディケーションを用いることにより、発行された各コマンドに対して、ワークアイテムを関与させることまたはさせないことが可能となる。

#### 【0029】

1つの例において、各APD計算ユニット104は、1つ以上のスカラーおよび/またはベクトル浮動小数点演算ユニットおよび/または算術論理ユニット (ALU : arithmetic and logic unit) を含み得る。APD計算ユニットは、逆平方根ユニットおよびサイン/コサインユニット等の特殊用途処理ユニット(図示せず)も含み得る。1つの例において、APD計算ユニットは、本明細書においてシェーダコア122と総称される。

#### 【0030】

1つ以上のSIMDが存在することにより、一般に、APD104は、グラフィックス処理において一般的なデータ並列タスク等のデータ並列タスクの実行に、理想的に好適なものとなる。

#### 【0031】

10

20

30

40

50

ピクセル処理等のいくつかのグラフィックスパイプライン処理と、他の並列演算処理とは、同一のコマンドストリームまたは計算カーネルが、ストリームまたは入力データ要素の集合体上で実行されることを要求する。同一の計算カーネルのそれぞれのインスタンス化は、上記データ要素を並列に処理するために、シェーダコア 122 の複数の計算ユニット上で同時に実行され得る。本明細書で参照されるように、例えば計算カーネルは、プログラム上で宣言され、APD 計算ユニット上で実行される命令を含む関数である。この関数は、カーネル、シェーダ、シェーダプログラムまたはプログラムとも称される。

#### 【0032】

1つの例示的な実施形態において、各計算ユニット（例えば SIMD 処理コア）は、入力されるデータを処理するために、特定ワークアイテムのそれぞれのインスタンス化を実行し得る。ワークアイテムは、コマンドによりデバイス上で呼び出されるカーネルの並列実行の集合体のうちの 1 つである。ワークアイテムは、計算ユニット上で実行されるワークグループの一部として、1 つ以上の処理エレメントにより実行され得る。10

#### 【0033】

ワークアイテムは、自身のグローバル ID およびローカル ID によって、集合体内の他の実行から区別される。1つの例において、ワークグループにおいて 1 つの SIMD エンジンで同時に実行されるワークアイテムの一部は、ウェーブフロント 136 と称され得る。ウェーブフロントの幅は、計算ユニット（例えば、SIMD 処理コア）のハードウェアの特性である。本明細書で参照されるワークグループは、単一の計算ユニット上で実行される関連するワークアイテムの集合体である。ワークグループ内のワークアイテムは、同一のカーネルを実行し、ローカルメモリおよびワークグループバリアを共有する。20

#### 【0034】

1つのワークグループからの全てのウェーブフロントは、同一の SIMD エンジンで処理される。ウェーブフロントにわたる命令は 1 つずつ発行され、全てのワークアイテムが同一の制御フローに従う場合には、各ワークアイテムは、同一のプログラムを実行する。実行マスクおよびワークアイテムプレディケーションは、ウェーブフロント内の拡散的な制御フローを可能にするために用いられる。なお、拡散的な制御フローにおいては、各個別のワークアイテムは、カーネルを通じて一意的なコードパスを実際に取り得る。部分的に占められたウェーブフロントは、ワークアイテムの全てのセットがウェーブフロント開始時に必ずしも利用可能とは限らない場合に、処理され得る。ウェーブフロントは、ワープ、ベクトルまたはスレッドと称され得る。30

#### 【0035】

コマンドは、ウェーブフロントに対して 1 つずつ発行され得る。全てのワークアイテムが同一の制御フローに従う場合には、各ワークアイテムは同一のプログラムを実行し得る。1つの例では、実行マスクおよびワークアイテムプレディケーションは、各個別のワークアイテムがカーネルドライバを通じて一意的なコードパスを実際に取り得る拡散的な制御フローを可能にするために用いられる。ワークアイテムの全てのセットが開始時において利用できない場合には、部分的なウェーブフロントを処理することができる。例えば、シェーダコア 122 は、所定数のウェーブフロント 136 を同時に実行することができ、各ウェーブフロント 136 は、所定数のワークアイテムを含む。40

#### 【0036】

システム 100において、APD 104 は、グラフィックスメモリ 130 等の自身のメモリを含む。グラフィックスメモリ 130 は、APD 104 における計算実行の間の使用のために、ローカルメモリを提供する。シェーダコア 122 内の個々の計算ユニット（図示せず）は、自身のローカルデータ記憶装置（図示せず）を有し得る。1つの実施形態において、APD 104 は、ローカルグラフィックスメモリ 130 へのアクセス、ならびにメモリ 106 へのアクセスを含む。他の実施形態において、APD 104 は、ダイナミックランダムアクセスメモリ (DRAM : dynamic random access memory)、または、APD 104 には直接的に接続されているがメモリ 106 からは分離している他のメモリ（図示せず）へのアクセスを含み得る。50

**【 0 0 3 7 】**

図示の例において、A P D 1 0 4 は、1つまたは「n」個のコマンドプロセッサ ( C P : command processor ) 1 2 4 を含み得る。C P 1 2 4 は、A P D 1 0 4 内の処理を制御する。C P 1 2 4 は、実行されるべきコマンドを、メモリ 1 0 6 内のコマンドバッファ 1 2 5 から取得し、A P D 1 0 4 でのこれらのコマンドの実行を調整する。

**【 0 0 3 8 】**

1つの例において、C P U 1 0 2 は、アプリケーション 1 1 1 に基づくコマンドを、適切なコマンドバッファ 1 2 5 に入力する。本明細書において参照されるように、アプリケーションは、C P U 内またはA P D 内の計算ユニット上で実行されるプログラム部分の組合せである。

10

**【 0 0 3 9 】**

複数のコマンドバッファ 1 2 5 は、各プロセスがA P D 1 0 4 での実行のためにスケジュールされた状態で、保持され得る。

**【 0 0 4 0 】**

C P 1 2 4 は、ハードウェア、ファームウェア、ソフトウェアまたはこれらの組合せにおいて実装され得る。1つの実施形態において、C P 1 2 4 は、スケジューリングロジックを含むロジックを実装するためのマイクロコードを有する縮小命令セットコンピュータ ( R I S C : r e d u c e d i n s t r u c t i o n s e t c o m p u t e r ) エンジンとして実装される。

20

**【 0 0 4 1 】**

A P D 1 0 4 は、1つまたは「n」個のディスパッチコントローラ ( D C : d i s p a t c h c o n t r o l l e r ) 1 2 6 を含み得る。本願において、ディスパッチという用語は、1セットの計算ユニット上の1セットのワークグループに対するカーネルの実行のスタートを起動するために、コンテキスト状態を使用するディスパッチコントローラにより実行されるコマンドを指す。D C 1 2 6 は、シェーダコア 1 2 2 内でワークグループを起動するためのロジックを含む。いくつかの実施形態において、D C 1 2 6 は、C P 1 2 4 の一部として実装され得る。

**【 0 0 4 2 】**

システム 1 0 0 は、A P D 1 0 4 上で実行するためのプロセスを実行リスト 1 5 0 から選択するためのハードウェアスケジューラ ( H W S : h a r d w a r e s c h e d u l e r ) 1 2 8 を含む。H W S 1 2 8 は、ラウンドロビン方式、優先レベルを用いて、または他のスケジューリングポリシーに基づいて、プロセスを実行リスト 1 5 0 から選択し得る。優先レベルは、例えば、動的に決定され得る。H W S 1 2 8 は、例えば、新規のプロセスを追加することによって、あるいは既存のプロセスを実行リスト 1 5 0 から削除することによって、実行リスト 1 5 0 を管理する機能を含み得る。H W S 1 2 8 の実行リスト管理ロジックは、実行リストコントローラ ( R L C : r u n l i s t c o n t r o l l e r ) と称されることもある。

30

**【 0 0 4 3 】**

本発明の様々な実施形態において、H W S 1 2 8 が、実行リスト 1 5 0 からプロセスの実行を開始すると、C P 1 2 4 は、対応するコマンドバッファ 1 2 5 からのコマンドの取得および実行を開始する。いくつかの事例において、C P 1 2 4 は、C P U 1 0 2 から受信したコマンドに対応する、A P D 1 0 4 内で実行される1つ以上のコマンドを生成し得る。1つの実施形態において、C P 1 2 4 は、A P D 1 0 4 リソースおよび/またはシステム 1 0 0 のリソースの利用が改善または最大化されるように、A P D 1 0 4 におけるコマンドの優先化およびスケジューリングを、他のコンポーネントとともに実装する。

40

**【 0 0 4 4 】**

A P D 1 0 4 は、インターフェトジェネレータ 1 4 6 に対してアクセスを有するか、またはインターフェトジェネレータ 1 4 6 を含み得る。インターフェトジェネレータ 1 4 6 は、A P D 1 0 4 がページフォールト等のインターフェトイイベントに遭遇すると、A P D 1 0 4 に

50

よってオペレーティングシステム 108 にインタラプトをかけるよう構成され得る。例えば、APD104 は、IOMMU116 内のインタラプト生成ロジックに依存して、上述のページフォールトインタラプトを生成し得る。

#### 【0045】

APD104 は、シェーダコア 122 内で現在実行中のプロセスを切り替えるためのプリエンプションおよびコンテキストスイッチロジック 120 を含み得る。コンテキストスイッチロジック 120 は、例えばプロセスを停止させ、その現在状態（例えばシェーダコア 122 状態および CP124 状態）を保存する機能を含む。

#### 【0046】

本明細書において参照される状態という用語は、初期状態、中間状態および / または最終状態を含み得る。初期状態は、機械がプログラム順序に従って入力データセットを処理することによって、データの出力セットを生成する開始点である。例えば、処理を前進させるためにいくつかのポイントにおいて記憶される必要がある中間状態が存在する。この中間状態は、他のプロセスによってインタラプトがかけられた場合に、後に実行を継続することを可能にするために記憶される場合もある。出力データセットの一部として記録され得る最終状態も存在する。10

#### 【0047】

プリエンプションおよびコンテキストスイッチロジック 120 は、他のプロセスを、APD104 にコンテキストスイッチするためのロジックを含み得る。他のプロセスを APD104 で実行するようにコンテキストスイッチするための機能は、APD104 上で実行するために、例えば CP124 および DC126 によってプロセスをインスタンス化することと、当該プロセスに対して以前に保存された状態を復元することと、当該プロセスの実行を開始することと、を含み得る。20

#### 【0048】

メモリ 106 は、DRAM（図示せず）等の非永続型メモリを含み得る。メモリ 106 は、例えば、アプリケーションまたは他の処理ロジックの部分を実行する間に、処理ロジック命令、定数および様々な変数を記憶し得る。例えば、1つの実施形態において、CPU102 上で 1 つ以上の演算を実行するための制御ロジックの部分は、CPU102 によって演算のそれぞれの部分が実行される間、メモリ 106 内に常駐し得る。本明細書において用いられる「処理ロジック」または「ロジック」という用語は、制御フローコマンド、計算実行コマンドおよびリソースアクセス関連コマンドを指す。30

#### 【0049】

実行中、個別のアプリケーション、オペレーティングシステム関数、処理ロジックコマンドおよびシステムソフトウェアは、メモリ 106 に常駐し得る。オペレーティングシステム 108 に対して必須である制御ロジックコマンドは、一般に、実行中にはメモリ 106 に常駐することとなるであろう。他のソフトウェアコマンド、例えばカーネルモードドライバ 110 およびソフトウェアスケジューラ 112 は、システム 100 の実行中にはメモリ 106 に常駐し得る。

#### 【0050】

この例において、メモリ 106 は、コマンドを APD104 に送るために、CPU102 によって用いられるコマンドバッファ 125 を含む。メモリ 106 は、プロセスリストおよびプロセス情報（例えば、アクティブライト 152 およびプロセス制御ブロック 154）を含み得る。これらのリストおよび情報は、スケジュール情報を、APD104 および / または関連するスケジューリングハードウェアに伝えるために、CPU102 上で実行されるスケジューリングソフトウェアによって使用される。メモリ 106 に対するアクセスは、メモリ 106 に接続されたメモリコントローラ 140 によって管理され得る。例えば、メモリ 106 に対する読み出しおよび書き込みを実行するための、CPU102 または他のデバイスからの要求は、メモリコントローラ 140 によって管理される。40

#### 【0051】

システム 100 の他の態様に戻ると、IOMMU116 は、マルチコンテキスト・メモリ

50

リ管理ユニットである。

#### 【0052】

本明細書で用いられるコンテキスト（プロセスともよばれる）という用語は、カーネルが実行される環境であって、同期およびメモリ管理が定義されるドメインであるとみなされる。コンテキストは、1セットのデバイスと、これらのデバイスに対してアクセス可能であるメモリと、対応するメモリ特性と、メモリオブジェクトにおけるカーネル（単数または複数）または演算の実行をスケジュールするために用いられる1つ以上のコマンドキューとを含む。一方、プロセスは、コンピュータ上で実行するプロセスを発生するアプリケーション用のプログラムの実行とみなすことができる。オペレーティングシステムは、実行対象プログラム用のデータ記録および仮想メモリアドレス空間を生成し得る。プログラム実行のメモリおよび現在の状態は、プロセスと呼ばれ得る。オペレーティングシステムは、メモリ上で動作させるべきプロセス用のタスクを、初期状態から最終状態までスケジュールする。

10

#### 【0053】

図1Aにおいて示される例に戻ると、I O M M U 1 1 6は、A P D 1 0 4を含むデバイスに対するメモリページアクセスに対して、仮想アドレスから物理アドレスへの変換を実行するためのロジックを含む。I O M M U 1 1 6は、例えば、A P D 1 0 4等のデバイスによるページアクセスの結果としてページフォールトが生じる場合に、インタラプトを生成するためのロジックを含み得る。I O M M U 1 1 6は、トランスレーションルックアサイドバッファ（T L B : t r a n s l a t i o n l o o k a s i d e b u f f e r ）

20 1 1 8を含むか、あるいはT L B 1 1 8に対するアクセスを有し得る。T L B 1 1 8は、1つの例として、メモリ1 0 6内のデータ用にA P D 1 0 4によりなされた要求に対して、論理（すなわち仮想）メモリアドレスから物理メモリアドレスへの変換を高速化するために、コンテンツアドレスブルメモリ（C A M : c o n t e n t a d d r e s s a b l e m e m o r y ）に実装され得る。

#### 【0054】

示された例において、通信インフラストラクチャ1 0 9は、必要に応じてシステム1 0 0のコンポーネントを相互接続する。通信インフラストラクチャ1 0 9は、周辺構成要素相互接続（P C I）バス、拡張P C I（P C I - E）バス、アドバンスト・マイクロコントローラ・バス・アーキテクチャ（A M B A）バス、アドバンスト・グラフィックス・ポート（A G P）または他の通信インフラストラクチャのうち1つ以上を含み得る（図示せず）。通信インフラストラクチャ1 0 9は、イーサネット（登録商標）若しくは同様のネットワークまたはアプリケーションの転送速度要求を満足する任意の好適な物理的通信インフラストラクチャを含み得る。通信インフラストラクチャ1 0 9は、コンピューティングシステム1 0 0のコンポーネントを含むコンポーネントを相互接続するための機能を含む。

30

#### 【0055】

この例において、オペレーティングシステム1 0 8は、システム1 0 0のハードウェアコンポーネントを管理する機能と、共通サービスを提供するための機能とを含む。様々な実施形態において、オペレーティングシステム1 0 8は、C P U 1 0 2上で実行し、共通サービスを提供する。これらの共通サービスは、例えば、C P U 1 0 2内での実行のためにアプリケーションをスケジューリングすることと、フォールト管理と、インタラプトサービスと、他のアプリケーションの入力および出力を処理することと、を含む。

40

#### 【0056】

いくつかの実施形態において、オペレーティングシステム1 0 8は、例えばインタラプトコントローラ1 4 8等のインタラプトコントローラによって生成されたインタラプトに基づいて、適切なインタラプトハンドリングルーチンを呼び出す。例えば、オペレーティングシステム1 0 8は、ページフォールト・インタラプトを検出すると、関連するページをメモリ1 0 6にロードし始め、且つ、対応するページテーブルを更新するために、インタラプトハンドラを呼び出す。

50

**【 0 0 5 7 】**

オペレーティングシステム 108 は、オペレーティングシステムにより管理されるカーネル機能を通して、ハードウェア部品に対するアクセスが仲介されることを確保することによって、システム 100 を保護する機能を含み得る。事実、オペレーティングシステム 108 は、アプリケーション 111 等のアプリケーションが、CPU 102 上でユーザースペースにおいて実行されることを確保する。オペレーティングシステム 108 は、アプリケーション 111 が、ハードウェアにアクセスするためにオペレーティングシステムにより提供されるカーネル機能および / または入出力機能を呼び出すことも確保する。

**【 0 0 5 8 】**

例として、アプリケーション 111 は、CPU 102 上でも実行されるユーザ計算を実行するための様々なプログラムまたはコマンドを含む。このような統一コンセプトによって、選択されたコマンドを APD 104 上での処理対象として CPU 102 からシームレスに送ることが可能になる。この統一 APD / CPU フレームワークにおいて、アプリケーション 111 からの入力 / 出力要求は、対応するオペレーティングシステム機能を通じて処理される。

10

**【 0 0 5 9 】**

1つの例において、KMD 110 は、CPU 102、CPU 102 上で実行されるアプリケーションまたは他のロジックが、APD 104 の機能を呼び出し得るアプリケーションプログラミングインターフェース (API) を実装する。例えば、KMD 110 は、CPU 102 からのコマンドを、コマンドバッファ 125 にエンキューし得る。なお、APD 104 は、このコマンドバッファ 125 からコマンドを続けて取得することとなる。加えて、KMD 110 は、APD 104 上で実行されるプロセスのスケジューリングを、SWS 112とともに実行する。SWS 112 は、例えば、APD 上で実行されるプロセスの優先度リストを保持するためのロジックを含み得る。

20

**【 0 0 6 0 】**

本発明の他の実施形態において、CPU 102 上で実行するアプリケーションは、コマンドをエンキューするときに、KMD 110 を完全にバイパスし得る。

**【 0 0 6 1 】**

いくつかの実施形態において、SWS 112 は、APD 104 上で実行されるプロセスのアクティビリスト 152 を、メモリ 106 に保持する。SWS 112 は、アクティビリスト 152 におけるプロセスのうち、ハードウェアの HWS 128 により管理される一部を選択する。各プロセスを APD 104 上で実行することに関する情報は、CPU 102 からプロセス制御ブロック (PCB : process control block ) 154 を通して、APD 104 に伝えられる。

30

**【 0 0 6 2 】**

アプリケーション、オペレーティングシステムおよびシステムソフトウェアのための処理ロジックは、マスクワーク / フォトマスクの生成を通して最終的に製造プロセスを構成することで、本明細書において説明される本発明の態様を具体化するハードウェア装置を生成することを可能にするための、例えば、C 言語等のプログラム言語および / または Verilog、RTL 等のハードウェア記述言語もしくはネットリストにおいて指定されるコマンドを含み得る。

40

**【 0 0 6 3 】**

当業者は、コンピューティングシステム 100 が、図 1A において示されるコンポーネントよりも多数または少数のコンポーネントを含み得ることを、本明細書を読むことで理解するであろう。例えば、コンピューティングシステム 100 は、1 つ以上の入力インターフェースと、不揮発性ストレージと、1 つ以上の出力インターフェースと、ネットワークインターフェースと、1 つ以上のディスプレイまたはディスプレイインターフェースと、を含み得る。

**【 0 0 6 4 】**

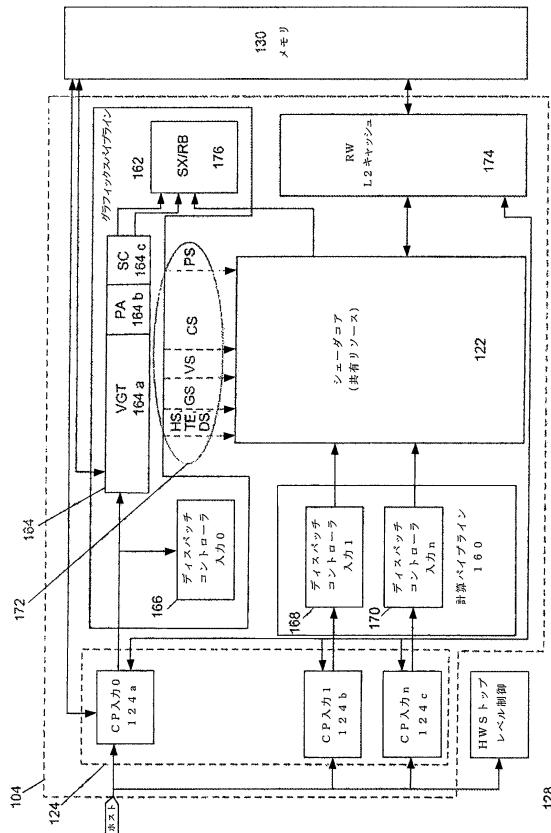

図 1B は、図 1A において示される APD 104 のより詳細な例示を示す実施形態であ

50

る。図1Bにおいて、CP124は、CPパイプライン124a, 124b, 124cを含み得る。CP124は、図1Aにおいて示されるコマンドバッファ125から入力として提供されるコマンドリストを、処理するように構成され得る。図1Bの典型的な動作において、CP入力0(124a)は、コマンドをグラフィックスパイプライン162に駆動することを担当する。CP入力1および2(124bおよび124c)は、コマンドを計算パイプライン160に伝える。HWS128の動作を制御するためのコントローラ機構166も提供される。

#### 【0065】

図1Bにおいて、グラフィックスパイプライン162は、本明細書において順序化パイプライン164と称される、1セットのブロックを含み得る。例えば、順序化パイプライン164は、頂点グループ変換器(VGT:vertex group translator)164aと、プリミティブアセンブラ(PA:primitive assembler)164bと、スキャンコンバータ(SC:scan converter)164cと、シェーダエクスポート・レンダーバック・ユニット(SX/RB:shader-export, render-back unit)176とを含む。順序化パイプライン164内の各ブロックは、グラフィックスパイプライン162内の異なる段階のグラフィックス処理を表し得る。順序化パイプライン164は、固定機能ハードウェアパイプラインであり得る。本発明の精神および範囲に含まれ得る他の実装を用いることも可能である。

#### 【0066】

わずかな量のデータが、入力としてグラフィックスパイプライン162に提供されるが、このデータは、グラフィックスパイプライン162からの出力として提供される回数分だけ増幅されることとなるであろう。グラフィックスパイプライン162は、CPパイプライン124aから受け取ったワークアイテムグループ内の範囲にわたってカウントするためのDC166も含む。DC166を通して提示された計算作業は、グラフィックスパイプライン162と準同期している。

#### 【0067】

計算パイプライン160は、シェーダDC168, 170を含む。DC168, 170のそれぞれは、CPパイプライン124b, 124cから受け取ったワークグループ内の計算範囲にわたってカウントするように構成されている。

#### 【0068】

図1Bにおいて示されるDC166, 168, 170は、入力範囲を受け取り、入力範囲をワークグループに分割し、次いでこれらのワークグループをシェーダコア122に伝える。

#### 【0069】

グラフィックスパイプライン162は、一般に固定機能パイプラインであるため、その状態を保存および復元することは困難であり、そのためグラフィックスパイプライン162は、コンテキストスイッチが困難である。したがって、ほとんどの場合、本明細書において論じられるコンテキストスイッチは、グラフィックス処理におけるコンテキストスイッチに関係しない。例外は、シェーダコア122におけるグラフィックス作業であり、これはコンテキストスイッチされ得る。

#### 【0070】

シェーダコア122は、グラフィックスパイプライン162および計算パイプライン160により共有され得る。シェーダコア122は、汎用プロセッサであり、ウェーブプロントを実行するように構成されている。

#### 【0071】

1つの例において、計算パイプライン160内の全てのワークは、シェーダコア122内で処理される。シェーダコア122は、プログラム可能なソフトウェアコードを実行し、多様な形態のデータ(例えば、状態データ)を含む。しかし、計算パイプライン160は、処理対象ワークをグラフィックスパイプライン162に送らない。グラフィックスパ

10

20

30

40

50

イプラン 162 内におけるワーク処理が完了した後、この完了したワークを、レンダーバックユニット 176 を通じて処理する。レンダーバックユニット 176 は、デプスおよび色の計算を行った後に、この最終結果を、グラフィックスメモリ 130 に書き込む。

#### 【0072】

以下に記載するように、本発明は、ソフトウェア、ハードウェア、ファームウェアおよび／または図示のエンティティの多数の異なる実施形態において実行することが可能であることが当業者にとって明らかである。本発明を実行するためのハードウェアの特殊制御を用いた実際のソフトウェアコードは、本発明を限定しない。従って、本明細書に記載された詳細に鑑みれば、実施形態の改変および変更が可能であるとの理解の下、本発明の動作挙動について説明する。

10

#### 【0073】

さらに、当業者であれば理解するように、（上記したような）コンピュータで読み出し可能なコード（例えば、汎用プログラミング言語（例えば、C または C++）、Verilog HDL、VHDL、Altera HDL（AHD L）などを含むハードウェア記述言語（HDL）または他の利用可能なプログラミングおよび／または回路図入力ツール（例えば、回路入力ツール））の利用を通じて、本発明の多様な実施形態のシミュレーション、合成および／または製造を遂行することが部分的に可能である。コンピュータで読み出し可能なコードは、任意の公知のコンピュータにおいて利用可能な媒体（例えば、半導体、磁気ディスク、光学ディスク（例えば、CD-ROM、DVD-ROM））内に配置することもできるし、あるいはコンピュータデータ信号としてコンピュータで利用可能な（例えば、読み出し可能な）伝送媒体（例えば、搬送波または他の任意の媒体（例えば、デジタル媒体、光学媒体、またはアナログ媒体））内に埋め込むことも可能である。

20

#### 【0074】

従って、上記コードは、通信ネットワーク（例えば、インターネットおよびイントラネット）を通じて送信することができる。上述のシステムおよび技術によって達成される機能および／または上述のシステムおよび技術によって提供される構造は、プログラムコードに具現化されているコア（例えば、APD コアおよび／または CPU コア）として表現され、集積回路製造の一部としてハードウェアに変換され得ることが理解される。

#### 【0075】

本発明の実施形態により、プログラマは、CPU と APD との間のデータ処理移動をシームレスに行うアプリケーションを書くことが可能になり、両者の最高の特性が得られるという利益を受けることが可能になる。統一された単一プログラミングプラットフォームによって、並列処理を利用する言語、フレームワークおよびアプリケーションの開発のための強固な基盤を得ることが可能になる。

30

#### 【0076】

本発明の実施形態により、プログラマは、CPU と APD との間のデータ処理移動をシームレスに行うアプリケーションをプログラマが書くことが可能になり、両者の最高の特性が得られるという利益を受けることが可能になる。統一された単一プログラミングプラットフォームにより、並列処理を利用する言語、フレームワークおよびアプリケーションの開発のための強固な基盤を得ることが可能になる。

40

#### 【0077】

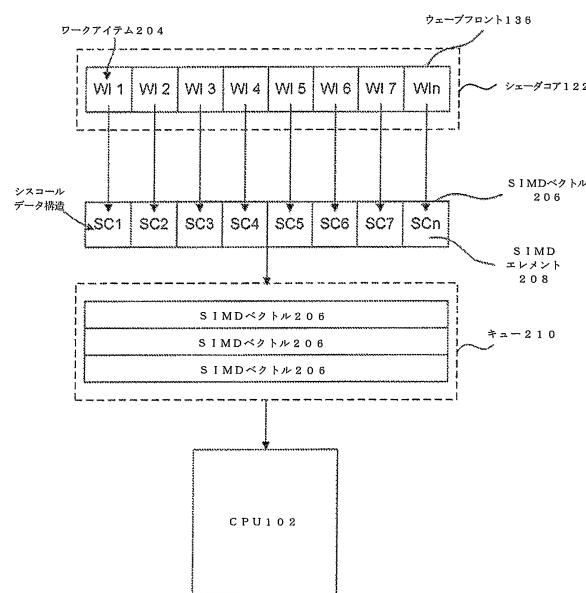

図 2 は、APD と CPU との間のシスコール要求についての最適化された通信プロセスの例示的ブロック図 200 である。ブロック図 200 は、ウェーブフロント 136 と、SIMD ベクトル 208 と、キューブ 210 とを含む。

#### 【0078】

ウェーブフロント 136 は、シェーダコア 122 によって順次処理される。各ウェーブフロントは、複数のワークアイテム 204 を含む。各ワークアイテム 204 には、処理すべきタスクまたは上記タスクの一部が割り当てられている。シェーダコア 122 は、ウェーブフロント 136 内のワークアイテム 204 を、並列に、且つ、同一の 1 組の命令と共に処理する。その結果、ウェーブフロント 136 内の各ワークアイテム 204 は、シスコ

50

ールをCPU102に同時に発行し得る。

#### 【0079】

APDが、各ワークアイテムからのシスコール要求をCPUに個別に送る構成である従来のシステムとは対照的に、APD104は、SIMDベクトル206を用いて要求を送るため、シスコール要求を单一データ構造としてまとめることが可能になる。SIMDベクトル206は、SIMDエレメント208を含む。各SIMDエレメントは、シスコールデータ構造を含む。シスコールデータ構造は、関数セレクタパラメータ（特定のシスコール要求）と、引数リストと、シスコール要求結果をAPD104へ返送するためのメモリ空間とを含む。本明細書では、一実施形態として例示的なシスコールデータ構造について説明する。

10

#### 【0080】

OSを必要とするプロセスがワークアイテム204から要求された場合には、APD104は、各ワークアイテム204からのシスコール要求を、対応するSIMDエレメント208に記憶する。例えば、図1において、ワークアイテムWI1は、シスコールSC1を、SIMDエレメント208に記憶し、ワークアイテムWI1は、シスコールSC2を、別のSIMDエレメント208に記憶する。APD104は、各ワークアイテム204からのシスコール要求の種類を、関数セレクタパラメータ内に保存する。また、APD104は、必要であれば、引数リストを引数リスト部に挿入する。さらに、APD104は、複数のウェーブフロント136のワークアイテムからのシスコールを、1つのSIMDベクトル206に記憶し得る。

20

#### 【0081】

キュー210は、高優先度の公的メモリキューである。キューは、（ファーストインファーストアウト（FIFO）原理に従って動作する。公的キューは、CPU102およびAPD104プロセッサが認識することが可能なキューである。すなわち、先行してキューに入れられたワーカロードは、先行してキューから取り外される。また、当業者であれば、キューデータ構造を用いた例は例示目的のためであり、限定的なものではなく、他のデータ構造も利用可能であることを理解するであろう。

#### 【0082】

APD104は、SIMDベクトル206と共にキュー210にエンキューする。APD104がSIMDベクトル206をキューに入れた後、一実施形態において、APDは、CPU102がSIMDベクトル206を処理する（すなわち、SIMDベクトル206を受信し、内部に保存されているシスコールを処理し、各シスコール結果をAPD104へ送信する）まで停止して待機する。別の実施形態において、APD104がキュー210をエンキューした後、APD104は、ウェーブフロントの状態をメモリ106中に保存し、別のウェーブフロントの処理を開始する。APD104は、処理完了を示す信号をCPU102から受信すると、元のウェーブフロント136をメモリ106から取り出し、処理を回復させる。

30

#### 【0083】

CPU102は、高優先度キューから受信したタスクを、他のプロセスよりも優先して処理する。よって、CPU102は、高優先度キュー（例えば、キュー210）から要求を受信すると、現在のプロセスを保存し、上記受信した要求を処理する。本明細書中に記載される高優先度公的キューの例は、例示的なものであり、限定的なものではなく、当業者であれば、他のメモリ保存構造も利用可能であることを理解するであろう。

40

#### 【0084】

CPU102は、SIMDベクトル206をキュー210から取り出し、SIMDエレメント208の処理を開始する。CPU102は、OSを呼び出し、各SIMDエレメント208内の関数セレクタパラメータに記憶されたシスコール要求の処理を開始する。また、CPU102は、必要であれば、SIMDエレメント208に記憶された引数リストを読み出す。CPU102は、各シスコール要求を完了した後に、その結果を、各SIMDエレメント208に割り当てられたメモリアドレスに書き込む。

50

**【0085】**

CPU102は、全ての SIMD エレメント 208 の処理を完了した後に、一実施形態において、 SIMD ベクトル 206 をキューレジスター 210 上に配置し、 SIMD ベクトル 206 を APD104 に返送する。典型的には、 CPU102 は、 SIMD ベクトル 206 を、 APD104 が認識することが可能なメモリキューレジスター 210 上に配置する。

**【0086】**

別の実施形態において、 CPU102 は、 SIMD ベクトル 206 の処理を完了すると、セマフォ機構を用いて、信号を APD104 に送る。当業者であれば、セマフォ機構を用いることにより、 APD104 が、処理要求されたシスコールを CPU102 が完了するのを待機しているときに、他のウェーブフロントを処理する事態が無くなることを理解するであろう。10

**【0087】**

APD104 は、 SIMD ベクトル 206 をキューレジスターから取り外すか、あるいはシスコールが処理された旨の信号を CPU102 から受信した後に、上記要求されたシスコールの結果を用いて、ウェーブフロント 136 の処理を開始する。APD104 が、プロセス SIMD ベクトル 206 を CPU が処理するのを待機しつつ、別のウェーブフロントを処理することが可能な実施形態において、 APD104 は、ウェーブフロント 136 を APD メモリ 130 から取り出した後に、処理を継続する。

**【0088】**

シスコールの一例として、メモリに対する要求（例えば、 `malloc()` 関数）がある。 `malloc()` 要求は、特定の処理または関数用のメモリをシステムメモリ 106 に割り当てる。APD104 は、 `malloc()` 要求を処理することができない。なぜならば、 APD104 は、 OS へのアクセスを有していないからである。そのため、 APD104 は、 `malloc()` 要求用のシスコールを、 CPU102 に送る。20

**【0089】**

APD104 は、ウェーブフロント 136 内のワークアイテム 204 がメモリを要求した場合に、 `malloc()` 要求を発行する。従来のシステムの場合、 APD が個別の `malloc()` 要求を各ワークアイテムから CPU に送る従来のシステムとは異なり、 APD104 は、ウェーブフロント 136 内のワーキングアイテム 204 ごとの `malloc()` 要求を含む 1 つの SIMD ベクトル 206 を、 CPU102 に送る。APD104 は、 `malloc()` 要求に必要な情報を、対応する SIMD エレメント 208 にワークアイテムごとに記憶する。上記必要な情報は、関数セレクタと、引数リストと、空パラメータとを含む。上記関数セレクタは、 `malloc()` 関数に対するメモリアドレスである。上記引数リストは、 CPU102 が各ワークアイテム 204 に割りあてることが必要なメモリサイズを含む。CPU102 は、上記割りあてられた空間のアドレスを、上記空パラメータに記憶する。30

**【0090】**

各ワークアイテムが、各シスコールの処理に必要な `malloc()` パラメータを含んだ後に、 APD104 は、本明細書に記載のように、 SIMD ベクトル 206 をキューレジスター 210 上に配置する。CPU102 は、 SIMD ベクトル 206 をキューレジスター 210 から取り出して、 SIMD エレメント 208 の処理を開始する。CPU102 が、 SIMD ベクトル 206 内の `malloc()` 要求を処理すると、 CPU102 は、 OS に対して 1 つのコールを発行する。その後、 CPU102 は、上記コールのワークアイテム 204 ごとのメモリを、 OS に割り当てる。その後、 CPU102 は、 SIMD エレメント 208 内のワークアイテム 204 ごとに割りあてられたメモリ空間に、アドレスを記憶する。CPU102 は、全てのシスコール要求を完了した後に、 SIMD ベクトル 206 を APD104 に返送する。40

**【0091】**

SIMD エレメント 208 は、シスコールを CPU102 へ送るための複数の構造を含む。一実施形態において、各 SIMD エレメント 208 は、関数セレクタパラメータと、50

引数リストと、シスコールの結果とを記憶するためのデータ構造を含み得る。非限定的な例において、例示的なデータ構造を以下に示す。

```

struct MyTask {

MyPtr _myCodePtr

myCPUCodePtr : pointer to code (e.g., x86 binary format)

myAPDCodePtr :

//GPR usage in kernel

//LDS required by kernel

//Pointer to code (e.g., shader binary format)

//other parameters

MyPtr _myDataPtr :

myExecRange:

//Global grid dimensions

//Local grid dimensions

myArgSize

myArgs {(variable size)}

MyNotification

//Notification mechanism

}

```

#### 【0092】

上記の MyTask 構造は、APD104 上の命令処理のための MyPtr myAPDCodePtr ポインタと、CPU102 上の命令処理のための MyPtr myCPUCodePtr ポインタと、データポインタである MyPtr \_myDataPtr を含む。ワークアイテム204が、CPU102からのシスコールを要求すると、myAPDCodePtr ポインタおよび myCPUCodePtr ポインタが、特定のシスコール機能のメモリアドレスをポイントする。上記 myDataPtr ポインタは、引数リスト用のパラメータと、各シスコール結果を含むメインメモリ106内のメモリアドレスへのポインタとを含む。

#### 【0093】

さらに、MyTask 構造は、MyNotification 機構を含む。APD104 は、上記通知機構を用いて、処理を必要とする MyTask がキュー110 に存在していることを、CPU102 に通知する。同様に、CPU102 は、MyNotification を用いて、CPU102 によるシスコール処理が完了したことを、APD104 に通知する。

#### 【0094】

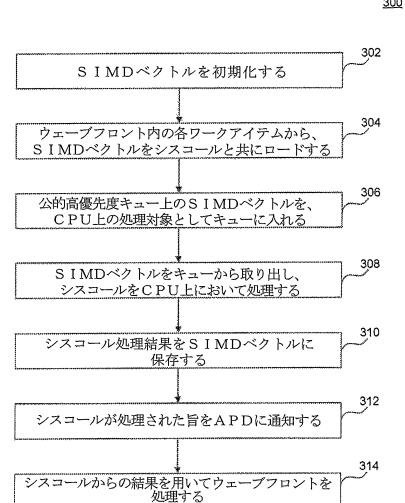

図3は、SIMDベクトル206を用いてシスコール要求を処理するシステム100の例示的なフローチャート200である。ステップ302において、ウェーブフロント136内のワークアイテム204が、CPU102を用いた処理を必要とするシスコールを要求した場合に、APD104は、SIMDベクトル206を初期化する。ステップ304において、各ワークアイテム204は、本明細書に記載のように、シスコール要求の処理に必要な情報を、対応する SIMD エレメント 208 に記憶する。ステップ306において、APD104は、SIMDベクトル206をキュー210にエンキューする。ステップ308において、CPU102は、SIMDベクトル206をキュー210から取り出す。CPU102は、SIMDベクトル206をキューから取り出した後に、OSを呼び出し、各 SIMD エレメント 208 内のシスコールの処理を開始する。

#### 【0095】

ステップ310において、CPU102は、各シスコールの結果を SIMD エレメント 208 に書き込む。当業者であれば、ステップ310を、ステップ308と共に実行することが可能であることを理解するであろう。ステップ312において、CPU102は、シスコール処理が完了したことを APD104 に通知する。一実施形態において、CPU

10

20

30

40

50

102は、APD104が認識することが可能なキー210を用いて、SIMDベクトル206をAPD104に返送する。別の実施形態において、CPU102は、セマフォを用いて、信号をAPD104に送信する。ステップ314において、APD104は、SIMDベクトル206をキー210から取り出し、ウェーブフロント136の処理を継続する。

#### 【0096】

本発明の様々な態様は、ソフトウェア、ファームウェア、ハードウェアまたはこれらの組み合わせによって実装することが可能である。例えば、図3のフローチャート300によって示す方法を、図1の統一コンピューティングシステム100において実行することが可能である。本発明の多様な実施形態について、本例の統一コンピューティングシステム100を用いて説明する。他のコンピュータシステムおよび/またはコンピューターアーキテクチャを用いて本発明を実行するための方法が、当業者にとって明らかである。10

#### 【0097】

本文書において、「コンピュータプログラム媒体」とおよび「コンピュータで利用可能な媒体」とは、例えばリムーバブルストレージユニットやハードディスクドライブなどの媒体を主に指す。また、コンピュータプログラム媒体およびコンピュータで利用可能な媒体は、メモリ（例えば、システムメモリ106およびグラフィックスメモリ130）を指す。上記メモリは、メモリ半導体（例えば、DRAM）であり得る。これらのコンピュータプログラム製品は、ソフトウェアを統一コンピューティングシステム100に提供するための手段である。20

#### 【0098】

本発明は、任意のコンピュータで利用可能な媒体に記憶されたソフトウェアを含むコンピュータプログラム製品にも関する。このようなソフトウェアが1つ以上のデータ処理デバイスにおいて実行された場合、データ処理デバイス（単数または複数）は、本明細書にて記載したように動作し、コンピューティングデバイス（例えば、ASICまたはプロセッサ）の合成および/または製造を許容して、本明細書に記載の本発明の実施形態の実行が可能となる。本発明の実施形態において、現在公知であるかまたは将来において公知となるコンピュータで利用可能な媒体、またはコンピュータで読み出し可能な媒体がすべて用いられる。コンピュータで利用可能な媒体の例を非限定的に挙げると、一次記憶デバイス（例えば、任意の種類のランダムアクセスメモリ）、二次記憶デバイス（例えば、ハードドライブ、フロッピー（登録商標）ディスク、CD-ROM、ZIPディスク、テープ、磁気記憶デバイス、光学記憶デバイス、MEMS、ナノ技術記憶デバイス）ならびに通信媒体（例えば、有線通信ネットワークおよび無線通信ネットワーク、ローカルエリアネットワーク、広域ネットワーク、インターネット）がある。30

#### 【0099】

本発明の多様な実施形態について上記において説明してきたが、これらの実施形態はひとえに例示的なものであり、制限的なものではないことが理解されるべきである。当業者であれば、これらの実施形態において、形態および詳細における多様な変更が（添付の特許請求の範囲に記載のような本発明の意図および範囲から逸脱することなく）可能であることを理解する。本発明はこれらの例に限定されないことが理解されるべきである。本発明は、本明細書中に記載のように動作する要素に適用することが可能である。よって、本発明の範囲は、上記した例示的実施形態のいずれによても限定されるべきではなく、以下の特許請求の範囲およびその均等物によって規定されるべきものである。40

【図 1 A】

【 図 1 B 】

【 図 2 】

【 図 3 】

---

フロントページの続き

早期審査対象出願

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ベンジャミン トーマス サンダー

アメリカ合衆国 78735 テキサス州、オースティン、メディシン クリーク 5701

(72)発明者 マイケル ヒューストン

アメリカ合衆国 95014 カリフォルニア州、クパチーノ、コロンバス アベニュー 213

30

(72)発明者 ニュートン チェン

アメリカ合衆国 94088 カリフォルニア州、サンベイル、ワン・エイ・エム・ディ・プレ

イス

(72)発明者 キース ローリー

アメリカ合衆国 98011 ワシントン州、ボセル、ノースイースト 197番 ストリート

10910

合議体

審判長 高木 進

審判官 辻本 泰隆

審判官 石井 茂和

(56)参考文献 特開2009-140491(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F9/46-9/54