(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4639162号

(P4639162)

(45) 発行日 平成23年2月23日(2011.2.23)

(24) 登録日 平成22年12月3日(2010.12.3)

(51) Int.CI.

H03M 1/08 (2006.01)

F 1

H03M 1/08

A

請求項の数 3 (全 7 頁)

(21) 出願番号 特願2006-103335 (P2006-103335)

(22) 出願日 平成18年4月4日 (2006.4.4)

(65) 公開番号 特開2007-281695 (P2007-281695A)

(43) 公開日 平成19年10月25日 (2007.10.25)

審査請求日 平成20年8月13日 (2008.8.13)

(73) 特許権者 308033711

OKIセミコンダクタ株式会社

東京都八王子市東浅川町550番地1

(73) 特許権者 591049893

株式会社 沖マイクロデザイン

宮崎県宮崎郡清武町大字木原7083番地

(74) 代理人 100086807

弁理士 柿本 恒成

(72) 発明者 河野 治美

宮崎県宮崎郡清武町大字木原7083番地

株式会社 沖マイクロデザイン内

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】アナログ・デジタル変換器

## (57) 【特許請求の範囲】

## 【請求項 1】

入力ノードに与えられるアナログ電圧を保持するキャパシタと、電源電位と接地電位の間に接続されて比較用の複数の電位を生成する抵抗分圧器と、前記複数の電位の中の1つを選択信号に従って出力するスイッチと、所定の論理に従って前記選択信号を生成して前記スイッチに与え、該スイッチから出力される電位と前記キャパシタに保持された前記入力ノードの電位を順次比較して前記アナログ電圧に対応するデジタル値を出力する比較制御部とを備えたアナログ・デジタル変換器において、

前記キャパシタは、一端が前記入力ノードに接続され他端が前記抵抗分圧器の中点に接続されたことを特徴とするアナログ・デジタル変換器。

## 【請求項 2】

入力ノードに与えられるアナログ電圧を保持するキャパシタと、電源電位と接地電位の間に接続されて比較用の複数の電位を生成する抵抗分圧器と、前記複数の電位の中の1つを選択信号に従って出力するスイッチと、所定の論理に従って前記選択信号を生成して前記スイッチに与え、該スイッチから出力される電位と前記キャパシタに保持された前記入力ノードの電位を順次比較して前記アナログ電圧に対応するデジタル値を出力する比較制御部とを備えたアナログ・デジタル変換器において、

前記電源電位と接地電位の間に接続されて中点から該電源電位と接地電位の中間電位を出力する第2の抵抗分圧器を設けると共に、

前記キャパシタの一端を前記入力ノードに接続し、他端を前記第2の抵抗分圧器の中点

に接続したことを特徴とするアナログ・ディジタル変換器。

**【請求項 3】**

前記アナログ・ディジタル変換器は、前記電源電位と接地電位が与えられる電源端子から電源が供給される論理回路ブロックを有することを特徴とする請求項 1 または 2 記載のアナログ・ディジタル変換器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、LSI（大規模集積回路）に内蔵されるアナログ・ディジタル変換器（以下、「ADC」という）に関するものである。 10

**【背景技術】**

**【0002】**

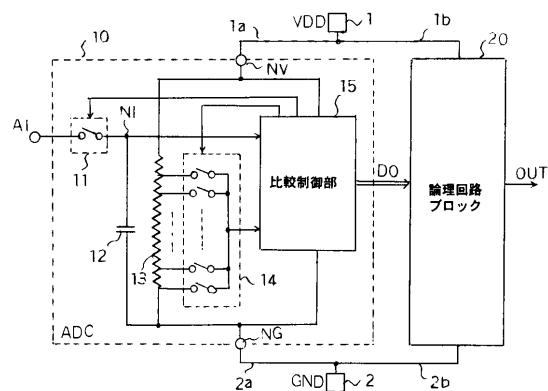

図2は、従来のADCを有するLSIの構成図である。

このLSIは、アナログ入力信号AIをデジタル信号DOに変換するADC10と、このデジタル信号DOに従って論理演算処理を行って出力信号OUTを出力する論理回路ブロック20を有し、これらのADC10と論理回路ブロック20は、共通の電源端子1と接地端子2に接続され、この電源端子1から供給される電源電圧VDDで駆動されるようになっている。

**【0003】**

このADC10は、アナログ入力信号AIをキャパシタに保持し、この保持した電圧を順次切り替えられる基準電圧と比較してデジタル信号DOに変換する逐次比較型の変換器である。アナログ入力信号AIは、サンプリング用のスイッチ11を介して内部ノードN1に与えられるようになっており、この内部ノードNIと接地ノードNGの間に入力電圧ホールド用のキャパシタ12が接続されている。一方、電源ノードNVと接地ノードNGの間には、複数の基準電圧を生成するための抵抗分圧器13が接続され、この抵抗分圧器13から出力される複数の基準電圧は、スイッチ14でいずれか1つが選択されて比較制御部15に与えられるようになっている。 20

**【0004】**

比較制御部15は、スイッチ14で選択された基準電圧とキャパシタ12に保持された内部ノードNIの電圧とを比較し、この比較結果に応じてスイッチ14を順次切り替え、アナログ入力信号AIに対応するデジタル信号DOを生成するものである。 30

**【0005】**

このADC10では、抵抗分圧器13の一端と比較制御部15の電源電位側が電源ノードNVに接続され、更にこの電源ノードNVが電源配線1aを介してLSIの電源端子1に接続されている。また、キャパシタ12と抵抗分圧器13の他端と比較制御部15の接地電位側が接地ノードNGに接続され、この接地ノードNGが接地配線2aを介してLSIの接地端子2に接続されている。

**【0006】**

一方、論理回路ブロック20は、電源電位側が電源配線1bを介してLSIの電源端子1に接続され、接地電位側が接地配線2bを介して接地端子2に接続されている。 40

**【0007】**

なお、下記特許文献1には、複数の比較器を用いてそれぞれアナログ入力電圧を異なる基準電圧と比較してデジタル値を出力する並列比較型のADCにおいて、基準電圧差が小さい比較器間で雑音によってデジタル出力が不安定になることを防止するために、各比較器に対する電源／接地の配線を分離するように構成したものが記載されている。

**【0008】**

**【特許文献1】特開平9-55661号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0009】**

しかしながら、前記ADC10では、次のような課題があった。

ADC10が変換動作中であっても、論理回路ブロック20は動作しているため、その動作時のスイッチングノイズが微小ではあるが発生する。このノイズは、電源配線1b, 1aを通してADC10の電源ノードNVに伝搬されると共に、接地配線2b, 2aを通してこのADC10の接地ノードNGに伝搬される。

#### 【0010】

接地ノードNGには、キャパシタ12の一端が接続されているので、この接地ノードNGにノイズが伝搬されると、このキャパシタ12を介して内部ノードNIの電位が変動する。このため、比較制御部15から出力されるデジタル信号DOに誤差が生ずるという問題があった。

10

#### 【0011】

この種の問題の対策の1つとしては、特許文献1の応用として考えられるように、ADC10と論理回路ブロック20の電源/接地の配線を分離する方法があるが、電源端子や接地端子が増加し、LSIの外部接続用のピンの数が増えると共に、このLSIを実装する配線ボードの配線も複雑になるという問題があった。

#### 【0012】

本発明は、電源/接地の配線を分離せずに、論理回路ブロックから発生する雑音の影響を抑制することができるADCを提供することを目的としている。

#### 【課題を解決するための手段】

#### 【0013】

20

本発明は、入力ノードに与えられるアナログ電圧を保持するキャパシタと、電源電位と接地電位の間に接続されて比較用の複数の電位を生成する抵抗分圧器と、前記複数の電位の中の1つを選択信号に従って出力するスイッチと、所定の論理に従って前記選択信号を生成して前記スイッチに与え、該スイッチから出力される電位と前記キャパシタに保持された前記入力ノードの電位を順次比較して前記アナログ電圧に対応するデジタル値を出力する比較制御部とを備えたADCにおいて、前記キャパシタは、一端が前記入力ノードに接続され他端が前記抵抗分圧器の中点に接続されたことを特徴としている。

#### 【発明の効果】

#### 【0014】

30

本発明では、入力ノードに与えられるアナログ電圧を保持するキャパシタの他端を、電源電位と接地電位の間に接続されて比較用の複数の電位を生成する抵抗分圧器の中点に接続している。電源電位と接地電位の中点の電位は、論理回路ブロックから発生する雑音の影響が少ないので、ADCと論理回路ブロックの電源/接地の配線を分離しなくても、論理回路ブロックの雑音の影響を抑制することができるという効果がある。

#### 【発明を実施するための最良の形態】

#### 【0015】

基準電位を生成する抵抗分圧器とは別に、電源電位と接地電位の中間電位を生成するための第2の抵抗分圧器を設け、この第2の抵抗分圧器の中点にキャパシタの他端を接続すると、論理回路ブロックの雑音だけでなく、基準電圧切り替え時の中点の電位変動による影響も抑制することができる。

40

#### 【0016】

この発明の前記並びにその他の目的と新規な特徴は、次の好ましい実施例の説明を添付図面と照らし合わせて読むと、より完全に明らかになるであろう。但し、図面は、もっぱら解説のためのものであって、この発明の範囲を限定するものではない。

#### 【実施例1】

#### 【0017】

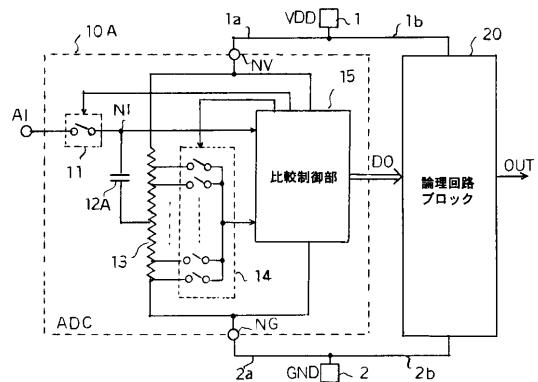

図1は、本発明の実施例1のADCを有するLSIの構成図であり、図2中の要素と共通の要素には共通の符号が付されている。

#### 【0018】

このLSIは、アナログ入力信号AIをデジタル信号DOに変換するADC10Aと

50

、このデジタル信号 D O に従って論理演算処理を行って出力信号 O U T を出力する論理回路ブロック 2 0 を有し、これらの A D C 1 0 A と論理回路ブロック 2 0 は、共通の電源端子 1 と接地端子 2 に接続され、この電源端子 1 から供給される電源電圧 V D D で駆動されるようになっている。

#### 【 0 0 1 9 】

この A D C 1 0 A は、アナログ入力信号 A I をキャパシタに保持し、この保持した電圧を順次切り替えられる基準電圧と比較してデジタル信号 D O に変換する逐次比較型の変換器である。アナログ入力信号 A I は、サンプリング用のスイッチ 1 1 を介して内部ノード N 1 に与えられるようになっており、この内部ノード N 1 に、入力電圧ホールド用のキャパシタ 1 2 A の一端が接続されている。一方、電源ノード N V と接地ノード N G の間には、複数の基準電圧を生成するための抵抗分圧器 1 3 が接続され、この抵抗分圧器 1 3 の中点（電源電位 V D D のほぼ 1 / 2 の基準電圧が出力される接続点）に、キャパシタ 1 2 A の他端が接続されている。10

#### 【 0 0 2 0 】

抵抗分圧器 1 3 から出力される複数の基準電圧は、スイッチ 1 4 でいずれか 1 つが選択されて比較制御部 1 5 に与えられるようになっている。比較制御部 1 5 は、スイッチ 1 4 で選択された基準電圧とキャパシタ 1 2 A に保持された内部ノード N 1 の電圧とを比較し、この比較結果に応じてスイッチ 1 4 を順次切り替えて、アナログ入力信号 A I に対応するデジタル信号 D O を生成するものである。比較制御部 1 5 から、スイッチ 1 1 に対するオン・オフの制御信号と、スイッチ 1 4 に対する切り替え信号が出力されるようになっている。20

#### 【 0 0 2 1 】

この A D C 1 0 A では、抵抗分圧器 1 3 の一端と比較制御部 1 5 の電源電位側が電源ノード N V に接続され、更にこの電源ノード N V が電源配線 1 a を介して L S I の電源端子 1 に接続されている。また、抵抗分圧器 1 3 の他端と比較制御部 1 5 の接地電位側が接地ノード N G に接続され、この接地ノード N G が接地配線 2 a を介して L S I の接地端子 2 に接続されている。一方、論理回路ブロック 2 0 は、電源電位側が電源配線 1 b を介して L S I の電源端子 1 に接続され、接地電位側が接地配線 2 b を介して接地端子 2 に接続されている。30

#### 【 0 0 2 2 】

この L S I における A D C 1 0 A のアナログ・デジタル変換動作は、本発明のテーマではないので詳細は省略するが、概略の動作例は次の通りである。

#### 【 0 0 2 3 】

まず、サンプリング期間に、比較制御部 1 5 の制御信号によってスイッチ 1 1 を閉じ、内部ノード N 1 の電位がアナログ入力信号 A I と同じ値になるようにキャパシタ 1 2 A を充電した後、このスイッチ 1 1 を開く。これにより、キャパシタ 1 2 A には、サンプリング時のアナログ入力信号がホールドされる。

#### 【 0 0 2 4 】

次に、比較制御部 1 5 の制御信号によってスイッチ 1 4 を制御し、フルスケールの 1 / 2 を基準電圧として選択し、内部ノード N 1 の電位をこの基準電圧と比較する。内部ノード N 1 の電位が基準電圧よりも高ければ、フルスケールの 3 / 4 を 2 回目の基準電圧として選択し、内部ノード N 1 の電位をこの 2 回目の基準電圧と比較する。このように、比較する電位の範囲を順次半分ずつに狭めながら、内部ノード N 1 の電位の最終的な範囲を決定し、デジタル信号 D O が求められる。40

#### 【 0 0 2 5 】

一方、A D C 1 0 A におけるアナログ・デジタル変換動作に並行して、論理回路ブロック 2 0 では論理演算動作が行われる。この論理回路ブロック 2 0 の動作に伴って、L I S の電源端子 1 から接地端子 2 にスイッチング電流が流れ、このスイッチング電流によるスイッチングノイズが微小ではあるが発生する。このノイズは、電源配線 1 b , 1 a を通して A D C 1 0 の電源ノード N V に伝搬されると共に、接地配線 2 b , 2 a を通してこの50

A D C 1 0 の接地ノード N G に伝搬される。

【 0 0 2 6 】

一般的に、電源ノード N V と接地ノード N G に発生するノイズは逆極性になる傾向がある。これは、電流が大きくなると配線抵抗による電圧降下が大きくなり、電源ノード N V の電位が低下すると共に、接地ノード N G の電位が上昇するためである。

【 0 0 2 7 】

従って、A D C 1 0 の電源ノード N V と接地ノード N G の間に接続された抵抗分圧器 1 3 の中点の電位は、ノイズの影響が相殺されてほぼ一定の電位に保持される。これにより、この抵抗分圧器 1 3 の中点にキャパシタ 1 2 A を介して接続された中間ノード N I の電位も、ほぼ一定の電位に保持される。

10

【 0 0 2 8 】

以上のように、この実施例 1 の A D C は、サンプリングした電位を保持するためのキャパシタ 1 2 A の他端を抵抗分圧器 1 3 の中点に接続しているので、電源端子 1 や接地端子 2 とその配線を分離しなくても、論理回路ブロック 2 0 から発生する雑音の影響を抑制することができるという利点がある。

【 実施例 2 】

【 0 0 2 9 】

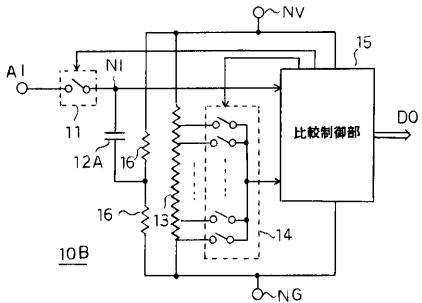

図 3 は、本発明の実施例 2 を示す A D C の構成図であり、図 2 中の要素と共に通の要素には共通の符号が付されている。

【 0 0 3 0 】

20

この A D C 1 0 B では、複数の基準電位を生成するための抵抗分圧器 1 3 の他に、電源電位 V D D と接地電位 G N D の中間電位を生成するための抵抗分圧器 1 6 を設け、この抵抗分圧器 1 6 の中点にキャパシタ 1 2 の他端を接続したものである。その他の構成は図 1 と同様である。なお、この抵抗分圧器 1 6 の全抵抗値は、抵抗分圧器 1 3 の全抵抗値の 2 ~ 3 倍に設定し、消費電流の増加を抑制するようにしている。

【 0 0 3 1 】

この実施例 2 の A D C 1 0 B の動作は、実施例 1 と同様であり、同様の利点に加えて、スイッチ 1 4 による基準電位切り替え時の影響を受けないという利点がある。

【 図面の簡単な説明 】

【 0 0 3 2 】

30

【 図 1 】本発明の実施例 1 の A D C を有する L S I の構成図である。

【 図 2 】従来の A D C を有する L S I の構成図である。

【 図 3 】本発明の実施例 2 を示す A D C の構成図である。

【 符号の説明 】

【 0 0 3 3 】

1 0 A , 1 0 B A D C

1 1 , 1 4 スイッチ

1 2 A キャパシタ

1 3 , 1 6 抵抗分圧器

1 5 比較制御部

40

【図1】

本発明の実施例1のADCを有するLSI

【図2】

従来のADCを有するLSI

【図3】

本発明の実施例2のADC

---

フロントページの続き

(56)参考文献 特開平8-298462(JP,A)

特開平9-55661(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M1/00-1/88