US009906746B2

(12) **United States Patent**

**Kondo**

(10) **Patent No.:** **US 9,906,746 B2**

(45) **Date of Patent:** **Feb. 27, 2018**

(54) **SOLID-STATE IMAGE PICKUP DEVICE AND IMAGE PICKUP APPARATUS**

(71) Applicant: **OLYMPUS CORPORATION**, Hachioji-shi, Tokyo (JP)

(72) Inventor: **Toru Kondo**, Hachioji (JP)

(73) Assignee: **OLYMPUS CORPORATION**, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: **15/333,700**

(22) Filed: **Oct. 25, 2016**

(65) **Prior Publication Data**

US 2017/0041565 A1 Feb. 9, 2017

**Related U.S. Application Data**

(63) Continuation of application No. PCT/JP2015/062663, filed on Apr. 27, 2015.

(30) **Foreign Application Priority Data**

May 2, 2014 (JP) ..... 2014-095478

(51) **Int. Cl.**

**H04N 5/232** (2006.01)

**H01L 27/146** (2006.01)

(Continued)

(52) **U.S. Cl.**

CPC ..... **H04N 5/3745** (2013.01); **H01L 27/1464** (2013.01); **H01L 27/14634** (2013.01);

(Continued)

(58) **Field of Classification Search**

None

See application file for complete search history.

(56) **References Cited**

**U.S. PATENT DOCUMENTS**

|                  |        |             |

|------------------|--------|-------------|

| 2013/0181316 A1  | 7/2013 | Tsukimura   |

| 2013/0182161 A1  | 7/2013 | Nakajima    |

| 2013/0229560 A1* | 9/2013 | Kondo ..... |

|                  |        | H04N 5/374  |

|                  |        | 348/308     |

**FOREIGN PATENT DOCUMENTS**

|                  |        |

|------------------|--------|

| JP 2007-228460 A | 9/2007 |

| JP 2011-135194 A | 7/2011 |

(Continued)

**OTHER PUBLICATIONS**

International Search Report dated Jun. 16, 2015, issued in counterpart application No. PCT/JP2015/062663. (2 pages).

*Primary Examiner* — Mark T Monk

(74) *Attorney, Agent, or Firm* — Westerman, Hattori, Daniels & Adrian, LLP

(57) **ABSTRACT**

A solid-state image pickup device includes: a first substrate which has a pixel part divided into a plurality of groups obtained by dividing a plurality of pixels arranged in a two-dimensional matrix into groups corresponding to each of a plurality of predetermined rows; and a second substrate including a pixel load current source corresponding to a vertical signal line to which the plurality of pixels disposed in the same column within the groups are connected, a column circuit that performs a predetermined process on a pixel signal which is output from the pixel to a corresponding vertical signal line, and a pixel for correction that outputs a pixel signal for correction for correcting the corresponding column circuit to the vertical signal line to which the corresponding column circuit is connected, for each column of the pixels belonging to the group.

**7 Claims, 17 Drawing Sheets**

(51) **Int. Cl.**

*H04N 5/3745* (2011.01)

*H04N 5/378* (2011.01)

(52) **U.S. Cl.**

CPC .. *H01L 27/14636* (2013.01); *H01L 27/14643* (2013.01); *H04N 5/23241* (2013.01); *H04N 5/23245* (2013.01); *H04N 5/23254* (2013.01); *H04N 5/378* (2013.01)

(56) **References Cited**

FOREIGN PATENT DOCUMENTS

|    |             |    |         |

|----|-------------|----|---------|

| JP | 2012-257095 | A  | 12/2012 |

| JP | 2013-168623 | A  | 8/2013  |

| JP | 2013-243781 | A  | 12/2013 |

| WO | 2013/041924 | A1 | 3/2013  |

| WO | 2014/007004 | A1 | 1/2014  |

\* cited by examiner

FIG. 2A

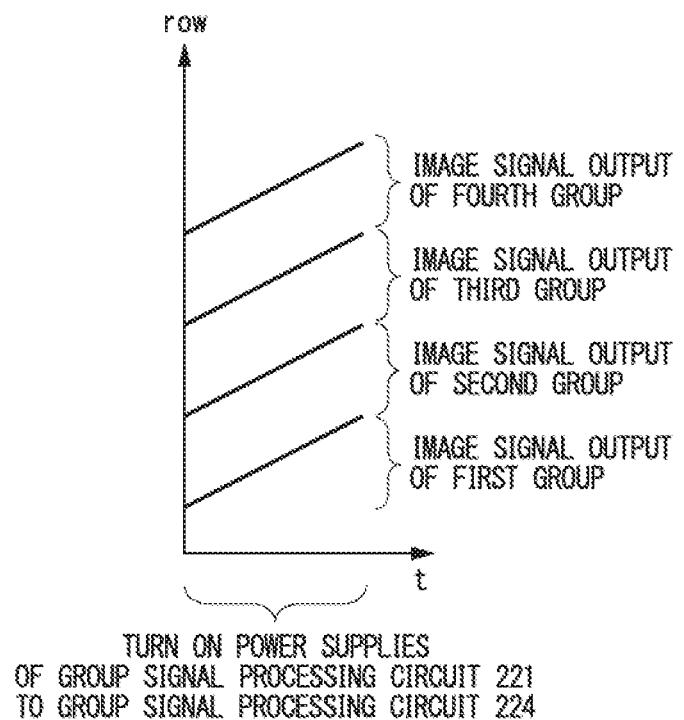

FIG. 2B

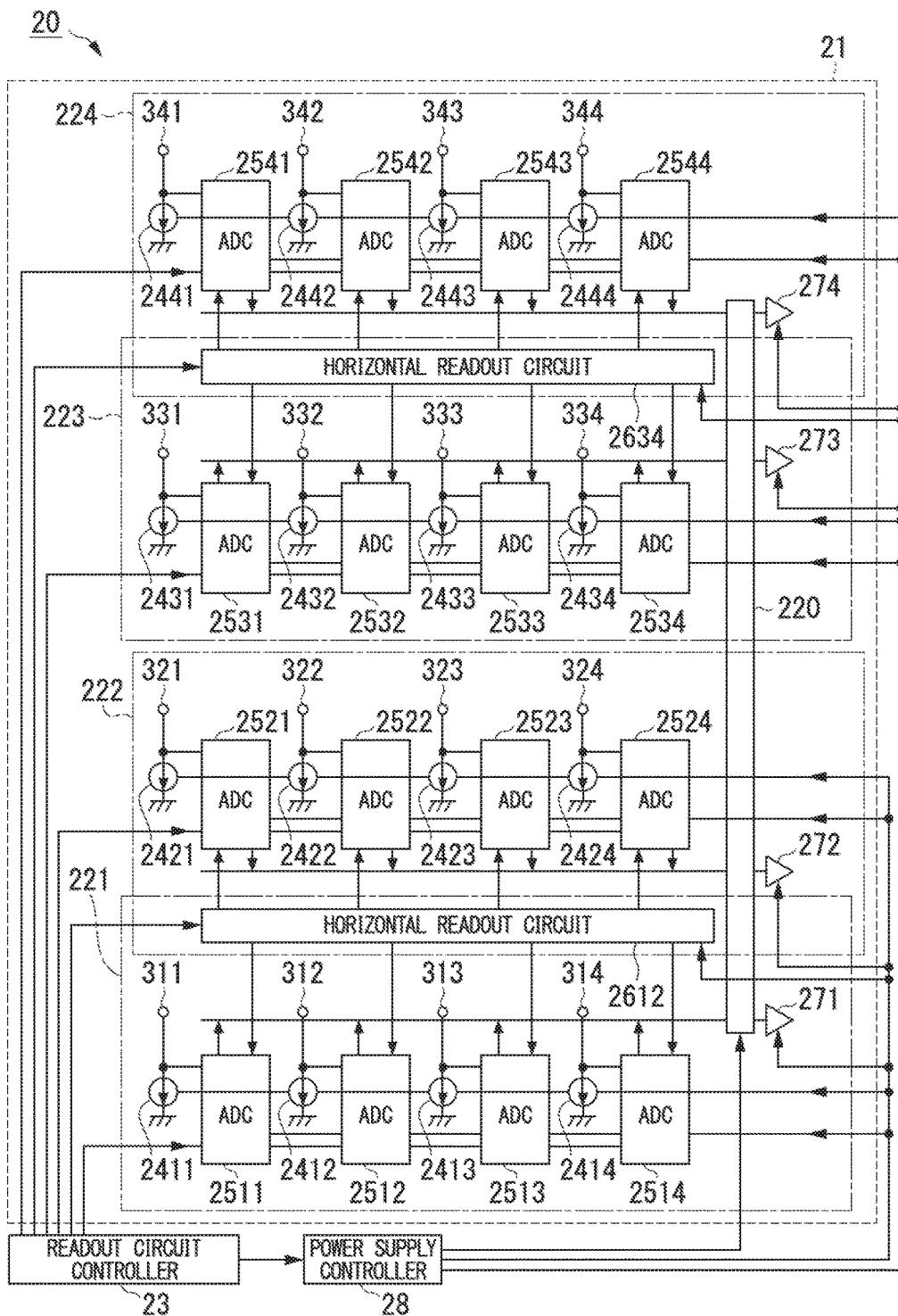

FIG. 3

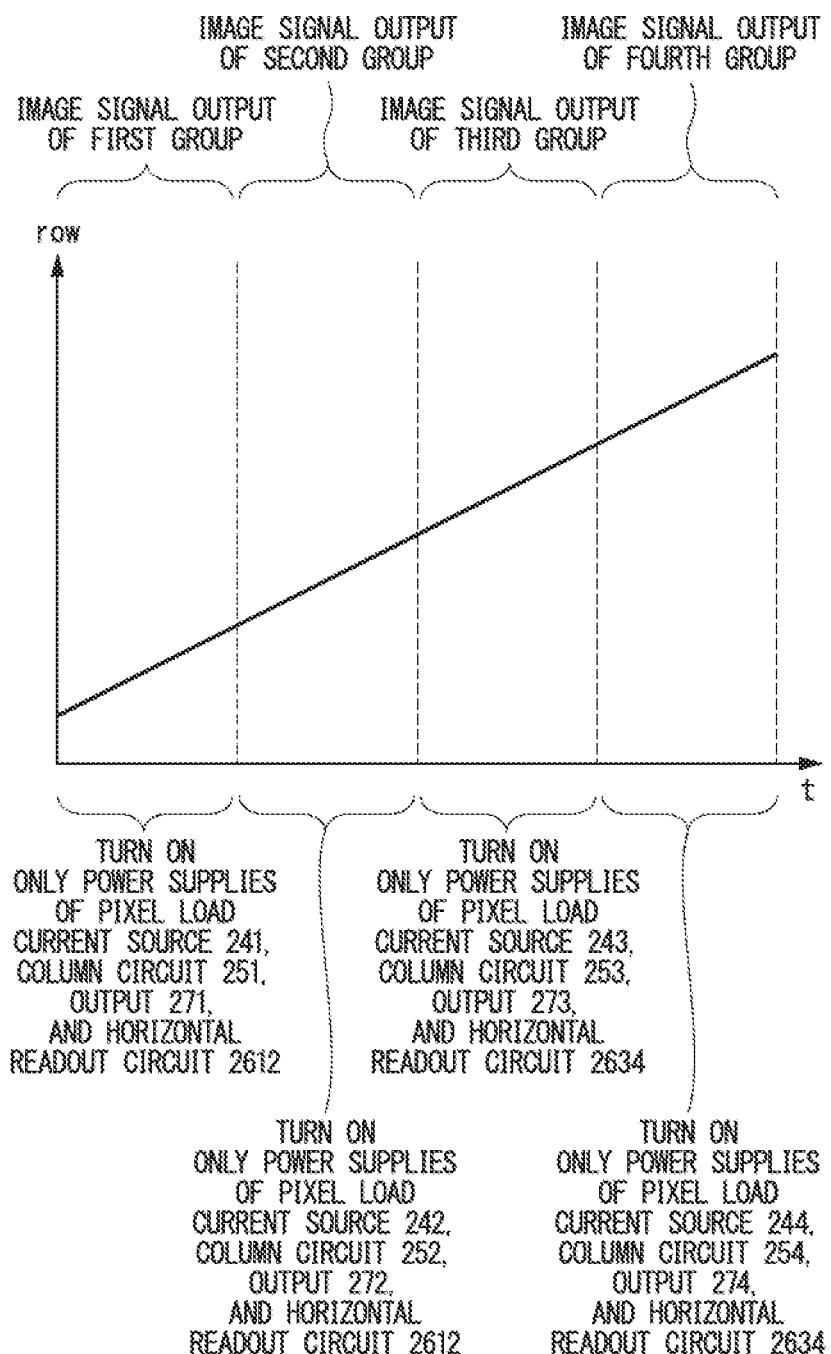

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 8

FIG. 9

FIG. 10

FIG. 11A

FIG. 11B

FIG. 11C

FIG. 12

FIG. 13A

FIG. 13B

FIG. 13C

## SOLID-STATE IMAGE PICKUP DEVICE AND IMAGE PICKUP APPARATUS

### CROSS REFERENCE TO RELATED APPLICATIONS

This application is a continuation application based on a PCT International Application No. PCT/JP2015/062663, filed on Apr. 27, 2015, whose priority is claimed on Japanese Patent Application No. 2014-095478, filed on May 2, 2014. Both of the contents of the PCT International Application and the Japanese Application are incorporated herein by reference.

### BACKGROUND OF THE INVENTION

#### Field of the Invention

The present invention relates to a solid-state image pickup device and an image pickup apparatus.

#### Description of Related Art

In recent years, image pickup apparatuses such as video cameras or electronic still cameras have generally been in widespread use. Charge coupled device (CCD)-type solid-state image pickup devices or amplification-type solid-state image pickup devices are used in these image pickup apparatuses. In the amplification-type solid-state image pickup device, a signal charge generated and accumulated by a photoelectric conversion part on which light is incident is guided to an amplification part, and a plurality of pixels that output a signal amplified by this amplification part as a pixel signal are disposed in a two-dimensional matrix.

Examples of the amplification-type solid-state image pickup device include a solid-state image pickup device using a junction-type electric field effect transistor in an amplification part, a CMOS-type solid-state image pickup device (hereinafter, also simply referred to as a "solid-state image pickup device") using a complementary metal oxide semiconductor (CMOS) transistor in an amplification part, and the like.

In addition, in recent years, the number of pixels included in the solid-state image pickup device has increased with an increase in the number of pixels and the image quality of the solid-state image pickup device. Consequently, a speed-up in readout of a pixel signal from each of the pixels included in the solid-state image pickup device has been required.

In general solid-state image pickup devices of the related art, a method of amplifying signal charge generated and accumulated by a photoelectric conversion part within each of pixels arrayed in a two-dimensional matrix, and sequentially reading out the signal charge for each row is adopted. For this reason, an increase in the number of pixels included in the solid-state image pickup device is accompanied with an increase in the number of transistors (selection parts) connected to one vertical signal line. Thereby, in the solid-state image pickup device, it takes a lot of time for the pixel signal which is read out for each row from each pixel to reach a column circuit provided for each column of the pixel, and increases power consumption. That is, an increase in the number of pixels included in the solid-state image pickup device increases the time taken to read out the pixel signal from the pixel to the column circuit, and increases the power consumption of the solid-state image pickup device.

In addition, in a case where a chip area is increased in accordance with an increase in the number of pixels included in the solid-state image pickup device, not only does a yield rate during the manufacturing of the solid-state image pickup device deteriorate, but also the capacity (wir-

ing capacity) of the vertical signal line itself increases. This increase in the capacity of the vertical signal line leads to a tendency for the readout time of the pixel signal to be further lengthened. In addition, the power consumption of the solid-state image pickup device also increases.

It is considered that the size of the pixel is reduced to cope with an increase in the number of pixels of the solid-state image pickup device. In this case, it is possible to speed up the readout of pixel signals from a large number of pixels by increasing the current value of a pixel load current source corresponding to each pixel.

Incidentally, in a case where the current value of the pixel load current source corresponding to each pixel is increased, characteristics during the readout of the pixel signal to the

vertical signal line cannot be secured without increasing the size of a transistor of the amplification part. However, in a pixel having a small size, an increase in the size of the transistor of the amplification part leads to the incapability of securing a size required for a photodiode which is a

photoelectric conversion part formed within a pixel, and thus a dynamic range or linearity is not sufficiently obtained. For this reason, it is very difficult to achieve both a reduction in the size of the pixel for coping with an increase in the number of pixels of the solid-state image pickup device and a speed-up in readout of the pixel signal from each pixel.

As a technique for solving such problems, for example, Japanese Unexamined Patent Application, First Publication No. 2013-243781 discloses a method of reducing the number of transistors (amplification parts) connected to one vertical signal line by dividing pixels included in a solid-state image pickup device into a plurality of groups. In the technique disclosed in Japanese Unexamined Patent Application, First Publication No. 2013-243781, one vertical signal line of the related art is divided into two parts by dividing the pixels included in the solid-state image pickup device into two groups. A column circuit corresponding to each of the divided vertical signal lines is provided. That is, in the technique disclosed in Japanese Unexamined Patent Application, First Publication No. 2013-243781, a set of column circuits corresponding to each column of the pixels included in the solid-state image pickup device is provided by the number of groups into which the pixels within a pixel part are divided.

With such a configuration, in the technique disclosed in Japanese Unexamined Patent Application, First Publication No. 2013-243781, the number of transistors (amplification parts) connected to each vertical signal line is reduced to  $\frac{1}{2}$ , that is, the load of the vertical signal line when a pixel signal is read out from each pixel to a column circuit is reduced, and thus the readout time of the pixel signal is shortened. In addition, in the technique disclosed in Japanese Unexamined Patent Application, First Publication No. 2013-243781, the pixel signals are read out from two groups in parallel, and thus a speed-up in readout of the pixel signal from each pixel is achieved.

### SUMMARY OF THE INVENTION

According to a first aspect of the present invention, a solid-state image pickup device is provided, including: a first substrate including a pixel part in which a plurality of pixels disposed in a two-dimensional matrix are divided into a plurality of groups forming a set for each of a plurality of rows which are set in advance; and a second substrate including pixel load current sources corresponding to vertical signal lines to which the plurality of pixels disposed in the same column within the groups are connected, and

column circuits that perform a process set in advance on a pixel signal which is output from the pixel to a corresponding vertical signal line, for each column of the pixels belonging to the group, and including a plurality of circuits that output the pixel signal processed by each of the column circuits, as an image signal, for each row of the pixels, so as to correspond to each of the groups, wherein the first substrate and the second substrate are laminated, and each of the vertical signal lines within each of the groups, and each of the pixel load current sources and the column circuits corresponding to the vertical signal line within the signal processing circuit corresponding to the group are electrically connected to each other through each inter-substrate connecting portion of the pixel load current source and the column circuit corresponding to the vertical signal line.

According to a second aspect of the present invention, in the solid-state image pickup device of the first aspect, the second substrate may further include a power supply controller that controls a power supply of a component within the signal processing circuit in accordance with an operation when the image signal is output from the solid-state image pickup device.

According to a third aspect of the present invention, in the solid-state image pickup device of the first or second aspect, the signal processing circuit may further include a pixel for correction that corresponds to each of the column circuits, and outputs a pixel signal for correction for correcting the corresponding column circuit to the vertical signal line to which the corresponding column circuit is connected.

According to a fourth aspect of the present invention, in the solid-state image pickup device of the second or third aspect, the power supply controller may set power supplies of all components within the signal processing circuit to be in an ON-state when the pixels within each of the groups are simultaneously driven, and the image signals based on the pixel signals which are output from the driven pixels are output from the solid-state image pickup device so as to be output from the signal processing circuit corresponding to each of the groups in parallel, and may set a power supply of a component within the signal processing circuit, operating in order to output the image signal, to be in an ON-state, and set a power supply of a component within the signal processing circuit, not operating in order to output the image signal, to be in an OFF-state, when each of the pixels is sequentially driven, and the image signals based on the pixel signals which are output from the driven pixels are sequentially output from the solid-state image pickup device so as to be output from the signal processing circuit corresponding to the driven pixels.

According to a fifth aspect of the present invention, in the solid-state image pickup device of the third or fourth aspect, the solid-state image pickup device may correct each of the column circuits included in each of the signal processing circuits, using the pixel signal for correction which is output by the corresponding pixel for correction, before the image signal is output from the solid-state image pickup device.

According to a sixth aspect of the present invention, in solid-state image pickup device of any one of the second to fifth aspects, the power supply controller may include an output part included in each of the signal processing circuits, and controls an ON-state and an OFF-state of a power supply of a component within the signal processing circuit.

According to a seventh aspect of the present invention, an image pickup apparatus provided with a solid-state image pickup device is provided, including: a first substrate including a pixel part in which a plurality of pixels disposed in a two-dimensional matrix are divided into a plurality of

groups forming a set for each of a plurality of rows which are set in advance; and a second substrate including pixel load current sources corresponding to vertical signal lines to which the plurality of pixels disposed in the same column within the groups are connected, and column circuits that perform a process set in advance on a pixel signal which is output from the pixel to a corresponding vertical signal line, for each column of the pixels belonging to the group, and including a plurality of signal processing circuits that output the pixel signal processed by each of the column circuits, as an image signal, for each row of the pixels, so as to correspond to each of the groups, wherein the first substrate and the second substrate are laminated, and each of the vertical signal lines within each of the groups, and each of the pixel load current sources and the column circuits corresponding to the vertical signal line within the signal processing circuit corresponding to the group are electrically connected to each other through each inter-substrate connecting portion of the pixel load current source and the column circuit corresponding to the vertical signal line.

According to an eighth aspect of the present invention, in the image pickup apparatus of the seventh aspect, the image pickup apparatus may further include a mechanical shutter that controls an amount of light incident on the solid-state image pickup device, and the light incident on the solid-state image pickup device may be blocked by the mechanical shutter when the pixels within each of the groups are simultaneously driven, and the image signals based on the pixel signals which are output from the driven pixels are output from the solid-state image pickup device so as to be output from the signal processing circuit corresponding to each of the groups in parallel.

#### BRIEF DESCRIPTION OF THE DRAWINGS

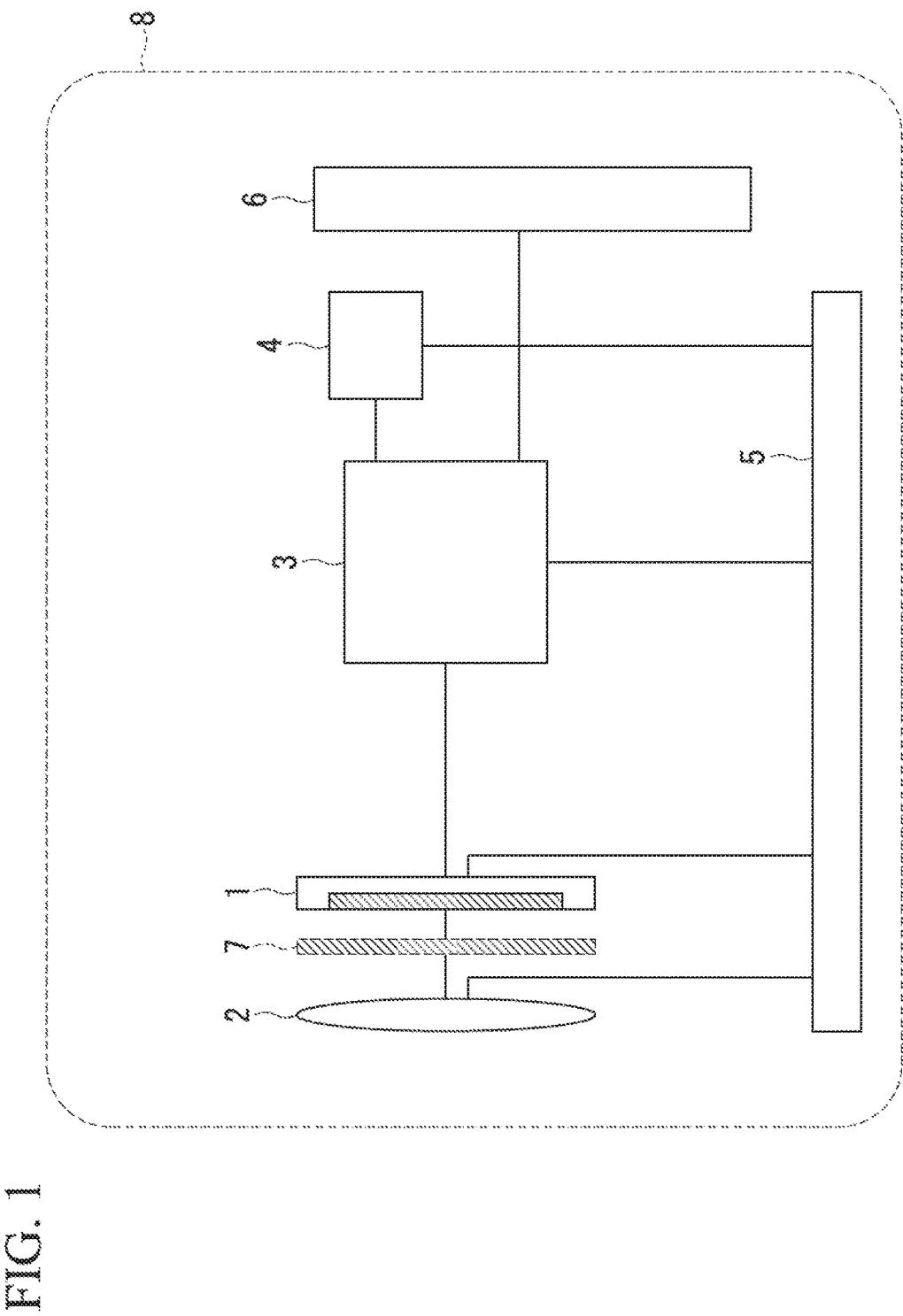

FIG. 1 is a block diagram illustrating a schematic configuration of an image pickup apparatus according to an embodiment of the present invention.

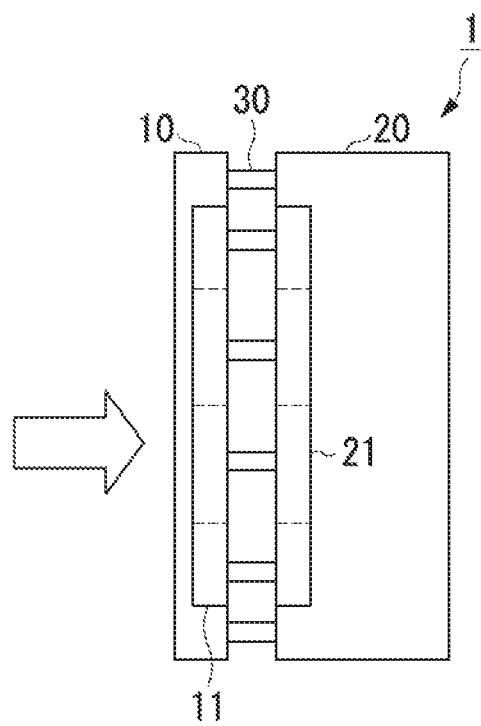

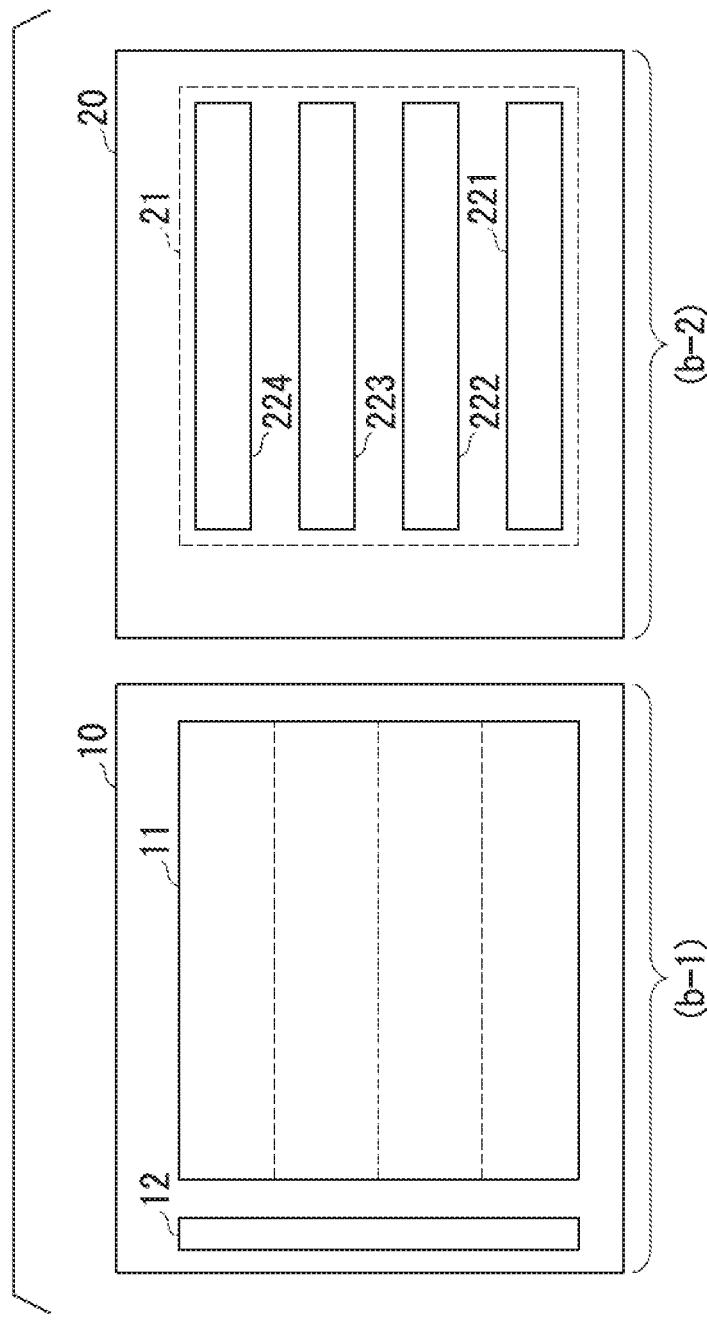

FIG. 2A is an overview diagram illustrating a schematic configuration of a solid-state image pickup device mounted in the image pickup apparatus of the present embodiment.

FIG. 2B is an overview diagram illustrating a schematic configuration of the solid-state image pickup device mounted in the image pickup apparatus of the present embodiment.

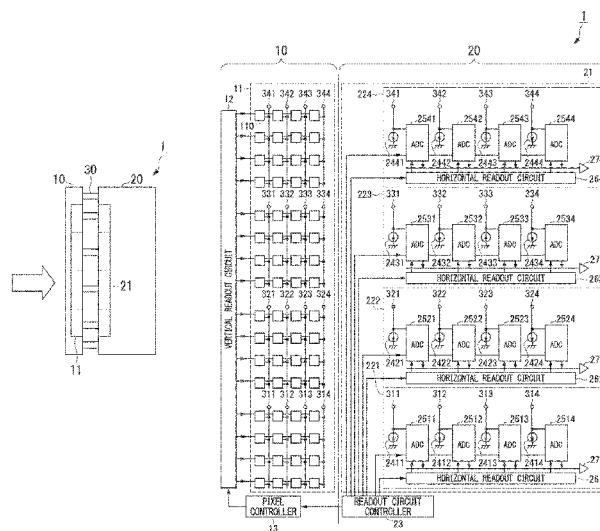

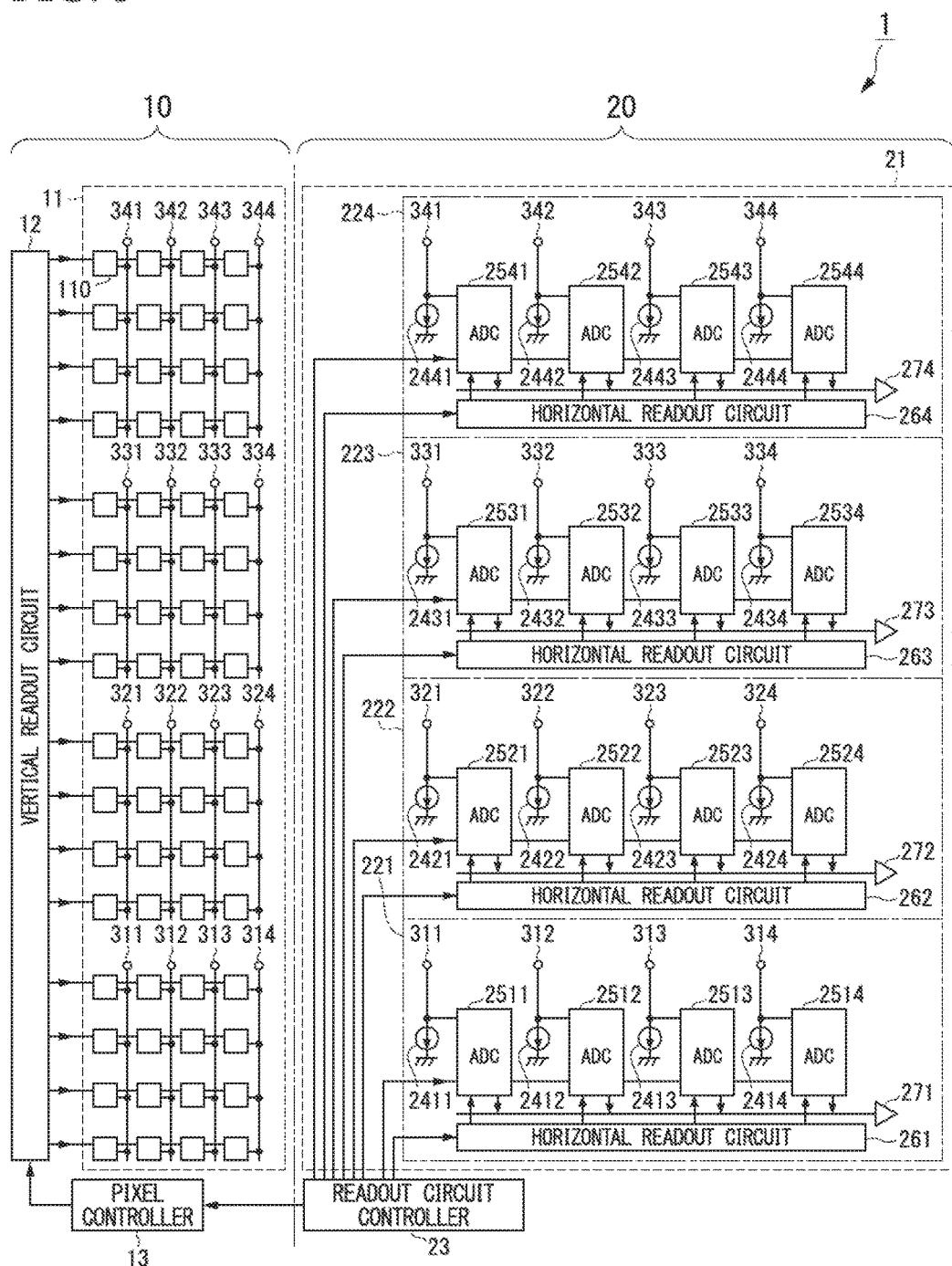

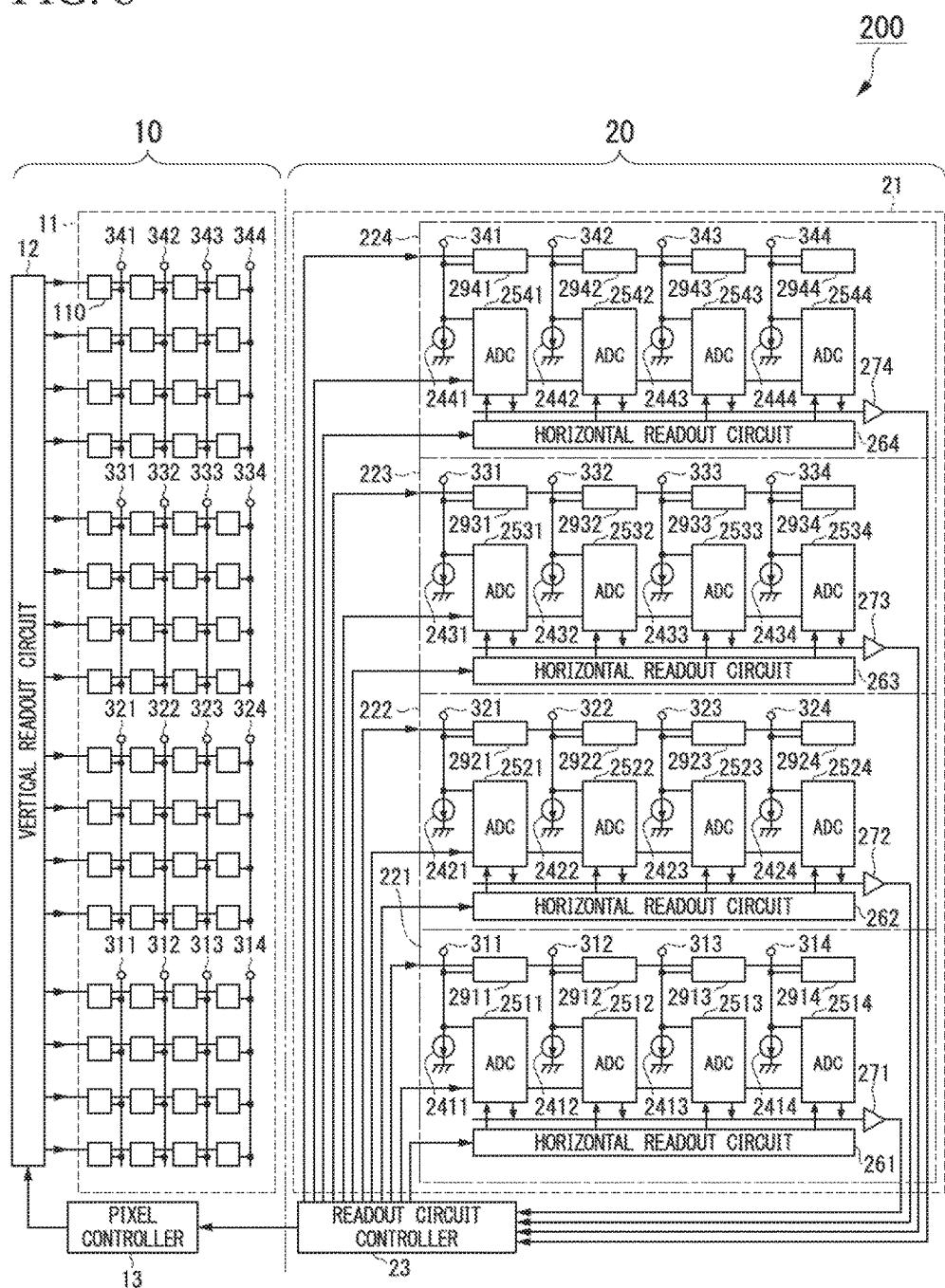

FIG. 3 is a block diagram illustrating a schematic configuration of a solid-state image pickup device according to a first embodiment of the present invention.

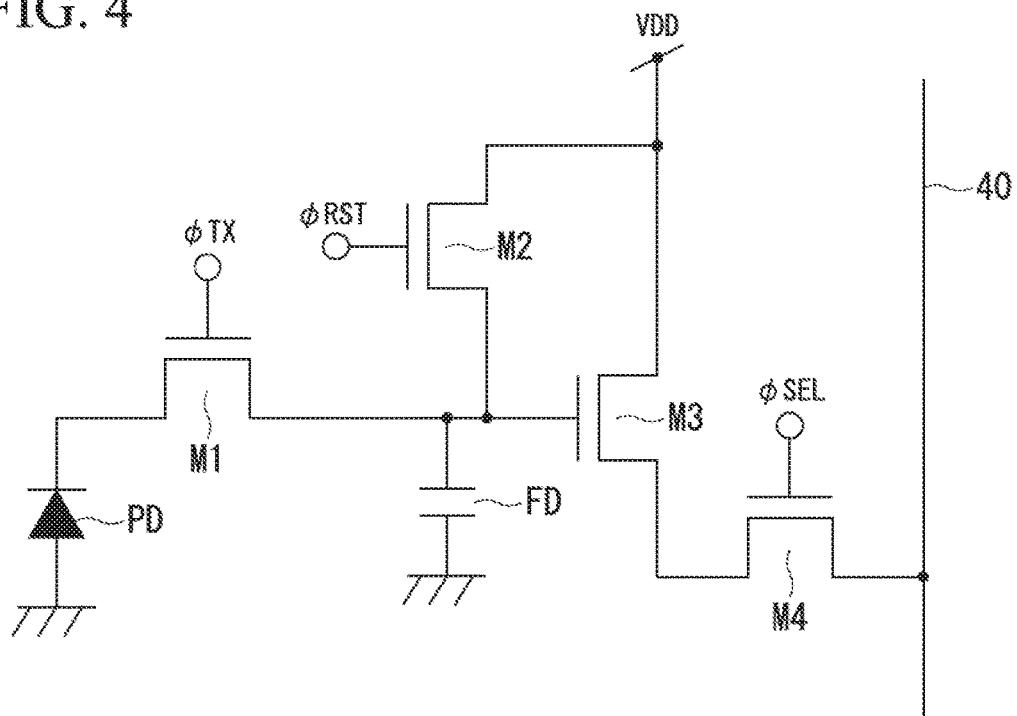

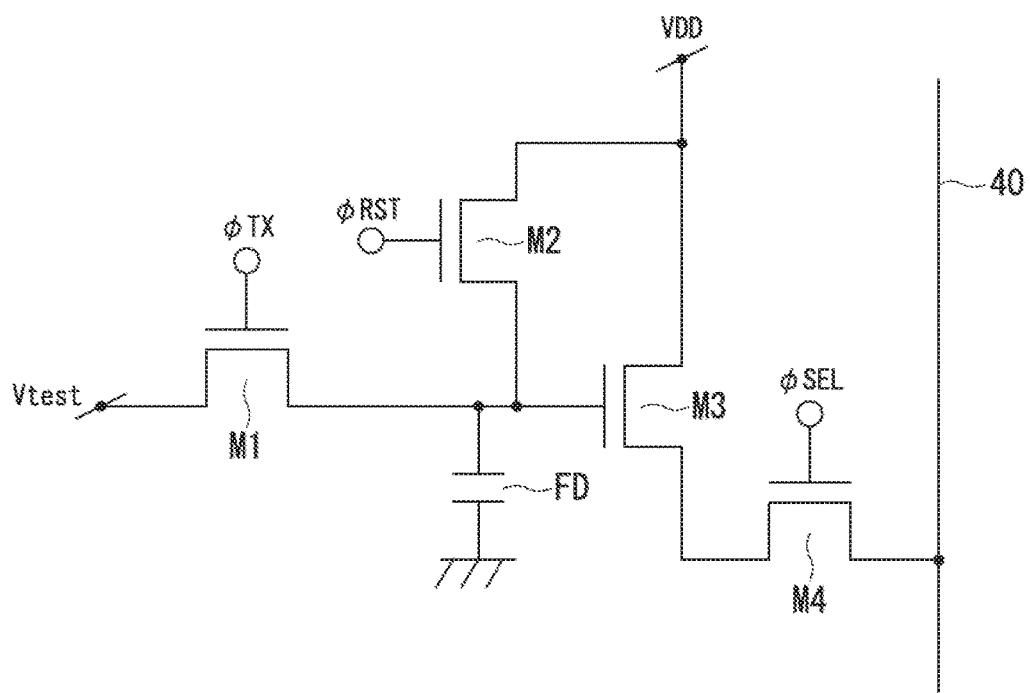

FIG. 4 is a circuit diagram illustrating a schematic configuration of a unit pixel within a pixel array part of the solid-state image pickup device of the first embodiment.

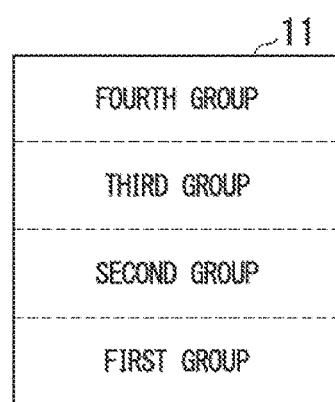

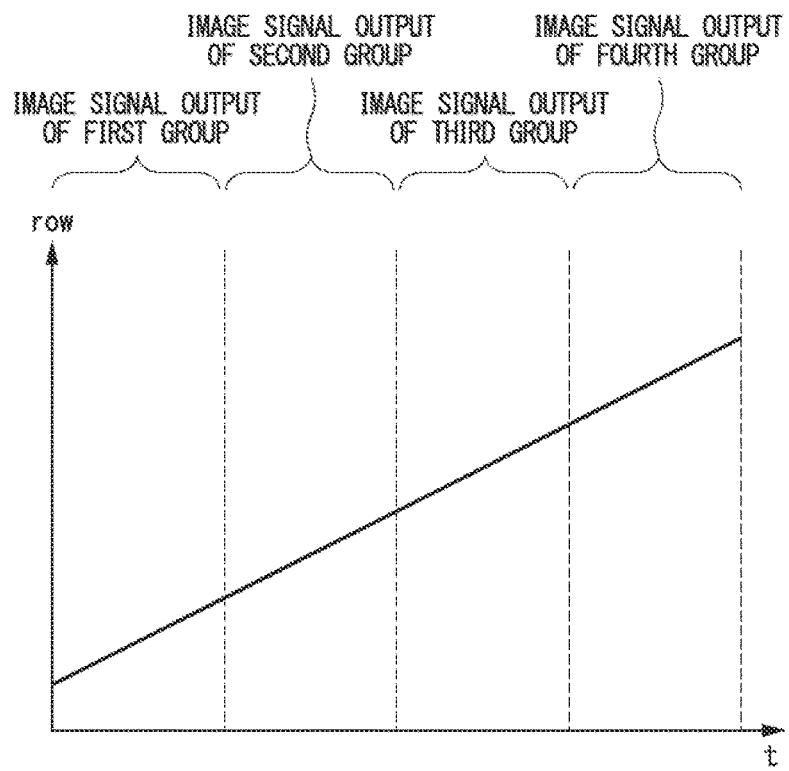

FIG. 5A is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the first embodiment.

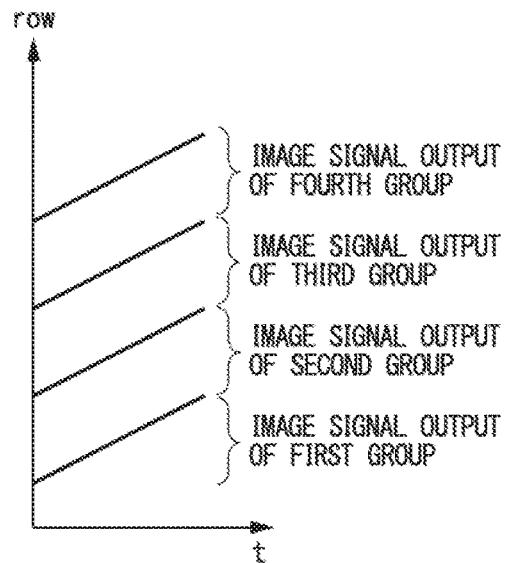

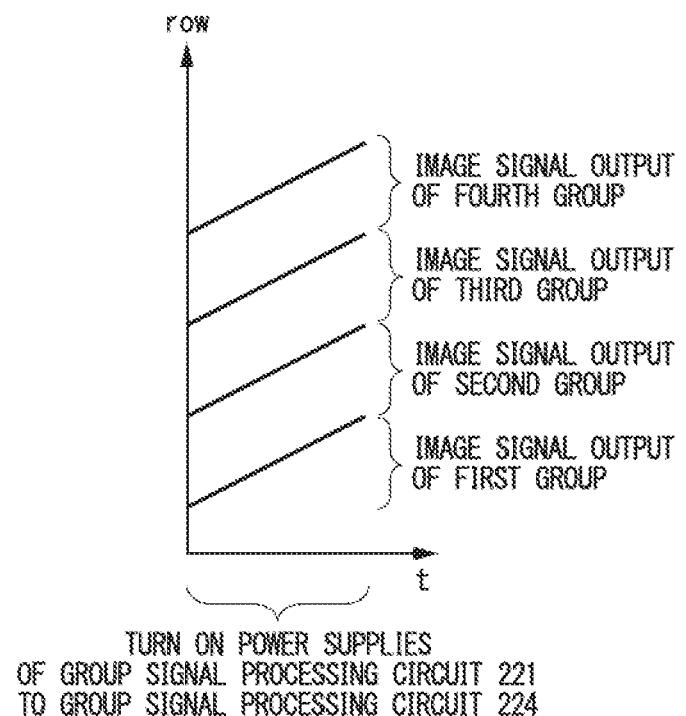

FIG. 5B is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the first embodiment.

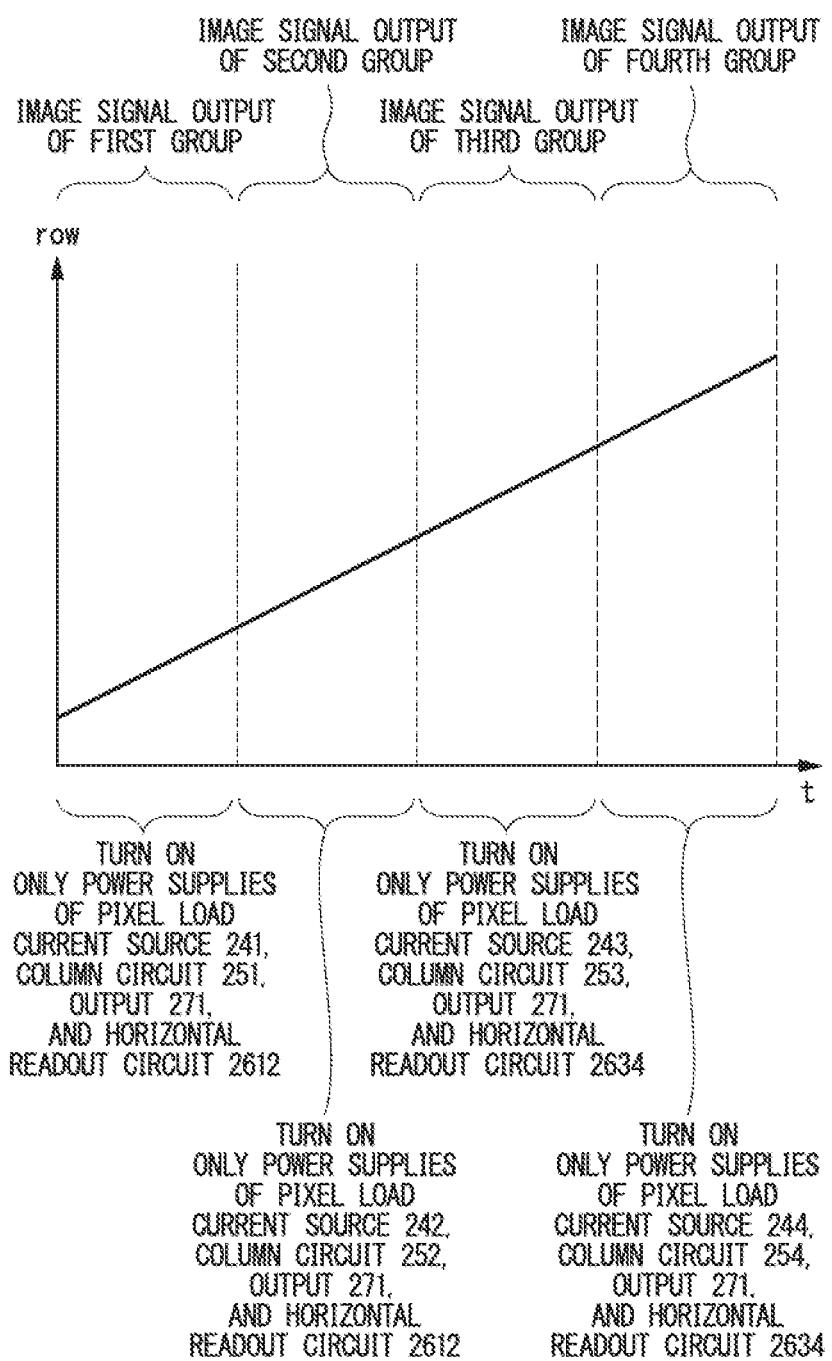

FIG. 5C is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the first embodiment.

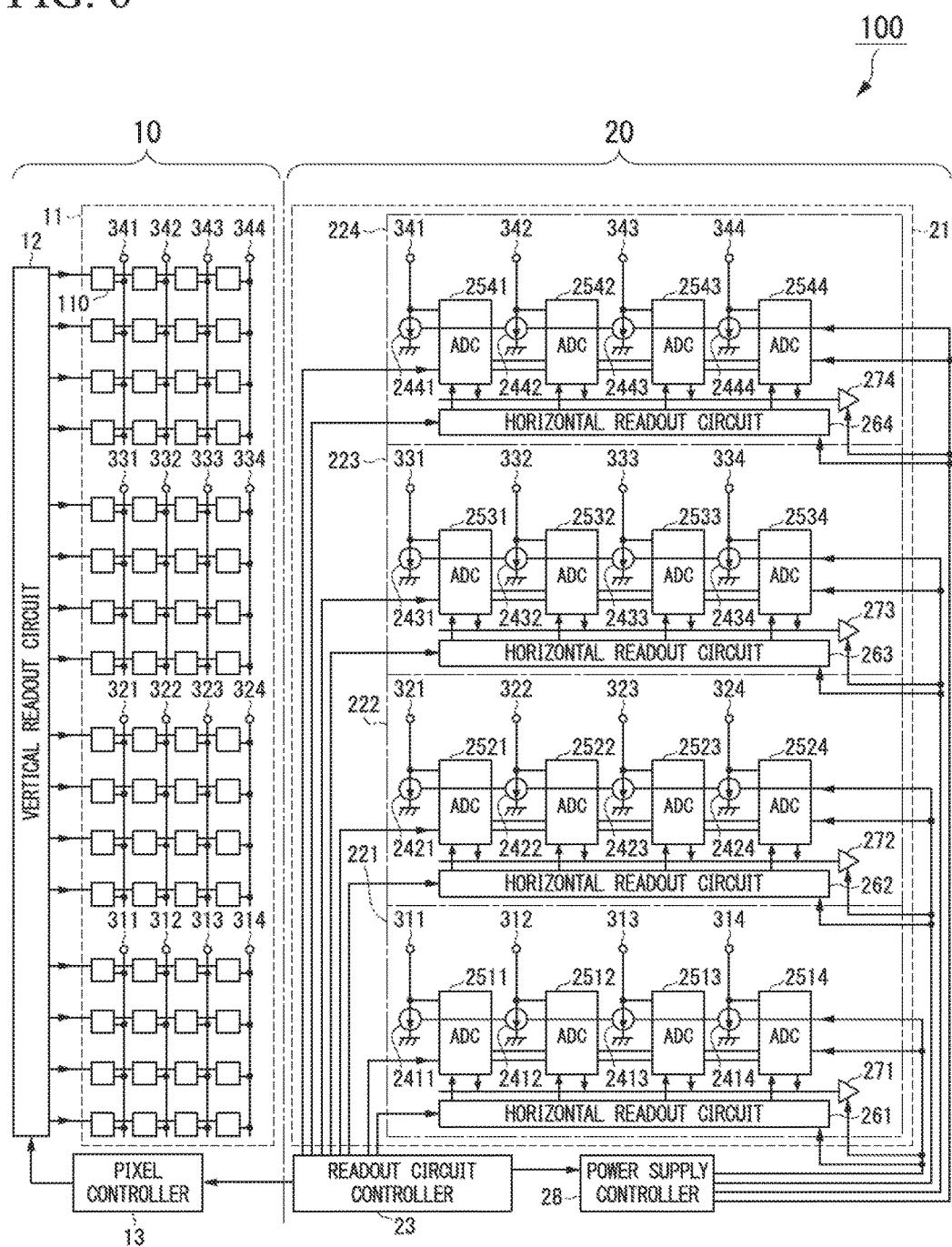

FIG. 6 is a block diagram illustrating a schematic configuration of a solid-state image pickup device according to a second embodiment of the present invention.

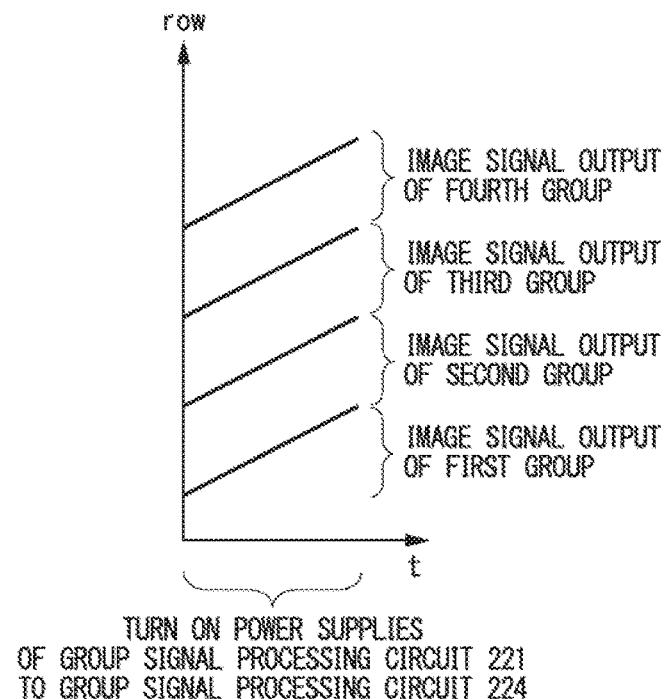

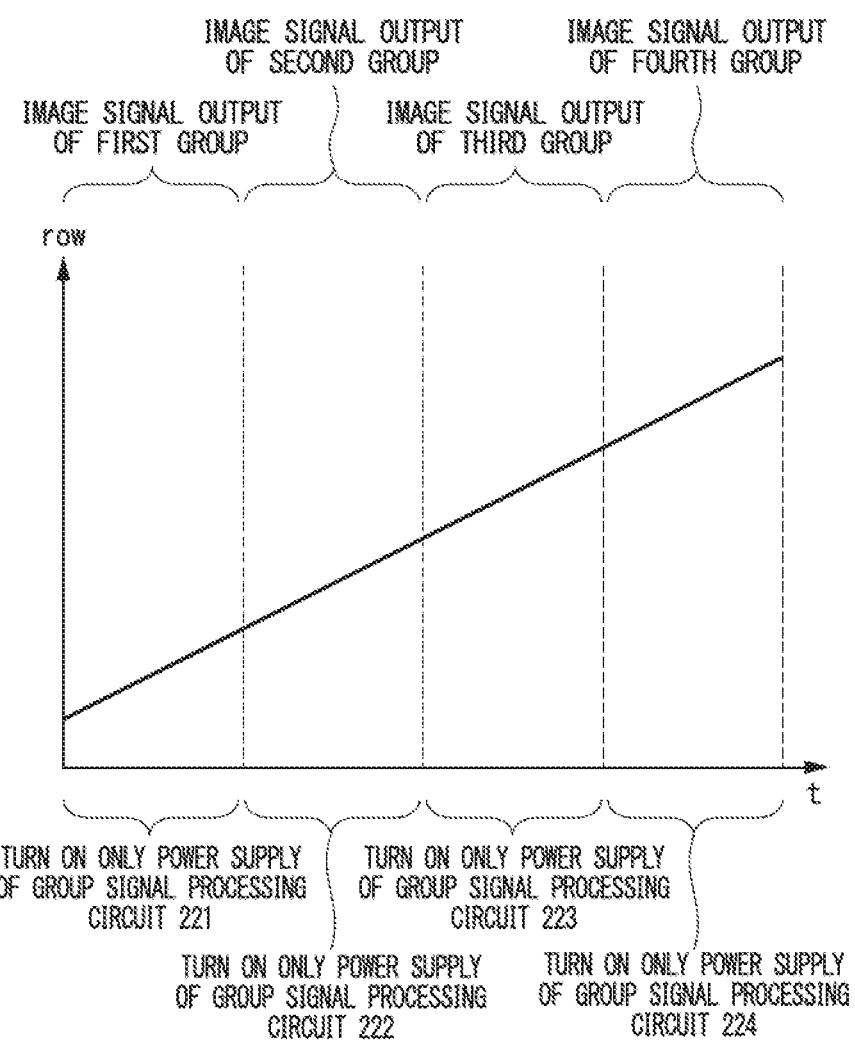

FIG. 7A is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the second embodiment.

FIG. 7B is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the second embodiment.

FIG. 7C is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the second embodiment.

FIG. 8 is a block diagram illustrating a schematic configuration of a solid-state image pickup device according to a third embodiment of the present invention.

FIG. 9 is a circuit diagram illustrating a schematic configuration of a pixel for correction within a signal processing circuit part of the solid-state image pickup device of the third embodiment.

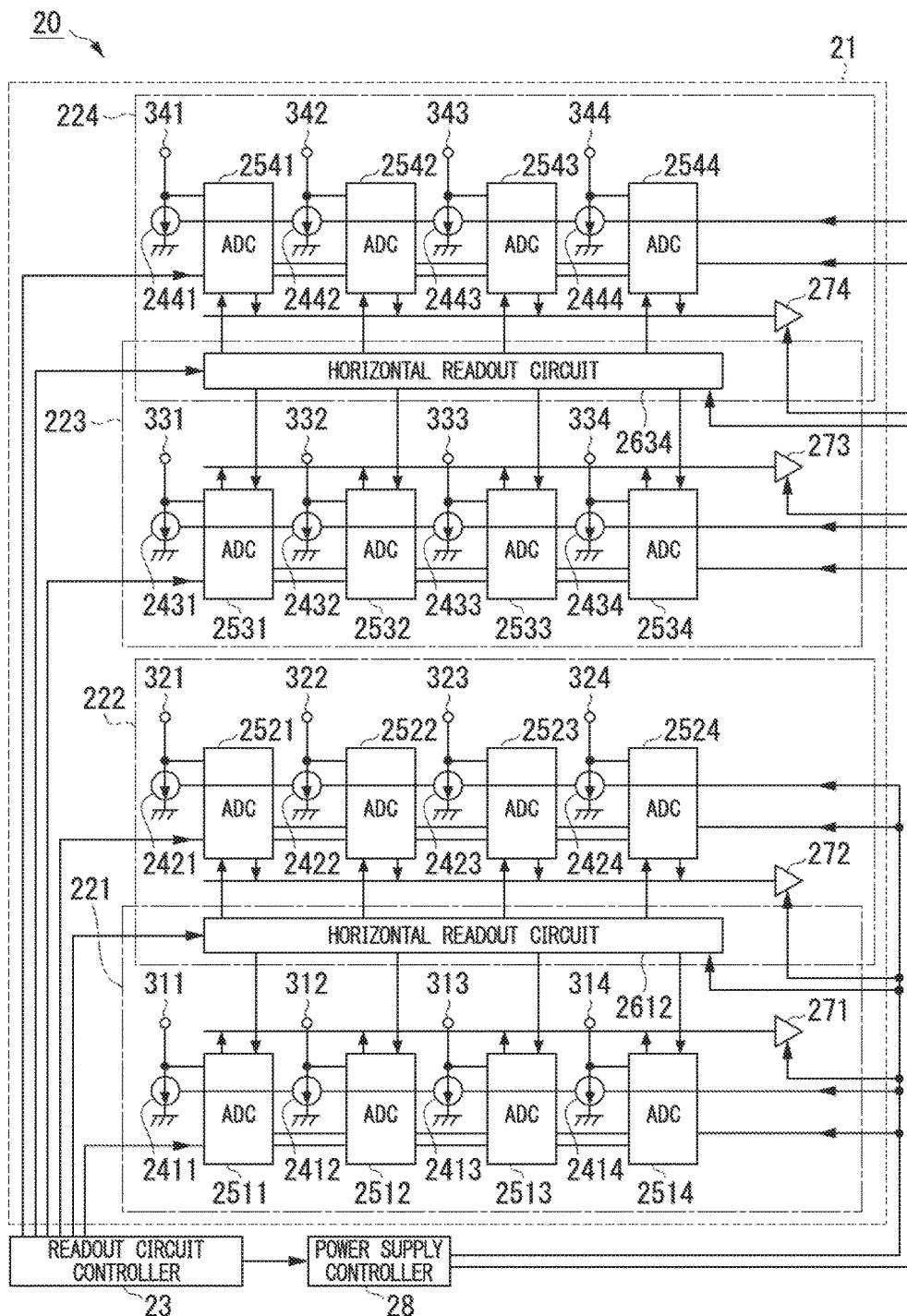

FIG. 10 is a block diagram illustrating a schematic configuration of a second substrate of a solid-state image pickup device according to a fourth embodiment of the present invention.

FIG. 11A is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the fourth embodiment.

FIG. 11B is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the fourth embodiment.

FIG. 11C is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the fourth embodiment.

FIG. 12 is a block diagram illustrating a schematic configuration of a second substrate of a solid-state image pickup device according to a fifth embodiment of the present invention.

FIG. 13A is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the fifth embodiment.

FIG. 13B is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the fifth embodiment.

FIG. 13C is a diagram illustrating a method of reading out a pixel signal in the solid-state image pickup device of the fifth embodiment.

#### DETAILED DESCRIPTION OF THE INVENTION

Hereinafter, an embodiment of the present invention will be described with reference to the accompanying drawings. FIG. 1 is a block diagram illustrating a schematic configuration of an image pickup apparatus (for example, digital monocular camera system) according to the present embodiment. An image pickup apparatus 8 shown in FIG. 1 includes a lens part 2, a solid-state image pickup device 1, an image signal processing device 3, a recording device 4, a camera control device 5, a display device 6, and a mechanical shutter 7.

The lens part 2 is configured such that zooming, a focus, an aperture diaphragm, and the like are driven and controlled by the camera control device 5, and forms a subject image on the solid-state image pickup device 1.

The mechanical shutter 7 is a screen for mechanically opening and closing in order to control (adjust) the amount of subject light incident on the solid-state image pickup device 1. When a still image is captured in the image pickup apparatus 8, for example, by the operation of the mechanical shutter 7, a time at which the subject light is incident on the solid-state image pickup device 1, that is, an exposure time is adjusted. In addition, when a moving image is captured in the image pickup apparatus 8, for example, by the operation

of the mechanical shutter 7, the amount of the subject light incident on the solid-state image pickup device 1 is adjusted.

The solid-state image pickup device 1 is a CMOS-type solid-state image pickup device, driven and controlled by the camera control device 5, which exposes subject light incident into the solid-state image pickup device 1 through the lens part 2 and converts the exposed light into an image signal. The details of this solid-state image pickup device 1 will be described later.

The image signal processing device 3 performs processes such as the amplification of a signal, the conversion of the signal into image data, various types of correction thereof, and the compression of the image data, with respect to an image signal which is output from the solid-state image pickup device 1. The image signal processing device 3 has a memory (not shown) used therein as means for temporarily storing image data in each process.

The recording device 4 is a removable recording medium such as a semiconductor memory, and records or reads out image data.

The display device 6 is a display device, such as a liquid crystal, which displays an image, formed in the solid-state image pickup device 1, which is based on image data processed by the image signal processing device 3 or image data read out from the recording device 4.

The camera control device 5 is a control device that controls the entire image pickup apparatus 8.

Next, the solid-state image pickup device 1 mounted in the image pickup apparatus 8 of the present embodiment will be described. FIGS. 2A and 2B are overview diagrams illustrating a schematic configuration of the solid-state image pickup device 1 mounted in the image pickup apparatus 8 of the present embodiment. The solid-state image pickup device 1 includes a first substrate 10, a second substrate 20, and an inter-substrate connecting portion 30. FIG. 2A shows a side view of the solid-state image pickup device 1, and 2B shows a plan view of each of the substrates constituting the solid-state image pickup device 1.

As shown in FIG. 2A, the solid-state image pickup device 1 has a configuration in which two substrates (chips) of the first substrate 10 and the second substrate 20 are laminated, and the first substrate 10 and the second substrate 20 are bonded (connected) to each other by the inter-substrate connecting portion 30.

A pixel array part 11 is formed in the first substrate 10, the pixel array part having a plurality of pixels (hereinafter, referred to as "unit pixels") that outputs a pixel signal based on incident subject light (visible light) being disposed in a two-dimensional matrix. In addition, the first substrate 10 includes a vertical readout circuit that reads out a pixel signal for each column from each unit pixel formed within the pixel array part 11 and outputs the read-out signal to the second substrate 20.

The second substrate 20 includes a plurality of column circuits that process the pixel signal, output by each unit pixel formed within the pixel array part 11 of the first substrate 10, for each column of the unit pixel, and has a signal processing circuit part 21 formed therein, the circuit part outputting the pixel signal processed by each column circuit, as an image signal, to the outside for each row of the unit pixel.

The inter-substrate connecting portion 30 is a connecting portion for electrically connecting a component within the first substrate 10 and a component within the second substrate 20. The components disposed in the first substrate 10 and the second substrate 20 which are bonded to each other

transmit and receive each electrical signal through each of the inter-substrate connecting portions **30** corresponding thereto.

The first substrate **10** is a backside illumination (BSI)-type silicon substrate in which subject light (visible light) is incident on the unit pixel formed within the pixel array part **11** from the opposite side of a wiring layer. As shown in (b-1) of FIG. 2B, the first substrate **10** includes the pixel array part **11** and a vertical readout circuit **12**.

As described above, the pixel array part **11** is a pixel part in which a plurality of unit pixels are disposed in a two-dimensional matrix. Each of the unit pixels within the pixel array part **11** includes a photoelectric conversion part that generates and accumulates signal charge based on the incident subject light (visible light) and an amplification part that amplifies the signal charge accumulated by this photoelectric conversion part to output the amplified signal charge as a pixel signal. Each of the unit pixels outputs the pixel signal based on the subject light amplified by the amplification part to a corresponding column circuit included within the signal processing circuit part **21** of the second substrate **20** through the inter-substrate connecting portion **30**, in accordance with a control signal which is input from the vertical readout circuit **12**. The details of this unit pixel will be described later.

The vertical readout circuit **12** drives each of the unit pixels within the pixel array part **11**, and causes a corresponding column circuit included within the signal processing circuit part **21** of the second substrate **20** to read out (output) the pixel signal based on the subject light generated and accumulated by each of the unit pixels. The vertical readout circuit **12** outputs a control signal for driving a unit pixel for each row of the unit pixels disposed in the pixel array part **11**.

As shown in (b-2) of FIG. 2B, the second substrate **20** includes the signal processing circuit part **21**. As described above, the signal processing circuit part **21** includes the plurality of column circuits that correspond to each column of the unit pixels disposed within the pixel array part **11**, and output a pixel signal after processing for which a process set in advance has been performed on each of the pixel signals which are sequentially input from corresponding unit pixels. In addition, the signal processing circuit part **21** includes a horizontal readout circuit that sequentially reads out the image signal processed by the column circuit corresponding to each of the unit pixels of each column disposed within the pixel array part **11**, for each row of the unit pixels disposed within the pixel array part **11** to output the read-out image signal to the outside.

In the solid-state image pickup device **1**, each of the unit pixels disposed within the pixel array part **11** is divided into a plurality of regions (groups) in a form of multiple rows of sets. Therefore, in the solid-state image pickup device **1**, a vertical signal line for outputting a pixel signal to a corresponding column circuit included within the signal processing circuit part **21** from each of the unit pixels is divided into multiple parts. Therefore, in the solid-state image pickup device **1**, the vertical readout circuit **12** can cause the unit pixels belonging to each group to simultaneously output the pixel signals to the corresponding column circuits. That is, the vertical readout circuit **12** can output not only a control signal for sequentially driving each unit pixel for each row to sequentially output the pixel signal from each group, but also a control signal for simultaneously driving the unit pixels within a plurality of groups to simultaneously output the pixel signals from each group. Therefore, in the solid-state image pickup device **1**, the signal processing circuit

part **21** is configured to correspond to each group of the unit pixel. More specifically, signal processing circuits (hereinafter, referred to as “group signal processing circuits”) forming a set of a plurality of column circuits and one horizontal readout circuit corresponding to each column of the unit pixel are provided by the number of groups. In the solid-state image pickup device **1**, the inter-substrate connecting portion **30** for transmitting the pixel signal output by each unit pixel to the corresponding group signal processing circuit is disposed for each divided vertical signal line.

FIGS. 2A and 2B show a configuration in which each of the unit pixels disposed within the pixel array part **11** is divided into four groups, that is, the vertical signal line within the pixel array part **11** is divided four. In addition, (b-2) of FIG. 2B shows a case where four group signal processing circuits **221** to **224** corresponding to the groups of the unit pixels, respectively, disposed within the pixel array part **11** are included within the signal processing circuit part **21**. In addition, FIG. 2A shows a case where the inter-substrate connecting portion **30** for connection to the column circuit included in each of the corresponding group signal processing circuits **221** to **224** is disposed for each group of the unit pixels obtained by dividing the vertical signal line, that is, the inter-substrate connecting portion **30** is disposed for each of the divided vertical signal lines.

An example of the inter-substrate connecting portion **30** to be used includes a microbump created using an evaporation method or a plating method, for example, a through-silicon-via (TSV), a structure in which connection is performed by a metal wiring layer, or the like. However, in the solid-state image pickup device **1**, considering that the inter-substrate connecting portion **30** is disposed within a region of the pixel array part **11**, it is preferable that a microbump be used. In this case, an insulating member such as an adhesive may be filled into a space present between the first substrate **10** and the second substrate **20**.

The inter-substrate connecting portion **30** may be used which has a plurality of structures based on a position at which a component within the first substrate **10** and a component within the second substrate **20** are connected to each other, that is, a position at which the inter-substrate connecting portion **30** is formed. For example, in the configuration shown in FIG. 2A, it is also possible to form a configuration in which a microbump is used as the inter-substrate connecting portion **30** that electrically connects a component within the pixel array part **11** formed in the first substrate **10** and a component within the signal processing circuit part **21** formed in the second substrate **20**, and a through-silicon-via is used as the inter-substrate connecting portion **30** that electrically connects a component other than the pixel array part **11** and a component other than the signal processing circuit part **21**.

With such a configuration, in the solid-state image pickup device **1**, each of the unit pixels disposed within the pixel array part **11** is divided into a plurality of groups, and the vertical signal line within the pixel array part **11** is divided into multiple parts. Thereby, in the solid-state image pickup device **1**, it is possible to reduce the length of each vertical signal line, and to reduce the number of unit pixels connected to each vertical signal line. Thereby, in the solid-state image pickup device **1**, it is possible to reduce the load of each vertical signal line. Thereby, in the solid-state image pickup device **1**, it is possible to realize a speed-up in readout of the pixel signal from each unit pixel to a corresponding column circuit and a reduction in power consumption, without increasing the current value of a pixel load

current source corresponding to each unit pixel, and without increasing the size of a transistor of the amplification part.

Further, in the solid-state image pickup device 1, since the first substrate 10 having the pixel array part 11 formed therein and the second substrate 20 having the signal processing circuit part 21 formed therein are configured to be laminated, there is no limitation to the number of vertical signal lines to be divided as in the configuration in which the load of the vertical signal line is reduced in the solid-state image pickup device of the related art, and the vertical signal line can be divided into a suitable number. Thereby, in the solid-state image pickup device 1, it is possible to reduce the load of each vertical signal line without increasing a chip area, and to realize a speed-up in readout of the pixel signal from each unit pixel to a corresponding column circuit and a reduction in power consumption.

In the solid-state image pickup device 1, the pixel signals are simultaneously output from the unit pixel belonging to each group to a corresponding signal processing circuit part 21 (any of the group signal processing circuit 221 to the group signal processing circuit 224), and thus it is possible to simultaneously output the image signals from each of the group signal processing circuit 221 to the group signal processing circuit 224. More specifically, the vertical readout circuit 12 simultaneously outputs control signals for reading out the pixel signal from each unit pixel to output the read-out signal to a corresponding column circuit, to the respective unit pixels belonging to different groups, that is, simultaneously outputs the pixel signals from the unit pixels of different rows disposed in the pixel array part 11 to corresponding column circuits. The image signals obtained by processing each pixel signal input from the unit pixel of a corresponding group are simultaneously output to the outside from each of the group signal processing circuit 221 to the group signal processing circuit 224. Thereby, in the configuration of the solid-state image pickup device 1 shown in FIGS. 2A and 2B, four rows' worth of image signals can be simultaneously output to the outside. Thereby, in the solid-state image pickup device 1, it is possible to realize a speed-up in output of the image signal.

In this manner, in the solid-state image pickup device 1, the load of each vertical signal line is reduced, and thus it is possible to achieve both a speed-up in readout of the pixel signal from each unit pixel to a corresponding column circuit and a reduction in power consumption, and the speed-up of the solid-state image pickup device 1 based on the image signals processed by each of the column circuits being output in parallel.

#### First Embodiment

Next, an example of the more detailed configuration of the solid-state image pickup device 1 mounted in the image pickup apparatus 8 of the present embodiment will be described. FIG. 3 is a block diagram illustrating a schematic configuration of the solid-state image pickup device 1 according to the first embodiment. The solid-state image pickup device 1 of the first embodiment shown in FIG. 3 includes the first substrate 10 including the pixel array part 11, the vertical readout circuit 12, and the pixel controller 13, and the second substrate 20 including the signal processing circuit part 21 and a readout circuit controller 23.

The pixel array part 11 is configured such that unit pixels 110 are disposed in a two-dimensional matrix of sixteen rows and four columns, and that each of the unit pixels 110 disposed is divided into four groups. The pixel array part 11 is configured such that each vertical signal line correspond-

ing to the unit pixels 110 disposed for each column is divided into four. More specifically, the pixel array part 11 is configured such that all the unit pixels 110 disposed are divided into a first group to a fourth group for every four rows and four columns, and that the vertical signal line corresponding to the unit pixel 110 the same one row is divided into four.

In addition, the signal processing circuit part 21 includes four group signal processing circuits 221 to 224 corresponding to the first group to the fourth group, respectively, of the unit pixels 110 divided in the pixel array part 11. Each of the group signal processing circuit 221 to the group signal processing circuit 224 includes pixel load current sources and column circuits having the number corresponding to the number of rows of the unit pixels 110 disposed within the pixel array part 11, and a horizontal readout circuit and an output part common to the respective column circuits. That is, each of the group signal processing circuit 221 to the group signal processing circuit 224 includes four pixel load current sources and four column circuits corresponding to each column of the unit pixels 110 disposed in four rows within the pixel array part 11, and one horizontal readout circuit and one output part.

More specifically, the group signal processing circuit 221 corresponding to the first group in the pixel array part 11 includes four pixel load current sources (pixel load current source 2411 to pixel load current source 2414) corresponding to the unit pixels 110 of four rows, respectively, belonging to the first group, four column circuits (column circuit 2511 to column circuit 2514), a horizontal readout circuit 261, and an output part 271. In addition, the group signal processing circuit 222 corresponding to the second group in the pixel array part 11 includes four pixel load current sources (pixel load current source 2421 to pixel load current source 2424) corresponding to the unit pixels 110 of four rows, respectively, belonging to the second group, four column circuits (column circuit 2521 to column circuit 2524), a horizontal readout circuit 262, and an output part 272. In addition, the group signal processing circuit 223 corresponding to the third group in the pixel array part 11 includes four pixel load current sources (pixel load current source 2431 to pixel load current source 2434) corresponding to the unit pixels 110 of four rows, respectively, belonging to the third group, four column circuits (column circuit 2531 to column circuit 2534), a horizontal readout circuit 263, and an output part 273. In addition, the group signal processing circuit 224 corresponding to the fourth group in the pixel array part 11 includes four pixel load current sources (pixel load current source 2441 to pixel load current source 2444) corresponding to the unit pixels 110 of four rows, respectively, belonging to the fourth group, four column circuits (column circuit 2541 to column circuit 2544), a horizontal readout circuit 264, and an output part 274.

In the following description, in a case where the group signal processing circuit 221, the group signal processing circuit 222, the group signal processing circuit 223, and the group signal processing circuit 224 are not distinguished from each other, these circuits are referred to as the "group signal processing circuits 22". In addition, in a case where the pixel load current source 2411 to the pixel load current source 2414 within the group signal processing circuit 221 are not distinguished from each other, these sources are referred to as the "pixel load current sources 241". In addition, in a case where the pixel load current source 2421 to the pixel load current source 2424 within the group signal processing circuit 222 are not distinguished from each other, these circuits are referred to as the "pixel load current

## 11

sources 242". In addition, in a case where the pixel load current source 2431 to the pixel load current source 2434 within the group signal processing circuit 223 are not distinguished from each other, these circuits are referred to as the "pixel load current sources 243". In addition, in a case where the pixel load current source 2441 to the pixel load current source 2444 within the group signal processing circuit 224 are not distinguished from each other, these circuits are referred to as the "pixel load current sources 244". In addition, in a case where the pixel load current source 2411 to the pixel load current source 2414 within the group signal processing circuit 221, the pixel load current source 2421 to the pixel load current source 2424 within the group signal processing circuit 222, the pixel load current source 2431 to the pixel load current source 2434 within the group signal processing circuit 223, and the pixel load current source 2441 to the pixel load current source 2444 within the group signal processing circuit 224 are not distinguished from each other, these sources are referred to as the "pixel load current sources 24".

In addition, in the following description, in a case where the column circuit 2511 to the column circuit 2514 within the group signal processing circuit 221 are not distinguished from each other, these circuits are referred to as the "column circuits 251". In addition, in a case where the column circuit 2521 to the column circuit 2524 within the group signal processing circuit 222 are not distinguished from each other, these circuits are referred to as the "column circuits 252". In addition, in a case where the column circuit 2531 to the column circuit 2534 within the group signal processing circuit 223 are not distinguished from each other, these circuits are referred to as the "column circuits 253". In addition, in a case where the column circuit 2541 to the column circuit 2544 within the group signal processing circuit 224 are not distinguished from each other, these circuits are referred to as the "column circuits 254". In addition, in a case where the column circuit 2511 to the column circuit 2514 within the group signal processing circuit 221, the column circuit 2521 to the column circuit 2524 within the group signal processing circuit 222, the column circuit 2531 to the column circuit 2534 within the group signal processing circuit 223, and the column circuit 2541 to the column circuit 2544 within the group signal processing circuit 224 are not distinguished from each other, these circuits are referred to as the "column circuits 25".

In addition, in the following description, in a case where the horizontal readout circuit 261 within the group signal processing circuit 221, the horizontal readout circuit 262 within the group signal processing circuit 222, the horizontal readout circuit 263 within the group signal processing circuit 223, and the horizontal readout circuit 264 within the group signal processing circuit 224 are not distinguished from each other, these circuits are referred to as the "horizontal readout circuits 26". In addition, in a case where the output part 271 within the group signal processing circuit 221, the output part 272 within the group signal processing circuit 222, the output part 273 within the group signal processing circuit 223, and the output part 274 within the group signal processing circuit 224 are not distinguished from each other, these output parts are referred to as the "output parts 27".

Each of the unit pixels 110 within the pixel array part 11 outputs the pixel signal based on the incident subject light to a corresponding vertical signal line, in accordance with the control signal which is input from the vertical readout circuit 12. Each of the vertical signal lines corresponding to the unit pixels 110 of the same one row within each group is connected to a pixel load current source and a column circuit

## 12

within each of the corresponding group signal processing circuits 22 through each of the corresponding inter-substrate connecting portions 30.

More specifically, the vertical signal line to which four unit pixels 110 of the first column of the first group are connected is connected to the corresponding pixel load current source 2411 and the corresponding column circuit 2511 in the group signal processing circuit 221, through the inter-substrate connecting portion 311. Similarly, each vertical signal line to which four unit pixels 110 of the second to fourth rows of the first group are connected is connected to the corresponding pixel load current sources 2412 to 2414 and the corresponding column circuits 2512 to 2514 in the group signal processing circuit 221, through each of the inter-substrate connecting portion 312 to the inter-substrate connecting portion 314.

Similarly, each vertical signal line to which four unit pixels 110 of the first to four rows of the second group are connected is connected to the corresponding pixel load current sources 2421 to 2424 and the corresponding column circuits 2521 to 2524 in the group signal processing circuit 222, through each of the inter-substrate connecting portion 321 to the inter-substrate connecting portion 324. Similarly, each vertical signal line to which four unit pixels 110 of the first to four rows of the third group are connected is connected to the corresponding pixel load current sources 2431 to 2434 and the corresponding column circuits 2531 to 2534 in the group signal processing circuit 223, through each of the inter-substrate connecting portion 331 to the inter-substrate connecting portion 334. Similarly, each vertical signal line to which four unit pixels 110 of the first to four rows of the fourth group are connected is connected to the corresponding pixel load current sources 2441 to 2444 and the corresponding column circuits 2541 to 2544 in the group signal processing circuit 224, through each of the inter-substrate connecting portion 341 to the inter-substrate connecting portion 344.

The pixel load current source 24 within each of the group signal processing circuits 22 is a current source which is configured such that one end thereof is connected to the ground of the group signal processing circuit 22, and that the other end thereof is connected to a corresponding vertical signal line. The pixel load current source 24 operates as the load of a transistor of an amplification part included within the unit pixel 110 connected to the corresponding vertical signal line.

The column circuit 25 within each of the group signal processing circuits 22 is a processing circuit that performs a process set in advance on each pixel signal which is sequentially input from the unit pixel 110 connected to the corresponding vertical signal line, in accordance with control from the readout circuit controller 23. Each of the column circuits outputs an output signal after having performed a process on the input pixel signal, to a corresponding output part 27, in accordance with control from the horizontal readout circuit 26 within the group signal processing circuit 22.

It is considered that an example of the column circuit 25 includes a correlated double sampling (CDS) circuit that performs noise suppression or the like on a pixel signal, an amplifier circuit that amplifies a pixel signal, an analog-digital converter circuit that performs analog-digital conversion on a pixel signal (analog signal) to output a digital signal based on the magnitude of the pixel signal, or the like. FIG. 3 shows a case where each of the column circuits 25 included in the solid-state image pickup device 1 of the first embodiment is an analog-digital converter circuit (ADC).

The analog-digital converter circuit may include, for example, a function of performing CDS processing.

The horizontal readout circuit 26 within each of the group signal processing circuits 22 sequentially reads out output signals after processing which are output from the corresponding column circuit 25, and sequentially outputs the read-out signals to the output part 27.

The output part 27 within each of the group signal processing circuits 22 outputs the output signals after processing which are sequentially input from the corresponding column circuit 25 by the horizontal readout circuit 26, as image signals, to the outside of the solid-state image pickup device 1.

The readout circuit controller 23 controls the pixel controller 13 included in the first substrate 10, and the column circuit 25 and the horizontal readout circuit 26 included in each of the group signal processing circuits 22 within the signal processing circuit part 21, in accordance with an operating mode when the solid-state image pickup device 1 reads out a pixel signal to output the read-out signal as an image signal. The details of an operating mode in which the solid-state image pickup device 1 outputs an image signal will be described later.

The pixel controller 13 controls a method of causing the vertical readout circuit 12 to drive each of the unit pixels 110 within the pixel array part 11 and read out a pixel signal, in accordance with control from the readout circuit controller 23, that is, in accordance with an operating mode when the solid-state image pickup device 1 reads out a pixel signal and outputs the read-out signal as an image signal.

The vertical readout circuit 12 drives each of the unit pixels 110 within the pixel array part 11 in accordance with control from the pixel controller 13, and outputs the pixel signal of each of the unit pixels 110 to a corresponding vertical signal line. As described above, the vertical readout circuit 12 can not only sequentially drive each of the unit pixels 110 included in the pixel array part 11, but also simultaneously drives the unit pixels 110 within a plurality of groups.

With such a configuration, in the solid-state image pickup device 1 of the first embodiment, each of the unit pixels 110 disposed within the pixel array part 11 is divided into four groups (first group to fourth group), that is, the vertical signal line within the pixel array part 11 is divided into four. Thereby, the length of each vertical signal line is reduced, and the number of unit pixels 110 connected to each vertical signal line is reduced to  $\frac{1}{4}$ . That is, in the solid-state image pickup device 1 of the first embodiment, the load of each divided vertical signal line is reduced to  $\frac{1}{4}$  of the load of the vertical signal line of one column in the solid-state image pickup device of the related art. Thereby, in the solid-state image pickup device 1 of the first embodiment, it is possible to realize a speed-up in readout of the pixel signal from each of the unit pixels 110 to a corresponding column circuit 25 and a reduction in power consumption, without increasing the current value of the pixel load current source 24 corresponding to each of the unit pixels 110, and without increasing the size of a transistor of the amplification part included within the unit pixel 110.

In addition, the solid-state image pickup device 1 according to the first embodiment includes the group signal processing circuit 22, that is, the pixel load current source 24, the column circuit 25, the horizontal readout circuit 26, and the output part 27, for each of the vertical signal lines divided in the pixel array part 11. Thereby, in the solid-state image pickup device 1 of the first embodiment, the pixel signals are simultaneously output from the unit pixels 110

belonging to each group to the corresponding group signal processing circuits 221 to 224, and thus it is possible to simultaneously output the image signals from each of the group signal processing circuit 221 to the group signal processing circuit 224. That is, in the solid-state image pickup device 1 of the first embodiment, it is possible to simultaneously output four rows' worth of image signals to the outside. Thereby, in the solid-state image pickup device 1 of the first embodiment, it is possible to realize a speed-up in output of the image signal.

In this manner, in the solid-state image pickup device 1 of the first embodiment, it is possible to achieve both a speed-up in readout of the pixel signal from unit pixel 110 to the column circuit 25 and a reduction in power consumption based on a reduction in the load of each vertical signal line, and the speed-up of the solid-state image pickup device 1 based on the image signals processed by each of the column circuits 25 being output in parallel.

Next, the unit pixels 110 included in the pixel array part 11 within the solid-state image pickup device 1 of the first embodiment will be described. FIG. 4 is a circuit diagram illustrating a schematic configuration of the unit pixel 110 within the pixel array part 11 of the solid-state image pickup device 1 of the first embodiment. FIG. 4 shows one unit pixel 110.

In FIG. 4, the unit pixel 110 includes a photoelectric conversion part PD, a transfer transistor M1, a charge accumulation unit FD, a pixel reset transistor M2, an amplification transistor M3, and a selection transistor M4. The unit pixel 110 converts incident subject light (visible light) into a pixel signal, and outputs the converted signal to the vertical signal line 40.

The photoelectric conversion part PD photoelectrically converts the incident subject light to generate signal charge, and accumulates the generated signal charge as a photoelectric conversion signal.

The transfer transistor M1 transfers the photoelectric conversion signal accumulated in the photoelectric conversion part PD to the gate terminal of the amplification transistor M3, in accordance with a control signal  $\phi_{TX}$  which is input from the vertical readout circuit 12. Thereby, the photoelectric conversion signal accumulated in the photoelectric conversion part PD and transferred by the transfer transistor M1 is accumulated in the charge accumulation unit FD.

The charge accumulation unit FD is a capacitor associated with a node connected to the gate terminal of the amplification transistor M3, and is denoted by a symbol of a capacitor in the schematic configuration of the unit pixel 110 shown in FIG. 4.

The amplification transistor M3 outputs a signal voltage based on the photoelectric conversion signal transferred to the gate terminal by the transfer transistor M1, that is, the photoelectric conversion signal accumulated in the charge accumulation unit FD. In this case, the amplification transistor M3 outputs a signal voltage obtained by amplifying the photoelectric conversion signal accumulated in the charge accumulation unit FD, in accordance with the current value of the pixel load current source 24 connected to the corresponding vertical signal line 40 through a corresponding inter-substrate connecting portion 30.

The selection transistor M4 outputs the signal voltage which is output from the amplification transistor M3, as a pixel signal, to the vertical signal line 40, in accordance with a control signal  $\phi_{SEL}$  which is input from the vertical readout circuit 12. Thereby, the pixel signal based on the

## 15

photoelectric conversion signal generated and accumulated by the photoelectric conversion part PD is read out to the vertical signal line 40.

The pixel reset transistor M2 resets the photoelectric conversion signal within the unit pixel 110 to a power supply voltage VDD, in accordance with a control signal φRST which is input from the vertical readout circuit 12.

With such a configuration, the pixel signal based on the photoelectric conversion signal obtained by photoelectrically converting the incident subject light by the photoelectric conversion part PD within the unit pixel 110 is input to a corresponding column circuit 25 through a corresponding inter-substrate connecting portion 30.

The operation of the unit pixel 110 shown in FIG. 4 is the same as the operation of a unit pixel disposed in a general solid-state image pickup device. Therefore, a detailed description of the operation of the unit pixel 110 will not be given.

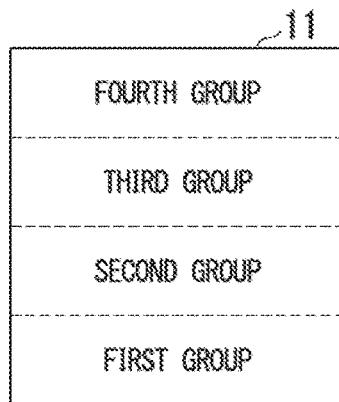

Next, an operating mode will be described in which the solid-state image pickup device 1 of the first embodiment reads out a pixel signal to output the read-out signal as an image signal. FIG. 5A to FIG. 5C are diagrams illustrating a method of reading out a pixel signal in the solid-state image pickup device 1 of the first embodiment. FIG. 5A shows regions of the first group to the fourth group in which all the unit pixels 110 disposed within the pixel array part 11 included in the solid-state image pickup device 1 are divided into four groups. In addition, FIGS. 5B and 5C schematically show the transition of a row of the unit pixels 110 that output a pixel signal in each operating mode of the solid-state image pickup device 1, that is, a row of the pixel array part 11 that performs an output as an image signal. In FIGS. 5B and 5C, the horizontal axis represents a time at which the solid-state image pickup device 1 outputs the image signal based on the pixel signal which is output by each of the unit pixels 110, and the vertical axis represents a row of the unit pixels 110 in which the solid-state image pickup device 1 outputs the image signal based on the pixel signal.

As shown in FIG. 5A, in the solid-state image pickup device 1, regions of all the unit pixels 110 disposed within the pixel array part 11 are divided into four groups of the first group to the fourth group. In the solid-state image pickup device 1, the vertical readout circuit 12 can not only sequentially drive each of the unit pixels 110 included in the pixel array part 11, but also simultaneously drives the unit pixels 110 within a plurality of groups. Therefore, in the solid-state image pickup device 1, it is possible to output image signals in two operating modes of an operating mode (hereinafter, referred to as a "parallel operating mode") in which the unit pixels 110 within a plurality of groups are simultaneously driven and the image signals based on the pixel signals of a plurality of rows are output in parallel, and an operating mode (hereinafter, referred to as a "sequential operating mode") in which each of the unit pixels 110 included in the pixel array part 11 are sequentially driven and the image signals based on the pixel signals of each row are sequentially output. FIG. 5B schematically shows the transition of a row of the unit pixels 110 in the parallel operating mode, and FIG. 5C schematically shows the transition of a row of the unit pixels 110 in the sequential operating mode.

Switching between two operating modes, that is, the setting of the parallel operating mode or the sequential operating mode is performed by, for example, the camera control device 5 included in the image pickup apparatus 8. In the image pickup apparatus 8, the image signal processing device 3 that performs a process on the image signal which is output from the solid-state image pickup device 1 per-

## 16

forms a process based on the operating mode of the solid-state image pickup device 1 which is set (switched) by the camera control device 5.

First, a method of reading out a pixel signal in the parallel operating mode shown in FIG. 5B will be described. The readout circuit controller 23 outputs a control signal indicating the output of an image signal in the parallel operating mode to the pixel controller 13. Thereby, the pixel controller 13 instructs the vertical readout circuit 12 to simultaneously drive the unit pixels 110 belonging to four groups and to sequentially read out the pixel signals. The vertical readout circuit 12 drives the unit pixels 110 of an initial row belonging to each of the first group to the fourth group in accordance with this instruction, and outputs each of the pixel signals to the group signal processing circuit 22 corresponding to each of the first group to the fourth group.

In addition, the readout circuit controller 23 causes each of the column circuits 25 within group signal processing circuit 22 to execute a process (here, analog digital conversion process) on the pixel signal which is output from the unit pixels 110 belonging to a corresponding group. In addition, the readout circuit controller 23 causes the horizontal readout circuit 26 within the group signal processing circuit 22 to sequentially output the output signals after processing which are output from each of the corresponding column circuits 25, to the output part 27.

Thereby, the image signals based on the pixel signals which are output by the unit pixels 110 of an initial row belonging to each of the first group to the fourth group, that is, four rows' worth of image signals output by the output part 27 within the group signal processing circuit 22 in parallel are simultaneously output to the outside.

Thereafter, the vertical readout circuit 12 drives the unit pixels 110 of the next row belonging to each of the first group to the fourth group, and outputs each of the pixel signals to the group signal processing circuit 22 corresponding to each of the first group to the fourth group. The readout circuit controller 23 executes a process by each of the column circuits 25 within the group signal processing circuit 22, and sequentially outputs the output signals after a process by the horizontal readout circuit 26 to the output part 27.

Thereby, four rows' worth of image signals based on the pixel signals output by the unit pixels 110 of the next row belonging to each of the first group to the fourth group are simultaneously output from the output part 27 within the group signal processing circuit 22.

Hereinafter, similarly, the vertical readout circuit 12 sequentially drives the unit pixels 110, for each row, belonging to each of the first group to the fourth group, and sequentially outputs each of the pixel signals to the group signal processing circuit 22 corresponding to each of the first group to the fourth group. In addition, the readout circuit controller 23 sequentially performs the process by each of the column circuits 25 within group signal processing circuit 22, and the output of the output signal after the process to the output part 27.

When the simultaneous output of the image signals based on the pixel signals, output by the unit pixels 110 of a final row belonging to each of the first group to the fourth group, from the output part 27 within the group signal processing circuit 22 is terminated, the solid-state image pickup device 1 completes the output of the image signals in the parallel operating mode.

In this manner, in the parallel operating mode, as shown in FIG. 5B, the image signals based on the pixel signals output by the unit pixels 110 belonging to each group of the

first group to the fourth group are output in parallel. Thereby, in the parallel operating mode, it is possible to speed up the output of the image signal from the solid-state image pickup device 1.

In the parallel operating mode, the image signals based on the pixel signals output by the unit pixels 110 belonging to regions of each of the divided vertical signal lines, that is, each of the first group to the fourth group are output in parallel. Therefore, the parallel operating mode is preferably set in a case where subject light which is incident after the exposure of the solid-state image pickup device 1 is terminated is blocked by the mechanical shutter 7 included in the image pickup apparatus 8, or a case where a so-called global shutter method is adopted in which the photoelectric conversion signals output by the photoelectric conversion part PD within all the unit pixels 110 are simultaneously transferred by the transfer transistor M1.

Subsequently, a method of reading out a pixel signal in the sequential operating mode shown in FIG. 5C will be described. The readout circuit controller 23 outputs a control signal indicating the output of the image signal in the sequential operating mode to the pixel controller 13. Thereby, the pixel controller 13 instructs the vertical readout circuit 12 to sequentially drive the unit pixels 110 belonging to four groups, and to sequentially read out the pixel signals. The vertical readout circuit 12 drives the unit pixels 110 of an initial row belonging to the first group in accordance with this instruction, and outputs each of the pixel signals to the group signal processing circuit 221 corresponding to the first group.

In addition, the readout circuit controller 23 causes each of the column circuits 251 within the group signal processing circuit 221 to execute a process (here, analog digital conversion process) on the pixel signals which are output from the unit pixels 110 belonging to the corresponding first group. In addition, the readout circuit controller 23 causes the horizontal readout circuit 261 within the group signal processing circuit 221 to sequentially output the output signals after processing, output from each of the corresponding column circuits 251, to the output part 271.

Thereby, the image signals based on the pixel signals output by the unit pixels 110 of an initial row belonging to the first group are output to the outside from the output part 271 within the group signal processing circuit 221.

Thereafter, the vertical readout circuit 12 drives the unit pixels 110 of the next row belonging to the first group, and outputs each of the pixel signals to the group signal processing circuit 221 corresponding to the first group. The readout circuit controller 23 executes a process by each of the column circuits 251 within the group signal processing circuit 221, and sequentially outputs the output signals after a process by the horizontal readout circuit 261 to the output part 271.

Thereby, the image signals based on the pixel signals output by the unit pixels 110 of the next row belonging to the first group are output from the output part 271 within the group signal processing circuit 221.

Hereinafter, similarly, the vertical readout circuit 12 sequentially drives the unit pixels 110, for each row, belonging to the first group, and sequentially output each of the pixel signals to the group signal processing circuit 221 corresponding to the first group. In addition, the readout circuit controller 23 sequentially performs a process by each of the column circuits 251 within the group signal processing circuit 221, and the output of the output signal after the process to the output part 271.

Thereafter, after the driving of the unit pixels 110 of a final row belonging to the first group is terminated, the vertical readout circuit 12 continuously drives the unit pixels 110 of an initial row belonging to the second group, and outputs each of the pixel signals to the group signal processing circuit 222 corresponding to the second group.

In addition, the readout circuit controller 23 causes each of the column circuits 252 within the group signal processing circuit 222 to execute a process on the pixel signals 10 which are output from the unit pixels 110 belonging to the corresponding second group, and causes the horizontal readout circuit 262 within the group signal processing circuit 222 to sequentially output the output signals after processing, output from each of the corresponding column circuits 252, to the output part 272.

Thereby, the image signals based on the pixel signals output by the unit pixels 110 of an initial row belonging to the second group are output to the outside from the output part 272 within the group signal processing circuit 222, subsequently to the pixel signals output by the unit pixels 110 of a final row of the first group.

Hereinafter, similarly, the vertical readout circuit 12 sequentially drives the unit pixels 110 belonging to the third group subsequently to the driving of the unit pixels 110 belonging to the second group, and further sequentially drives the unit pixels 110 belonging to the fourth group subsequently to the driving of the unit pixels 110 belonging to the third group, to sequentially output each of the pixel signals to a corresponding group signal processing circuit 22. In addition, the readout circuit controller 23 executes a process by each of the column circuits 25 within the group signal processing circuit 22 corresponding to the unit pixels 110 driven by the vertical readout circuit 12, and sequentially outputs the output signal after a process by the horizontal readout circuit 26 to the output part 27.

Thereby, subsequently to the output of the image signals based on the pixel signals, output by the unit pixels 110 of a final row belonging to the second group, from the output part 272 within the group signal processing circuit 222, the image signals based on the pixel signals output by the unit pixels 110 of an initial row belonging to the third group are sequentially output from the output part 273 within the group signal processing circuit 223. Further, subsequently to the output of the image signals based on the pixel signals, output by the unit pixels 110 of a final row belonging to the third group, from the output part 273 within the group signal processing circuit 223, the image signals based on the pixel signals output by the unit pixels 110 of an initial row belonging to the fourth group are sequentially output from the output part 274 within the group signal processing circuit 224.

When the output of the image signals based on the pixel signal, output by the unit pixels 110 of a final row belonging to the fourth group, from the output part 274 within the group signal processing circuit 224 is terminated, the solid-state image pickup device 1 completes the output of the image signals in the sequential operating mode.

In this manner, in the sequential operating mode, as shown in FIG. 5C, the image signals based on the pixel signals output by the unit pixels 110 belonging to each group of the first group to the fourth group are sequentially output from each of the group signal processing circuit 221 to the group signal processing circuit 224 corresponding to each of the unit pixels 110. Thereby, in the sequential operating mode, similarly to the solid-state image pickup device of the related art, it is possible to sequentially output the image signals based on the pixel signals output by all the unit pixels

110 disposed in the pixel array part 11. In this case, in the solid-state image pickup device 1, each of the unit pixels 110 disposed within the pixel array part 11 is divided into four groups and the vertical signal line is divided into four. Thereby, the length of each vertical signal line is reduced, and the number of unit pixels 110 connected to each vertical signal line is reduced to  $\frac{1}{4}$ . Therefore, in the solid-state image pickup device 1, the load of each divided vertical signal line is reduced to  $\frac{1}{4}$  of the load of the vertical signal line of one row in the solid-state image pickup device of the related art, and thus power consumption when the image signal is output can be further reduced than in the solid-state image pickup device of the related art. Alternatively, in a case where the current value of the pixel load current source is set to be equal to that of the solid-state image pickup device of the related art, it is possible to further speed up readout from the pixel to the column circuit.

In addition, in the sequential operating mode, since the image signals are read out in a so-called rolling shutter system in which the image signals based on the pixel signals output by the unit pixels 110 belonging to each group are sequentially output across regions of the respective divided vertical signal lines, that is, the first group to the fourth group, the distortion of a subject becomes uniform in a column direction. Therefore, in the image pickup apparatus 8 having the solid-state image pickup device 1 of the first embodiment mounted therein, when a moving image is generated on the basis of the image signals which are output in the sequential operating mode, it is possible to prevent a difference in level of subject distortion from occurring between the respective groups (regions).

According to the first embodiment, a solid-state image pickup device (solid-state image pickup device 1) is configured which is provided with a first substrate (first substrate 10) including a pixel part (pixel array part 11) in which a plurality of pixels (unit pixels 110) disposed in a two-dimensional matrix are divided into a plurality of groups (first group to fourth group) forming a set for each of a plurality of rows which are set in advance; and a second substrate (second substrate 20) including pixel load current sources (pixel load current sources 24) corresponding to vertical signal lines (vertical signal lines 40) to which a plurality of unit pixels 110 disposed in the same column within each group of the first group to the fourth group are connected, and column circuits (column circuits 25) that perform a process set in advance on a pixel signal which is output from the unit pixel 110 to a corresponding vertical signal line 40, for each column of the unit pixels 110 belonging to each group of the first group to the fourth group, and including a plurality of signal processing circuits (group signal processing circuits 22) that output the pixel signal processed by each of the column circuits 25, as an image signal, for each column of the unit pixels 110, so as to correspond to each of the first group to the fourth group. The first substrate 10 and the second substrate 20 are laminated. Each of the vertical signal lines 40 within each group of the first group to the fourth group, and each of the pixel load current sources 24 and the column circuits 25 corresponding to each of the vertical signal lines 40 within the group signal processing circuit 22 corresponding to each group of the first group to the fourth group are electrically connected to each other through each inter-substrate connecting portion (inter-substrate connecting portion 30) corresponding to each of the vertical signal lines 40.

In addition, according to the first embodiment, an image pickup apparatus (image pickup apparatus 8) is configured which includes a solid-state image pickup device 1 provided

with a first substrate 10 including a pixel array part 11 in which a plurality of unit pixels 110 disposed in a two-dimensional matrix are divided into a plurality of groups (first group to fourth group) forming a set for each of a plurality of rows which are set in advance; and a second substrate 20 including pixel load current sources 24 corresponding to vertical signal lines 40 to which a plurality of unit pixels 110 disposed in the same column within each group of the first group to the fourth group are connected, and column circuits 25 that perform a process set in advance on a pixel signal which is output from the unit pixel 110 to a corresponding vertical signal line 40, for each column of the unit pixels 110 belonging to each group of the first group to the fourth group, and including a plurality of group signal processing circuits 22 that output the pixel signal processed by each of the column circuits 25, as an image signal, for each column of the unit pixels 110, so as to correspond to each of the first group to the fourth group. The first substrate 10 and the second substrate 20 are laminated. Each of the vertical signal lines 40 within each group of the first group to the fourth group, and each of the pixel load current sources 24 and the column circuits 25 corresponding to each of the vertical signal lines 40 within the group signal processing circuit 22 corresponding to each group of the first group to the fourth group are electrically connected to each other through each inter-substrate connecting portion 30 corresponding to each of the vertical signal lines 40.

In addition, according to the first embodiment, the image pickup apparatus 8 is configured which further includes a mechanical shutter (mechanical shutter 7) that controls the amount of light incident on the solid-state image pickup device 1. The light incident on the solid-state image pickup device 1 is blocked by the mechanical shutter 7 when the unit pixels 110 within each group of the first group to the fourth group are simultaneously driven, and the image signals based on the pixel signals output from the unit pixels 110 driven herein are output from the solid-state image pickup device 1 so as to be output from the group signal processing circuits 22 corresponding to each group of the first group to the fourth group in parallel.

As described above, the solid-state image pickup device 1 of the first embodiment is configured such that the first substrate 10 having the pixel array part 11 formed therein and the second substrate 20 having the signal processing circuit part 21 formed therein are laminated. Thereby, in the solid-state image pickup device 1 of the first embodiment, each of the unit pixels 110 disposed within the pixel array part 11 can be divided into a plurality of groups without being limited to the number. In the solid-state image pickup device 1 of the first embodiment, the vertical signal line to which the unit pixels 110 of the same column within the pixel array part 11 are connected can be divided into the number of groups into which the unit pixels 110 are divided. Thereby, in the solid-state image pickup device 1 of the first embodiment, it is possible to reduce the length of each vertical signal line, to reduce the number of unit pixels 110 connected to each vertical signal line, and to further reduce the load of each divided vertical signal line than the load of the vertical signal line of one column in the solid-state image pickup device of the related art. Thereby, in the solid-state image pickup device 1 of the first embodiment, it is possible to realize a speed-up in readout of the pixel signal from each of the unit pixels 110 to a corresponding column circuit 25 and a reduction in power consumption, without increasing the current value of the pixel load current source 24 corre-