(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-156969

(P2006-156969A)

(43) 公開日 平成18年6月15日(2006.6.15)

| (51) Int.CI.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>H01L 27/28</b> (2006.01)  | H01L 27/10 | 449 5B035   |

| <b>H01L 51/05</b> (2006.01)  | H01L 29/78 | 613B 5F083  |

| <b>H01L 29/786</b> (2006.01) | G06K 19/00 | H 5F110     |

| <b>G06K 19/07</b> (2006.01)  | G06K 19/00 | K           |

| <b>G06K 19/077</b> (2006.01) | G11C 13/00 | Z           |

審査請求 未請求 請求項の数 20 O L (全 31 頁) 最終頁に続く

|              |                              |          |                                              |

|--------------|------------------------------|----------|----------------------------------------------|

| (21) 出願番号    | 特願2005-306607 (P2005-306607) | (71) 出願人 | 000153878                                    |

| (22) 出願日     | 平成17年10月21日 (2005.10.21)     |          | 株式会社半導体エネルギー研究所                              |

| (31) 優先権主張番号 | 特願2004-317398 (P2004-317398) |          | 神奈川県厚木市長谷398番地                               |

| (32) 優先日     | 平成16年10月29日 (2004.10.29)     | (72) 発明者 | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 安部 寛子<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内 |

|              |                              | (72) 発明者 | 湯川 幹央<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内 |

|              |                              | (72) 発明者 | 岩城 裕司<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内 |

最終頁に続く

(54) 【発明の名称】半導体装置、ICカード、ICタグ、RFIDタグ、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグおよび衣類

## (57) 【要約】

【課題】 製造時以外にデータの書き込みが可能であり、書き換えによる偽造を防止可能な半導体装置を提供することを目的とする。さらに、本発明は、単純な構造の有機メモリから構成される安価な半導体装置の提供を課題とする。

【解決手段】 有機化合物層を有する有機素子にトランジスタを並列または直列に接続したメモリセルを構成し、そのメモリセルを直列または並列に接続することによって、NAND型メモリまたはNOR型メモリを構成する。

前記有機素子は電流または電圧の印加、光の照射などで不可逆的にその電気特性を変化させることができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

有機素子とトランジスタを並列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを直列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有することを特徴とする半導体装置。

**【請求項 2】**

有機素子とトランジスタを並列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを直列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有し、NAND型メモリ装置を構成することを特徴とする半導体装置。

**【請求項 3】**

有機素子とトランジスタを直列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを並列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有することを特徴とする半導体装置。

**【請求項 4】**

有機素子とトランジスタを直列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを並列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有し、NOR型メモリ装置を構成することを特徴とする半導体装置。

**【請求項 5】**

請求項 1 乃至 請求項 4 のいずれか一項において、前記メモリセル列の信号を検出する手段は、センスアンプであることを特徴とする半導体装置。

**【請求項 6】**

請求項 1 乃至 請求項 5 のいずれか一項において、前記有機素子は有機化合物層を有し、前記有機化合物層は、電子輸送材料またはホール輸送材料であることを特徴とする半導体装置。

**【請求項 7】**

請求項 1 乃至 請求項 5 のいずれか一項において、前記有機素子は有機化合物層を有し、前記有機化合物を含む層は、光を照射することによって電気抵抗が変化する材料を有することを特徴とする半導体装置。

**【請求項 8】**

請求項 6 において、前記有機化合物層は、レーザ光の照射により導電性が変化することを特徴とする半導体装置。

**【請求項 9】**

請求項 1 乃至 請求項 5 のいずれか一項において、前記有機素子は有機化合物層を有し、前記有機化合物を含む層は、電圧または電流を印加することによって電気抵抗が変化する材料を有することを特徴とする半導体装置。

**【請求項 10】**

請求項 1 乃至 請求項 5 のいずれか一項において、前記有機素子は、書き込みにより不可逆的に電気抵抗が変化することを特徴とする半導体装置。

**【請求項 11】**

請求項 10 において、前記有機素子は、書き込みにより電極間距離が変化することを特徴とする半導体装置。

**【請求項 12】**

請求項 1 乃至 請求項 11 のいずれか一項において、前記有機化合物層の導電率は  $10^{-5} \text{ S/cm}^2$  以上、 $10^{-3} \text{ S/cm}^2$  以下であることを特徴とする半導体装置。

**【請求項 13】**

請求項 1 乃至 請求項 11 のいずれか一項において、前記有機化合物層の膜厚は 5 ~ 60 nm、好ましくは 10 ~ 20 nm であることを特徴とする半導体装置。

**【請求項 14】**

10

20

30

40

50

請求項 1 乃至 請求項 13 のいずれか一項において、前記有機素子および前記トランジスタは、半導体基板上に設けられることを特徴とする半導体装置。

【請求項 15】

請求項 1 乃至 請求項 13 のいずれか一項において、前記有機素子および前記トランジスタは、ガラス基板上に設けられることを特徴とする半導体装置。

【請求項 16】

請求項 1 乃至 請求項 13 のいずれか一項において、前記有機素子および前記トランジスタは、可撓性基板上に設けられることを特徴とする半導体装置。

【請求項 17】

請求項 1 乃至 請求項 13 のいずれか一項において、前記有機素子および前記トランジスタは、S O I 基板上に設けられることを特徴とする半導体装置。 10

【請求項 18】

請求項 1 乃至 請求項 17 のいずれか一項において、前記トランジスタは、薄膜トランジスタを含むことを特徴とする半導体装置。

【請求項 19】

請求項 1 乃至 請求項 18 のいずれか一項に記載された半導体装置を有する I C カード、I C タグ、R F I D タグ、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ、衣類。

【請求項 20】

請求項 1 乃至 請求項 18 のいずれか一項に記載された半導体装置を有し、電源回路、クロック発生回路、データ復調回路、データ変調回路、制御回路、及びインターフェイス回路のいずれか一を少なくとも有する R F I D タグ。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機素子を有する半導体装置に関する。特に、有機素子を用いたメモリ回路を有する半導体装置に関する。

【背景技術】

【0002】

コンピュータ技術の発展や、画像認識技術の向上によって、バーコードなどの媒体を用いた情報認識が広く普及し、商品データの認識などに用いられている。今後はさらに多量の情報認識が実施されると予想される。その一方、バーコードによる情報読み取りなどではバーコードリーダーがバーコードとの接触を必要とする、またバーコードに記録される情報量があまり多くできないという欠点があり、非接触の情報認識および媒体の記憶容量増大が望まれている。 30

【0003】

このような要望から、近年 I C を用いた I D チップが開発されている。I D チップとは I C チップ内のメモリ回路に必要な情報を記憶し、非接触手段、一般的には無線手段を用いて内部の情報を読み取るものである。このような I D チップの実用化によって、商品流通などの簡素化、低コスト化、高いセキュリティの確保が可能になるものと期待されている。 40

【0004】

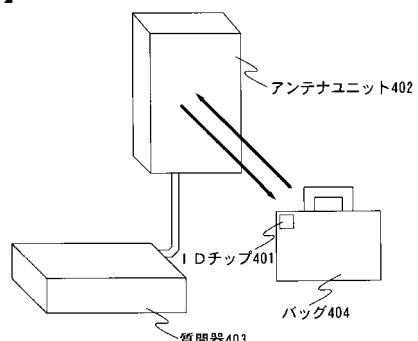

I D チップを用いた個体認証システムの概要について図 4 を用いて説明する。図 4 はバッグの個体情報を非接触で得ることを目的とした固体認証システムの概要を示す図である。特定の固体情報を記憶した I D チップ 401 はバッグ 404 に貼り付けられている、もしくは埋め込まれている。この I D チップに対して質問器（リーダライタともいう）403 のアンテナユニット 402 より電磁波が発信される。その電磁波を受けると I D チップ 401 はその I D チップが持っている個体情報をアンテナユニット 402 に対して送り返す。アンテナユニット 402 は送り返された個体情報を質問器に送り、質問器は個体情報 50

の判別をおこなう。このようにして、バグ 404 の情報を質問器は得ることが可能になる。また、このシステムを用いることによって物流管理、集計、偽造品の除去などが可能になる。

#### 【0005】

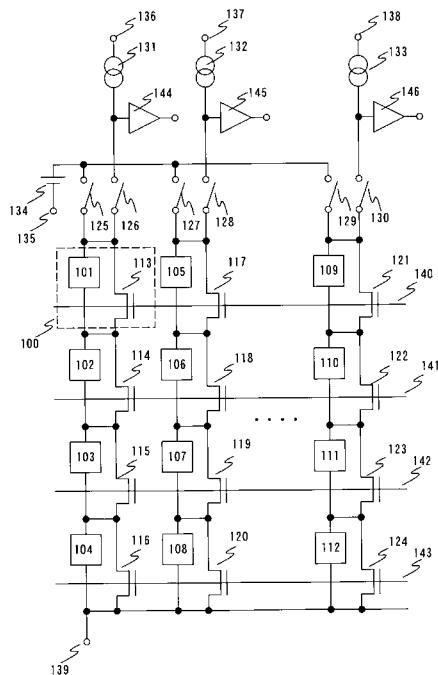

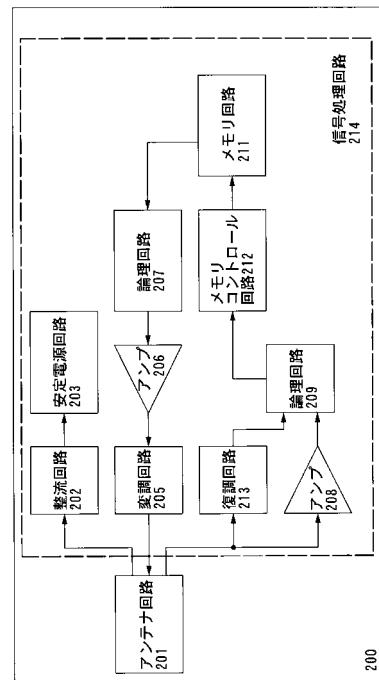

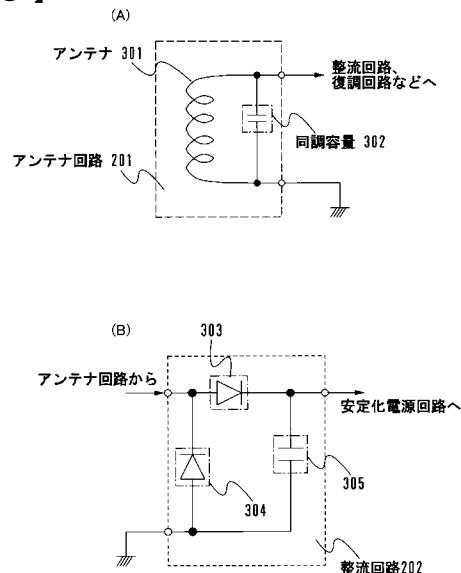

このような ID チップの技術としては例えば図 2 に示すようなものがある。ID チップに用いる半導体装置 200 はアンテナ回路 201、整流回路 202、安定化電源回路 203、アンプ 208、復調回路 213、論理回路 209、メモリコントロール回路 212、メモリ回路 211、論理回路 207、アンプ 206、変調回路 205 によって構成される。また、アンテナ回路 201 はアンテナコイル 301、同調容量 302 によって構成される(図 3(A))。また、整流回路 202 はダイオード 303、304、平滑容量 305 によって構成される(図 3(B))。アンテナ回路 201 以外を信号処理回路 214 と称する。

#### 【0006】

このような ID チップの動作を以下に説明する。アンテナ回路 201 で受信した交流信号はダイオード 303、304 によって半波整流され、平滑容量 305 によって平滑される。この平滑された電圧は多数のリップルを含んでいるため、安定化電源回路 203 で安定化され、安定化された後の電圧を復調回路 213、アンプ 206、論理回路 207、アンプ 208、論理回路 209、メモリ回路 211、メモリコントロール回路 212 に供給する。一方、アンテナ回路 201 で受信された信号はアンプ 208 を介して、クロック信号として、論理回路 209 に入力される。また、アンテナから入力された信号は復調回路 213 で復調され、データとして論理回路 209 に入力される。

#### 【0007】

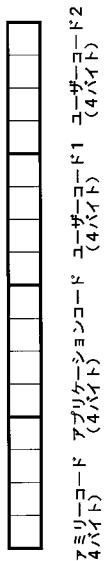

論理回路 209 において、入力されたデータはデコードされる。質問器がデータを変形ミラー符号、NRZ-L 符号などでエンコードして送信するため、それを論理回路 209 はデコードする。デコードされたデータは、メモリコントロール回路 212 に送られ、それに従いメモリ回路 211 に記憶された記憶データが読み出される。メモリ回路 211 は電源が切れても保持できる不揮発性メモリ回路である必要があり、マスク ROM や EEPROM、フラッシュメモリなどが使用される。記憶される内容は、例えば 16 バイトのデータ(図 12 参照)であり、ID チップの系列を示すファミリーコード 4 バイト、アプリケーションコード 4 バイト、使用者が設定するユーザーコード 4 バイトが 2 種類となっている。

#### 【0008】

送受信される信号は、125 kHz、13.56 MHz、915 MHz、2.45 GHz などがあり、それぞれ ISO 規格などが設定される。また、送受信の際の変調・復調方式も規格化されている。このような ID チップの例として例えば特許文献 1 などがある。

#### 【0009】

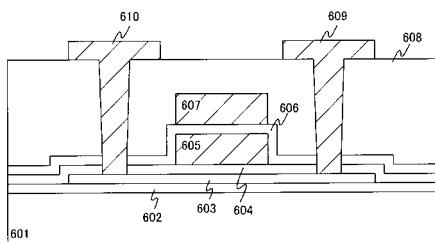

また、EEPROM やフラッシュメモリはフローティングゲートというようなゲートを重ねたトランジスタ構成をとっている。フローティングゲートを薄膜トランジスタ(以下 TFT)に用いると、図 6 に示す様に、フローティングゲートトランジスタは基板 601、下地膜 602、活性層 603、第 1 のゲート絶縁膜 604、フローティングゲート 605、第 2 のゲート絶縁膜 606、コントロールゲート 607、層間膜 608、ソース電極 609、ドレイン電極 610 より構成されている。

#### 【0010】

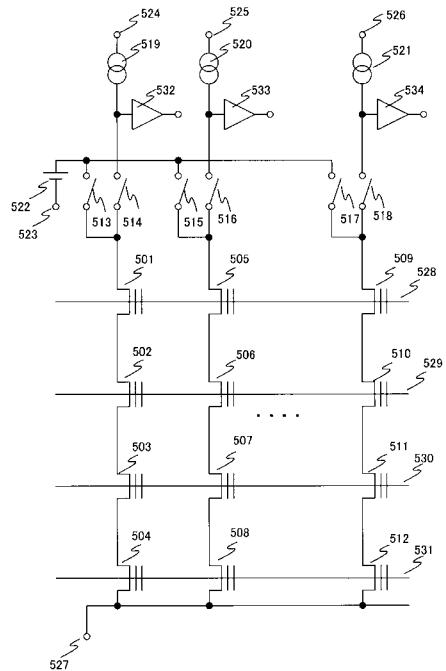

フラッシュメモリは図 5 に示す様にフローティングゲートトランジスタを直列に接続したような構成をとっている。図 5 において、フラッシュメモリはフローティングゲートトランジスタ 501 ~ 512、スイッチ 513 ~ 518、電流源 519 ~ 521、電圧源 522、電源端子 523 ~ 527、信号線 528 ~ 531、センスアンプ 532 ~ 534 によって構成される。データを書き込む時には電圧源 522 よりスイッチ 513、515、517 を介して、フローティングゲートトランジスタに電圧を印加する。さらに信号線 528 ~ 531 を制御して、トランジスタを選択することができる。

10

20

30

40

50

**【0011】**

読み出し時には、スイッチ514、516、518を介して電流源519～521より電流をフローティングゲートトランジスタに印加する。そのときの電位をセンスアンプ532～534で増幅し、信号として取りだす。フラッシュメモリに関しては以下の文献に記載されている（非特許文献1参照）。

**【特許文献1】特開2001-250393号公報**

【非特許文献1】躍進するフラッシュメモリ　舛岡富士雄著　工業調査会発行　91-1

54

**【発明の開示】****【発明が解決しようとする課題】****【0012】**

以上に述べた、従来のIDチップ用半導体装置は、以下のような課題があった。不揮発性メモリとしてマスクROMを使用した場合には、チップの形成工程でデータを書き込むため、製造終了後にデータを書き込むことができないという課題がある。

**【0013】**

E PROMやフラッシュメモリは書き換えが可能な不揮発性メモリとして有効である。第二のゲート絶縁膜に電荷を保持して記憶をおこなうため、保持性能を維持するためには、ゲート絶縁膜の膜質が良好であることが要求される。しかし、ガラスのような絶縁基板上にトランジスタを形成する場合、600 を超えるような高温処理をおこなうことはできない。従って、ゲート絶縁膜の膜質をよくすることにおいて限界があり、良好な不揮発性メモリを構成するのが困難であるという課題があった。

**【0014】**

そこで本発明は、IDチップに用いる半導体装置において、低温で製造が困難なフローティングゲート構造を使用しない不揮発性メモリを有する半導体装置を提供することを課題とする。

**【課題を解決するための手段】****【0015】**

上記課題を解決するため本発明では以下の手段を講じる。

**【0016】**

本発明の半導体装置は有機素子とトランジスタを並列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを直列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有することを特徴としている。

**【0017】**

本発明の半導体装置は有機素子とトランジスタを並列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを直列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有し、NAND型メモリ装置を構成することを特徴としている。

**【0018】**

本発明の半導体装置は有機素子とトランジスタを直列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを並列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有することを特徴としている。

**【0019】**

本発明の半導体装置は有機素子とトランジスタを直列に接続した構成を有する複数のメモリセルと、前記複数のメモリセルを並列に接続した複数のメモリセル列と、前記複数のメモリセル列の一端に該メモリセル列の信号を検出する手段とを有し、NOR型メモリ装置を構成することを特徴としている。

**【0020】**

上記において、前記メモリセル列の信号を検出する手段は、センスアンプであることを

10

20

30

40

50

特徴としている。

【0021】

上記において、前記有機素子は有機化合物層を有し、前記有機化合物層は、電子輸送材料またはホール輸送材料であることを特徴としている。

【0022】

上記において、前記有機素子は有機化合物層を有し、前記有機化合物を含む層は、光を照射することによって電気抵抗が変化する材料を有することを特徴としている。

【0023】

上記において、前記有機化合物層は、レーザ光の照射により導電性が変化することを特徴としている。

【0024】

上記において、前記有機素子は有機化合物層を有し、前記有機化合物を含む層は、電圧または電流を印加することによって電気抵抗が変化する材料を有することを特徴としている。

【0025】

上記において、前記有機素子は、書き込みにより不可逆的に電気抵抗が変化することを特徴としている。

【0026】

上記において、前記有機素子は、書き込みにより電極間距離が変化することを特徴としている。

【0027】

上記において、前記有機化合物層の導電率は  $10^{-15} \text{ S/cm}^2$  以上、  $10^{-3} \text{ S/cm}^2$  以下であることを特徴としている。

【0028】

上記において、前記有機化合物層の膜厚は 5 ~ 60 nm、好ましくは 10 ~ 20 nm であることを特徴としている。

【0029】

上記において、前記有機素子および前記トランジスタは、半導体基板上に設けられることを特徴としている。

【0030】

上記において、前記有機素子および前記トランジスタは、ガラス基板上に設けられることを特徴としている。

【0031】

上記において、前記有機素子および前記トランジスタは、可撓性基板上に設けられることを特徴としている。

【0032】

上記において、前記有機素子および前記トランジスタは、S O I 基板上に設けられることを特徴としている。

【0033】

上記において、前記トランジスタは、薄膜トランジスタを含むことを特徴としている。

【0034】

本発明は上記に記載の半導体装置を有する I C カード、I C タグ、R F I D タグ、トランシスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ、衣類である。

【0035】

本発明は上記に記載の半導体装置を有し、電源回路、クロック発生回路、データ復調回路、データ変調回路、制御回路、及びインターフェイス回路のいずれか一を少なくとも有する R F I D タグである。

【発明の効果】

【0036】

以上に述べたように、本発明を用いることによって、低温で高性能なゲート絶縁膜を用

10

20

30

40

50

いることなく、不揮発性メモリを有する半導体装置を構成することが可能となる。

**【発明を実施するための最良の形態】**

**【0037】**

以下、本発明の実施の態様について、図面を参照して説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

**【0038】**

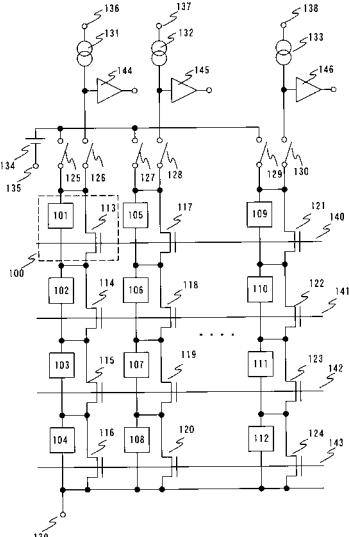

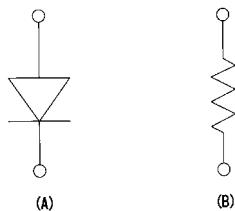

図1に本発明の第1の実施形態を示す。図1の実施形態は有機素子101～112、トランジスタ113～124、スイッチ125～130、電流源131～133、電源134、電源端子135～139、信号線140～143、センスアンプ144～146から構成される回路である。トランジスタ113～124は薄膜トランジスタであることが望ましいがそれには限定されない。また、有機素子101とトランジスタ113は並列に接続されメモリセル100を構成する。他の有機素子とトランジスタ、例えば有機素子102とトランジスタ114も同様に並列に接続されメモリセルを構成する。図1から明らかなように、複数のメモリセルが直列に接続され、メモリセル列を構成する。ここで使用する有機素子は2つのモードを有するものとする。例えば第1のモードとして図7(A)に示すようなダイオードで等価回路を示せるモード有する。また、第1のモードの有機素子に電圧、電流、光(レーザ光を含む)などを与えることによって不可逆的に図7(B)に示すような抵抗で等価回路を示せる第2のモードに変化するものとする。

**【0039】**

次に図1に示す回路の動作を説明する。この回路を記憶回路として使用する場合について説明を行う。まず、記憶すべきデータを有機素子101～112に記憶させる方法について説明する。有機素子101にデータを記憶させる場合を考える。

**【0040】**

最初に信号線141～143をアクティブにする。これによってトランジスタ114～116、118～120、122～124はオンし、トランジスタ114～116、118～120、122～124のソースとドレインが短絡され、電源端子139とほぼ同じ電位となる。一方信号線140はノンアクティブとすると、トランジスタ113、117、121はオフとなる。

**【0041】**

次にスイッチ125をオンさせる、すると有機素子101の一方の端子には電源134の電位が加わり、他方の端子には電源端子139の電位が加わる。

電源134の電圧として有機素子がモード変化するような電圧を加えれば、有機素子101は低抵抗でショート状態になる。

**【0042】**

次に、有機素子101に記憶されたデータを読み出す場合について説明をおこなう。最初に信号線141～143をアクティブにする。これによってトランジスタ114～116、118～120、122～124はオンし、トランジスタ114～116、118～120、122～124のソースとドレインは短絡され、電源端子139とほぼ同じ電位となる。一方信号線140はノンアクティブとすると、トランジスタ113、117、121はオフとなる。そして、スイッチ126をオンさせる。電源端子136に接続された電流源131よりスイッチ126を介して有機素子101に電流が流れ、その電流は更にトランジスタ114、115、116を介して、電源端子139に流れる。トランジスタ114、115、116のオン抵抗が十分低く、且つ、モード変化後の有機素子の抵抗が十分低ければ、電流源131の電源端子136に接続しない方の端子は電源端子139の電位とほぼ同等となる。

**【0043】**

10

20

30

40

50

有機素子にデータが記憶されない場合、有機素子は図7(A)に示すダイオードの状態であり有機素子101に電流が流れると、電流源131の電源端子136に接続されない方の端子には電源端子139にダイオードの順方向電圧を加えた電圧が発生する。このようにデータが記憶されたか否かで、電流源131の電源端子に接続しないほうの端子の電位は異なり、これによって有機素子の記憶状態を読み出すことが可能となる。電流源131に接続されたセンスアンプ144の出力を見ることによって、明確に記憶状態を判断することが可能になる。

#### 【0044】

以上において、有機素子101について説明をおこなったが、同様に有機素子102に書き込みをおこなう場合には信号線140、142、143をアクティブとし、スイッチ125をオンさせ、有機素子102の両端に電圧を印加して、有機素子のモードを変えることによって記憶が可能となる。代表的には、2つの電極間距離が変化するとともに、有機化合物層の厚さが部分的に変化する。また、有機素子102に記憶された情報を読み出す場合においても、信号線140、142、143をアクティブとし、スイッチ126をオンさせ電流源131の電位を読むことによって記憶状態を読み出すことができ、センスアンプ144の出力をみれば更に明確に記憶状態を判断することが可能となる。同様に有機素子103または104についても記憶が可能となる。

#### 【0045】

以上においては有機素子101～104の列について説明をおこなったが、有機素子105～108の列、有機素子109～112の列についても同じである。また、図1では有機素子を4つ直列に接続しているが、その数は4つに限定されず他の数であっても良い。上記は有機素子とトランジスタを並列に接続してメモリセルを構成し、さらにそのメモリセルを直列に接続してNAND型のメモリ構成をとっている。そしてその一端から信号を検出する手段（ここではセンスアンプであるがセンスアンプには限定しない）を有している。

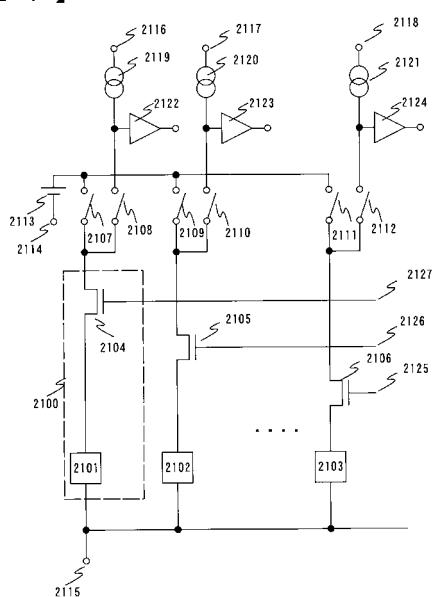

#### 【0046】

図21に本発明の第2の実施形態を示す。図21の実施形態は有機素子2101～2103、トランジスタ2104～2106、スイッチ2107～2112、電流源2119～2121、電源2113、電源端子2114～2118、センスアンプ2122～2124、信号線2125～2127から構成される回路である。トランジスタ2104～2106は薄膜トランジスタであることが望ましいがそれには限定されない。また、有機素子2101とトランジスタ2104は直列に接続されメモリセル2100を構成する。他の有機素子、トランジスタも同様である。ここで使用する有機素子は2つのモードを有するものとする。例えば第1のモードとして図7(A)に示すようなダイオードで等価回路を示せるモード有する。また、第1のモードの有機素子に電圧、電流、光（レーザ光を含む）などを与えることによって不可逆的に図7(B)に示すような抵抗で等価回路を示せる第2のモードに変化するものとする。

#### 【0047】

次に図21に示す回路の動作を説明する。この回路を記憶回路として使用する場合について説明を行う。まず、記憶すべきデータを有機素子2101～2103に記憶させる方法について説明する。まず有機素子2101にデータを記憶させる場合を考える。

#### 【0048】

最初に信号線2127をアクティブにする。これによってトランジスタ2104はオンし、トランジスタ2104のソースとドレインが短絡され、有機素子2101はスイッチ2107、2108と接続される。一方信号線2126、2127はノンアクティブとすると、トランジスタ2105、2106はオフとなる。

#### 【0049】

次にスイッチ2107をオンさせる、すると有機素子2101の一方の端子には電源2113の電位が加わり、他方の端子には電源端子2115の電位が加わる。電源2113の電圧として有機素子がモード変化するような電圧を加えれば、有機素子2101は低抵

抗でショート状態になる。

#### 【0050】

次に、有機素子2101に記憶されたデータを読み出す場合について説明をおこなう。最初に信号線2127をアクティブにする。これによってトランジスタ2104はオンし、トランジスタ2104のソースとドレインは短絡され、電源端子2115とほぼ同じ電位となる。一方信号線2125、2126はノンアクティブとすると、トランジスタ2105、2106はオフとなる。そして、スイッチ2108をオンさせる。電源端子2116に接続された電流源2119よりスイッチ2108を介して有機素子2101に電流が流れ、電源端子2115に流れる。トランジスタ2104のオン抵抗が十分低く、且つ、モード変化後の有機素子の抵抗が十分低ければ、電流源2119の電源端子2116に接続しない方の端子は電源端子2115の電位とほぼ同等となる。

#### 【0051】

有機素子にデータが記憶されない場合、有機素子は図7(A)に示すダイオードの状態であり有機素子2101に電流が流れると、電流源2119の電源端子2116に接続されない方の端子には電源端子2115にダイオードの順方向電圧を加えた電圧が発生する。このようにデータが記憶されたか否かで、電流源2119の電源端子に接続しないほうの端子の電位は異なり、これによって有機素子の記憶状態を読み出すことが可能となる。さらに電流源2119に接続されたセンスアンプ2122の出力を見ることによって、明確に記憶状態を判断することが可能になる。

#### 【0052】

以上において、有機素子2101について説明をおこなったが、同様に有機素子2102に書き込みをおこなう場合には信号線2126をアクティブとし、スイッチ2109をオンさせ、有機素子2102の両端に電圧を印加して、有機素子のモードをえることによって記憶が可能となる。また、有機素子2102に記憶された情報を読み出す場合においても、信号線2126をアクティブとし、スイッチ2110をオンさせ電流源2120の電位を読むことによって記憶状態を読み出すことができ、センスアンプ2123の出力をみれば更に明確に記憶状態を判断することが可能となる。同様に有機素子2103についても記憶が可能となる。

#### 【0053】

また、図21では有機素子3つを記載しているが、その数は3つに限定されず他の数であっても良い。上記は有機素子とトランジスタを直列に接続してメモリセルを構成し、さらにそのメモリセルを並列に接続してNOR型のメモリ構成をとっている。そしてその一端から信号を検出する手段(ここではセンスアンプであるがセンスアンプに限定しない)を有している。

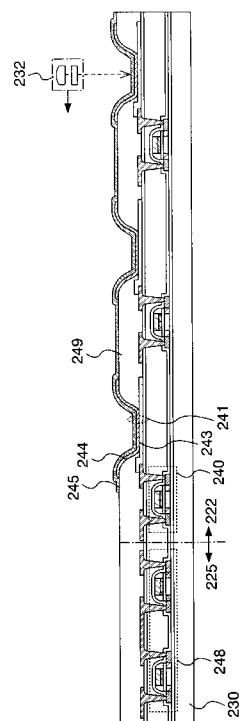

#### 【実施例1】

#### 【0054】

本発明の半導体装置の断面構造について説明する(図22参照)。ここでは、メモリセルアレイ222が含むトランジスタ240及び有機素子241と、スイッチ、センスアンプなど(図22では225に相当)が含むCMOS回路248の断面構造を示す。本発明に用いる基板230は、ガラス基板や可撓性基板の他、石英基板、シリコン基板、金属基板、ステンレス基板等を用いる。可撓性基板とは、フレキシブルな折り曲げができる基板のことであり、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルファン等からなるプラスチック基板等が挙げられる。

#### 【0055】

有機素子241は、第1の導電層243と、有機化合物層244と、第2の導電層245の積層体に相当し、隣接する有機素子241の間には、絶縁層249が設けられる。また、図22はNOR型メモリ回路の例であり、有機素子241の第2の導電層は他の有機素子と共通である。

#### 【0056】

第1の導電層243と第2の導電層245は、アルミニウム(A1)、銅(Cu)、銀

10

20

30

40

50

(A g) 等の公知の導電性材料を用いて形成される。

【0057】

光学的作用によりデータの書き込みを行う場合、第1の導電層243と第2の導電層245の一方又は両方は、インジウム錫酸化物(ITO)等の透光性がある材料により形成するか、又は光を透過する厚さで形成する。電気的作用によりデータの書き込みを行う場合、第1の導電層243と第2の導電層245に用いる材料に特に制約はない。

【0058】

有機化合物層244としては、単層または積層した構造を用いることができる。なお、有機化合物層合計の膜厚は5~60nm、好ましくは10~20nmである。また、各有機化合物層の導電率は $10^{-1.5} \text{ S/cm}^{-1}$ 以上、 $10^{-3} \text{ S/cm}^{-1}$ 以下である。

10

【0059】

有機化合物層244として、有機化合物材料を用いた場合には、データの書き込みはレーザ光等の光学的作用や電気的作用を加えることによって行う。また、光酸発生剤をドープした共役高分子材料を用いた場合、データの書き込みは光学的作用により行う。データの読み出しへは、有機化合物層244の材料には依存せず、いずれの場合であっても、電気的作用により行う。

【0060】

続いて、光学的作用によりデータの書き込みを行う場合について説明する。この場合、レーザ照射装置232により、透光性を有する導電層側(ここでは第2の導電層245とする)から、有機化合物層244に対して、レーザ光を照射することにより行う。

20

【0061】

有機化合物層244として、有機化合物材料を用いた場合、レーザ光の照射により、有機化合物層244が酸化又は炭化して絶縁化する。そうすると、レーザ光が照射された有機素子241の抵抗値は増加し、レーザ光が照射されない有機素子241の抵抗値は変化しない。また、光酸発生剤をドープした共役高分子材料を用いた場合、レーザ光の照射により、有機化合物層244に導電性が与えられる。つまり、レーザ光が照射された有機素子241には導電性が与えられ、レーザ光が照射されない有機素子241には導電性が与えられない。

【実施例2】

【0062】

30

光によりデータの書き込みを行う場合、第1の導電層243と第2の導電層245のうち、一方又は両方は透光性を有している。透光性を有する導電層は、インジウム錫酸化物(ITO)等の透明な導電性材料を用いて形成するか、又は、透明な導電性材料でなくとも、光を透過する厚さで形成する。

【0063】

有機化合物層244は、導電性を有する有機化合物材料を用いることができ、例えば、4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル(略称:-NPD)や4,4'-ビス[N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル(略称:TPD)や4,4',4'''-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン(略称:TDATA)、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニル-アミノ]-トリフェニルアミン(略称:MTDAT)や4,4'-ビス(N-(4-(N,N-ジ-m-トリルアミノ)フェニル)-N-フェニルアミノ)ビフェニル(略称:DNTPD)などの芳香族アミン系(即ち、ベンゼン環-窒素の結合を有する)の化合物やフタロシアニン(略称:H2Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)等のフタロシアニン化合物等の正孔輸送性の高い物質を用いることができる。

40

【0064】

また、他にも有機化合物材料としては電子輸送性が高い材料を用いることができ、例えばトリス(8-キノリノラト)アルミニウム(略称:Alq<sub>3</sub>)、トリス(4-メチル-8-キノリノラト)アルミニウム(略称:Almq<sub>3</sub>)、ビス(10-ヒドロキシベンゾ

50

[ h ] - キノリナト ) ベリリウム ( 略称 : B e B q<sub>2</sub> ) 、 ビス ( 2 - メチル - 8 - キノリノラト ) - 4 - フェニルフェノラト - アルミニウム ( 略称 : B A l q ) 等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料や、 ビス [ 2 - ( 2 - ヒドロキシフェニル ) ベンゾオキサゾラト ] 亜鉛 ( 略称 : Z n ( B O X )<sub>2</sub> ) 、 ビス [ 2 - ( 2 - ヒドロキシフェニル ) ベンゾチアゾラト ] 亜鉛 ( 略称 : Z n ( B T Z )<sub>2</sub> ) などのオキサゾール系、 チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、 金属錯体以外にも、 2 - ( 4 - ビフェニリル ) - 5 - ( 4 - t e r t - プチルフェニル ) - 1 , 3 , 4 - オキサジアゾール ( 略称 : P B D ) 、 1 , 3 - ビス [ 5 - ( p - t e r t - プチルフェニル ) - 1 , 3 , 4 - オキサジアゾール - 2 - イル ] ベンゼン ( 略称 : O X D - 7 ) 、 3 - ( 4 - t e r t - プチルフェニル ) - 4 - フェニル - 5 - ( 4 - ビフェニリル ) - 1 , 2 , 4 - トリアゾール ( 略称 : T A Z ) 、 3 - ( 4 - t e r t - プチルフェニル ) - 4 - ( 4 - エチルフェニル ) - 5 - ( 4 - ビフェニリル ) - 1 , 2 , 4 - トリアゾール ( 略称 : p - E t T A Z ) 、 バソフェナントロリン ( 略称 : B P h e n ) 、 パソキュプロイン ( 略称 : B C P ) 等の化合物等を用いることができる。

#### 【 0 0 6 5 】

また、 他にも有機化合物材料として、 4 - ジシアノメチレン - 2 - メチル - 6 - ( 1 , 1 , 7 , 7 - テトラメチルジュロリジル - 9 - エニル ) - 4 H - ピラン ( 略称 : D C J T ) 、 4 - ジシアノメチレン - 2 - t - プチル - 6 - ( 1 , 1 , 7 , 7 - テトラメチルジュロリジル - 9 - エニル ) - 4 H - ピラン、 ペリフランテン、 2 , 5 - ジシアノ - 1 , 4 - ビス ( 1 0 - メトキシ - 1 , 1 , 7 , 7 - テトラメチルジュロリジル - 9 - エニル ) ベンゼン、 N , N ' - ジメチルキナクリドン ( 略称 : D M Q d ) 、 クマリン 6 、 クマリン 5 4 5 T 、 トリス ( 8 - キノリノラト ) アルミニウム ( 略称 : A l q<sub>3</sub> ) 、 9 , 9 ' - ビアントリル、 9 , 1 0 - ジフェニルアントラセン ( 略称 : D P A ) や 9 , 1 0 - ビス ( 2 - ナフチル ) アントラセン ( 略称 : D N A ) 、 2 , 5 , 8 , 1 1 - テトラ - t - プチルペリレン ( 略称 : T B P ) 等が挙げられる。また、 上記発光材料を分散してなる層を形成する場合に母体となる材料としては、 9 , 1 0 - ジ ( 2 - ナフチル ) - 2 - t e r t - プチルアントラセン ( 略称 : t - B u D N A ) 等のアントラセン誘導体、 4 , 4 ' - ビス ( N - カルバゾリル ) ビフェニル ( 略称 : C B P ) 等のカルバゾール誘導体、 ビス [ 2 - ( 2 - ヒドロキシフェニル ) ピリジナト ] 亜鉛 ( 略称 : Z n p p<sub>2</sub> ) 、 ビス [ 2 - ( 2 - ヒドロキシフェニル ) ベンゾオキサゾラト ] 亜鉛 ( 略称 : Z n B O X ) などの金属錯体等を用いることができる。また、 トリス ( 8 - キノリノラト ) アルミニウム ( 略称 : A l q<sub>3</sub> ) 、 9 , 1 0 - ビス ( 2 - ナフチル ) アントラセン ( 略称 : D N A ) 、 ビス ( 2 - メチル - 8 - キノリノラト ) - 4 - フェニルフェノラト - アルミニウム ( 略称 : B A l q ) 等を用いることができる。

#### 【 0 0 6 6 】

また、 有機化合物層の材料として、 他にも光または電気的作用を加えることによって電気抵抗が変化する材料を用いることができる。例えば、 光を吸収することによって酸を発生する化合物 ( 光酸発生剤 ) をドープした共役高分子を用いることができる。ここで共役高分子としては、 ポリアセチレン類、 ポリフェニレンビニレン類、 ポリチオフェン類、 ポリアニリン類、 ポリフェニレンエチレン類等を用いることができる。また、 光酸発生剤としては、 アリールスルホニウム塩、 アリールヨードニウム塩、 o - ニトロベンジルトシレート、 アリールスルホン酸 p - ニトロベンジルエステル、 スルホニルアセトフェノン類、 F e - アレン錯体 P F 6 塩等を用いることができる。

#### 【 0 0 6 7 】

上記のような有機素子 2 4 1 は、 一対の導電層間に有機化合物層を設ける単純な構成を有するため、 作製工程が単純であり、 安価な半導体装置の提供を可能とする。また、 有機素子 2 4 1 は、 不揮発性メモリであるため、 データを保持するための電池を内蔵する必要がなく、 小型、 薄型、 軽量の半導体装置の提供することができる。また、 有機素子 2 4 1 として不可逆的な材料を用いることによって、 データの書き込み ( 追記 ) は可能であるが、 データの書き換えを行うことはできない。そうすると、 偽造を防止し、 セキュリティを

確保した半導体装置を提供することができる。

【実施例 3】

【0068】

次に、光学的作用によりデータの書き込みを行う場合について説明する。この場合、透光性を有する導電層側（ここでは第2の導電層245とする）から、有機化合物層244にレーザ光を照射することにより行う。ここでは、所望の部分の有機化合物層244に選択的にレーザ光を照射して有機化合物層244を破壊する。破壊された有機化合物層は、絶縁化するため、他の部分と比較すると電気抵抗が大幅に大きくなる。このように、レーザ光の照射により、有機化合物層244を挟んで設けられた2つの導電膜間の電気抵抗が変化することを利用してデータの書き込みを行う。例えば、レーザ光を照射していない有機化合物層を「0」のデータとする場合、「1」のデータを書き込む際は、所望の部分の有機化合物層に選択的にレーザ光を照射して破壊することによって電気抵抗を大きくする。

【0069】

また、有機化合物層244として、光を吸収することによって酸を発生する化合物（光酸発生剤）をドープした共役高分子を用いた場合、レーザ光を照射すると、照射された部分だけが導電性が増加し、未照射の部分は導電性を有しない。そのため、所望の部分の有機化合物層に選択的にレーザ光を照射することにより、有機化合物層の導電性が変化することを利用してデータの書き込みを行う。例えば、レーザ光を照射していない有機化合物層を「0」のデータとする場合、「1」のデータを書き込む際は、所望の部分の有機化合物層に選択的にレーザ光を照射して導電性を増加させる。

【0070】

レーザ光を照射する場合、有機化合物層244の電気抵抗の変化は、メモリセルの大きさによるが、 $\mu\text{m}$ オーダの径に絞ったレーザ光の照射により実現する。例えば、径が $1\mu\text{m}$ のレーザビームが $10\text{ m/sec}$ の線速度で通過するとき、1つのメモリセルが含む有機化合物を含む層にレーザ光が照射される時間は $100\text{ nsec}$ となる。 $100\text{ nsec}$ という短い時間内で相を変化させるためには、レーザパワーは $10\text{ mW}$ 、パワー密度は $10\text{ kW/mm}^2$ とするよい。また、レーザ光を選択的に照射する場合は、パルス発振のレーザ照射装置を用いて行なうことが好ましい。

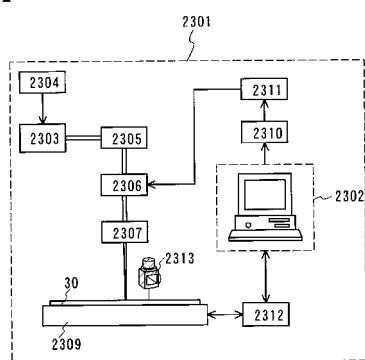

【0071】

ここで、レーザ照射装置の一例に関して、図23を用いて簡単に説明する。レーザ照射装置2301は、レーザ光を照射する際の各種制御を実行するコンピュータ（以下、PCと示す。）2302と、レーザ光を出力するレーザ発振器2303と、レーザ発振器2303の電源2304と、レーザ光を減衰させるための光学系（NDフィルタ）2305と、レーザ光の強度を変調するための音響光学変調器（Acousto-Optic Modulator；AOM）2306と、レーザ光の断面を縮小するためのレンズおよび光路を変更するためのミラー等で構成される光学系2307、X軸ステージ及びY軸ステージを有する移動機構2309と、PCから出力される制御データをデジタルーアナログ変換するD/A変換部2310と、D/A変換部から出力されるアナログ電圧に応じて音響光学変調器2306を制御するドライバ2311と、移動機構2309を駆動するための駆動信号を出力するドライバ2312と、被照射物上にレーザ光の焦点を合わせるためのオートフォーカス機構2313を備えている。

【0072】

レーザ発振器2303としては、紫外光、可視光、又は赤外光を発振することが可能なレーザ発振器を用いることができる。レーザ発振器としては、KrF、ArF、XeF、XeCl等のエキシマレーザ発振器、He、He-Cd、Ar、He-Ne、HF等の気体レーザ発振器、YAG、GdVO<sub>4</sub>、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶にCr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープした結晶を使った固体レーザ発振器、GaN、GaAs、GaAlAs、InGaAsP等の半導体レーザ発振器を用いることができる。なお、固体レーザ発振器においては、基本波か第2高調波～第5高調波

10

20

30

40

50

を適用するのが好ましい。

【0073】

次に、レーザ照射装置を用いた照射方法について述べる。有機化合物層（図示せず）が設けられた基板30が移動機構2309に装着されると、PC2302は図外のカメラによって、レーザ光を照射する有機化合物層の位置を検出する。次いで、PC2302は、検出した位置データに基づいて、移動機構2309を移動させるための移動データを生成する。

【0074】

この後、PC2302が、ドライバ2311を介して音響光学変調器2306の出力光量を制御することにより、レーザ発振器2303から出力されたレーザ光は、光学系2305によって減衰された後、音響光学変調器2306によって所定の光量になるように光量が制御される。一方、音響光学変調器2306から出力されたレーザ光は、光学系2307で光路及びビームスポット形状を変化させ、レンズで集光した後、基板30上に該レーザ光を照射する。

【0075】

このとき、PC2302が生成した移動データに従い、移動機構2309をX方向及びY方向に移動制御する。この結果、所定の場所にレーザ光が照射され、レーザ光の光エネルギーが熱エネルギーに変換され、基板30上に設けられた有機化合物層に選択的にレーザ光を照射することができる。なお、ここでは移動機構2309を移動させてレーザ光の照射を行う例を示しているが、光学系2307を調整することによってレーザ光をX方向およびY方向に移動させててもよい。

【0076】

上記の通り、レーザ光の照射によりデータの書き込みを行う本発明の構成は、半導体装置を簡単に大量に作製することができる。従って、安価な半導体装置を提供することができる。

【実施例4】

【0077】

本実施例では、基板上に有機素子を作製し、その有機素子に電気的作用によりデータの書き込みを行った結果について説明する。

【0078】

有機素子は、基板上に、第1の導電層、第1の有機化合物層、第2の有機化合物層、第2の導電層の順に積層した素子であり、第1の導電層は酸化珪素とインジウム錫酸化物の化合物（ITOと略称されることがある）、第1の有機化合物層は4,4'-ビス[N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル（TPDと略称されることがある）、第2の有機化合物層は、4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル（-NPDと略称されることがある）、第2の導電層はアルミニウム、により形成した。また、第1の有機化合物層は10nm、第2の有機化合物層は50nmの膜厚で形成した。なお、有機化合物層合計の膜厚は5~60nm、好ましくは10~20nmである。また、各有機化合物層の導電率は $10^{-15}$ S/cm<sup>-1</sup>以上、 $10^{-3}$ S/cm<sup>-1</sup>以下である。

【0079】

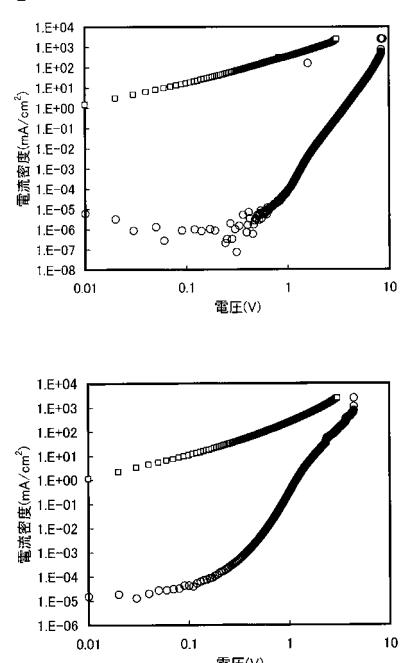

まず、電気的作用によりデータの書き込みを行う前と、電気的作用によりデータを書き込んだ後の、有機素子の電流電圧特性の測定結果について、図8を用いて説明する。

【0080】

図8は、横軸が電圧値、縦軸が電流値、プロット261は電気的作用によりデータを書き込む前の有機素子の電流電圧特性、プロット262は電気的作用によりデータを書き込んだ後の有機素子の電流電圧特性を示す。図8から、データの書き込み前と、データの書き込み後とで、有機素子の電流電圧特性には大きな変化がみられる。例えば、印加電圧1Vでは、データ書き込み前の電流値は $4.8 \times 10^{-5}$ mAであるのに対し、データ書き込み後の電流値は $1.1 \times 10^2$ mAであり、データの書き込み前と、データの書き込み

10

20

30

40

50

後では、電流値に7桁の変化が生じている。

#### 【0081】

このように、データの書き込み前と、データの書き込み後では、有機素子の抵抗値に変化が生じてあり、この有機素子の抵抗値の変化を、電圧値又は電流値により読み取れば、記憶回路として機能させることができる。

#### 【0082】

なお、上記のような有機素子を記憶回路として用いる場合、データの読み出し動作の度に、有機素子には所定の電圧値（短絡しない程度の電圧値）が印加され、その抵抗値の読み取りが行われる。従って、上記の有機素子の電流電圧特性には、読み出し動作を繰り返し行っても、つまり、所定の電圧値を繰り返し印加しても、変化しないような特性が必要となる。

#### 【0083】

そこで、データの読み出し動作を行った後の有機素子の電流電圧特性の測定結果について、図9を用いて説明する。

#### 【0084】

なお、この実験では、データの読み出し動作を1回行う度に、有機素子の電流電圧特性を測定した。データの読み出し動作を複数回行うことにより、有機素子の電流電圧特性の測定を行った。また、この電流電圧特性の測定は、電気的作用によりデータの書き込みが行われて抵抗値が変化した有機素子と、抵抗値が変化していない有機素子の、2つの有機素子に対して行った。

#### 【0085】

図9は、横軸が電圧値、縦軸が電流値、プロット272は電気的作用によりデータの書き込みが行われて抵抗値が変化した有機素子の電流電圧特性、プロット271は抵抗値が変化していない有機素子の電流電圧特性を示す。

#### 【0086】

プロット271から分かるように、抵抗値が変化していない有機素子の電流電圧特性は、電圧値が1V以上のときに特に良好な再現性を示す。同様に、プロット272から分かるように、抵抗値が変化した有機素子の電流電圧特性は、特に良好な再現性を示す。

#### 【0087】

上記の結果から、データの読み出し動作を複数回繰り返し行っても、その電流電圧特性は変化しないことが分かる。従って、上記の有機素子を記憶回路として用いることができる。

#### 【実施例5】

#### 【0088】

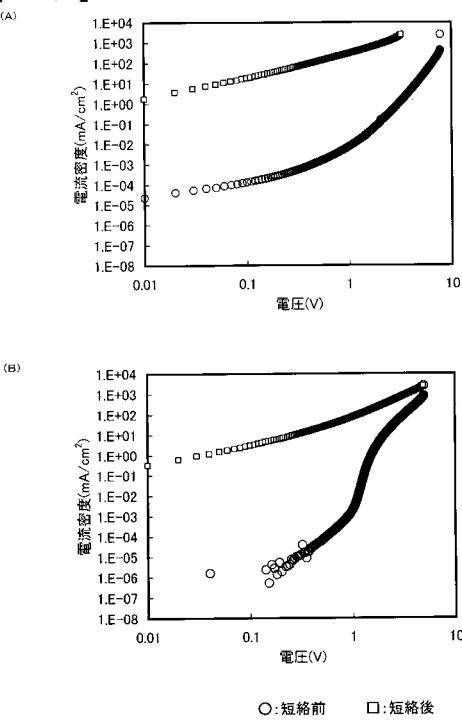

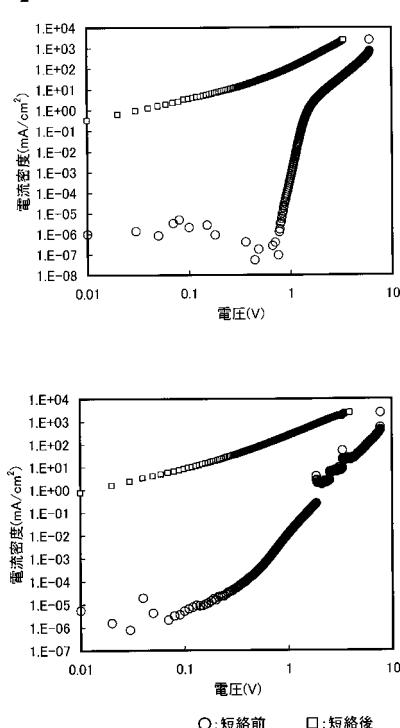

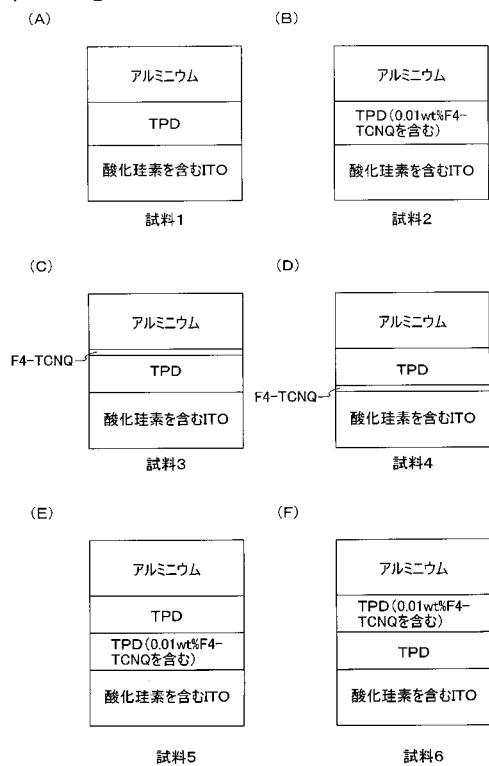

次に、図28に示すような基板上に有機素子を作製した試料1～試料6において、有機素子に電気的にデータの書き込みを行ったときの電流電圧特性の測定結果を図25～27に示す。なお、ここでは、有機素子に電圧を印加して、有機素子を短絡させて書き込みを行った。有機化合物層合計の膜厚は5～60nm、好ましくは10～20nmである。また、各有機化合物層の導電率は $10^{-15}$  S/cm<sup>-1</sup>以上、 $10^{-3}$  S/cm<sup>-1</sup>以下である。

#### 【0089】

図25～27は、それぞれ、横軸が電圧、縦軸が電流密度値、丸印のプロットはデータを書き込む前の有機素子の電流電圧特性の測定結果、四角印のプロットはデータを書き込んだ後の、有機素子の電流電圧特性の測定結果を示す。また、試料1～試料6の水平面における大きさは、2mm×2mmである。

#### 【0090】

試料1としては、第1の導電層、第1の有機化合物層、第2の導電層の順に積層した素子である。ここでは、図28(A)に示すように、第1の導電層を酸化珪素を含むインジウム錫酸化物(ITO)で形成し、第1の有機化合物層をTPDで形成し、第2の導電層をアルミニウムで形成した。また、第1の有機化合物層を厚さ50nmで形成した。試料

10

20

30

40

50

1 の電流電圧特性の測定結果を図 25 (A) に示す。

【0091】

また、試料 2 としては、第 1 の導電層、第 1 の有機化合物層、第 2 の導電層の順に積層した素子である。ここでは、図 28 (B) に示すように、第 1 の導電層を酸化珪素を含む ITO で形成し、第 1 の有機化合物層を、2, 3, 5, 6 - テトラフルオロ - 7, 7, 8, 8, - テトラシアノキノジメンタン (F4-TCNQ と略称されることがある) を添加した TPD で形成し、第 2 の導電層をアルミニウムで形成した。また、第 1 の有機化合物層を厚さ 50 nm で、F4-TCNQ を 0.01 wt % 添加して形成した。試料 2 の電流電圧特性の測定結果を図 25 (B) に示す。

【0092】

また、試料 3 としては、第 1 の導電層、第 1 の有機化合物層、第 2 の有機化合物層、第 2 の導電層の順に積層した素子である。ここでは、図 28 (C) に示すように、第 1 の導電層を酸化珪素を含む ITO で形成し、第 1 の有機化合物層を TPD で形成し、第 2 の有機化合物層を F4-TCNQ で形成し、第 2 の導電層をアルミニウムで形成した。また、第 1 の有機化合物層を厚さ 50 nm で形成し、第 2 の有機化合物層を厚さ 1 nm で形成した。試料 3 の電流電圧特性の測定結果を図 26 (A) に示す。

【0093】

また、試料 4 としては、第 1 の導電層、第 1 の有機化合物層、第 2 の有機化合物層、第 2 の導電層の順に積層した素子である。ここでは、図 28 (D) に示すように、第 1 の導電層を酸化珪素を含む ITO で形成し、第 1 の有機化合物層を F4-TCNQ で形成し、第 2 の有機化合物層を TPD で形成し、第 2 の導電層をアルミニウムで形成した。また、第 1 の有機化合物層を厚さ 1 nm で形成し、第 2 の有機化合物層を厚さ 50 nm で形成した。試料 4 の電流電圧特性の測定結果を図 26 (B) に示す。

【0094】

また、試料 5 としては、第 1 の導電層、第 1 の有機化合物層、第 2 の有機化合物層、第 2 の導電層の順に積層した素子である。ここでは、図 28 (E) に示すように、第 1 の導電層を酸化珪素を含む ITO で形成し、第 1 の有機化合物層を、F4-TCNQ を添加した TPD で形成し、第 2 の有機化合物層を TPD で形成し、第 2 の導電層をアルミニウムで形成した。また、第 1 の有機化合物層を厚さ 40 nm で、F4-TCNQ を 0.01 wt % 添加して形成した。また、第 2 の有機化合物層を厚さ 40 nm で形成した。試料 5 の電流電圧特性の測定結果を図 27 (A) に示す。

【0095】

また、試料 6 としては、第 1 の導電層、第 1 の有機化合物層、第 2 の有機化合物層、第 2 の導電層の順に積層した素子である。ここでは、図 28 (F) に示すように、第 1 の導電層を酸化珪素を含む ITO で形成し、第 1 の有機化合物層を TPD で形成し、第 2 の有機化合物層を F4-TCNQ を添加した TPD で形成し、第 2 の導電層をアルミニウムで形成した。また、第 1 の有機化合物層を厚さ 40 nm で形成した。また、第 2 の有機化合物層を厚さ 40 nm で、F4-TCNQ を 0.01 wt % 添加して形成した。試料 6 の電流電圧特性の測定結果を図 27 (B) に示す。

【0096】

図 25 ~ 27 に示す実験結果からも、試料 1 ~ 試料 6 において、データの書き込み前と、有機素子の短絡前後で、有機素子の電流電圧特性に大きな変化がみられる。また、これらの試料の有機素子において、各有機素子が短絡する電圧にも再現性があり、誤差は 0.1 V 以内であった。

【0097】

次に、試料 1 ~ 試料 6 の書き込み電圧、及び書き込み前後の特性を表 1 に示す。

10

20

30

40

【表1】

|     | 書き込み電圧(V) | R(1V)   | R(3V)   |

|-----|-----------|---------|---------|

| 試料1 | 8.4       | 1.9E+07 | 8.4E+03 |

| 試料2 | 4.4       | 8.0E+08 | 2.1E+02 |

| 試料3 | 3.2       | 8.7E+04 | 2.0E+02 |

| 試料4 | 5.0       | 3.7E+04 | 1.0E+01 |

| 試料5 | 6.1       | 2.0E+05 | 5.9E+01 |

| 試料6 | 7.8       | 2.0E+04 | 2.5E+02 |

10

20

30

40

## 【0098】

表1において、書き込み電圧(V)は、各有機素子が短絡するときの印加電圧を示す。また、R(1V)は、書き込み後の有機素子に電圧を1V印加したときの電流密度を、書き込み前の有機素子に電圧を1V印加したときの電流密度で除した値である。同様に、R(3V)は、書き込み後の有機素子に電圧を3V印加した時の電流密度を、書き込み前の有機素子に3V印加した時の電流密度で除した値である。即ち、有機素子の書き込み前後における電流密度の変化を示す。印加電圧が3Vの場合と比較して1V印加した場合、有機素子の書き込み前後における電流密度の変化は10の4乗以上と大きいことが分かる。

## 【実施例6】

## 【0099】

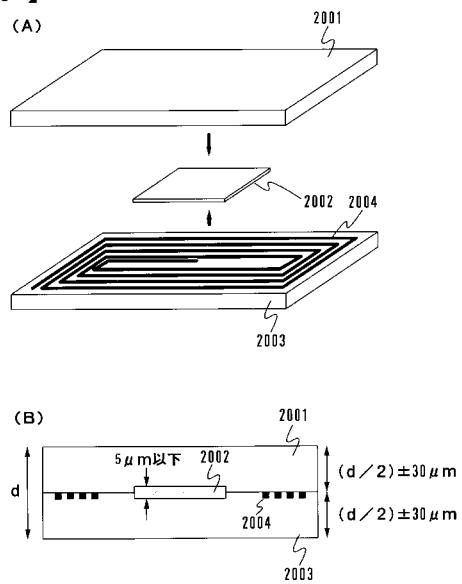

剥離プロセスを用いて、フレキシブルなIDタグを構成する場合の例について図20を用いて説明する。IDタグはフレキシブルな保護層2001、2003、および剥離プロセスを用いて形成されたIDチップ2002より構成される。本実施例において、アンテナ2004はIDチップ2002上ではなく、保護層2003上に形成され、IDチップ2002に電気的に接続されている。図20(A)では保護層2003上にのみ形成されているが、保護層2001上にもアンテナを形成しても良い。アンテナは銀、銅、またはそれらでメッキされた金属であることが望ましい。IDチップ2002とアンテナとの接続は異方性導電膜を用い、UV処理をおこない接続をおこなうが、接続方法はこれに限定されない。

## 【0100】

図20(B)は図20(A)の断面を示したものである。IDチップ2002の厚さは5μm以下であり、望ましくは0.1μm~3μmの厚さを有する。また保護層2001、2003の厚さは、保護層2001、2003を重ねたときの厚さをdとしたとき、(d/2)±30μmとなっていることが望ましく、とくに(d/2)±10μmであれば最良である。保護層2001、2003の厚さは10μm~200μmであることが望ましい。IDチップ2002の面積は5mm角以下であり、望ましくは0.3mm角~4mm角の面積を有する。

## 【0101】

保護層2001、2003は有機樹脂材料で形成され折り曲げに対して強い構造をもっている。剥離プロセスを用いたIDチップ2002自体も単結晶半導体に比べて、折り曲げに対して強いため、保護層2001、2003と密着させることが可能である。このような保護層2001、2003で囲われたIDチップをさらに他の個体物の表面または内部に配置しても良い。また、紙の中に埋め込んでも良い。

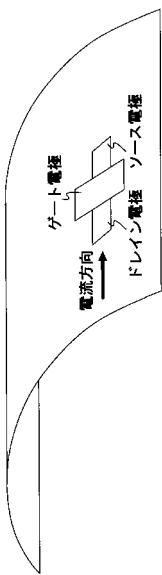

## 【実施例7】

## 【0102】

IDチップを曲面にはる場合、つまり、IDチップが弧を描いている方向と垂直にTFTを配置した例について図19を用いて説明する。図19のIDチップが含むTFTは、

50

電流が流れる方向、すなわち、ドレイン電極～ゲート電極～ソース電極の位置は直線状にあり、応力の影響が少なくなるような配置となっている。このような配置をおこなうことによって、TFT特性の変動を抑えることができる。また、TFTを構成する結晶は電流の流れる方向にそろっており、これらをCWL Cなどで形成することによって、S値を0.35V/dec以下、(好ましくは0.09~0.25V/dec)、移動度を100cm<sup>2</sup>/Vs以上にすることができる。

このようなTFTを用いて19段リングオシレータを構成した場合において、電源電圧3~5Vにおいて、その発振周波数は1MHz以上、好ましくは100MHz以上の特性を有する。電源電圧3~5Vにおいて、インバータ1段あたりの遅延時間は26ns、好ましくは0.26ns以下を有する。

10

### 【0103】

また、応力に対して、TFTなどのアクティブ素子を破壊させないためには、TFTなどのアクティブ素子の活性領域(シリコンアイランド部分)の面積が全体の面積に占める割合は、5%~50%であることが望ましい。

TFTなどのアクティブ素子の存在しない領域には下地絶縁材料、層間絶縁材料および配線材料が主として設けられている。TFTの活性領域以外の面積は全体の面積の60%以上であることが望ましい。

アクティブ素子の活性領域の厚さは20nm~200nm、代表的には40~170nm、好ましくは45~55nm、145~155nmを有する。

20

### 【0104】

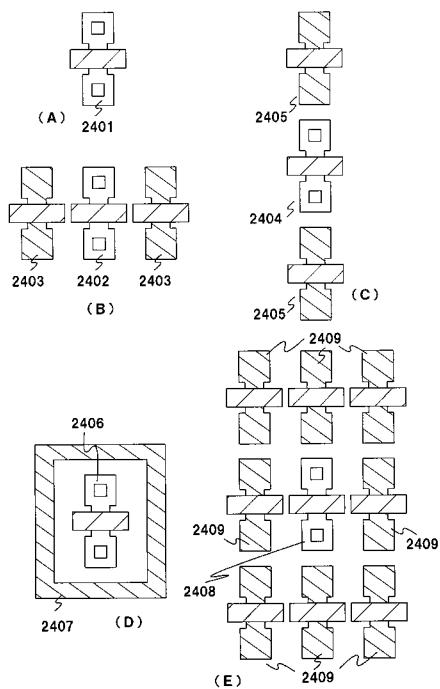

また、TFT2401が単体でまたは単体に近い状態で半導体装置内に配置されると(図24(A))、静電気による破壊、または、剥離工程を有する場合のストレスによる破壊などが起こりやすくなる。そこで、図24(B)~(E)にあるようにTFTの周囲にシリコン、メタル等のダミーパターンまたはダミーTFTを置くことによって、静電気またはストレスによる破壊を防止することができる。図24(B)はTFT2402の左右にダミーTFT2403を配置した例である。図24(C)はTFT2404の上下にダミーTFT2405を配置した例である。図24(D)はTFT2406の周りにダミーパターン2407を配置した例である。図24(E)はTFT2408の四方にダミーTFT2409を配置した例である。

30

### 【0105】

また対象物の表面が曲面を有しており、それにより該曲面に貼り合わされたIDチップの支持体が、錐面、柱面など母線の移動によって描かれる曲面を有するように曲がってしまう場合、該母線の方向とTFTのキャリアが移動する方向とを揃えておくことが望ましい。上記構成により、支持体が曲がっても、それによってTFTの特性に影響が出るのを抑えることができる。また、島状の半導体膜が集積回路内において占める面積の割合を、1~30%とすることで、支持体が曲がっても、それによってTFTの特性に影響が出るのをより抑えることができる。本実施例は、上記の実施の形態や他の実施例と組み合わせて用いることが可能である。

### 【実施例8】

#### 【0106】

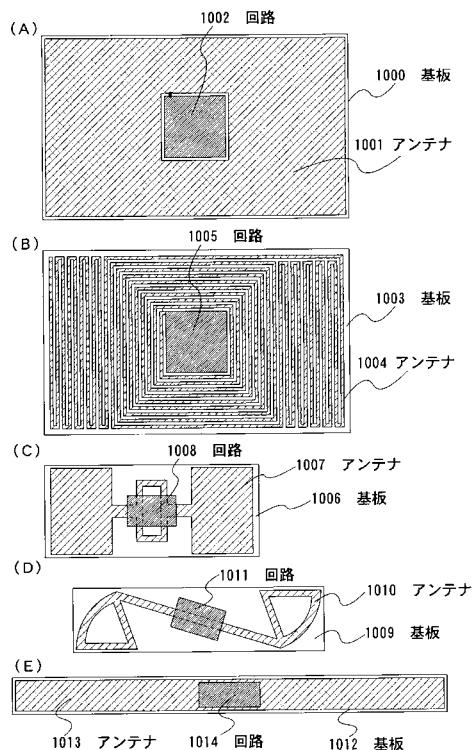

本実施例では本発明を用いた回路に外付けのアンテナをつけた例について図10、図11を用いて説明する。

40

#### 【0107】

図10(A)は回路の周りを一面のアンテナで覆ったものである。基板1000上にアンテナ1001を構成し、本発明を用いた回路1002を接続する。図面では回路1002の周りをアンテナ1001で覆う構成になっているが、全面をアンテナで覆い、その上に電極を構成した回路1002を貼り付けるような構造を取っても良い。

#### 【0108】

図10(B)は細いアンテナを回路の周りを回るように配置したものである。基板1003上にアンテナ1004を構成し、本発明を用いた回路1005を接続する。なお、ア

50

ンテナの配線は一例であってこれに限定するものではない。

【0109】

図10(C)は高周波数のアンテナである。基板1006上にアンテナ1007を構成し、本発明を用いた回路1008を接続する。

【0110】

図10(D)は180度無指向性(どの方向からでも同じく受信可能)なアンテナである。基板1009上にアンテナ1010を構成し、本発明を用いた回路1011を接続する。

【0111】

図10(E)は棒状に長く伸ばしたアンテナである。基板1012上にアンテナ1013を構成し、本発明を用いた回路1014を接続する。

【0112】

本発明を用いた回路とこれらのアンテナへの接続は公知の方法で行うことができる。例えばアンテナと回路をワイヤボンディング接続やバンプ接続を用いて接続する、あるいはチップ化した回路の一面を電極にしてアンテナに貼り付けるという方法を取ってもよい。この方式ではACF(anisotropic conductive film; 異方性導電性フィルム)を用いて貼り付けることができる。

【0113】

アンテナに必要な長さは受信に用いる周波数によって適正な長さが異なる。一般には波長の整数分の1の長さにすると良いとされる。例えば周波数が2.45GHzの場合は約60mm(1/2波長)、約30mm(1/4波長)とすれば良い。

【0114】

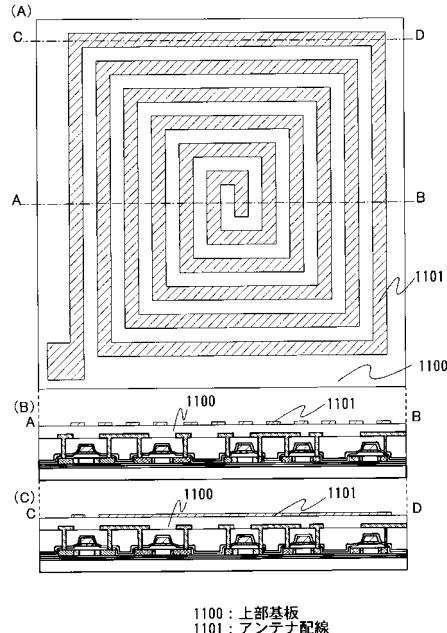

また、本発明の回路上に基板を取りつけ、さらにその上にアンテナを構成してもよい。図11(A)～(C)にその一例として回路上に基板を取りつけ、らせん状のアンテナを配置したものの上面図および断面図を示す。1100は上部基板を、1101はアンテナ配線を示している。

【0115】

なお、本実施例に示した例はごく一例であり、アンテナの形状を限定するものではない。あらゆる形状のアンテナについて本発明は実施することが可能である。この実施例は実施形態および上記の実施例1～6のどのような組み合わせからなる構成を用いても実現することができる。

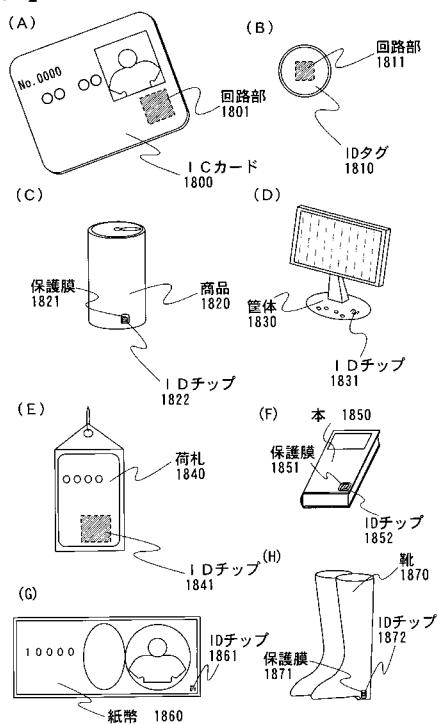

【実施例9】

【0116】

本実施例では本発明の半導体装置は、ICカード、ICタグ、RFIDタグ、トランスポンダ、紙幣、有価証券、パスポート、電子機器、バッグ及び衣類に用いることができる。ここでは、ICカード、IDタグおよびIDチップなどの例について図18を用いて説明する。なお、ICカード、ICタグ、RFIDタグ等は、電源回路、クロック発生回路、データ復調回路、データ変調回路、制御回路、インターフェイス回路等を有していてよい。

【0117】

図18(A)はICカードであり、個人の識別用のほかに内蔵された回路のメモリが書き換え可能であることを利用して現金を使わずに代金の決済が可能なクレジットカード、あるいは電子マネーといったような使い方もできる。ICカード1800の中に本発明を用いた回路部1801を組み込んでいる。

【0118】

図18(B)はIDタグであり、個人の識別用のほかに、小型化可能であることから特定の場所での入場管理などに用いることができる。IDタグ1810の中に本発明を用いた回路部1811を組み込んでいる。

【0119】

図18(C)はスーパーマーケットなどの小売店で商品を扱う際の商品管理を行うため

10

20

30

40

50

のＩＤチップ1822を商品1820に貼付した例である。本発明はＩＤチップ1822内の回路に適用される。このようにＩＤチップを用いることにより、在庫管理が容易になるだけではなく、万引きなどの被害を防ぐことも可能である。図面ではＩＤチップ1822が剥がれ落ちてしまうことを防ぐために接着を兼ねた保護膜1821を用いているが、ＩＤチップ1822を接着剤を用いて直接貼付するような構造を取っていてもよい。また、商品に貼付する構造上、実施例2で挙げたフレキシブル基板を用いて作製すると好ましい。

#### 【0120】

図18( D )は商品製造時に識別用のＩＤチップを組み込んだ例である。図面では例としてディスプレイの筐体1830にＩＤチップ1831が組み込まれている。本発明はＩＤチップ1831内の回路に適用される。このような構造を取ることにより製造メーカーの識別、商品の流通管理などを容易に行うことができる。なお、図面ではディスプレイの筐体を例として取り上げているが、本発明はこれに限定されることはなく、さまざまな電子機器、物品に対して適用することが可能である。

#### 【0121】

図18( E )は物品搬送用の荷札である。図面では荷札1840内にＩＤチップ1841が組み込まれている。本発明はＩＤチップ1841内の回路に適用される。このような構造を取ることにより搬送先の選別や商品の流通管理などを容易に行うことができる。なお、図面では物品を縛るひも状のものにくくりつけるような構造を取っているが、本発明はこれに限定されることはなく、シール材のようなものを用いて物品に直接貼付するような構造を取ってもよい。

#### 【0122】

図18( F )は本1850にＩＤチップ1852が組み込まれたものである。本発明はＩＤチップ1852内の回路に適用される。このような構造を取ることにより書店における流通管理や図書館などでの貸し出し処理などを容易に行うことができる。図面ではＩＤチップ1852が剥がれ落ちてしまうことを防ぐために接着を兼ねた保護膜1851を用いているが、ＩＤチップ1852を接着剤を用いて直接貼付するような構造を取る、または本1850の表紙に埋め込む構造を取っていてもよい。

#### 【0123】

図18( G )は紙幣1860にＩＤチップ1861が組み込まれたものである。本発明はＩＤチップ1861内の回路に適用される。このような構造を取ることにより偽札の流通を阻止することが容易に行える。なお、紙幣の性質上ＩＤチップ1861が剥がれ落ちるのを防ぐために紙幣1860に埋め込むような構造を取るとより好ましい。本発明は紙幣に限らず、有価証券、パスポートなど紙を材質にしたものに適用可能である。

#### 【0124】

図18( H )は靴1870にＩＤチップ1872が組み込まれたものである。本発明はＩＤチップ1872内の回路に適用される。このような構造を取ることにより製造メーカーの識別、商品の流通管理などを容易に行うことができる。図面ではＩＤチップ1872が剥がれ落ちてしまうことを防ぐために接着を兼ねた保護膜1871を用いているが、ＩＤチップ1872を接着剤を用いて直接貼付するような構造を取る、または靴1870に埋め込む構造を取っていてもよい。本発明は靴に限らず、バッグ、衣類など身に付けるものに適用可能である。

#### 【0125】

セキュリティ確保を目的として、多様な物品へＩＤチップを実装する場合を説明する。セキュリティ確保とは、盗難防止又は偽造防止の面から捉えることができる。

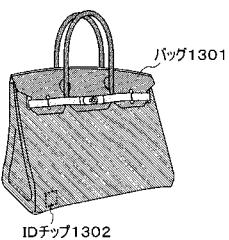

#### 【0126】

盗難防止の例として、バッグにＩＤチップを実装する場合を説明する。図13に示すように、バッグ1301にＩＤチップ1302を実装する。例えば、バッグ1301の底又は側面の一部等にＩＤチップ1302を実装することができる。ＩＤチップ1302は非常に薄型で小さいため、バッグ1301のデザイン性を低下させずに実装することができ

10

20

30

40

50

る。加えてIDチップ1302は透光性を有し、盗難者はIDチップ1302が実装されているかを判断しにくい。そのため、盗難者によってIDチップ1302が取り外される恐れがない。

#### 【0127】

このようなIDチップ実装バッグが盗難された場合、例えばGPS(Global Positioning System)を用いてバッグの現在位置に関する情報を得ることができる。なおGPSとは、GPS用の衛星から送られる信号をとらえてその時間差を求め、これをもとに測位するシステムである。

#### 【0128】

また盗難された物品以外にも忘れ物や落とし物を、GPSを用いて現在位置に関する情報を得ることができる。 10

#### 【0129】

またバッグ以外にも、自動車、自転車等の乗物、時計やアクセサリーにIDチップを実装することができる。

#### 【0130】

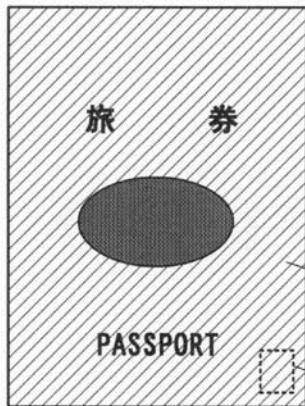

次に偽造防止の例として、パスポートや免許証等にIDチップを実装する場合を説明する。 20

#### 【0131】

図14(A)に、IDチップを実装したパスポート1401を示す。図14(A)ではIDチップ1402がパスポート1401の表紙に実装されているが、その他のページに実装してもよく、IDチップ1402は透光性を有するため表面に実装してもよい。またIDチップ1402を表紙等の材料で挟み込むようにし、表紙の内部に実装することも可能である。 20

#### 【0132】

図14(B)には、IDチップを実装した免許証1403を示す。図14(B)では、IDチップ1404が免許証1403の内部に実装されている。またIDチップ1404は透光性を有するため、免許証1403の印刷面上に設けても構わない。例えば。IDチップ1404は免許証1403の印字面上に実装し、フィルムで覆うことができる。またIDチップ1404を免許証1403の材料で挟み込むようにし、内部に実装することも可能である。 30

#### 【0133】

以上のような物品にIDチップを実装することにより、偽造を防止することができる。また上述したバッグにIDチップを実装し、偽造を防止することもできる。加えて非常に薄型で小さいIDチップを用いるため、パスポートや免許証等のデザイン性を損ねることがない。さらにIDチップは透光性を有するため、表面に実装しても構わない。

#### 【0134】

またIDチップにより、パスポートや免許証等の管理を簡便に行うことができる。さらにパスポートや免許証等に直接情報を記入することなく、IDチップに保存することができるため、プライバシーを守ることができる。

#### 【0135】

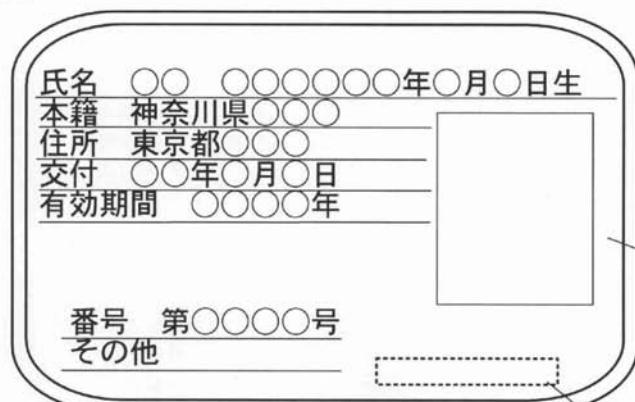

安全管理を行うため、食料品等の商品へIDチップを実装する場合を図15を用いて説明する。 40

IDチップ1503を実装したラベル1502と、当該ラベル1502が貼られた肉のパック1501を示す。IDチップ1503はラベル1502の表面に実装していてよいし、ラベル1502内部に実装してもよい。また野菜等の生鮮食品の場合、生鮮食品を覆うラップにIDチップを実装してもよい。

#### 【0136】

IDチップ1503には、商品の生産地、生産者、加工年月日、賞味期限等の商品に関する基本事項、更には商品を用いた調理例等の応用事項を記録することができる。このような基本事項は、書き換える必要がないためMR ROM(マスクROM: Mask ROM)

d Only Memory) や前述した有機素子を用いたメモリ等の書き換え不能なメモリを用いて記録するとよい。

【0137】

また食料品の安全管理を行うためには、加工前の動植物の状態を知り得ることが重要である。そのため、動植物内にIDチップを埋め込み、リーダ装置によって動植物に関する情報を取得するとよい。動植物に関する情報とは、飼育地、飼料、飼育者、伝染病の感染の有無等である。

【0138】

またIDチップに、商品の値段が記録されていれば、従来のバーコードを用いる方式よりも、簡便、短時間に商品の精算を行うことが可能となる。すなわち、IDチップが実装された複数の商品を一挙に精算することができる。但し、このように複数のIDチップを読み取る場合、アンチコリジョン機能をリーダ装置に搭載する必要がある。

【0139】

さらにIDチップの通信距離によっては、レジスターと商品との距離が遠くても、商品の精算を可能とすることができます。またIDチップは万引き防止にも役立つ。

【0140】

さらにIDチップは、バーコード、磁気テープ等のその他の情報媒体と併用することもできる。例えば、IDチップには書き換え不要な基本事項を記録し、バーコードには更新すべき情報、例えば値引き価格や特価情報を記録するとよい。バーコードはIDチップと異なり、情報の修正を簡便に行うことができるからである。

【0141】

このようにIDチップを実装することにより、消費者へ提供できる情報を増大させることができるために、消費者は安心して商品を購入することができる。

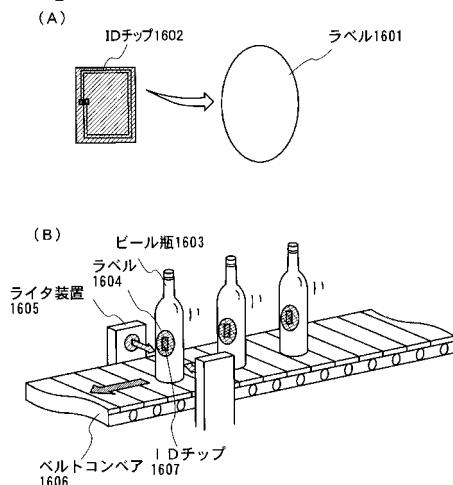

【0142】

物流管理を行うため、ビール瓶等の商品へIDチップを実装する場合を説明する。図16(A)に示すように、ビール瓶にIDチップ1602を実装する。例えば、ラベル1601を用いてIDチップ1602を実装することができる。

【0143】

IDチップには、製造日、製造場所、使用材料等の基本事項を記録する。このような基本事項は、書き換える必要がないためMR ROM(マスクROM: Mask Read Only Memory) や前述した有機素子を用いたメモリ等の書き換え不能なメモリを用いて記録するとよい。加えてIDチップには、各ビール瓶の配送先、配送日時等の個別事項を記録する。例えば、図16(B)に示すように、各ビール瓶1603がベルトコンベア1606により流れ、ライタ装置1605を通過するときに、ラベル1604に内蔵されたIDチップ1607に各配送先、配送日時を記録することができる。このような個別事項は、本発明の有機メモリを用いて記録するとよい。

【0144】

また配達先から購入された商品情報がネットワークを通じて物流管理センターへ送信されると、この商品情報に基づき、ライタ装置又は当該ライタ装置を制御するパーソナルコンピュータ等が配送先や配送日時を算出し、IDチップへ記録するようなシステムを構築するとよい。

【0145】

また配達はケース毎に行われるため、ケース毎、又は複数のケース毎にIDチップを実装し、個別事項を記録することもできる。

【0146】

このような複数の配達先が記録されうる飲料品は、IDチップを実装することにより、手作業で行う入力にかかる時間を削減でき、それに起因した入力ミスを低減することができる。加えて物流管理の分野において最もコストのかかる人件費用を削減することができる。従って、IDチップを実装したことにより、ミスの少ない、低コストな物流管理を行うことができる。

10

20

30

40

50

## 【0147】

さらに配達先において、ビールに合う食料品や、ビールを使った料理法等の応用事項を記録してもよい。その結果、食料品等の宣伝を兼ねることができ、消費者の購買意欲を高めることができる。このような応用事項は、本発明の有機メモリを用いて記録するとよい。このようにIDチップを実装することにより、消費者へ提供できる情報を増大させることができるために、消費者は安心して商品を購入することができる。

## 【0148】

製造管理を行うため、IDチップを実装した製造品と、当該IDチップの情報に基づき制御される製造装置（製造ロボット）について説明する。

## 【0149】

現在、オリジナル商品を生産する場面が多くみられ、このような場合、生産ラインでは当該商品のオリジナル情報に基づくように生産する。例えば、ドアの塗装色を自由に選択することができる自動車の生産ラインにおいては、自動車の一部にIDチップを実装し、当該IDチップからの情報に基づき、塗装装置を制御する。そしてオリジナルな自動車を生産することができる。

IDチップを実装する結果、事前に生産ラインに投入される自動車の順序や同色を有する数を調整する必要がない。強いては、自動車の順序や数それに合わせるように塗装装置を制御するプログラムを設定しなくてすむ。すなわち製造装置は、自動車に実装されたIDチップの情報に基づき、個別に動作することができる。

## 【0150】

このようにIDチップは様々な場所で使用することができる。そしてIDチップに記録された情報により、製造に関する固有情報を得ることができ、当該情報に基づき製造装置を制御することができる。

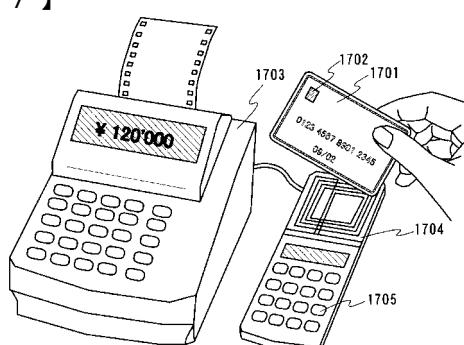

## 【0151】

次に、本発明のIDチップを用いたICカードを、電子マネーとして利用する形態について説明する。図17に、ICカード1701を用いて、決済をおこなっている様子を示す。ICカード1701は、本発明のIDチップ1702を有している。ICカード1701の利用の際には、レジスター1703、リーダ／ライタ1704を用いる。IDチップ1702には、ICカード1701に入金されている金額の情報が保持されており、リーダ／ライタ1704は該金額の情報を非接触で読み取り、レジスター1703に送信することができる。レジスター1703では、ICカード1701に入金されている金額が、決済する金額以上であることを確認し、決済を行なう。そしてリーダ／ライタ1704に決済後の残額の情報を送信する。リーダ／ライタ1704は該残額の情報を、ICカード1701のIDチップ1702に書き込むことができる。

## 【0152】

なおリーダ／ライタ1704に、暗証番号などを入力することができるキー1705を付加し、第三者によってICカード1701を用いた決済が無断で行なわれるのを制限できるようにしても良い。

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

## 【0153】

以上の様に、本発明の適用範囲は極めて広く、あらゆる物品の固体認識用のチップとして適用することが可能である。また、本発明は実施形態、実施例1～9のどのような組み合わせからなる構成を用いても実現することができる。

## 【図面の簡単な説明】

## 【0154】

【図1】本発明の有機素子を用いたメモリを示すブロック図。

【図2】従来の半導体装置の構成を示すブロック図。

【図3】従来の半導体装置の構成を示すブロック図。

【図4】RFタグシステムの概要を示す図。

10

20

30

40

50

- 【図 5】従来の N A N D 型フラッシュメモリの構成を示す図。

- 【図 6】フローティングゲート構造を示す図。

- 【図 7】有機素子の等価回路を示す図。

- 【図 8】本発明の有機素子のデータを示す図。

- 【図 9】本発明の有機素子のデータを示す図。

- 【図 10】本発明のアンテナの実施例を示す図。

- 【図 11】本発明のアンテナの実施例を示す図。

- 【図 12】メモリ回路に記憶されるデータの例を示す図。

- 【図 13】本発明を用いたバッグを示す図。

- 【図 14】本発明を用いた証明書を示す図。

- 【図 15】本発明を用いた食料品管理を説明する図。

- 【図 16】本発明を用いた物流管理を説明する図。

- 【図 17】本発明を用いた I C カード決済を説明する図。

- 【図 18】本発明の応用例を示す図。

- 【図 19】本発明における T F T の配置を示す図。

- 【図 20】本発明の半導体装置と保護層を組み合わせた図。

- 【図 21】本発明の N O R 型有機メモリの構成を示す図。

- 【図 22】本発明の断面図。

- 【図 23】本発明に用いるレーザ装置を示す図。

- 【図 24】本発明における T F T の配置を示す図。

- 【図 25】本発明の有機素子のデータを示す図。

- 【図 26】本発明の有機素子のデータを示す図。

- 【図 27】本発明の有機素子のデータを示す図。

- 【図 28】本発明の有機素子の積層構造。

## 【符号の説明】

## 【0 1 5 5】

|               |        |

|---------------|--------|

| 1 0 0         | メモリセル  |

| 1 0 1 ~ 1 1 2 | 有機素子   |

| 1 1 3 ~ 1 2 4 | トランジスタ |

| 1 2 5 ~ 1 3 0 | スイッチ   |

| 1 3 1 ~ 1 3 3 | 電流源    |

| 1 3 4         | 電源     |

| 1 3 5 ~ 1 3 9 | 電源端子   |

| 1 4 0 ~ 1 4 3 | 信号線    |

| 1 4 4 ~ 1 4 6 | センスアンプ |

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

○:短絡前 □:短絡後

【 図 2 6 】

【 図 27 】

【 図 2 8 】

【図14】

(A)

パスポート1401

IDチップ1402

(B)

免許証1403

IDチップ1404

【図15】

パック1501

ラベル1502

IDチップ1503

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

**G 1 1 C 13/00 (2006.01)**

G 1 1 C 13/02

**G 1 1 C 13/02 (2006.01)**

(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

F ターム(参考) 5B035 AA04 AA15 BA05 BB09 CA01 CA23

5F083 EP02 EP23 ER21 ER22 FZ07 GA29 HA02 JA36 JA37 JA42

JA60 LA03

5F110 AA17 BB04 BB08 BB20 CC02 DD01 DD02 DD03 DD05 GG06

GG13 GG25 HK07 NN71 PP03 PP24 QQ16