(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2014/147865 A1

(43) International Publication Date

25 September 2014 (25.09.2014)

WIPO | PCT

(51) International Patent Classification:

*G06F 11/00* (2006.01) *G11C 16/34* (2006.01)

*G06F 12/02* (2006.01) *G06F 11/20* (2006.01)

(72) Inventors: **HASHIMOTO, Daisuke**; c/o Intellectual Property Division, Toshiba Corporation, 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP). **NAGAI, Koichi**; c/o Intellectual Property Division, Toshiba Corporation, 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP). **WATANABE, Takanori**; c/o Intellectual Property Division, Toshiba Corporation, 1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP).

(21) International Application Number:

PCT/JP2013/073859

(22) International Filing Date:

29 August 2013 (29.08.2013)

(25) Filing Language: English

(74) Agent: **SAKAI, Hiroaki**; Sakai International Patent Office, Kasumigaseki Building, 2-5, Kasumigaseki 3-chome, Chiyoda-ku, Tokyo, 1006020 (JP).

(26) Publication Language: English

(30) Priority Data:

2013-055548 18 March 2013 (18.03.2013) JP

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(71) Applicant: **KABUSHIKI KAISHA TOSHIBA** [JP/JP];

1-1, Shibaura 1-chome, Minato-ku, Tokyo, 1058001 (JP).

[Continued on next page]

(54) Title: INFORMATION PROCESSING SYSTEM, CONTROL PROGRAM, AND INFORMATION PROCESSING DEVICE

FIG.1

(57) Abstract: According to an embodiment, an information processing system determines a storage status of a first storage unit based on reliability information acquired from the first storage unit, when the storage status of the first storage unit is recognized as a protected state, executes write on a second storage unit and executes read on at least one of the first and second storage units, and updates addresses of stored data in the first and second storage units according to the write.

(84) **Designated States** (*unless otherwise indicated, for every kind of regional protection available*): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

**Published:**

— *with international search report (Art. 21(3))*

## DESCRIPTION

INFORMATION PROCESSING SYSTEM, CONTROL PROGRAM, AND

INFORMATION PROCESSING DEVICE

5

## CROSS-REFERENCE TO RELATED APPLICATION

This application is based upon claims the benefit of priority from Japanese Patent Application No. 2013-055548 filed on March 18, 2013, the entire contents of all of 10 which are incorporated herein by reference.

## FIELD

Embodiments described herein relate to an information processing system, a control program, and an information 15 processing device for migrating data of a first storage unit to a second storage unit.

## BACKGROUND

When a secondary storage device for a personal 20 computer or a server is configured using a flash memory, in some case, there are a defective block that cannot be used as a storage area or a defective area that cannot be read because, for example, errors often occur. When the number of defective blocks or the number of defective areas 25 exceeds an upper limit value, because a new defective block or defective area cannot be registered, write of write-requested data in a flash memory cannot be guaranteed. Therefore, when the number of defective blocks or the number of defective areas exceeds the upper limit value, 30 even if there is a free area in the flash memory, write of data is suddenly disabled.

Therefore, there is a method of monitoring deterioration of a storage device and limiting write of

data from an information processing device to the storage device before the life end of the storage device. With this method, it is possible to back up user data in another storage device and migrate the user data before the life 5 end of the storage device and prevent a data loss due to the life end of the storage device.

However, this method is complicated because work for backing up the user data in the other storage device has to be performed. Further, because data write in the original 10 storage device for backup is limited by the information processing device, it is likely that the operation of various application programs loaded in the information processing device is limited and processing speed of the application programs falls.

15 There are literatures related to the related art as listed below.

Patent Literature 1 United States Patent Application Publication No. 2012/0284453

20 Patent Literature 2 United States Patent Application Publication No. 2012/0246388

Patent Literature 3 United States Patent Application Publication No. 2009/0222617

Patent Literature 4 United States Patent No. 8,230,164

Patent Literature 5 United States Patent No. 7,861,122

25 Patent Literature 6 United States Patent No. 7,840,836

Patent Literature 7 United States Patent Application Publication No. 2007/0214187

Patent Literature 8 United States Patent No. 7,606,946

Patent Literature 9 United States Patent No. 6,529,992

30 Patent Literature 10 United States Patent No. 7, 222,259

Patent Literature 11 United States Patent No. 7,424,639

Patent Literature 12 United States Patent No.

7,739,544

Patent Literature 13 United States Patent No.

7,525,749

5 Patent Literature 14 United States Patent No.

8,037,380

Patent Literature 15 United States Patent

Application Publication No. 2010/0325199

Patent Literature 16 United States Patent

10 Application Publication No. 2011/0239083

Patent Literature 17 Japanese Patent No. 5052376

Patent Literature 18 Japanese Patent Application

Laid-Open No. 2010-225021

Patent Literature 19 Japanese Patent No. 3,565,687

15 Patent Literature 20 United States Patent No.

8,176,367

Patent Literature 21 United States Patent

Application Publication No. 2011/0197045

Patent Literature 22 Japanese Patent No. 4,643,456

20 Patent Literature 23 Japanese Patent No. 4,764,490

Patent Literature 24 Japanese Patent Application

Laid-Open No. 2011-209879

Patent Literature 25 WO2013/027642

Non-Patent Literature 1 Information technology

25 ATA/ATAPI Command Set-3 (ACS-3), d2161r4-

ATAATAPI\_Command\_Set\_-\_3.pdf, Sep. 04. 2012,

<http://www.t13.org/>

Non-Patent Literature 2 NVM Express Revision 1.1, Oct.

11. 2012, [NVM\\_Express\\_1\\_1.pdf](http://www.nvexpress.org/), <http://www.nvexpress.org/>

30 Non-Patent Literature 3 Serial ATA International

Organization: Serial ATA Revision 3.1 Gold Revision, Jul.

18. 2011, <http://www.serialata.org/>

Non-Patent Literature 4 PCI Express Base

Specification Revision 3.0, Nov. 10. 2010,

<http://www.pcisig.com/>

Non-Patent Literature 5 Serial ATA Technical

Proposal: SATA31\_TPR\_C108 Title: Device Sleep,

5 <http://www.serialata.org/>

Non-Patent Literature 6 SCSI Primary Commands-4 (SPC-

4), INCITS T10/1731-D, Revision 36e, <http://www.t10.org/>

Non-Patent Literature 7 Masaru Kitsuregawa,

"Yokuwakaru Storage Networking", First Edition, Ohm, Ltd.,

10 May 20, 2011, p. 6 to 9 and p. 67 to 93

#### BRIEF DESCRIPTION OF THE DRAWINGS

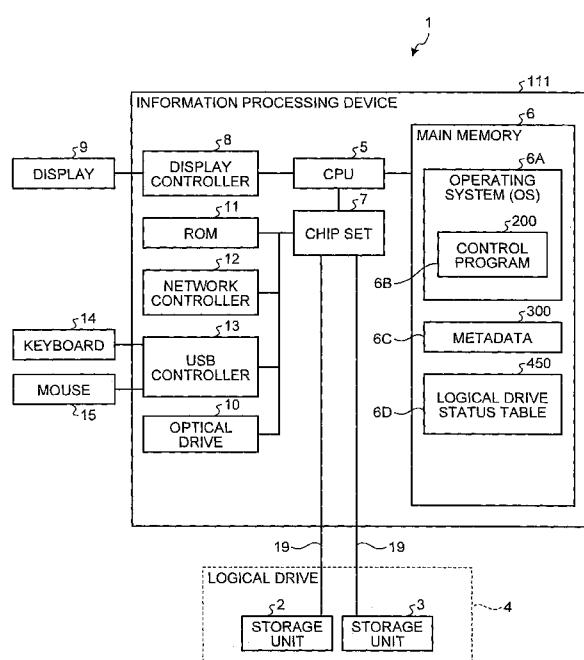

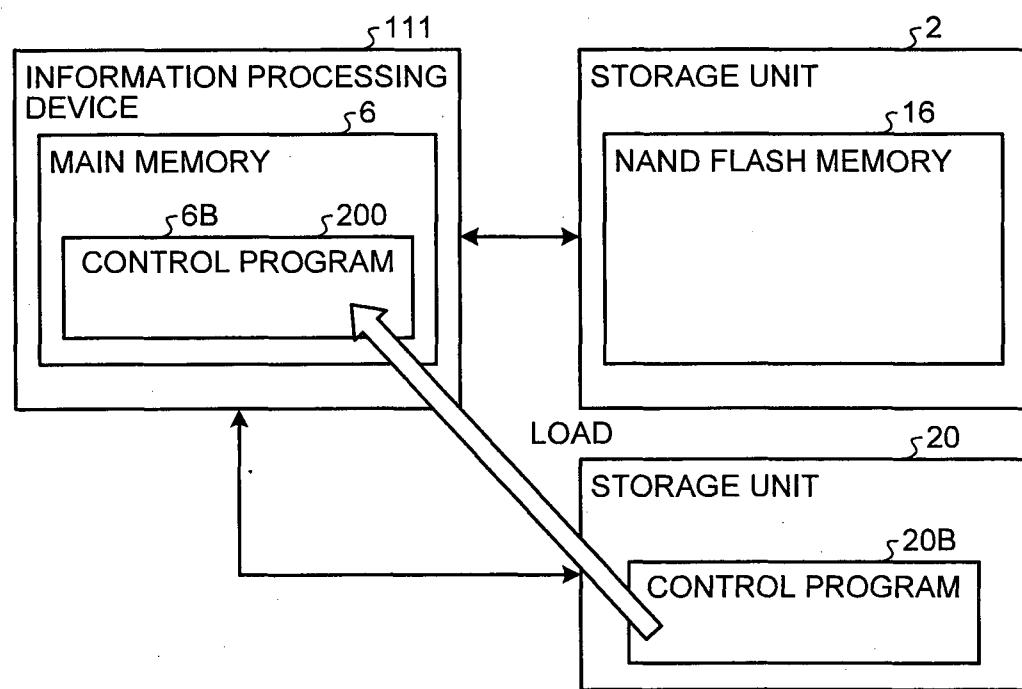

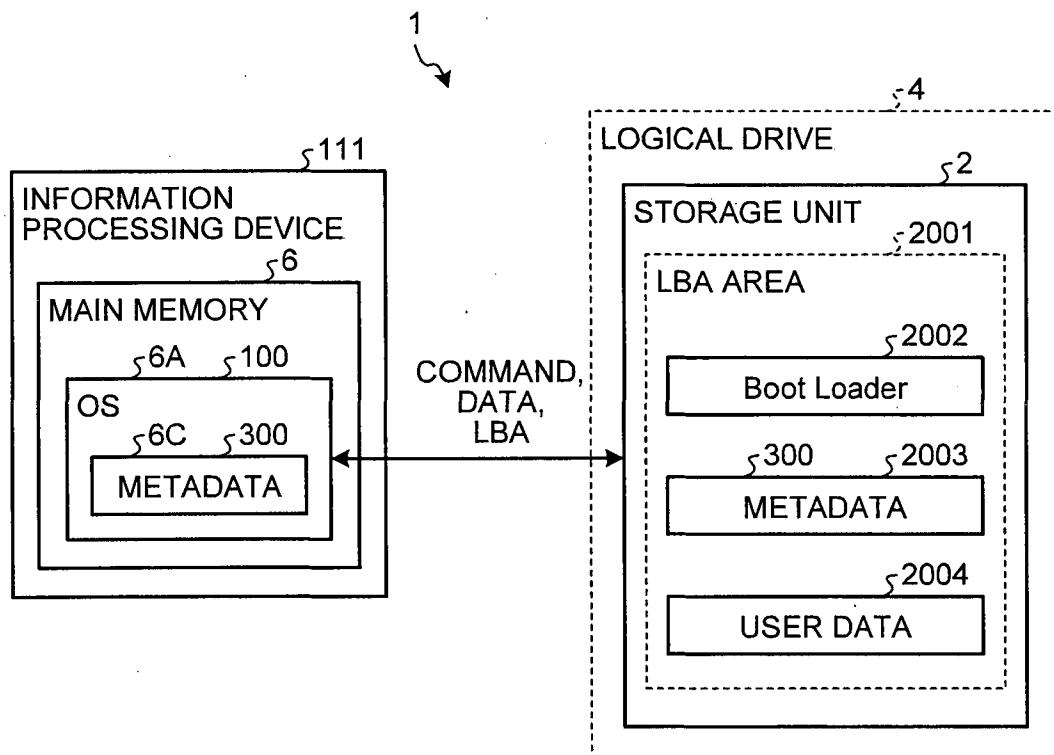

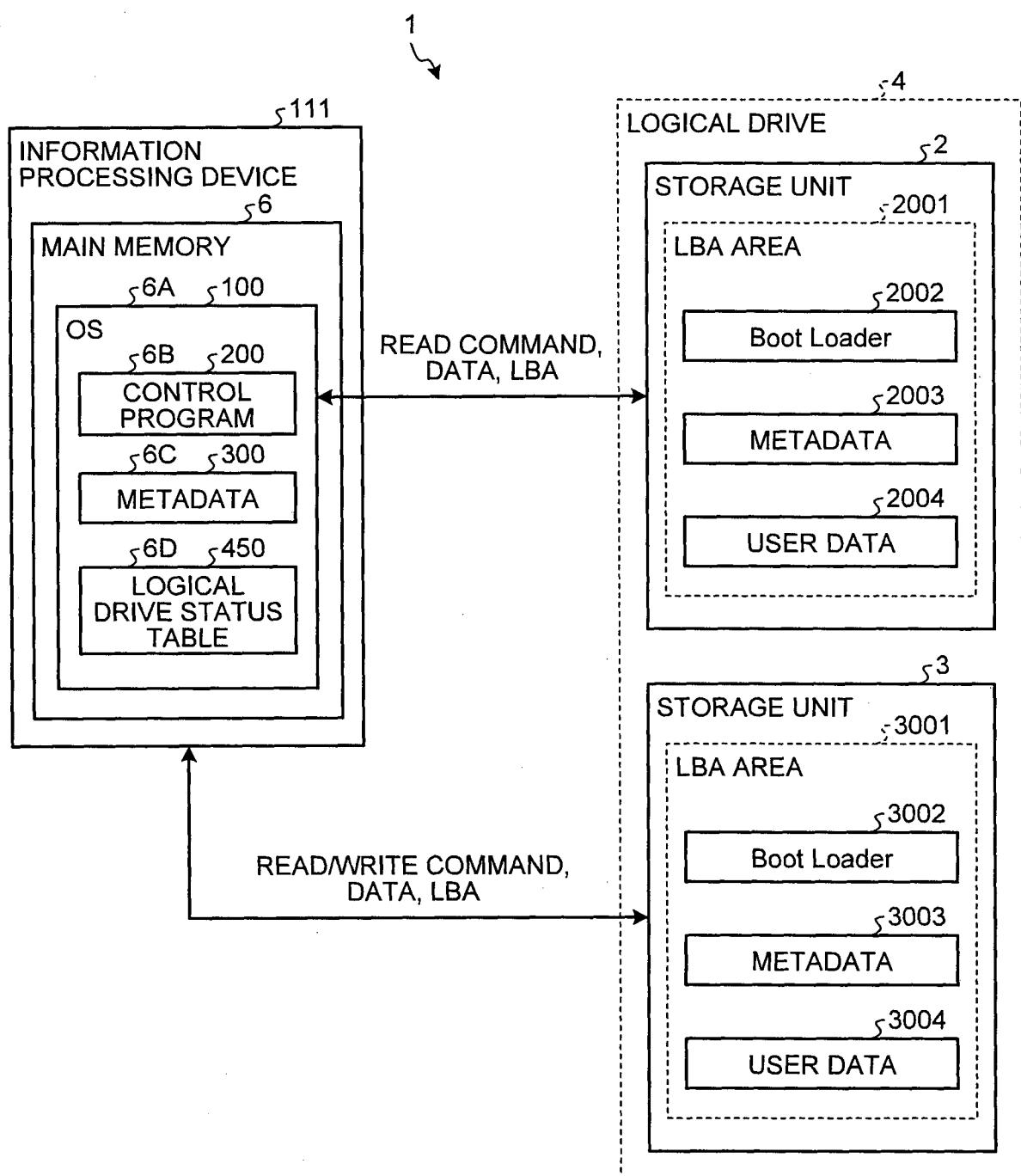

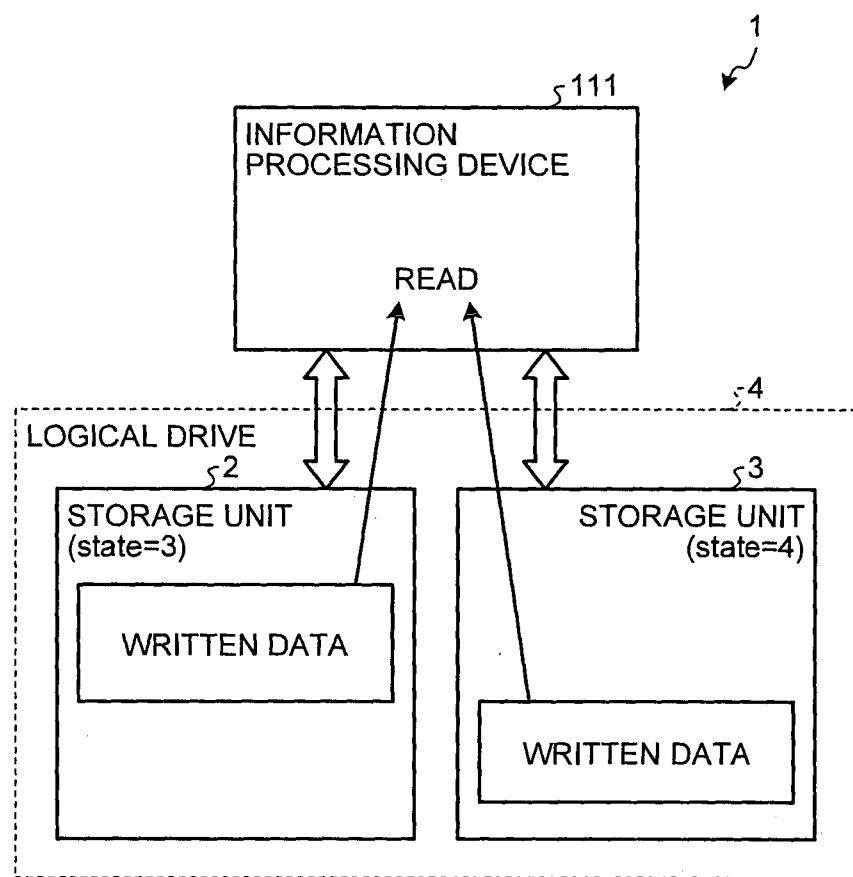

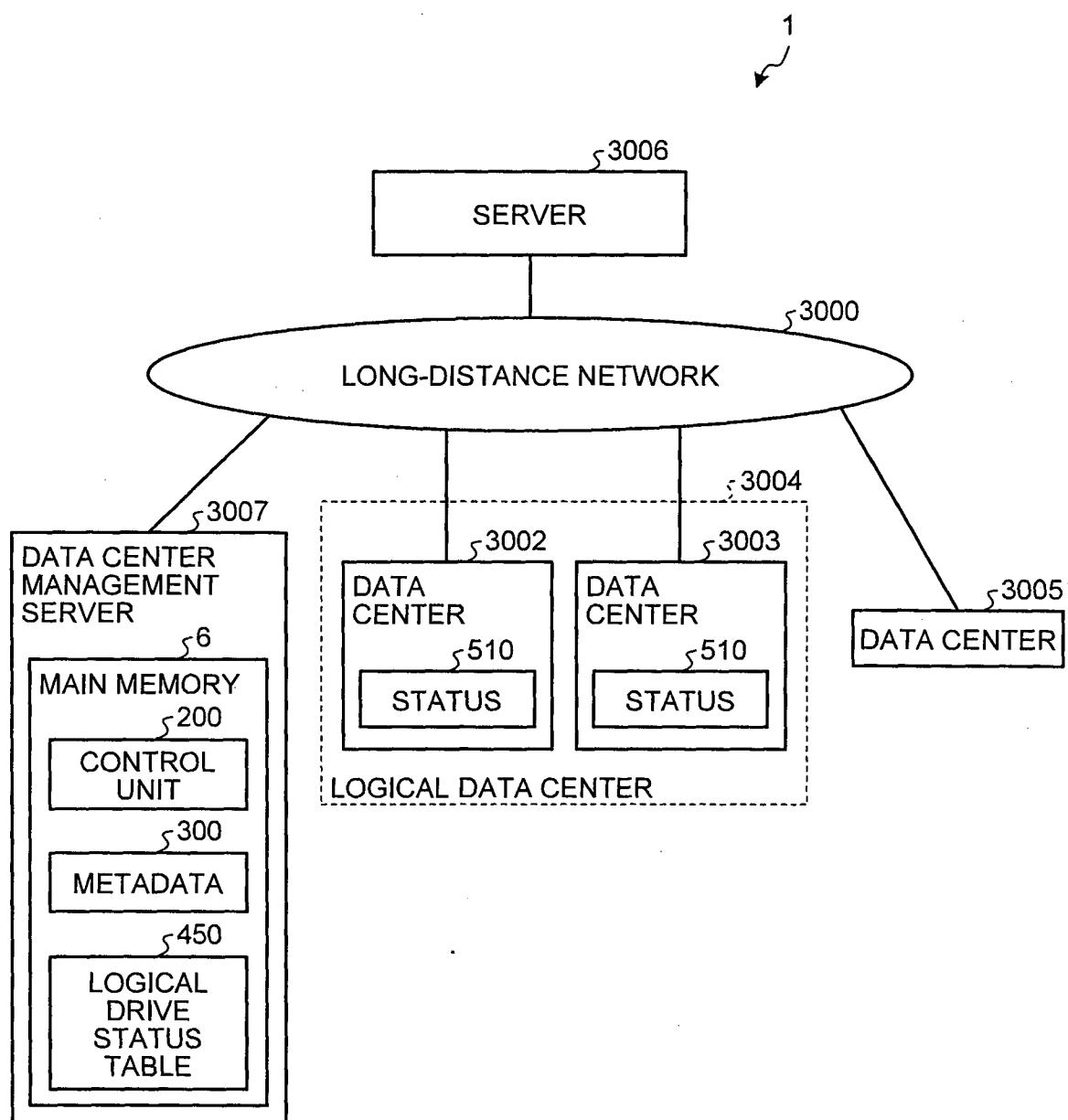

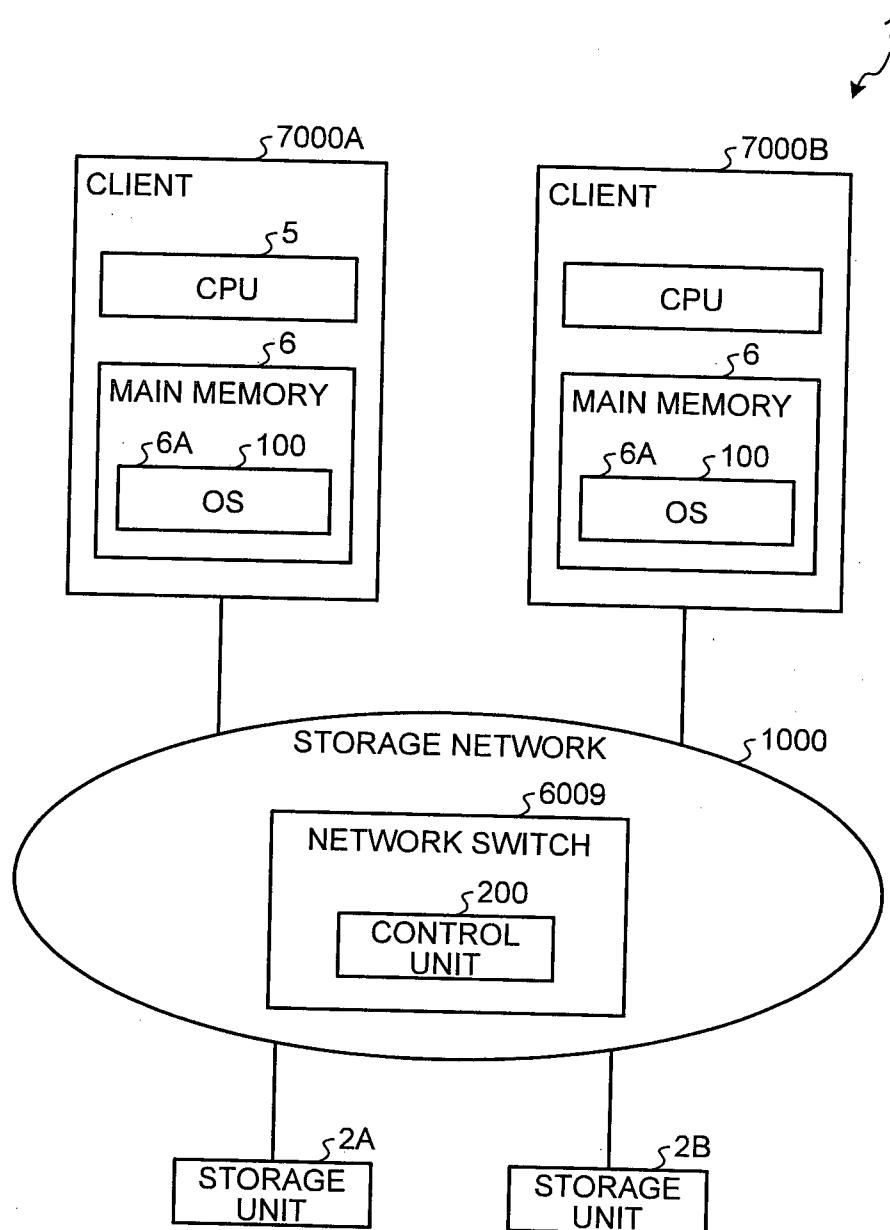

Fig. 1 is a block diagram of a functional

configuration example of an information processing system

15 in a first embodiment;

Fig. 2 is a block diagram of a functional

configuration example of the information processing system

in storing a control program in a SSD;

Fig. 3 is a block diagram of a functional

20 configuration example of the information processing system

in storing the control program in another external storage

device;

Fig. 4 is a block diagram of a functional

configuration example of the information processing system

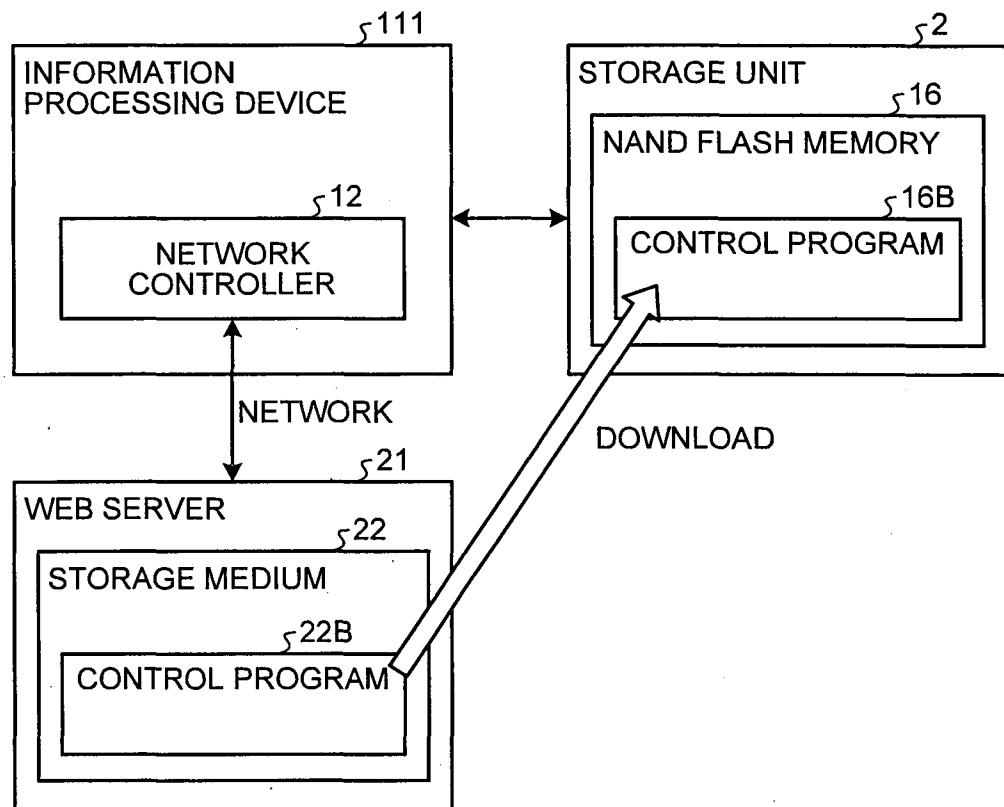

25 in installing the control program from a WEB;

Fig. 5 is block diagram of a functional configuration

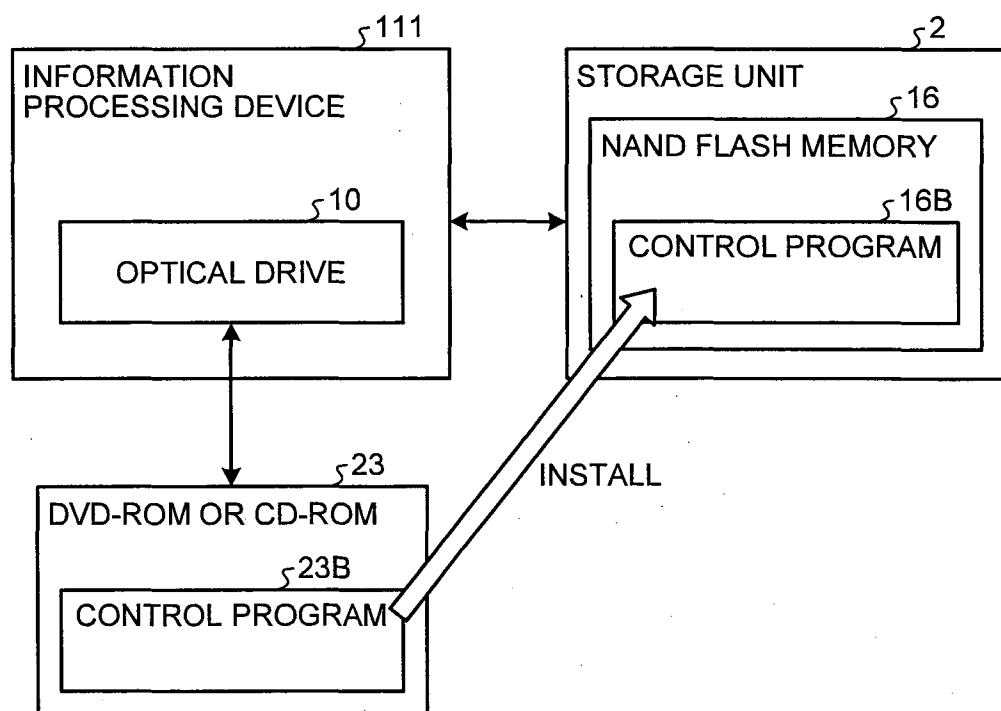

example of the information processing system in installing

the control program from an optical drive;

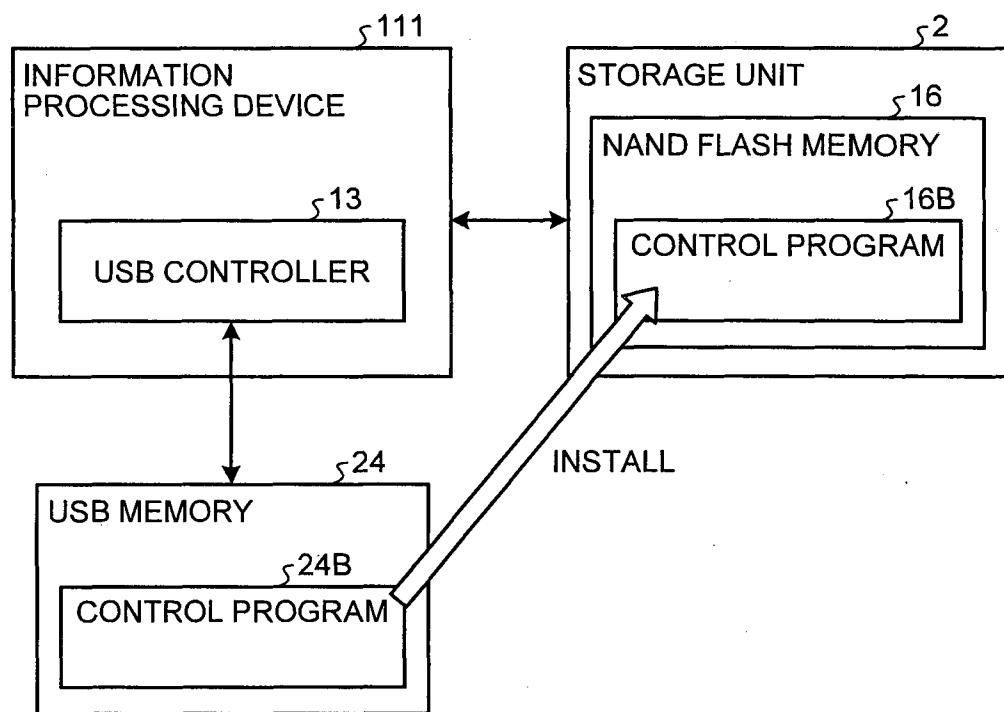

Fig. 6 is a block diagram of a functional

30 configuration example of the information processing system

in installing the control program from a USB memory;

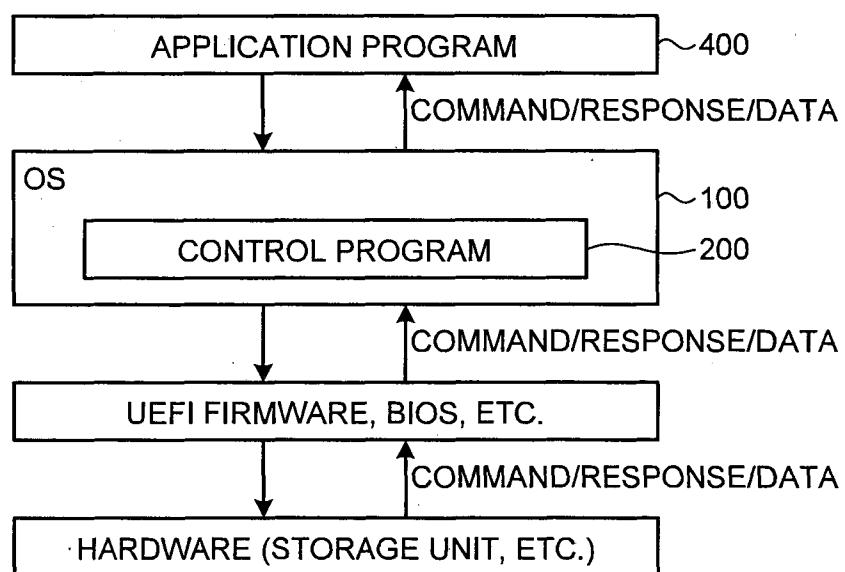

Fig. 7 is a block diagram of a hierarchical functional

configuration example of the information processing device;

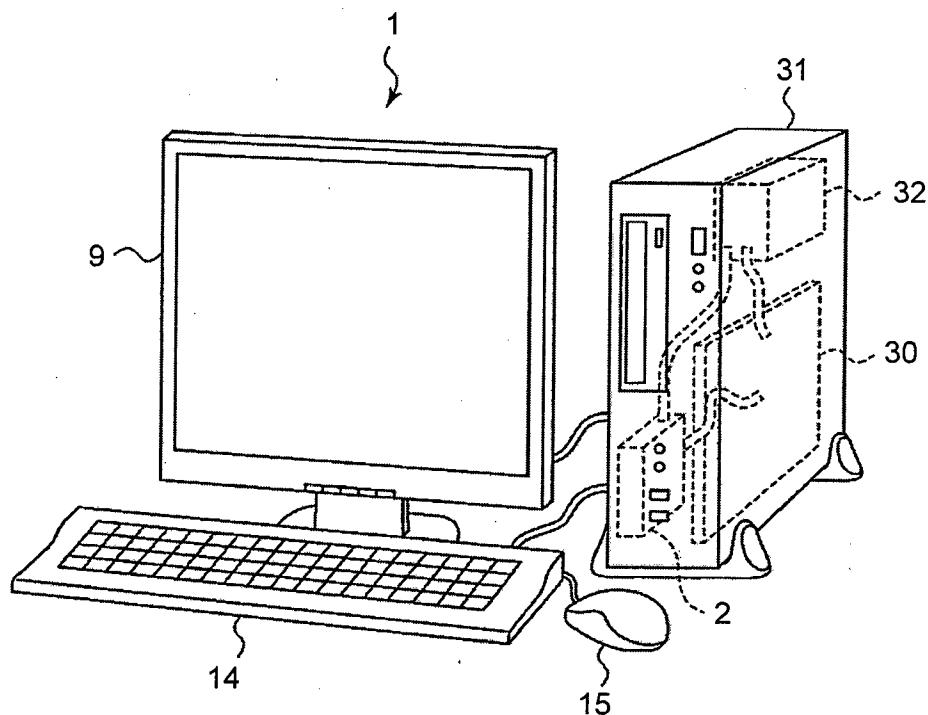

Fig. 8 is a diagram of an external configuration of the information processing system;

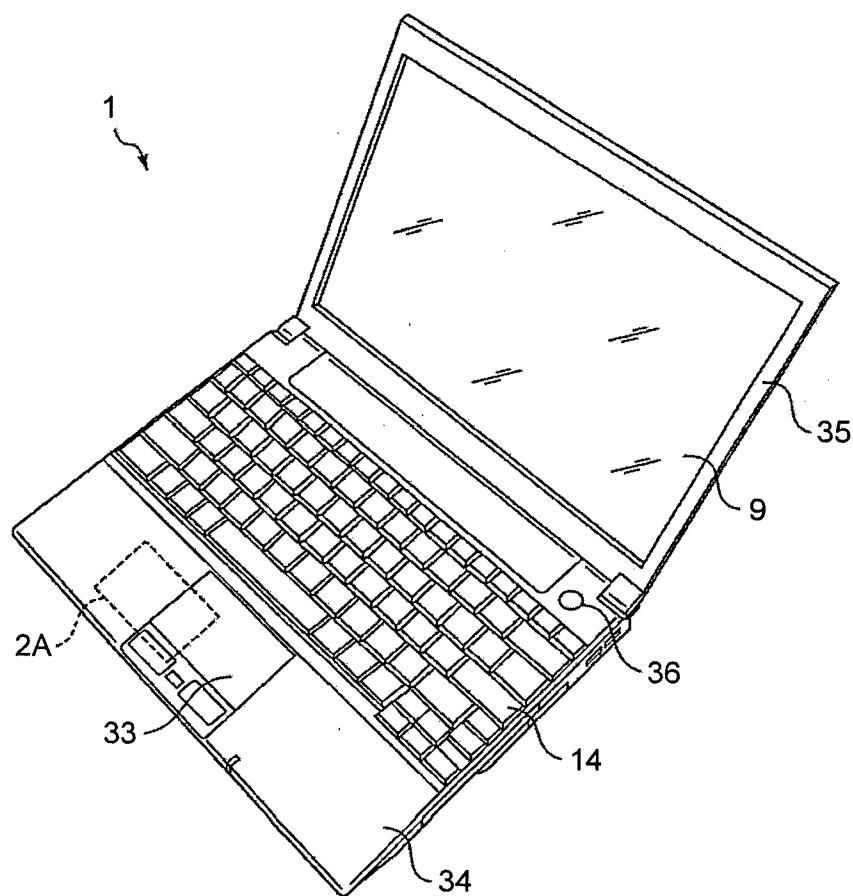

Fig. 9 is a diagram of another external configuration of the information processing system;

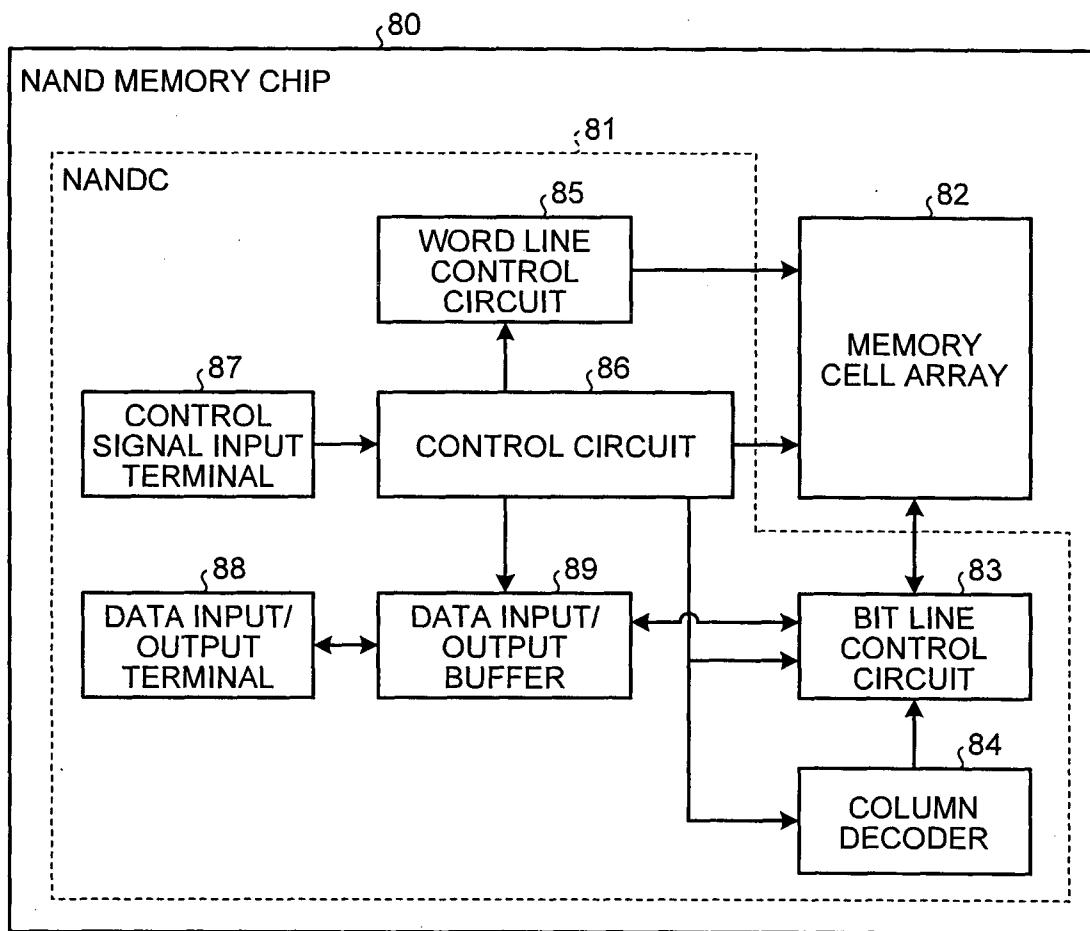

5 Fig. 10 is a block diagram of a functional configuration example of a NAND memory chip;

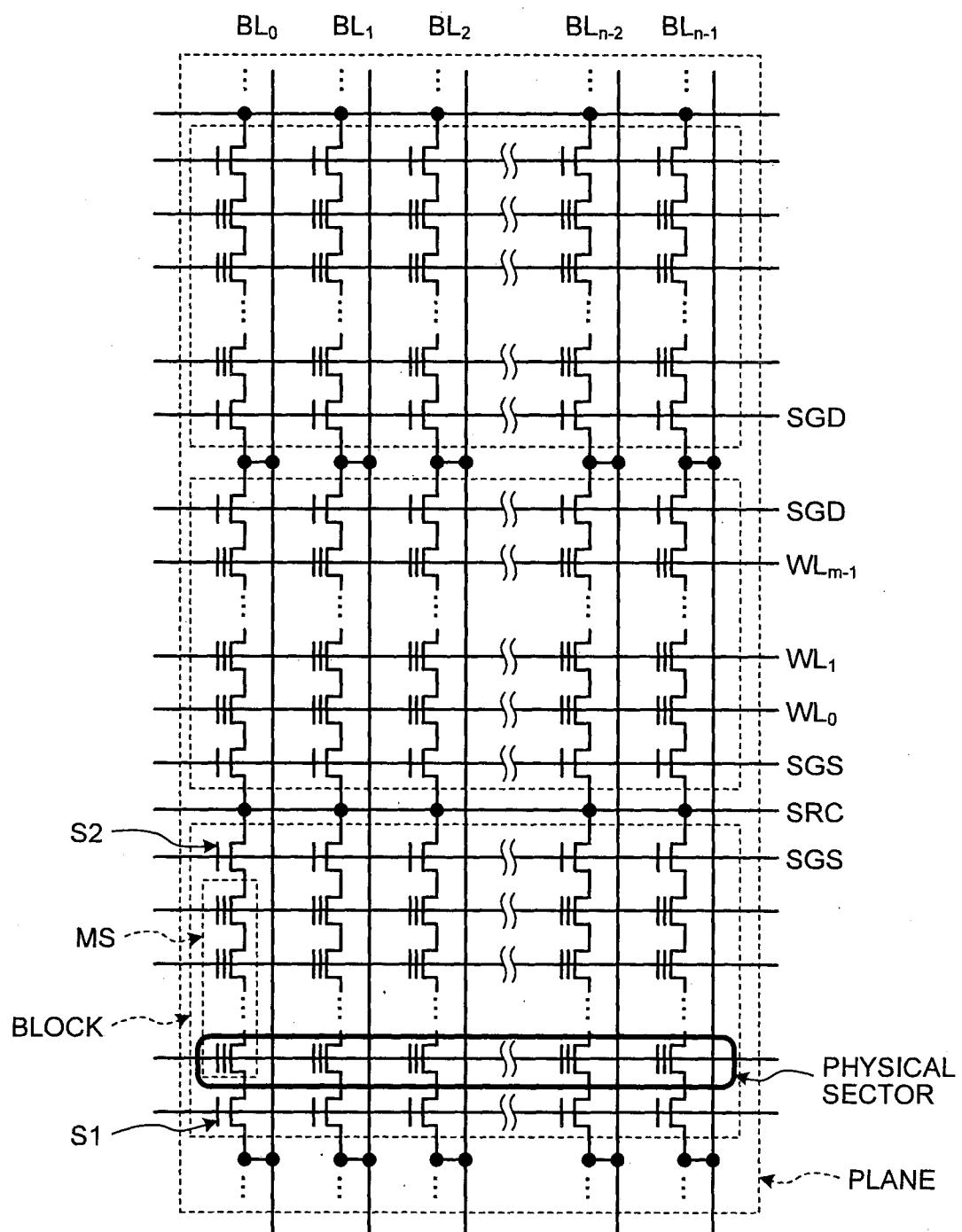

Fig. 11 is a circuit diagram of a configuration example of one plane included in the NAND memory chip;

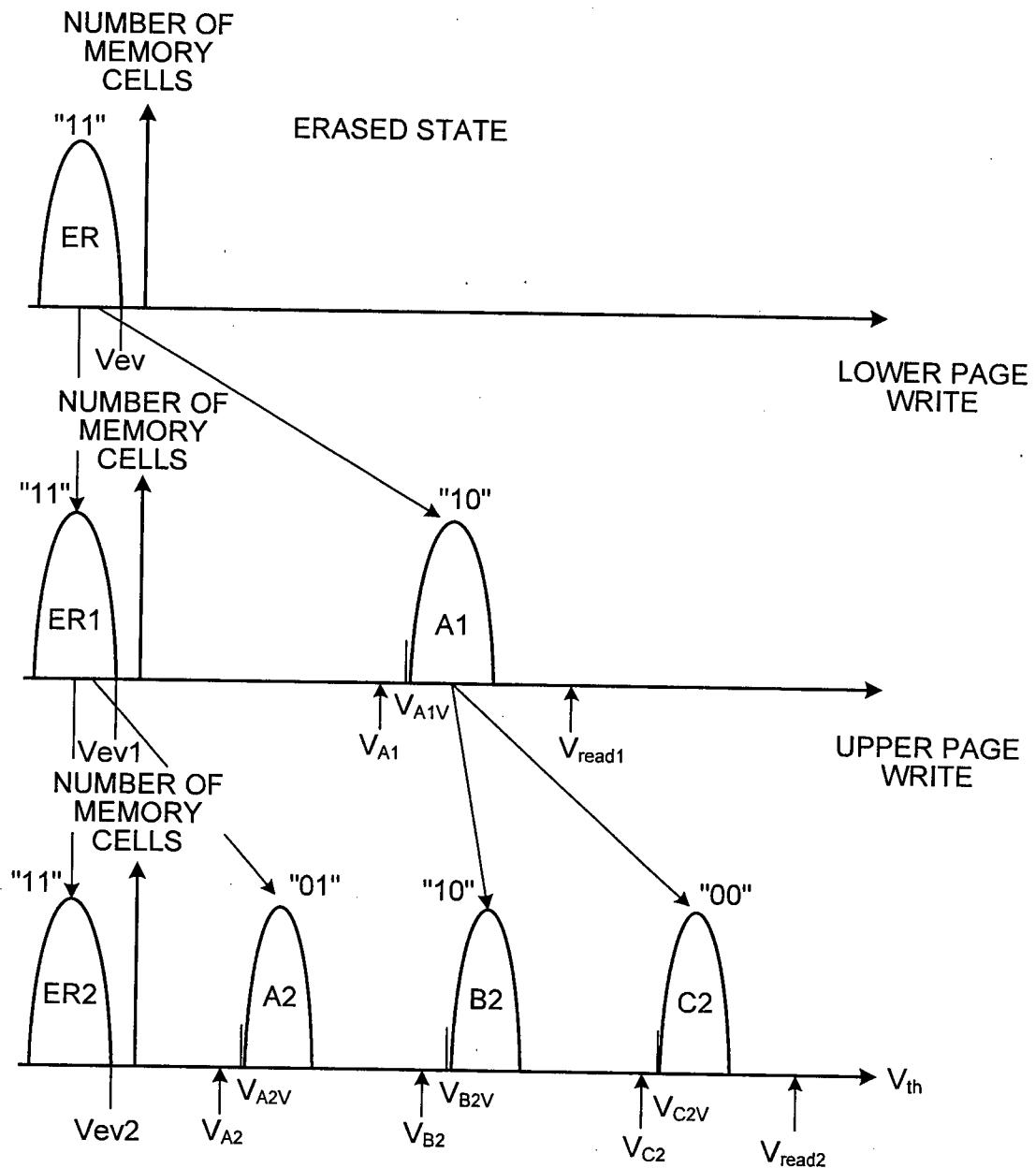

10 Fig. 12 is a diagram of a threshold voltage distribution in a four-level data storage method;

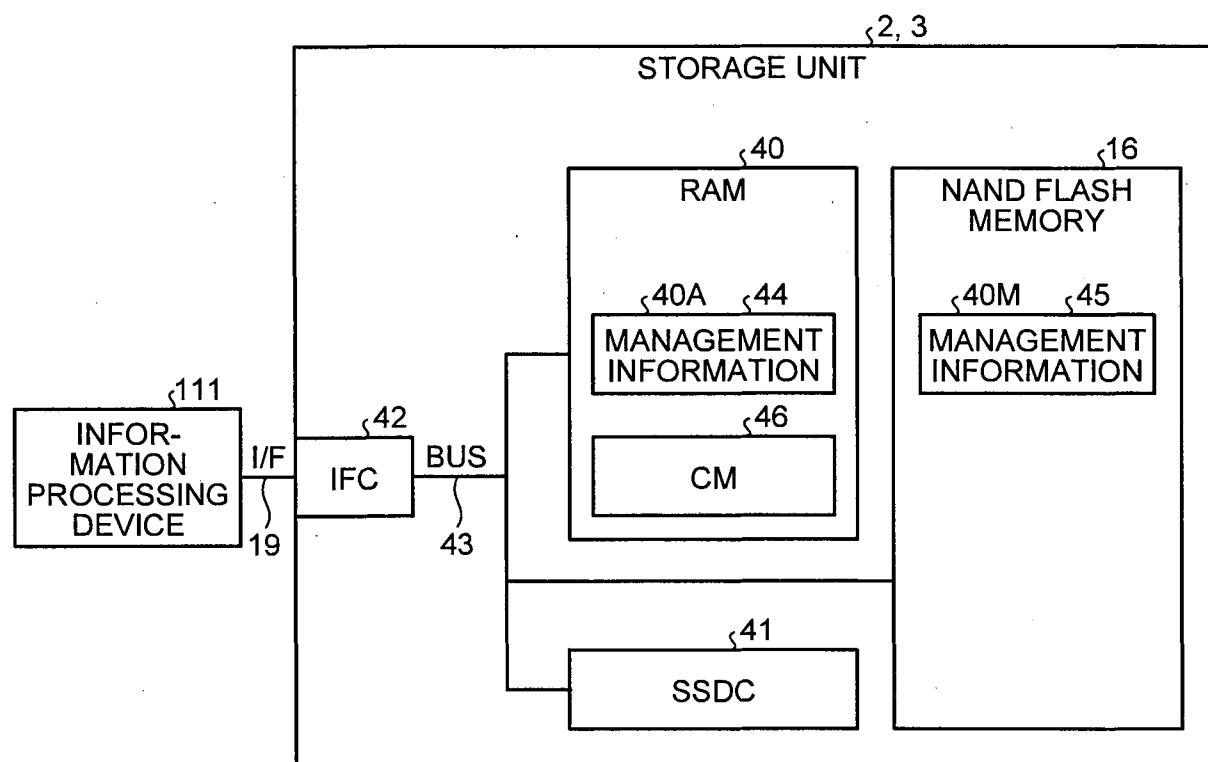

Fig. 13 is a block diagram of a functional configuration example of the SSD;

Fig. 14 is a diagram of management information of the SSD;

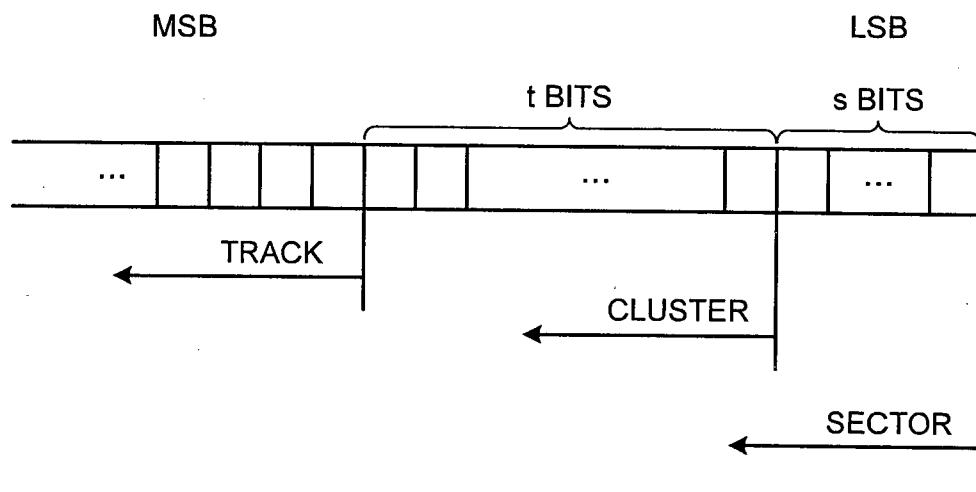

15 Fig. 15 is a diagram of a relation between an LBA and a management unit of the SSD;

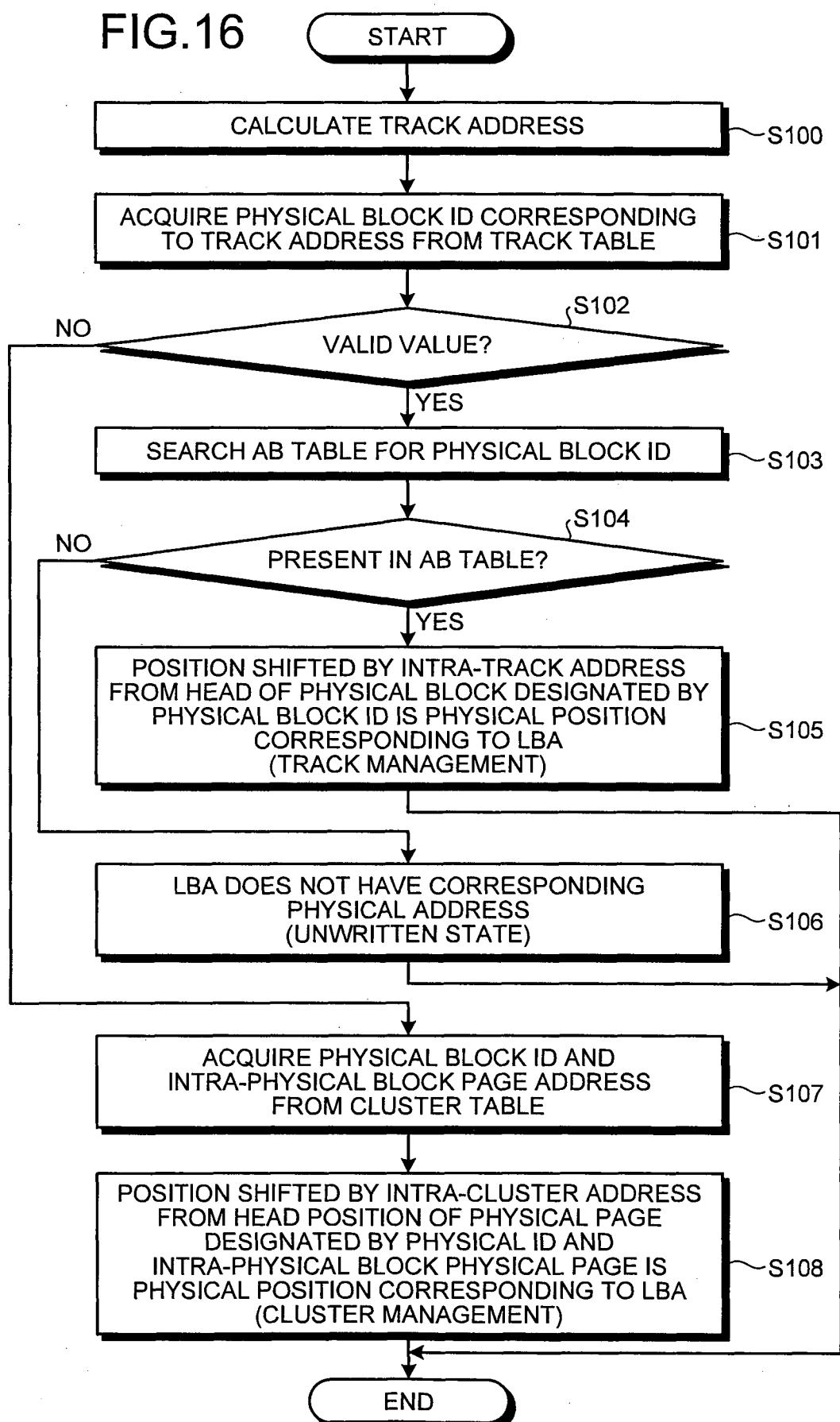

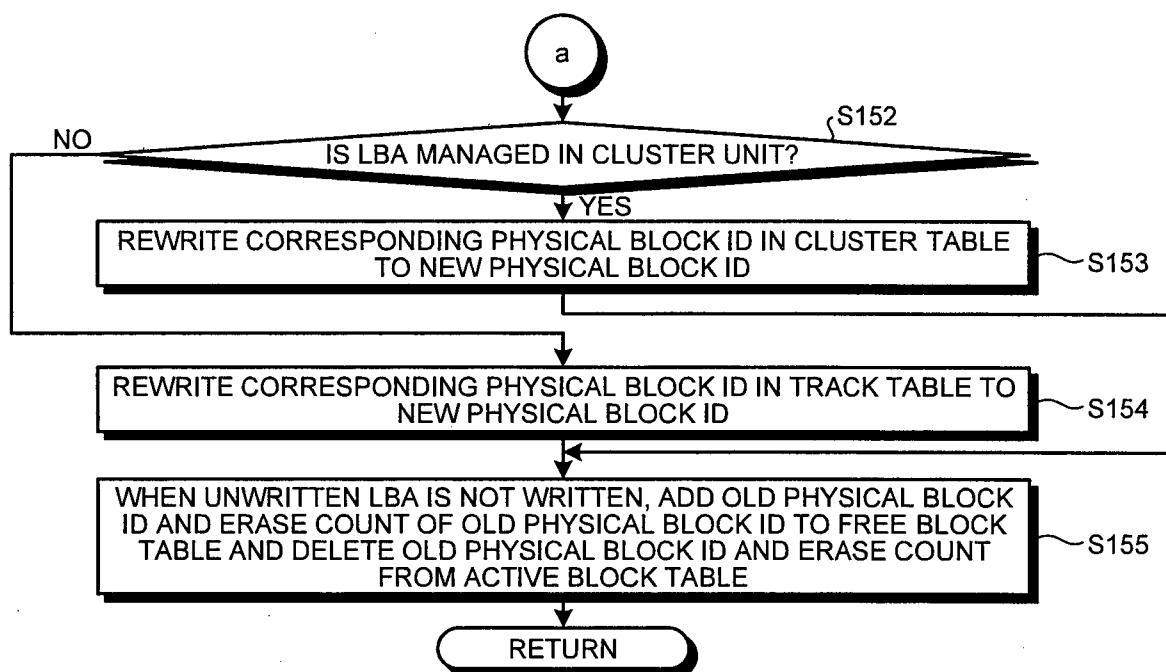

Fig. 16 is a flowchart for explaining a procedure for specifying a physical address from the LBA;

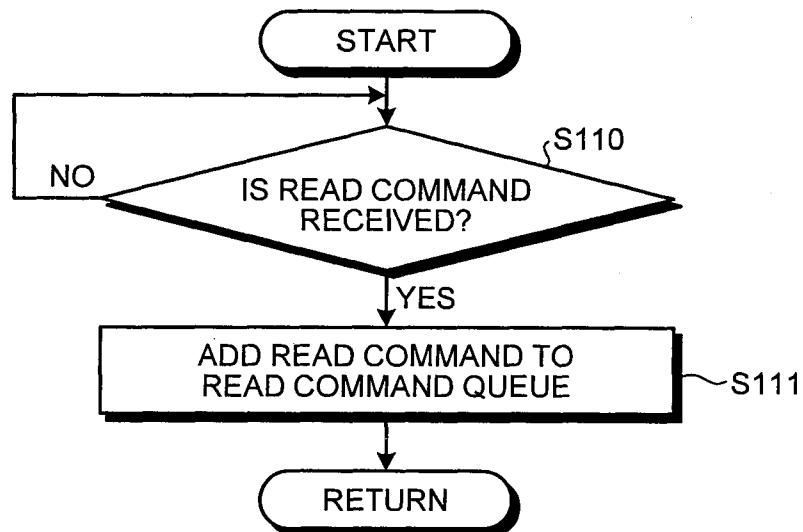

20 Fig. 17 is a flowchart for explaining an example of a read operation from the SSD;

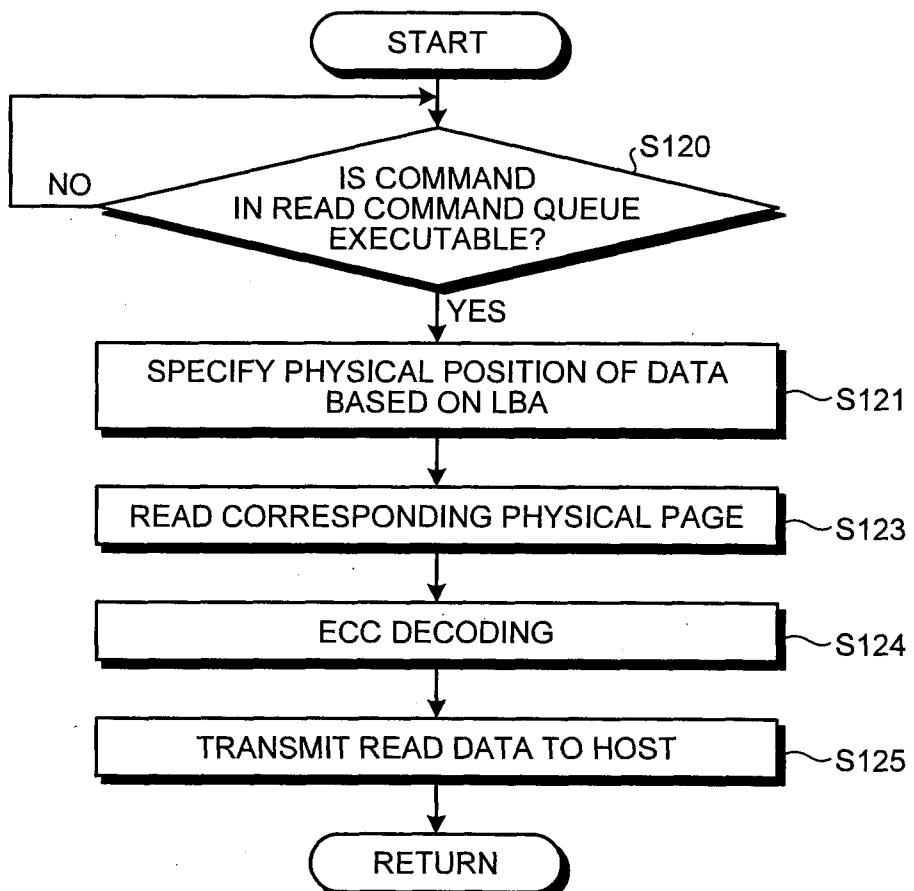

Fig. 18 is a flowchart for explaining an example of a read operation from the SSD;

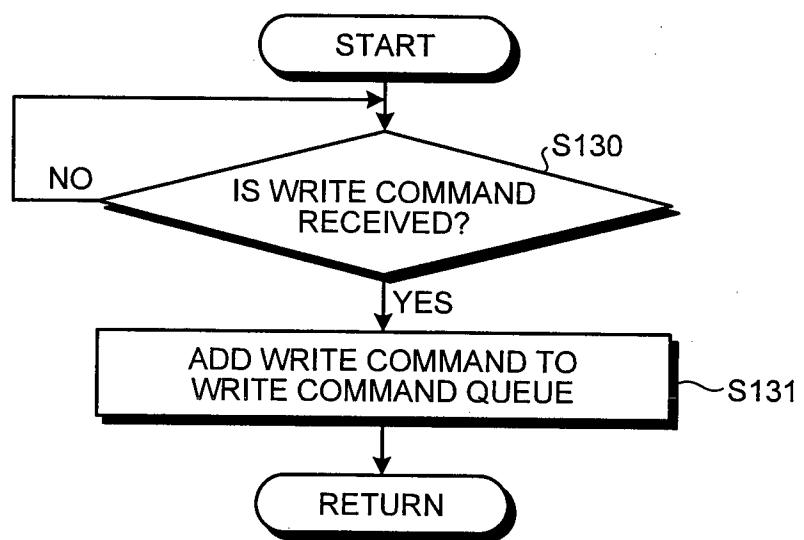

Fig. 19 is a flowchart for explaining an example of a read operation from the SSD;

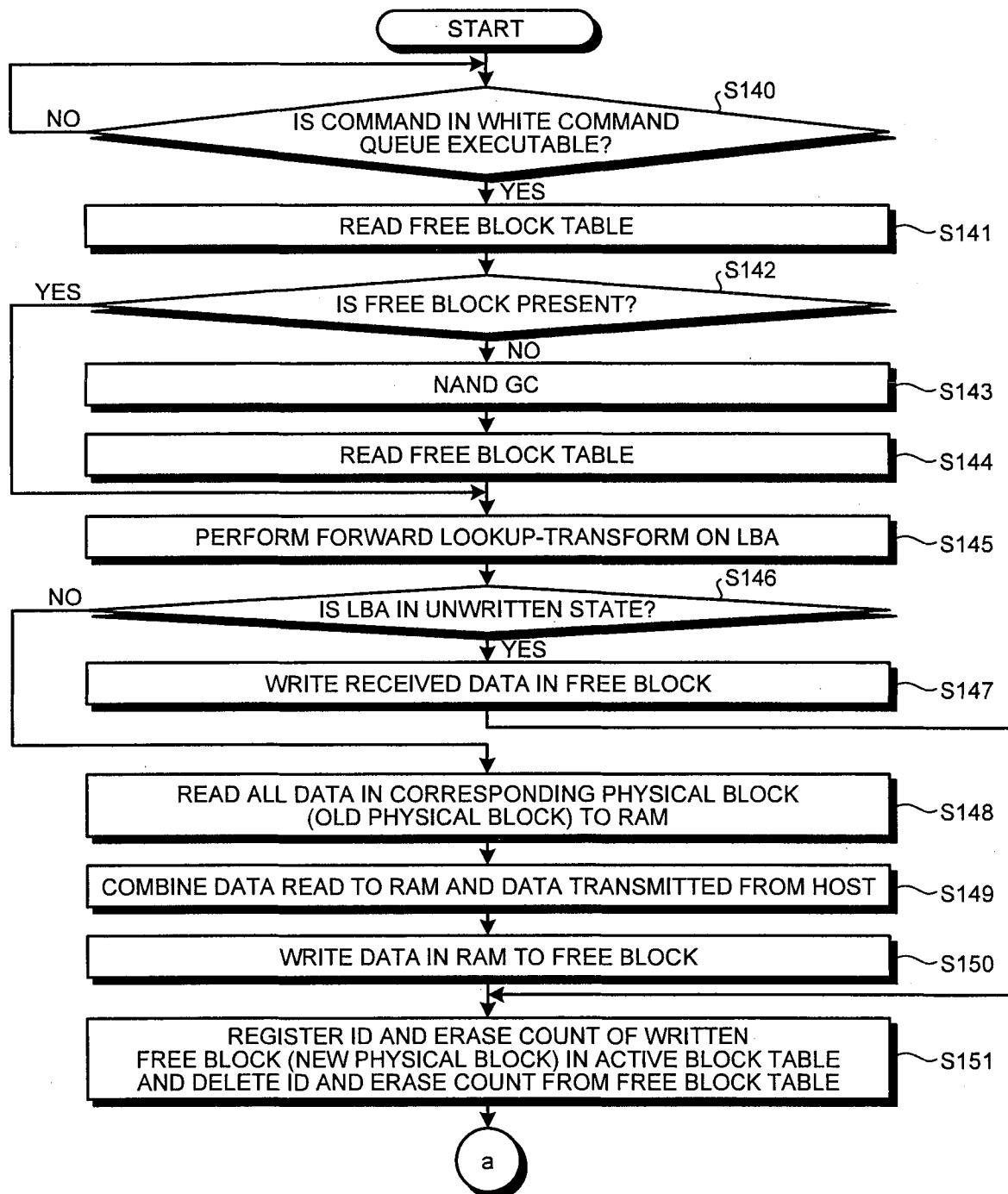

25 Fig. 20A and Fig. 20B are flowchart for explaining an example of a read operation from the SSD;

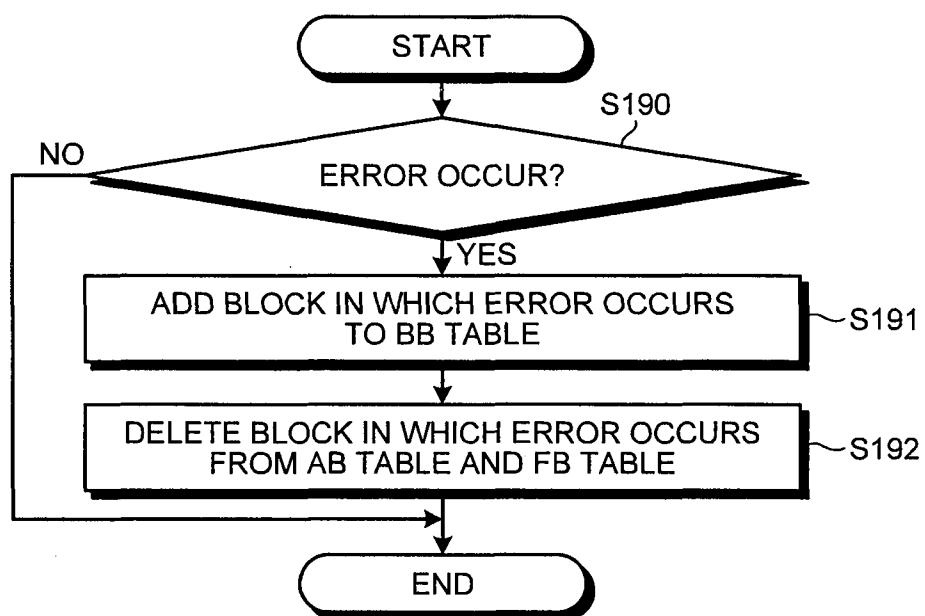

Fig. 21 is a flowchart for explaining an operation procedure in performing NAND GC;

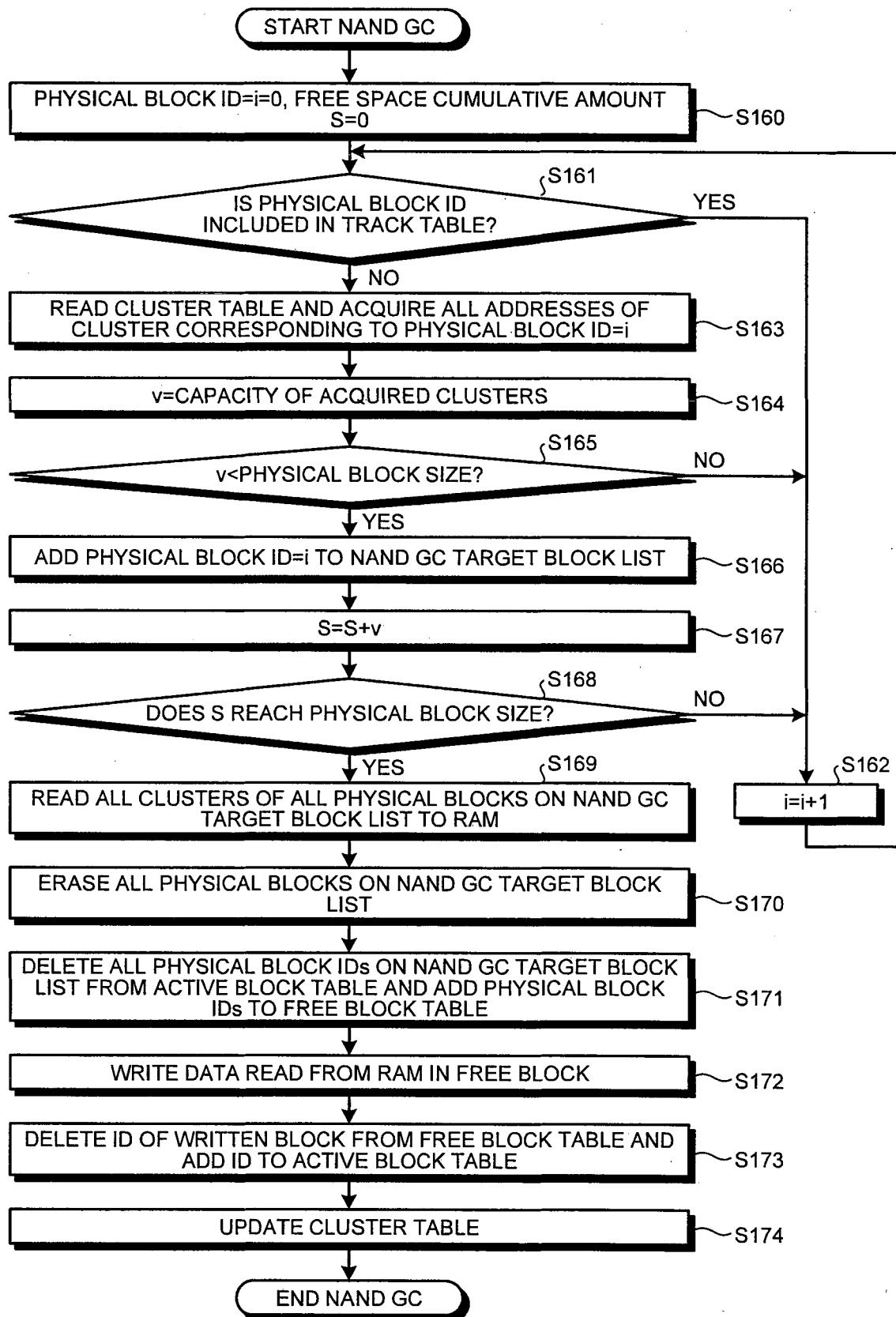

30 Fig. 22 is a flowchart for explaining an operation example of the SSD performed when a delete notification is received;

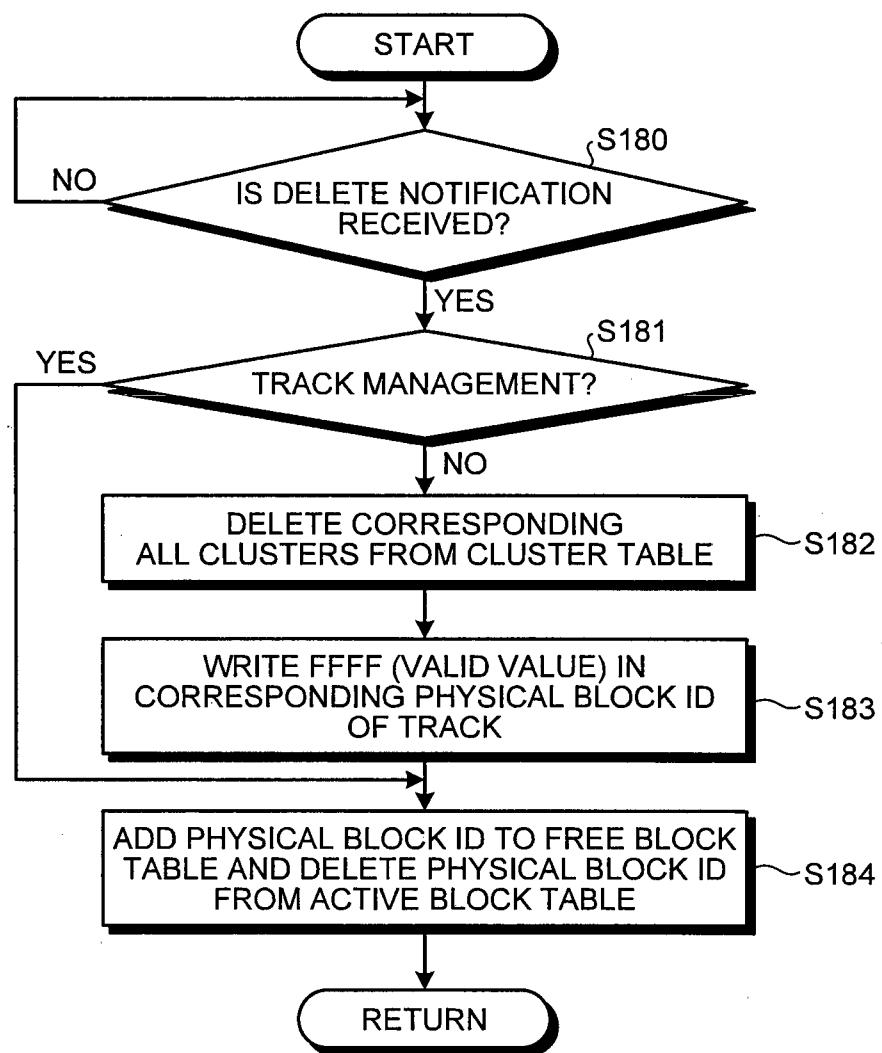

Fig. 23 is a flowchart for explaining an operation example of the SSD performed when an error occurs;

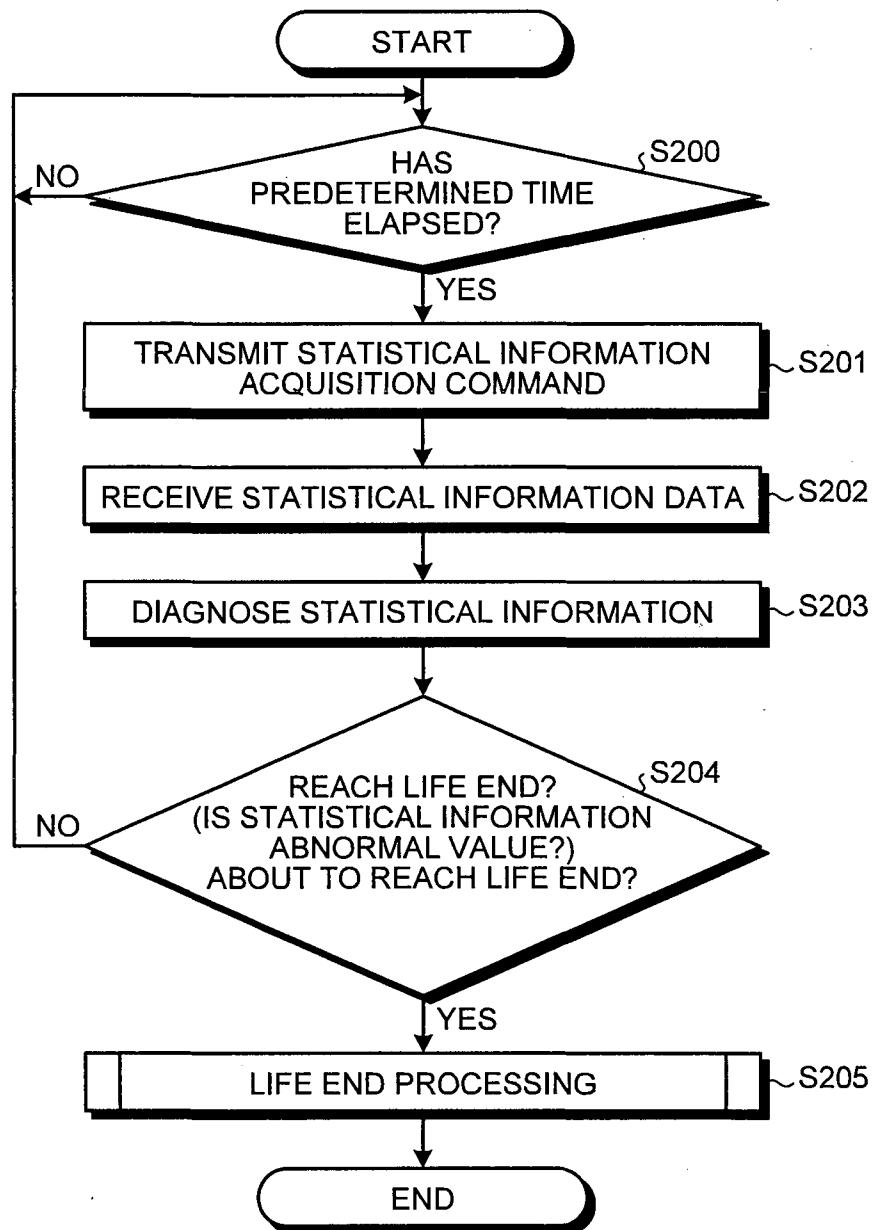

Fig. 24 is a flowchart for explaining statistical information acquisition processing;

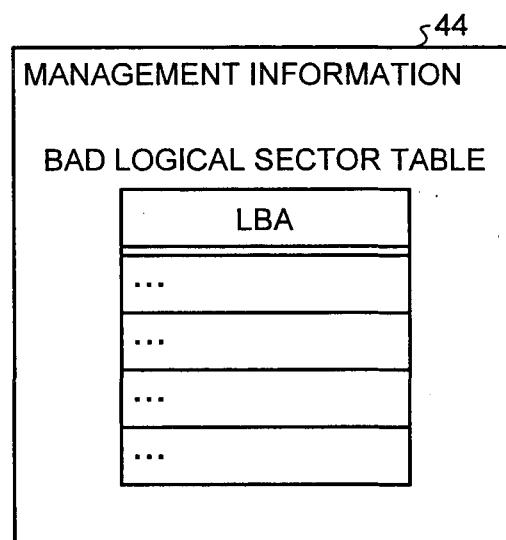

Fig. 25 is a diagram of a bad logical sector table;

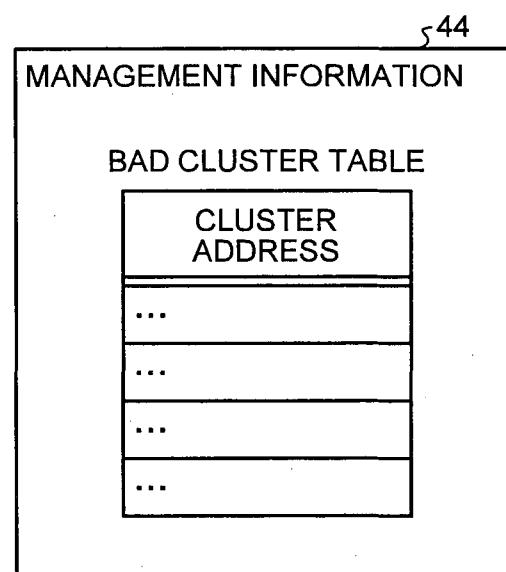

Fig. 26 is a diagram of a bad cluster table;

5 Fig. 27A and Fig. 27B are diagram of SMART information serving as an example of statistical information;

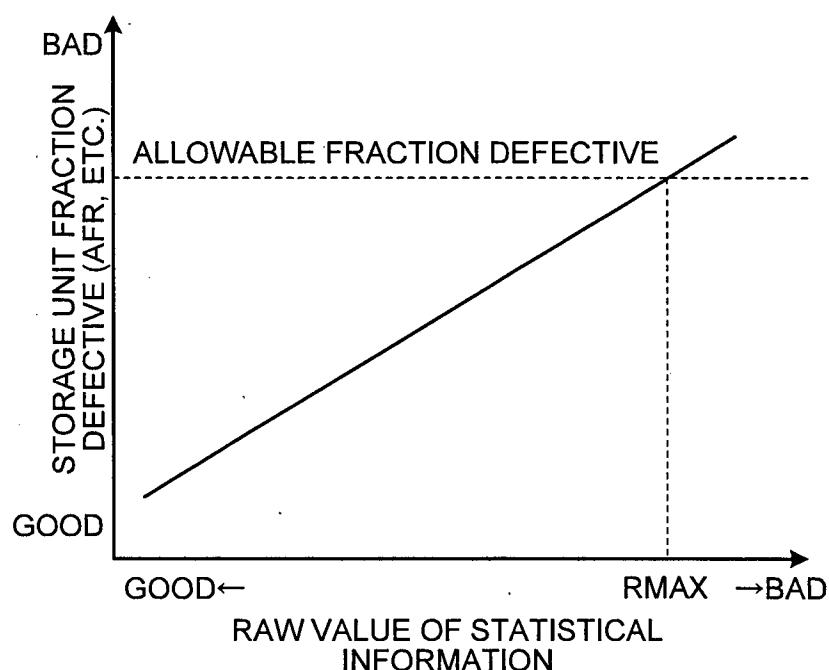

Fig. 28 is a graph of a relation between a Raw Value of the statistical information and a reject ratio of the SSD;

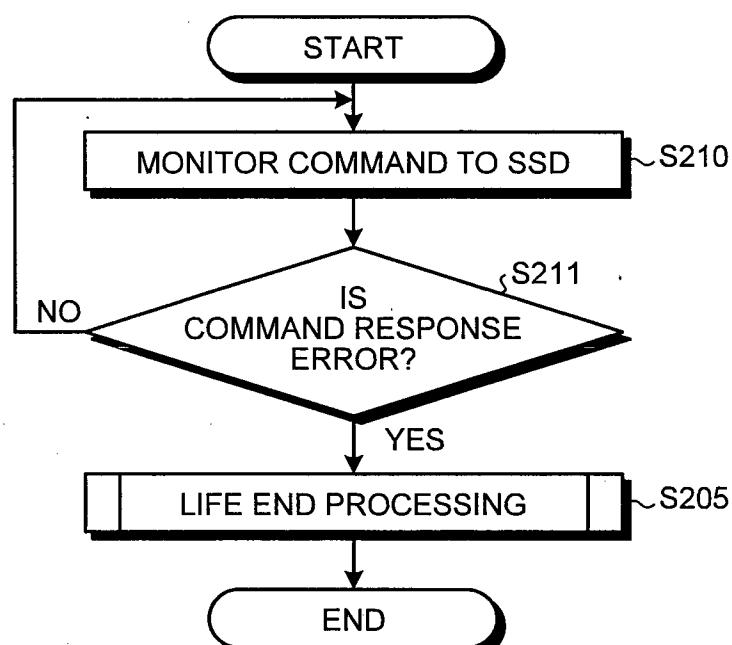

10 Fig. 29 is a flowchart for explaining an error command response handling process;

Fig. 30 is a flowchart for explaining another error command response handling process;

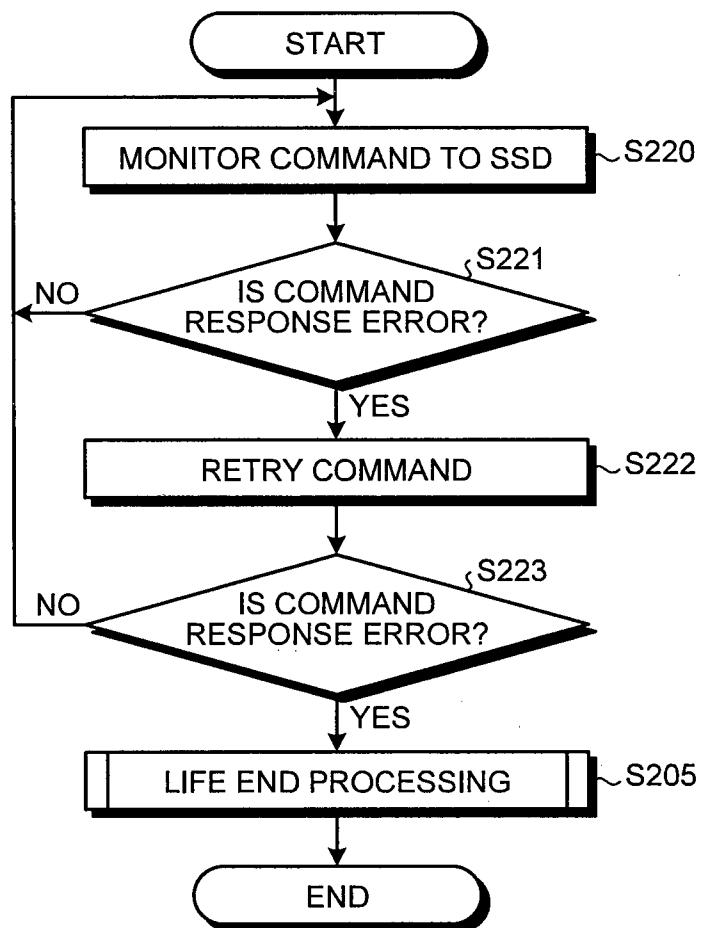

15 Fig. 31 is a diagram of a configuration example of data managed by an information processing device before life end processing is performed;

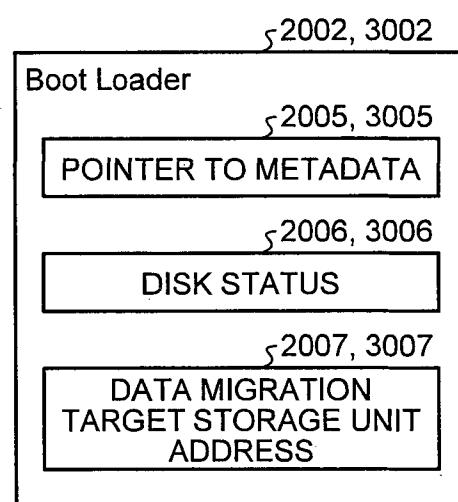

Fig. 32 is a diagram of internal data of a Boot Loader;

20 Fig. 33 is a diagram of a configuration example of metadata;

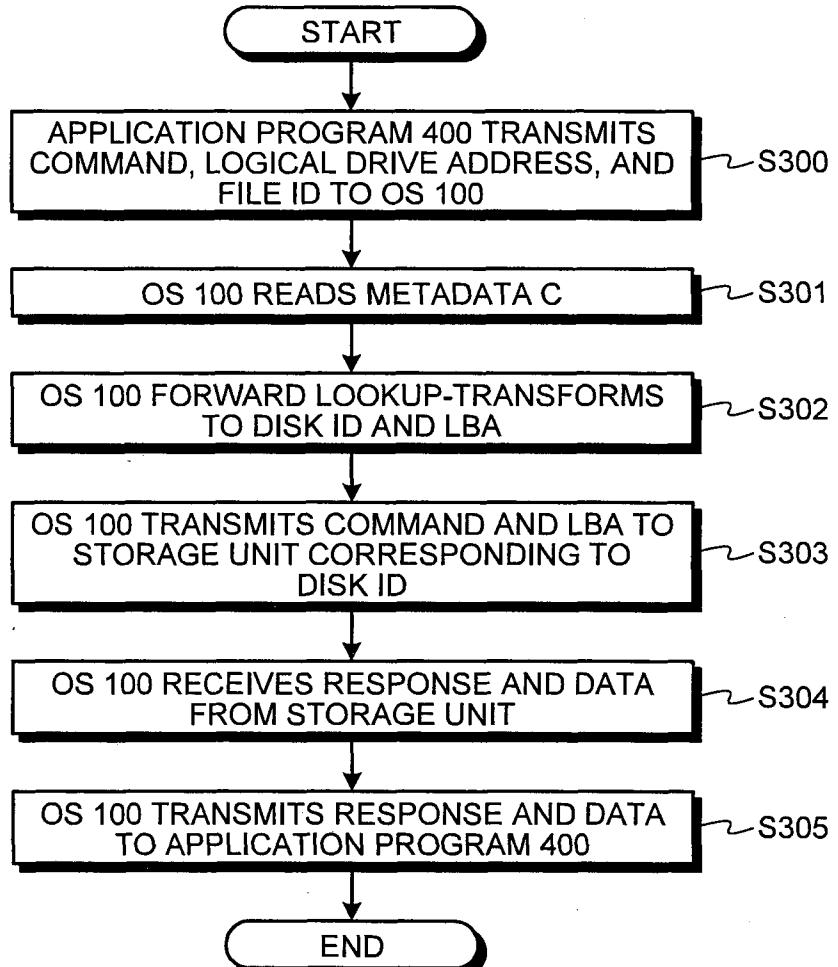

Fig. 34 is a flowchart of a procedure performed when an application program transmits an access request to a logical drive to an OS;

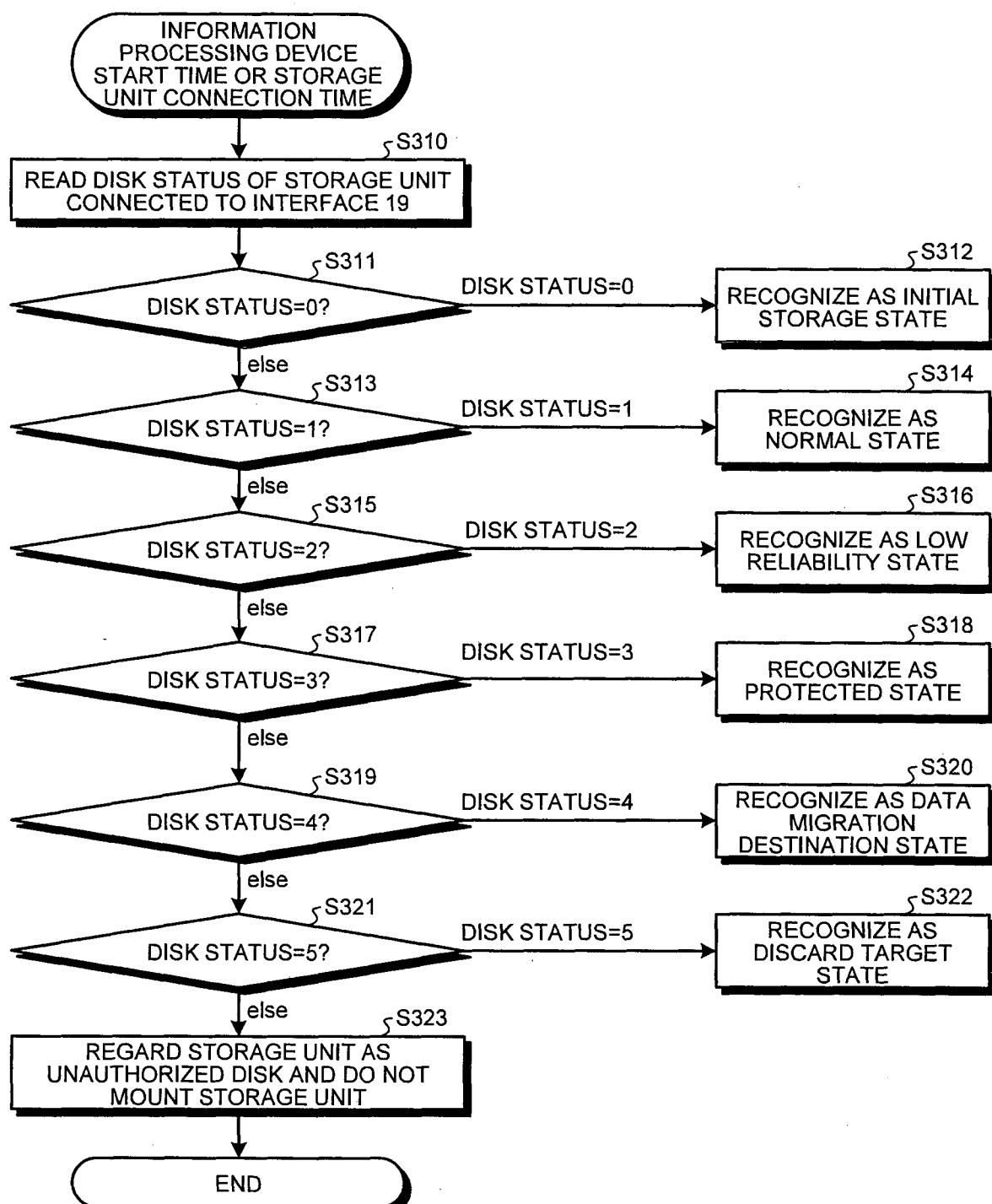

25 Fig. 35 is a flowchart for explaining a processing procedure of a control program performed when, for example, the information processing device starts;

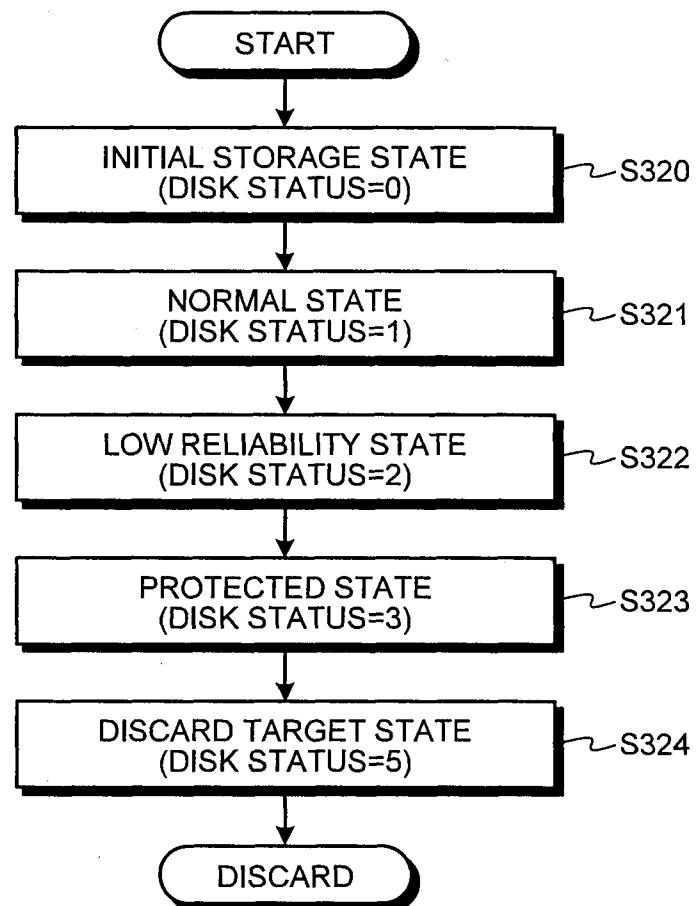

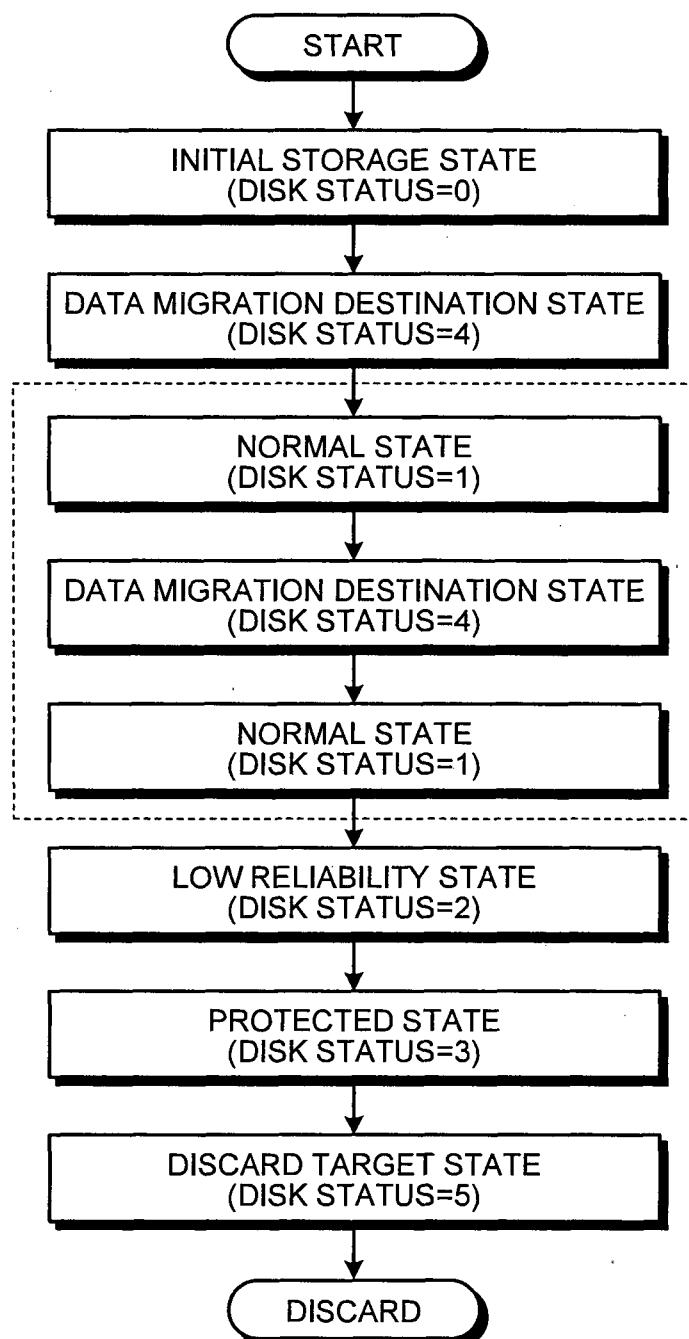

Fig. 36 is a state transition chart for explaining a life cycle of a storage unit;

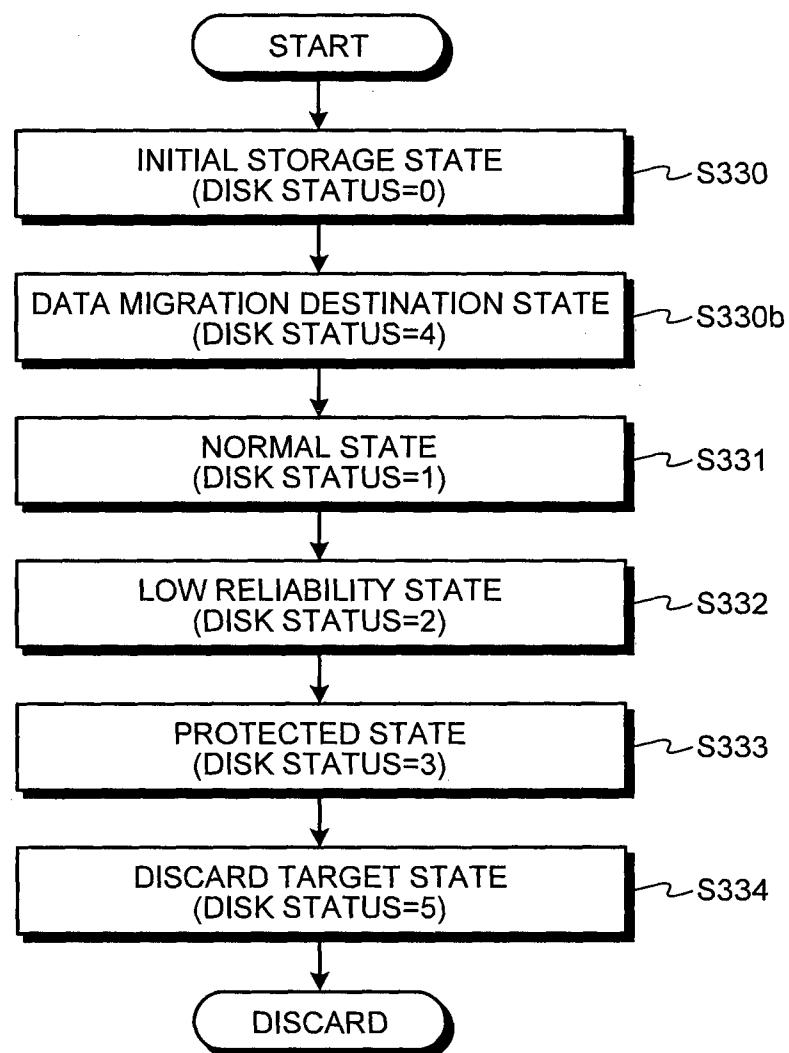

30 Fig. 37 is a state transition chart for explaining a life cycle of the storage unit;

Fig. 38 is a diagram of a configuration example of data managed by the information processing device in a state in which a data migration source storage unit and a

data migration destination storage unit are connected;

Fig. 39 is a state transition chart of a life cycle of the storage unit;

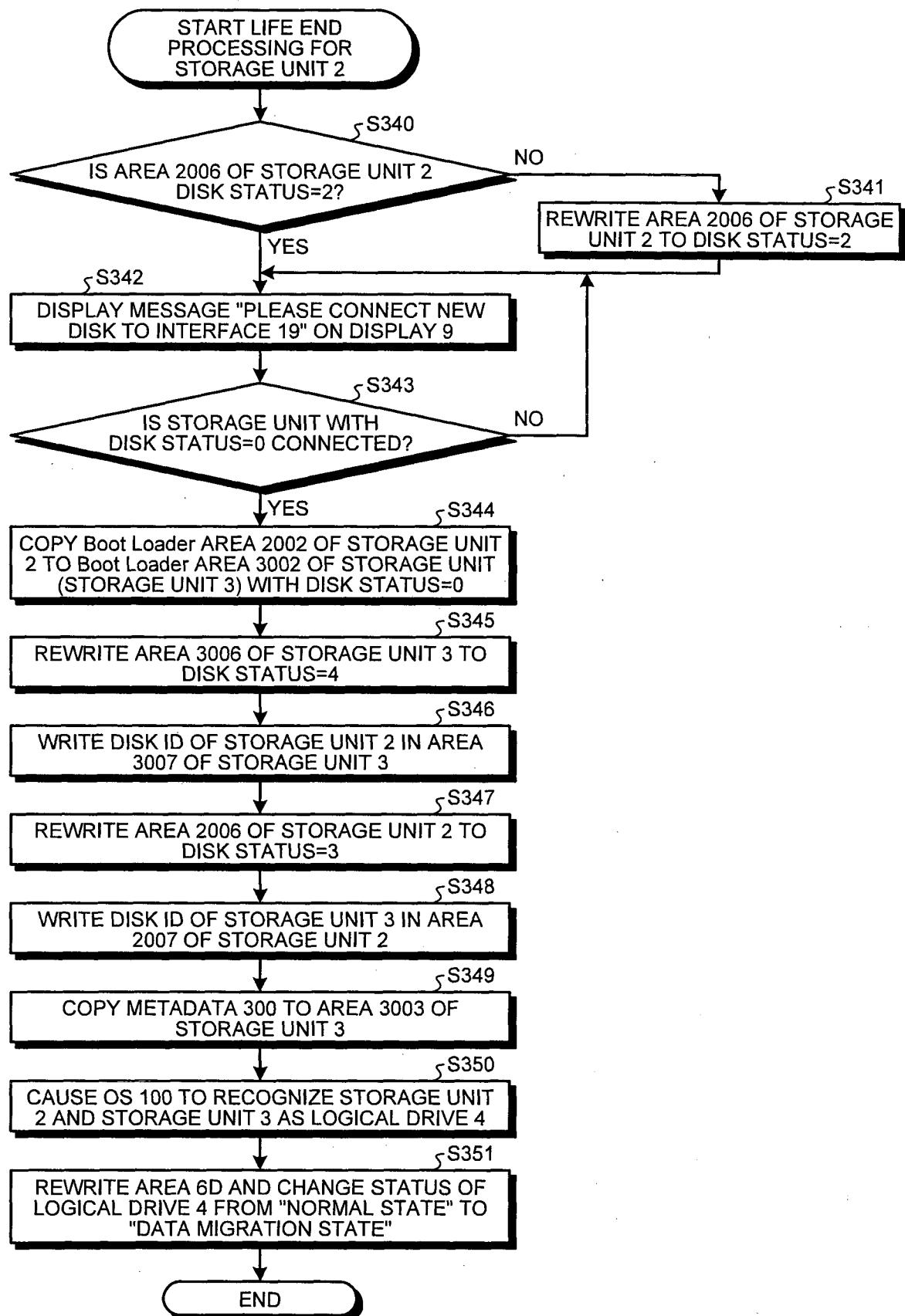

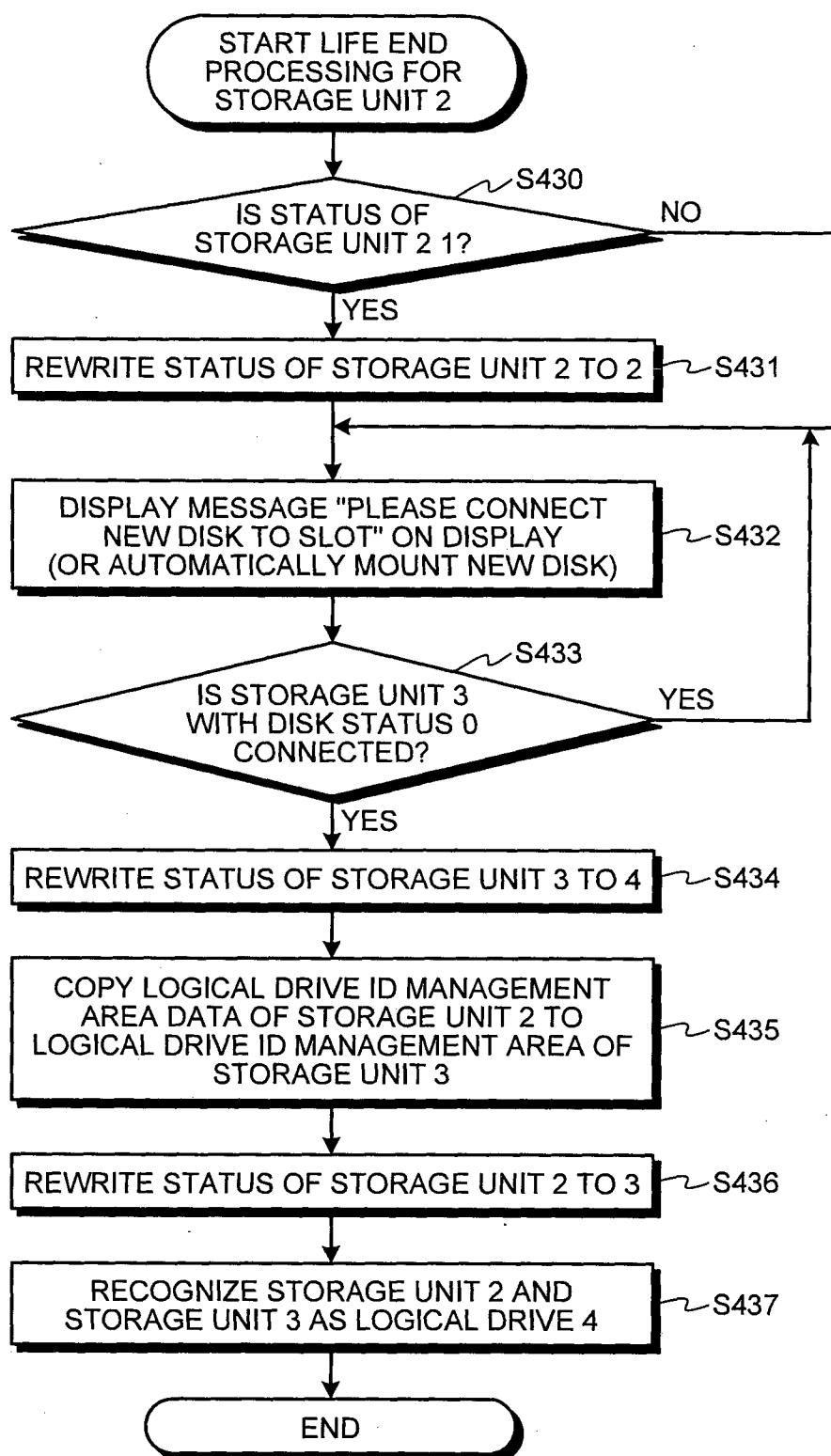

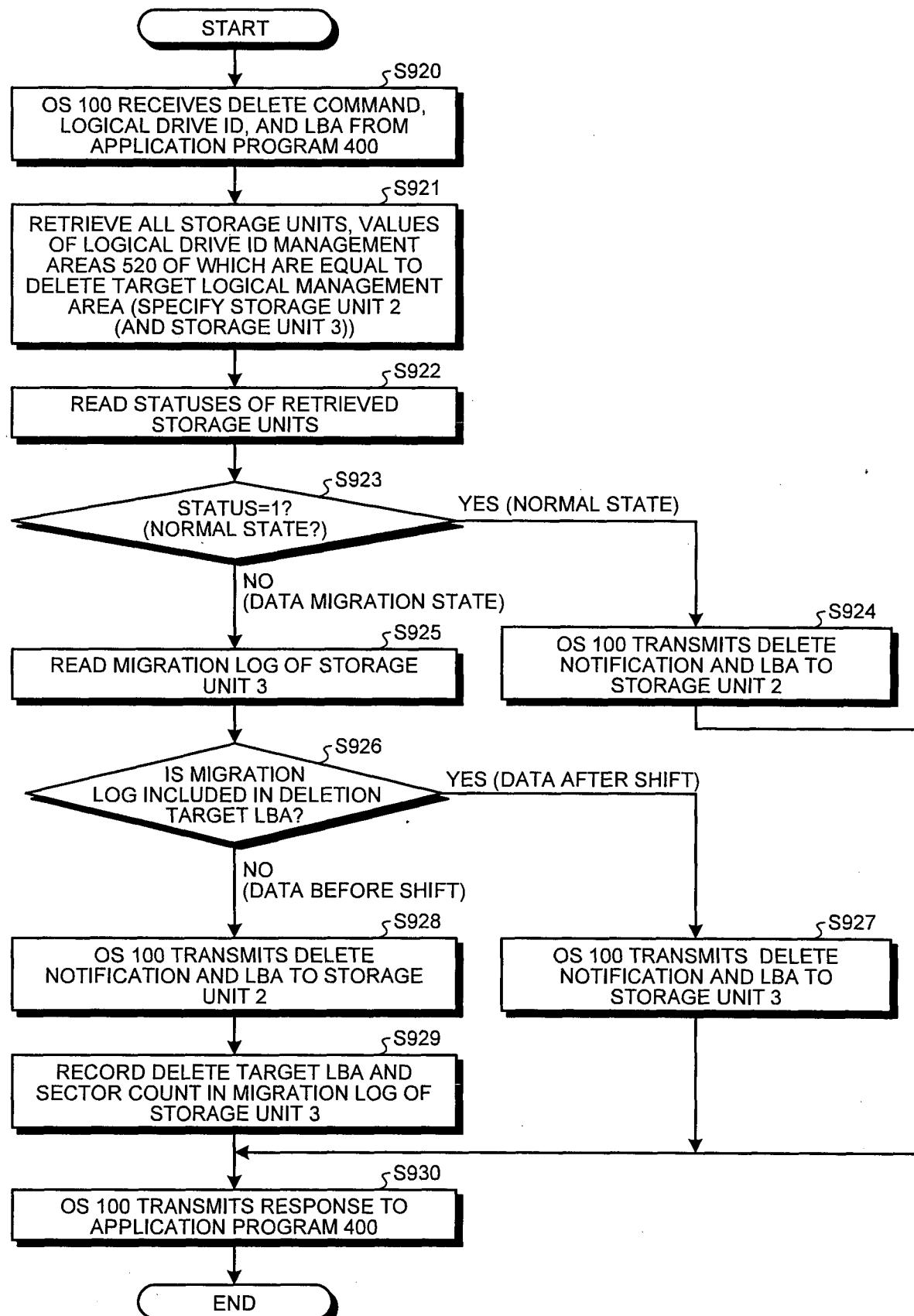

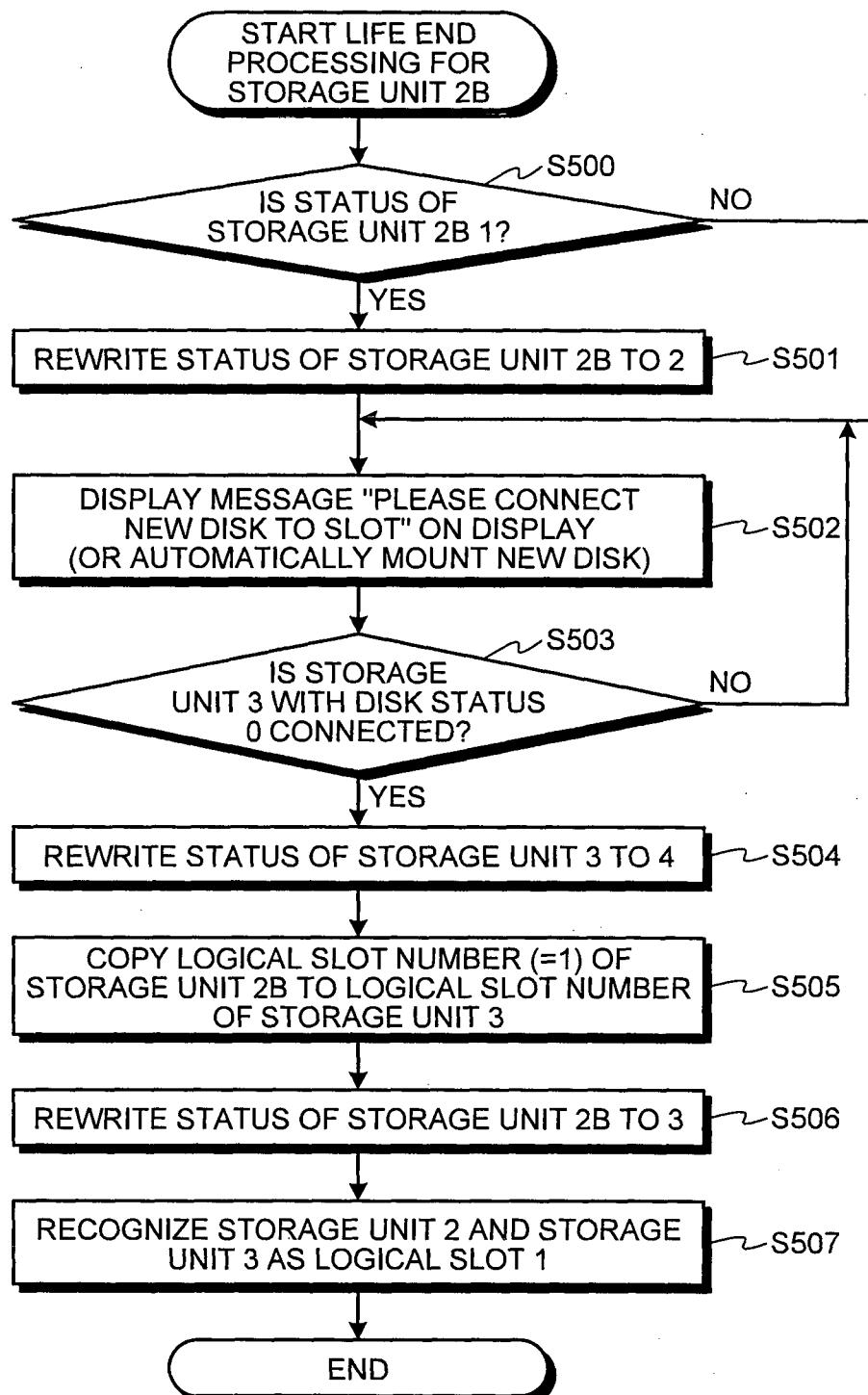

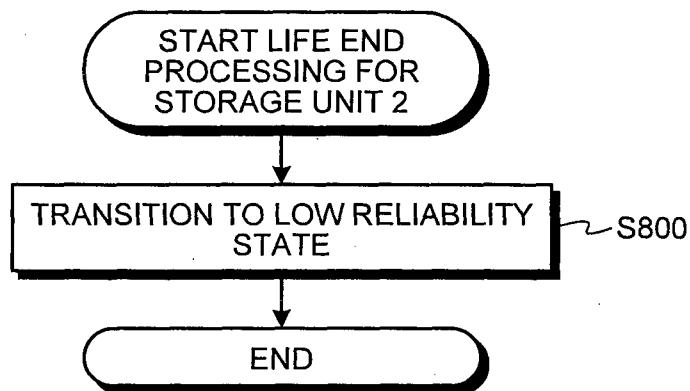

5 Fig. 40 is a flowchart for explaining processing performed by the control program in the life end processing;

Fig. 41 is a diagram of a logical drive status table;

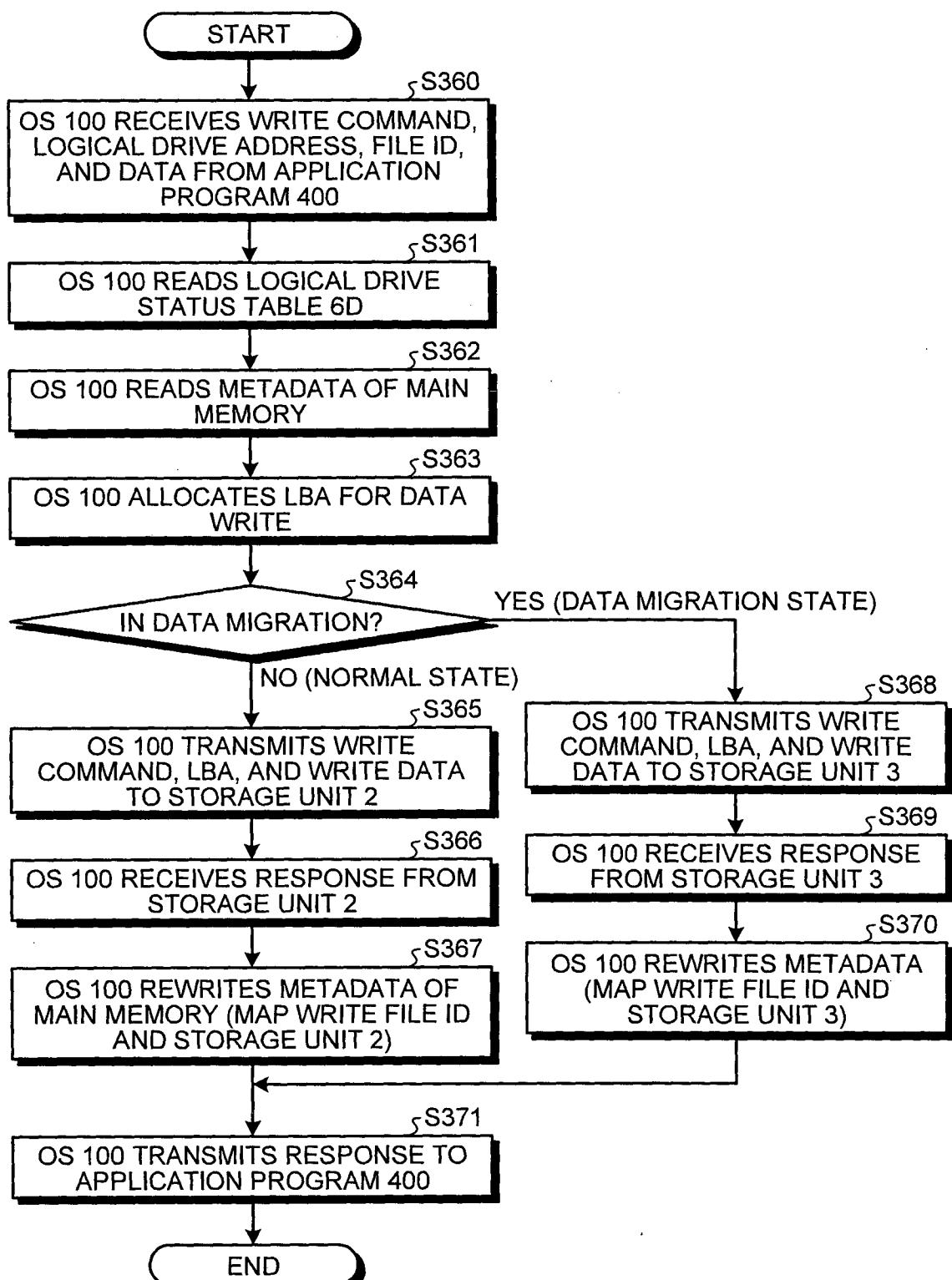

10 Fig. 42 is a flowchart for explaining a processing procedure of the OS performed when a write request is transmitted from the application program to the OS;

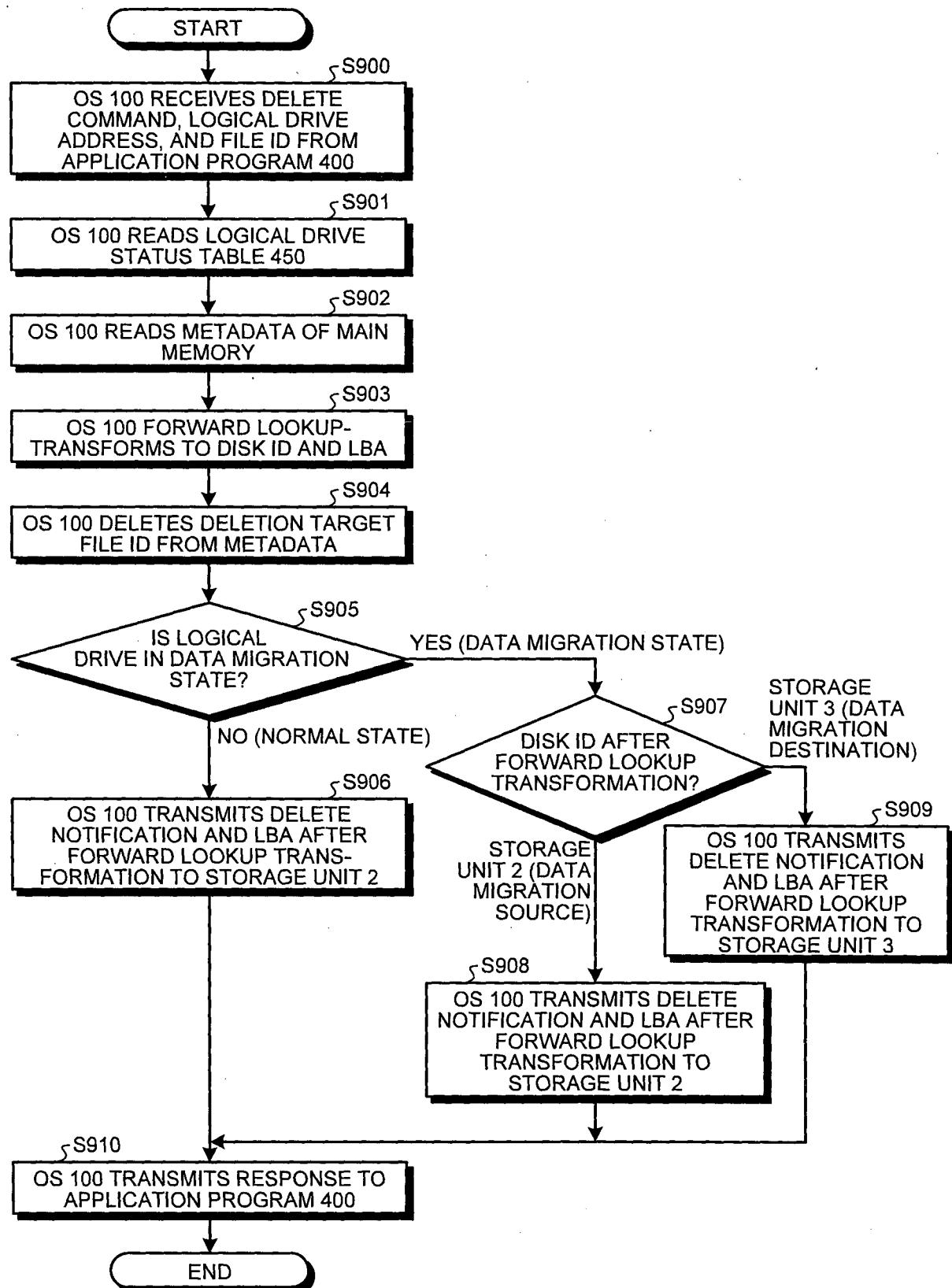

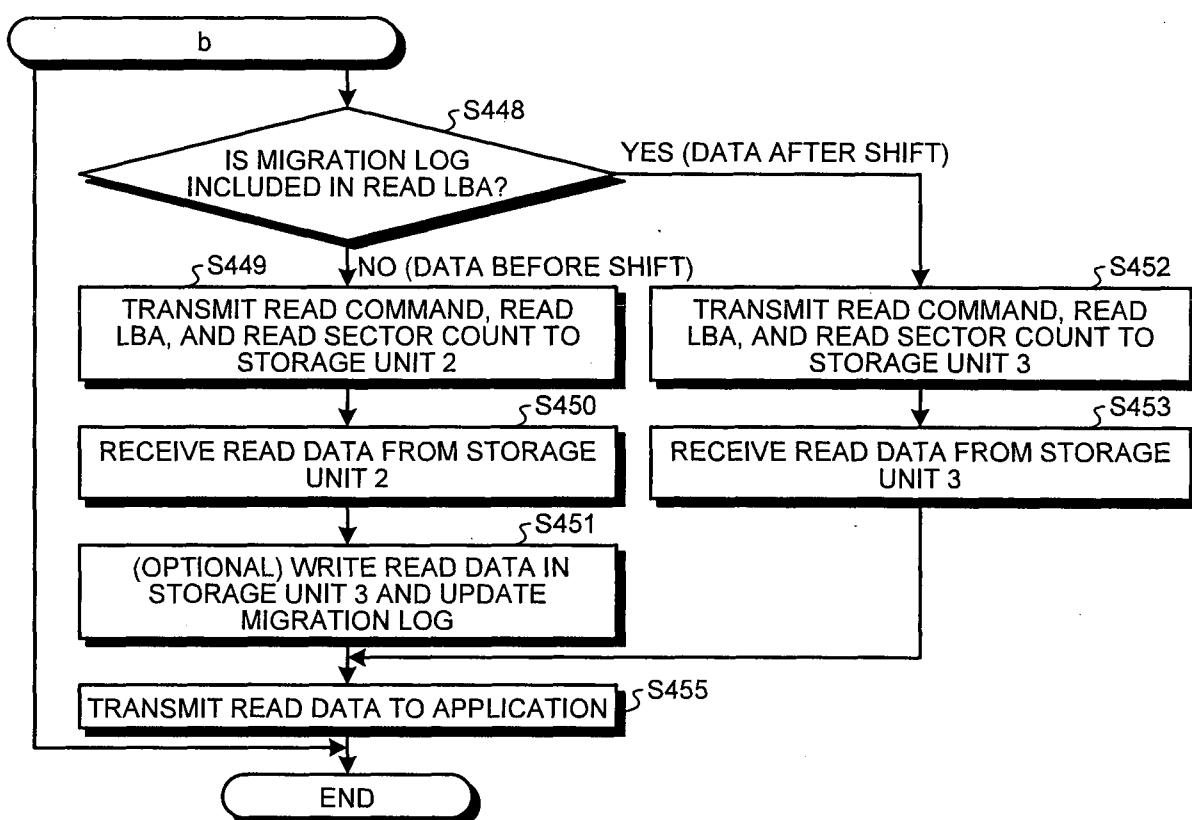

Fig. 43 is a flowchart for explaining a processing procedure of the OS performed when a delete request is transmitted from the application program to the OS;

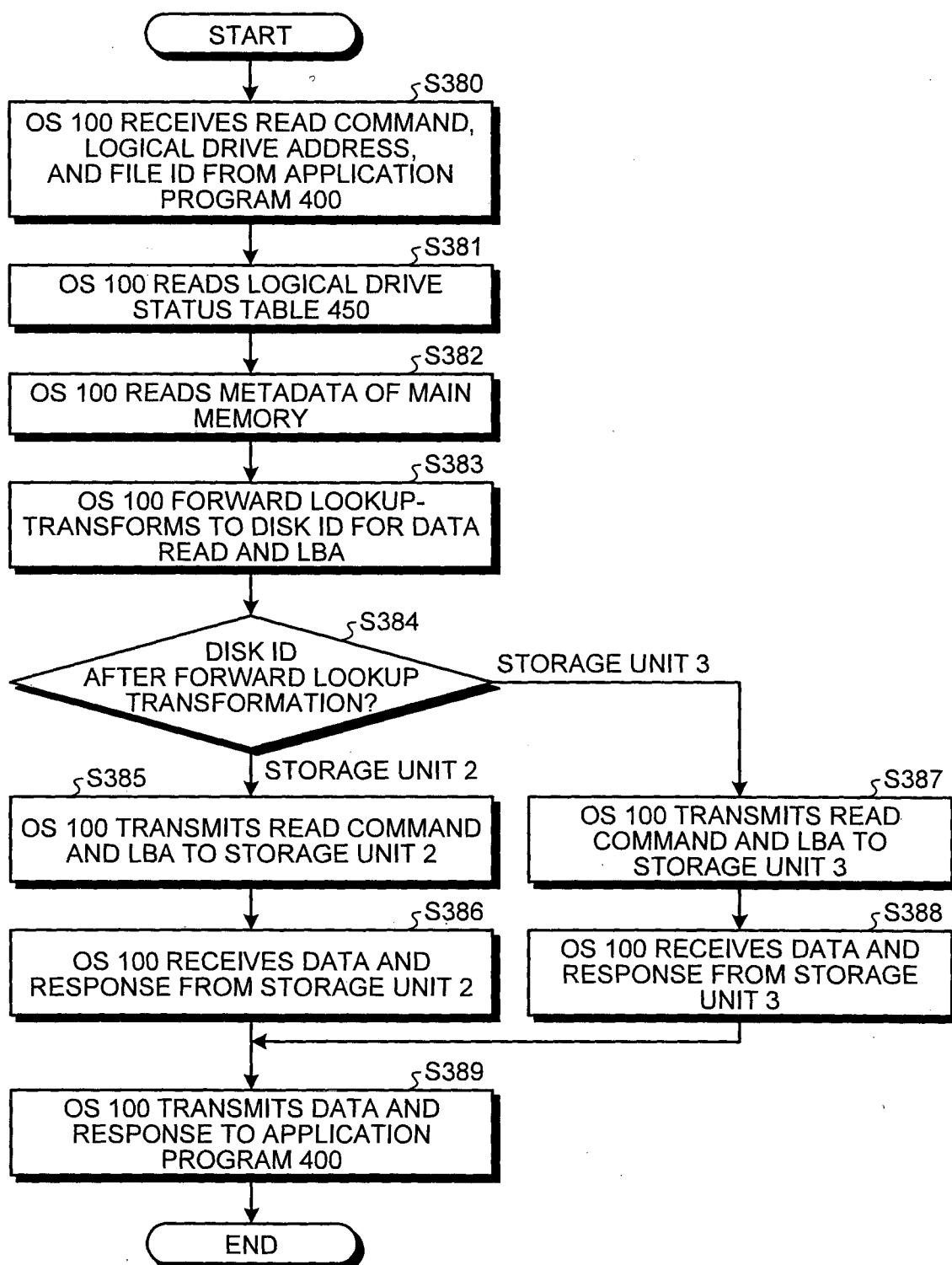

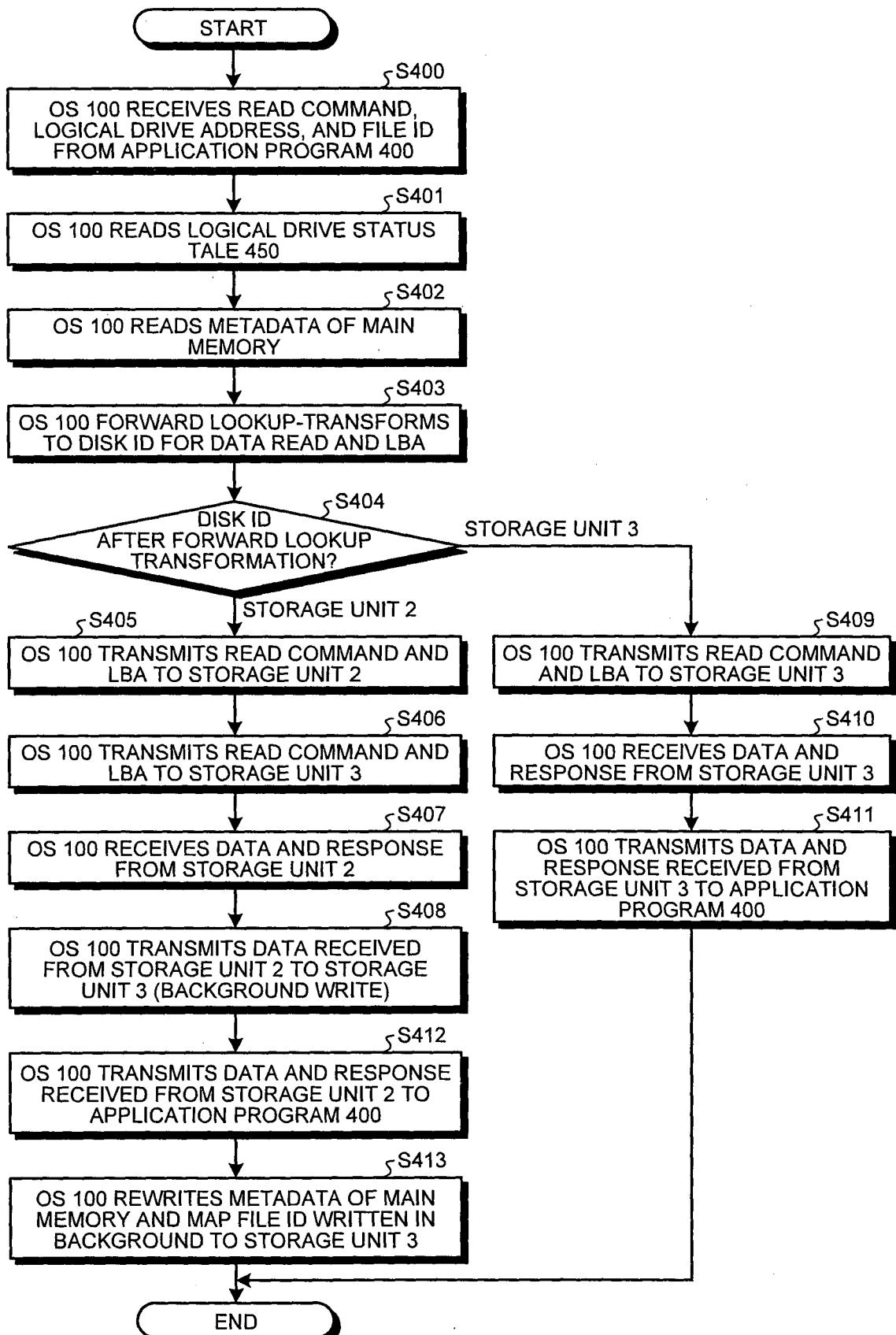

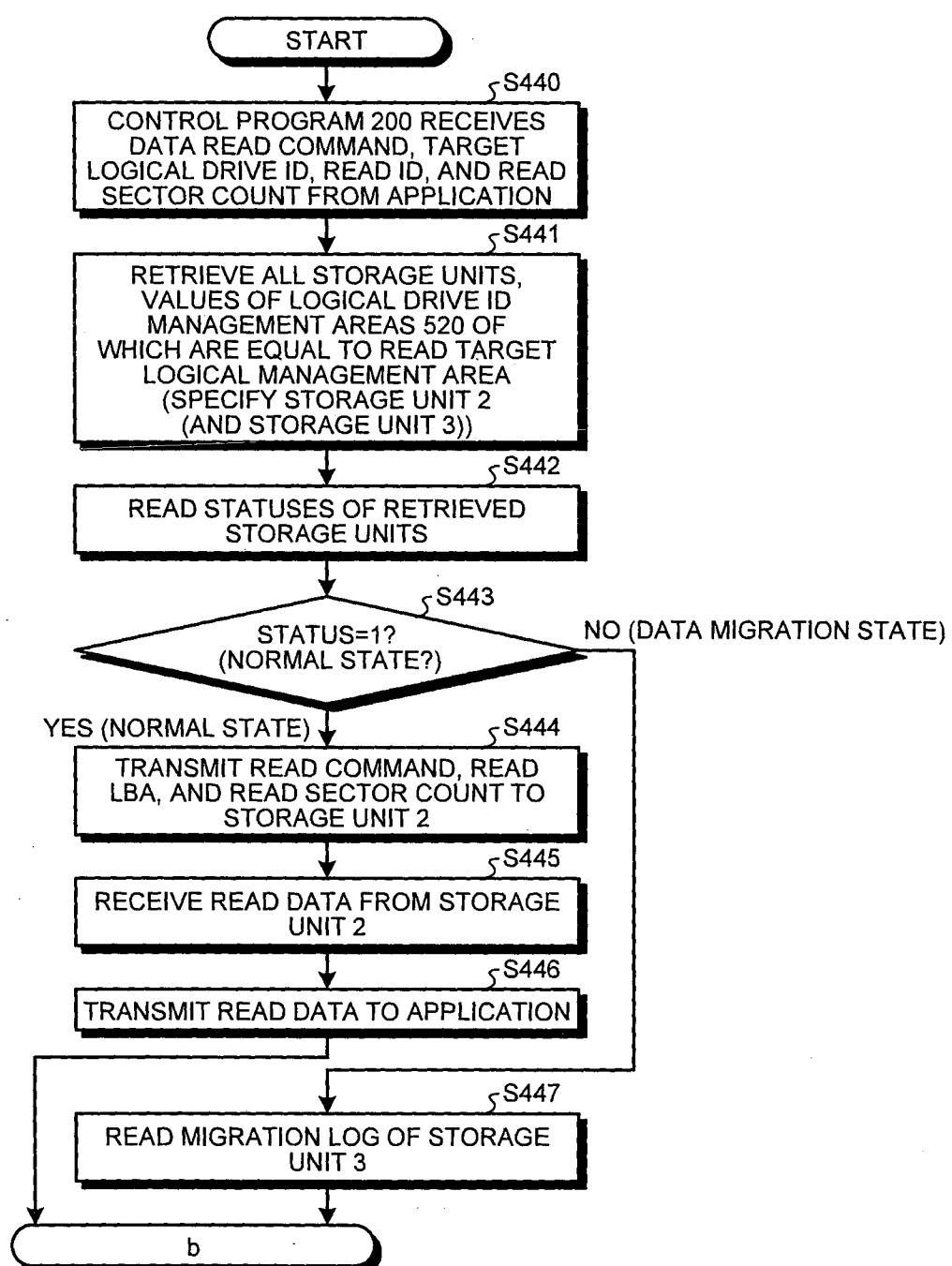

15 Fig. 44 is a flowchart for explaining a processing procedure of the OS performed when a read request is transmitted from the application program to the OS;

Fig. 45 is a flowchart for explaining a processing procedure of background backup;

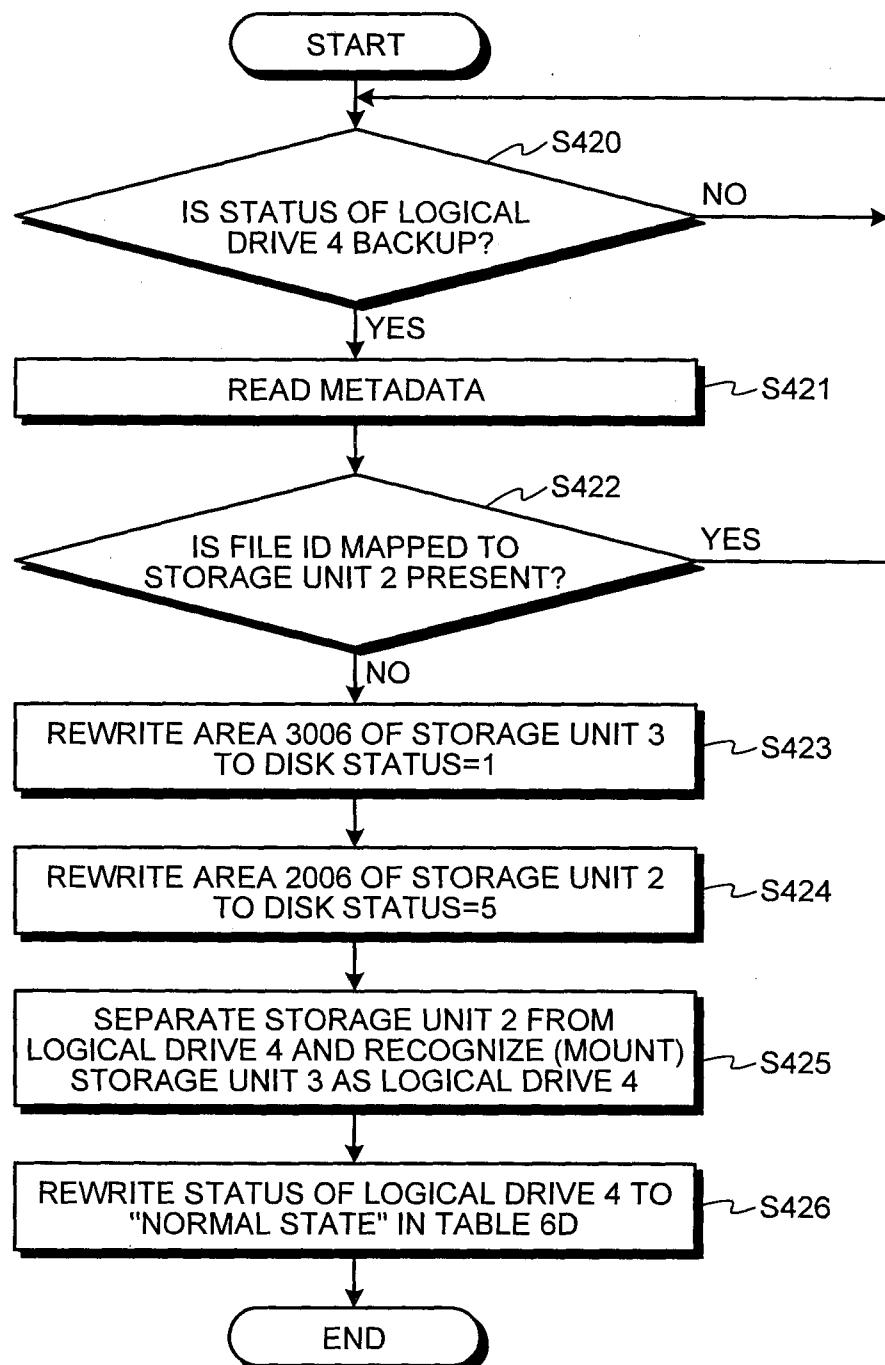

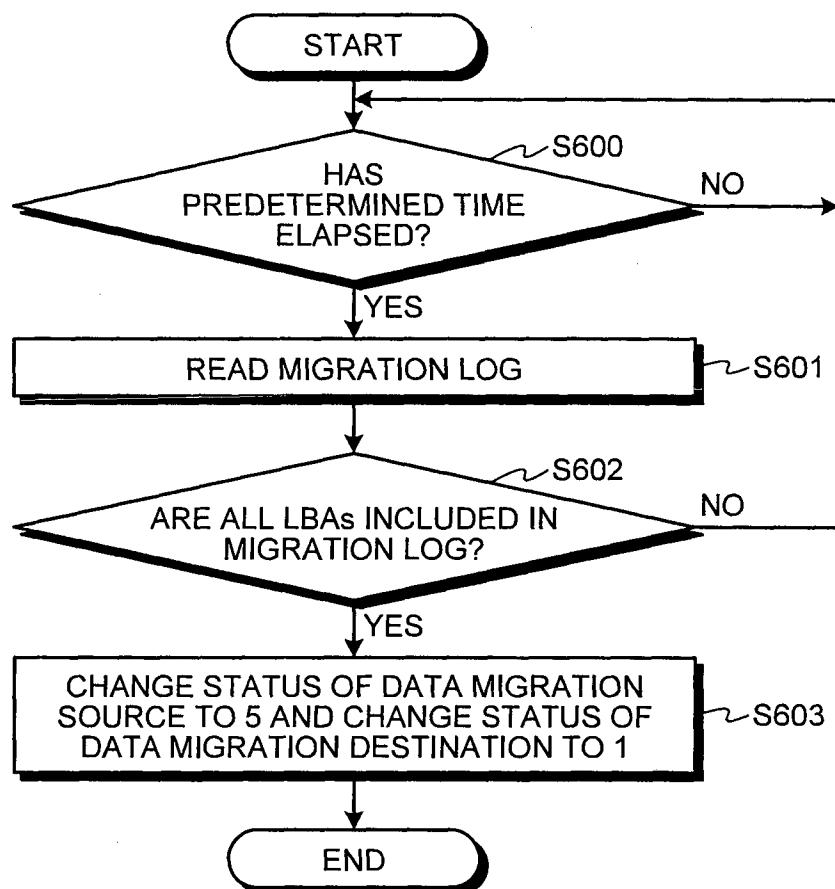

20 Fig. 46 is a flowchart for explaining an operation procedure of the control program performed when data migration is completed;

Fig. 47 is a conceptual diagram of read from a logical drive in a data migrating state;

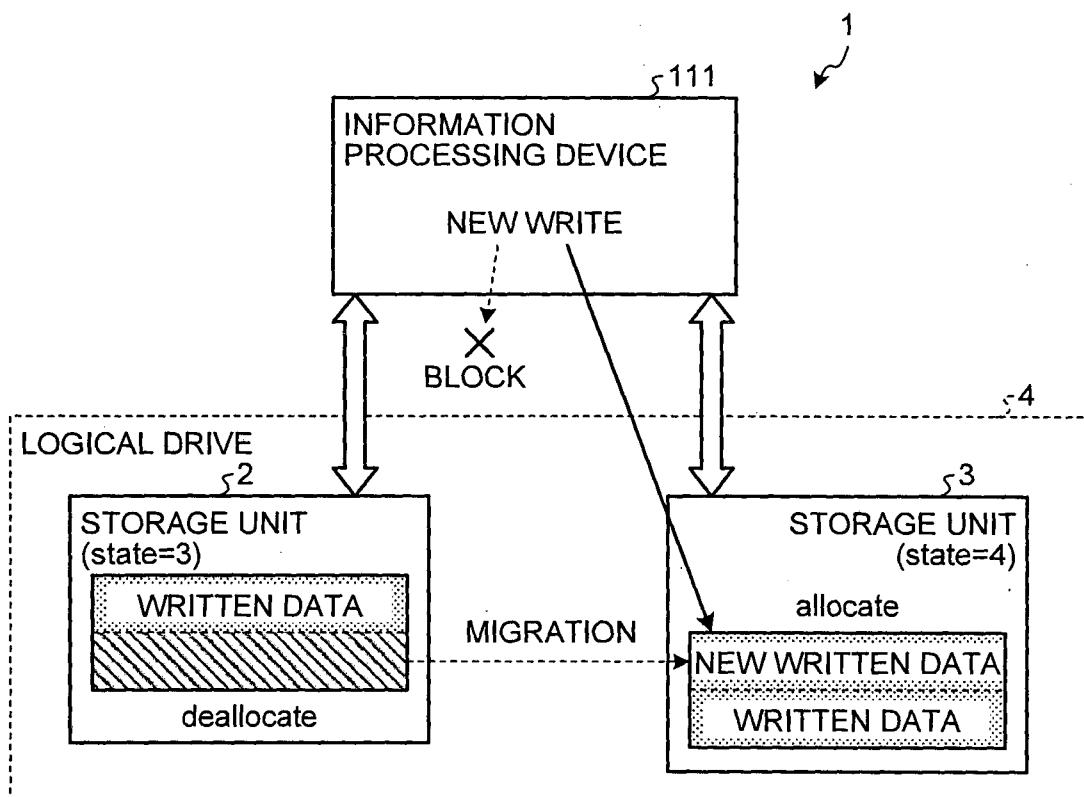

25 Fig. 48 is a conceptual diagram of write in the logical drive in the data migrating state;

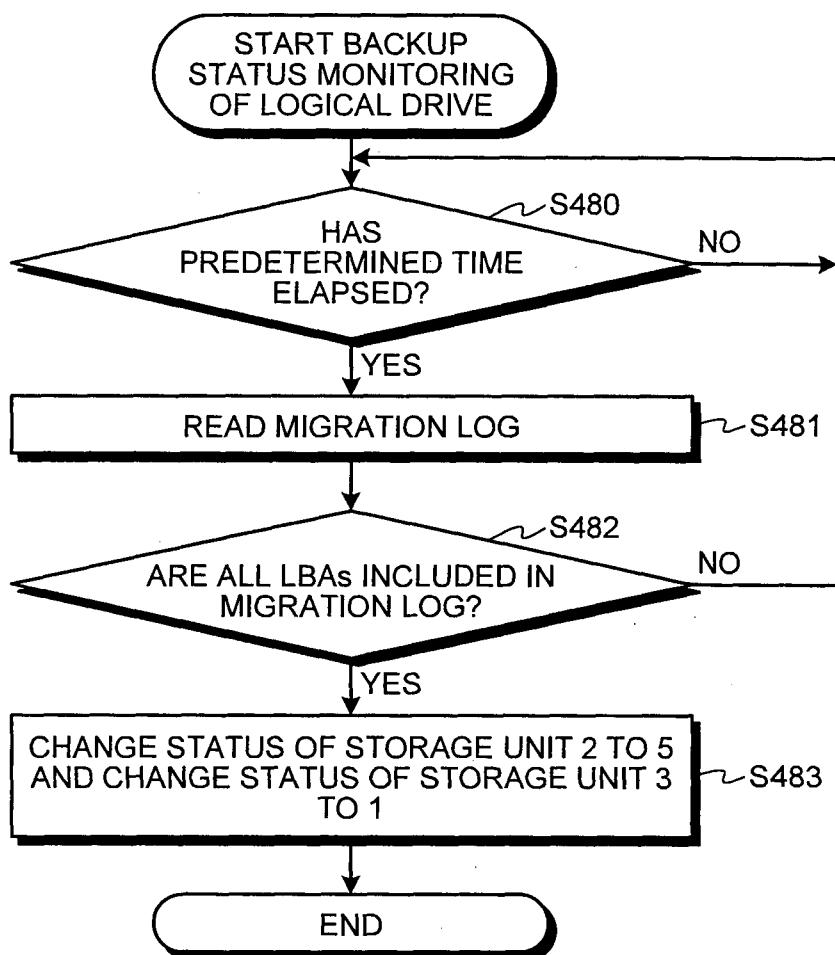

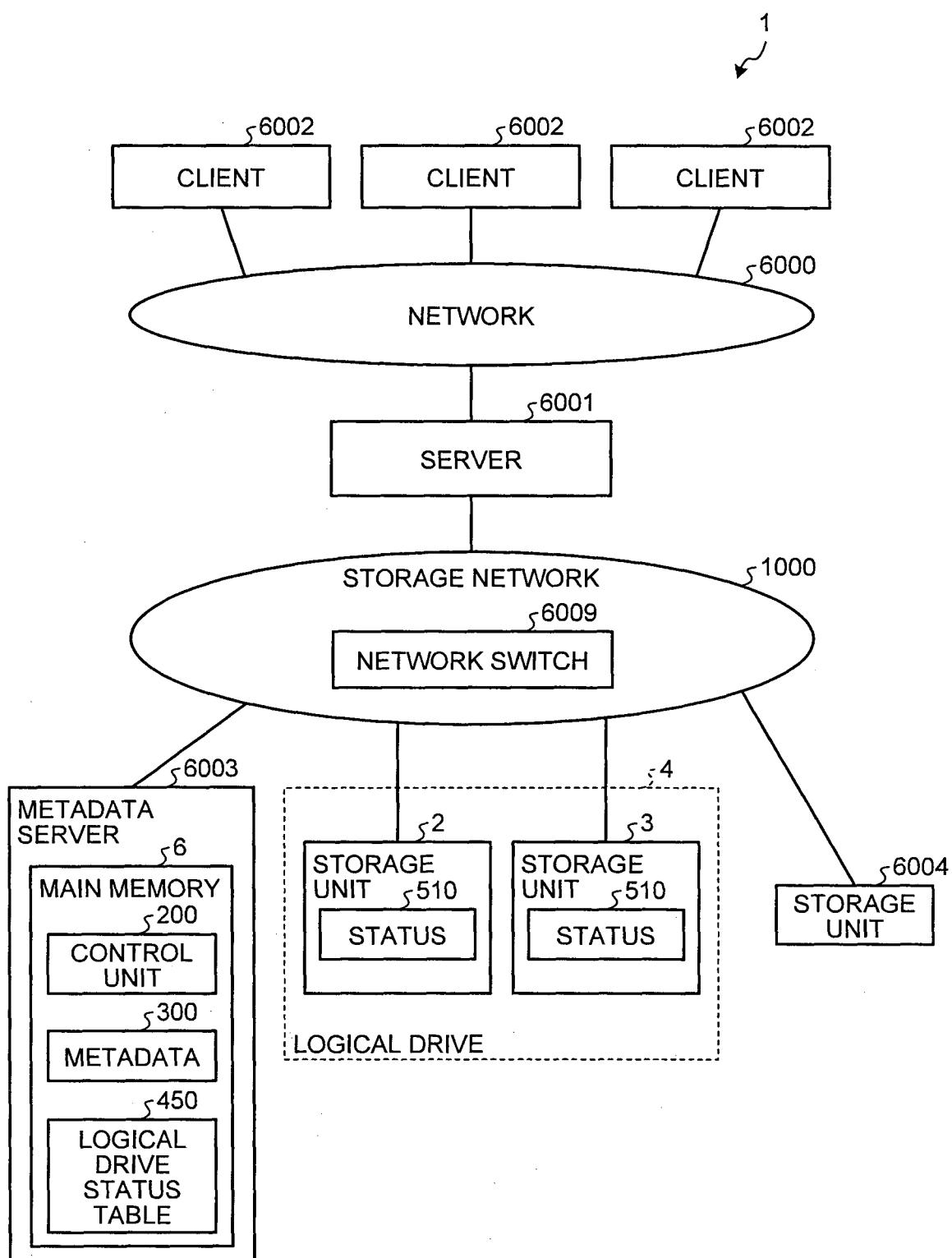

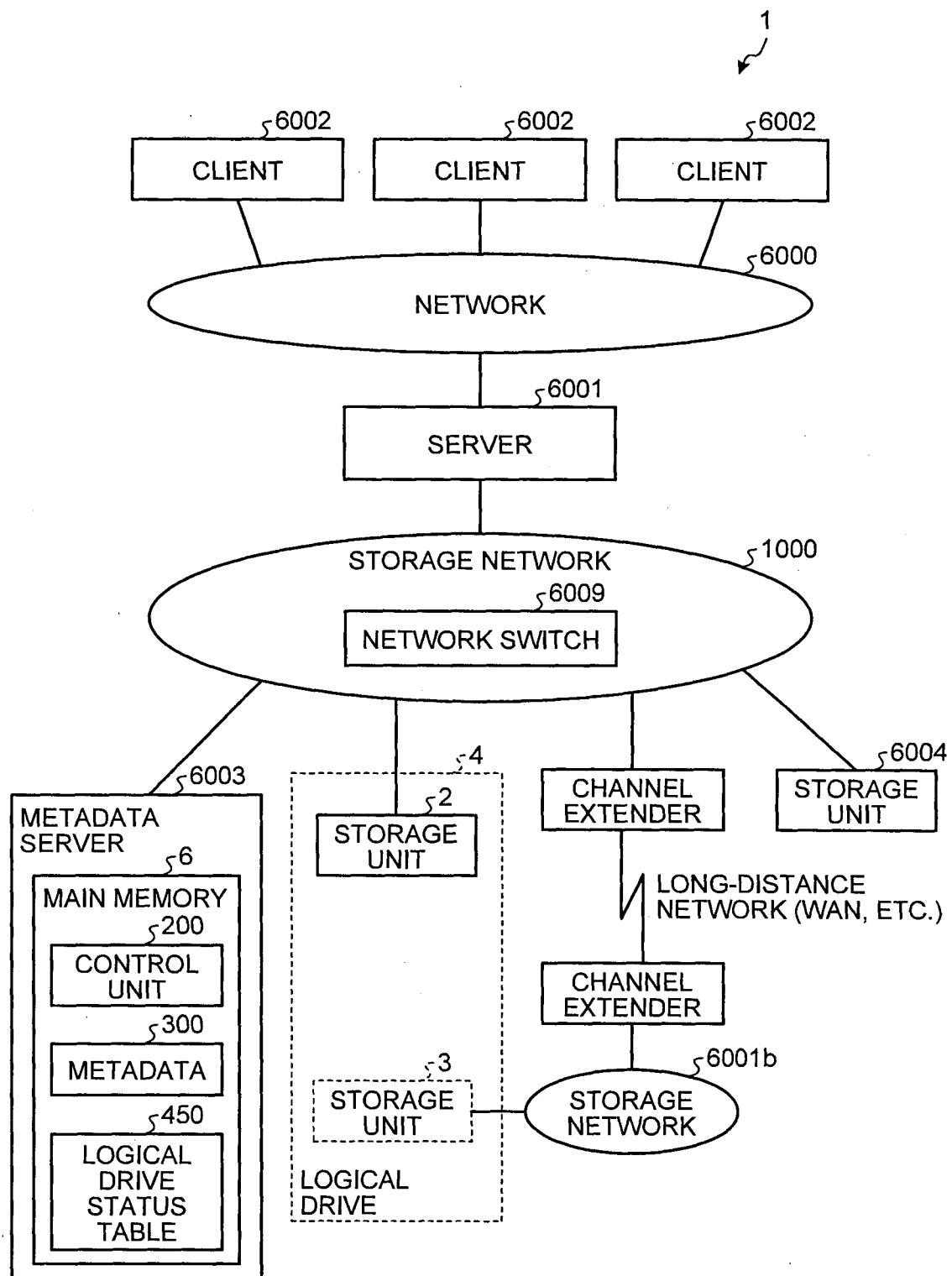

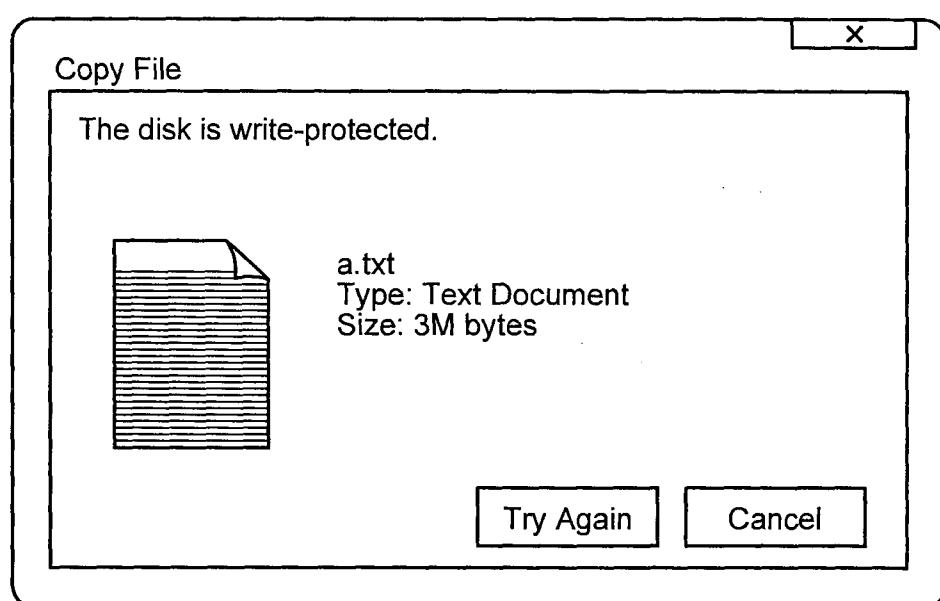

Fig. 49 is a block diagram of a functional configuration example of an information processing system in a second embodiment;

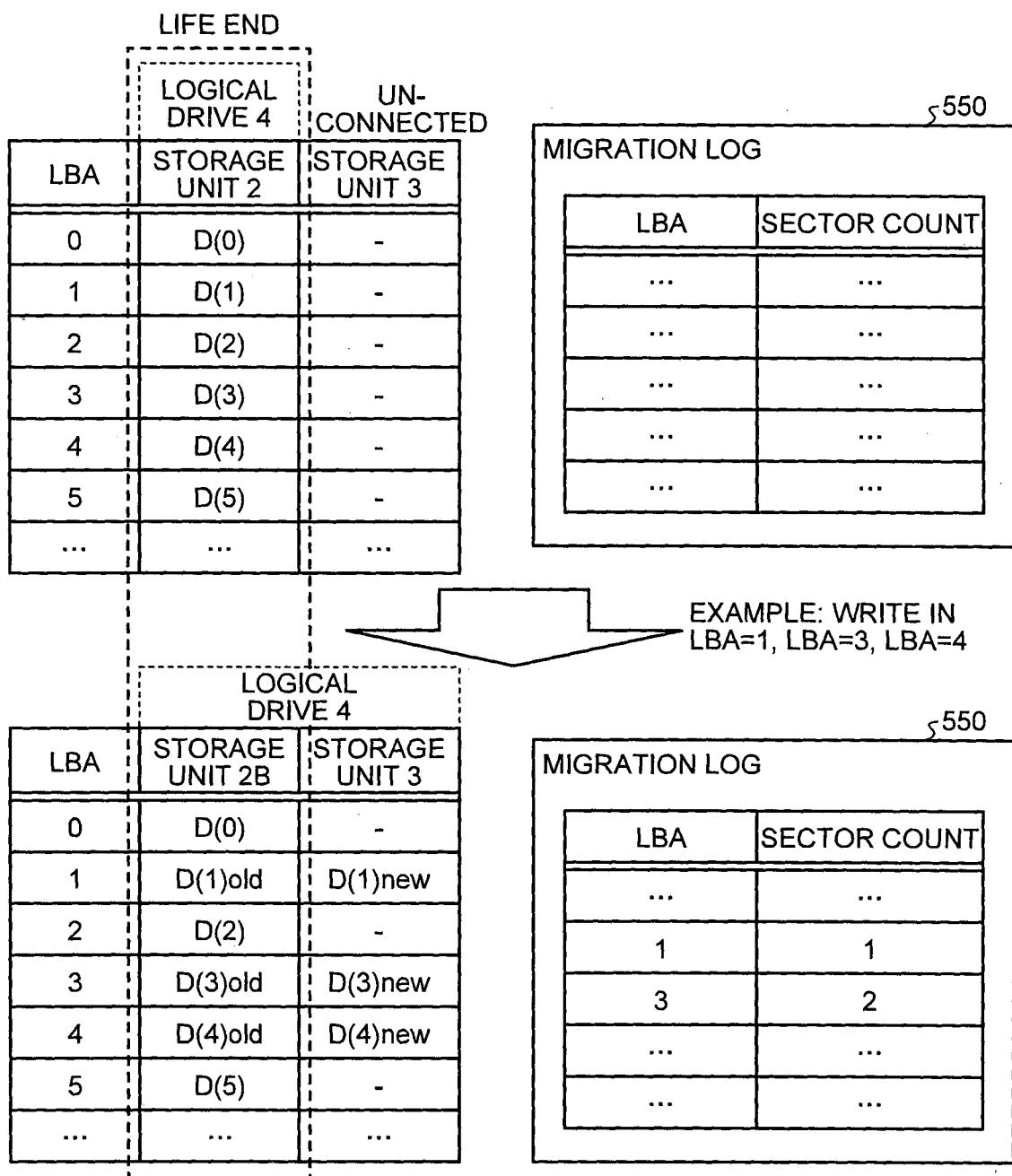

Fig. 50 is a diagram of a data migration log;

30 Fig. 51 is a diagram of a write example of a log in the data migration log;

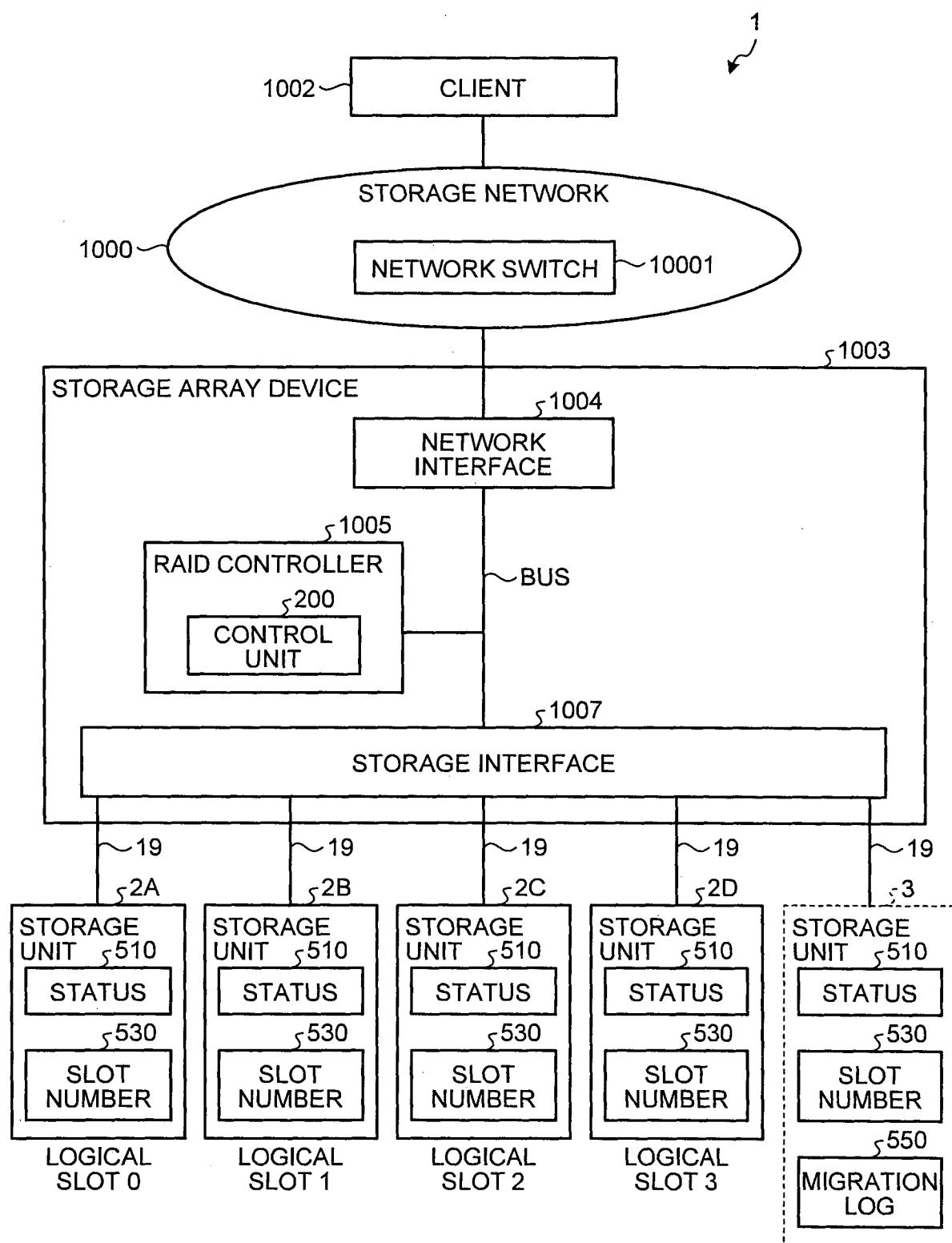

Fig. 52 is a flowchart for explaining life end processing;

Fig. 53A and Fig. 53B are flowchart for explaining an operation procedure of read from a logical drive;

Fig. 54 is a flowchart for explaining a processing procedure of an OS performed when an LBA data delete

5 request is transmitted from an application program to the OS;

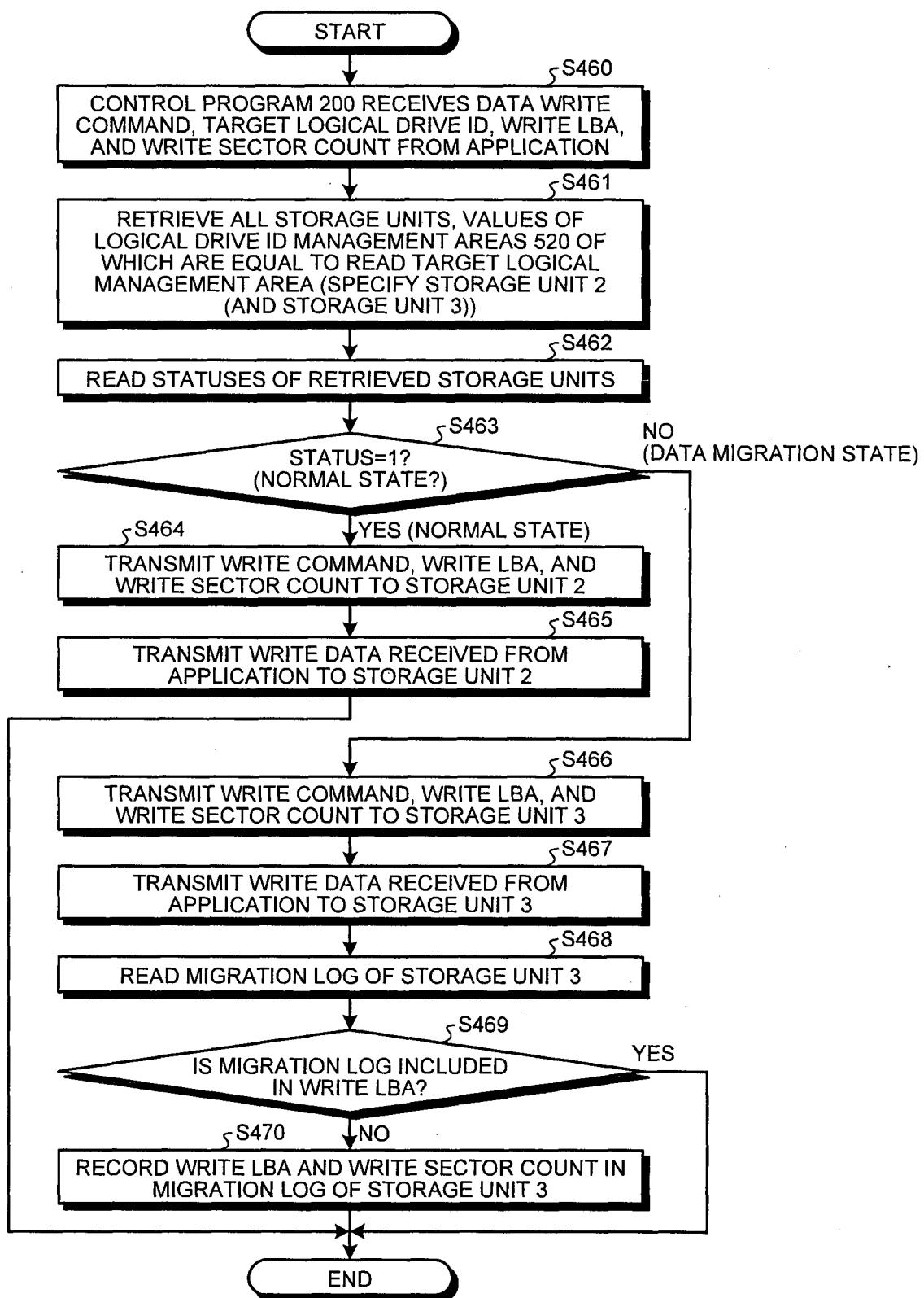

Fig. 55 is a flowchart for explaining an operation procedure of write in the logical drive;

Fig. 56 is a flowchart for explaining a monitoring procedure of a data migrating state performed using the data migration log;

Fig. 57 is a diagram of transition of states of the logical drive that takes places when a storage unit has reached the life end;

15 Fig. 58 is a block diagram of a functional configuration example of an information processing system in a third embodiment;

Fig. 59 is a diagram for explaining a transformation method for an array LBA (ALBA) and a storage unit LBA

20 (SLBA) in a normal state;

Fig. 60 is a diagram for explaining a transformation method for the array LBA (ALBA) and the storage unit LBA (SLBA) immediately after migration state transition;

Fig. 61 is a diagram of a data migration log;

25 Fig. 62 is a flowchart for explaining life end processing;

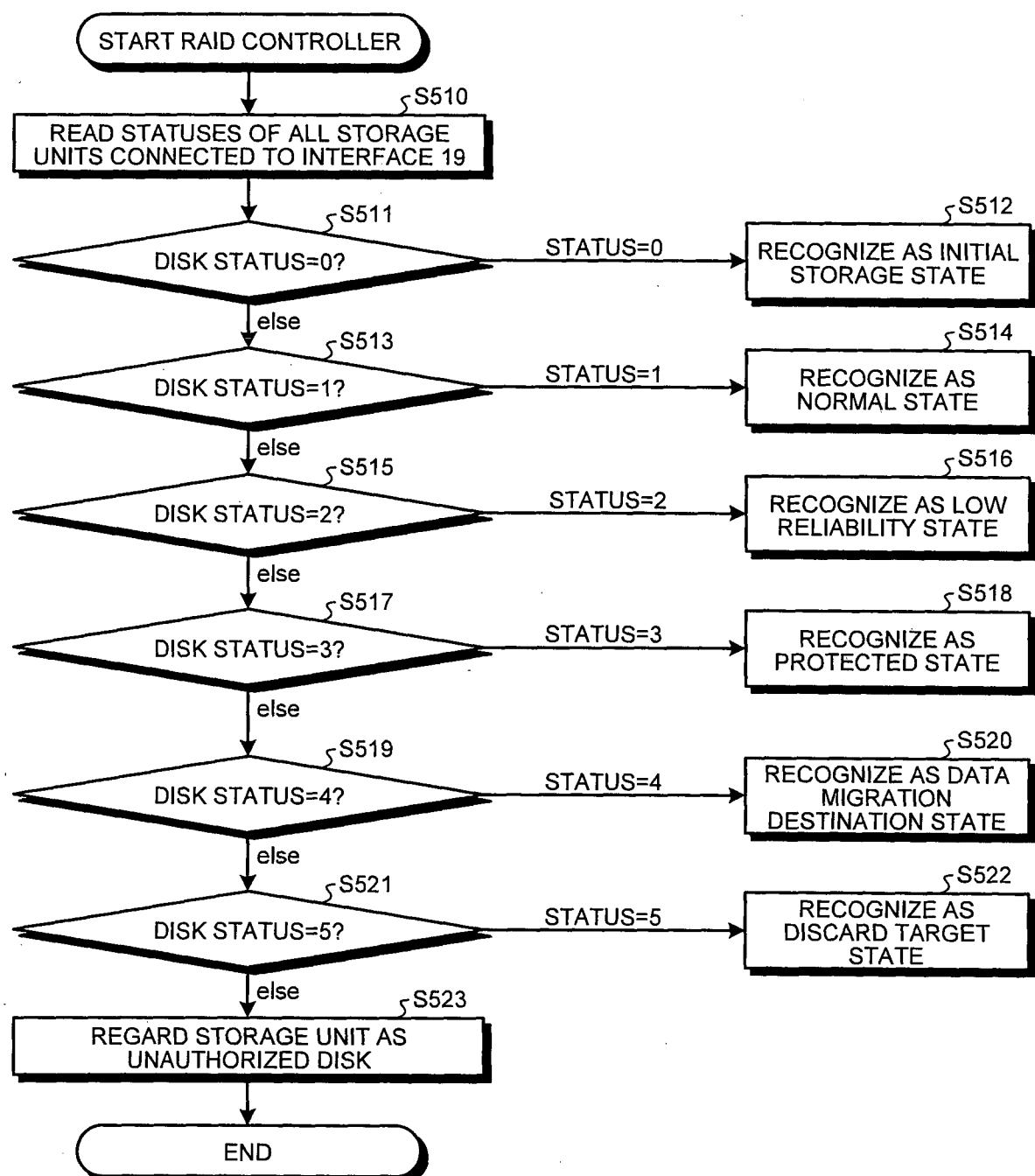

Fig. 63 is a flowchart for explaining a processing procedure of a control unit performed when, for example, a RAID controller starts;

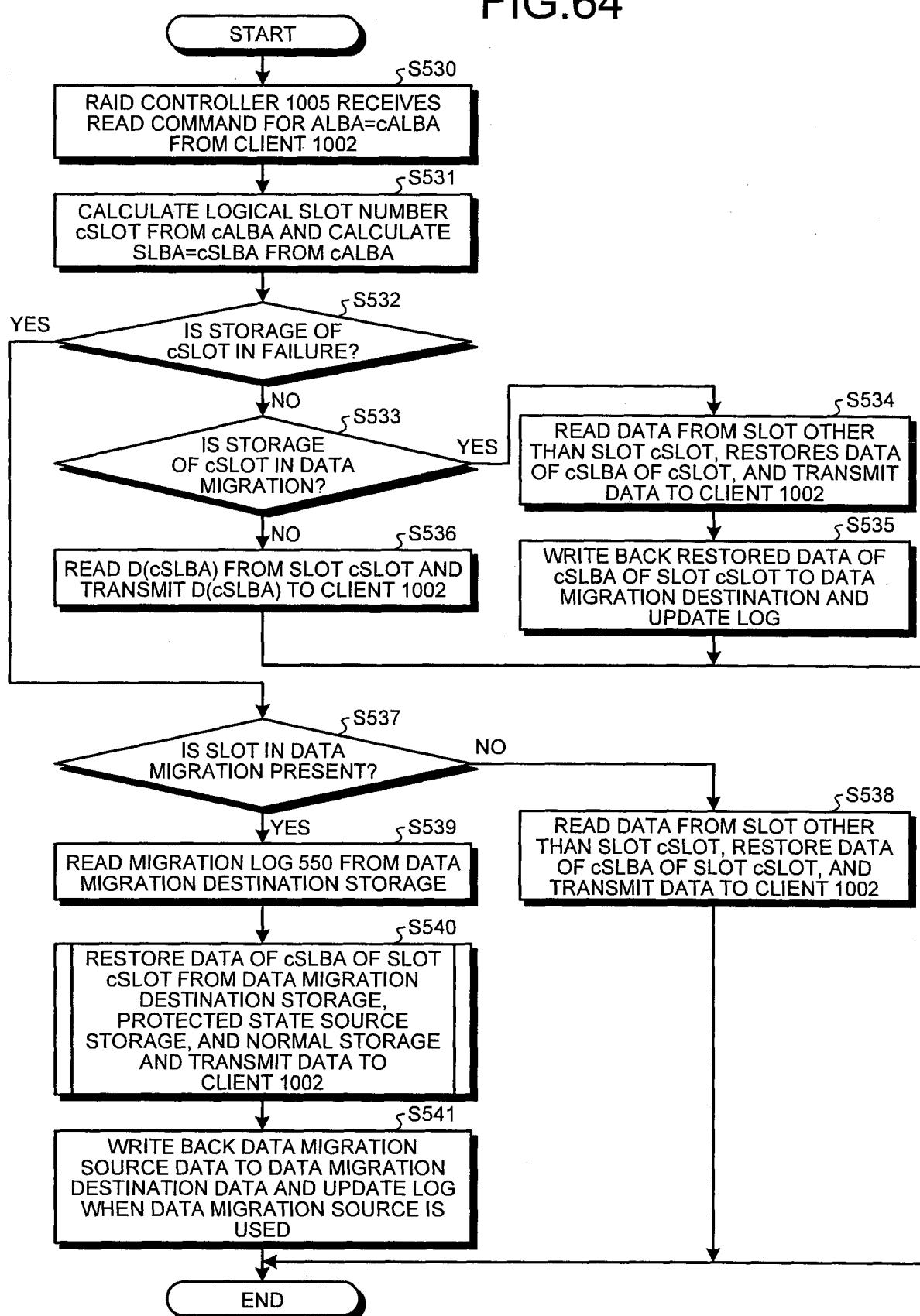

30 Fig. 64 is a flowchart for explaining a processing procedure of the RAID controller in executing a read request;

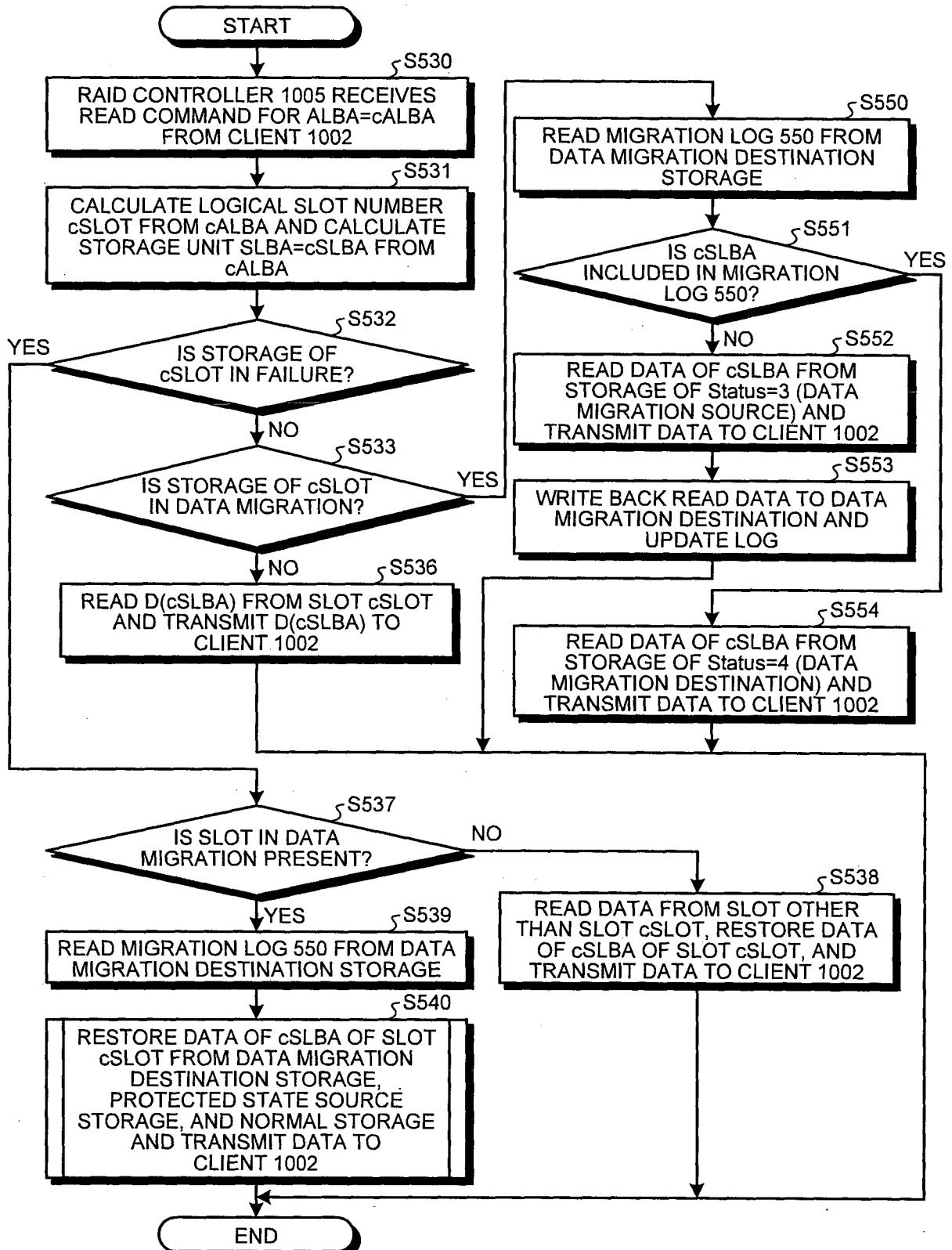

Fig. 65 is a flowchart for explaining another

processing procedure of the RAID controller in executing the read request;

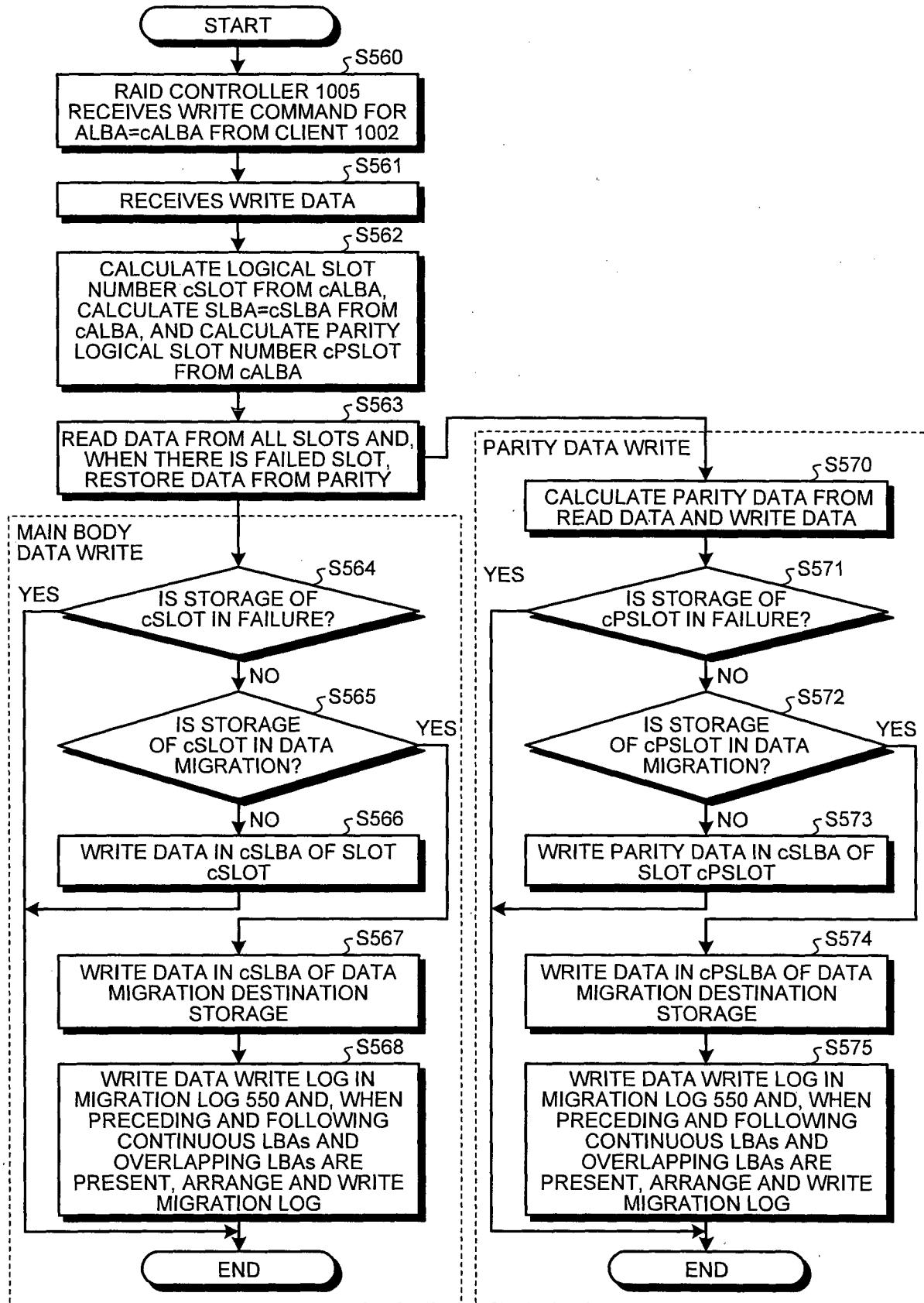

Fig. 66 is a flowchart for explaining a processing procedure of the RAID controller in executing a write

5 request;

Fig. 67 is a diagram of a specific example of write processing;

Fig. 68 is a flowchart for explaining a monitoring procedure for a data migrating state performed using the

10 data migration log;

Fig. 69 is a diagram of transition of statuses of storage units;

Fig. 70 is a diagram of an example in which a data migrating state of one storage unit and a failure of

15 another storage unit simultaneously occur;

Fig. 71 is a diagram of an example in which a data migrating state of two storage units and a failure of another storage unit simultaneously occur;

Fig. 72 is a diagram of an example in which, in a data

20 migrating state of one storage unit, an uncorrectable ECC error occurs in another storage unit;

Fig. 73 is a block diagram of a functional configuration example of an information processing system in a fourth embodiment;

25 Fig. 74 is a block diagram of another functional configuration example of the information processing system in the fourth embodiment;

Fig. 75 is a diagram of a status table;

Fig. 76 is a block diagram of a functional

30 configuration example of an information processing system in a fifth embodiment;

Fig. 77 is a block diagram of a functional configuration example of an information processing system

in a sixth embodiment;

Fig. 78 is a block diagram of another functional configuration example of the information processing system in the sixth embodiment;

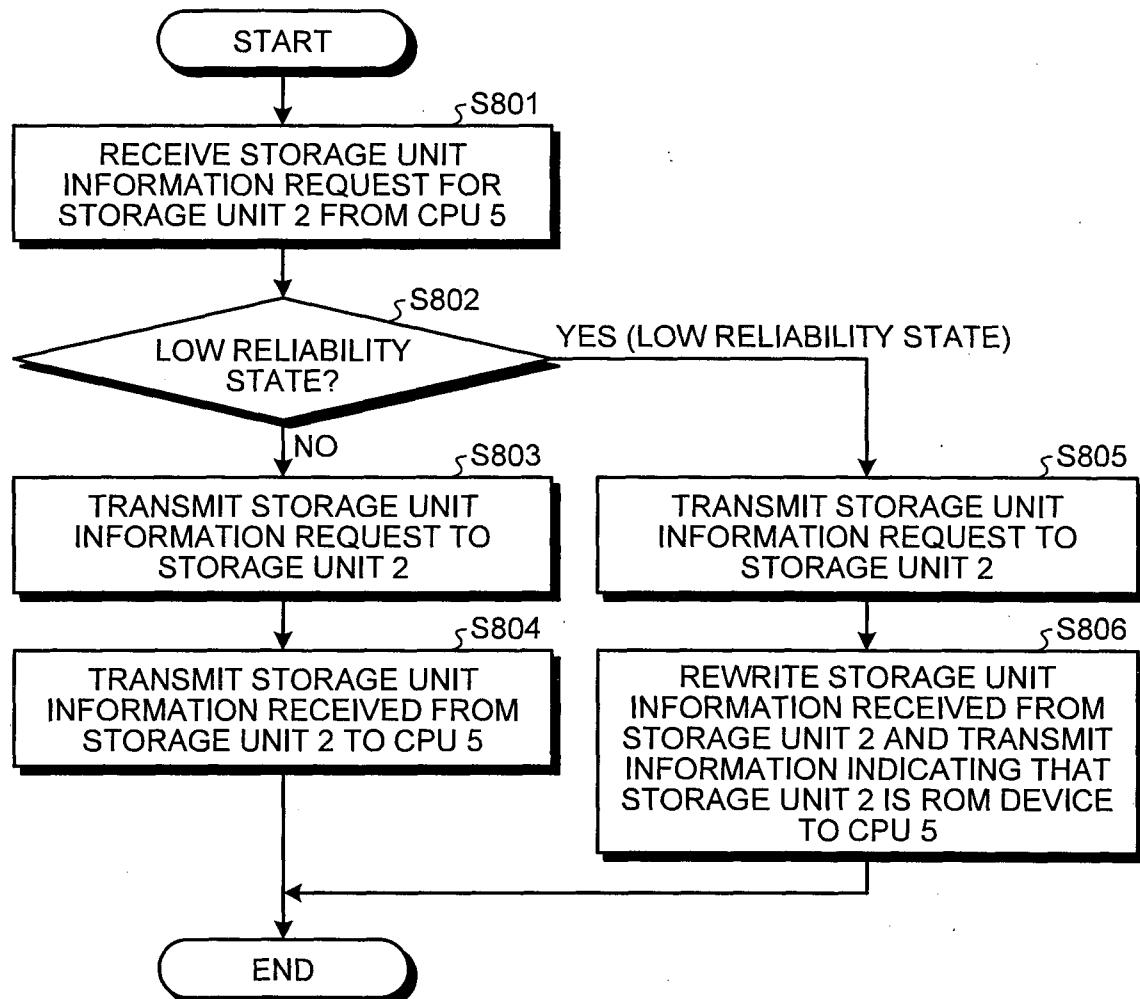

5 Fig. 79 is a flowchart for explaining transition operation of a control unit from a normal state to a low reliability state;

Fig. 80 is a flowchart for explaining an example of a processing procedure performed when the control unit 10 receives a storage unit information request for a storage unit from a CPU;

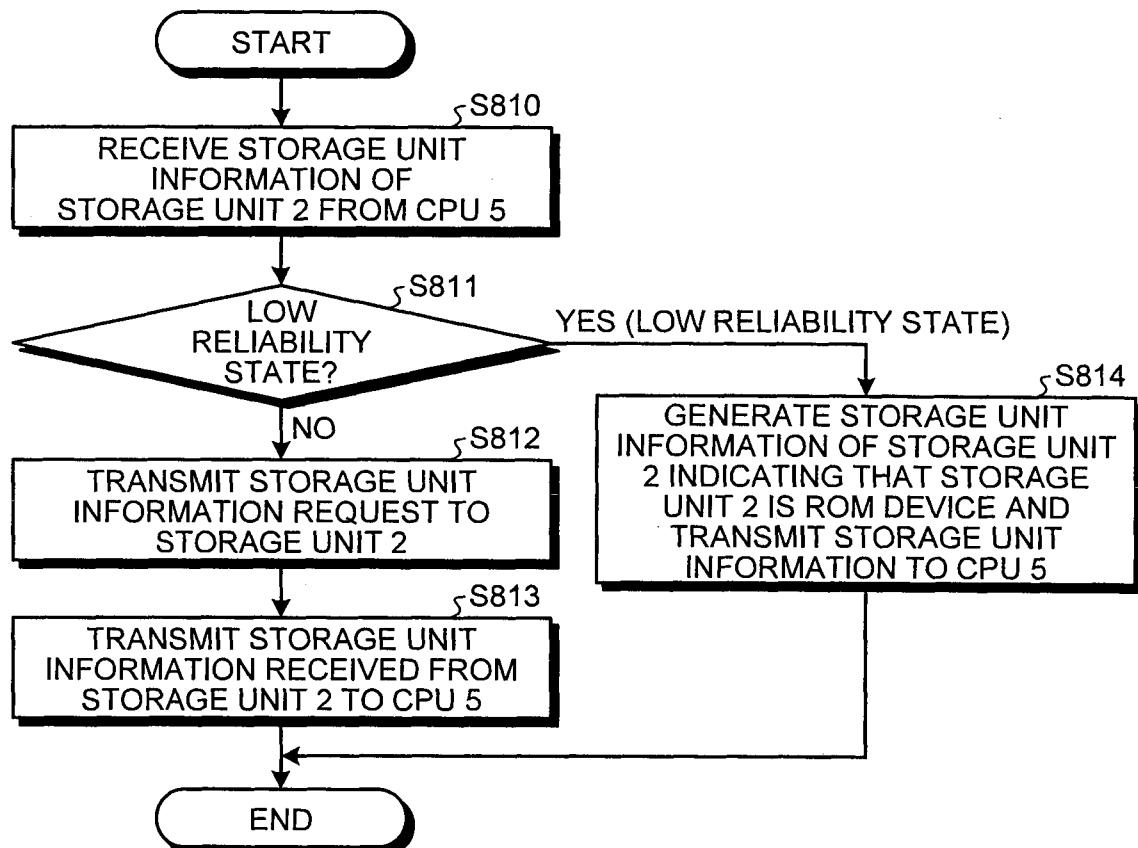

Fig. 81 is a flowchart for explaining an example of another processing procedure performed when the control unit receives the storage unit information request for the 15 storage unit from the CPU;

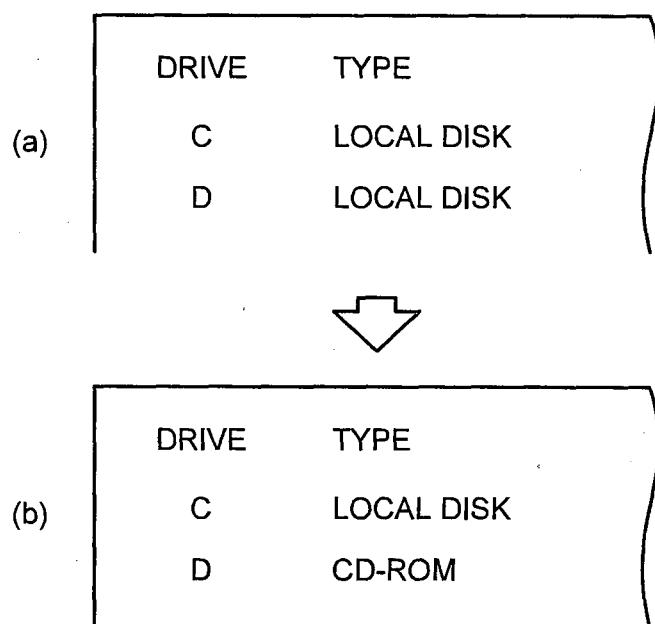

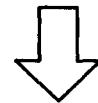

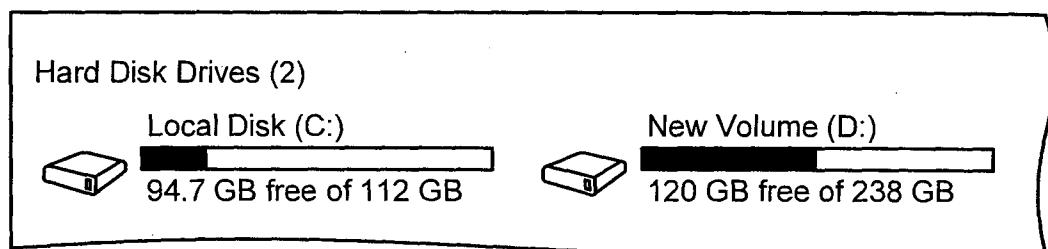

Fig. 82 is a diagram of a drive display screen example in an information processing device;

Fig. 83 is a diagram of another drive display screen example in the information processing device;

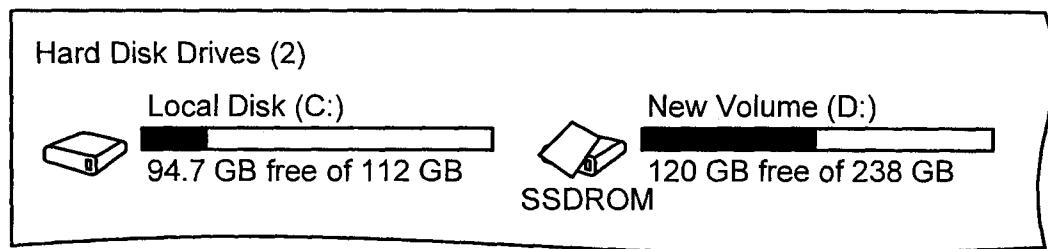

20 Fig. 84 is a diagram of another display screen example in the information processing device; and

Fig. 85 is a block diagram of another functional configuration example of the information processing system in the sixth embodiment.

25

#### DETAILED DESCRIPTION

According to an embodiment, an information processing system includes a first storage unit including a readable and writable first memory, a second storage unit including 30 a readable and writable second memory, and an information processing device connectable to the first storage unit and the second storage unit. The information processing device includes a control unit configured to execute, based on

reliability information acquired from the first storage unit, first processing for determining a storage status of the first storage unit, second processing for, when the storage status of the first storage unit is recognized as a 5 protected state by the first processing, executing write on the second storage unit and executing read on the first and second storage units, and third processing for updating addresses of stored data in the first and second storage units according to the write by the second processing.

10 Information processing systems, control programs, and information processing devices according to embodiments are explained in detail below with reference to the accompanying drawings. The invention is not limited by the embodiments.

15 (First Embodiment)

#### Configuration of a system

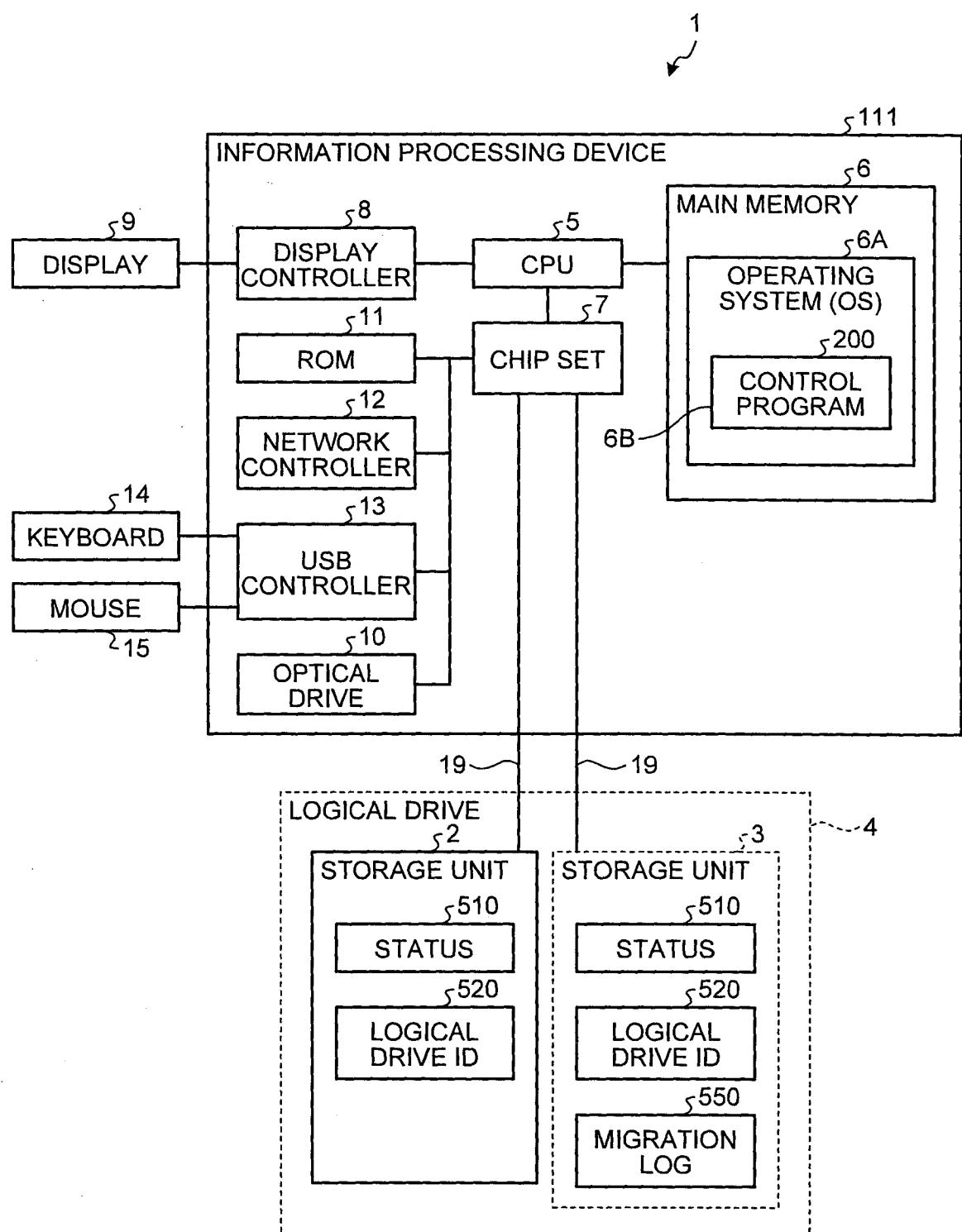

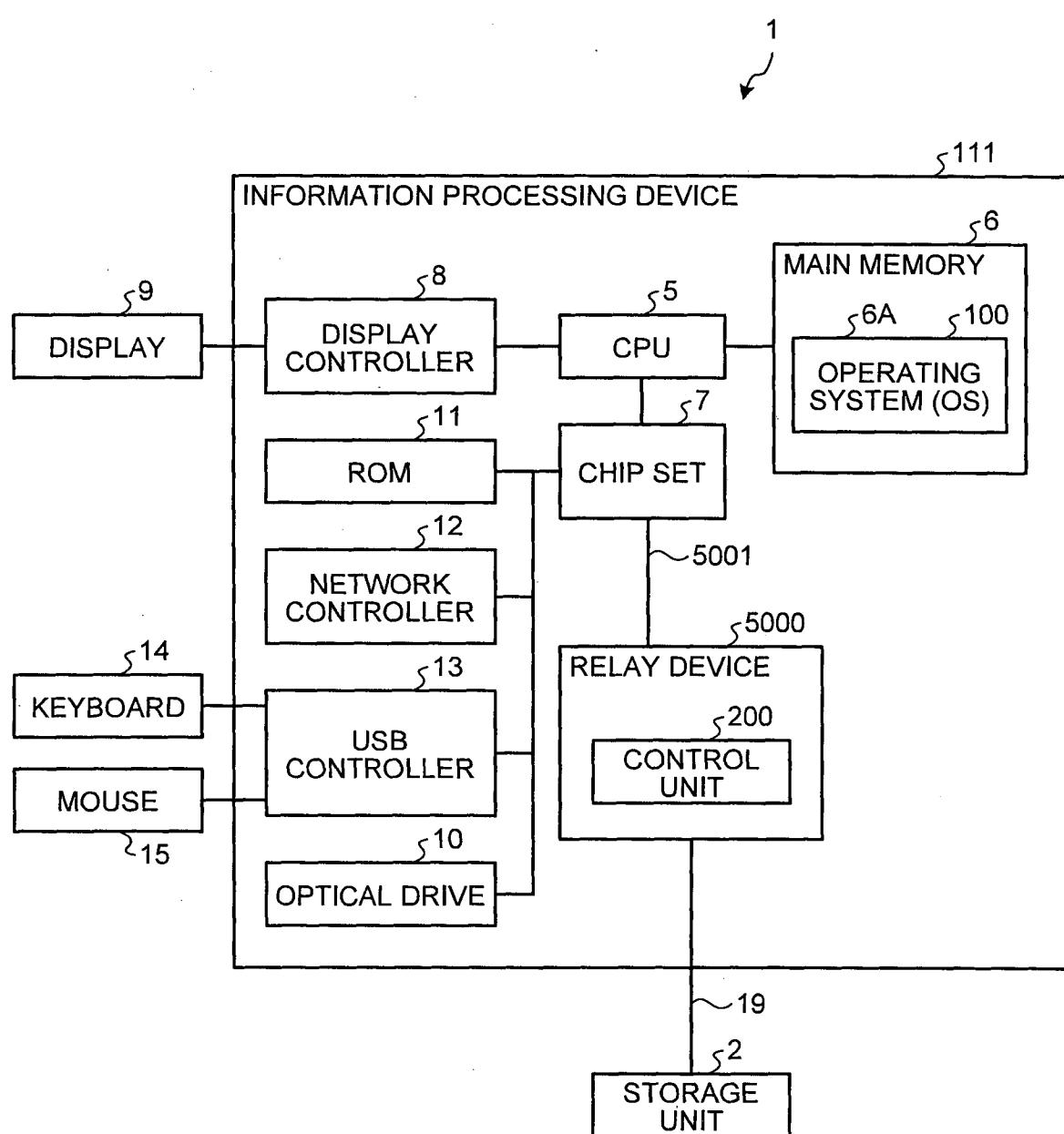

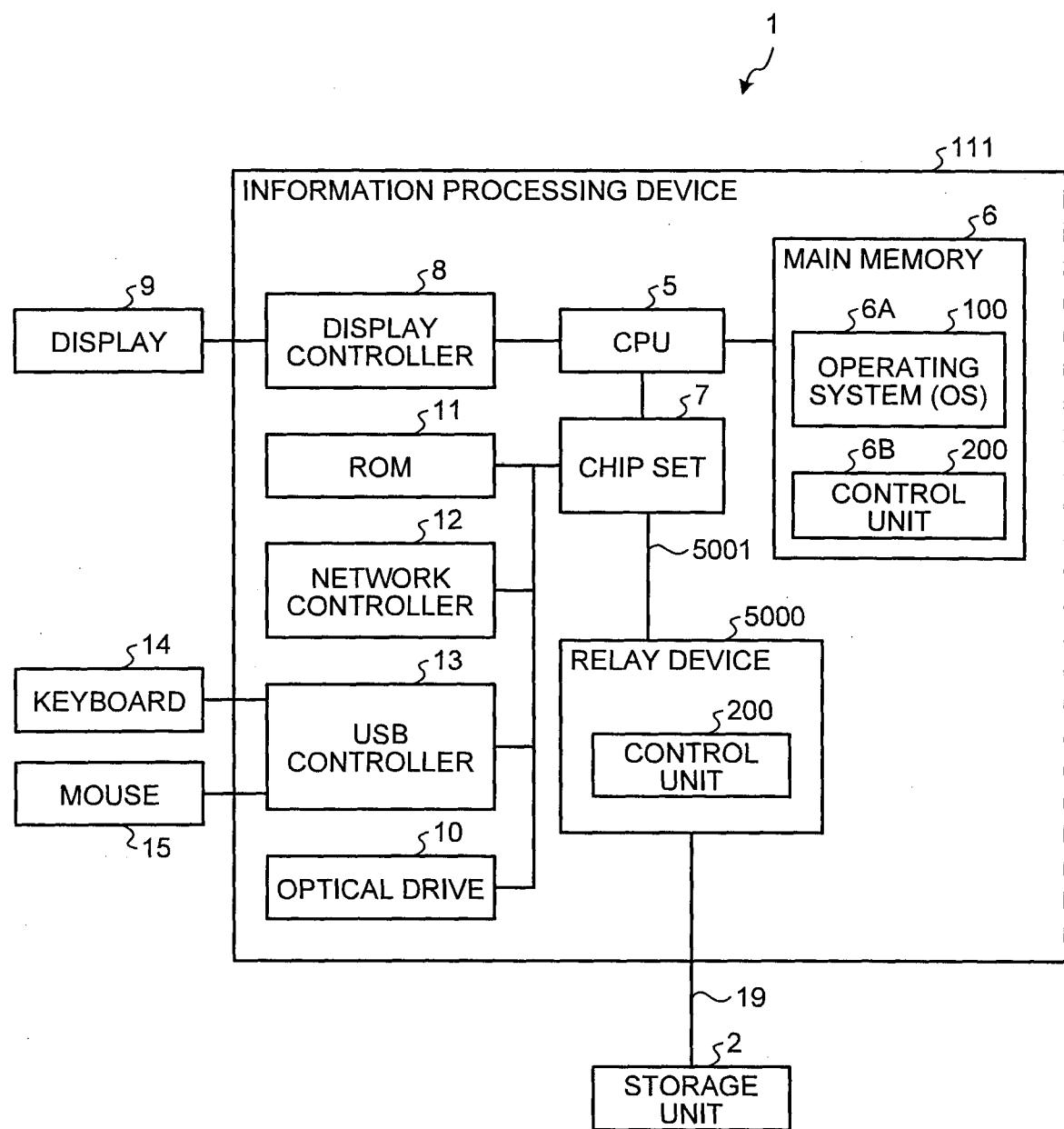

The configuration of a computer system, which is an example of an information processing system, in a first embodiment is shown in Fig. 1. An information processing 20 system 1 includes an information processing device 111, one or a plurality of storage units, and an interface 19 configured to connect the information processing device 111 and the storage units. In this embodiment, a SSD (Solid State Drive), which is a nonvolatile storage device, is 25 used as the storage unit. However, the storage unit can be other storage devices such as a hard disk drive (HDD), a hybrid drive, a SD card, a USB memory, a NAND flash memory chip, a magnetic tape, an embedded Multi Media Card (eMMC), and a storage device and a memory node described in United 30 States Patent Application Publication No. 2012/0117354. A plurality of storage areas included in one storage device can be respectively used as separate storage units. In the following explanation in this embodiment, a SATA (Serial

Advanced Technology Attachment) interface is used as the interface 19. However, a PCI Express (Peripheral Component Interconnect Express, PCIe), a USB (Universal Serial Bus), a SAS (Serial Attached SCSI), a Thunderbolt (registered trademark), an Ethernet (registered trademark), a Fibre channel, and the like can be used. A CPU (a control circuit) 5 is a central processing unit in the information processing device 111. Various calculations and controls in the information processing device 111 are performed by the CPU 5. The CPU 5 and a chip set 7 are connected by an interface such as a DMI (Direct Media Interface). The CPU 5 performs control of a storage unit 2 and an optical drive 10 such as a DVD drive via the chip set 7. The CPU 5 performs control of a main memory 6. As the main memory 6, for example, a DRAM (Dynamic Random Access Memory), a MRAM (Magnetoresistive Random Access Memory), a ReRAM (Resistance Random Access Memory), and a FeRAM (Ferroelectric Random Access Memory) can be adopted.

A user performs control of the information processing device 111 through an input device such as a keyboard 14 or a mouse 15. A signal from the keyboard 14 or the mouse 15 is processed by the CPU 5 via, for example, a USB (Universal Serial Bus) controller 13 and the chip set 7. The CPU 5 sends image data and text data to a display (a display device) 9 via a display controller 8. The user can visually recognize, via the display 9, the image data and the text data sent from the information processing device 111.

The CPU 5 is a processor provided to control the operation of the information processing device 111. The CPU 5 executes, for example, an operating system (OS) 100 loaded from the storage unit 2 to the main memory 6. Further, when the optical drive 10 enables execution of at

least one of read processing and write processing on an inserted optical disk, the CPU 5 executes the processing. The CPU 5 executes UEFI (Unified Extensible Firmware Interface) firmware, a system BIOS (Basic Input/Output System), and the like stored in a ROM 11. The UEFI firmware and the system BIOS are programs for hardware control in the information processing device 111. Besides, the CPU 5 controls a network controller 12 via the chip set 7. As the network controller 12, there are, for example, a LAN (Local Area Network) controller and a wireless LAN controller.

The main memory 6 temporarily stores a program and data and functions as a work memory of the CPU 5. The main memory 6 includes a storage area 6A for storing the OS 100 and a storage area 6B for storing a control program 200. As generally known as, for example, Windows (registered trademark), the OS 100 is a program for managing the entire information processing device 111, for example, managing an input and output device of the information processing device 111, managing a storage unit and a memory, and performing control for enabling software to use hardware and a storage device of the information processing device 111. In an example explained in this embodiment, the control program 200 is a part of the OS 100. However, the control program 200 and the OS 100 can be independent programs. In this embodiment, the control program 200 is explained as a program read to the main memory 6 via the interface 19 and executed. However, the control program 200 can be stored in the ROM 11 and operate as a part of the UEFI firmware or the system BIOS. The control program 200 can be implemented in the information processing device 111 as hardware. In the main memory 6, metadata 300 and a logical drive status table 450 are stored.

The display controller 8 is a video reproduction controller configured to control the display 9 of the information processing device 111. The chip set 7 is a bridge device connected to a local bus of the CPU 5. The 5 chip set 7 controls the storage unit 2 and a storage unit 3, which are storage devices configured to store various kinds of software and data, via the interface 19. The storage unit 2 and the storage unit 3 can be connected to the CPU 5 through the chip set 7 or can be directly connected to the 10 CPU 5.

The information processing device 111 accesses the storage unit 2 and the storage unit 3 in a unit of a logical sector. A write command (a write request), a read command (a read request), a flash command, and the like are 15 input to the storage unit 2 and the storage unit 3 via the interface 19.

The chip set 7 also has a function for subjecting the ROM 11, the optical drive 10, the network controller 12, and the USB controller 13 to access control. The keyboard 20 14 and the mouse 15 are connected to the USB controller 13.

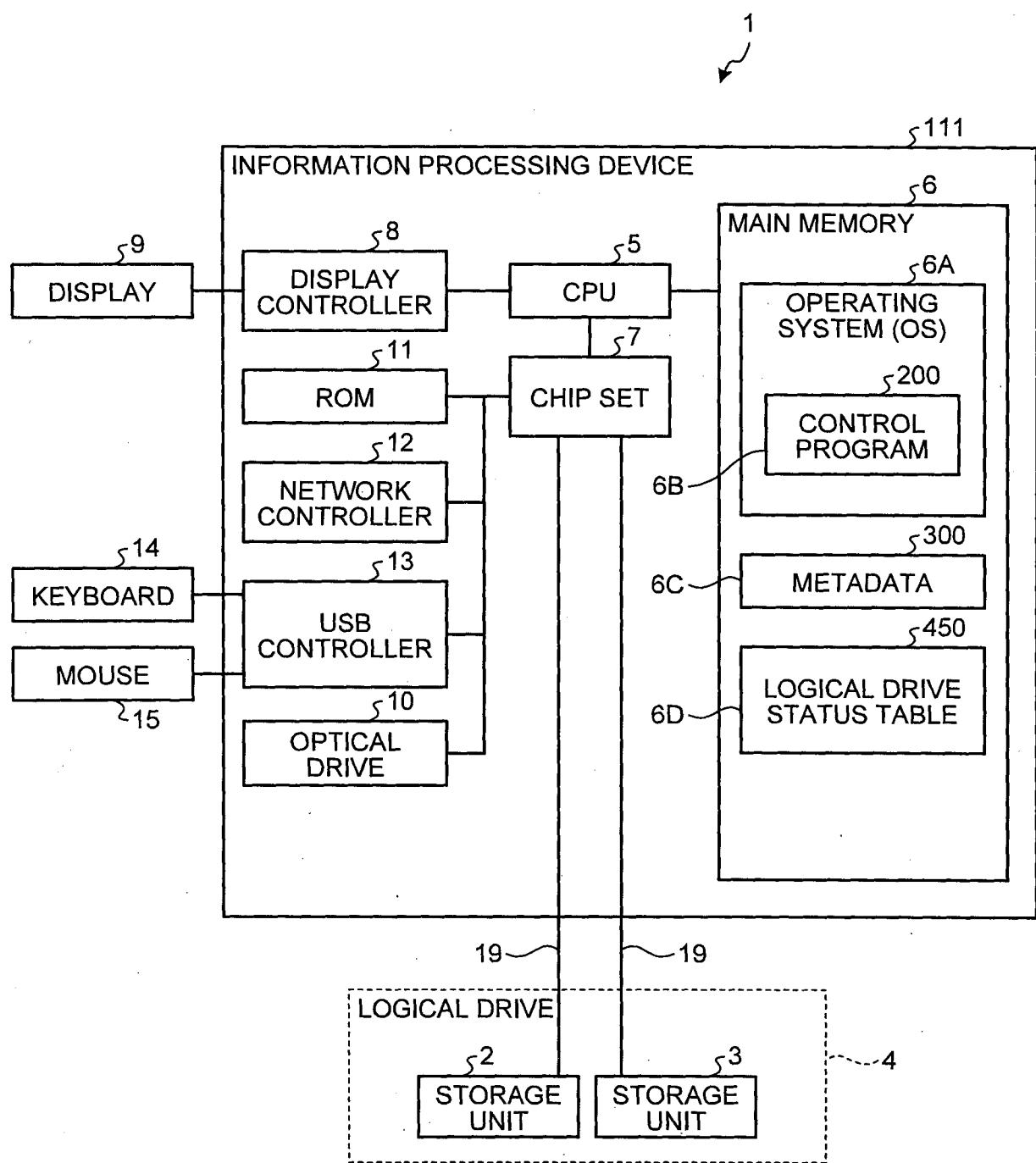

#### Form of a control program

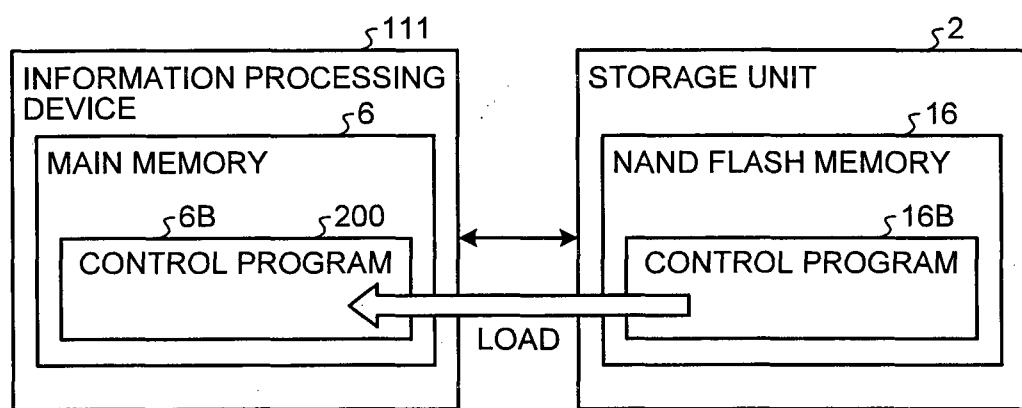

In this embodiment, for example, as shown in Fig. 2, when the information processing device 111 is off, the control program 200 is stored in an area 16B of a NAND 25 flash memory (a NAND memory) 16 of the storage unit 2. As shown in Fig. 2, when the information processing device 111 starts or a program starts, the control program 200 is loaded from the area 16B of the NAND memory 16 to an area 6B on the main memory 6. On the other hand, when a 30 plurality of storage units are connected to the information processing device 111, for example, when a storage unit 20 separate from the storage unit 2 and the storage unit 3 is connected to the information processing device 111, as

shown in Fig. 3, the control program 200 can be stored in an area 20B of the storage unit 20. Then, when the information processing device 111 starts or the program starts, the control program 200 is loaded from the area 20B 5 to the area 6B on the main memory 6. In particular, when the storage unit 20 is used as a system drive configured to store an OS and the storage unit 2 is used as a data drive configured to store user data such as a document, still image data, and moving image data, it is desirable to store 10 the control program 200 in the storage unit 20, which functions as a system drive, in terms of clearly distinguishing roles of the storage unit 2 and the storage unit 20. For example, the storage unit 20 functioning as the system drive is used as a storage drive configured to 15 mainly store an OS and an application program and the storage unit 2 functioning as the data drive is used as a storage drive configured to store user data.

In terms of saving labor for setup of the control program 200 by the user, for example, as shown in Figs. 2 20 and 3, it is desirable that the information processing system 1 is shipped from a manufacturer, displayed in a shop, and delivered to the user in a state in which the control program 200 is stored in the storage unit 2 or the storage unit 20. On the other hand, in terms of enabling 25 the user to select propriety of installation of the control program 200 and in terms of enabling a latest control program to be provided to the user, it is desirable that the control program 200 can be stored in the storage unit 2 or the storage unit 20 by download from a WEB or 30 installation from an external storage medium such as a DVD-ROM or a USB memory.

Fig. 4 is an example of the download from the WEB. The control program 200 is stored in an area 22B of a

storage medium 22 in a WEB server 21. The control program 200 is downloaded (or installed) in the area 16B on the NAND memory 16 of the storage unit through, for example, the network controller 12 via a network such as the 5 Internet, a local network, or a wireless LAN. As the storage medium 22, for example, a SSD, a HDD, a hybrid drive, or a magnetic tape is used. In the case of Fig. 3, the control program 200 is downloaded to or installed in the area 20B on the storage unit 20.

10 Fig. 5 is an example of the installation from the optical medium. The control program 200 is stored in an optical medium 23 such as a DVD-ROM, a CD-ROM, a DVD-RW, or a Blu-ray (registered trademark) disc. When the optical medium 23 is set on the optical drive 10, the control 15 program 200 is installed in the area 16B on the NAND memory 16 (or the area 20B) of the storage unit 2 via the optical drive 10.

Fig. 6 is an example of the installation from the USB memory. The control program 200 is stored in an area 24B 20 of a USB memory 24. When the USB memory 24 is connected to the USB controller 13, the control program 200 is installed in the area 16B on the NAND memory 16 (or the area 20B) of the storage unit 2 via the USB controller 13. Naturally, other external memories such as a SD card can be used 25 instead of the USB memory 24. In terms of easiness of acquisition by the user, it is desirable that the optical medium 23 and the USB memory 24 are packaged together with the information processing system 1 or the storage unit 2 as accessories when the information processing system 1 or 30 the storage unit 2 is shipped. On the other hand, the optical medium 23 and the USB memory 24 can be independently sold as software commodities or can be attached as supplements of a magazine or a book.

Hierarchical structure of software

A hierarchical structure in a software level of the information processing device 111 is shown in Fig. 7. Usually, an application program 400 loaded on the main memory 6 does not directly communicate with storage units such as the storage unit 2 and the storage unit 3 and communicates with the storage units through the OS 100 loaded to the main memory 6. The OS 100 communicates with the storage units through the UEFI firmware or the system BIOS. Before life end processing (processing at the end of the storage unit's life or Lifespan-reached processing) explained below, the OS 100 recognizes the storage unit 2 as a logical drive 4 (see Fig. 38) functioning as a logical unit and notifies the application program 400 of the logical drive 4 as an accessible storage drive. When the application program 400 needs to transmit a command such as a read request or a write request to the logical drive 4, the application program 400 transmits a request for access to the logical drive in a file unit to the OS 100. The OS 100 refers to the metadata 300 stored in the main memory 6, specifies a logical address (LBA: Logical block Address) of the storage unit 2 corresponding to the access-requested file, and transmits the command, the LBA, and data to the storage unit 2 via the interface 19. Upon receiving a response from the storage unit 2, the OS 100 transmits a response to the application program 400. When the logical drive 4 changes to a migration state explained below, the OS 100 recognizes the storage unit 2 and the storage unit 3 as the logical drive 4.

30 Configuration of the information processing device

A configuration example of the information processing system 1 is explained. Fig. 8 is a schematic diagram of a desktop computer functioning as the information processing

system 1. The desktop computer includes a computer main body 31, the display 9, the keyboard 14, and the mouse 15. The computer main body 31 includes a motherboard 30 mounted with main hardware, the storage unit 2, and a power supply device 32. The storage unit 2 is physically connected to the motherboard 30 via a SATA cable and electrically connected to, via the chip set 7 mounted on the motherboard 30, the CPU 5 also mounted on the motherboard. The power supply device 32 generates various kinds of electric power used in the desktop computer and supplies the electric power to the motherboard 30, the storage unit 2, and the like via a power supply cable. The storage unit 3 can be physically connected to the motherboard 30 via the SATA cable. Consequently, the storage unit 3 is electrically connected to, via the chip set 7 mounted on the motherboard 30, the CPU 5 also mounted on the motherboard.

Fig. 9 is a schematic diagram of a portable computer functioning as the information processing system 1. The portable computer includes a computer main body 34 and a display unit 35. In the display unit 35, a display device 9 configured by, for example, an LCD (Liquid Crystal Display) is incorporated. The display unit 35 is attached to the computer main body 34 to be capable of pivoting between an open position where the upper surface of the computer main body 34 is exposed and a closed position where the upper surface of the computer main body 34 is covered. The computer main body 34 includes a thin box-like housing. A power switch 36, the keyboard 14, a touch pad 33, and the like are arranged on the upper surface of the computer main body 34. As in the desktop computer, the computer main body 34 includes the storage unit 2, a motherboard, and a power supply device.

The information processing system 1 applied with the

present invention can be, besides the above, an image pickup apparatus such as a still camera or a video camera or can be a tablet computer, a smart phone, a game apparatus, a car navigation system, a printer apparatus, a 5 scanner apparatus, a server system, or the like.

#### Configuration of the storage device (1)

The configuration of the storage unit 2 is explained. In the explanation in this embodiment, a main component of the storage unit 2 is the NAND memory 16. In the 10 explanation in this embodiment, the storage unit 2 and the storage unit 3 have the same configuration. On the other hand, the present invention can also be applied when the storage unit 3 has a configuration different from the configuration of the storage unit 2. For example, the 15 storage unit 2 is a SSD including the NAND memory 16 as a main component and the storage unit 3 is a hard disk drive including a magnetic disk as a main component. It is desirable that the storage unit 2 and the storage unit 3 have stored statistical information 65 therein. However, 20 the present invention can also be applied when the storage unit 2 has stored the statistical information 65 therein and the storage unit 3 does not have stored the statistical information 65 therein. It is desirable that the storage capacity of the storage unit 3, which is a data migration 25 destination, is equal to or larger than the storage capacity of the storage unit 2, which is a data migration source. However, the present invention can also be applied when the storage capacity of the storage unit 3 is smaller than the storage capacity of the storage unit 2.

#### 30 Configuration of the NAND memory

In Fig. 10, an internal configuration example of a NAND memory chip 80 included in the NAND memory 16 used as components of the storage unit 2 and the storage unit 3 in

this embodiment is shown. The NAND memory 16 includes one or a plurality of NAND memory chips 80.

The NAND memory chip 80 includes a memory cell array in which a plurality of memory cells are arrayed in a matrix shape. A memory cell transistor included in the memory cell array is configured by a MOSFET (Metal Oxide Semiconductor Field Effect Transistor) having a stacked gate structure formed on a semiconductor substrate. The stacked gate structure includes a charge storage layer (a floating gate electrode) formed on the semiconductor substrate via a gate insulating film and a control gate electrode formed on the floating gate electrode via an inter-gate insulating film. A threshold voltage of the memory cell transistor changes according to the number of electrons accumulated in the floating gate electrode. The memory cell transistor stores data according to a difference in the threshold voltage.

In the explanation in this embodiment, the respective memory cells adopt a write system of a four-level store method for 2 bit/cell for writing data using an upper page and a lower page. However, the essence of the present invention is the same when the memory cells adopts a write system of a two-level store method of 1 bit/cell for writing data using a single page, a write system of an eight-level store method for 3 bit/cell for writing data using an upper page, a middle page, and a lower page, or a write system of a write system of a multi-level store method for 4 bit/cell or more. The memory cell transistor is not limited to the structure including the floating gate electrode and can be a structure such as a MONOS (Metal-Oxide-Nitride-Oxide-Silicon) type that can adjust a threshold voltage by trapping electrons on a nitride interface functioning as a charge storage layer. Similarly,

the memory cell transistor of the MONOS type can be configured to store one bit or can be configured to store a multi-level. The memory cell transistor can be, as a nonvolatile storage medium, a semiconductor storage medium 5 in which memory cells are three-dimensionally arranged as described in United States Patent 8,189,391, United States Patent Application Publication No. 2010/0207195, and United States Patent Application Publication No. 2010/0254191.

As shown in Fig. 10, the NAND memory chip 80 includes 10 a memory cell array 82 configured by arranging memory cells for storing data in a matrix shape. The memory cell array 82 includes a plurality of bit lines, a plurality of word lines, and a common source line. Electrically data-rewritable memory cells are arranged in a matrix shape at 15 intersections of the bit lines and the word lines. A bit line control circuit 83 for controlling the bit lines and a word line control circuit 85 for controlling the word lines are connected to the memory cell array 82. That is, the bit line control circuit 83 reads data of the memory cells 20 in the memory cell array 82 via the bit lines and applies a write control voltage to the memory cells in the memory cell array 82 via the bit lines and writes data in the memory cells.

A column decoder 84, a data input/output buffer 89, 25 and a data input/output terminal 88 are connected to the bit line control circuit 83. The data of the memory cells read from the memory cell array 82 is output to the outside from the data input/output terminal 88 via the bit line control circuit 83 and the data input/output buffer 89. 30 Write data input to the data input/output terminal 88 from the outside is input to the bit line control circuit 83 by the column decoder 84 via the data input/output buffer 89 and written in designated memory cells.

The memory cell array 82, the bit line control circuit 83, the column decoder 84, the data input/output buffer 89, and the word line control circuit 85 are connected to a control circuit 86. The control circuit 86 generates, 5 according to a control signal input to the control signal input terminal 87, control signals and control voltages for controlling the memory cell array 82, the bit line control circuit 83, the column decoder 84, the data input/output buffer 89, and the word line control circuit 85. A circuit 10 section other than the memory cell array 82 in the NAND memory chip 80 is referred to as NAND controller (NANDC) 81.

Fig. 11 shows the configuration of the memory cell array 82 shown in Fig. 10. The memory cell array 82 is a NAND cell type memory cell array and is configured to 15 include a plurality of NAND cells. One NAND cell includes a memory string MS formed by memory cells connected in series and selection gates S1 and S2 connected to both ends of the memory string MS. The selection gate S1 is connected to a bit line BL and the selection gate S2 is 20 connected to a source line SRC. Control gates of memory cells MC arranged in the same row are connected in common to word lines WL0 to WLm-1. First selection gates S1 are connected in common to a select line SGD and second selection gates S2 are connected in common to a select line 25 SGS.

The memory cell array 82 includes one or a plurality of planes. The plane includes a plurality of blocks. Each of the blocks includes a plurality of NAND cells. Data is erased in a unit of the block.

30 A plurality of memory cells connected to one word line configure one physical sector. Data is written and read for each physical sector. The physical sector is unrelated to a logical sector of the LBA explained below. In the one

physical sector, for example, data equivalent to two physical pages (two pages) is stored in the case of the 2 bit/cell write system (four-level). On the other hand, in the case of the 1 bit/cell write system (two-level), for 5 example, data equivalent to one physical page (one page) is stored in the one physical sector. In the case of the 3 bit/cell write system (eight-level), for example, data equivalent to three physical pages (three pages) is stored in the one physical sector.

10 During a read operation, a program verify operation, and a program operation, one word line is selected and one physical sector is selected according to a physical address such as a Row Address received from a SSDC 41 explained below. Switching of a page in the physical sector is 15 performed according to a physical address. In this embodiment, the NAND memory 16 adopts the 2 bit/cell write system, the SSDC 41 handles the physical sector assuming that two pages, i.e., an upper page and a lower page, are allocated to the physical sector as physical pages.

20 Physical addresses are allocated to all the pages.

The four-level NAND memory of 2 bit/cell is configured such that a threshold voltage in one memory cell could have four kinds of distributions. Fig. 12 shows a relation between 2-bit four-level data (data "11", "01", "10", and 25 "00") stored in memory cells of a four-level NAND cell type flash memory and a threshold voltage distribution of the memory cells. In Fig. 12, VA1 represents a voltage applied to a selected word line when two data are read concerning a physical sector, a lower page of which is already written 30 and an upper page of which is not written yet. VA1V represents a verify voltage applied to check whether write is completed when write in A1 is performed.

VA2, VB2, and VC2 represent voltages applied to a

selected word line when four data are read concerning a physical sector, a lower page and an upper page of which are already written. VA2V, VB2V, and VC2V represent, when write in threshold voltage distributions is performed, 5 verify voltages applied to check whether the write is completed. Vread1 and Vread2 represent, when read of data is performed, read voltages applied to an unselected memory cell in the NAND cells and conducting the unselected memory cell irrespective of retained data of the unselected memory 10 cell. Further, Vev1 and Vev2 represent, when data of the memory cells are erased, erasing verify voltages applied to the memory cells to check whether the erasing is completed. Vev1 and Vev2 have negative values. The magnitude of Vev1 and Vev2 are determined taking into account the influence 15 of interference of adjacent memory cells. Magnitude relations of the voltages are as follows:

Vev1 < VA1 < VA1V < Vread1

Vev2 < VA2 < VA2V < VB2 < VB2V < VC2 < VC2V < Vread2

The erasing verify voltages Vev1, Vev2, and Vev3 are 20 negative values as explained above. However, a voltage actually applied to the control gate of the memory cell MC in the erasing verify operation is not a negative value and is zero or a positive value. That is, in the actual erasing verify operation, a positive voltage is given to a 25 back gate of the memory cell MC and a voltage of zero or a positive value smaller than the back gate voltage is applied to the control gate of the memory cell MC. In other words, the erasing verify voltages Vev1, Vev2, and Vev3 are voltage equivalently having negative values.

30 An upper limit value of a threshold voltage distribution ER of the memory cell after block erasing is also a negative value. Data "11" is allocated to the memory cell. The memory cells of data "11", "01", "10",

and "00" in a lower page and upper page written state respectively have positive threshold voltage distributions ER2, A2, B2, and C2 (lower limit values of A2, B2, and C2 are also positive values). The threshold voltage distribution A2 of the data "01" has a lowest voltage value, the threshold voltage distribution C2 of the data "00" has a highest voltage value, and the voltage values of the various threshold voltage distributions have a relation of A2<B2<C2. The memory cell of the data "10" in a lower page written and upper page unwritten state has a positive threshold voltage distribution A (a lower limit value of A1 is also a positive value). The threshold voltage distribution shown in Fig. 12 is only an example. The present invention is not limited to this. For example, in the explanation referring to Fig. 12, all the threshold voltage distributions A2, B2, and C2 are positive threshold voltage distributions. However, when the threshold voltage distribution A2 is a negative voltage distribution and the threshold voltage distributions B2 and C2 are positive voltage distributions, the distributions are also included in the scope of the present invention. Even if threshold voltage distributions ER1 and ER2 are positive values, the present invention is not limited to this. In this embodiment, the correspondence relation among the data of ER2, A2, B2, and C2 is "11", "01", "10", and "00". However, the correspondence relation can be another correspondence relation such as "11", "01", "00", and "10".

2-bit data of one memory cell includes lower page data and upper page data. The lower page data and the upper page data are written in the memory cell according to separate write operations, i.e., two write operations. When data is represented as "\*@", \* represents the upper page data and @ represents the lower page data.

First, write of the lower page data is explained with reference to first and second sections of Fig. 12. It is assumed that all the memory cells have the threshold voltage distribution ER in the erased state and store the 5 data "11". As shown in Fig. 12, when write of the lower page data is performed, the threshold voltage distribution ER of the memory cells is divided into two threshold voltage distributions (ER1 and A1) according to a value ("1" or "0") of the lower page data. When the value of the 10 lower page data is "1", ER1=ER because the threshold voltage distribution ER in the erased state is maintained. However, a relation between the threshold voltage distributions ER and ER1 can be ER1>ER.

On the other hand, when the value of the lower page 15 data is "0", a high electric field is applied to tunnel oxide films of the memory cells, electrons are injected into the floating gate electrode, and the threshold voltage Vth of the memory cells is increased by a predetermined value. Specifically, the verify voltage VA1V is set and 20 the write operation is repeated until the threshold voltage is increased to be equal to or higher than the verify voltage VA1V. As a result, the memory cells change to the written state (the data "10"). When the memory cells do not reach the threshold voltage even if the write operation 25 is repeated a predetermined number of times (or the number of memory cells not reaching the threshold voltage is equal to or larger than a threshold value), write in the physical page is "Program Error" (Program Fail or Write Error).

Write of the upper page data is explained with 30 reference to the second and third sections of Fig. 12. The write of the upper page data is performed based on write data (upper page data) input from the outside of the chip and lower page data already written in the memory cells.

That is, as shown in the second and third sections of Fig. 12, when a value of the update data is "1", a high electric field is not applied to the tunnel oxide films of the memory cells to prevent a rise of the threshold voltage  $V_{th}$  of the memory cells. As a result, the memory cells having the data "11" (the threshold voltage distribution ER1 of the erased state) maintain the data "11" (ER2) and the memory cells having the data "10" (the threshold voltage distribution A1) maintain the data "10" (B2).

10 However, in terms of securing a voltage margin between the distributions, it is desirable to adjust a lower limit value of the threshold voltage distribution using the positive verify voltage  $VB2V$  larger than the verify voltage  $VA1V$  to thereby form a threshold voltage distribution B2 obtained by narrowing the width of the threshold voltage distribution. When the memory cells do not reach the threshold voltage even if the lower limit value adjustment is repeated a predetermined number of times (or the number of memory cells not reaching the threshold voltage is equal

15 to or larger than the predetermined value), write in the physical page is "Program Error".

20

On the other hand, when the value of the upper page data is "0", a high electric field is applied to the tunnel oxide films of the memory cells, electrons are injected into the floating gate electrode, and the threshold voltage  $V_{th}$  of the memory cells is increased by a predetermined value. Specifically, the verify voltages  $VA2V$  and  $VC2V$  are set and the write operation is repeated until the threshold voltage is increased to be equal to or higher than the verify voltages  $VA2V$  and  $VC2V$ . As a result, the memory cells having the data "11" (the threshold voltage distribution ER1 in the erased state) change to the data "01" of the threshold voltage distribution A2 and the

memory cells having the data "10" (A1) changes to the data "00" of the threshold voltage distribution C2. At this point, the verify voltages VA2V and VC2V are used and lower limit values of the threshold voltage distributions A2 and 5 C2 are adjusted. When the memory cells do not reach the threshold voltage even if the write operation is repeated the predetermined number of times (or the number of memory cells not reaching the threshold voltage is equal to or larger than the threshold value), write in the physical 10 page is "Program Error".

On the other hand, in an erase operation, an erasing verify voltage Vev is set and the erase operation is repeated until the threshold voltage is reduced to be equal to or lower than the verify voltage Vev. As a result, the 15 memory cells change to the written state (the data "00"). When the memory cells do not reach the threshold voltage even if the erase operation is repeated a predetermined number of times (or the number of memory cells not reaching the threshold voltage is equal to or larger than the 20 predetermined value), erasing for the physical page is "Erase Error" (erase fail).

An example of the data write system in the general four-level store method is explained above. In a multi-bit storage system of 3 bit/cell or more, according to higher 25 order page data, an operation for dividing the threshold voltage distribution into eight or more kinds is only added to the operation explained above. Therefore, a basic operation is the same.

#### Configuration of the storage device (2)

30 A configuration example of the storage unit 2 and the storage unit 3 is explained. In this embodiment, as shown in Fig. 13, the storage unit 2 and the storage unit 3 functioning as SSD include a NAND flash memory (hereinafter

abbreviated as NAND memory) 16 functioning as a non-volatile semiconductor memory, an interface controller (IFC) 42 configured to perform transmission and reception of signals to and from the information processing device 5 111 via the interface 19, a RAM (Random Access Memory) 40 functioning as a semiconductor memory including a cache memory (CM) 46 functioning as an intermediate buffer between the IFC 42 and the NAND memory 16, a SSD controller (SSDC) 41 configured to administer management and control 10 of the NAND memory 16 and the RAM 40 and control of the interface controller 42, and a bus 43 configured to connect these components.

As the RAM 40, for example, a volatile RAM such as a DRAM (Dynamic Random Access Memory) or a SRAM (Static 15 Random Access Memory) or a nonvolatile RAM such as a FeRAM (Ferroelectric Random Access Memory), a MRAM (Magnetoresistive Random Access Memory), a PRAM (Phase Change Random Access Memory), or a ReRAM (Resistance Random Access Memory) can be adopted. The RAM 40 can be included 20 in the SSDC 41.

The NAND memory 16 includes a plurality of NAND memory chips 80. The NAND memory 16 stores user data designated by the information processing device 111, stores a management table for managing the user data, and stores, 25 for backup, management information managed by the RAM 40. The NAND memory 16 includes the memory cell array 82 in which a plurality of memory cells are arrayed in a matrix shape. The respective memory cells can perform multi-level storage using an upper page and a lower page. The NAND 30 memory 16 includes a plurality of memory chips. Each of the memory chips is configured by arraying a plurality of blocks, which are units of data erasing. In the NAND memory 16, write of data and read of data are performed for

each page. The block includes a plurality of pages.

The RAM 40 includes the cache memory (CM) 46 functioning as a cache for data transfer between the information processing device 111 and the NAND memory 16.

5 The RAM 40 functions as a memory for management information storage and a memory for work area. Management tables managed in an area 40A of the RAM 40 are various management tables stored in an area 40M of the NAND memory 16 and loaded when the storage unit 2 and the storage unit 3 are

10 started. The management data are backed up in the area 40M of the NAND memory 16 periodically, when a standby command is received, when a flash command is received, or when a power supply is interrupted.

A function of the SSDC 41 is realized by a processor

15 configured to execute a system program (firmware) stored in the NAND memory 16, various hardware circuits, and the like. The SSDC 41 executes, in response to various commands such as a write request, a cache flash request, and a read request from the information processing device 111, data

20 transfer control between the information processing device 111 and the NAND memory 16, update and management of the various management table stored in the RAM 40 and the NAND memory 16, ECC decryption of data read from the NAND memory 16, and the like.

25 When the information processing device 111 transmits a read request or a write request to the storage unit 2, the information processing device 111 inputs an LBA serving as a logical address via the interface 19. The LBA is a logical address in which serial numbers are given to

30 logical sectors (size: e.g., 512 Bytes) starting from 0. When the information processing device 111 issues a read request or a write request to the storage unit 2, the information processing device 111 inputs, together with the

LBA, the size of a logical sector for which the read request or the write request is issued.

The IFC 42 has a function for receiving a read request, a write request, other requests, and data from the 5 information processing device 111, transmitting the received requests and the data to the SSDC 41, and transmitting the data to the RAM 40 according to the control by the SSDC 41.

A configuration example of management information 44 used in the storage unit 2 and the storage unit 3 is shown 10 in Fig. 14. As explained above, the management information 44 is stored in the area 40M of the NAND memory 16 in a nonvolatile manner. The management information stored in the area 40M is loaded to the area 40A of the RAM 40 and 15 used when the storage unit 2 is started. The management information 44 in the area 40A is backed up in the area 40M periodically or when the power supply is interrupted. When the RAM 40 is a nonvolatile RAM such as a MRAM or a FeRAM, the management information 44 can be stored in only the RAM 20 40. Then, the management information 44 is not stored in the NAND memory 16. To reduce a write amount in the NAND memory 6, it is desirable that data stored in the management information 44 is data obtained by compressing data stored in the area 40A of the RAM 40. To reduce a 25 write frequency in the NAND memory 16, it is desirable that update information (difference information) of the management information 44 stored in the area 40A of the RAM 40 is additionally written.

As shown in Fig. 14, the management information 30 includes a free block table (FBT) 60, a bad block table (BT) 61, an active block table (ABT) 62, a track table (a logical-to-physical transformation table in a track unit) 63, a cluster table (a logical-to-physical transformation

table in a cluster unit) 64, and statistical information 65.

As shown in Fig. 15, the LBA is a logical address in which serial numbers are given to logical sectors (size: e.g., 512 Bytes) starting from 0. In this embodiment, as

5 management units for the logical address (LBA) of the storage unit 2, a cluster address configured by higher order bit rows from a lower order  $(s+1)$ th bit of the LBA and a track address configured by higher order bit rows from a lower order  $(s+t+1)$ th bit of the LBA are defined.

10 That is, the logical sector is a minimum access unit from the information processing device 111. A cluster is a management unit for managing "small data" in the SSD. The cluster size is defined to be a natural number times as large as the logical sector size. A track is a management

15 unit for managing "large data" in the SSD. The track size is defined to be two or a larger natural number times as large as the cluster size. Therefore, the track address is obtained by dividing the LBA by the track size. An address in the track is a remainder obtained by dividing the LBA by

20 the track size. The cluster address is obtained by dividing the LBA by the cluster size. An address in the cluster is a remainder obtained by dividing the LBA by the cluster size. In the following explanation, for convenience, the size of the track is equal to the size of

25 data recordable in one physical block (when a redundant bit of ECC processing performed by the SSDC 41 is included in the physical block, a size obtained by removing the redundant bit). The size of the cluster is equal to the size of data recordable in one physical page (when a

30 redundant bit of the ECC processing performed by the SSDC 41 is included in the physical page, a size obtained by removing the redundant bit).

The free block table (FBT) 60 manages a block address

(a physical block ID) of a use-unallocated physical block (a free block: FB) that can be allocated anew for write when write in the NAND memory 16 is performed. The free block table (FBT) 60 manages erase count for each physical 5 block ID. When a physical block is erased, the free block table (FBT) 60 increments the erase count of the block.

The bad block table (BBT) 61 manages a block ID of a bad block (BB) serving as a physical block that cannot be used as a storage are because, for example, errors often 10 occur. As in the FBT 60, the erase count can be managed for each physical block ID.

The active block table (ABT) 62 manages an active block (AB), which is a physical block to which a use is allocated. The active block table (ABT) 62 manages the 15 erase count for each physical block ID. When a physical block is erased, the active block table (ABT) 62 increments the number of times of easing of the block.

The track table 63 manages a correspondence relation between a track address and a physical block ID of a 20 physical block in which track data corresponding to the track address is stored.

The cluster table 64 manages a correspondence relation among a cluster address, a physical block ID of a physical block in which cluster data corresponding to the cluster 25 address is stored, and a page address in the physical block in which the cluster data corresponding to the cluster address is stored.

The SSDC 41 stores, in the statistical information 65, various parameters (X01 to X32) related to the reliability 30 of the storage unit 2 as reliability information (see Fig. 27).

Values (Raw Values) of the statistical information 65 used as an example of the reliability information include a

total bad block count (statistical information X01), a total bad logical sector count (statistical information X02), a total erase count (statistical information X03), an average erase count (statistical information X04), a total 5 program error count of the NAND memory (statistical information X05), a total erase error count of the NAND memory (statistical information X06), a total read logical sector count (statistical information X07), a total written logical sector count (statistical information X08), a total 10 uncorrectable ECC error count (statistical information X09), a total retry read count (statistical information X10), a corrected n bit-m bit ECC event count (statistical information X11), data corruption error count of the interface 19 (statistical information X12), a link speed 15 down shift count of the interface 19 (statistical information X13), a lane count down shift count of the interface 19 (statistical information X14), an error count of the interface 19 (statistical information X15), an error count of the RAM 40 (statistical information X16), a power 20 on time of the storage unit 2 (statistical information X17), a power cycle count (statistical information X18), an unintentional power down count (statistical information X19), a cumulative time when temperature exceeds a maximum value of a recommended operation temperature (statistical 25 information X20), a cumulative time when temperature falls below a minimum value of a recommended operation temperature (statistical information X21), a maximum value of a response time of a command (statistical information X22), an average value of a response time of a command 30 (statistical information X23), a maximum value of a response time of the NAND memory (statistical information X24), an average value of a response time of the NAND memory (statistical information X25), a present temperature

(statistical information X26), a highest temperature (statistical information X27), a lowest temperature (statistical information X28), system data redundancy (statistical information X29), a total of written data 5 amount in the RAM 40 (statistical information X30), a statistical information increase ratio (statistical information X31), and a NAND GC Error Flag (statistical information X32).

The total bad block count (statistical information 10 X01) is explained. The SSDC 41 increments the statistical information X01 by one every time one physical block of the NAND memory 16 in the storage unit 2 is added to a bad block. It is desirable that the SSDC 41 resets the statistical information X01 to zero during manufacturing 15 (e.g., before a test process) of the storage unit 2. It is desirable that, when an error occurs in a block during the test process or when a block with a small inter-distribution margin of a threshold voltage distribution is detected, the SSDC 41 adds the block to the bad block in 20 advance. The SSDC 41 can directly calculate the statistical information X01 from the BBT 61 without storing the statistical information X01 in the statistical information 65. A larger value of the statistical information X01 indicates that reliability is further 25 deteriorated.

The total bad logical sector count (the statistical information X02) is explained. When a read command and an LBA are received from the information processing device 111 and read data cannot be subjected to ECC correction during 30 read from the NAND flash memory 16, the SSDC 41 can register the LBA in the bad logical sector table in the management information 44 as a bad logical sector (see Fig. 25). The SSDC 41 stores the number of LBAs registered in

the bad logical sector table in the statistical information 65 as the total bad logical sector count (the statistical information X02). When a read command is received from the information processing device 111, the SSDC 41 reads the 5 bad logical sector table on the RAM 40 and searches for the received LBA in the bad logical sector table. When the LBA is found in the bad logical sector table, the SSDC 41 notifies the information processing device 111 of a read error without reading data from the NAND flash memory 16.

10 When a write command is received from the information processing device 111 concerning the LBA of the bad logical sector and write processing is performed, the SSDC 41 deletes the written LBA from the bad logical sector table. When a delete notification is received from the information 15 processing device 111 concerning the LBA of the bad logical sector and delete notification processing is performed, the SSDC 41 deletes the LBA subjected to the delete notification processing from the bad logical sector table. When an erase command (a Secure Erase command) for the 20 storage unit 2 is received from the information processing device 111, the SSDC 41 erases the bad logical sector table. As the erase command for the storage unit 2, for example, an F4h Security Erase Unit command of ACS-3 or an 80h Format NVM command of NVM Express Revision 1.1 can be used.

25 Instead of managing the bad logical sector table in an LBA unit (a logical sector unit), as shown in Fig. 26, the SSDC 41 can manage the bad logical sector table in a cluster unit as a bad cluster table. The SSDC 41 manages, as the statistical information X02, the number of LBAs registered 30 in the bad logical sector table or the number of cluster addresses registered in the bad cluster table. The SSDC 41 can directly calculate the statistical information X02 from the bad logical sector table and the bad cluster table

without storing the statistical information X02 in the statistical information 65. A larger value of the statistical information X02 indicates that reliability is further deteriorated.

5 The total erase count (statistical information X03) is explained. The statistical information X03 indicates a cumulative value of the erase count of all blocks of the NAND memory 16 in the storage unit 2. The SSDC 41 increments the statistical information X03 by one every 10 time one physical block of the NAND memory 16 in the storage unit 2 is erased. It is desirable that the statistical information X03 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. The SSDC 41 can directly calculate the statistical 15 information X03 from the FBT 60, BBT 61, and the ABT 62 without storing the statistical information X03 in the statistical information 65. A larger value of the statistical information X03 indicates that reliability is further deteriorated.

20 The average erase count (the statistical information X04) is explained. The SSDC 41 calculates an average erase count per one block concerning all the blocks of the NAND memory 16 and stores the average erase count in the statistical information 65 as the statistical information 25 X04. The SSDC 41 can exclude, from a totalization target of the statistical information X04, a part of the blocks such as a block in which the management information 44 is stored. It is desirable that the statistical information X04 is reset to zero during manufacturing (e.g., before a 30 test process) of the storage unit 2. The SSDC 41 can directly calculate the statistical information X04 from the FBT 60, the BBT 61, and the ABT 62 without storing the statistical information X04 in the statistical information

65. The SSDC 41 can use a maximum value of the erase count or a minimum value of the erase count instead of the average erase count. A larger value of the statistical information X04 indicates that reliability is further

5 deteriorated.

The total program error count (the statistical information X05) of the NAND memory is explained. The SSDC 41 increments (or can increment in a block unit) the statistical information X05 by one every time a program

10 error occurs in one write unit in the NAND memory 16 in the storage unit 2. It is desirable that the statistical information X05 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X05 indicates that

15 reliability is further deteriorated.

The total erase error count of the NAND memory (the statistical information X06) is explained. It is desirable that the statistical information X06 is reset to zero during manufacturing (e.g., before a test process) of the

20 storage unit 2. The SSDC 41 increments the statistical information X06 by one every time an erase error occurs in one block in the NAND memory 16 in the storage unit 2. The SSDC 41 can collectively set a plurality of blocks as an erasing unit and increment the statistical information X06

25 by one every time an erase error occurs in one erasing unit. A larger value of the statistical information X06 indicates that reliability is further deteriorated.

The total read logical sector count (the statistical information X07) is explained. The SSDC 41 stores a

30 cumulative number of the numbers of logical sectors of data transmitted to the information processing device 111 as read data by the IFC 42 in the statistical information 65 as the statistical information X07. It is desirable that

the statistical information X07 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X07 indicates that reliability is further deteriorated.

5        The total written logical sector count (the statistical information X08) is explained. The SSDC 41 stores a total number of logical sectors of data received from the information processing device 111 as write data by the IFC 42 in the statistical information 65 as the 10 statistical information X08. It is desirable that the statistical information X08 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X08 indicates that reliability is further deteriorated.

15       The total uncorrectable ECC error count (the statistical information X09) is explained. When an error bit cannot be corrected by ECC correction, the SSDC 41 increments the statistical information X09 by 1 in every one read unit. The SSDC 41 can add an estimated value of 20 the number of error bits that cannot be corrected or can add the number of error blocks that cannot be corrected. It is desirable that the statistical information X09 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the 25 statistical information X09 indicates that reliability is further deteriorated.

30       The total retry read count (the statistical information X10) is explained. When the number of error bits is larger and error correction impossible (ECC error) during data read, it is desirable that the SSDC 41 executes error correction using the ECC again. In particular, when the SSDC 41 shifts the read levels VA1, VA2, VB2, and VC2 shown in Fig. 12 from default values and performs read,

data that cannot be error-corrected can be sometimes error-corrected. The SSDC 41 can store the total retry read count in the statistical information X09 as the statistical information X10 and use the total retry read count for life 5 end prediction and life end determination. It is desirable that the statistical information X10 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X10 indicates that reliability is further 10 deteriorated.

The corrected n bit-m bit ECC event count (the statistical information X11) is explained. In the corrected n bit-m bit ECC event count, n and m are natural numbers and  $0 \leq n \leq$  maximum number of correctable bits. When 15 the ECC correction is performed for an ECC correction unit (e.g., a physical page), if all error bits are normally corrected and the number of corrected error bits is equal to or larger than n and equal to or smaller than m, the SSDC 41 increments the corrected n bit-m bit ECC event 20 count by one for one ECC correction unit. If maximum 64 bits can be corrected per one correction unit by the ECC correction, for example, the SSDC 41 reserves eight parameters "corrected 1 bit-8 bit ECC event count", "corrected 9 bit-16 bit ECC event count", "corrected 17 25 bit-24 bit ECC event count", "corrected 25 bit-32 bit ECC event count", "corrected 33 bit-40 bit ECC event count", "corrected 41 bit-48 bit ECC event count", "corrected 49-bit-56 bit ECC event count", and "corrected 57 bit-64 bit ECC event count". If the ECC correction is normally 30 performed, the SSDC 41 increments any one of the eight parameters by 1 every time the EEC correction in one ECC correction unit is performed. It is desirable that the statistical information X11 is reset to zero during

manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X11 indicates that reliability is further deteriorated.

The data corruption error count of the interface 19 (the statistical information X12) is explained. The SSDC 41 increments the statistical information X12 by one every time data corruption of a signal is detected on the interface 19. Data transmitted and received on the interface 19 is subjected to error detection and error correction by the SSDC 41, the IFC 42, and the chip set 7 using, for example, a Cyclic Redundancy Check (CRC) code, a Bose-Chaudhuri-Hocquenghem (BCH) code, a Reed-Solomon (RS) code, a Low-Density Parity-Check (LDPC) code, and the like. When an error is detected or when the error correction cannot be performed, the SSDC 41 increments the statistical information X12 by one. For example, when the interface 19 is based on a SATA standard, the SSDC 41 increments the statistical information X12 by one every time an R error (Reception Error, R\_ERR) in the SATA standard occurs once. As the statistical information X12, any one of Phy Event Counters of the SATA standard can be adopted. It is desirable that the statistical information X12 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X12 indicates that reliability is further deteriorated.

The link speed down shift count of the interface 19 (the statistical information X13) is explained. When the SSDC 41, the IFC 42, and the chip set 7 detect that communication speed of the interface 19 decreases to be smaller than a design value, the SSDC 41 increments the statistical information X13 by one. For example, although the interface 19, the IFC 42, and the SSDC 41 are designed

at SATA communication speed of the maximum 6 Gbps, when it is detected that communication speed actually established between the interface 19, the IFC 42, and the SSDC 41 and the storage unit 2 and the information processing device 111 is lower communication speed such as 3 Gbps, the SSDC 41 regards this as an error in SATA communication and increments the statistical information X13 by one. For example, although the interface 19, the IFC 42, and the SSDC 41 are designed at Express communication speed of the maximum 8 Gbps, when it is detected that communication speed actually established between the interface 19, the IFC 42, and the SSDC 41 and the storage unit 2 and the information processing device 111 is lower communication speed such as 5 Gbps, the SSDC 41 regards this as an error in PCI Express communication and increments the statistical information X13 by one. It is desirable that the statistical information X13 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X13 indicates that reliability is further deteriorated.

The lane count down shift count of the interface 19 (the statistical information X14) is explained. When the SSDC 41, the IFC 42, and the chip set 7 detect that the number of active transmission lines of the interface 19 decreases to be smaller than a design value, the SSDC 41 increments the statistical information X14 by one. For example, although the interface 19, the IFC 42, and the SSDC 41 are designed at the number of PCI express transmission line (number of Lanes) of the maximum 8 Lanes, when it is detected that the number of transmission lines actually established between the interface 19, the IFC 42, and the SSDC 41 and the storage unit 2 and the information processing device 111 is a smaller number of transmission

lines such as 4 Lanes, the SSDC 41 regards this as an error in PCI Express communication and increments the statistical information X14 by one. It is desirable that the statistical information X14 is reset to zero during 5 manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X14 indicates that reliability is further deteriorated.

The error count of the interface 19 (the statistical information X15) is explained. Every time the SSDC 41, the 10 IFC 42, and the chip set 7 detect an other abnormality in the interface 19 (other than X12) once, the SSDC 41 increments the statistical information X15 by one. It is desirable that the statistical information X15 is reset to zero during manufacturing (e.g., before a test process) of 15 the storage unit 2. A larger value of the statistical information X15 indicates that reliability is further deteriorated.

The error count of the RAM 40 (the statistical information X16) is explained. When the SSDC 41 writes 20 data in the RAM 40, an ECC encoding unit or an error-detection-code creating unit of the SSDC 41 or the RAM 40 encodes the data and writes the data in the RAM 40. When the SSDC 41 reads data from the RAM 40, an ECC decoding unit or an error detecting unit of the SSDC 41 or the RAM 25 40 subjects the data to error correction or error detection and reads the data from the RAM 40. If the error correction cannot be performed or if an error is detected when the SSDC 41 reads data from the RAM 40, the SSDC 41 increments the statistical information X16 by one. It is 30 desirable that the statistical information X16 is reset to zero during manufacturing (e.g., before a test process) of the storage unit 2. A larger value of the statistical information X16 indicates that reliability is further

deteriorated.