(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7566397号

(P7566397)

(45)発行日 令和6年10月15日(2024.10.15)

(24)登録日 令和6年10月4日(2024.10.4)

(51)国際特許分類

|        |                  |        |       |         |

|--------|------------------|--------|-------|---------|

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78 | 3 0 1 G |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/78 | 3 0 1 B |

| H 01 L | 29/788 (2006.01) | H 01 L | 29/78 | 3 7 1   |

| H 01 L | 29/792 (2006.01) | H 01 L | 29/78 | 6 1 7 S |

| H 01 L | 29/786 (2006.01) | H 01 L | 29/78 | 6 1 7 T |

請求項の数 25 (全27頁) 最終頁に続く

(21)出願番号 特願2019-150490(P2019-150490)

(22)出願日 令和1年8月20日(2019.8.20)

(65)公開番号 特開2020-31213(P2020-31213A)

(43)公開日 令和2年2月27日(2020.2.27)

審査請求日 令和4年7月26日(2022.7.26)

(31)優先権主張番号 10-2018-0096828

(32)優先日 平成30年8月20日(2018.8.20)

(33)優先権主張国・地域又は機関

韓国(KR)

(31)優先権主張番号 10-2019-0008347

(32)優先日 平成31年1月22日(2019.1.22)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

(74)代理人 100133400

弁理士 阿部 達彦

(74)代理人 100110364

弁理士 実広 信哉

(74)代理人 100154922

最終頁に続く

(54)【発明の名称】 ロジックスイッチング素子及びその製造方法

## (57)【特許請求の範囲】

## 【請求項1】

チャネル要素と、

前記チャネル要素に連結されたソース及びドレインと、

前記チャネル要素に対向して配置されたゲート電極と、

前記チャネル要素と前記ゲート電極との間に配置されたドメインスイッチング層と、を含み、

前記ドメインスイッチング層は、ヒステリシス特性を有さず、強誘電ドメインを含む強誘電物質領域と、反強誘電ドメインを含む反強誘電物質領域と、を具備するロジックスイッチング素子。

## 【請求項2】

前記ドメインスイッチング層は、外部電場による分極の変化において、非ヒステリシス特性を有することを特徴とする請求項1に記載のロジックスイッチング素子。

## 【請求項3】

前記ドメインスイッチング層は、少なくとも1つの前記強誘電物質領域と、少なくとも1つの前記反強誘電物質領域とが、前記ゲート電極に平行な方向に配列された構造を有することを特徴とする請求項1または2に記載のロジックスイッチング素子。

## 【請求項4】

前記ドメインスイッチング層は、少なくとも1つの前記強誘電物質領域と、少なくとも1つの前記反強誘電物質領域とが、前記ゲート電極に垂直方向に配列された構造を有する

ことを特徴とする請求項 1 または 2 に記載のロジックスイッティング素子。

【請求項 5】

前記ドメインスイッティング層は、少なくとも 1 つの前記強誘電物質領域と、少なくとも 1 つの前記反強誘電物質領域とが、前記ゲート電極に平行な方向に配列された構造と、それに垂直方向に配列された構造との組み合わせを含むことを特徴とする請求項 1 または 2 に記載のロジックスイッティング素子。

【請求項 6】

前記強誘電物質領域と前記反強誘電物質領域は、同一ベース物質を含むが、互いに異なる結晶相を有することを特徴とする請求項 1 から 5 のいずれか一項に記載のロジックスイッティング素子。

10

【請求項 7】

前記強誘電物質領域は直方晶系結晶相を含み、前記反強誘電物質領域は正方晶系結晶相を含むことを特徴とする請求項 1 から 6 のいずれか一項に記載のロジックスイッティング素子。

【請求項 8】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング濃度を有することを特徴とする請求項 1 から 5 のいずれか一項に記載のロジックスイッティング素子。

【請求項 9】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング物質を含むことを特徴とする請求項 1 から 5 のいずれか一項に記載のロジックスイッティング素子。

20

【請求項 10】

前記強誘電物質領域及び前記反強誘電物質領域のうち少なくとも一つは、Hf系酸化物及びZr系酸化物のうち少なくとも一つを含むことを特徴とする請求項 1 から 9 のいずれか一項に記載のロジックスイッティング素子。

【請求項 11】

前記強誘電物質領域及び前記反強誘電物質領域のうち少なくとも一つは、ドーパントを含み、前記ドーパントは、Si、Al、Zr、Y、La、Gd、Sr及びHfのうち少なくとも一つを含むことを特徴とする請求項 1 から 10 のいずれか一項に記載のロジックスイッティング素子。

【請求項 12】

前記ドメインスイッティング層において、前記強誘電物質領域と前記反強誘電物質領域との体積比は、10:90ないし90:10の範囲であることを特徴とする請求項 1 から 11 のいずれか一項に記載のロジックスイッティング素子。

30

【請求項 13】

前記ドメインスイッティング層は、前記チャネル要素に直接接触していることを特徴とする請求項 1 から 12 のいずれか一項に記載のロジックスイッティング素子。

【請求項 14】

前記チャネル要素と前記ドメインスイッティング層との間に配置された絶縁層をさらに含むことを特徴とする請求項 1 から 12 のいずれか一項に記載のロジックスイッティング素子。

40

【請求項 15】

前記チャネル要素と前記ドメインスイッティング層との間に配置された絶縁層と、前記絶縁層と前記ドメインスイッティング層との間に配置された導電層と、をさらに含むことを特徴とする請求項 1 から 12 のいずれか一項に記載のロジックスイッティング素子。

【請求項 16】

前記チャネル要素は、Si、Ge、SiGe、III-V 族半導体、酸化物半導体、窒化物半導体、窒化酸化物半導体、二次元物質、量子点及び有機半導体のうち少なくとも一つを含むことを特徴とする請求項 1 から 15 のいずれか一項に記載のロジックスイッティング素子。

【請求項 17】

チャネル要素を含む基板を設ける段階と、

50

前記チャネル要素上に、非晶質薄膜を形成する段階と、

前記非晶質薄膜上に、導電性物質層を形成する段階と、

前記非晶質薄膜をアニーリングし、前記非晶質薄膜からドメインスイッチング層を形成する段階と、を含み、

前記ドメインスイッチング層は、ヒステリシス特性を有さず、強誘電ドメインを含む強誘電物質領域と、反強誘電ドメインを含む反強誘電物質領域と、を具備するように形成されるロジックスイッチング素子の製造方法。

【請求項 18】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なる結晶相を有することを特徴とする請求項 17 に記載のロジックスイッチング素子の製造方法。

10

【請求項 19】

前記強誘電物質領域は直方晶系結晶相を含み、前記反強誘電物質領域は正方晶系結晶相を含むことを特徴とする請求項 17 または 18 に記載のロジックスイッチング素子の製造方法。

【請求項 20】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング濃度を有することを特徴とする請求項 17 に記載のロジックスイッチング素子の製造方法。

【請求項 21】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング物質を含むことを特徴とする請求項 17 に記載のロジックスイッチング素子の製造方法。

20

【請求項 22】

前記強誘電物質領域及び前記反強誘電物質領域のうち少なくとも一つは、Hf系酸化物及びZr系酸化物のうち少なくとも一つを含むことを特徴とする請求項 17 から 21 のいずれか一項に記載のロジックスイッチング素子の製造方法。

【請求項 23】

前記アニーリングは、400 ないし 1,200 の温度で行うことを特徴とする請求項 17 から 22 のいずれか一項に記載のロジックスイッチング素子の製造方法。

【請求項 24】

前記導電性物質層からゲート電極を形成する段階をさらに含むことを特徴とする請求項 17 から 23 のいずれか一項に記載のロジックスイッチング素子の製造方法。

30

【請求項 25】

前記チャネル要素に連結されたソース及びドレインを形成する段階をさらに含むことを特徴とする請求項 17 から 24 のいずれか一項に記載のロジックスイッチング素子の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ロジックスイッチング素子及びその製造方法に関する。

【背景技術】

【0002】

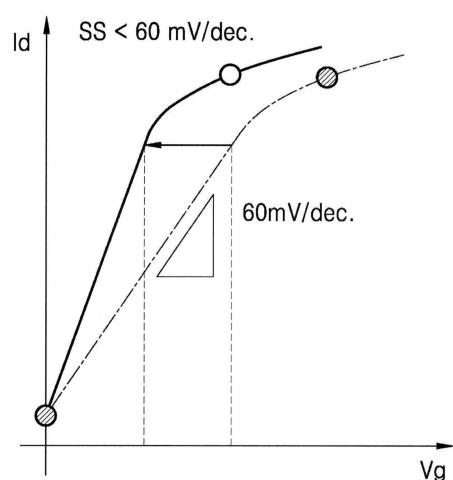

既存シリコン基板のトランジスタは、動作特性の改善、及びスケールダウン ( scaling down ) に限界がある。例えば、既存シリコン基板のトランジスタにおいて、動作電圧及び電流特性を測定すれば、サブレショルドスイング ( SS : sub threshold swing ) ( SS ) 値は、下記式 1 のように与えられるが、SS 値は、約 60 mV / dec が限界であると知られている。

40

【0003】

【数1】

50

$$SS = \frac{k_B T}{q} \ln(10) \left( 1 + \frac{C_D}{C_{ins}} \right)$$

## 【0004】

ここで、 $k_B$  はボルツマン定数 (Boltzmann constant) であり、 $T$  は絶対温度 (absolute temperature) であり、 $q$  は電荷素量 (elementary charge) であり、 $C_D$  は空乏層 (depletion layer) のキャパシタンスであり、 $C_{ins}$  はゲート絶縁体 (gate insulator) のキャパシタンスである。

## 【0005】

トランジスタのサイズが小さくなるにつれ、動作電圧を約 0.8 V 以下に低くし難い要因により、パワー密度 (power density) は増大している。従って、素子のスケールダウンに限界がある。サブスレショルドスイング (SS) のような動作特性を改善させることができ、スケールダウンに有利であり、制御効率を高めることができるとの開発が要求される。

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

本発明が解決しようとする課題は、ネガティブキャパシタンス (negative capacitance) 効果を利用したロジックスイッチング素子を提供し、強誘電 (ferroelectric) 物質及び反強誘電 (anti-ferroelectric) 物質を利用するロジックスイッチング素子を提供し、サブスレショルドスイング (SS) のような動作特性を改善させることができ、制御効率を高めることができ、スケールダウンに有利なロジックスイッチング素子を提供し、前述のロジックスイッチング素子の製造方法を提供することである。

## 【課題を解決するための手段】

## 【0007】

一側面によれば、チャネル要素と、前記チャネル要素に連結されたソース及びドレンと、前記チャネル要素に対向して配置されたゲート電極と、前記チャネル要素と前記ゲート電極との間に配置されたドメインスイッチング層 (domain switching layer) と、を含み、前記ドメインスイッチング層は、非メモリ (non-memor y) 要素であり、強誘電ドメインを含む強誘電 (ferroelectric) 物質領域と、反強誘電ドメインを含む反強誘電 (anti-ferroelectric) 物質領域と、を具備するロジックスイッチング素子が提供される。

## 【0008】

前記ドメインスイッチング層は、外部電場による分極の変化において、非履歴 (non-hysteresis) 挙動特性を有することができる。

## 【0009】

前記ドメインスイッチング層は、少なくとも 1 つの前記強誘電物質領域と、少なくとも 1 つの前記反強誘電物質領域とが、前記ゲート電極に平行な方向に配列された構造を有することができる。

## 【0010】

前記ドメインスイッチング層は、少なくとも 1 つの前記強誘電物質領域と、少なくとも 1 つの前記反強誘電物質領域とが、前記ゲート電極に垂直方向に配列された構造を有することができる。

## 【0011】

前記ドメインスイッチング層は、少なくとも 1 つの前記強誘電物質領域と、少なくとも 1 つの前記反強誘電物質領域とが、前記ゲート電極に平行な方向に配列された構造と、そ

10

20

30

40

50

れに垂直方向に配列された構造との組み合わせを含んでもよい。

【0012】

前記強誘電物質領域と前記反強誘電物質領域は、同一ベース物質を含み、互いに異なる結晶相を有することができる。

【0013】

前記強誘電物質領域は、直方晶系 (orthorhombic) 結晶相を含み、前記反強誘電物質領域は、正方晶系 (tetragonal) 結晶相を含んでもよい。

【0014】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング濃度を有することができる。

10

【0015】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング物質を含んでもよい。

【0016】

前記強誘電物質領域及び前記反強誘電物質領域のうち少なくとも一つは、Hf系酸化物及びZr系酸化物のうち少なくとも一つを含んでもよい。

20

【0017】

前記強誘電物質領域及び前記反強誘電物質領域のうち少なくとも一つは、ドーパント (dopant) を含み、前記ドーパントは、Si、Al、Zr、Y、La、Gd、Sr及びHfのうち少なくとも一つを含んでもよい。

【0018】

前記ドメインスイッチング層において、前記強誘電物質領域と前記反強誘電物質領域との体積比は、約10:90ないし約90:10の範囲である。

【0019】

前記ドメインスイッチング層は、前記チャネル要素に直接接触されてもよい。

【0020】

前記チャネル要素と前記ドメインスイッチング層との間に配置された絶縁層をさらに含んでもよい。

【0021】

前記チャネル要素と前記ドメインスイッチング層との間に配置された絶縁層と、前記絶縁層と前記ドメインスイッチング層との間に配置された導電層と、をさらに含んでもよい。

30

【0022】

前記チャネル要素は、Si、Ge、SiGe、III-V族半導体、酸化物半導体、窒化物半導体、窒化酸化物半導体、二次元物質 (2D material)、量子点 (quantum dot) 及び有機半導体のうち少なくとも一つを含んでもよい。

40

【0023】

他の側面によれば、チャネル要素を含む基板を設ける段階と、前記チャネル要素上に、非晶質薄膜を形成する段階と、前記非晶質薄膜上に、導電性物質層を形成する段階と、前記非晶質薄膜をアニーリング (annealing) し、前記非晶質薄膜からドメインスイッチング層を形成する段階と、を含み、前記ドメインスイッチング層は、非メモリ要素であり、強誘電ドメインを含む強誘電物質領域と、反強誘電ドメインを含む反強誘電物質領域と、を具備するように形成されるロジックスイッチング素子の製造方法が提供される。

【0024】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なる結晶相を有することができる。

【0025】

前記強誘電物質領域は、直方晶系結晶相を含み、前記反強誘電物質領域は、正方晶系結晶相を含んでもよい。

【0026】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング濃度を有する

50

ことができる。

【0027】

前記強誘電物質領域と前記反強誘電物質領域は、互いに異なるドーピング物質を含んでもよい。

【0028】

前記強誘電物質領域及び前記反強誘電物質領域のうち少なくとも一つは、Hf系酸化物及びZr系酸化物のうち少なくとも一つを含んでもよい。

【0029】

前記アニーリングは、約400ないし約1,200の温度で行うことができる。

【0030】

前記製造方法は、前記導電性物質層からゲート電極を形成する段階をさらに含んでもよい。

【0031】

前記製造方法は、前記チャネル要素に連結されたソース及びドレインを形成する段階をさらに含んでもよい。

【発明の効果】

【0032】

本発明によれば、ネガティブキャパシタンス効果を利用するロジックスイッチング素子を具現することができ、強誘電物質及び反強誘電物質をいずれも適用したロジックスイッチング素子を具現することができ、サブスレショルドスイング(SS)のような動作特性を改善させることができ、制御効率を高めることができ、スケールダウンにも有利なロジックスイッチング素子を具現することができ、前記ロジックスイッチング素子を利用し、多様な電子素子/装置/回路/システムを具現することができる。

【図面の簡単な説明】

【0033】

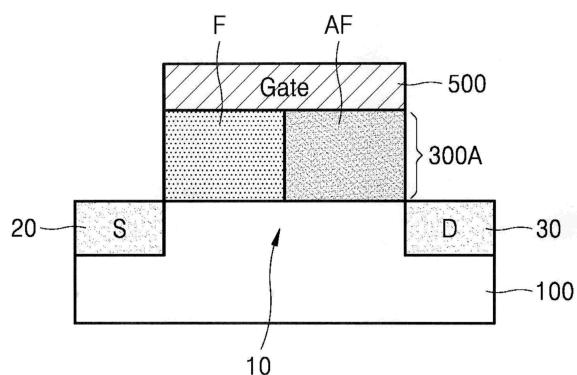

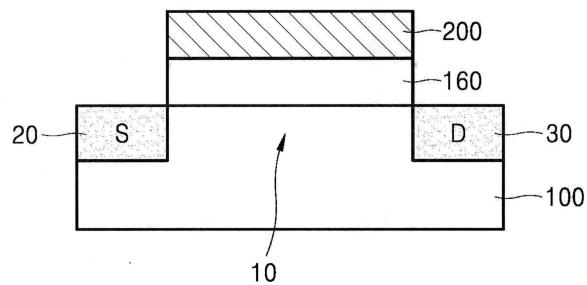

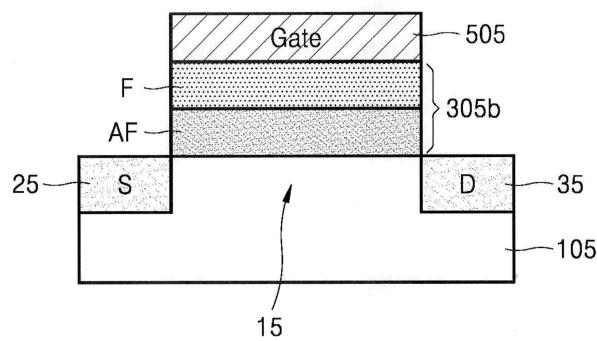

【図1】一実施形態によるロジックスイッチング素子を示す断面図である。

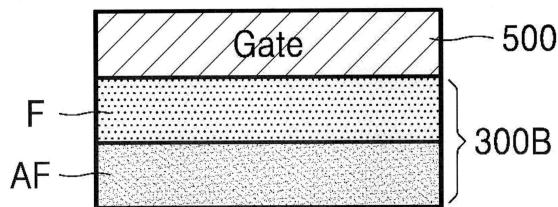

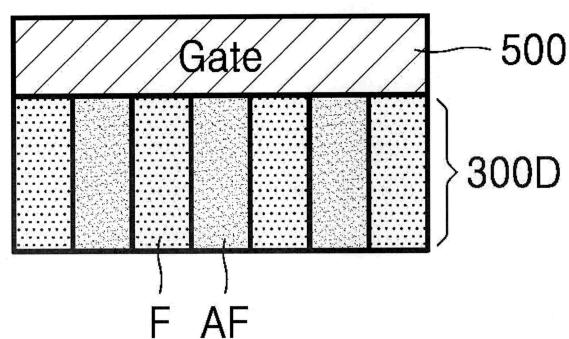

【図2】他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

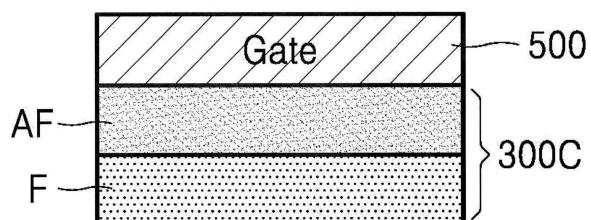

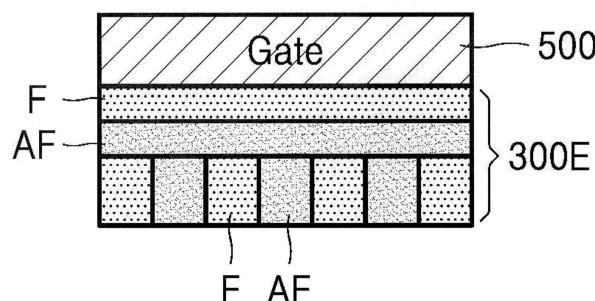

【図3】他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

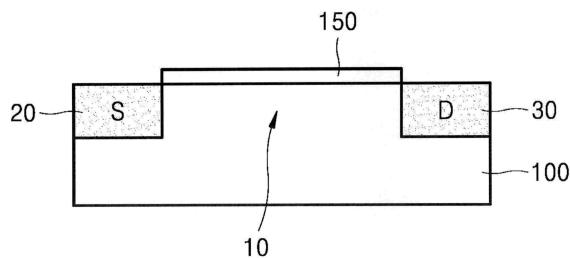

【図4】他の実施形態によるロジックスイッチング素子のドメインスイッチング層下にも適用される下部構造を示す断面図である。

【図5】他の実施形態によるロジックスイッチング素子のドメインスイッチング層下にも適用される下部構造を示す断面図である。

【図6】他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

【図7】他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

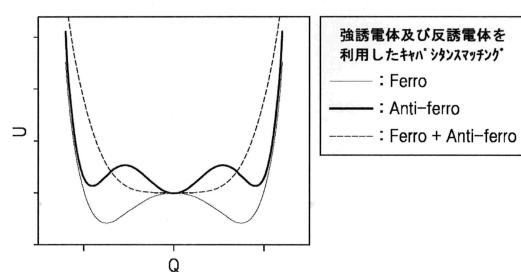

【図8】一実施形態によるものであり、ドメインスイッチング層構成において、強誘電体及び反強誘電体を利用したキャパシタンスマッチング(capacitance matching)を例示的に示すグラフである。

【図9】比較例による素子の構成を示す断面図である。

【図10】比較例によるものであり、強誘電体と誘電体とを利用したキャパシタンスマッチングを示すグラフである。

【図11A】強誘電体の特性を示すグラフである。

【図11B】強誘電体の特性を示すグラフである。

【図12A】反強誘電体の特性を示すグラフである。

【図12B】反強誘電体の特性を示すグラフである。

【図13A】強誘電体と反強誘電体との組み合わせの特性を示すグラフである。

【図13B】強誘電体と反強誘電体との組み合わせの特性を示すグラフである。

10

20

30

40

50

【図14A】誘電体の特性を示すグラフである。

【図14B】誘電体の特性を示すグラフである。

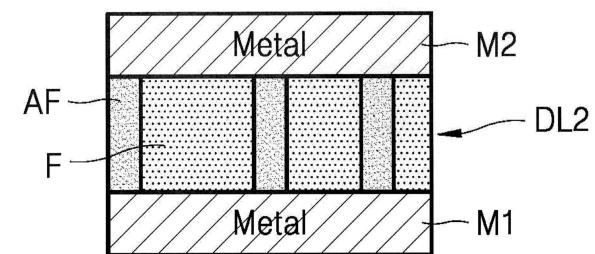

【図15】一実施形態によるものであり、金属 / HfZrO層 / 金属構造において、HfZrO層の構成 / 物性による誘電定数 (dielectric constant)・電圧特性を測定した結果を示すグラフである。

【図16】一実施形態によるものであり、図15で説明した金属 / HfZrO層 / 金属構造において、分極 (polarization)・電圧特性を測定した結果を示すグラフである。

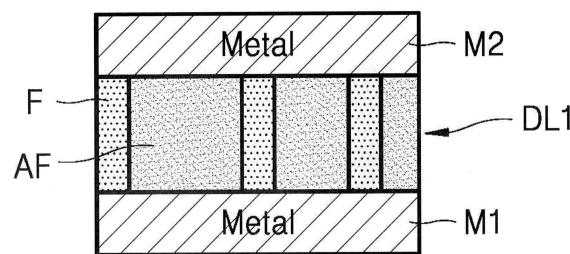

【図17A】反強誘電ドミナント (anti-ferroelectric dominant) である場合のドメイン層DL1の構成 (ドメイン配列) を例示的に示す断面図である。

【図17B】強誘電ドミナント (ferroelectric dominant) である場合のドメイン層DL2の構成 (ドメイン配列) を例示的に示す断面図である。

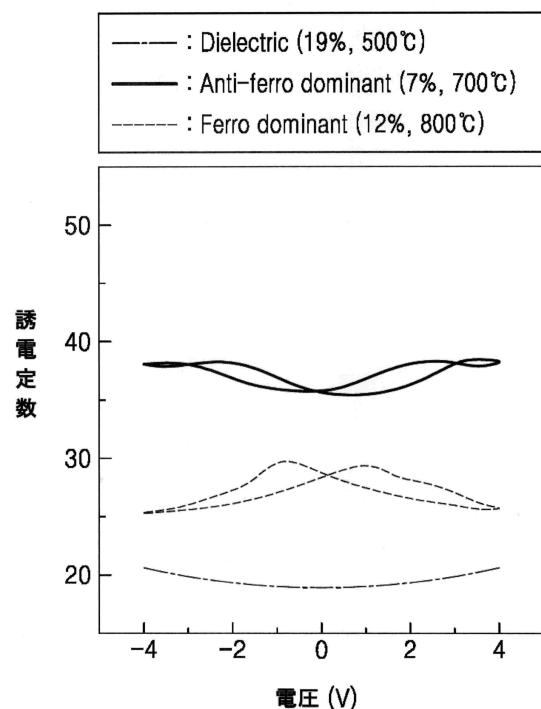

【図18】一実施形態によって製造したAl : HfO薄膜の構成 / 物性による誘電定数・電圧特性を測定した結果を示すグラフである。

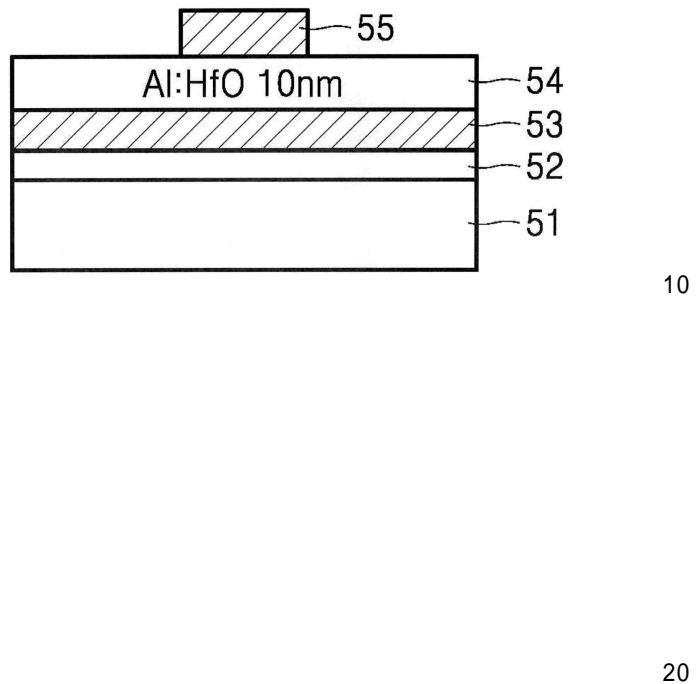

【図19】図18の結果を得るのに使用した素子の構造を示す断面図である。

【図20】一実施形態によるロジックスイッチング素子のサブスレショルドスイング (SS : sub threshold swing) 特性が改善される効果について説明するためのグラフである。

【図21】他の実施形態によるロジックスイッチング素子を示す断面図である。

【図22A】一実施形態によるロジックスイッチング素子の製造方法を示す断面図である。

【図22B】一実施形態によるロジックスイッチング素子の製造方法を示す断面図である。

【図22C】一実施形態によるロジックスイッチング素子の製造方法を示す断面図である。

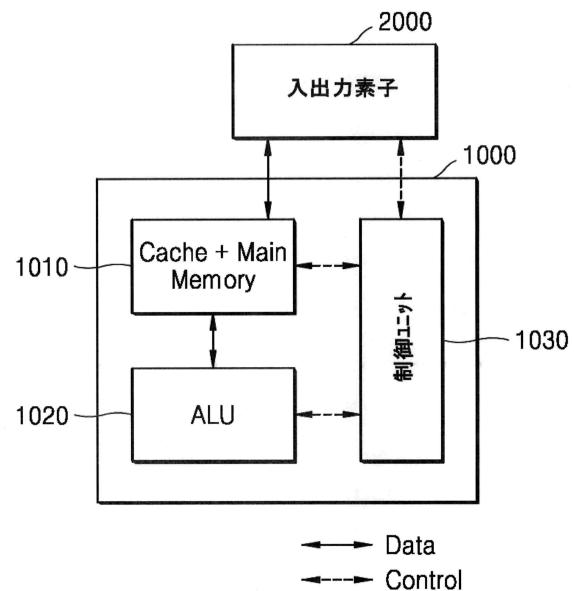

【図23】一実施形態による電子素子のアーキテクチャを概略的に示す概念図である。

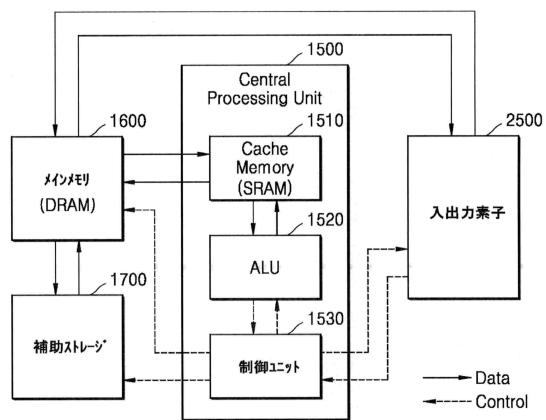

【図24】他の実施形態による電子素子のアーキテクチャを概略的に示す概念図である。

【発明を実施するための形態】

【0034】

以下、本実施形態によるロジックスイッチング素子及びその製造方法について、添付された図面を参照し、詳細に説明する。添付された図面に図示された層や領域の幅及び厚みは、明細書の明確性、及び説明の便宜性のために若干誇張されている。詳細な説明全体にわたり、同一参照番号は同一構成要素を示す。

【0035】

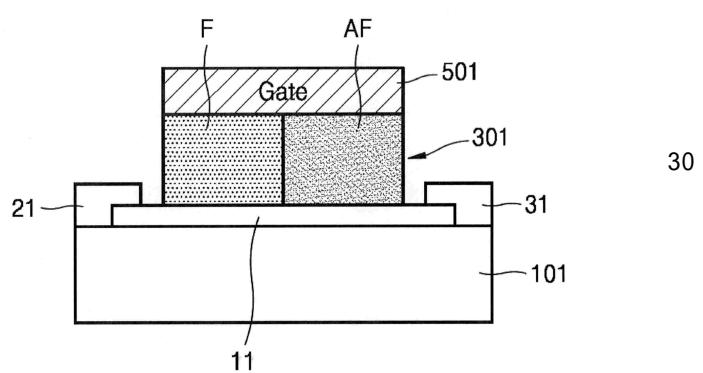

図1は、一実施形態によるロジックスイッチング素子を示す断面図である。ここで、該ロジックスイッチング素子は、ロジックトランジスタでもある。「ロジックスイッチング素子」という用語は、メモリ素子 (メモリトランジスタ) と対比される概念であり、非メモリ用のオン / オフ用スイッチング素子を意味する。

【0036】

図1を参照すれば、チャネル要素10が具備され、チャネル要素10に電気的に連結されたソース20及びドレイン30が具備されてもよい。ソース20は、チャネル要素10の第1領域にも、電気的に連結 / 接触し、ドレイン30は、チャネル要素10の第2領域に電気的に連結 / 接触されてもよい。チャネル要素10、ソース20及びドレイン30は、所定基板100内にも具備される。基板100の互いに異なる領域に不純物を注入し、ソース20及びドレイン30を形成することができ、ソース20とドレイン30との間の基板100領域が、チャネル要素 (チャネル領域) 10とも定義される。基板100は、例えば、Si基板もあるが、Si以外の他の物質、例えば、Ge、SiGe、III-V族半導体などを含む基板もある。その場合、チャネル要素10は、Si、Ge、SiGeまたはIII-V族半導体を含んでもよい。基板100の物質は、前述のものに限定されるものではなく、多様に変化される。また、チャネル要素10は、基板100の一部ではない基板100と別個の物質層 (薄膜) によっても具備される。その場合、チャネル要素10の物質構成は、多様である。例えば、チャネル要素10は、酸化物半導体、窒

10

20

30

40

50

化物半導体、窒化酸化物半導体、二次元物質（2D（two-dimensional material）、量子点（QD：quantum dot）及び有機半導体のうち少なくとも一つを含んでもよい。前記酸化物半導体は、例えば、InGaZnOなどを含み、前記二次元物質は、例えば、TMD（transition metal dichalcogenide）やグラフェンを含み、前記量子点は、コロイダル量子点（colloidal QD）、ナノ結晶（nanocrystal）構造などを含んでもよいが、それらは、例示的なものに過ぎず、本願実施形態は、それらに限定されるものではない。

#### 【0037】

チャネル要素10に対向するように配置されたゲート電極（gate）500が具備されてもよい。ゲート電極500は、ソース20とドレイン30との間ににおいて、チャネル要素10と離隔されるようにも具備される。チャネル要素10とゲート電極500との間に、ドメインスイッチング層（domain switching layer）300Aが具備されてもよい。ドメインスイッチング層300Aは、非メモリ（non-memor）要素である。ドメインスイッチング層300Aは、強誘電（ferroelectric）ドメインを含む強誘電物質領域Fと、反強誘電ドメイン（anti-ferroelectric）を含む反強誘電物質領域AFを具備することができる。強誘電物質領域Fと反強誘電物質領域AFとの組み合わせにより、ドメインスイッチング層300Aは、外部電場による分極（polarization）変化において、実質的に非履歴（non-hysteresis）挙動特性を有することができる。言い換えれば、ドメインスイッチング層300Aは、ヒステリシス（hysteresis）特性を有さないか、あるいは実質的に有さない。

#### 【0038】

強誘電物質は、結晶化された物質構造において、単位セル（unit cell）内電荷分布が中心対称的ではなく（non-centrosymmetric）、自発的な双極子（dipole）（electric dipole）、すなわち、自発分極（spontaneous polarization）を有する。該強誘電物質は、外部電場がない状態でも、双極子（dipole）による残留分極（remnant polarization）を有する。同時に、外部電場により、分極方向がドメイン単位において変わる（switch）。

反強誘電物質は、電気双極子（dipole）のアレイを含んでもよいが、残留分極が0であるか、あるいは0に近い。電場がない状態において、隣接双極子（dipole）の方向が反対になり、分極が相殺されるので、全体的な自発分極及び残留分極は、0であるか、あるいは0に近い。しかし、外部電場が印加された状態においては、分極特性及びスイッチング特性を示すことができる。

#### 【0039】

本実施形態においては、相互接触した少なくとも1つの強誘電物質領域Fと、少なくとも1つの反強誘電物質領域AFとの組み合わせを利用し、キャパシタンスマッチング（capacitance matching）を行うことにより、ドメインスイッチング層300Aがヒステリシス特性を有さないようにすることができる。従って、強誘電物質領域Fと反強誘電物質領域AFとのそれぞれにおいて、ドメインスイッチングが起こり、ドメインスイッチング時に生じる電圧増幅（voltage amplification）により、ロジクスイッチング素子（ロジックトランジスタ）のスイッチング特性を改善させることができる。特に、ロジクスイッチング素子（ロジックトランジスタ）のサブスレショルドスイング（SS：sub threshold swing）値をさらに低くする効果を得ることができる。また、ドメインスイッチング層300Aは、非履歴挙動特性を有するために、メモリではないオン／オフ特性を有する優秀なスイッチング素子を得ることができる。

#### 【0040】

さらに、図1の実施形態において、ドメインスイッチング層300Aは、チャネル要素10に直接接触することができる。その場合、チャネル要素10とドメインスイッチング

10

20

20

30

40

50

層 300A との間に別途の誘電体層を使用せず、誘電定数が低い誘電体層による特性低下を防止することができる。

#### 【0041】

図1においては、ドメインスイッチング層300Aの強誘電物質領域Fと反強誘電物質領域AFとがゲート電極500に平行な方向に配列された、すなわち、横に(1ater a11y)配列された構造を有する場合を図示したが、他の実施形態によれば、強誘電物質領域Fと反強誘電物質領域AFは、ゲート電極500に垂直方向、すなわち、上下に配列された構造を有することができる。その例が、図2及び図3に図示されている。

#### 【0042】

図2及び図3は、他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

10

#### 【0043】

図2及び図3を参照すれば、ドメインスイッチング層300B, 300Cは、少なくとも1つの強誘電物質領域Fと、少なくとも1つの反強誘電物質領域AFとがゲート電極500に垂直方向に配列された構造を有することができる。図2においては、強誘電物質領域Fがゲート電極500に接触し、強誘電物質領域F下に、反強誘電物質領域AFが具備される。図3においては、反強誘電物質領域AFがゲート電極500に接触し、反強誘電物質領域AF下に、強誘電物質領域Fが具備される。図2及び図3のドメインスイッチング層300B, 300Cを、図1のドメインスイッチング層300Aの代わりに適用することができる。図2及び図3の構造においても、強誘電物質領域Fと反強誘電物質領域AFとの組み合わせにより、キャパシタンスマッチングされることにより、ドメインスイッチング層300B, 300Cは、ヒステリシス特性を有さないことになる。

20

#### 【0044】

図1においては、ドメインスイッチング層300Aが、チャネル要素10に直接接触する場合を図示して説明したが、ドメインスイッチング層300A下に配置される下部構造は、異なってもよい。その例が、図4及び図5に図示されている。

#### 【0045】

図4は、他の実施形態によるロジックスイッチング素子のドメインスイッチング層下に適用される下部構造を示す断面図である。

30

#### 【0046】

図4を参照すれば、チャネル要素10上に、絶縁層150が具備されてもよい。絶縁層150上に、図1ないし図3のドメインスイッチング層300A, 300B, 300C及びゲート電極500が配置されてもよい。絶縁層150の厚みは、約5nm以下または約3nm以下と薄い。しかし、絶縁層150の厚みは、前述のところに限定されるものではなく、5nm以上であってもよい。絶縁層150としては、例えば、Si酸化物、Al酸化物、Hf酸化物、Zr酸化物などを適用するか、あるいはh-BN(hexagonal boron nitride)のような二次元絶縁体(2D insulator)を使用することができる。しかし、絶縁層150の物質は、それらに限定されるものではなく、異なってもよい。強誘電物質領域F及び反強誘電物質領域AFを使用し、キャパシタンスマッチングを行うために、絶縁層150において、比較的誘電定数が高い誘電体を適用しやすい。絶縁層150の誘電定数が高いほど、スイッチング素子の性能向上に有利である。また、絶縁層150を使用すれば、電気的漏れ( leakage )を抑制したり防止したりする効果を得ることができる。

40

#### 【0047】

図5は、他の実施形態によるロジックスイッチング素子のドメインスイッチング層下にも適用される下部構造を示す断面図である。

#### 【0048】

図5を参照すれば、チャネル要素10上に、絶縁層160が具備され、絶縁層160上に、導電層200がさらに具備されてもよい。導電層200上に、図1ないし図3のドメインスイッチング層300A, 300B, 300C及びゲート電極500が配置されても

50

よい。絶縁層 160 の物質は、図 4 の絶縁層 150 と同一であるか、あるいは類似している。導電層 200 は、金属や金属化合物によつても形成される。導電層 200 は、フローティング電極 (floating electrode) であつてもよく、ドメインスイッチング層 300A, 300B, 300C の製造工程や特性制御に関与することができる。絶縁層 160 は、チャネル要素 10 と導電層 200 とを絶縁する役割を行うことができ、例えは、約 10 nm 以上の厚みを有することができる。

#### 【0049】

図 1 においては、ドメインスイッチング層 300A が、1 つの強誘電物質領域 F と、1 つの反強誘電物質領域 AF とから構成された場合を図示したが、他の実施形態によれば、複数の強誘電物質領域 F と、複数の反強誘電物質領域 AF とが、1 つのドメインスイッチング層を構成することができる。その一例が、図 6 に図示されている。

10

#### 【0050】

図 6 は、他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

#### 【0051】

図 6 を参照すれば、ドメインスイッチング層 300D は、複数の強誘電物質領域 F と、複数の反強誘電物質領域 AF とが、水平方向 (横) に相互に配置された構造を有することができる。強誘電物質領域 F と反強誘電物質領域 AF との比率及びサイズは、例示的なものであり、異なつてもよい。

20

#### 【0052】

他の実施形態によれば、ドメインスイッチング層は、少なくとも 1 つの前記強誘電物質領域と、少なくとも 1 つの前記反強誘電物質領域とが、ゲート電極に平行な方向に配列された構造と、ゲート電極に垂直方向に配列された構造との組み合わせを含んでもよい。その一例が、図 7 に図示されている。

#### 【0053】

図 7 は、他の実施形態によるロジックスイッチング素子に適用することができるドメインスイッチング層及びゲート電極の積層構造を示す断面図である。

#### 【0054】

図 7 を参照すれば、ドメインスイッチング層 300E は、複数の強誘電物質領域 F と、複数の反強誘電物質領域 AF とが水平方向 (横) に配列された構造、及び垂直方向 (上下) に配列された構造の組み合わせを含んでもよい。製造工程の条件により、そのような組み合わせ配列が形成されてもよい。しかし、図 7 の構造は、例示的なものであり、それは多様に変化されもする。

30

#### 【0055】

以上の実施形態において、強誘電物質領域 F と反強誘電物質領域 AF は、同一ベース物質を含むが、互いに異なる結晶相 (crystalline phase) を有することができる。強誘電物質領域 F と反強誘電物質領域 AF は、同一系列の物質で構成されながら、互いに異なる結晶相を有することにより、一方 (F) は、強誘電特性を示し、他方 (AF) は、反強誘電特性を示すことができる。例えは、強誘電物質領域 F は、直方晶系 (orthorhombic) 結晶相を有することができ、反強誘電物質領域 AF は、正方晶系 (tetragonal) 結晶相を有することができる。例えは、強誘電物質領域 F 及び反強誘電物質領域 AF は、Hf 系酸化物または Zr 系酸化物を含んでもよい。一例として、HfO<sub>2</sub> 系の非晶質薄膜を形成した後、アニーリング (annealing) (熱処理) 制御を介して、その一部は、直方晶系結晶相を有する強誘電物質領域 F にし、他の一部は、正方晶系結晶相を有する反強誘電物質領域 AF にする。

40

#### 【0056】

アニーリング (熱処理) 制御だけではなく、ドーピング濃度やドーピング物質を異なるように制御することにより、強誘電物質領域 F と反強誘電物質領域 AF とを形成することができる。例えは、HfO<sub>2</sub> 系の非晶質薄膜の一部は、第 1 ドーピング濃度を有し、他の一部は、第 2 ドーピング濃度を有することができ、それらを所定条件でアニーリング (熱処

50

理)することにより、前記第1ドーピング濃度を有する領域は、強誘電物質領域Fにし、前記第2ドーピング濃度を有する領域は、反強誘電物質領域A Fにすることができる。ドーピング濃度の代わりに、ドーピング物質を異ならせることによっても、そのような効果を得ることができる。従って、場合により、強誘電物質領域Fと反強誘電物質領域A Fは、互いに異なるドーピング濃度を有することができ、かつ/または互いに異なるドーピング物質を含んでもよい。強誘電物質領域F及び反強誘電物質領域A Fのうち少なくとも一つがドーパントを含む場合、前記ドーパントは、Si、Al、Zr、Y、La、Gd、Sr及びHfのうち少なくとも一つを含んでもよい。

#### 【0057】

他の実施形態の場合、強誘電物質領域Fのベース物質と、反強誘電物質領域A Fのベース物質とが、互いに異なってもよい。

10

#### 【0058】

以上の実施形態において、ドメインスイッチング層300A~300Eの強誘電物質領域Fと反強誘電物質領域A Fとの体積比(vol%)は、約0.1:99.9ないし99.9:0.1の範囲内でも決定される。例えば、ドメインスイッチング層300A~300Eの強誘電物質領域Fと反強誘電物質領域A Fとの体積比(vol%)は、約10:90ないし90:10ほどの範囲でも決定される。ドメインスイッチング層300A~300Eがヒステリシス特性を有さないか、あるいは実質的に有さない条件を満足するよう、前記体積比が決定されてもよい。

#### 【0059】

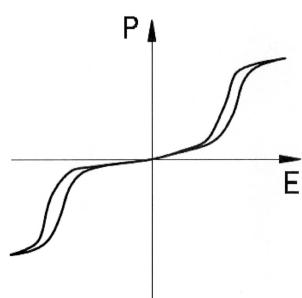

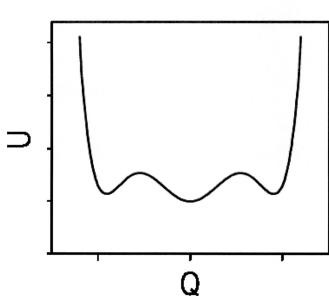

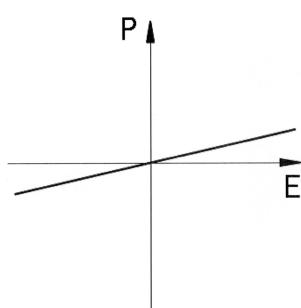

図8は、一実施形態によるものであり、ドメインスイッチング層構成において、強誘電体と反強誘電体とを利用したキャパシタンスマッチングを例示的に示すグラフである。図8においてX軸は、当該物質の電荷(charge)(Q)を示し、Y軸は、当該物質のエネルギー(energy)(U)を示す。

20

#### 【0060】

図8を参照すれば、強誘電体(ferrro)のグラフは、左右両側にウェル形態を有する。2つのウェル形態は、2つの安定した分極状態に対応するものであり、そのようなグラフ形態は、ヒステリシス挙動を意味する。2つのウェル間の転移部(transition region)に、ネガティブキャパシタンス(negative capacitance)を有する地点が存在する。本実施形態による素子は、強誘電体を含み、強誘電体のネガティブキャパシタンス効果を利用するため、そのような側面において、ネガティブキャパシタンス効果を利用したロジックスイッチング素子であるとされる。

30

#### 【0061】

反強誘電体(anti-ferrro)のグラフは、強誘電体(ferrro)のグラフと異なる屈曲を有する。強誘電体と反強誘電体とを適切に混合してデザインする場合、強誘電体と反強誘電体との組み合わせ(ferrro+anti-ferrro)は、2つのウェルを有する形態ではないU字形のグラフになり、実質的にヒステリシス挙動を示さない。言い換えれば、強誘電体と反強誘電体とを利用したキャパシタンスマッチングを介して、ヒステリシスのない結果を得ることができる。

#### 【0062】

このとき、ドメインスイッチング層がチャネル領域に接触する場合、該チャネル領域のキャパシタンスも考慮し、前述のキャパシタンスマッチングを行うことができる。また、前述のキャパシタンスマッチングは、チャネル領域と、ソース及びドレインとの間の寄生キャパシタンスまで考慮して行うこともできる。また、ドメインスイッチング層が、その下の絶縁層(誘電体層)に接触する場合、絶縁層(誘電体層)のキャパシタンスも考慮し、前述のキャパシタンスマッチングを行うことができる。結果として、ドメインスイッチング層は、キャパシタンスマッチングにより、ヒステリシスを有さない。

40

#### 【0063】

ドメインスイッチング層がチャネル領域に接触し、チャネル領域のキャパシタンスも考慮し、前記キャパシタンスマッチングを行った場合、ドメインスイッチング層とチャネル

50

領域との組み合わせがヒステリシスを有さないとされる。または、ドメインスイッチング層とチャネル領域とが接触した状態で、ドメインスイッチング層がヒステリシスを有さないとされる。それと類似し、ドメインスイッチング層が絶縁層（誘電体層）に接触し、絶縁層（誘電体層）のキャパシタンスも考慮し、前記キャパシタンスマッチングを行った場合、ドメインスイッチング層と絶縁層（誘電体層）との組み合わせが、ヒステリシスを有さないとされる。または、ドメインスイッチング層と絶縁層（誘電体層）とが接触した状態で、ドメインスイッチング層がヒステリシスを有さないとされる。

#### 【0064】

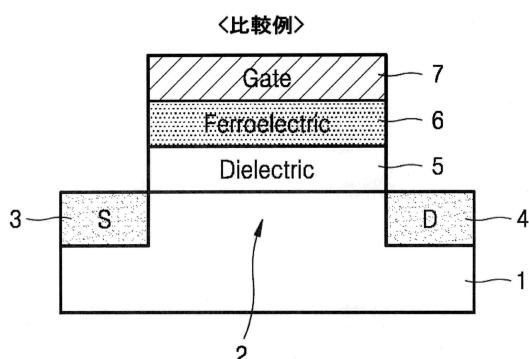

図9は、比較例による素子の構成を示す断面図である。

図9を参照すれば、基板1に、チャネル要素2、ソース3及びドレイン4が具備されてもよい。チャネル要素2上に、誘電体層(dielectric)5が配置され、誘電体層5上に、強誘電体層(ferroelectric)6が配置され、強誘電体層6上に、ゲート電極7が配置されてもよい。チャネル要素2とゲート電極7との間に、強誘電体層6が具備され、強誘電体層6とチャネル要素2との間に、誘電体層5が具備される。本比較例は、強誘電体層6と誘電体層5とを利用し、キャパシタンスマッチングを行う場合である。

#### 【0065】

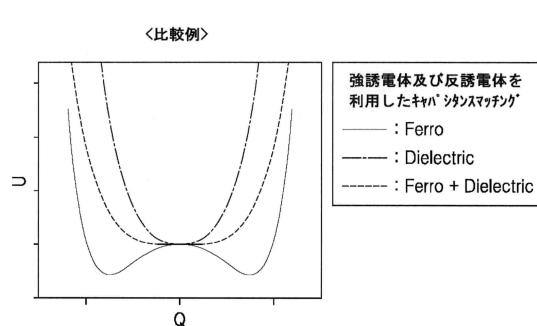

図10は、比較例によるものであり、強誘電体と誘電体とを利用したキャパシタンスマッチングを示すグラフである。

図10を参照すれば、強誘電体(ferro)は、図8を参照して説明したようなグラフ形態を有する。誘電体(dielectric)は、比較的幅が狭いU字形グラフ形態を有する。強誘電体と誘電体とが組み合わされた場合(ferro+dielectric)には、キャパシタンスマッチングによってヒステリシスが消え、比較的幅が広いU字形グラフ形態を示す。

#### 【0066】

しかし、図10の比較例のように、強誘電体と誘電体とを利用してキャパシタンスマッチングを行う場合には、誘電定数が低い誘電体を使用するために、ゲート効率が落ちるという問題が生じてしまう。本実施形態においては、誘電定数が低い誘電体の使用を排除することができるため、それに係わる問題を解消することができる。例えば、本実施形態において、ドメインスイッチング層に適用されるHfZrOの誘電定数と、比較例において誘電体として使用されるSiO<sub>2</sub>の誘電定数は、約50対4ほどと大きな差がある。また、該誘電体は、強誘電ドメイン(ferroelectric domain)がない状態であり、ゲート電圧動作時、ドメインスイッチングがないが、本願の実施形態で使用する反強誘電体は、ドメインスイッチング特性を有するために、スイッチング時に生じる電圧増幅により、スイッチング素子のサブスレショルドスイング(SS)値がさらに低くなる効果を得ることができる。従って、反強誘電体と強誘電体との組み合わせにより、ドメインスイッチング効果を極大化させながら、キャパシタンスマッチングを介して、ヒステリシスを除去したロジクスイッチング素子を具現することができる。

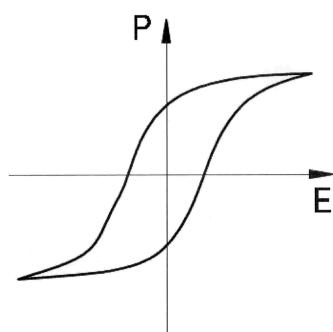

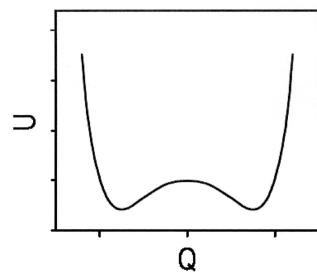

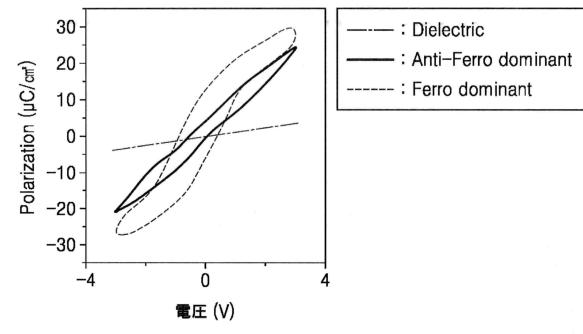

#### 【0067】

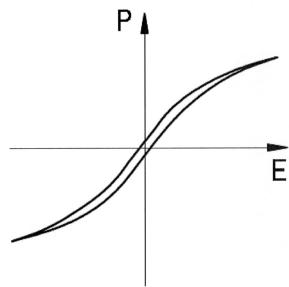

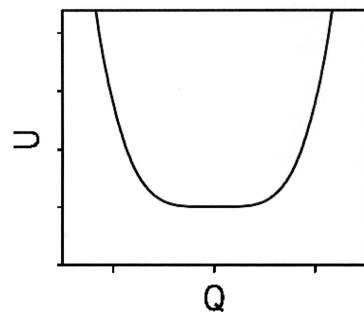

図11Aないし図14Bは、それぞれ強誘電体(ferro)、反強誘電体(anti-ferro)、強誘電体と反強誘電体との組み合わせ(ferro+anti-ferro)、及び誘電体(dielectric)の特性を示すグラフである。図11A、図12A、図13A及び図14Aのグラフは、当該物質層に印加される電場(electric field)(E)と分極(P)との関係であり、図11B、図12B、図13B及び図14Bのグラフは、当該物質層の電荷(Q)とエネルギー(U)との関係である。特に、図13A及び図13Bは、本実施形態によるドメインスイッチング層にも適用される強誘電体と反強誘電体との組み合わせ(混合体)の特性に対応する。

#### 【0068】

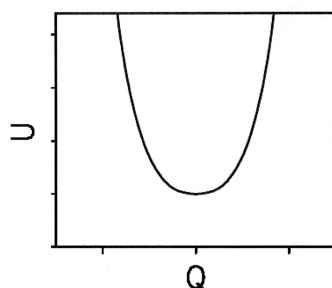

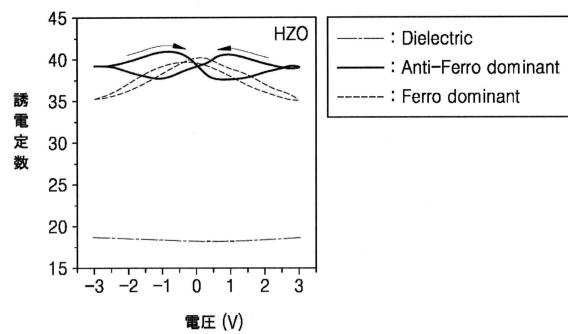

図15は、本実施形態によるものであり、金属/HfZrO層/金属構造において、HfZrO層の構成/物性による誘電定数(dielectric constant)・

10

20

30

40

50

電圧特性を測定した結果を示すグラフである。図15は、HfZrO層が誘電体(dielectric)である場合と、HfZrO層が反強誘電ドミナント(anti-ferroelectric dominant)である場合と、HfZrO層が強誘電ドミナント(ferroelectric dominant)である場合との結果を含む。

#### 【0069】

図15を参照すれば、アニーリング(熱処理)を行っていない非晶質HfZrO層は、誘電体の特性を示し、非晶質HfZrO層を第1条件でアニーリングした場合、反強誘電ドミナントである特性を示すことができ、非晶質HfZrO層を第2条件でアニーリングした場合、強誘電ドミナントである特性を示すことができる。HfO薄膜やHfO系の薄膜に対するアニーリング条件により、強誘電体と反強誘電体との比率を制御することができる。

#### 【0070】

図16は、本実施形態によるものであり、図15で説明した金属/HfZrO層/金属構造において、分極・電圧特性を測定した結果を示すグラフである。

#### 【0071】

図16を参照すれば、反強誘電ドミナントである場合、残留分極が0に近く、ヒステリシスも低減するが、強誘電ドミナントである場合、残留分極が10ほどに上昇し、ヒステリシスも大きくなっていることが分かる。

#### 【0072】

図17Aは、反強誘電ドミナントである場合のドメイン層DL1の構成(ドメイン配列)を例示的に示す断面図である。

#### 【0073】

図17Bを参照すれば、強誘電ドミナントである場合のドメイン層DL2の構成(ドメイン配列)を例示的に示す断面図である。

#### 【0074】

図17A及び図17Bを参照すれば、反強誘電ドミナントである場合のドメイン層DL1は、反強誘電体AFの総体積が、強誘電体Fの総体積よりかなり大きくなり、強誘電ドミナントである場合のドメイン層DL2は、強誘電体Fの総体積が、反強誘電体AFの総体積よりかなり大きくなる。アニーリング(熱処理)条件により、強誘電特性を有する直方晶系結晶領域と、反強誘電特性を有する正方晶系結晶領域とが薄膜内に混合している。図17A及び図17Bにおいて、M1及びM2は、金属層(metal)を示す。

#### 【0075】

図18は、本実施形態によって製造したA1:HfO薄膜の構成/物性による誘電定数・電圧特性を測定した結果を示すグラフである。図18は、A1:HfO薄膜が誘電体(dielectric)である場合と、A1:HfO薄膜が反強誘電ドミナントである場合と、A1:HfO薄膜が強誘電ドミナントである場合との結果を含む。ここで、A1:HfO薄膜は、A1がドーピングされたHfO薄膜を意味する。

#### 【0076】

図18を参照すれば、A1のドーピングレベルが19at%であり、アニーリング温度が500である場合、誘電体特性を有するA1:HfO薄膜を得ることができる。A1のドーピングレベルが7at%であり、アニーリング温度が700である場合、反強誘電ドミナントである特性を有するA1:HfO薄膜を得ることができる。A1のドーピングレベルが12at%であり、アニーリング温度が800である場合、強誘電ドミナントである特性を有するA1:HfO薄膜を得ることができる。A1のドーピングレベル及び/または非晶質A1:HfO薄膜に対するアニーリング条件を調節することにより、A1:HfO薄膜の物性を変化させることができる。

#### 【0077】

図19は、図18の結果を得るために使用した素子の構造を示す断面図である。

図19を参照すれば、シリコン基板51上に、シリコン酸化物層52を形成し、その上に、第1金属層53を形成し、第1金属層53上に、A1:HfO薄膜54を形成するこ

10

20

30

40

50

とができる。次に、Al : HfO薄膜54上に、第2金属層55を形成することができる。このとき、第1金属層53及び第2金属層55は、いずれもMo層であり、Al : HfO薄膜54の厚みは、約10nmである。Al : HfO薄膜54の幅は、約5μmないし400μmほどである。

【0078】

Al : HfO薄膜54のドーピングレベル及び/またはアニーリング温度により、Al : HfO薄膜54の強誘電特性及び反強誘電特性を制御することができる。すなわち、Al : HfO薄膜54のドーピングレベル及び/またはアニーリング温度により、Al : HfO薄膜54は、誘電体特性を有するか、反強誘電ドミナントである特性を有するか、あるいは強誘電ドミナントである特性を有することができる。従って、Al : HfO薄膜54内に形成される強誘電体及び反強誘電体の比率を制御することができる。

10

【0079】

例えば、ドーピングレベル及びアニーリング温度による特性変化を整理すれば、下記表1の通りである。

【0080】

【表1】

|       | 7at%        | 12at%       | 19at% | 22at% |

|-------|-------------|-------------|-------|-------|

| 500°C | D           | D           | D     | D     |

| 600°C | F dominant  | D           | D     | D     |

| 700°C | F dominant  | D           | D     | D     |

| 800°C | F dominant  | AF dominant | D     | D     |

| 900°C | AF dominant | AF dominant | D     | D     |

20

【0081】

前記表1において、Dは、誘電体特性を示し、F dominantは、強誘電ドミナントである特性を示し、AF dominantは、反強誘電ドミナントである特性を示す。使用する物質及びドーピング程度により、適切なアニーリング温度は、異なってもよい。それと係わり、本実施形態によるロジックスイッチング素子の製造時に使用されるアニーリング温度は、約400ないし1,200ほどもある。

30

【0082】

図20は、一実施形態によるロジックスイッチング素子のサブスレショルドスイング(SS)特性が改善される効果について説明するためのグラフである。

【0083】

図20を参照すれば、既存シリコン基板のトランジスタの場合(一点鎖線グラフ)、サブスレショルドスイング(SS)値は、約60mV/decが限界であると知られている。しかし、本実施形態によるロジックスイッチング素子の場合(実線グラフ)、ネガティブキャパシタンス効果、及び反強誘電体のドメインスイッチング効果により、サブスレショルドスイング(SS)値が約60mV/dec以下に低下する。

40

【0084】

図21は、他の実施形態によるロジックスイッチング素子を示す断面図である。

図21を参照すれば、基板101上に、チャネル層11が具備されてもよい。言い換えれば、チャネル層11は、基板101の一部ではない基板101と別個の物質層(薄膜)としても具備される。チャネル層11は、例えば、酸化物半導体、窒化物半導体、窒化酸化物半導体、二次元(2D)物質、量子点及び有機半導体のうち少なくとも一つを含んでもよい。前記酸化物半導体は、例えば、InGaZnOなどを含み、前記二次元物質は、

50

例えば、TMDやグラフェンを含み、前記量子点は、コロイダル量子点、ナノ結晶構造などを含んでもよいが、それらは、例示的なものに過ぎず、本願実施形態は、それらに限定されるものではない。

【0085】

チャネル層11の互いに異なる領域に電気的に接触したソース電極21及びドレイン電極31が具備されてもよい。チャネル層11の第1端部上に、ソース電極21が具備され、チャネル層11の第2端部上に、ドレイン電極31が具備されてもよい。ソース電極21及びドレイン電極31は、金属、金属化合物、導電性ポリマーのような導電性物質によって形成されてもよい。

【0086】

ソース電極21とドレイン電極31との間のチャネル層11領域上に、ドメインスイッチング層301が具備されてもよい。ドメインスイッチング層301は、図1を参照して説明したドメインスイッチング層300Aと同一であるか、あるいは類似している。ドメインスイッチング層301は、少なくとも1つの強誘電物質領域F、及び少なくとも1つの反強誘電物質領域AFを含んでもよい。ドメインスイッチング層301上に、ゲート電極501が具備されてもよい。図21の素子は、図2ないし図7を参照して説明したように変形されてもよい。

10

【0087】

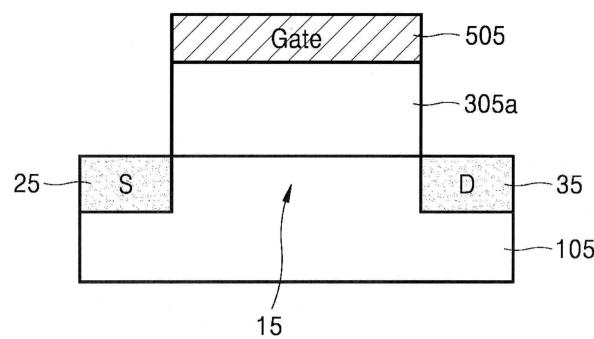

図22Aないし図22Cは、一実施形態によるロジックスイッチング素子の製造方法を示す断面図である。

20

【0088】

図22Aを参照すれば、チャネル要素15を含む基板105を設けることができ、チャネル要素15上に、非晶質薄膜305a及びゲート電極505の積層構造体を形成することができる。基板105上に、非晶質物質層及び導電性物質層を順に蒸着した後、それらをパターニングし、前記非晶質物質層から非晶質薄膜305aを、前記導電性物質層からゲート電極505を形成することができる。非晶質薄膜305a及びゲート電極505の積層構造体は、「ゲートスタック」とも言う。前記非晶質物質層は、例えば、ALD (atomic layer deposition) またはCVD (chemical vapor deposition)などの工程によって蒸着することができ、前記導電性物質層は、例えば、ALD、CVDまたはPVD (physical vapor deposition)などの工程によって蒸着することができる。

30

【0089】

非晶質薄膜305aは、比較的高い誘電定数を有する薄膜である。例えば、非晶質薄膜305aの誘電定数は、約10以上である。それと係わり、非晶質薄膜305aは、高誘電層 (high-k dielectric layer) と言うことができる。非晶質薄膜305aは、例えば、Hf系酸化物及びZr系酸化物のうち少なくとも一つを含んでもよい。前記Hf系酸化物は、HfOまたはHfZrOなどもある。前記Zr系酸化物はZrOなどもある。ここで、HfO、HfZrO、ZrOは、構成元素の組成比を無視して表記したものである。必要により、非晶質薄膜305aは、ドーパントをさらに含んでもよい。前記ドーパントは、Si、Al、Zr、Y、La、Gd、Sr及びHfのうち少なくとも一つを含んでもよい。非晶質薄膜305aがドーパントを含む場合、全体的に、同一濃度 (実質的に、同一濃度) にドーピングされるか、あるいは領域により、互いに異なる濃度 (レベル) にもドーピングされる。また、非晶質薄膜305aの領域により、互いに異なるドーパントがドーピングされてもよい。非晶質薄膜305aに対するドーピングは、前記非晶質物質層を形成する間にも行われ、前記非晶質物質層を形成した後、別途の工程によっても行われる。

40

【0090】

非晶質薄膜305a及びゲート電極505を形成する前に、基板105に、ソース25及びドレイン35を形成することができる。所定ドーパントを、基板105の互いに異なる領域にイオン注入し、ソース25及びドレイン35を形成した後、非晶質薄膜305a

50

及びゲート電極 505 を形成することができる。しかし、ソース 25 及びドレイン 35 の形成時点は、異なってもよい。非晶質薄膜 305a 及びゲート電極 505 を形成した後、基板 105 内に、ソース 25 及びドレイン 35 を形成することもできる。

#### 【0091】

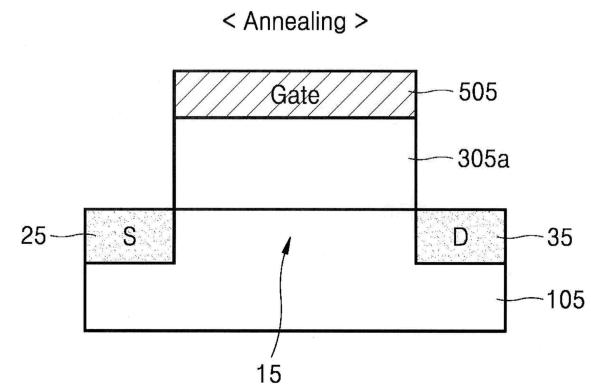

図 22B を参照すれば、非晶質薄膜 305a に対するアニーリング工程を遂行することができる。前記アニーリング工程は、約 400 ないし 1,200 範囲の温度で遂行することができる。前記アニーリング工程を介して、非晶質薄膜 305a を結晶化させることができ、非晶質薄膜 305a から、強誘電物質領域及び反強誘電物質領域を形成することができる。ゲート電極 505 が非晶質薄膜 305a に接触した状態で前記アニーリング工程を進めれば、非晶質薄膜 305a の結晶化がさらに容易に行われる。アニーリング工程の結果物が図 22C に図示されている。

10

#### 【0092】

図 22C を参照すれば、非晶質薄膜 305a (図 22B) から、ドメインスイッチング層 305b が形成されてもよい。ドメインスイッチング層 305b は、少なくとも 1 つの強誘電物質領域 F、及び少なくとも 1 つの反強誘電物質領域 AF を含んでもよい。強誘電物質領域 F と反強誘電物質領域 AF は、互いに異なる結晶相を有することができる。例えば、強誘電物質領域 F は、直方晶系結晶相を含み、反強誘電物質領域 AF は、正方晶系結晶相を含んでもよい。このとき、強誘電物質領域 F は、ゲート電極 505 に接するように具備され、反強誘電物質領域 AF は、強誘電物質領域 F とチャネル要素 15 との間に配置されてもよい。アニーリング条件及び非晶質薄膜 305a (図 22B) の構成により、強誘電物質領域 F と反強誘電物質領域 AF との配列及び配置関係が異なってもよい。ここでは、例示的に、反強誘電物質領域 AF 上に、強誘電物質領域 F が具備された場合を図示したが、それらの配列及び配置関係は、図 1 ないし図 7 を参照して説明したように異なってもよい。

20

#### 【0093】

アニーリング条件により、ドメインスイッチング層 305b 内に形成される強誘電性物質領域 F と反強誘電性物質領域 AF との比率が制御され、それにより、キャパシタンスマッチングがなされる。従って、ドメインスイッチング層 305b は、非メモリ要素でもある。強誘電物質領域 F と反強誘電物質領域 AF との組み合わせにより、ドメインスイッチング層 305b は、外部電場による分極変化において、実質的に非履歴挙動特性を有することができる。言い換えれば、ドメインスイッチング層 305b は、ヒステリシス特性を有さないか、あるいは実質的に有さない。場合により、強誘電物質領域 F と反強誘電物質領域 AF は、互いに異なるドーピング濃度を有するか、あるいは互いに異なるドーパントによってドーピングされた領域もある。

30

#### 【0094】

必要により、ドメインスイッチング層 305b は、2 段階以上の蒸着工程、または 2 段階以上のドーピング工程を経て形成されてもよい。また、ドメインスイッチング層 305b は、1 回のアニーリング工程ではない 2 段階以上のアニーリング工程を経て形成されてもよい。また、本実施形態の工程を変形し、図 1 ないし図 7 で説明したような多様な変形構造を形成することができる。

40

#### 【0095】

本実施形態によるロジックスイッチング素子 (ロジックトランジスタ) は、多様な電子素子、論理素子などにも適用される。ロジックスイッチング素子 (ロジックトランジスタ) は、多様な電子素子 / 論理素子の基本構成要素にもなる。本実施形態によれば、サブスレショルドスイッチング (SS) のような動作特性を改善させることができ、制御効率を高めることができ、スケールダウンにも有利なロジックスイッチング素子を具現することができるために、それを適用し、優秀な性能の電子素子 / 論理素子を製造することができる。

#### 【0096】

図 23 は、一実施形態による電子素子のアーキテクチャを概略的に示す概念図である。

図 23 を参照すれば、1 つのチップ 1000 にメモリユニット (memory uni

50

t ) 1010、ALU ( arithmetic logic unit ) 1020 及び制御ユニット ( control unit ) 1030 が形成されてもよい。同一基板上に、メモリユニット 1010、ALU 1020 及び制御ユニット 1030 をモノリシック ( monolithic ) に集積し、チップ 1000 を形成することができる。ALU 1020 及び制御ユニット 1030 それぞれは、前述の実施形態による「ロジックスイッチング素子」を含んでもよい。例えば、ロジックスイッチング素子は、強誘電ドメインを含みながら、実質的に非履歴挙動特性を有するドメインスイッチング層を含んでもよい。メモリユニット 1010 は、メモリ素子を含んでもよい。例えば、前記メモリ素子は、強誘電ドメインを含みながら、履歴挙動特性を有するドメイン層を含んでもよい。メモリユニット 1010、ALU 1020 及び制御ユニット 1030 は、オンチップ ( on - chip ) において、メタルライン ( metal line ) に相互連結され、直接通信することができる。メモリユニット 1010 は、メインメモリ ( main memory ) 及びキャッシュメモリ ( cache memory ) をいずれも含んでもよい。そのようなチップ 1000 は、オンチップメモリ処理装置 ( on - chip memory processing unit ) とされる。チップ 1000 と連結された入出力素子 2000 がさらに具備されてもよい。

#### 【0097】

そのような電子素子は、1つのチップに、メモリユニットとロジック素子ユニットと共に集積して製造することができるために、コスト側面で有利である。また、メモリユニットとロジック素子ユニットとの間に、データ伝送量が多く、データ伝送が連続的になされる応用分野、例えば、ニューロモーフィック素子 ( neuromorphic device ) 分野に、本実施形態の電子素子を適用すれば、効率向上、速度向上、電力消耗低減のような多様な効果を得ることができる。ニューロモーフィック素子の基本的な構成及び動作方式は周知があるので、それに係わる詳細な説明は省略する。

#### 【0098】

場合により、本実施形態による電子素子は、1つのチップにおいて、サブユニット ( sub - units ) の区分なしに、コンピューティング ( computing ) 単位素子とメモリ単位素子とが相互隣接して形成されるアーキテクチャとしても具現される。

#### 【0099】

図 24 は、他の実施形態による電子素子のアーキテクチャを概略的に示す概念図である。

#### 【0100】

図 24 を参照すれば、CPU ( central processing unit ) チップ 1500 は、キャッシュメモリ ( cache memory ) 1510、ALU 1520 及び制御ユニット 1530 を含んでもよい。ALU 1520 及び制御ユニット 1530 それぞれは、前述の実施形態による「ロジックスイッチング素子」を含んでもよい。例えば、該ロジックスイッチング素子は、強誘電ドメインを含みながら、実質的に非履歴挙動特性を有するドメインスイッチング層を含んでもよい。

#### 【0101】

CPU チップ 1500 と別個に、メインメモリ 1600 及び補助ストレージ 1700 が具備され、入出力素子 2500 が具備されてもよい。例えば、キャッシュメモリ 1510 は、SRAM ( static random access memory ) で構成され、メインメモリ 1600 は、DRAM ( dynamic random access memory ) で構成されてもよい。

#### 【0102】

本開示によれば、ネガティブキャパシタンス効果を利用するロジックスイッチング素子を具現することができる。本開示によれば、強誘電物質及び反強誘電物質をいずれも適用したロジックスイッチング素子を具現することができる。本開示によれば、サブスレショルドスイッチング ( SS ) のような動作特性を改善させることができ、制御効率を高めることができ、スケールダウンにも有利なロジックスイッチング素子を具現することができる。本開示によれば、前記ロジックスイッチング素子を利用し、多様な電子素子 / 装置 / 回路

/システムを具現することができる。

#### 【0103】

前述の説明において、多くの事項が具体的に記載されているが、それらは、発明の範囲を限定するものとするよりも、具体的な実施形態の例示として解釈されなければならない。例えば、本発明が属する技術分野において当業者であるならば、図1ないし図7、及び図21のロジックスイッチング素子の構成は、多様に変形されるということが分かるであろう。また、図22Aないし図22Cを参照して説明したロジックスイッチング素子の製造方法も、多様に変形されるということが分かるであろう。従って、本発明の範囲は、説明された実施形態によって決められるものではなく、特許請求の範囲に記載された技術的思想によって決められなければならない。

10

#### 【産業上の利用可能性】

#### 【0104】

本発明の、ロジックスイッチング素子及びその製造方法は、例えば、電子素子関連の技術分野に効果的に適用可能である。

#### 【符号の説明】

#### 【0105】

10 チャネル要素

20 ソース

30 ドレイン

100 基板

20

150, 160 絶縁層

200 導電層

300A, 300B, 300C, 300D, 300E ドメインスイッチング層

500 ゲート電極

A F 反強誘電物質領域

F 強誘電物質領域

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

10

20

30

40

50

【図 1 1 A】

&lt; Ferro &gt;

【図 1 1 B】

10

【図 1 2 A】

&lt; Anti-ferro &gt;

【図 1 2 B】

20

30

40

50

【図 1 3 A】

&lt; Ferro + Anti-ferro &gt;

【図 1 3 B】

10

【図 1 4 A】

&lt; Dielectric &gt;

【図 1 4 B】

20

30

40

50

【図 1 5】

【図 1 6】

10

【図 1 7 A】

&lt; Anti-ferroelectric dominant &gt;

【図 1 7 B】

&lt; Ferroelectric dominant &gt;

20

30

40

50

【図 1 8】

【図 1 9】

【図 2 0】

【図 2 1】

【図 2 2 A】

【図 2 2 B】

10

【図 2 2 C】

【図 2 3】

【図 2 4】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

|         |       |           |         |       |         |

|---------|-------|-----------|---------|-------|---------|

| H 1 0 B | 51/00 | (2023.01) | F I     |       |         |

| H 1 0 B | 53/00 | (2023.01) | H 0 1 L | 29/78 | 6 1 8 B |

|         |       |           | H 0 1 L | 29/78 | 6 2 7 F |

|         |       |           | H 1 0 B | 51/00 |         |

|         |       |           | H 1 0 B | 53/00 |         |

弁理士 崔 允辰

## (74)代理人

木内 敬二

## (72)発明者

許 鎮盛

大韓民国京畿道水原市靈通區三星路130 三星綜合技術院内

## (72)発明者

李 潤姓

大韓民国京畿道水原市靈通區三星路130 三星綜合技術院内

## (72)発明者

趙 常 ヒョン

大韓民国京畿道水原市靈通區三星路130 三星綜合技術院内

## 審査官

柴山 将隆

## (56)参考文献

特開2017-059751 (JP, A)

特開平05-090599 (JP, A)

米国特許出願公開第2018/0233573 (US, A1)

米国特許出願公開第2017/0162250 (US, A1)

中国特許出願公開第1011047189 (CN, A)

米国特許出願公開第2010/0006953 (US, A1)

国際公開第2003/023858 (WO, A1)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 29 / 786

H 10 B 51 / 00

H 10 B 53 / 00

H 01 L 21 / 336