#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5257204号 (P5257204)

(45) 発行日 平成25年8月7日(2013.8.7)

(24) 登録日 平成25年5月2日(2013.5.2)

| (51) Int.Cl. |              |           | F 1  |       |   |

|--------------|--------------|-----------|------|-------|---|

| H02M         | 3/28         | (2006.01) | HO2M | 3/28  | Q |

| HO1F         | <i>30/00</i> | (2006.01) | HO2M | 3/28  | R |

|              |              |           | HO1F | 31/00 | A |

|              |              |           | HO1F | 31/00 | C |

請求項の数 7 (全 33 頁)

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号<br>(43) 公開日<br>審査請求日 | 特願2009-85955 (P2009-85955)<br>平成21年3月31日 (2009.3.31)<br>特開2010-239797 (P2010-239797A)<br>平成22年10月21日 (2010.10.21)<br>平成23年11月29日 (2011.11.29) | (73) 特許権者<br>(74) 代理人<br>(74) 代理人<br>(72) 発明者 | 新 000003067<br>TDK株式会社<br>東京都港区芝浦三丁目9番1号<br>100109656<br>弁理士 三反崎 泰司<br>100098785<br>弁理士 藤島 洋一郎<br>中堀 渉<br>東京都中央区日本橋一丁目13番1号 T<br>DK株式会社内 |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                                               | 審査官                                           | 安食 泰秀                                                                                                                                    |

最終頁に続く

## (54) 【発明の名称】スイッチング電源装置

## (57)【特許請求の範囲】

## 【請求項1】

入力端子対から入力される直流入力電圧に基づいて電圧変換を行うことにより直流出力電圧を生成し、出力端子対から出力するスイッチング電源装置であって、

前記入力端子対側に配置されると共に、2つのアームを形成する4つのスイッチング素子を含んで構成されたフルブリッジ型のスイッチング回路と、

前記出力端子対側に配置され、複数の第1整流素子を含んで構成された整流回路と、前記スイッチング回路と前記整流回路との間に配置されると共に、前記入力端子対側の第1の巻線と、前記出力端子対側の第2の巻線と、第3の巻線とを有するトランスと、

前記スイッチング回路に並列接続されると共に、2つのアームを形成する逆方向接続の4つの第2整流素子からなるフルブリッジ回路を含んで構成されたサージ電圧抑止回路と

前記スイッチング回路を駆動する駆動回路と を備え、

前記第3の巻線は、前記フルブリッジ回路に対してHブリッジ接続され、

前記第1および第2の巻線間ならびに前記第1および第3の巻線間がそれぞれ、前記第

2 および第3 の巻線間と比べて疎に磁気結合されている

ことを特徴とするスイッチング電源装置。

#### 【請求項2】

前記4つのスイッチング素子に対してそれぞれ並列接続された第3整流素子を備え、

前記スイッチング回路における一方のアームを形成する2つのスイッチング素子に並列接続された前記第3整流素子が、前記フルブリッジ回路における一方のアームを形成する2つの第2整流素子を兼ねている

ことを特徴とする請求項1に記載のスイッチング電源装置。

#### 【請求項3】

前記スイッチング素子が電界効果型トランジスタにより構成され、

前記第3整流素子は、前記電界効果型トランジスタの寄生ダイオードから構成されている

ことを特徴とする請求項2に記載のスイッチング電源装置。

#### 【請求項4】

前記4つのスイッチング素子に対してそれぞれ並列接続された容量素子を備え、

前記第3の巻線は、前記容量素子と共にLC共振回路を構成する

ことを特徴とする請求項1ないし請求項3のいずれか1項に記載のスイッチング電源装置。

## 【請求項5】

前記スイッチング素子が電界効果型トランジスタにより構成され、 前記容量素子は、前記電界効果型トランジスタの寄生容量から構成されている ことを特徴とする請求項4に記載のスイッチング電源装置。

#### 【請求項6】

前記トランスは、

互いに対向する2つの基体部と、前記2つの基体部の対向面内で互いに交差する2直線上に一対ずつ配置され、前記2つの基体部同士を連結する4つの脚部と、を有する磁芯と

各脚部が個別に貫通する貫通孔を有し、前記脚部を巻回すると共に前記第1の巻線を構成する第1の導電部材と、

各脚部が個別に貫通する貫通孔を有し、前記脚部を巻回すると共に前記第2の巻線を構成する第2の導電部材と、

各脚部が個別に貫通する貫通孔を有し、前記脚部を巻回すると共に前記第3の巻線を構成する第3の導電部材と

を有し、

前記第1ないし第3の巻線を流れる電流によって、前記4つの脚部および前記2つの基体部の内部に磁路が形成され、

前記4つの脚部のうち、一方の直線上の2つの脚部の各内部に生ずる磁束がともに第1の方向を向くと共に、他方の直線上の2つの脚部の各内部に生ずる磁束の向きがともに前記第1の方向とは逆の第2の方向を向くように、前記第1ないし第3の巻線が巻回されている

ことを特徴とする請求項1ないし請求項5のいずれか1項に記載のスイッチング電源装置。

## 【請求項7】

前記トランスは、

互いに対向する2つの基体部と、前記2つの基体部の対向面内で互いに交差する2直線上に一対ずつ配置され、前記2つの基体部同士を連結する4つの脚部と、を有する磁芯と

各脚部が個別に貫通する貫通孔を有し、前記脚部を巻回すると共に前記第1の巻線を構成する第1の導電部材と、

各脚部が個別に貫通する貫通孔を有し、前記脚部を巻回すると共に前記第2の巻線を構成する第2の導電部材と、

各脚部が個別に貫通する貫通孔を有し、前記脚部を巻回すると共に前記第3の巻線を構成する第3の導電部材と

を有し、

10

20

30

40

前記第1ないし第3の巻線を流れる電流によって、前記4つの脚部および前記2つの基体部の内部に、前記4つの脚部のうち互いに隣り合った2つの脚部と前記2つの基体部とをそれぞれ一方方向に通る磁路が4つ形成されるように、前記第1ないし第3の巻線が巻回されている

ことを特徴とする請求項1ないし請求項5のいずれか1項に記載のスイッチング電源装 置。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、直流入力電圧をスイッチングして得られるスイッチング出力を電力変換トランスの出力巻線に取り出すように構成されたスイッチング電源装置に関する。

#### 【背景技術】

#### [0002]

従来より、スイッチング電源装置として種々のDC - DCコンバータが提案され、実用に供されている。その多くは、電力変換トランス(変圧素子)の1次側巻線に接続されたスイッチング回路(インバータ回路)のスイッチング動作により直流入力電圧をスイッチングし、スイッチング出力(インバータ出力)を電力変換トランス(トランス)の2次側巻線に取り出す方式である。スイッチング回路のスイッチング動作に伴い、2次側巻線に現れる電圧は、整流回路によって整流された後、平滑回路によって直流に変換されて出力される。

#### [0003]

この種のスイッチング電源装置では、上記整流回路内において電力伝送ラインに直列に、出力整流ダイオードなどの出力整流素子が接続される。したがって、この出力整流ダイオードでの損失を低減させることは、スイッチング電源装置の効率を向上させる上で、極めて有効である。

## [0004]

出力整流ダイオードでの損失を低減させるには、順方向電圧降下の小さいダイオードを使用すればよい。ところが、順方向電圧降下の低いダイオードは逆方向耐電圧も低い。このため、出力整流ダイオードとして、順方向電圧降下の低いダイオードを使用する場合には、特に、逆方向電圧を抑制する必要がある。

## [0005]

この種のスイッチング電源装置において、逆方向電圧として最も考慮しなければならないのは、スイッチング回路のオン・オフ動作に伴う、寄生要素に起因したサージ(スパイク)電圧であり、出力整流ダイオードに対して逆方向電圧として印加されるようになっている。そこで、従来より、このようなサージ電圧を抑制するため、様々な試みがなされている(例えば、特許文献1,2)。

#### 【先行技術文献】

## 【特許文献】

#### [0006]

【特許文献1】米国特許第4864479号明細書

【特許文献2】特開2008-187801号公報

## 【発明の概要】

【発明が解決しようとする課題】

#### [0007]

ここで、上記特許文献1では、スイッチング素子におけるドレイン・ソース間の静電容量と、トランスのリーケージインダクタンスとを利用してLC共振動作を行うことにより、ゼロボルトスイッチング(ZVS; Zero Volt Switching)動作を実現している。これにより、スイッチング素子における短絡損失を抑制することができる。

#### [0008]

ところが、トランスのリーケージインダクタンスを共振のインダクタンス成分として利

20

30

40

用する場合、 1 次側巻線および 2 次側巻線の結合からなる理想トランス部分と、リーケージインダクタンス部分とを分離できない。そのため、理想トランス部分における端子両端の容量成分と、リーケージインダクタンス部分とによる共振動作がなされることとなり、出力整流ダイオードに対してサージ電圧をもたらしてしまうことになる。

## [0009]

一方、上記特許文献 2 では、上記した Z V S 動作を実現するために、トランスは結合の高いものとすると共に、L C 共振用のインダクタンス成分として、トランスとは別体の共振用インダクタを設けている。ここで、トランスにおける端子両端の容量成分と上記共振用インダクタとによる共振動作がなされた場合、これらのトランスと共振用インダクタとの接続点は、電圧源の 2 倍の振幅で共振しようとする。したがって、トランスと共振用インダクタとの接続点の電圧が電圧源の電圧を超えたときに、この電圧源にクランプされるようにダイオードを接続してなるサージ電圧抑止回路を設けることにより、出力整流ダイオードにおけるサージ電圧の発生を抑えるようになっている。

#### [0010]

しかしながら、この手法を用いるにはトランスとは別に共振用インダクタを設ける必要があることから、装置内の部品点数が増加してしまうことになる。

#### [0011]

このように従来の手法では、装置内の部品点数を削減しつつ、スイッチング素子における短絡損失を抑制すると共に、出力整流素子に印加されるサージ電圧を抑制するのが困難であり、改善の余地があった。

#### [0012]

本発明はかかる問題点に鑑みてなされたもので、その目的は、装置内の部品点数を削減しつつ、スイッチング素子における短絡損失を抑制すると共に出力整流素子に印加されるサージ電圧を抑制することが可能なスイッチング電源装置を提供することにある。

#### 【課題を解決するための手段】

#### [0013]

本発明のスイッチング電源装置は、入力端子対から入力される直流入力電圧に基づいて電圧変換を行うことにより直流出力電圧を生成し、出力端子対から出力するものであって、入力端子対側に配置されると共に、2つのアームを形成する4つのスイッチング素子を含んで構成されたフルブリッジ型のスイッチング回路と、出力端子対側に配置され、複数の第1整流素子を含んで構成された整流回路と、スイッチング回路と整流回路との間に配置されると共に、入力端子対側の第1の巻線と、出力端子対側の第2の巻線と、第3の巻線とを有するトランスと、スイッチング回路に並列接続されると共に、2つのアームを形成する逆方向接続の4つの第2整流素子からなるフルブリッジ回路を含んで構成されたサージ電圧抑止回路と、スイッチング回路を駆動する駆動回路とを備えたものである。また、上記第3の巻線間ならびに上記第1および第3の巻線間ならびに上記第1および第3の巻線間と比べて疎に磁気結合されている。

## [0014]

本発明のスイッチング電源装置では、入力端子対から入力した入力電圧がスイッチング回路においてスイッチングされ、交流電圧が生成される。そして、この交流電圧がトランスにより変圧され、この変圧された交流電圧が整流回路によって整流されることにより、出力端子対から出力電圧が出力される。ここで、第1および第2の巻線間ならびに第1および第3の巻線間がそれぞれ、第2および第3の巻線間と比べて疎に磁気結合されていることにより、トランスにリーケージインダクタンス成分が生ずる。そして、このリーケージインダクタンス成分と、上記スイッチング素子の両端間の容量成分(スイッチング素子の寄生容量や別個の容量素子)とによりLC共振回路が構成されるため、このLC共振回路の共振動作によって、トランスとは別個のインダクタを設けることなく、ZVS動作が実現される。このとき、トランスにおける理想トランス部分(第1および第2の巻線)における端子両端の容量成分と、リーケージインダクタンス成分とによる共振動作がなされ

10

20

30

40

20

30

40

50

るため、第1整流素子に対してサージ電圧(逆電圧)が印加されることになる。ここで、 上記サージ電圧抑止回路内の第2整流素子による第3の巻線の両端の電圧に対するクラン プ作用により、このような第1整流素子に加わるサージ電圧が抑制される。

#### [0015]

本発明のスイッチング電源装置では、上記4つのスイッチング素子に対してそれぞれ並列接続された第3整流素子を設けると共に、上記スイッチング回路における一方のアームを形成する2つのスイッチング素子に並列接続された第3整流素子が、上記フルブリッジ回路における一方のアームを形成する2つの第2整流素子を兼ねているようにしてもよい。このように構成した場合、全体として整流素子の数が減るため、部品点数をより削減可能となる。

#### [0016]

本発明のスイッチング電源装置では、上記4つのスイッチング素子に対してそれぞれ並列接続された容量素子を設けると共に、上記第3の巻線が、これらの容量素子と共にLC 共振回路を構成するようにしてもよい。このように構成した場合、上記LC共振回路による共振動作によって、スイッチング素子での短絡損失が抑制される。

#### [0017]

これらの場合において、上記スイッチング素子を電界効果型トランジスタにより構成すると共に、上記容量素子および上記第3整流素子のうちの少なくとも一方を、この電界効果型トランジスタの寄生容量または寄生ダイオードから構成するようにしてもよい。このように構成した場合、使用する素子数が少なくなり、回路構成が簡素化する。

#### [0018]

本発明のスイッチング電源装置では、上記トランスが、互いに対向する2つの基体部と 、これらの2つの基体部の対向面内で互いに交差する2直線上に一対ずつ配置され、2つ の基体部同士を連結する4つの脚部と、を有する磁芯と、各脚部が個別に貫通する貫通孔 を有し、上記脚部を巻回すると共に上記第1の巻線を構成する第1の導電部材と、各脚部 が個別に貫通する貫通孔を有し、上記脚部を巻回すると共に上記第2の巻線を構成する第 2の導電部材と、各脚部が個別に貫通する貫通孔を有し、上記脚部を巻回すると共に上記 第3の巻線を構成する第3の導電部材とを有すると共に、上記第1ないし第3の巻線を流 れる電流によって、4つの脚部および2つの基体部の内部に磁路が形成され、上記4つの 脚部のうち、一方の直線上の2つの脚部の各内部に生ずる磁束がともに第1の方向を向く と共に、他方の直線上の2つの脚部の各内部に生ずる磁束の向きがともに上記第1の方向 とは逆の第2の方向を向くように、上記第1ないし第3の巻線が巻回されているようにし てもよい。このように構成した場合、4つの脚部および2つの基体部の内部に、4つの脚 部のうち互いに隣り合った2つの脚部と2つの基体部とをそれぞれ一方方向に通る磁路が 4 つ形成される。したがって、U型コアの場合と比べ、磁路が分散されることにより磁 芯における磁束密度が低下するため、コア損失が低減する。また、E型コアの場合と比べ て放熱経路が拡大するため、磁芯自体の冷却と共に第1および第2の巻線の冷却がし易く なる。よって、信頼性を向上させつつコスト低減を図ることが可能となる。

## [0019]

本発明のスイッチング電源装置では、上記トランスが、互いに対向する2つの基体部と、これらの2つの基体部の対向面内で互いに交差する2直線上に一対ずつ配置され、2つの基体部同士を連結する4つの脚部と、を有する磁芯と、各脚部が個別に貫通する貫通孔を有し、上記脚部を巻回すると共に上記第1の巻線を構成する第1の導電部材と、各脚部が個別に貫通する貫通孔を有し、上記脚部を巻回すると共に上記第2の巻線を構成する第2の導電部材と、各脚部が個別に貫通する貫通孔を有し、上記脚部を巻回すると共に上記第3の巻線を構成する第3の巻線を構成する第3の巻線を構成する第3の巻線を構成する第3の巻線を構成する第3の巻線を有すると共に、上記第1ないし第3の巻線を流れる電流によって、4つの脚部および2つの基体部の内部に、4つの脚部のうち互いに隣り合った2つの脚部と2つの基体部とをそれぞれ一方方向に通る磁路が4つ形成されるように、上記第1ないし第3の巻線が巻回されているようにしてもよい。このように構成した場合、U型コアの場合と比べ、磁路が分散されることにより磁芯における磁束密度が低

下するため、コア損失が低減する。また、E型コアの場合と比べて放熱経路が拡大するた め、磁芯自体の冷却と共に第1および第2の巻線の冷却がし易くなる。よって、信頼性を 向上させつつコスト低減を図ることが可能となる。

#### 【発明の効果】

## [0020]

本発明のスイッチング電源装置によれば、第1および第2の巻線間ならびに第1および 第3の巻線間がそれぞれ、第2および第3の巻線間と比べて疎に磁気結合されているよう にすると共に、これにより生ずるリーケージインダクタンス成分とスイッチング素子の両 端間の容量成分とによってLC共振回路を構成するようにしたので、トランスとは別個の インダクタを設けることなく、ZVS動作を実現することができる。また、上記サージ電 圧抑止回路を設けるようにしたので、第2整流素子による第3の巻線の両端の電圧に対す るクランプ作用により、トランスにおける理想トランス部分における端子両端の容量成分 とリーケージインダクタンス成分とによる共振動作に起因して第1整流素子に加わるサー ジ電圧を抑制することができる。よって、装置内の部品点数を削減しつつ、スイッチング 素子における短絡損失を抑制すると共に出力整流素子に印加されるサージ電圧を抑制する ことが可能となる。

#### 【図面の簡単な説明】

#### [0021]

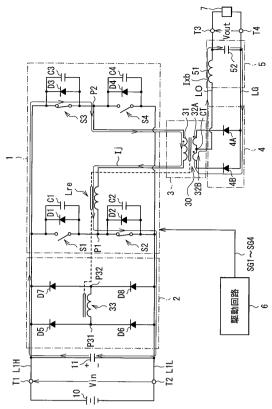

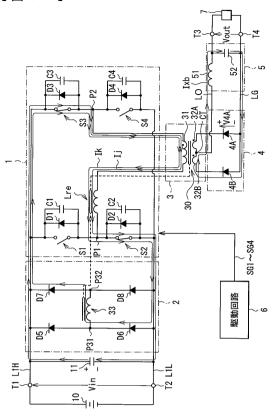

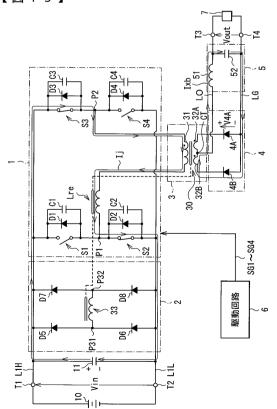

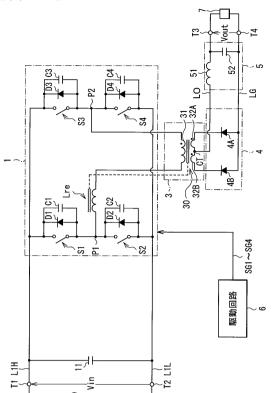

- 【図1】本発明の一実施の形態に係るスイッチング電源装置の構成を表す回路図である。

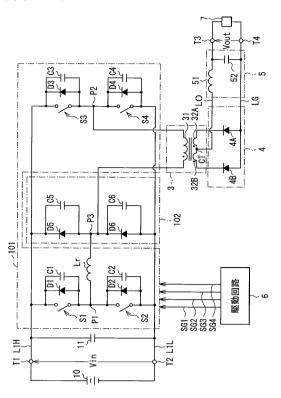

- 【図2】図1に示したスイッチング電源装置の等価回路を表す回路図である。

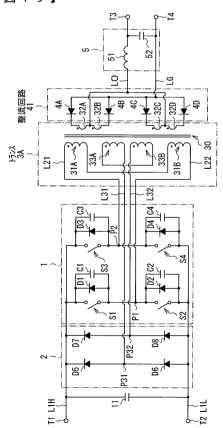

- 【図3】図2に示したトランスにおける主要部の外観構成を表す分解斜視図である。

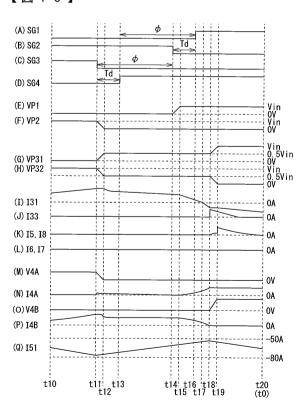

- 【図4】図1に示したスイッチング電源装置の動作を表すタイミング波形図である。

- 【図5】図1に示したスイッチング電源装置の動作を説明するための回路図である。

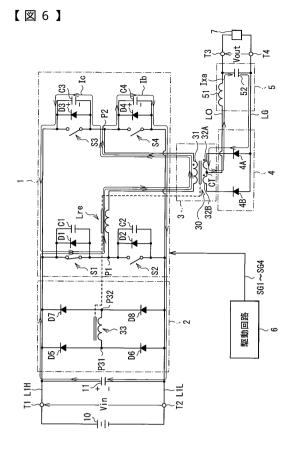

- 【図6】図5に続くスイッチング電源装置の動作を説明するための回路図である。

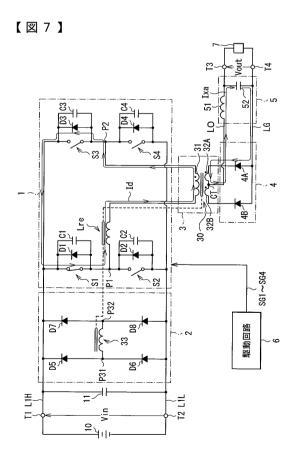

- 【図7】図6に続くスイッチング電源装置の動作を説明するための回路図である。

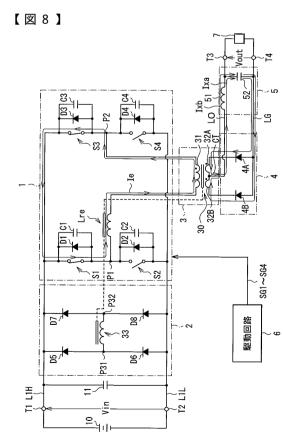

- 【図8】図7に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図9】図8に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図10】図9に続くスイッチング電源装置の動作を説明するための回路図である。

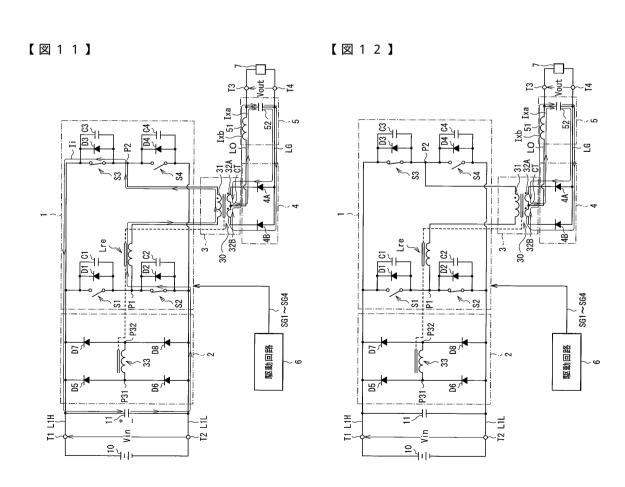

- 【図11】図10に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図12】図11に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図13】図12に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図14】図13に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図15】図14に続くスイッチング電源装置の動作を説明するための回路図である。

- 【図16】図15に続くスイッチング電源装置の動作を表すタイミング波形図である。

- 【図17】比較例1に係るスイッチング電源装置の構成を表す回路図である。

- 【図18】比較例2に係るスイッチング電源装置の構成を表す回路図である。

- 【図19】本発明の変形例1に係るスイッチング電源装置の構成(等価回路構成)を表す 回路図である。

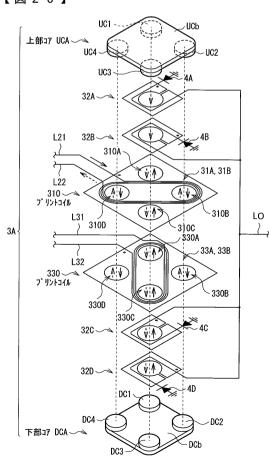

- 【図20】図19に示したトランスにおける主要部の外観構成を表す分解斜視図である。

- 【図21】図19に示したトランスにおける各巻線間の結合係数の一例を表す図である。

- 【図22】図19に示したトランスにおいて形成される還流磁路の例を表す模式図である

- 【図23】図19に示したトランスの作用について説明するための平面模式図である。

- 【図24】図19に示したトランスにおける上部コアおよび下部コアの他の外観構成例を 表す平面図である。

- 【図25】本発明の変形例2に係るスイッチング電源装置の構成を表す回路図である。

- 【図26】本発明の変形例3に係るスイッチング電源装置の構成を表す回路図である。

## 【発明を実施するための形態】

#### [0022]

以下、本発明の実施の形態について、図面を参照して詳細に説明する。

10

20

30

40

#### [0023]

#### 「実施の形態]

(スイッチング電源装置の全体構成例)

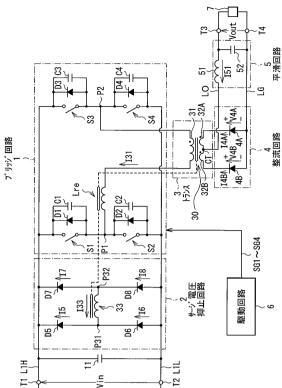

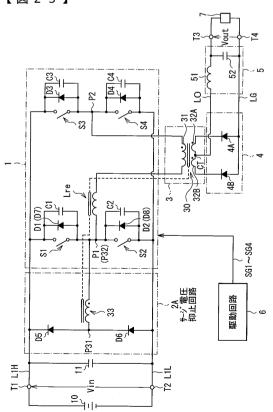

図1は、本発明の一実施の形態に係るスイッチング電源装置の回路構成を表すものであり、図2は、図1に示したスイッチング電源装置において、後述する駆動回路6を除く部分の等価回路構成を表すものである。このスイッチング電源装置は、高圧バッテリ10から供給される高圧の直流入力電圧Vinをより低い直流出力電圧Voutに変換し、図示しない低圧バッテリに供給して負荷7を駆動するDC-DCコンバータとして機能するものである。

## [0024]

このスイッチング電源装置は、1次側高圧ラインL1Hと1次側低圧ラインL1Lとの間に設けられた入力平滑コンデンサ11、ブリッジ回路1およびサージ電圧抑止回路2と、磁芯30、第1の巻線(1次側巻線)31(31A~31D))、第2の巻線(2次側巻線)32A,32Bおよび第3の巻線33(33A,33B)を有するトランス3とを備えている。1次側高圧ラインL1Hの入力端子T1と1次側低圧ラインL1Lの入力端子T2との間には、高圧バッテリ10から出力される直流入力電圧Vinが印加されるようになっている。このスイッチング電源装置はまた、トランス3の2次側に設けられた整流回路4と、この整流回路4に接続された平滑回路5と、ブリッジ回路1を駆動する駆動回路6とを備えている。

## [0025]

入力平滑コンデンサ11は、入力端子T1,T2から入力された直流入力電圧Vinを平滑化するためのものである。

#### [0026]

ブリッジ回路1は、4つのスイッチング素子S1~S4と、これらスイッチング素子S1~S4に対してそれぞれ並列接続されたコンデンサC1~C4およびダイオードD1~D4とを有しており、フルブリッジ型の回路構成となっている。具体的には、スイッチング素子S1,S2の一端同士が接続点P1において互いに接続されると共に、スイッチング素子S3,S4の一端同士が接続点P2において互いに接続され、これらの一端(接続 スイッチング素子S3,S4の一端同士が接続点P2において互いに接続され、これらの一端(接続 31を介して互いに接続されている。スイッチング素子S1,S3の他端同士は互いに接続されている。ブリッジ回路1はこのように接続されると共にスイッチング素子S2,S4の他端同士は互いに接続され、これらの他端同士は、それぞれ入力端子T1,T2に接続されている。ブリッジ回路1はこのようは構成により、駆動回路6から供給される駆動信号SG1~SG4に応じて、入力端子T1,T2間に印加される直流入力電圧Vinを交流電圧に変換し出力するようになっている。

## [0027]

なお、これらスイッチング素子S1~S4としては、例えば電界効果型トランジスタ(MOS-FET;MetalOxideSemiconductor-FieldEffectTransistor)やIGBT(Insulated Gate Bipolor Transistor)などのスイッチ素子が用いられる。これらスイッチ素子として<math>MOS-FETを用いた場合には、上記コンデンサ  $C1 \sim C4$  およびダイオード  $D1 \sim D4$  をそれぞれ、このMOS-FET の寄生容量または寄生ダイオードから構成することが可能である。また、上記コンデンサ  $C1 \sim C4$  をそれぞれ、ダイオード  $D1 \sim D4$  の接合容量で構成することも可能である。このように構成した場合、スイッチ素子とは別個にコンデンサ  $C1 \sim C4$  やダイオード  $D1 \sim D4$  を設ける必要がなくなり、回路構成を簡素化することができる。

#### [0028]

このブリッジ回路1はまた、トランス3のリーケージインダクタンスにより構成された 共振用のインダクタLreを有している。すなわち、このインダクタLreは、図1中に 示したように、トランス3の1次側巻線31、2次側巻線32および第3の巻線と互いに 磁気的に結合されている。また、このインダクタLreのインダクタンスは、1次側巻線 31、2次側巻線32A,32Bおよび第3の巻線33のインダクタンスと比べ、非常に 10

20

30

40

20

30

40

50

小さくなるように設定されている。なお、図2および後述する図3においては、説明上の便宜のため、インダクタLreの図示を省略している。インダクタLreは、一端が接続点P1に接続され、他端がトランス3の1次側巻線31を介して接続点P2に接続されている。すなわち、このインダクタLreは、スイッチング素子S1,S2とスイッチング素子S3,S4とから構成されるブリッジ回路に、Hブリッジ接続されている。このような構成によりインダクタLreは、ブリッジ回路1内のコンデンサC1~C4と共にLC直列共振回路を構成し、このLC直列共振回路による共振特性を利用することで、後述するように、スイッチング素子S1~S4における短絡損失を抑制するようになっている。【0029】

サージ電圧抑止回路 2 は、逆方向接続された 2 対のダイオード D 5 , D 6 およびダイオード D 7 , D 8 と、前述した第 3 の巻線 3 3 とを有している。ダイオード D 5 , D 7 のカソードは互いに 1 次側高圧ライン L 1 Hに接続され、ダイオード D 5 , D 7 のアノードとダイオード D 6 , D 8 のアノードとダイオード D 6 のカソードとは互いに接続点 P 3 1 において接続されている。そして、ライオード D 8 のカソードとは互いに接続点 P 3 2 において接続されている。そして、これらの接続点 P 3 1 , P 3 2 間に第 3 の巻線 3 3 が接続されている。 具体的には、第 3 の巻線 3 3 A の一端は接続ライン L 3 1 を介して接続点 P 3 1 に接続され、第 3 の巻線 3 3 A の他端は第 3 の巻線 3 3 B の一端に接続されている。すなわち、第 3 の巻線 3 3 L、ダイオード D 5 ~ D 8 から構成されるフルブリッジ回路に対して H ブリッジ接続されている。この 6 およびダイオード D 7 , D 8 による第 3 の巻線 3 3 の両端の電圧に対するクランプ作用により、後述する整流回路 4 内の整流ダイオード 4 A , 4 B に加わるサージ電圧を抑制するようになっている。

#### [0030]

トランス3は、後述する互いに対向する上部コアUCおよび下部コアDCから構成され る磁芯 3 0 と、 4 つの 1 次側巻線 3 1 A ~ 3 1 D と、 2 つの 2 次側巻線 3 2 A , 3 2 B と 、 2 つの第 3 の巻線 3 3 A , 3 3 B とを有している。ここで、 1 次側巻線 3 1 A ~ 3 1 D および2次側巻線32A,32B間と、1次側巻線31A~31Dおよび第3の巻線33 A , 3 3 B 間とはそれぞれ、 2 次側巻線 3 2 A , 3 2 B および第 3 の巻線 3 3 A , 3 3 B 間と比べて、疎に磁気結合されている。すなわち、1次側巻線31A~31Dおよび2次 側巻線 3 2 A , 3 2 B 間と、 1 次側巻線 3 1 A ~ 3 1 D および第 3 の巻線 3 3 A , 3 3 B 間とはそれぞれ、疎に磁気結合される一方、2次側巻線32A,32Bおよび第3の巻線 3 3 A , 3 3 B 間は、密に磁気結合されている。また、 1 次側巻線 3 1 A ~ 3 1 D は、互 いに直列接続されている。具体的には、1次側巻線31Aでは、一端が接続ラインL21 を介して接続点P2に接続され、他端が1次側巻線31Bの一端に接続されている。そし て、1次側巻線31Bの他端は1次側巻線31Cの一端に接続され、1次側巻線31Cの 他端は1次側巻線31Dの一端に接続され、1次側巻線31Dの他端は、接続点P1に接 続されている。ここで、1次側巻線31A~31Dおよび2次側巻線32A,32Bのリ ーケージインダクタンスとして、前述したインダクタLreが存在している。トランス3 の2次側では、2次側巻線32A,32Bが互いに直列接続されている。具体的には、 次側巻線32Aの一端が後述する整流ダイオード4Aのカソードに接続され、2次側巻線 3 2 B の一端が後述する後述する整流ダイオード 4 B のカソードに接続されている。これ らの2次側巻線32A,32Bの他端同士は、センタタップCTで互いに接続され、この センタタップCTからの配線が出力ラインLOに導かれている。また、第3の巻線33A では、一端が接続ラインL31を介して接続点P31に接続され、他端が第3の巻線33 Bの一端に接続されている。そして、第3の巻線33Bの他端は、接続ラインL32を介 して接続点 P 3 2 に接続されている。このトランス 3 は、ブリッジ回路 1 によって生成さ れた交流電圧(トランス3に入力される交流電圧)を降圧し、2次側巻線32A,32B の各端部から、互いに180度位相が異なる交流電圧を出力するようになっている。この 場合の降圧の度合いは、1次側巻線31A~31Dと2次側巻線32A,32Bとの巻数 比によって定まる。なお、このトランス3の詳細構成については、後述する。

#### [0031]

整流回路 4 は、一対の整流ダイオード 4 A , 4 B からなる単相全波整流型のものである。整流ダイオード 4 A のカソードは 2 次側巻線 3 2 A の一端に接続され、整流ダイオード 4 B のカソードは 2 次側巻線 3 2 B の一端に接続されている。これらの整流ダイオード 4 A , 4 B のアノード同士は互いにセンタタップ C T において接続され、接地ライン L G に 導かれている。つまり、この整流回路 4 はセンタタップ型のアノードコモン接続の構成と なっており、トランス 3 からの出力交流電圧の各半波期間を、それぞれ整流ダイオード 4 A , 4 B によって個別に整流している。

## [0032]

平滑回路 5 は、チョークコイル 5 1 と出力平滑コンデンサ 5 2 とを含んで構成されている。チョークコイル 5 1 は出力ラインLOに挿入配置されており、一端がセンタタップ C T に接続され、他端が出力ラインLOの出力端子 T 3 に接続されている。出力平滑コンデンサ 5 2 は、出力ラインLOと接地ラインLGとの間に接続されている。また、接地ラインLGの端部には、出力端子 T 4 が設けられている。このような構成により平滑回路 5 では、整流回路 4 で整流された電圧を平滑化して直流出力電圧 V out を生成し、これを出力端子 T 3 , T 4 から低圧バッテリ(図示せず)に出力して給電するようになっている。

#### [0033]

駆動回路 6 は、ブリッジ回路 1 内のスイッチング素子 S 1 ~ S 4 を駆動するためのものである。具体的には、スイッチング素子 S 1 ~ S 4 に対してそれぞれ駆動信号 S G 1 ~ S G 4 を供給し、これらスイッチング素子 S 1 ~ S 4 をオン・オフ制御するようになっている。また、この駆動回路 6 は、後述するようにこれらスイッチング素子 S 1 ~ S 4 に対してスイッチング位相制御を行い、スイッチング位相差を適切に設定することで、直流出力電圧 Vout を安定化させるようになっている。

#### [0034]

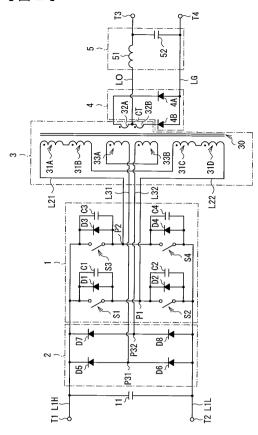

## (トランス3の詳細構成)

次に、図3を参照して、本実施の形態のトランス3の詳細構成について説明する。図3 は、トランス3における主要部の外観構成を分解斜視図で表したものである。

## [0035]

トランス3は、互いに対向する上部コアUCおよび下部コアDCからなるコア材(磁芯30)に対して、1次側巻線31A~31Dと、2次側巻線32A,32Bと、第3の巻線33A,33Bとが、以下説明する3つの脚部の延在方向(垂直方向)に垂直な面内(水平面内)に巻回された構造となっている。なお、1次側巻線31A~31Dおよび第3の巻線33A,33Bは、例えばプリントコイルにより構成され、2次側巻線32A,32Bは、例えば板金(板状導電部材)により構成されている。

# [0036]

上部コアUCは、ベースコアUCbと、このベースコアUCbから上記垂直方向に延びた3本の脚部分である第1脚部UC1、第2脚部UC2および中央脚部(共通脚部)UCcとから構成されている。下部コアDCは、ベースコアDCbと、このベースコアDCbから上記垂直方向に延びた3本の脚部分である第1脚部DC1、第2脚部DC2および第2脚部UC2、DC2は、矩形状のベースコアUCb,DCbにおける両端部に配置され、中央脚部UC2、DC2は、ベースコアUCb,DCbにおける両端部に配置され、中央脚部UCc,DCcは、ベースコアUCb,DCbにおいて第1脚部UC1、DC1および第2脚部UC2、DC2の間(中間部)に配置されている。すなわち、上部コアUCよび第2脚部UC1、UC2、DC1、DC2、DCcは、互いに対向する2つのベースコアUCb,DCbには、DC2、DCcは、互いに対向する2つのベースコアUCb,DCbにを磁気的に連結するようになっている。なお、上部コアUCおよび下部コアDCはそれぞれ、例えばフェライトなどの磁性材料により構成されている。また、以下説明する1次側巻線31A~31D、2次側巻線32A,32Bおよび第3の巻

10

20

30

40

線33A,33Bを構成するプリントコイルや板金はそれぞれ、例えば銅やアルミニウムなどの導電性材料により構成されている。

#### [0037]

1次側巻線31A,31Cはそれぞれ、第1脚部UC1,DC1および中央脚部UCc,DCcを巻回しており、1次側巻線31B,31Dはそれぞれ、第2脚部UC2,DC2および中央脚部UCc,DCcを巻回している。2次側巻線32A,32Bはそれぞれ、1次側巻線31A,31Bと1次側巻線31C,31Dとの間に配置されており、中央磁芯UCc,DCcを巻回している。第3の巻線33Aは、2次側巻線32Aと1次側巻線31A,31Bとの間に配置されており、中央磁芯UCc,DCcを巻回している。第3の巻線33Bは、2次側巻線32Bと1次側巻線31C,31Dとの間に配置されており、中央磁芯UCc,DCcを巻回している。第3の巻線33Bは、2次側巻線32Bと1次側巻線31C,31Dおよびに、1次側巻線31A~31Dおよび第3の巻線33A,33B間とはそれぞれ、疎に磁気結合される一方、2次側巻線32A,32Bおよび第3の巻線33A,33B間は、密に磁気結合されている。

#### [0038]

なお、ここでは、1次側巻線31A~31D、2次側巻線32A,32Bおよび第3の巻線33A,33Bがそれぞれ、配線(接続ラインL21,L22、接続ラインL31,L32、出力ラインLOまたは接地ラインLG)を介して、プリントコイルまたは板金の面内方向に沿って外部から取り出しが可能なように構成されている。

## [0039]

このような構成によりトランス3では、例えば図3の矢印で示したように、1次側巻線31A~31D、2次側巻線32A,32Bおよび第3の巻線33A,33Bを流れる電流によって、3つの脚部UC1~UC2,DC1~DC2,UCc,DCcおよび2つのベースコアUCb,DCbの内部に、磁束を構成する磁路(還流磁路)が形成されるようになっている。なお、図3中の1次側巻線31A~31D、2次側巻線32A,32B、第3の巻線33A,33BおよびベースコアUCb,DCb内に示した磁束の向きを表す矢印は、実線のものが、接続ラインL21から実線で示した向きの電流が流れるときに形成されるものに、破線のものが、接続ラインL22から破線で示した向きの電流が流れるときに形成されるものに、それぞれ対応している。

# [0040]

ここで、入力端子T1,T2が本発明における「入力端子対」の一具体例に対応し、出力端子T3,T4が本発明における「出力端子対」の一具体例に対応する。また、1次側巻線31が本発明における「第1の巻線」の一具体例に対応し、2次側巻線32A,32Bが本発明における「第2の巻線」の一具体例に対応する。また、ブリッジ回路1が、本発明における「第1整流素子」の一具体例に対応し、ダイオードD5~D8が本発明における「第2整流素子」の一具体例に対応し、ダイオードD5~D8が本発明における「第2整流素子」の一具体例に対応し、ダイオードD1~D4が本発明における「第3整流素子」の一具体例に対応し、ダイオードD1~D4が本発明における「第3整流素子」の一具体例に対応する。また、スイッチング素子S1,S2により形成されるアームとが、本発明における「スイッチング回路における2つのアーム」の一具体例に対応する。また、ダイオードD5,D6により形成されるアームとダイオードD7,D8により形成されるアームとが、本発明における「サージ電圧抑止回路における2つのアーム」の一具体例に対応する。

# [0041]

次に、本実施の形態のスイッチング電源装置の作用および効果について説明する。

#### [0042]

(1.スイッチング電源装置の基本動作)

最初に、このスイッチング電源装置の基本動作について説明する。

#### [ 0 0 4 3 ]

このスイッチング電源装置では、ブリッジ回路1において、入力端子T1,T2から供

10

20

30

40

給される直流入力電圧 Vinがスイッチングされて交流電圧が生成され、この交流電圧がトランス 3 の 1 次側巻線 3 1 ( 3 1 A ~ 3 1 D)へ供給される。そしてトランス 3 では交流電圧が変圧され、 2 次側巻線 3 2 A , 3 2 B から、変圧された交流電圧が出力される。

#### [0044]

整流回路 4 では、トランス 3 から出力された交流電圧が、整流ダイオード 4 A , 4 B によって整流される。これにより、センタタップ C T (出力ライン L O)と整流ダイオード 4 A , 4 B の接続点(接地ライン L G)との間に、整流出力が発生する。

## [0045]

平滑回路5では、整流回路4において発生する整流出力が、チョークコイル51と出力平滑コンデンサ52とによって平滑化され、出力端子T3,T4から直流出力電圧Voutとして出力される。そしてこの直流出力電圧Voutは、図示しない低圧バッテリに給電されてその充電に供されると共に、負荷7が駆動される。

#### [0046]

(2.サージ電圧抑止動作)

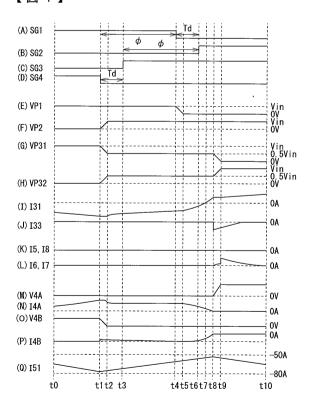

次に、図4~図16を参照して、本発明の主な特徴である、整流回路4内の整流ダイオード4A,4Bに加わるサージ電圧を抑止する動作について詳細に説明する。

#### [0047]

図4は、図1のスイッチング電源装置における各部の電圧波形または電流波形をタイミング波形図(タイミング t 0 ~ t 1 0 )で表したものであり、図中の(A) ~ (D)は駆動信号SG1~SG4の電圧波形を、(E)~(H)は接続点P1,P2,P31,P32の電位VP1,VP2,VP31,VP32を、(I)はトランス3の1次側巻線31を流れる電流I31を、(J)はトランス3の第3の巻線33を流れる電流I33を、(K)はサージ電圧抑止回路2におけるダイオードD5,D8を流れる電流I5,I8を、(L)はサージ電圧抑止回路2におけるダイオードD6,D7を流れる電流I5,I8を、(M),(O)はそれぞれ整流ダイオード4A,4Bのアノード・カソード間に加わる逆電圧V4A,V4Bを、(N),(P)はそれぞれ整流ダイオード4A,4Bを流れる電流I4A,I4Bを、(Q)はチョークコイル51を流れる電流I51を、それぞれ表している。なお、各電圧の方向は図1に矢印で示したとおりであり、「-」から「+」の方向を正方向としている。また、各電流の方向も、図1に矢印で示した方向を正方向としている。

#### [0048]

また、図5~図15は、図4の各タイミング(タイミングt0~t10)におけるスイッチング電源装置の動作状態を表したものであり、図16は、図4で示したタイミング以降(タイミングt10~t20(t0))の各部の電圧波形または電流波形を表したものである。なお、図4,図16でそれぞれ示したタイミングは、それぞれスイッチング電源装置の動作の半周期分のものを表しており、これらの動作を合わせて一周期分の動作となっている。

#### [0049]

(2-1.前半の半周期分のサージ電圧抑止動作)

まず、図4~図15を参照して、前半の半周期分の動作について説明する。

# [0050]

スイッチング素子S1~S4の駆動信号SG1~SG4(図4(A)~(D))についてみると、これらのスイッチング素子は、2つのスイッチング素子対に区分されることが分かる。具体的には、スイッチング素子S1,S2はいずれも時間軸上における固定タイミングでオンするように制御され、「位相固定側スイッチング素子」と称される。また、スイッチング素子S3,S4はいずれも時間軸上における可変タイミングでオンするように制御され、「位相シフト側スイッチング素子」と称される。

#### [0051]

また、これらスイッチング素子S1~S4は、スイッチング動作のいかなる状態においても、直流入力電圧Vinが印加された入力端子T1,T2が電気的に短絡されない組み合

10

20

30

40

20

30

40

50

わせおよびタイミングで駆動される。具体的には、スイッチング素子S3,4(位相シフト側スイッチング素子)は、同時にオンとなることはなく、また、スイッチング素子S1,S2(位相固定側スイッチング素子)も、同時にオンとなることはない。これらが同時にオンとなるのを回避するためにとられる時間的間隔は、デッドタイムTdと称される(図4(A),(D))。

## [0052]

また、スイッチング素子S1,S4は同時にオンとなる期間を有し、この同時にオンとなる期間において、トランス3の1次側巻線31が励磁される。そしてこれらスイッチング素子S1,S4は、スイッチング素子S1(位相固定側スイッチング素子)を基準としてスイッチング位相差をなすように動作する(図4(A),(D))。また同様に、スイッチング素子S2,S3は同時にオンとなる期間を有し、この同時にオンとなる期間である。そしてこれる。そしてスイッチング素子S2,S3は同時にオンとなる期間を有し、この同時にオンとなる期間である。そしてスイッチング素子S2,S3は、スイッチング素子S2(位相固定側スイッチング表子S2,S3は、スイッチング素子S2(位相固定側スイッチング。このに、スイッチングを表達としてスイッチング位相差をなすように動作する(図4(B),(C))のでは、スイッチング素子S1とスイッチング素子S4とのスイッチング位相差がそれぞれではあると、スイッチング素子S1およびスイッチングを表すS1が同時にオンになっている時間がそれぞれ変化する。これにより、トランス3の1次側巻線31に印加される交流電圧のデューティ比が変化し、直流出力電圧Voutが安定化されるようになっている

[0053]

まず、図5に示したタイミングt0~t1までの期間では、スイッチング素子S1,S4がオン状態となっており(図4(A),(D))、スイッチング素子S2,S3はオフ状態となっている(図4(B),(C))。また、接続点P1の電位VP1=Vin(図4(E))、接続点P2の電位VP2=0V(図4(F))、接続点P31の電位VP31=Vin(図4(G))および接続点P32の電位VP32=0V(図4(H))となっている。したがって、ブリッジ回路1には図5に示したようなループ電流Iaが流れ、インダクタLreが励磁されると共に、トランス3の1次側から2次側へ電力伝送が行われる。よって、トランス3の2次側には、整流ダイオード4Aおよびチョークコイル51を介するループ電流Ixaが流れ、負荷7が駆動される。なお、この期間では、整流ダイオード4Aには順方向電圧が印加されるため、逆電圧V4A=0V(図4(M))となる一方、整流ダイオード4Bには、逆電圧V4Bが印加されている(図4(O))。

[0054]

次に、図6で示したタイミングt1~t2までの期間では、タイミングt1でスイッチング素子S4がオフ状態となる(図4(D))。すると、コンデンサC3,C4とインダクタLreとが協働してLC直列共振回路が構成され、LC共振動作が行われる。したがって、図6に示したようなループ電流Ib,Icが流れ、コンデンサC3が放電される一方、コンデンサC4は充電されるため、接続点P2の電位VP2が徐々に上昇していき、タイミングt2でVP2=Vinとなる(図4(F))。また、このとき整流ダイオード4Bの逆電圧V4Bが徐々に下降していき、タイミングt2で0Vとなる(図4(O))。

[0055]

ここで、図7で示したように、タイミングt2でVP2 = Vinとなると(図4(F))、ダイオードD3が導通するようになる。また、このようにVP2 = VinとなってダイオードD3が導通した後に、図8に示したように、タイミングt3でスイッチング素子S3がオン状態となることで(図4(C))、ゼロボルトスイッチング(ZVS)動作がなされ、その結果、スイッチング素子S3における短絡損失が抑制される。

[0056]

また、このタイミング t 2 ~ t 4 の期間では、タイミング t 0 ~ t 1 の期間で励磁されることによりインダクタ L r e に蓄えられたエネルギーが、このインダクタ L r e の両端

20

30

40

50

に接続された回路において、電流として循環しようとする。具体的には、図8に示したように、インダクタLreの一端(1次側巻線31側)からスイッチング素子S1の他端(1次側高圧ラインL1H側)までの間の電位差が互いに等しくなるように、ループ電流IEが流れる。ここで、このループ電流Ieの経路では、この電位差は、1次側巻線31の両端間の電圧V31と、スイッチング素子S3の両端間の電圧VS3との和になる。V31は、1次側巻線と2次側巻線との巻数比をnとすると、整流ダイオード4Aの順方向電圧降下をこの巻数比nで割ったものとなる。一方、VS3は、スイッチング素子S3がオフ状態のとき(タイミングt2~t3の期間)には、ダイオードD3の順方向電圧降下となり、スイッチング素子S3がオン状態のとき(タイミングt3~t4の期間)には、スイッチング素子S3のオン抵抗と流れる電流との積になる。

[0057]

ここで、これらダイオード4A,D3の順方向電圧降下の値は、流れている順方向電流値や周囲の温度によって変化するが、ループ電流 I e は、上記電位差が互いに等しくなるように流れる。また、トランス3でのアンペア・ターンが等しくなると共に、2次側巻線32A,32Bをそれぞれ流れる電流の和がチョークコイル51を流れる電流 I 5 1 に等しくなるように、この電流 I 5 1 が、整流ダイオード4Aを流れるループ電流 I × a と、整流ダイオード4Bを流れるループ電流 I × b とに分流する。

[0058]

次に、図9で示したように、タイミング t 4 になると、スイッチング素子 S 1 がオフ状態となる(図4(A))。すると、コンデンサ C 1 ,C 2 とインダクタ L r e とが協働して L C 直列共振回路が構成され、L C 共振動作が行われる。したがって、図9 に示したようなループ電流 I f ,I g が流れる。よって、コンデンサ C 2 が放電される一方、コンデンサ C 1 は充電されるため、接続点 P 1 の電位 V P 1 が徐々に下降していき、タイミング E 5 で V P 1 = 0 V となる(図 E 4 E ))。

[0059]

ここで、図10で示したように、タイミング t 5 で V P 1 = 0 V となると(図4(E))、ダイオード D 2 が導通するようになり、図に示したようなループ電流 I h が流れる。また、このように V P 1 = 0 V となってダイオード D 2 が導通した後に、図11に示したように、タイミング t 6 でスイッチング素子 S 2 がオン状態となることで(図4(B)) Z V S 動作がなされ、その結果、スイッチング素子 S 2 における短絡損失が抑制される。

[0060]

[0061]

20

30

40

50

ランス3でのアンペア・ターンが等しくなると共に、トランス3の2次側巻線32A,32Bをそれぞれ流れる電流の和がチョークコイル51を流れる電流I51に等しくなるように、この電流I51が、整流ダイオード4Aを流れるループ電流Ixaと、整流ダイオード4Bを流れるループ電流Ixbとに分流する。ただし、整流ダイオード4Aを流れる電流I4Aは徐々に減少していく一方、整流ダイオード4Bを流れる電流I4Bは徐々に増加していく(図4(N),(P))。そしてI4A=0Aとなり、トランス3の2次側巻線32Bを流れる電流がチョークコイル51を流れる電流I51と等しくなったとき、このトランス3でのアンペア・ターンはこれ以上増加しないため、I31の増加が妨げられようとする。ただし、以下説明するサージ電圧抑止回路2における作用により、依然としてI31は増加していくことになる。このときが、タイミングt8に相当する。

[0062]

次に、図14に示したタイミング t 8 ~ t 9までの期間では、接続点 P 3 1 の電位 V P 3 1 が緩やかに下降していく(図4(G))と共に、接続点 P 3 2 の電位 V P 3 2 が緩やかに上昇していく(図4(H))。これに伴い、トランス 3 の 1 次側巻線 3 1 の両端間の電圧 V 3 1 の絶対値が増加すると共に、 2 次側巻線 3 2 A , 3 2 B にもそれぞれ電圧 V 3 2 A , V 3 2 B が発生し、 V 3 2 A = V 3 2 B = V 3 1 / n (n; トランス 3 の 1 次側巻線と 2 次側巻線との巻数比)、(整流ダイオード 4 B のカソードの電位) < (センタタップ C T の電位) < (整流ダイオード 4 A のカソードの電位)となる。上記のように V P 3 1 が緩やかに下降していくと共に V P 3 2 が緩やかに上昇していき、 V P 3 1 = 0 V および V P 3 2 = V in (図4 (G)), (I))となったときが、タイミング t 9 に相当する。すると、このタイミング t 9 において、 V P 3 1 = 0 V (図4 (G)) および V P 3 2 = V in (図4 (H)) であることから、ダイオード D 6 , D 7 の両端の電圧はいずれも 0 V となり、ダイオード D 6 , D 7 が導通することにより、第 3 の巻線 3 3 に電流 I 3 3 が流れるようになる(図4 (J))。

[0063]

したがって、図15に示したタイミング  $t9 \sim t10$ までの期間では、ダイオードD6 ,D7が導通することから、トランス3の第3の巻線33の両端の電圧がVinにクランプされ、これによりトランスの2次側巻線32Bの両端の電圧V32Bが、Vin/n(n;トランス3の1次側巻線と2次側巻線との巻数比)にクランプされる。このため、整流ダイオード4Aに加わる逆電圧V4Aは、整流回路4がセンタタップ型の構成であることから、2×Vin/nよりも大きくなることはない(図4(M))。言い換えると、この整流ダイオード4Aに加わる逆電圧V4Aは、最大でも2×Vin/n以下となり、サージ電圧の上昇が抑制される。

[0064]

また、このタイミング t 9 ~ t 1 0 までの期間では、トランス3の2次側巻線32Bの両端の電圧 V 3 2 B によってチョークコイル5 1 が励磁されるのに伴い、このチョークコイル5 1 を流れる電流 I 5 1 が増加し、I 3 1 = (2次側巻線32 A を流れる電流 I 3 2 A) + (2次側巻線32 B を流れる電流 I 3 2 B) = I 3 2 B = I 5 1 であることから、I 3 1 も増加していく(図4(I))。また、I 3 1 の増加により、I 6 , I 7 が減少する(図4(L))。I 6 , I 7 の A となったときが、図16に示したタイミング t 10に相当する。以上で、最初の半周期分の動作が終了する。

[0065]

(2-2.後半の半周期分のサージ電圧抑止動作)

次に、図 1 6 を参照して、図 2 で示したタイミング t 0 ~ t 1 0 以降の半周期分 ( タイミング t 1 0 ~ t 2 0 ( t 0 ) ) の動作について説明する。

[0066]

この半周期分の動作も、基本的には図 4 ~ 図 1 5 で説明した半周期分の動作と同様である。すなわち、タイミング t 1 0 ~ t 1 1 までの期間では、スイッチング素子 S 2 , S 3 がオン状態となっており(図 1 6 6 8 9 , 9 9 9 、スイッチング素子 9 9 9 、状態となっている(図 1 9 9 9 9 、また、接続点 9 9 9 の電位 9 9 9 9 、

20

30

40

50

16(E))、接続点 P 2の電位 V P 2 = V in(図 16(F))、接続点 P 3 1の電位 V P 3 1 = 0 V (図 16(G)) および接続点 P 3 2の電位 V P 3 2 = V in(図 16(H)) となっている。したがって、ブリッジ回路 1にはループ電流が流れ、インダクタLreが励磁されると共に、トランス 3の 1次側から 2次側へ電力伝送が行われる。よって、トランス 3の 2次側には、整流ダイオード 4 B およびチョークコイル 5 1を介するループ電流が流れ、負荷 7 が駆動される。なお、この期間では、整流ダイオード 4 B には順方向電圧が印加されるため、逆電圧 V 4 B = 0 V (図 16(O))となる一方、整流ダイオード 4 A には、逆電圧 V 4 A が印加されている(図 16(M))。

[0067]

[0068]

ここで、タイミング t 1 2 で V P 2 = 0 V となると (図 1 6 ( F ) )、ダイオード D 4 が導通するようになる。また、このように V P 2 = 0 V となってダイオード D 4 が導通した後に、タイミング t 1 3 でスイッチング素子 S 4 がオン状態となることで (図 1 6 ( D ) )、 Z V S 動作がなされ、その結果、スイッチング素子 S 4 における短絡損失が抑制される。

[0069]

[0070]

次に、タイミング t 1 4 になると、スイッチング素子 S 2 がオフ状態となる(図 1 6 ( B ) )。すると、コンデンサ C 1 , C 2 とインダクタ L r e とが協働して L C 直列共振回路が構成され、L C 共振動作が行われる。したがって、 2 つのループ電流が流れることにより、コンデンサ C 2 が充電される一方、コンデンサ C 1 は放電されるため、接続点 P 1 の電位 V P 1 が徐々に上昇していき、タイミング t 1 5 で V P 1 = V inとなる(図 1 6 ( E ) )。

[0071]

ここで、タイミング t 15で V P 1 = V inとなると(図 16 (E))、ダイオード D 1 が導通するようになる。また、このように V P 1 = V inとなってダイオード D 1 が導通した後に、タイミング t 16でスイッチング素子 S 1 がオン状態となることで(図 16 (A)) Z V S 動作がなされ、その結果、スイッチング素子 S 1 における短絡損失が抑制される。

[0072]

次に、タイミング t 1 6 ~ t 1 7 までの期間では、インダクタLreに蓄えられたエネルギーは、コンデンサ C 1 , C 2 における充放電が終了した後も、1 つのループ電流によって入力平滑コンデンサ 1 1 に回生される。そしてこの入力平滑コンデンサ 1 1 へ回生されるに従ってインダクタLreに蓄えられたエネルギーは減少し、それに伴ってインダク

20

30

40

50

タLreおよび1次側巻線31を流れる電流 I 31の絶対値も減少していく(図16(I))。このため、トランス3でのアンペア・ターンが等しくなると共に、トランス3の2次側巻線32A,32Bをそれぞれ流れる電流の和がチョークコイル51を流れる電流 I 51に等しくなるように、この電流 I 51が、整流ダイオード4Aを流れるループ電流 I x a と、整流ダイオード4Bを流れるループ電流 I x b とに分流する。

## [0073]

次に、タイミングt17になると、インダクタLreに蓄えられたエネルギーがすべて 回生されるため、インダクタLreおよびトランス3の1次側巻線31を流れる電流I3 1 = 0 A ( 図 1 6 ( I ) ) となり、整流ダイオード 4 A を流れる電流 I 4 A = 整流ダイオ ード4Bを流れる電流 I4B(図16(N),(P))となる。そしてこのタイミング t 1 7 から、インダクタLreはこれまでと逆方向のエネルギーを蓄えるようになり、イン ダクタLreおよびトランス3の1次側巻線31には、これまでと反対方向のループ電流 が流れるようになると共に、電流I31はVin/L(L;インダクタLreのインダクタ ンス)の割合で増加していく(図16(I))。このため、トランス3でのアンペア・タ ーンが等しくなると共に、トランス3の2次側巻線32A,32Bをそれぞれ流れる電流 の和がチョークコイル51を流れる電流I51に等しくなるように、この電流I51が、 整流ダイオード4Aを流れるループ電流Ixaと、整流ダイオード4Bを流れるループ電 流Ixbとに分流する。ただし、整流ダイオード4Bを流れる電流I4Bは徐々に減少し ていく一方、整流ダイオード4Aを流れる電流I4Aは徐々に増加していく(図16(N ) , ( P ) ) 。そして I 4 B = 0 A となり、トランス 3 の 2 次側巻線 3 2 A を流れる電流 がチョークコイル51を流れる電流I51と等しくなったとき、このトランス3でのアン ペア・ターンはこれ以上増加しないため、I31の増加が妨げられようとする。ただし、 以下説明するサージ電圧抑止回路2における作用により、依然としてI31は増加してい くことになる。このときが、タイミングt18に相当する。

#### [0074]

次に、タイミング t 1 8 ~ t 1 9 までの期間では、接続点 P 3 2 の電位 V P 3 2 が緩やかに下降していく(図 4 ( H ) )と共に、接続点 P 3 1 の電位 V P 3 1 が緩やかに上昇していく(図 4 ( G ) )。これに伴い、トランス 3 の 1 次側巻線 3 1 の両端間の電圧 V 3 1 が増加すると共に、 2 次側巻線 3 2 A , 3 2 B にもそれぞれ電圧 V 3 2 A , V 3 2 B が発生する。上記のように V P 3 2 が緩やかに下降していくと共に V P 3 1 が緩やかに上昇していき、 V P 3 2 = 0 V および V P 3 1 = V in ( 図 1 6 ( G ) , ( I ) )となったときが、タイミング t 1 9 に相当する。すると、このタイミング t 1 9 において、 V P 3 2 = 0 V ( 図 1 6 ( H ) )および V P 3 1 = V in ( 図 4 ( G ) )であることから、ダイオード D 5 , D 8 の両端の電圧はいずれも 0 V となり、ダイオード D 5 , D 8 が導通することにより、第 3 の巻線 3 3 に電流 I 3 3 が流れるようになる ( 図 1 6 ( J ) )。

## [0075]

したがって、タイミング t 1 9 ~ t 2 0 までの期間では、ダイオード D 5 , D 8 が導通することから、トランス 3 の第 3 の巻線 3 3 の両端の電圧が V inにクランプされ、これによりトランスの 2 次側巻線 3 2 A の両端の電圧 V 3 2 A が、V in / n (n; トランス 3 の 1 次側巻線と 2 次側巻線との巻数比)にクランプされる。このため、整流ダイオード 4 B に加わる逆電圧 V 4 B は、整流回路 4 がセンタタップ型の構成であることから、 2  $\times$  V in / n よりも大きくなることはない(図 1 6 (O))。言い換えると、この整流ダイオード 4 B に加わる逆電圧 V 4 B は、最大でも  $2 \times V$  in / n 以下となり、サージ電圧の上昇が抑制される。

#### [0076]

また、このタイミング t 1 9 ~ t 2 0 までの期間では、トランス 3 の 2 次側巻線 3 2 A の両端の電圧 V 3 2 A によってチョークコイル 5 1 が励磁されるのに伴い、このチョークコイル 5 1 を流れる電流 I 5 1 が増加し、 I 3 1 も増加していく(図 1 6 (I))。また、 I 3 1 の増加により、 I 5 , I 8 が減少する(図 1 6 (I))。 I 5 , I 8 = 0 A となったとき(図 1 6 (I))が、タイミング I 2 0 に相当する。以上で後半の半周期分の動

作が終了し、図4のタイミングt0と等価な状態となる。

#### [0077]

(2-3.本実施の形態と比較例との作用の比較)

次に、図17,図18を参照して、本実施の形態のスイッチング電源装置における整流 ダイオードに加わるサージ電圧の抑制作用と、従来のスイッチング電源装置(比較例1, 2)におけるサージ電圧の抑制作用とについて、比較しつつ詳細に説明する。

#### [0078]

## (比較例の作用)

ここで、図17,図18はそれぞれ、比較例1,2に係るスイッチング電源装置の回路構成を表すものである。具体的には、比較例1は、本実施の形態のサージ電圧抑止回路2が設けられていないものに対応する。また、比較例2は、サージ電圧抑止回路2の代わりに、ダイオードD5およびコンデンサC5とを並列接続してなる素子対と、ダイオードD6およびコンデンサC6とを並列接続してなる素子対とを、互いに直列接続したサージ電圧抑止回路102を設けたものに対応する。

#### [0079]

まず、図17に示した比較例1では、スイッチング素子S1~S4におけるドレイン・ソース間の静電容量(コンデンサC1~C4)と、トランス3のリーケージインダクタンスLreとを利用してLC共振動作を行うことにより、ZVS動作を実現している。これにより、スイッチング素子S1~S4における短絡損失を抑制することができる。

## [0800]

ところが、トランス3のリーケージインダクタンスLreを共振のインダクタンス成分として利用しているため、1次側巻線31および2次側巻線32A,32Bの結合からなる理想トランス部分と、リーケージインダクタンスLreとを分離できない。そのため、理想トランス部分における端子両端の容量成分と、リーケージインダクタンスLreとによる共振動作がなされることとなり、整流ダイオード4A,4Bに対してサージ電圧をもたらしてしまうことになる。

## [0081]

一方、図18に示した比較例2では、上記したZVS動作を実現するために、トランス3は結合の高いものとすると共に、LC共振用のインダクタンス成分として、トランス3とは別体の共振用インダクタLrを設けている。ここで、トランス3における端子両端の容量成分とこの共振用インダクタLrとによる共振動作がなされた場合、これらのトランス3と共振用インダクタLrとの接続点P3は、直流入力電圧Vinの2倍の振幅で共振しようとする。このとき、トランス3と共振用インダクタLrとの接続点P3の電圧が直流入力電圧Vinを超えようとすると、この直流入力電圧VinにクランプされるようにダイオードD5,D6が作用し、整流ダイオード4A,4Bにおけるサージ電圧の発生が抑えられる。

# [0082]

しかしながら、この手法を用いるにはトランス3とは別に共振用インダクタLrを設ける必要があることから、装置内の部品点数が増加してしまうことになる。

#### [0083]

# (本実施の形態の作用)

これに対して本実施の形態では、1次側巻線31A~31Dおよび2次側巻線32A,32B間と、1次側巻線31A~31Dおよび第3の巻線33A,33B間とがそれぞれ、2次側巻線32A,32Bおよび第3の巻線33A,33B間と比べて疎に磁気結合されていることにより、トランス3においてリーケージインダクタンス成分(インダクタLre)が生ずる。そして、このインダクタLreと、スイッチング素子S1~S4の両端間の容量成分(コンデンサC1~C4)とから構成されるLC共振回路による共振動作によって、記比較例2のようにトランス3とは別個のインダクタを設けることなく、ZVS動作が実現される。また、サージ電圧抑止回路2内のダイオードD5~D8による第3の巻線33の両端の電圧に対するクランプ作用により、トランス3における端子両端の容量

10

20

30

40

20

30

40

50

成分とインダクタLreとによる共振動作に起因して整流ダイオード4A,4Bに加わるサージ電圧が抑制される。

#### [0084]

以上のように本実施の形態では、1次側巻線31A~31Dおよび2次側巻線32A,32B間と、1次側巻線31A~31Dおよび第3の巻線33A,33B間とがそれぞれ、2次側巻線32A,32Bおよび第3の巻線33A,33B間と比べて疎に磁気結合されているようにすると共に、これにより生ずるリーケージインダクタンス成分(インダクタLre)とスイッチング素子S1~S4の両端間の容量成分(コンデンサC1~C4)とによってLC共振回路を構成するようにしたので、トランス3とは別個のインダクタを設けることなく、ZVS動作を実現することができる。また、サージ電圧抑止回路2を設けるようにしたので、ダイオードD5~D8による第3の巻線33の両端の電圧に対するクランプ作用により、トランス3における端子両端の容量成分とインダクタLreとによる共振動作に起因して整流ダイオード4A,4Bに加わるサージ電圧を抑制することができる。よって、装置内の部品点数を削減しつつ、スイッチング素子S1~S4における短絡損失を抑制すると共に整流ダイオード4A,4Bに印加されるサージ電圧を抑制することが可能となる。

#### [0085]

また、サージ電圧を抑制することができることにより、整流素子での損失を低減し、装置の効率を向上させることが可能となる。また、整流素子での損失を低減することにより、素子での発熱を抑制することも可能となる。

#### [0086]

また、サージ電圧の上昇を抑制することにより、耐圧の低い整流素子(整流ダイオード)を使用することでき、部品コストを低減することが可能となる。

#### [0087]

次に、本発明の変形例をいくつか挙げて説明する。なお、上記実施の形態における構成要素と同一のものには同一の符号を付し、適宜説明を省略する。

## [0088]

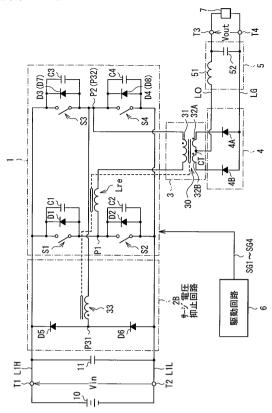

#### 「変形例1]

## (スイッチング電源装置の全体構成例)

図19は、本発明の変形例1に係るスイッチング電源装置の構成(等価回路構成)を表すものである。本変形例のスイッチング電源装置は、上記実施の形態のスイッチング電源装置において、トランス3および整流回路4の代わりに、以下説明するトランス3Aおよび整流回路41を設けるようにしたものである。

#### [0089]

トランス3Aは、後述する互いに対向する上部コアUCAおよび下部コアDCAから構 成される磁芯30Aと、2つの1次側巻線31A,31Bと、4つの2次側巻線32A~ 32Dと、2つの第3の巻線33A,33Bとを有している。ここで、上記実施の形態と 同様に、1次側巻線31A,31Bおよび2次側巻線32A~32D間と、1次側巻線3 1 A , 3 1 B および第 3 の巻線 3 3 A , 3 3 B 間とはそれぞれ、 2 次側巻線 3 2 A ~ 3 2 Dおよび第3の巻線33A,33B間と比べて、疎に磁気結合されている。すなわち、1 次側巻線31A,31Bおよび2次側巻線32A~32D間と、1次側巻線31A,31 B および第 3 の巻線 3 3 A , 3 3 B 間とはそれぞれ、疎に磁気結合される一方、 2 次側巻 線32A~32Dおよび第3の巻線33A,33B間は、密に磁気結合されている。また 1次側巻線31A,31Bは、互いに直列接続されている。具体的には、1次側巻線3 1 A では、一端が接続ラインL21を介して接続点P2に接続され、他端が1次側巻線3 1Bの一端に接続されている。そして、1次側巻線31Bの他端は、インダクタLreお よび接続ラインL22を介して接続点P1に接続されている。トランス3の2次側では、 2次側巻線32A,32Bが互いに直列接続されると共に、2次側巻線32C,32Dが 互いに直列接続されている。具体的には、2次側巻線32Aの一端が後述する整流ダイオ ード4Aのカソードに接続され、2次側巻線32Bの一端が後述する後述する整流ダイオ

20

30

40

50

ード4Bのカソードに接続されている。これらの2次側巻線32A,32Bの他端同士は互いに接続され、出力ラインLOに導かれている。また、2次側巻線32Cの一端は後述する整流ダイオード4Cのカソードに接続され、2次側巻線32Dの一端は後述する後述する整流ダイオード4Dのカソードに接続されている。これらの2次側巻線32C,32Dの他端同士は互いに接続され、出力ラインLOに導かれている。また、第3の巻線33Aでは、一端が接続ラインL31を介して接続点P31に接続され、他端が第3の巻線33Bの一端に接続されている。そして、第3の巻線33Bの他端は、接続ラインL32を介して接続点P32に接続されている。

#### [0090]

整流回路41は、4つの整流ダイオード4A~4Dからなる単相全波整流型のものである。整流ダイオード4Aのカソードは2次側巻線32Aの一端に接続され、整流ダイオード4Bのカソードは2次側巻線32Bの一端に接続されている。これらの整流ダイオード4A,4Bのアノード同士は互いに接続され、接地ラインLGに導かれている。また、整流ダイオード4Cのカソードは2次側巻線32Cの一端に接続され、整流ダイオード4Dのカソードは2次側巻線32Dの一端に接続されている。これらの整流ダイオード4C,4Dのアノード同士は互いに接続され、接地ラインLGに導かれている。つまり、この整流回路41はセンタタップ型のアノードコモン接続の構成となっており、トランス3Aからの出力交流電圧の各半波期間を、それぞれ整流ダイオード4A~4Dによって個別に整流している。

# [0091]

なお、これらのトランス 3 A および整流回路 4 1 において、 2 次側巻線 3 2 A , 3 2 B および整流ダイオード 4 A , 4 B を設けないようにしてもよい。

## [0092]

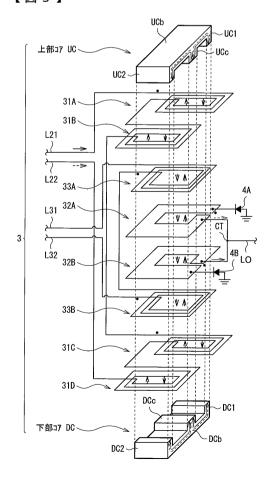

(トランス3Aの詳細構成)

次に、図20~図22を参照して、本変形例のトランス3Aの詳細構成について説明する。図20は、トランス3Aにおける主要部の外観構成を分解斜視図で表したものであり、図21は、このトランス3Aにおける各巻線間の結合係数の一例を表したものである。また、図22は、トランス3Aにおいて形成される還流磁路の例を模式的に表したものである。

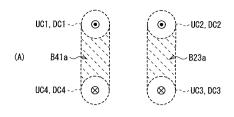

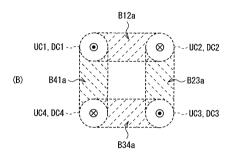

# [0093]

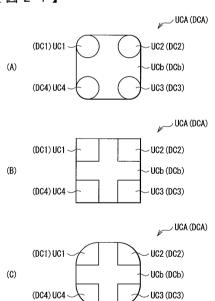

図20に示したように、トランス3Aは、互いに対向する上部コアUCAおよび下部コ アDCAからなるコア材(磁芯30A)に対して、1次側巻線31A,31Bを構成する プリントコイル 3 1 0 と、 2 次側巻線 3 2 A ~ 3 2 D を個別に構成する 4 枚の板金と、第 3の巻線33A,33Bを構成するプリントコイル330とが、それぞれ、以下説明する 4 つの脚部の延在方向(垂直方向)に垂直な面内(水平面内)に巻回された構造となって いる。上部コアUCAは、ベースコアUCbと、このベースコアUCbから上記垂直方向 (貫通方向)に延びた4本の脚部分である第1脚部UC1、第2脚部UC2、第3脚部U C 3 および第 4 脚部 U C 4 とから構成されている。また、下部コア D C A は、ベースコア DCbと、このベースコアDCbから上記垂直方向(貫通方向)に延びた4本の脚部分で ある第1脚部DC1、第2脚部DC2、第3脚部DC3および第4脚部DC4とから構成 されている。これらの第1脚部UC1,DC1、第2脚部UC2,DC2、第3脚部UC 3 , D C 3 および第 4 脚部 U C 4 , D C 4 は、ベースコア U C b , D C b の対向面内で互 いに交差する2直線(2つの対角線)上に、一対ずつ離間して配置されている。そして、 これらの4つの脚部UC1~UC4,DC1~DC4は、互いに対向する2つのベースコ アUCb,DCb同士を磁気的に連結するようになっている。具体的には、ここでは、第 1脚部UC1,DC1、第2脚部UC2,DC2、第3脚部UC3,DC3および第4脚 部UC4,DC4は、ベースコアUCb,DCb上の正方形状の面の四隅をなすように配 置されている。すなわち、これら4つの脚部は、矩形状(正方形状)のベースコアUCb ,DCbの四隅に配置されている。そして、第1脚部UC1,DC1と第3脚部UC3, DC3とが、互いに一方の対角線上の両端に配置されて脚部対(第1の脚部対)を構成す

20

30

40

50

ると共に、第2脚部UC2,DC2と第4脚部UC4,DC4とが、互いに他方の対角線上の両端に配置されて脚部対(第2の脚部対)を構成している。なお、上部コアUCAおよび下部コアDCAはそれぞれ、例えばフェライトなどの磁性材料により構成され、以下説明するプリントコイル310,330および4枚の板金はそれぞれ、例えば銅やアルミニウムなどの導電性材料により構成されている。

## [0094]

プリントコイル 3 1 0 には、各脚部 U C 1 ~ U C 4 , D C 1 ~ D C 4 が個別に貫通する 4 つの貫通孔 3 1 0 A ~ 3 1 0 D が設けられている。貫通孔 3 1 0 A には第 1 脚部 U C 1 , D C 1 が貫通し、貫通孔 3 1 0 B には第 2 脚部 U C 2 , D C 2 が貫通し、貫通孔 3 1 0 C には第 3 脚部 U C 3 , D C 3 が貫通し、貫通孔 3 1 0 D には第 4 脚部 U C 4 , D C 4 が 貫通している。また、このプリントコイル 3 1 0 では、接続ライン L 2 1 側から接続ライン L 2 2 側へ向けて、第 2 脚部 U C 2 , D C 2 および第 4 脚部 U C 4 , D C 4 を巻回する 1 次側巻線 3 1 A , 3 1 B が接続されている。

# [0095]

プリントコイル 3 3 0 は、プリントコイル 3 1 0 と下部コア D C A との間に配置されており、各脚部 U C 1 ~ U C 4 , D C 1 ~ D C 4 が個別に貫通する 4 つの貫通孔 3 3 0 A ~ 3 3 0 D が設けられている。貫通孔 3 3 0 A には第 1 脚部 U C 1 , D C 1 が貫通し、貫通孔 3 3 0 B には第 2 脚部 U C 2 , D C 2 が貫通し、貫通孔 3 3 0 C には第 3 脚部 U C 3 , D C 3 が貫通し、貫通孔 3 3 0 D には第 4 脚部 U C 4 , D C 4 が貫通している。また、このプリントコイル 3 3 0 では、接続ライン L 3 1 側から接続ライン L 3 2 側へ向けて、第 1 脚部 U C 1 , D C 1 および第 3 脚部 U C 3 , D C 3 を巻回する第 3 の巻線 3 3 A , 3 3 B が接続されている。

#### [0096]

2次側巻線32A,32Bを構成する2枚の板金は、プリントコイル310と上部コアUCAとの間に配置されている。これらの板金にはそれぞれ、脚部UC3,DC3が貫通する1つの貫通孔が設けられている。また、2次側巻線32C,32Dを構成する2枚の板金は、プリントコイル330と下部コアDCAとの間に配置されている。これらの板金にはそれぞれ、脚部UC1,DC1が貫通する1つの貫通孔が設けられている。

## [0097]

これにより、このトランス 3 A では、例えば図 2 1 に示したように、 1 次側巻線 3 1 A , 3 1 B および 2 次側巻線 3 2 A ~ 3 2 D 間と、 1 次側巻線 3 1 A , 3 1 B および第 3 の巻線 3 3 A , 3 3 B 間とはそれぞれ、疎に磁気結合される一方、 2 次側巻線 3 2 A ~ 3 2 D および第 3 の巻線 3 3 A , 3 3 B 間は、密に磁気結合されている。

#### [0098]

なお、ここでは、 1 次側巻線 3 1 A , 3 1 B 、 2 次側巻線 3 2 A ~ 3 2 D および第 3 の巻線 3 3 A , 3 3 B がそれぞれ、配線(接続ラインL 2 1 , L 2 2 、接続ラインL 3 1 , L 3 2 、出力ラインL O または接地ラインL G )を介して、プリントコイル 3 1 0 , 3 3 0 および 4 枚の板金の面内方向に沿って外部から取り出しが可能なように構成されている

#### [0099]

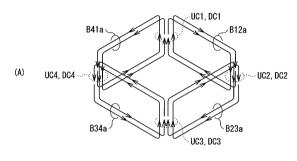

このような構成によりトランス3Aでは、例えば図20および図22中の矢印で示したように、1次側巻線31A,31B、2次側巻線32A~32Dおよび第3の巻線33A,33Bを流れる電流によって、4つの脚部UC1~UC4,DC1~DC4および2つのベースコアUCb,DCbの内部に磁路(還流磁路)が形成されるようになっている。これにより、4つの脚部UC1~UC4,DC1~DC4内の貫通方向に、磁束が形成される。なお、図20中の貫通孔310A~310D,330A~330D等内に示した磁束の向きを表す矢印は、実線のものが、接続ラインL21から実線で示した向きの電流が流れるときに形成されるものに、破線のものが、接続ラインL22から破線で示した向きの電流が流れるときに形成されるものに、それぞれ対応している。また、図22(A)は、接続ラインL21から実線で示した向きの流れるときに形成される還流磁路を、図22

20

30

40

50

(B)は、接続ラインL22から破線で示した向きの電流が流れるときに形成される還流 磁路を、それぞれ表している。そして、このような4つの脚部UC1~UC4,DC1~ DC4内に形成される磁束の向きが、第1脚部UC1,DC1および第3脚部UC3,D C 3 からなる第 1 の脚部対内で互いに同一方向であると共に、第 2 脚部 U C 2 , D C 2 お よび第4脚部UC4,DC4からなる第2の脚部対内で互いに同一方向となっている。ま た、これら第1の脚部対と第2の脚部対との間で、磁束の向きが互いに逆方向となってい る。言い換えると、第1脚部UC1,DC1および第3脚部UC3,DC3の各内部に生 ずる磁束がともに第1の方向を向くと共に、第2脚部UC2,DC2および第4脚部UC 4 , D C 4 の各内部に生ずる磁束がともに上記第 1 の方向とは逆の第 2 の方向を向くよう になっている。さらに、例えば図22に示したように、第1脚部UC1,DC1および第 2 脚部 U C 2 , D C 2 同士内を互いに貫通する環状磁路 B 1 2 a , B 1 2 b と、第 2 脚部 UC2,DC2および第3脚部UC3,DC3同士内を互いに貫通する環状磁路B23a , B 2 3 b と、第 3 脚部 U C 3 , D C 3 および第 4 脚部 U C 4 , D C 4 同士内を互いに貫 通する環状磁路 B 3 4 a , B 3 4 b と、第 4 脚部 U C 4 , D C 4 および第 1 脚部 U C 1 , DC1同士内を互いに貫通する環状磁路B41a,B41bと、からなる4つの環状磁路 が形成されている。すなわち、第1脚部UC1,DC1では、環状磁路B12a,B12 bと環状磁路B41a,B41bとが共有化され、第2脚部UC2,DC2では、環状磁 路B12a,B12bと環状磁路B23a,B23bとが共有化され、第3脚部UC3, DC3では、環状磁路B23a,B23bと環状磁路B34a,B34bとが共有化され 、第4脚部UC4,DC4では、環状磁路B34a,B34bと環状磁路B41a,B4 1 b とが共有化されている。言い換えると、4つの脚部UC1~UC4,DC1~DC4 および2つのベースコアUCb,DCbの内部に、4つの脚部UC1~UC4,DC1~ DC4のうち互いに隣り合った2つの脚部と2つのベースコアUCb,DCbとをそれぞ れ一方方向に通る磁路が4つ形成されている。そして、詳細は後述するが、これら4つの 環状磁路の形成領域が、ベースコアUCb,DCb上において4つの脚部間を周回するよ うになっている。

## [0100]

ここで、上部コアUCAおよび下部コアDCAからなるコア材(磁芯30A)が、本発明における「磁芯」の一具体例に対応する。また、プリントコイル310が本発明における「第1の導電部材」の一具体例に対応し、2次側巻線32A~32Dを構成する4枚の板金が本発明における「第2の導電部材」の一具体例に対応し、プリントコイル330が本発明における「第3の導電部材」の一具体例に対応する。また、ベースコアUCb,DCbが本発明における「2つの基体部」の一具体例に対応し、第1脚部UC1,DC1、第2脚部UC2,DC2、第3脚部UDC3,DC3および第4脚部UC4,DC4が、本発明における「4つの脚部」の一具体例に対応する。

#### [0101]

次に、本変形例のスイッチング電源装置の作用および効果について説明する。なお、スイッチング電源装置の基本動作およびサージ電圧抑止動作については、上記実施の形態と同様であるため説明を省略し、主にトランス3Aの作用および効果について説明する。

#### [0102]

# (トランス3Aの作用)

本変形例のトランス3Aでは、図20および図22に示したように、4つの脚部UC1~UC4,DC1~DC4内に形成される磁束の向きが、第1脚部UC1,DC1および第3脚部UC3,DC3からなる第1の脚部対内で互いに同一方向であると共に、第2脚部UC2,DC2および第4脚部UC4,DC4からなる第2の脚部対内で互いに同一方向となっている。また、これら第1の脚部対と第2の脚部対との間で、磁束の向きが互いに逆方向となっている。言い換えると、第1脚部UC1,DC1および第3脚部UC3,DC3の各内部に生ずる磁束がともに第1の方向を向くと共に、第2脚部UC2,DC2および第4脚部UC4,DC4の各内部に生ずる磁束がともに上記第1の方向とは逆の第2の方向を向いている。

20

30

40

50

#### [0103]

そして、このような磁束の向きとなるように、1次側巻線31A,31B、2次側巻線 32A~32Dおよび第3の巻線33A,33Bが巻回されていることにより、例えば図 2 2 および図 2 3 ( B ) に示したように、第 1 脚部 U C 1 , D C 1 および第 2 脚部 U C 2 , D C 2 同士内を互いに貫通する環状磁路 B 1 2 a , B 1 2 b と、第 2 脚部 U C 2 , D C 2 および第 3 脚部 U C 3 , D C 3 同士内を互いに貫通する環状磁路 B 2 3 a , B 2 3 b と 、第3脚部UC3,DC3および第4脚部UC4,DC4同士内を互いに貫通する環状磁 路 B 3 4 a , B 3 4 b と、第 4 脚部 U C 4 , D C 4 および第 1 脚部 U C 1 , D C 1 同士内 を互いに貫通する環状磁路B41a,B41bと、からなる4つの環状磁路が形成される 。そして、これら4つの環状磁路B12a,B12b、B23a,B23b、B34a, B34bおよびB41a, B41bの形成領域が、ベースコアUCb, DCb上において 4 つの脚部UC1~UC4, DC1~DC4間を周回するようになる。すなわち、第1脚 部UC1,DC1では、環状磁路B12a,B12bと環状磁路B41a,B41bとが 共有化され、第2脚部UC2,DC2では、環状磁路B12a,B12bと環状磁路B2 3a,B23bとが共有化され、第3脚部UC3,DC3では、環状磁路B23a,B2 3bと環状磁路B34a,B34bとが共有化され、第4脚部UC4,DC4では、環状 磁路B34a,B34bと環状磁路B41a,B41bとが共有化されている。言い換え ると、4つの脚部UC1~UC4,DC1~DC4および2つのベースコアUCb,DC bの内部に、4つの脚部UC1~UC4,DC1~DC4のうち互いに隣り合った2つの 脚部と2つのベースコアUCb,DCbとをそれぞれ一方方向に通る磁路が4つ形成され ている。

#### [0104]

したがって、例えば図23(A)に示したように、第1脚部UC1,DC1および第4脚部UC4,DC4同士内を互いに貫通する環状磁路B41a,B41bと、第2脚部UC2,DC2および第3脚部UC3,DC3同士内を互いに貫通する環状磁路B23a,B23bと、からなる2つの環状磁路のみが形成されるように磁束の向きが設定されている場合(従来のU型コアが2つ設けられた場合に相当する)と比べ、磁芯30Aにおける磁束が分散されることから、磁束密度を低下させることができ、コア損失を低減させることができる。また、従来のE型コアの場合と比べて放熱経路が拡大するため、磁芯30A、1次側巻線31A,31B、2次側巻線32A~32Dおよび第3の巻線33A,33Bの冷却がし易くなる。

# [0105]

以上のように本変形例では、4つの脚部UC1~UC4,DC1~DC4内の貫通方向 に形成される磁束の向きが、第1脚部UC1,DC1および第3脚部UC3,DC3から なる第1の脚部対内で互いに同一方向であると共に、第2脚部UC2,DC2および第4 脚部UC4,DC4からなる第2の脚部対内で互いに同一方向であり、かつ、これら第1 の脚部対と第2の脚部対との間で互いに逆方向となるように、1次側巻線31A,31B 、 2 次側巻線 3 2 A ~ 3 2 D および第 3 の巻線 3 3 A , 3 3 B を巻回するようにしたので 、上記した4つの環状磁路B12a,B12b、B23a,B23b、B34a,B34 bおよびB41a,B41が形成されると共に、これら4つの環状磁路の形成領域が、ベ ースコアUCb, DCb上において4つの脚部UC1~UC4, DC1~DC4間を周回 するようになる。言い換えると、本実施の形態では、第1脚部UC1,DC1および第3 脚部UC3,DC3の各内部に生ずる磁束がともに第1の方向を向くと共に、第2脚部U C2,DC2および第4脚部UC4,DC4の各内部に生ずる磁束がともに上記第1の方 向とは逆の第2の方向を向くように、1次側巻線31A,31B、2次側巻線32A~3 2 D および第 3 の巻線 3 3 A , 3 3 B を巻回するようにしたので、 4 つの脚部 U C 1 ~ U C4,DC1~DC4および2つのベースコアUCb,DCbの内部に、4つの脚部UC 1 ~ U C 4 , D C 1 ~ D C 4 のうち互いに隣り合った 2 つの脚部と 2 つのベースコア U C b,DCbとをそれぞれ一方方向に通る磁路が、4つ形成されるようになる。これにより 、U型コアの場合と比べ、磁芯30Aにおける磁束密度を低下させてコア損失を低減する

ことができるため、コア厚(基体部の厚み)を薄くして低背化を図ることができる。また、E型コアの場合と比べて放熱経路が拡大するため、磁芯30A、1次側巻線31A,3 1B、2次側巻線32A~32Dおよび第3の巻線33A,33Bの冷却がし易くなる。 よって、信頼性を向上させつつコスト低減を図ることが可能となる。

#### [0106]

また、これにより、複数のブリッジ回路1やトランス3A等を並列運転させることなく、スイッチング電源装置全体として大電流を扱うことが可能となる。よって、部品点数を減少させることができ、この点からもコストを低減することが可能となる。

#### [0107]

さらに、1次側巻線31A,31B、2次側巻線32A~32Dおよび第3の巻線33A,33Bがそれぞれ、配線(接続ラインL21,L22、接続ラインL31,L32、出力ラインLOまたは接地ラインLG)を介して、プリントコイル310,330および4枚の板金の面内方向に沿って外部から取り出しが可能なように構成したので、このような配線をプリントコイル310,330および4枚の板金の面内に垂直な方向から取り出す場合と比べ、配線も含めた低背化を実現することができると共に、配線の取り出し構造が簡易となる。

#### [0108]

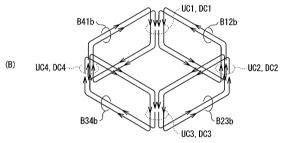

なお、本変形例では、図24(A)に示した上部コアUCA(下部コアDCA)のように、4つの脚部UC1(DC1)~UC4(DC4)の側面が曲面となっている場合について説明したが、各脚部の側面形状は、この場合には限られない。具体的には、例えば図24(B),(C)に示したように、4つの脚部UC1(DC1)~UC4(DC4)において、少なくとも対向する側面同士が、互いに平行となっているようにしてもよい。このように構成した場合、磁芯30Aにおける磁束最短経路の磁束集中がより効果的に緩和されるため、コア損失がより低減する。また、この場合において更に、例えば図24(C)に示したように、4つの脚部UC1(DC1)~UC4(DC4)において、互いに構成した場合、各脚部の周囲に対して1次側巻線31A,31B、2次側巻線32A~32Dおよび第3の巻線33A,33Bが巻回し易くなるため、電流経路が短縮されると共に、角部への電流分布の集中が緩和される。なお、これらの図24(B),(C)に示した4つの脚部UC1(DC1)~UC4(DC4)において、側面における角部が面取りされることにより、その角部の部分が、曲面または平面からなる側面となっているようにしてもよい。

#### [0109]

また、本変形例では、4つの脚部UC1(DC1)~UC4(DC4)が、矩形状(正方形状)のベースコアUCb,DCbの四隅に配置されている場合について説明したが、これらの4つの脚部の配置関係は、この場合には限られない。すなわち、4つの脚部は、ベースコア上の互いに交差する2直線上に、一対ずつ離間して配置されていればよい。また、ベースコアの形状や大きさについても、上記実施の形態等で説明した矩形状(正方形状)のものには限られず、4つの脚部の基体として機能するのであれば、どのような形状や大きさであってもよい。

# [0110]

#### 「変形例2,3]

図 2 5 は、本発明の変形例 2 に係るスイッチング電源装置の回路構成を表すものであり、図 2 6 は、本発明の変形例 3 に係るスイッチング電源装置の回路構成を表すものである。これらの変形例に係るスイッチング電源装置は、上記実施の形態のスイッチング電源装置において、サージ電圧抑止回路 2 の代わりに、サージ電圧抑止回路 2 A , 2 B を設けるようにしたものである。

## [0111]

サージ電圧抑止回路 2 A は、 2 つのダイオード D 5 , D 6 と、第 3 の巻線 3 3 とを有している。具体的には、ダイオード D 5 のカソードは 1 次側高圧ライン L 1 H に接続され、

10

20

30

40

20

30

40

50

アノードは接続点 P 3 1 に接続されている。ダイオード D 6 のカソードは接続点 P 3 1 に接続され、アノードは 1 次側低圧ライン L 1 L に接続されている。第 3 の巻線 3 3 の一端は接続点 P 3 1 に接続され、他端は接続点 P 1 (上記実施の形態の接続点 P 3 2 に対応)に接続されている。このような構成によりサージ電圧抑止回路 2 A では、ブリッジ回路 1 におけるダイオード D 1 , D 2 を、サージ電圧抑止回路 2 で説明したダイオード D 7 , D 8 としても機能させるようになっている。

#### [0112]

サージ電圧抑止回路 2 B も、サージ電圧抑止回路 2 A と同様に、 2 つのダイオード D 5 , D 6 と、第 3 の巻線 3 3 とを有している。具体的には、ダイオード D 5 のカソードは 1 次側高圧ライン L 1 H に接続され、アノードは接続点 P 3 1 に接続されている。ダイオード D 6 のカソードは接続点 P 3 1 に接続され、アノードは 1 次側低圧ライン L 1 L に接続されている。第 3 の巻線 3 3 の一端は接続点 P 3 1 に接続され、他端は接続点 P 2 (上記実施の形態の接続点 P 3 2 に対応)に接続されている。このような構成によりサージ電圧抑止回路 2 B では、ブリッジ回路 1 におけるダイオード D 3 , D 4 を、サージ電圧抑止回路 2 で説明したダイオード D 7 , D 8 としても機能させるようになっている。

#### [0113]

すなわち、これらのサージ電圧抑止回路 2 A , 2 B では、ブリッジ回路 1 における一方のアームを形成する 2 つのスイッチング素子(スイッチング素子 S 1 , S 2 またはスイッチング素子 S 3 , S 4 ) に並列接続されたダイオード(ダイオード D 1 , D 2 またはダイオード D 3 , D 4 ) が、サージ電圧抑止回路内のフルブリッジ回路における一方のアームを形成する 2 つのダイオード(ダイオード D 5 , D 6 またはダイオード D 7 , D 8 ) を兼ねている。なお、サージ電圧抑止回路 2 A , 2 B における構成の違いは、第 3 の巻線 3 3 の他端の接続先(接続点 P 1 または接続点 P 2 ) と、この第 3 の巻線 3 3 における巻き方向とである。

#### [0114]

このような構成により変形例 2 , 3 においても、サージ電圧抑止回路 2 A , 2 B におけるサージ電圧抑止回路 2 と同様のサージ電圧抑止作用により、上記実施の形態と同様の効果を得ることができる。

## [0115]

また、ブリッジ回路1におけるダイオード D 1 , D 2 またはダイオード D 3 , D 4 を、サージ電圧抑止回路 2 で説明したダイオード D 7 , D 8 としても機能させるようにしたので、サージ電圧抑止回路 2 A , 2 B 内のダイオードの数( 2 つ)を、サージ電圧抑止回路 2 内のダイオードの数( 4 つ)よりも減らすことができ、上記実施の形態と比べて部品点数をより削減することが可能となる。

## [0116]

## (その他の変形例)

以上、実施の形態および変形例を挙げて本発明を説明したが、本発明はこれらの実施の 形態等に限定されるものではなく、種々の変形が可能である。

## [0117]

例えば、上記実施の形態等では、1次側巻線や2次側巻線、第3の巻線の形状を具体的に挙げて説明したが、これらの形状はこの場合(板状)には限られず、他の形状でもよい。また、1次側巻線、2次側巻線および第3の巻線が、ともにプリントコイルや板金により構成されているようにしてもよい。

# [0118]

また、上記実施の形態等では、整流回路 4 , 4 1 がアノードコモン接続のセンタタップ型の整流回路である場合について説明したが、整流回路の構成はこれには限られない。具体的には、例えば、アノードコモン接続ではなくカソードコモン接続のセンタタップ型でもよく、また、センタタップ型以外(例えば、フルブリッジ型やハーフブリッジ型、カレントダブラ型、フォワード型、フライバック型など)の構成でもよい。また、全波整流型の整流回路ではなく、半波整流型の整流回路でもよい。なお、整流回路をフルブリッジ型

20

の構成とした場合、上記実施の形態等と同様の作用により、4つの整流ダイオードに加わるサージ電圧の最大値(ピーク値)を、1 x V in / n (n;トランスの1次側巻線と2次側巻線との巻数比)に抑えることができる。

#### [0119]

さらに、上記実施の形態等において説明した変形例等を組み合わせてもよい。

#### 【符号の説明】

#### [0120]

1 ... ブリッジ回路、 1 0 ... 高圧バッテリ、 1 1 ... 入力平滑コンデンサ、 2 , 2 A , 2 B ...サージ電圧抑止回路、 3 , 3 A ...トランス、 3 0 , 3 0 A ...磁芯、 3 1 , 3 1 A ~ 3 1 D...第1の巻線(1次側巻線)、310...プリントコイル、310A~310D...貫通孔 (開口部)、32A~32D...第2の巻線(2次側巻線)、33,33A,33B...第3 の巻線、330...プリントコイル、330A~330D...貫通孔(開口部)、4,41... 整流回路、4A~4D...整流ダイオード、5...平滑回路、51...チョークコイル、52... 出力平滑コンデンサ、6…駆動回路、7…負荷、S1~S4…スイッチング素子、D1~ D 8 ... ダイオード、C 1 ~ C 4 ... コンデンサ、L r e ... (共振用) インダクタ (リーケー ジインダクタンス)、UC,UCA…上部コア、DC,DCA…下部コア、UCb,DC b ... ベースコア(基体部)、UC1,DC1...第1脚部、UC2,DC2...第2脚部、U С3, DС3…第3脚部、UС4, DС4…第4脚部、UСc, DСc…中央脚部、T1 ,T2…入力端子、T3,T4…出力端子、L1H…1次側高圧ライン、L1L…1次側 低圧ライン、LO...出力ライン、LG...接地ライン、L21,L22,L31,L32... 接続ライン、 P 1 , P 2 , P 3 1 , P 3 2 ... 接続点、 C T ... センタタップ、 V in... 直流入 力電圧、Vout...直流出力電圧、VP1,VP2,VP31,VP32...電位、V4A, V 4 B ... 逆電圧 ( サージ電圧 ) 、 I 3 1 , I 3 3 , I 5 ~ I 8 , I 4 A , I 4 B , I 5 1 , I a ~ l j , I x a , I x b ...電流、SG1~SG4...スイッチング信号、t0~t2 0 ... タイミング、Td... デッドタイム、 ... 位相差、B 1 2 a , B 1 2 b , B 2 3 a , B 23b, B34a, B34b, B41a, B41b... 還流磁路。

【図1】

【図2】

【図3】

【図4】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

# 【図21】

|          | 31A, 31B | 33A, 33B | 32A     | 32B     | 320     | 32D     |

|----------|----------|----------|---------|---------|---------|---------|

| 31A, 31B |          | 0. 99    | 0. 99   | 0. 99   | 0. 99   | 0. 99   |

| 33A, 33B | 0. 99    |          | 0. 9999 | 0. 9999 | 0. 9999 | 0. 9999 |

| 32A      | 0. 99    | 0. 9999  |         | 0. 9999 | 0. 9999 | 0. 9999 |

| 32B      | 0. 99    | 0. 9999  | 0. 9999 |         | 0. 9999 | 0. 9999 |

| 32C      | 0. 99    | 0. 9999  | 0. 9999 | 0. 9999 |         | 0. 9999 |

| 32D      | 0. 99    | 0. 9999  | 0. 9999 | 0. 9999 | 0. 9999 |         |

【図22】

【図24】

【図23】

【図25】

# 【図26】

## フロントページの続き

# (56)参考文献 特開2008-187801(JP,A)

特開2008-48527(JP,A)

特開2007-104766(JP,A)

特開2005-86052(JP,A)

特開平3-204913(JP,A)

特開2006-32861(JP,A)

米国特許第5198969(US,A)

米国特許第4864479(US,A)

# (58)調査した分野(Int.CI., DB名)

H 0 2 M 3 / 2 8

H01F 30/00