# (19) World Intellectual Property Organization

#### (43) International Publication Date 27 November 2003 (27.11.2003)

### **PCT**

# (10) International Publication Number WO 03/098368 A1

- (51) International Patent Classification7: G05F 3/24, 3/26

- (21) International Application Number: PCT/GB03/02156

- (22) International Filing Date: 19 May 2003 (19.05.2003)

- (25) Filing Language: English

- English (26) Publication Language:

- (30) Priority Data:

0211564.0 21 May 2002 (21.05.2002) GB

- (71) Applicant (for all designated States except US): TOUMAZ TECHNOLOGY LIMITED [GB/GB]; The Innovation Centre, Building D5, Culham Science Centre, Abingdon, Oxford OX14 3DB (GB).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): TOUMAZOU, Christofer [GB/GB]; 8 Barrett Street, Oxford, Oxfordshire OX2 0AT (GB). GEORGIOU, Julius [CY/CY]; 7 Thesalonikis Avenue, Strovlos 2020, Nicosia (CY).

- (74) Agent: LIND, Robert; Marks & Clerk, 4220 Nash Court, Oxford Business Park South, Oxford, Oxfordshire OX4 2RU (GB).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: REFERENCE CIRCUIT

(57) Abstract: A reference circuit comprising first and second field effect transistors connected to form a first current mirror, and a third and fourth field effect transistors connected to form a second current mirror, wherein a property of the first transistor is mismatched relative to the second transistor such that the threshold voltage of the first transistor is significantly higher than the threshold voltage of the second transistor, and the drain current versus gate-source voltage responses of the first and second transistors have substantially different gradients for current levels at which the reference current is operated.

WO 03/098368 A1

#### **REFERENCE CIRCUIT**

The present invention relates to a reference circuit, and particularly though not exclusively to a reference circuit suitable for providing a current.

5

10

15

20

25

Current reference circuits are fundamental building blocks of integrated circuits, and biasing for most integrated circuits can be traced back to an on-chip current reference circuit.

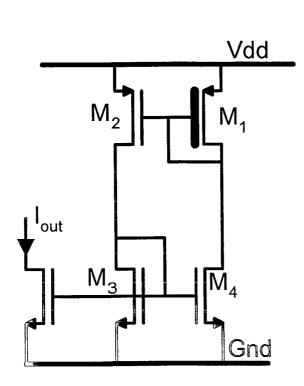

A conventional prior art current reference circuit [1] is shown in figure 1. The circuit comprises two pairs of field effect transistors (FETs) and a resistor. The first pair of FETs, M<sub>1</sub> and M<sub>2</sub>, are matched and are n-channel FETs. They form a first current mirror that maintains equal currents in the drains of M<sub>3</sub> and M<sub>4</sub>. The term 'matched pair' refers to the fact that M<sub>1</sub> and M<sub>2</sub> are constructed such that their properties are as identical as possible. A second pair of FETs M<sub>3</sub> and M<sub>4</sub> are pchannel FETs, and form a current mirror-like structure of non-unity gain, which is connected to the first current mirror. M<sub>4</sub> is K times wider than M<sub>3</sub>, and has a resistance R<sub>S</sub> connected between the source terminal and Vdd, the positive supply rail. The first current mirror and the current mirror-like structure are connected together to minimise the effect of supply voltage variation upon the current provided. secondary effects, the size of the current generated by the prior art reference circuit is determined by the magnitude of a resistor  $R_S$ , the mobility  $\mu_h$  of the holes of the PMOS devices, the gate oxide capacitance per unit area  $C_{ox}$ , the ratio K between the width of M<sub>3</sub> and M<sub>4</sub>, and the aspect ratio (W/L) of the PMOS devices according to the following relationship:

$$I_{out} = \frac{2}{\mu_n C_{ox}(W/L)_P} \cdot \frac{1}{R_1^2} \left( 1 - \frac{1}{\sqrt{K}} \right)^2$$

2

The prior art circuit shown in figure 1 suffers from the disadvantage that a large resistor, necessary for producing small reference currents, cannot easily be incorporated into an integrated circuit design (it usually occupies a substantial chip area). This is particularly the case in implanted bio-medical applications, where the current required to be generated by a current reference circuit is very small, typically of the order of nanoamperes, and the magnitude of resistor R<sub>1</sub> needed to provide the current is correspondingly large. The area occupied by a resistor of suitable magnitude may be prohibitive for bio-medical applications.

10

15

20

25

30

5

Alternative reference circuits based on replacing the resistor with active devices have been proposed [2][3][4], but these circuits are much more complicated and occupy substantial chip areas.

It is an object of the present invention to provide a reference circuit that overcomes or mitigates one or more of the above disadvantages.

According to the invention there is provided a reference circuit comprising first and second field effect transistors connected to form a first current mirror, and a third and fourth field effect transistors connected to form a second current mirror, wherein a property of the first transistor is mismatched relative to the second transistor such that the threshold voltage of the first transistor is significantly higher than the threshold voltage of the second transistor, and the drain current versus gate-source voltage responses of the first and second transistors have substantially different gradients for current levels at which the reference circuit is operated.

Suitably, the property of the first transistor is selected such that, for a particular voltage applied to the common gate of the first transistor and the second transistor, the second transistor operates substantially in its strong inversion saturation region whilst the first transistor operates substantially in its weak inversion saturation region.

3

Suitably, the mismatch is obtained by providing the first transistor with an oxide layer having a thickness which is greater than the oxide layer of the second transistor.

Suitably, the thickness of the oxide layer provided on the first transistor is at least twice the thickness of the oxide layer provided on the second transistor.

Suitably, the thickness of the oxide layer provided on the first transistor is at least 5 nanometers greater than the thickness of the oxide layer provided on the second transistor.

Suitably, the thickness of the oxide layer provided on the first transistor is at least 10 nanometers greater than the thickness of the oxide layer provided on the second transistor.

15

20

25

10

5

Suitably, the mismatch is obtained by providing more doping to the substrate of the first transistor than the substrate of the second transistor.

Suitably, the first transistor comprises a modified twin tub configuration, in which a well layer separating an upper tub layer and a substrate layer is omitted during fabrication such that the upper tub layer is located directly on the substrate layer, the upper tub layer thereby providing a substrate layer having increased doping.

Suitably, the third and fourth transistors are matched such that either side of the second current mirror is constrained to draw substantially the same current, the circuit having a stable operating point where the drain current versus gate-source voltages of the first and second transistors intersect.

Suitably, the third and fourth transistors are not matched, so that one side of the second current mirror is constrained to draw more current than the other side.

WO 03/098368

4

Suitably, the third and fourth transistors are field effect transistors, and the width of the channel of one of the transistors is selected to be different to the width of the channel of the other transistor so that that side of the current mirror is constrained to draw a current which is a ratio of the current on the other side.

5

Suitably, the third and fourth transistors are field effect transistors, and the length of the channel of one of the transistors is selected to be different to the length of the channel of the other transistor so that that side of the current mirror is constrained to draw a current which is a ratio of the current on the other side.

10

Suitably, the third and fourth transistors are bipolar transistors.

Suitably, the length of the first transistor is selected to be different to the length of the second transistor.

15

Suitably, the width of the first transistor is selected to be different to the width of the second transistor.

Suitably, a reference voltage is obtained from the common gate of the third and fourth transistors.

Suitably, a copy of the reference current is obtained by connecting a FET to the common gate of the third and the fourth transistor.

25

Suitably, the first and second transistors are p-channel field effect transistors, and the third and fourth transistors are n-channel field effect transistors.

A specific embodiment of the invention will now be described by way of example only, with reference to the accompanying figures in which:

30

Figure 1 is a circuit diagram which represents a conventional prior art current reference circuit;

5

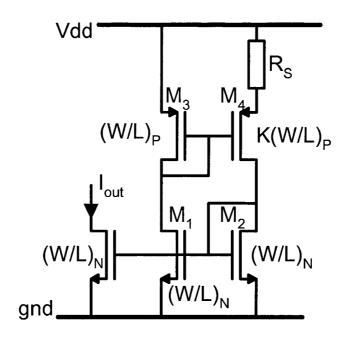

Figure 2 is a circuit diagram which represents a current reference circuit according to the invention;

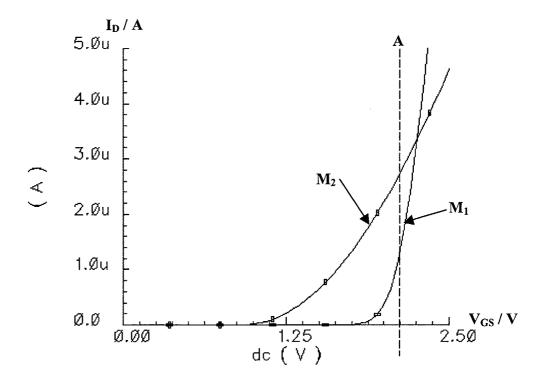

Figure 3 is a graph which illustrates drain current versus gate-source voltage responses of field effect transistors of the circuit shown in figure 2; and

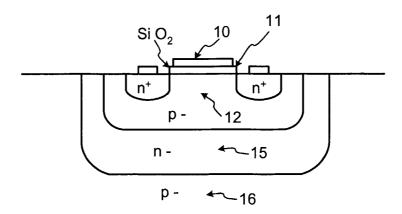

Figure 4 is a schematic illustration of a prior art twin tub field effect transistor.

Referring to figure 2, a circuit according to the invention comprises two n-channel field effect transistors  $M_3$  and  $M_4$  connected to form a first current mirror, and two p-channel field effect transistors  $M_1$  and  $M_2$  connected to form a second current mirror. The sources of the p-channel transistors  $M_1$  and  $M_2$  are connected to a voltage rail  $V_{dd}$  which provides between 3.5 and 5 volts (the voltage source may be for example a lithium battery which provides 4 volts). The sources of the n-channel transistors  $M_3$  and  $M_4$  are connected to ground.

In a conventional arrangement the field effect transistors  $M_1$  and  $M_2$  would be of different width and have a resistor in series with  $M_1$  such that, for a given gate voltage, the current provided from the drain of each of the transistors is equal. However, in the circuit shown in figure 2 the transistors  $M_3$  and  $M_4$  have no need for a series resistance, but instead the thickness of the oxide layer provided on transistor  $M_1$  is significantly thicker than the oxide thickness provided on transistor  $M_2$ . In one embodiment of the invention the thickness of the oxide layer on  $M_2$  is 17 nanometers, whereas the thickness of the oxide layer on  $M_1$  is 40 nanometers. The effect of the oxide thickness mismatch is that the threshold voltage of  $M_1$  is much greater than that of  $M_2$ .

25

30

5

10

15

20

In operation,  $M_2$  is turned on first and enters the square law saturation region (i.e. the rate of increase of current with respect to gate source voltage is quadratic).  $M_1$  is weakly turned on at a higher voltage, and operates in the weak inversion region (i.e. the rate of increase of current with respect to gate source voltage is exponential). Since  $M_1$  is turned on at a higher voltage than  $M_2$ , and provides current which increases with a steeper gradient, it follows that there is a value of gate voltage for which both  $M_1$  and  $M_2$  provide the same output current. This is the stable operating

6

point of the circuit, given that the gain of the current mirror comprising of  $M_3$  and  $M_4$  is unity.

It will be understood that the output current of the reference circuit is stable, under stable ambient conditions. If the ambient conditions, e.g. the temperature varies, then the output current of the reference circuit may vary accordingly. This property may be used to provide a reference current which tracks changes in ambient conditions.

5

10

15

20

25

Figure 3 is a graph that represents drain current as a function of gate source voltage for both  $M_1$  and  $M_2$ . Referring to figure 3,  $M_2$  enters the weak inversion region at a gate source voltage of around 0.3V. The current provided by  $M_2$  at 0.3V is very low, and consequently is not apparent in figure 3.  $M_2$  enters the square law saturation region at around 0.9V, and remains in the square law saturation region up to 2.5V and beyond as is apparent from figure 3.

$M_1$  enters the weak inversion region at a gate source voltage of around 1.6V, and remains in the weak inversion region over the range of currents represented in figure 3. Since  $M_1$  remains in the weak inversion region, the current provided by  $M_1$  rises exponentially.

The currents provided by  $M_1$  and  $M_2$  intersect at a value of approximately 3.2 $\mu$ A for a gate source voltage of approximately 2.25V. This intersection provides a current which satisfies the operating requirements of the current mirror formed by n-channel transistors  $M_3$  and  $M_4$ , i.e. that the current provided by each side of the circuit is equal. The intersection is a stable operating point for the circuit, and the circuit will consequently generate a fixed current of approximately 3.2 $\mu$ A which is independent of the voltage  $V_{dd}$  at the bias rail.

The currents provided by  $M_1$  and  $M_2$  will not intersect at higher values, since the gradient of  $M_1$  will never be less than the gradient of  $M_2$  ( $M_1$  will eventually enter the square law saturation region). This means that the circuit has no stable operating

5

10

15

points at higher currents. The currents provided by  $M_1$  and  $M_2$  will converge at zero gate-source voltage and zero current, therefore this could be considered to be a stable operating point of the circuit. The circuit will leave the zero current operating point given a sufficient voltage at  $V_{dd}$  and an initial startup charge at the gates of  $M_3$  and  $M_4$  and move to the stable intended operating point which generates the approximately  $3.2\mu A$  current, in this particular case. Leakage currents can sometime be sufficient to start-up the circuit.

Different current settings for the circuit may be achieved by scaling the response of  $M_1$  and  $M_2$  with respect to each other. For example, by providing  $M_1$  with a thicker oxide layer, the voltage at which  $M_1$  is weakly turned on will increase, and the current provided by the stable operating point will increase.

The quadratic behaviour of a field effect transistor operating in the square law saturation region is determined by the following:

$$I_d = \frac{\mu_h C_{ox} W}{I_c} (V_{gs} - V_T)^2$$

where  $I_d$  is the drain current,  $\mu_h$  is the mobility of holes,  $C_{ox}$  is the capacitance per unit area of the gate, W is the width of the channel, L is the length of the channel,  $V_{gs}$  is the gate/source voltage and  $V_T$  is the threshold voltage.

20

25

30

The exponential behaviour of a field effect transistor operating in the weak inversion region is determined by the following:

$$I_d = I_k \left(\frac{W}{L}\right) \exp(V_{gs} / nV_T)$$

where  $I_d$  is the drain current,  $I_k$  is a constant, W is the width of the channel, L is the length of the channel, n is a constant,  $V_{gs}$  is the gate/source voltage and  $V_T$  is the threshold voltage.

From the above it is clear that different current settings for the circuit may be achieved by modifying the channel width and/or the channel length of the transistors, and in particular by selecting the ratio of width to length. For example, referring to

8

figure 2, if the width W of the channel of  $M_2$  were to be doubled then the current provided by the circuit would double. Similarly, if the length L of the channel of  $M_2$  were to be doubled then the current provided by the circuit would halve.

The modification of the width or length need not be confined to the p-channel transistors  $M_1$  and  $M_2$ , but may instead be used to adjust the properties of the n-channel transistors  $M_3$  and  $M_4$ . For example, instead of matching  $M_3$  and  $M_4$ , the channel width of  $M_3$  could be double of  $M_4$ . This would constrain the circuit to provide twice as much current on the left hand side as on the right hand side. The stable operating point of the circuit would then be at approximately 2.13 volts as indicated by the vertical line A in figure 3. Where n-channel transistors  $M_3$  and  $M_4$  are not matched, it will be appreciated that there is no requirement for the drain currents  $M_1$  and  $M_2$  to be identical.

One suitable combination of channel widths and channel lengths is as follows:

$$M_2$$

: Width = 2  $M_1$ : Width = 40

Length = 10 Length = 5

20

$$M_3$$

: Width = 2  $M_4$ : Width = 2 Length = 20

5

10

15

25

30

Since  $M_3$  and  $M_4$  are matched, the stable operating point of the circuit is the point at which  $M_1$  and  $M_2$  provide the same current. The large channel width of  $M_1$  compared to  $M_2$  is necessary since the threshold voltage of  $M_1$  is much higher than that of  $M_2$ .

The circuit may be used to generate a reference current via a copy of the drain current of  $M_3$  by connecting yet another matched device to the common gate of  $M_1$  and  $M_2$ . Alternatively, the gate voltage of  $M_1$  and  $M_2$ , can be used as a reference voltage.

9

In the described embodiment of the invention the transistors are field effect transistors. It will be appreciated that any suitable field effect transistors may be used.  $M_1$  and  $M_2$  could be bipolar transistors, for example where biCMOS is used.

The invention may be implemented as a single semiconductor chip, making it particularly suited to biomedical applications.

In the above mentioned semiconductor technology process, the chip has a standard feature size of  $0.8\mu m$ , and the low voltage field effect transistors provided on the chip has a typical standard gate oxide layer of around 17nm. Where the invention is used, the mid-gate oxide layer of transistor  $M_1$  is approximately 50nm. Some semiconductor manufacturers already provide transistors with oxide layers of similar this thickness, for use in high voltage processors (high voltage typically means around 20-30V rather than a normal voltage of around 5.5V). It would be possible therefore to manufacture a chip which incorporates the invention using existing techniques.

10

15

20

25

30

For a semiconductor chip having a standard feature size of  $0.25\mu m$ , the field effect transistors provided on the chip will have an oxide layer of around 5 or 6nm. Where the invention is used, the oxide layer of transistor  $M_1$  could be approximately 13nm. Again, a chip that incorporates the invention could be manufactured using existing manufacturing processes that support two different voltages e.g. 3V and 5V devices.

An alternative, or additional, means of modifying the threshold voltage of transistor  $M_1$  is by modifying the doping of the substrate. An increase of the doping of the substrate will cause a corresponding increase of the threshold voltage required to invert the channel of the transistor.

One manner in which the substrate doping may be increased in a silicon chip is by modifying a conventional twin tub field effect transistor configuration. A prior art twin tub FET is shown in figure 4. The FET comprises a contact 10 and silicon oxide layer 11, located on top of a negatively doped p-tub 12. Positively doped n+

10

source 13 and drain 14 regions are provided at either side of the silicon oxide layer 11. The entire p-well 12 is located in a negatively doped n-well 15. The n-well 15 is located in a positively doped p-substrate 16. The n-well 15 isolates the p-well 12 from the p-substrate 16, providing the FET with advantageous features, and this is why the twin tub FET is used in prior art silicon chips.

5

10

15

20

25

30

The invention may be implemented by omitting the n-well 15 during fabrication of the FET, so that the p-well layer lies directly over the p-substrate layer. The effect of doing this will be to provide a conventionally configured FET having a substrate layer which is more strongly doped than the substrate layers of other FET's provided on the chip. The threshold of the FET is increased by the higher doping of the p-substrate.

Use of technologies with two different gate oxide thickness is preferred over modification of the doping because the oxide thickness is better controlled and supplied device models are more accurate.

Where different gate oxide thickness devices are used to implement the invention, the thicknesses should be carefully controlled in order to ensure that the invention functions correctly. The thickness of the oxide layer provides separation of the current versus gate source voltage curves as shown in figure 3. If the thicknesses of the oxide layers are very close, then small changes of the doping or device size may influence the operation of the invention. Thus, it is preferred to provide oxide layers having very different thicknesses, for example a difference of a factor of two or greater.

It will be appreciated by those skilled in the art that the circuit shown in figure 2 may be constructed in an 'opposite' sense by replacing n-channel transistors with p-channel transistors, and vice versa. Other modifications of the invention will be apparent to those skilled in the art.

11

# **REFERENCES**

[1] B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw Hill, 2000

5

- [2] W.M. Sansen et all "A New CMOS current reference", in Proc. ESSCIRC'87, p125

- [3] W.M. Sansen, F. O. Eynde and M. Steyaert, "A CMOS Temperature Compensated Current Reference", IEEE J. of Solid- State Circuits, Vol.23, No.3, June 1988.

- [4] H. Oguey, "Generateur de courant de reference en technologie CMOS", French patent application no 9503352, Mar.22, 1995.

12

#### **Claims**

- 1. A reference circuit comprising first and second field effect transistors connected to form a first current mirror, and third and fourth field effect transistors connected to form a second current mirror, wherein a property of the first transistor is mismatched relative to the second transistor such that the threshold voltage of the first transistor is significantly higher than the threshold voltage of the second transistor, and the drain current versus gate-source voltage responses of the first and second transistors have substantially different gradients for current levels at which the reference current is operated.

- 2. A reference circuit according to claim 1, wherein the property of the first transistor is selected such that, for a particular voltage applied to the common gate of the first transistor and the second transistor, the second transistor operates substantially in its strong inversion saturation region whilst the first transistor operates substantially in its weak inversion saturation region.

- 3. A reference circuit according to claim 1 or claim 2, wherein the mismatch is obtained by providing the first transistor with an oxide layer having a thickness which is greater than the oxide layer of the second transistor.

- 4. A reference circuit according to claim 3, wherein the thickness of the oxide layer provided on the first transistor is at least twice the thickness of the oxide layer provided on the second transistor.

25

5

10

15

- 5. A reference circuit according to claim 3 or claim 4, wherein the thickness of the oxide layer provided on the first transistor is at least 5 nanometers greater than the thickness of the oxide layer provided on the second transistor.

- 6. A reference circuit according to claim 4, wherein the thickness of the oxide layer provided on the first transistor is at least 10 nanometers greater than the thickness of the oxide layer provided on the second transistor.

13

7. A reference circuit according to any preceding claim, wherein the mismatch is obtained by providing more doping to the substrate of the first transistor than the substrate of the second transistor.

5

10

15

20

25

- 8. A reference circuit according to claim 7, wherein the first transistor comprises a modified twin tub configuration, in which a well layer separating an upper tub layer and a substrate layer is omitted during fabrication such that the upper tub layer is located directly on the substrate layer, the upper tub layer thereby providing a substrate layer having increased doping.

- 9. A reference circuit according to any preceding claim, wherein the third and fourth transistors are matched such that either side of the second current mirror is constrained to draw substantially the same current, the circuit having a stable operating point where the drain current versus gate-source voltages of the first and second transistors intersect.

- 10. A reference circuit according to any of claims 1 to 8, wherein the third and fourth transistors are not matched, so that one side of the second current mirror is constrained to draw more current than the other side.

- 11. A reference circuit according to claim 10, wherein the third and fourth transistors are field effect transistors, and the width of the channel of one of the transistors is selected to be different to the width of the channel of the other transistor so that that side of the current mirror is constrained to draw a current which is a ratio of the current on the other side.

- 12. A reference circuit according to claim 10 or claim 11, wherein the third and fourth transistors are field effect transistors, and the length of the channel of one of the transistors is selected to be different to the length of the channel of the other transistor so that that side of the current mirror is constrained to draw a current which is a ratio of the current on the other side.

14

- 13. A reference circuit according to any of claims 1 to 10, wherein the third and fourth transistors are bipolar transistors.

- 5 14. A reference circuit according to any preceding claim, wherein the length of the first transistor is selected to be different to the length of the second transistor.

- 15. A reference circuit according to any preceding claim, wherein the width of the first transistor is selected to be different to the width of the second transistor.

- 16. A reference circuit according to any preceding claim, wherein a reference voltage is obtained from the common gate of the third and fourth transistors.

10

- 17. A reference circuit according to any preceding claim, wherein a copy of the reference current is obtained by connecting a FET to the common gate of the third and the fourth transistor.

- 18. A reference circuit according to any preceding claim, wherein the first and second transistors are p-channel field effect transistors, and the third and fourth transistors are n-channel field effect transistors.

WO 03/098368

1/2

PCT/GB03/02156

FIGURE 1- PRIOR ART

FIGURE 2

FIGURE 3

FIGURE 4 – Prior Art

# INTERNATIONAL SEARCH REPORT

Interna pplication No PCT/GB 03/02156

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 G05F3/24 G05F3/26

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)  $IPC \ 7 \ G05F$

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

#### EPO-Internal

| C. DOCUM   | ENTS CONSIDERED TO BE RELEVANT                                                                                    |                       |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                | Relevant to claim No. |  |  |

| Х          | US 4 300 091 A (SCHADE JR ÖTTO H)<br>10 November 1981 (1981-11-10)                                                | 1,9-18                |  |  |

| Y          | column 1, line 1 -column 5, line 50 column 7, line 2 - line 33 column 8, line 44 - line 57; figures 1,7,17        | 2,7,8                 |  |  |

| Y          | EP 0 992 871 A (CSELT CENTRO STUDI LAB<br>TELECOM) 12 April 2000 (2000-04-12)<br>claims 1-8; figures 1-3          | 2                     |  |  |

| Y          | US 6 096 610 A (GHANI TAHIR ET AL) 1 August 2000 (2000-08-01) column 9, line 66 -column 12, line 10; figures 3A-4 | 7,8                   |  |  |

|            |                                                                                                                   |                       |  |  |

| χ Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <ul> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>"&amp;" document member of the same patent family</li> </ul> |  |  |  |  |

| Date of mailing of the international search report  04/08/2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Authorized officer  Gardella, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

# INTERNATIONAL SEARCH REPORT

Interna pplication No

PCT/GB 03/02156

|            | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                              | I Delevient to eleim No |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Category ° | Citation of document, with Indication, where appropriate, of the relevant passages                                                                                                                                                                                                                      | Relevant to claim No.   |

| A          | FR 2 732 129 A (SUISSE ELECTRONIQUE MICROTECH) 27 September 1996 (1996-09-27) cited in the application the whole document                                                                                                                                                                               | 1,2                     |

| A          | US 2001/020844 A1 (WATANABE HIROFUMI ET AL) 13 September 2001 (2001-09-13) paragraph '0171! - paragraph '0194! paragraph '0220! - paragraph '0222!; figure 8                                                                                                                                            | 1,3                     |

| A          | EP 0 483 537 A (EUROSIL ELECTRONIC GMBH) 6 May 1992 (1992-05-06) abstract; figures 1,2                                                                                                                                                                                                                  | 1                       |

| A          | KIMURA K: "LOW VOLTAGE TECHNIQUES FOR BIAS CIRCUITS" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: FUNDAMENTAL THEORY AND APPLICATIONS, IEEE INC. NEW YORK, US, vol. 44, no. 5, 1 May 1997 (1997-05-01), pages 459-465, XP000724594 ISSN: 1057-7122 page 462, left-hand column, line 5,6,11,12; figure 1 |                         |

# INTERNATIONAL SEARCH REPORT

Interna pplication No

PCT/GB 03/02156

| Patent document cited in search report |            |    | Publication date |                                        | Patent family<br>member(s)                                               |                          | Publication date                                                                               |

|----------------------------------------|------------|----|------------------|----------------------------------------|--------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------|

| US                                     | 4300091    | Α  | 10-11-1981       | NONE                                   |                                                                          |                          | <del>                                      </del>                                              |

| EP                                     | 0992871    | Α  | 12-04-2000       | IT<br>EP<br>JP<br>JP<br>US             | T0980831<br>0992871<br>3181898<br>2000122740<br>6166587                  | A2<br>B2<br>A            | 05-04-2000<br>12-04-2000<br>03-07-2001<br>28-04-2000<br>26-12-2000                             |

| US                                     | 6096610    | Α  | 01-08-2000       | US                                     | 5798552                                                                  | Α                        | 25-08-1998                                                                                     |

| FR                                     | 2732129    | A  | 27-09-1996       | FR<br>DE<br>DE<br>EP<br>US             | 2732129<br>69609104<br>69609104<br>0733961<br>5949278                    | D1<br>T2<br>A1           | 27-09-1996<br>10-08-2000<br>15-03-2001<br>25-09-1996<br>07-09-1999                             |

| US                                     | 2001020844 | A1 | 13-09-2001       | JP<br>US                               | 2001284464<br>2002175664                                                 |                          | 12-10-2001<br>28-11-2002                                                                       |

| EP                                     | 0483537    | A  | 06-05-1992       | DE<br>DE<br>EP<br>HK<br>JP<br>JP<br>US | 4034371<br>59107888<br>0483537<br>59797<br>2504647<br>5189071<br>5204612 | D1<br>A2<br>A<br>B2<br>A | 31-10-1991<br>11-07-1996<br>06-05-1992<br>16-05-1997<br>05-06-1996<br>30-07-1993<br>20-04-1993 |