US007466609B2

### (12) United States Patent

Takahashi et al.

# (54) SEMICONDUCTOR MEMORY DEVICE AND SEMICONDUCTOR MEMORY DEVICE CONTROL METHOD

(75) Inventors: **Hiroyuki Takahashi**, Kanagawa (JP);

Takuya Hirota, Kanagawa (JP); Atsushi

Nakagawa, Kanagawa (JP)

(73) Assignee: **NEC Electronics Corporation**,

Kanagawa (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 11/882,230

(22) Filed: Jul. 31, 2007

(65) **Prior Publication Data**

US 2007/0280025 A1 Dec. 6, 2007

#### Related U.S. Application Data

(63) Continuation of application No. 10/507,117, filed on Sep. 10, 2004, now Pat. No. 7,301,830, which is a continuation of application No. PCT/JP03/02095, filed on Feb. 26, 2003.

### (30) Foreign Application Priority Data

Mar. 15, 2002 (JP) ...... 2002-072953

(51) Int. Cl.

G11C 7/22 (2006.01)

G11C 8/18 (2006.01)

G11C 8/08 (2006.01)

G11C 5/14 (2006.01)

G11C 7/12 (2006.01)

### (10) Patent No.: US 7,466,609 B2

(45) **Date of Patent:** \*Dec. 16, 2008

(52) **U.S. Cl.** ...... **365/194**; 365/189.11; 365/226; 365/230.06

See application file for complete search history.

(56) References Cited

U.S. PATENT DOCUMENTS

5,086,238 A 2/1992 Watanabe et al.

(Continued)

FOREIGN PATENT DOCUMENTS

2-000350 A 1/1990

JР

(Continued)

#### OTHER PUBLICATIONS

Office Action issued Aug. 7, 2008, in U.S. Appl. No. 11/907,442, 7 pages.

Primary Examiner—J. H. Hur (74) Attorney, Agent, or Firm—Foley & Lardner LLP

### (57) ABSTRACT

A cell core unit and its peripheral circuit are driven by a relatively low voltage power supply. A constant voltage that does not depend on the power supply voltage is provided as a boosted voltage (VBOOST) to be supplied to a control signal for a word line of the cell core unit. A sense amplifier amplifies a higher voltage level of a bit line to the power supply voltage. Then, a circuit for generating a signal for defining the transition timing and/or the pulse width of a control signal from the peripheral circuit to the cell core unit performs signal delay using a delay circuit having a characteristic in which a delay time thereof decreases with reduction of the provided power supply voltage.

### 2 Claims, 19 Drawing Sheets

# **US 7,466,609 B2**Page 2

| U.S. PATENT                           | DOCUMENTS          | 6,624,680                 |         | 9/2003         | Schenck                 |

|---------------------------------------|--------------------|---------------------------|---------|----------------|-------------------------|

| 5,130,564 A 7/1992                    | Sin                | 7,301,830<br>2002/0021159 |         | 11/2007        | Takahashi et al 365/194 |

| 5,197,033 A 3/1993                    |                    |                           |         | 2/2002         | Takahashi               |

| , ,                                   |                    | 2002/0033721              | Al      | 3/2002         | Tachimori               |

| 5,222,044 A 6/1993                    | 3                  | -                         |         | T TO 1 PROTEIN |                         |

| 5,264,743 A 11/1993                   | Nakagome et al.    | FOREIGN PATENT DOCUMENTS  |         |                |                         |

| 5,276,843 A 1/1994                    | Tillinghast et al. |                           |         |                |                         |

| 5,307,315 A 4/1994                    |                    | JР                        | 2-214   | l49 A          | 8/1990                  |

| , ,                                   | Watanabe et al.    | JP                        | 3-2376  | 582 A          | 10/1991                 |

| 5,394,077 A 2/1995                    |                    | JP                        | 3-273   | 594 A          | 12/1991                 |

| · · · · · · · · · · · · · · · · · · · |                    | JP                        | 4-038   | 786 A          | 2/1992                  |

| 5,396,116 A 3/1995                    |                    | JР                        |         | 220 A          | 3/1992                  |

| 5,398,207 A 3/1995                    | Tsuchida et al.    |                           |         |                |                         |

| 5,426,601 A 6/1995                    | Agata et al.       | JP                        |         | 375 A          | 12/1993                 |

| 5,499,209 A 3/1996                    | Oowaki et al.      | JР                        | 6-2829  | 986 A          | 10/1994                 |

| , ,                                   |                    | JР                        | 7-2400  | )94 A          | 9/1995                  |

|                                       | Nakagome et al.    | JP 20                     | 02-0509 | 945 A          | 2/2002                  |

| 5,592,421 A 1/1997                    | Kaneko et al.      | JP 20                     | 02-1248 | 858 A          | 4/2002                  |

| 5,822,267 A 10/1998                   | Watanabe et al.    | JP                        |         | 238 A          | 12/2002                 |

| 6,125,075 A 9/2000                    | Watanabe et al.    | JF                        | 0-340   | 230 A          | 12/2002                 |

| 6,363,029 B1 3/2002                   |                    | * cited by examiner       |         |                |                         |

| 0,303,029 B1 3/2002                   | watanauc ci ai.    | ched by exal              | mnei    |                |                         |

FIG. 1

FIG . 2

FIG . 3

FIG . 4

₽ |S

VDD 30

BAND-GAPREFERENCE

CIRCUIT

R11

R12

FIG . 9

tpd CONVENTIONAL

PRESENT INVENTION

CELL CORE UNIT tpd

PERIPHERAL CIRCUIT Tpd

VDD

**►** VDD

FORWARD CHARACTERISTIC

REVERSE CHARACTERISTIC

FIG . 12 ACCESS SPEEDING UP CELL ARRAY--CELL ARRAY PER I PHERAL-PERIPHERAL LOW HIGH LOW HIGH (L2) (H2) (H1) (L1) COMPARISON EXAMPLE PRESENT INVENTION

FIG . 13

FIG. 17 PRIOR ART

P81

P82

(HIGH Vt)

SIN

(LOW Vt)

(HIGH Vt)

(HIGH Vt)

VDD - |Vthp|

Vthn

GND

tA

tB

# SEMICONDUCTOR MEMORY DEVICE AND SEMICONDUCTOR MEMORY DEVICE CONTROL METHOD

### CROSS-REFERENCE TO RELATED PATENT APPLICATIONS

This application is a continuation of U.S. patent application Ser. No. 10/507,117, filed Sep. 10, 2004; which is a continuation of International Application No. PCT/JP03/ 10 02095, filed on Feb. 26, 2003, and claims priority to Japanese Patent Application No. 2002-72953, filed on Mar. 15, 2002, by Hiroyuki Takahashi, Takuya Hirota, and Atsushi Nakagawa, all of which are incorporated herein by reference in their entirety. This application claims only subject matter 15 disclosed in the parent application and therefore presents no new matter.

#### FIELD OF THE INVENTION

The present invention relates to a semiconductor memory device. More specifically, the invention relates to a semiconductor memory device suitable for being driven by a low voltage power supply, and its control method.

### BACKGROUND OF THE INVENTION

In recent years, reduction of a supply voltage for semiconductor integrated circuits has been pursued. In logic devices and memories mounted on portable devices and driven by 30 batteries, in particular, lower power consumption (dissipation) is required.

In the semiconductor integrated circuit and the like, a delay circuit is employed so as to obtain signal timings required for operating respective circuits therein. On the other hand, in 35 asynchronous, dynamic-type semiconductor memory devices that are not driven by an external clock signal, various timing signals are generated inside the semiconductor memory devices. More specifically, for various signals for controlling a memory core unit, a pulse signal is generated 40 based on detection on a change in an address signal, a predetermined input signal, or the result of decoding of it, and a control signal in pulse form, which rises being delayed by a predetermined time and having a predetermined pulse width is generated from the pulse signal and its delayed signal.

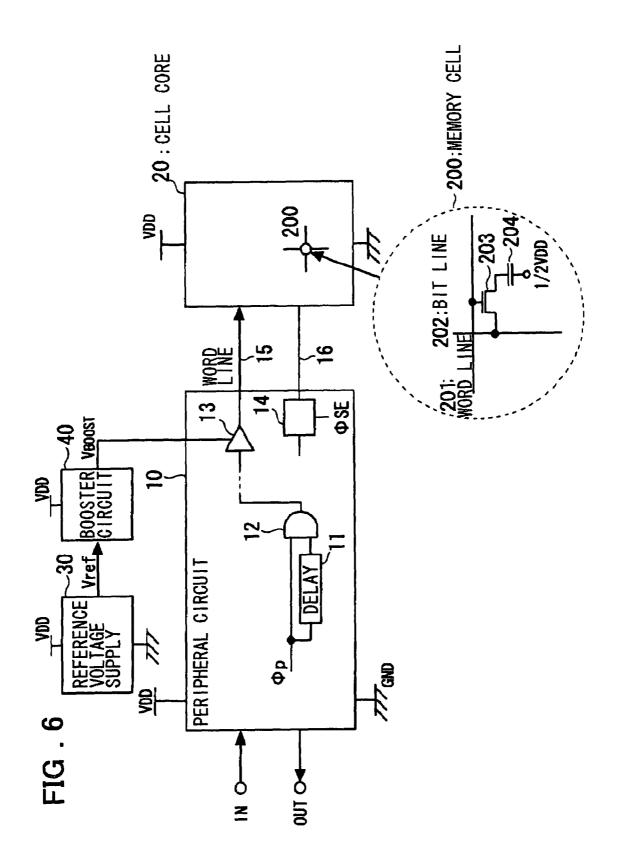

As the background art of the present invention, an overview of an asynchronous dynamic RAM will be described below with reference to FIG. 6, which will be referred to in the embodiments of the present invention. Referring to FIG. 6, a peripheral circuit 10 controls driving of a word line driver 13 50 for driving a word line based on a signal indicating the result of operation by a logic circuit 12 that receives a signal supplied to a delay circuit 11 and the output of the delay circuit. A step up voltage (boost voltage) is supplied to a driving power supply of the word line driver 13 from a step-up con- 55 verter (booster circuit 40). As the step-up voltage, a voltage obtained by adding a voltage exceeding a threshold voltage Vth of an NMOS transistor to a power supply voltage VDD is provided. It is noted that a reference voltage source 30 in FIG. 6 is specific to the embodiments in the present invention and 60 is not included in the conventional dynamic RAM. In an NMOS transistor 203 of a memory cell 200 provided at an intersection between a word line and a bit line in a cell core unit 20, a high voltage not less than VDD+Vt is supplied to the gate connected to a selected word line 201 so that the output 65 voltage of the NMOS transistor 203 can rise up to the power supply voltage VDD.

2

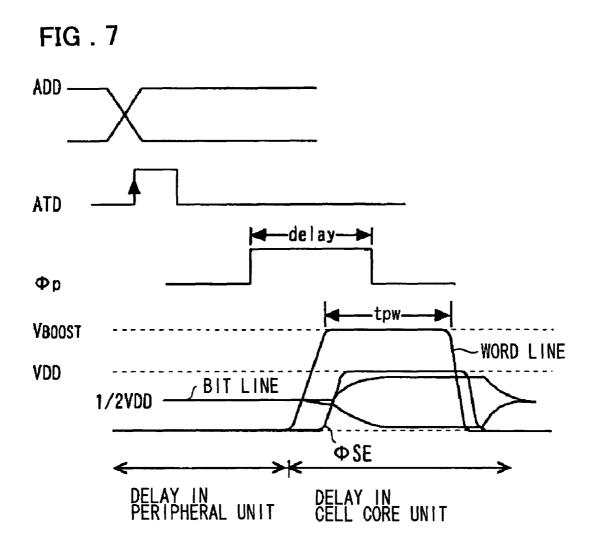

FIG. 7 is a diagram for explaining timing operations in the asynchronous dynamic RAM. When a transition in an address in memory cycle is detected by an ATD circuit not shown, an ATD signal is activated and then, a strobe signal φp for activating a row address is generated based on this signal, the result of decoding the address signal, and a control signal not shown for controlling access to the memory. By a signal generated based on this signal φp and its delayed signal, a word line rise timing and/or its pulse width are/is controlled. Likewise, a signal φSE for controlling activation of a sense amplifier 14 for amplifying a signal read onto a bit line 16 or a Y switch enable signal not shown, a control signal for precharging the bit line to ½ VDD, and the like are generated.

As the delay circuit 11 of this type, an inverter-chain constituted by connecting a plurality of inverters in cascade, for example is employed. The number of the inverters constituting the delay circuit is set to an even when the delay circuit outputs a delayed signal in phase with the input signal, and the number of the inverters is even when the delay circuit outputs a delayed signal having a phase reversed from the input signal is output.

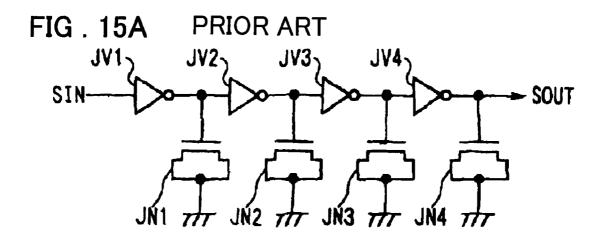

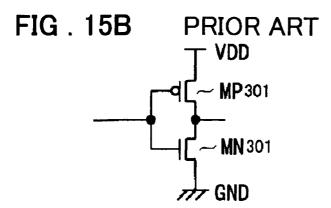

FIG. 15 shows a configuration example of a conventional delay circuit using a CMOS inverter-chain. As shown in FIG. 15A, the conventional delay circuit is constituted from a plurality of inverters JV1 to JV4 connected in cascade, and load capacitors constituted from MOS capacitors JN1 to JN4 are connected to respective outputs of the inverters. As shown in FIG. 15B, each inverter is constituted from an PMOS transistor MP301 having its source connected to a high-potential power supply VDD, an NMOS transistor MN301 having its gate and drain connected to the gate and drain of the PMOS transistor MP301 respectively, and having its source connected to a low potential power supply GND. When a signal input to common gates undergoes a transition from a low level to a high level, electric charge on the load capacitance connected to the common drain is discharged to the power supply GND through the NMOS transistor MN301 which is in an on state, so that its output goes low. When the signal input to the common gate undergoes a transition from the high level to the low level, the load capacitance connected to the common drains is charged from the power supply VDD through the PMOS transistor MP301 which is in an on state, so that the output of the inverter goes high. As described above, by charging and discharging the load capacitances of the outputs of the inverters, signal propagation is performed.

The fall tf and rise times (delays) tf and tr of a CMOS-type inverter (which are delay times required for 10 to 90% transition of an amplitude) are derived from formulas that depend on a load capacitance, power supply voltage, transconductance, and a ratio between the power supply voltage and its threshold value, based on a drain current-voltage characteristic in the nonsaturation region and the saturation region of a MOS transistor. The characteristic between drain-to-source current and voltage in the nonsaturation region is defined by gate-to-source voltage, drain-to-source voltage, threshold voltage, and transconductance, while the characteristic between drain-to-source current and voltage in the saturation region is defined by gate-to-source voltage, threshold voltage, and transconductance. Roughly, as is well known, the rise time tf and the fall time tr are approximated by:

$tf = k1 \times CL/(\beta n \times VDD)$

$tr = k2 \times CL/(\beta p \times VDD)$

where CL indicates the load capacitance,  $\beta p$  and  $\beta n$  indicate respective transconductances of the PMOS transistor and the

NMOS transistor of the CMOS inverter, VDD indicates the supply voltage, and k1 and k2 are constants.

When the power supply voltage VDD is high, the rise time tr and the fall time tf of the inverter are both reduced, so that a propagation delay time tpd of the inverter decreases. The 5 propagation delay time tpd includes a propagation delay time tpHL from rise of an input signal to fall of an inverted output signal and a propagation delay time tpLH from the fall of the input signal to the rise of the inverted output.

On the other hand, when the power supply voltage VDD is 10 reduced, the rise time tr and the fall time tf of the inverter are both increase, so that the propagation delay time of the inverter increases.

Due to increases in delay times of the inverters JV1 to JV4 constituting the delay circuit in FIG. 15, the propagation 15 delay time of the delay circuit also increases. Further, as in the delay circuit constituted from the inverter chain, the propagation delay time of other circuit as well decrease/increase due to elevation and lowering of an operation supply voltage. Thus, the operation speed of the device becomes fast or slow. 20

Recently, due to the demands in regard to a breakdown voltage with the progress in miniaturization of devices and for lower power consumption, a configuration in which the supply voltage of the semiconductor device is stepped down and internal circuits are operated at a low voltage is generally 25 employed. In the dynamic-type semiconductor memory device as well, an internal power supply voltage VINT obtained by reducing the power supply voltage VDD supplied externally by a voltage step-down circuit is employed as the supply voltage for a peripheral circuit and a cell core section 30 (which is also referred to as a "memory cell array"). However, the semiconductor memory device that uses the steppeddown supply voltage sometimes cannot accommodate the reduction of the power supply voltage VDD. It is because if the internal power supply voltage VINT obtained by further 35 stepping down the reduced power supply voltage VDD is employed, the operation speed of the device becomes slow, thereby making an access time slow, so that it sometimes happens that functional specifications are not satisfied.

The conventional circuit shown in FIG. **15** also has a problem: when the power supply voltage VDD is reduced, the delay time increases more compared with an increase in the amount of the delay of an ordinary logic circuit, so that it sometimes happens that timing relationship among signals is not satisfied. This is caused by the following reason: since 45 wiring connected to the output sections of the respective inverters is short, substantial wiring resistance is not present. Thus, the on resistance of each transistor is dominant as a resistive component which, together with the MOS capacitors, contributes to the time constant.

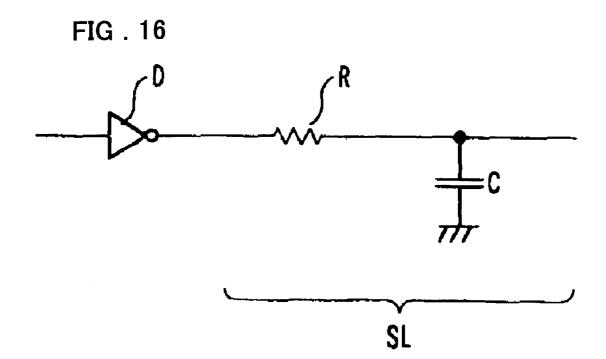

On contrast therewith, the signal line of the ordinary logic circuit is driven in a circuit configuration as shown in FIG. 16. Rise and fall of a signal line SL having a wiring resistance (parasitic resistance) R and a parasitic capacitance C is defined by the time constant stipulated by the parasitic resistance R of the signal line, the output resistance of a driver (output circuit) D, and the parasitic capacitance C of the signal line. In a circuit for driving a wiring having a wiring parasitic resistance as a load, the delay time of a signal is not so dependent on the power supply voltage as the inverter 60 chain in FIG. 15.

Accordingly, the delay time of the delay circuit shown in FIG. **15** excessively increases when the supply voltage is reduced, on contrast with the ordinary logic circuit.

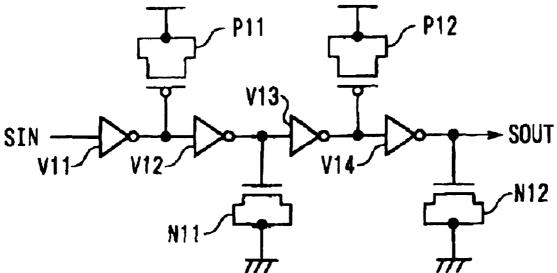

In order to solve the problem as described above, the inventor of the present application already proposed a delay circuit of a configuration as shown in FIG. 17 in the priority claim

4

(US Patent Application Publication No. US 2002/0021159 A1) based on JP Patent Application No. 2001-097083. This delay circuit is the delay circuit of which the delay time does not excessively increase, compared with the ordinary logic circuit even if the supply voltage is reduced and can suppress the increase of the delay time.

Referring to FIG. 17, the delay circuit includes a plurality of inverters V11, V12, V13, and V14 connected in cascade. PMOS capacitors P11 and P12 are provided between the output of the inverter V11 and the high potential power supply VDD and the output of the inverter V13 and the high potential power supply VDD, respectively. NMOS capacitors N11 and N12 are provided between the output of the inverter V12 and the low potential power supply GND and the output of the inverter V14 and the low potential power supply GND, respectively.

The PMOS capacitors P11 and P12 become from an off state to the on state (inversion state) in response to falling transition of the outputs of the inverters V11 and V13 from the high level to the low level, respectively. The NMOS capacitors N11 and N12 become from the off state to the on state (inversion state) in response to rising transition of the outputs of the inverters V12 and V14 from the low level to the high level, respectively. As is well known, the NMOS capacitor is in an accumulation state when its gate voltage Vg is negative or a ground voltage GND (0V), and its capacitance value is constituted from a capacitance Co of a gate oxide film therein alone. When the gate voltage Vg is larger than 0, a depletion layer is formed in the surface of a substrate, so that its capacitance value becomes a capacitance C obtained by series synthesis of the gate oxide film capacitance Co and a capacitance Cd of the depletion layer formed in the surface of the substrate, which is smaller than Co. When the gate voltage Vg is positive and increases (Vg>Vt, in which Vt is the threshold voltage), an inversion layer resulting from polarity inversion of the surface of the p-type substrate is formed. If so-called strong inversion occurs, its capacitance value becomes closer to Co. Likewise, the PMOS capacitor is in the accumulation state when its gate voltage is the power supply voltage VDD. Then, when the gate voltage falls below the supply voltage and transitions toward the ground voltage GND, the PMOS capacitor becomes a depletion state and then an inversion state.

In the inverter chain shown in FIG. 17, assume that the power supply voltage VDD is reduced, the driving currents of the MOS transistors are reduced and then the on resistances of the MOS transistors constituting the inverters increase in appearance. Then, the capacitance values of the MOS capacitors relatively decrease. An increase in the amount of the delay is thereby suppressed. This delay circuit suppresses an excessive increase in the delay time due to lowering of the power supply voltage VDD, in response to rise (transition from GND to VDD) of an input SIN to the inverter V11 in the first stage.

The inventor of this application already proposed a delay circuit of a configuration as shown in FIG. 18 in JP Patent Application No. 2001-097083. This delay circuit is the delay circuit of which the delay time does not excessively increase and which can suppress an increase in the delay circuit, even if the supply voltage is reduced. Referring to FIG. 18, the threshold value of a PMOS transistor P81 of an inverter V81 is set to be high, and the threshold value of an NMOS transistor N81 of the inverter V81 is set to be low. The threshold value of a PMOS transistor P82 of an inverter V82 is set to be low and the threshold value of an NMOS transistor N82 of the inverter V82 is set to be high. The input threshold value of the inverter V81 tends to decrease as the power supply voltage is

reduced, while the input threshold value of the inverter V82 tends to rise as the power supply voltage is reduced. The input threshold value of the delay circuit thereby decreases in a region in which the power supply voltage VDD is low, and the propagation delay time tpd from the rise of the input signal to the rise of the output signal becomes relatively shorter than the propagation delay time from the fall of the input signal to the fall of the output signal. As a result, the delay time in the rise of the signal can be reduced, so that dependency of this delay time on the power supply voltage is suppressed.

As described above, the delay circuits shown in FIGS. 17 and 18, respectively, suppress an excessive increase in the delay time caused by reduction of the power supply voltage VDD in the configuration as shown in FIG. 15. However, the delay circuits do not have a reverse sensitivity characteristic 15 in which the delay time thereof decreases with reduction of the power supply voltage. For this reason, with respect to reduction of the power supply voltage of the semiconductor memory device, when edges and pulses of a control signal are generated for using the delay circuits shown in FIGS. 17 and 20 18, respectively, the delay of the control signal does not decrease as the power supply voltage is reduced. Thus, a constraint is imposed on the lower power consumption.

Accordingly, it is an object of the present invention to provide a semiconductor memory device in which by speeding up access to the cell core unit while reducing a power supply voltage for driving, reduction of a combined access speed to the cell core unit and the peripheral circuit caused by the reduced power supply voltage is suppressed, and its control method.

Still other object of the present invention is to provide a semiconductor device in which due to its simple configuration, an increase in the delay time caused by the reduction of the power supply voltage is further suppressed, so that the delay time shows a tendency of decreasing.

### SUMMARY OF THE DISCLOSURE

A semiconductor memory device in accordance with one aspect of the present invention includes: a memory cell array 40 having a plurality of memory cells arranged in an array from; and a word line driving circuit for receiving a constant voltage that does not depend on a power supply voltage as a driving voltage and driving a selected word line by the constant voltage. The higher voltage level of the amplitude of a 45 selected bit line is amplified to the power supply voltage.

In the semiconductor memory device according to other aspect of the present invention, a peripheral circuit including a circuit for generating a signal for defining the transition timing of a control signal to the memory cell array and/or the 50 pulse width of the control signal includes a delay circuit for delaying an input signal, and the delay circuit has a characteristic in which a delay time thereof decreases more when the provided power supply voltage is low than when the provided power supply voltage is high.

The delay circuit according to other aspect of the present invention includes: at least one circuit unit including: an inverter including a first MOS transistor with a source thereof connected to a first power supply and a second MOS transistor with a source thereof connected to a second power supply, 60 the gate of the second MOS transistor and the gate of the first MOS transistor being connected in common to an input terminal, the drain of the second MOS transistor and the drain of the first MOS transistor being connected in common to an output terminal, the second MOS transistor having a different conductivity type from the conductivity type of the first MOS transistor; a resistor (resistance element) with one terminal

6

thereof connected to the output terminal of the inverter; and a MOS capacitor connected between the other terminal of the resistor and the first or second power supply.

In the delay circuit according to the present invention, the capacitance value of the MOS capacitor increases when a voltage at the other terminal of the resistor transitions from the power supply voltage of one of the first and second power supplies to the power supply voltage of the other of the first and second power supplies. One terminal of the MOS capacitor is connected to the other terminal of the resistor and the other terminal of the MOS capacitor is connected to one of the first and second power supplies. In the present invention, a depletion layer or an inversion layer is formed in the MOS capacitor according to a transition of a voltage at the other terminal of the resistor from the power supply voltage of one of the first and second power supplies to the power supply voltage of the other of the first and second power supplies. The MOS capacitor is connected to one of the first and second power supplies.

In the delay circuit according to the present invention, the circuit unit is constituted from a plurality of stages of circuit units connected in cascade. The input signal is input to the input terminal of the inverter of the circuit unit in the first one of the stages. An output signal is taken from a connection point between the MOS capacitor and the other terminal of the resistor connected to the output terminal of the inverter in the circuit unit in the final one of the stages. MOS capacitors in the stages of the circuit units adjacent to each other are connected to the first power supply and the second power supply, alternately.

In one aspect of the present invention, the delay circuit is the delay circuit including one or more inverters connected in cascade, and each of the inverters includes: the resistor with the one terminal thereof connected to the output terminal of the each of the inverters; and a capacitance element connected between the other terminal of the resistance and a high potential power supply or a low potential power supply. The capacitance value of the capacitance element increases when a voltage at the other terminal of the resistance transitions from the power supply voltage of one of the high potential and low potential power supplies to the power supply voltage of the other of the high potential and low potential power supplies. One terminal of the capacitance element is connected to the other terminal of the resistor and the other terminal of the capacitance element is connected to one of the high potential and low potential power supplies.

In other aspect of the present invention, the delay circuit includes: a first inverter for inputting the input signal at an input terminal thereof; a first resistor with one terminal thereof connected to the output terminal of the first inverter; a first capacitance element with one terminal thereof and the other terminal thereof connected to the other terminal of the first resistor and the first power supply, respectively, the capacitance value of the first capacitance element changing 55 according to a transition of a voltage at the one terminal thereof connected to the other terminal of the first resistor; a second inverter with an input terminal thereof connected to a connection point between the first resistor and the first capacitance element; a second resistor with one terminal thereof connected to the output terminal of the second inverter; and a second capacitance element with one terminal thereof and the other terminal thereof connected to the other terminal of the second resistor and the second power supply, respectively, the capacitance value of the second capacitance element changing according to a transition of a voltage at the one terminal thereof connected to the other terminal of the second resistor. A connection point between the second resistor and the sec-

ond capacitance element is the output terminal of a delayed signal, and an in-phase output signal obtained by delaying the transition edge of the input signal is output from the output terminal. In the present invention, the capacitance value of the first capacitance element increases when the voltage at the 5 one terminal thereof connected to the other terminal of the first resistor transitions from the power supply voltage of the first power supply to the power supply voltage of the second power supply, and the capacitance value of the second capacitance element increases when the voltage at the one terminal 10 thereof connected to the other terminal of the second resistor transitions from the power supply voltage of the second power supply to the power supply voltage of the first power supply. In the present invention, preferably, the first capacitance element is constituted from the MOS capacitor. The 15 MOS capacitor constituting the first capacitance element changes to an inversion state when the voltage at the other terminal of the first resistor transitions from the power supply voltage of the first power supply to the power supply voltage of the second power supply. Preferably, the second capaci- 20 tance element is constituted from the MOS capacitor. The MOS capacitor constituting the second capacitance element changes to an inversion state when the voltage at the other terminal of the second resistor transitions from the power supply voltage of the second power supply to the power 25 supply voltage of the first power supply.

The delay circuit according to other aspect of the present invention may further include: a third capacitance element with one terminal thereof and the other terminal thereof connected to the other terminal of the first resistor and the second 30 power supply, respectively, the capacitance value of the third capacitance element changing according to a transition of a voltage at the one terminal thereof connected to the other terminal of the first resistor; and a fourth capacitance element with one terminal thereof and the other terminal thereof con- 35 nected to the other terminal of the second resistor and the first power supply, respectively, the capacitance value of the fourth capacitance element changing according to a transition of a voltage at the one terminal thereof connected to the other terminal of the second resistor. In the present invention, the 40 capacitance value of the third capacitance element increases when the voltage at the one terminal thereof connected to the other terminal of the first resistor transitions from the power supply voltage of the second power supply to the power supply voltage of the first power supply. The capacitance 45 value of the fourth capacitance element increases when the voltage at the one terminal thereof connected to the other terminal of the second resistor transitions from the power supply voltage of the first power supply to the power supply voltage of the second power supply. In the delay circuit 50 according to the present invention, preferably, the third capacitance element is constituted from the MOS capacitor, and the MOS capacitor constituting the third capacitance element changes to an inversion state when the voltage at the other terminal of the first resistor transitions from the power 55 supply voltage of the second power supply to the power supply voltage of the first power supply. Preferably, the fourth capacitance element is constituted from the MOS capacitor, and the MOS capacitor constituting the fourth capacitance element changes to an inversion state when the voltage at the 60 other terminal of the second resistor transitions from the power supply voltage of the first power supply to the power supply voltage of the second power supply.

The delay circuit according to the present invention may include a reset circuit having a first switch inserted between 65 the first power supply and the other terminal of the first resistor and with a control terminal thereof connected to the

8

input terminal of the first inverter. Alternatively, the delay circuit according to the present invention may include the reset circuit having a third inverter with an input terminal thereof connected to the input terminal of the first inverter and a second switch inserted between the other terminal of the second resistor and the second power supply and with the control terminal thereof connected to the output terminal of the third inverter.

The delay circuit according to other aspect of the present invention further includes a third capacitance and a fourth capacitance. The third capacitance is connected between the other terminal of the first resistor and the second power supply, and the capacitance value of the third capacitance increases when the voltage at the other terminal of the first resistor transitions from the power supply voltage of the second power supply to the power supply voltage of the first power supply. The fourth capacitance is connected between the other terminal of the second resistor and the first power supply, and the capacitance value of the fourth capacitance increases when the voltage at the other terminal of the second resistor transitions from the power supply voltage of the first power supply to the power supply voltage of the second power supply. In the present invention, the third capacitance element is constituted from the MOS capacitor. The third capacitance changes to an inversion state when the voltage at the other terminal of the first resistor transitions from the power supply voltage of the second power supply to the power supply voltage of the first power supply. The fourth capacitance element is constituted from the MOS capacitor, and the fourth capacitance changes to an inversion state when the voltage at the other terminal of the second resistor transitions from the power supply voltage of the first power supply to the power supply voltage of the second power supply.

In the semiconductor memory device according to other aspect of the present invention, the peripheral circuit for generating the signal for defining the transition timing of the control signal to the memory cell array and/or the pulse width of the control signal includes the delay circuit for delaying the input signal, and as the delay circuit, the delay circuit according to one of the aspects of the invention described above is provided.

The semiconductor memory device of the present invention includes a circuit for supplying a constant voltage that does not depend on the power supply voltage as a boosted voltage to be supplied to the control line of the memory cell array. In the semiconductor memory device according to the present invention, the memory cell array, the delay circuit, and the peripheral circuit are driven by the relatively low voltage power supply. Alternatively, the memory cell array and the delay circuit may be driven by the low voltage power supply obtained by stepping down the power supply voltage, and the peripheral circuit may be driven by the power supply voltage.

In a method according to other aspect of the present invention for delaying the transition edge of a logic signal by the inverter comprising one or more inverters connected in cascade, one terminal of the resistor is connected to the output terminal of each of the one or more inverters, and the other terminal of the resistor is connected to the power supply through the MOS capacitor, and the method includes:

(a) a step of inputting a rising or falling transition signal to the input terminal of one of the one or more inverters through an input terminal or the other terminal of the resistor with the one terminal thereof connected to the output terminal of the inverter at a preceding stage; and

(b) a step of the MOS capacitor being changed to an inversion state when the output signal of the each of the one or

more inverters transitions from one logic value to the other logic value, the one logic value corresponding to the power supply with the MOS capacitor connected thereto, the MOS capacitor corresponding to the each of the one or more inverters to which the transition signal has been input.

The method of controlling a semiconductor memory device according to other aspect of the present invention includes: driving the memory cell array and a peripheral circuit thereof by the relatively low voltage power supply; supplying the constant voltage that does not depend on the 10 power supply voltage as a boosted voltage to be supplied to a control signal for the memory cell array; and performing signal delay using a delay circuit having a characteristic in which a delay time thereof decreases with reduction of the power supply voltage, by a circuit for generating the signal for 15 defining the transition timing and/or the pulse width of a control signal supplied from the peripheral circuit to the memory cell array.

As clear from the following description, at least one of the problems described above is likewise solved by the inven- 20 principle between the delay circuit shown in FIG. 1 and the tions as set forth in respective claims as well.

### BRIEF DESCRIPTION OF THE DRAWINGS

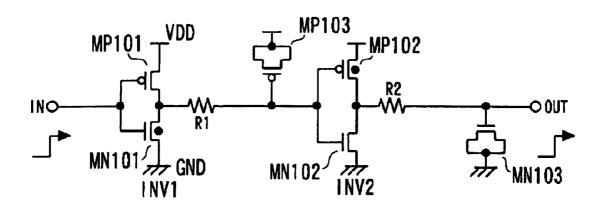

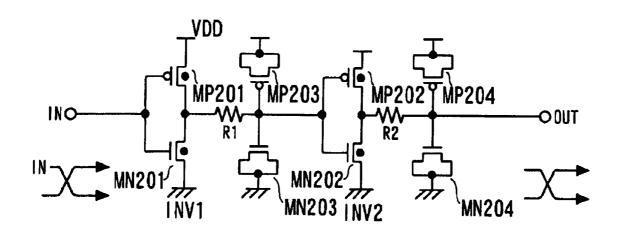

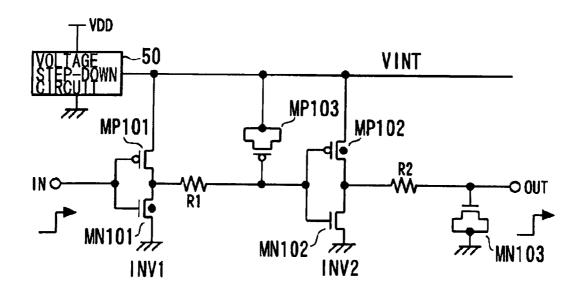

- FIG. 1 is a diagram showing a configuration of a delay circuit according to an embodiment of the present invention;

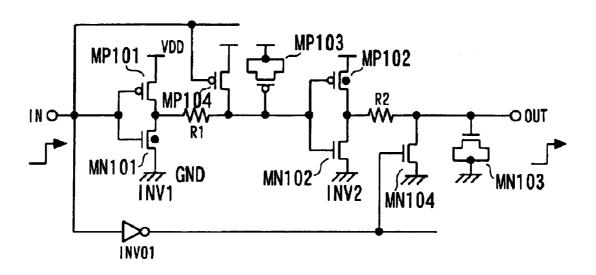

- FIG. 2 is a diagram showing a configuration of a delay circuit according to a second embodiment of the present

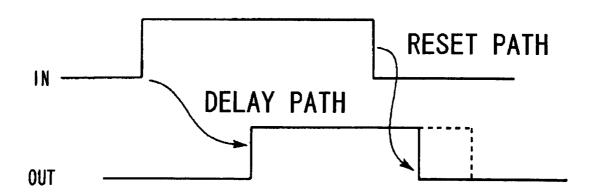

- FIG. 3 is a diagram for explaining a timing operation of the delay circuit according to the second embodiment of the present invention;

- FIG. 4 is a diagram showing a configuration of a delay circuit according to a third embodiment of the present inven-

- FIG. 5 is a diagram showing a configuration of a delay circuit according to a fourth embodiment of the present inven-

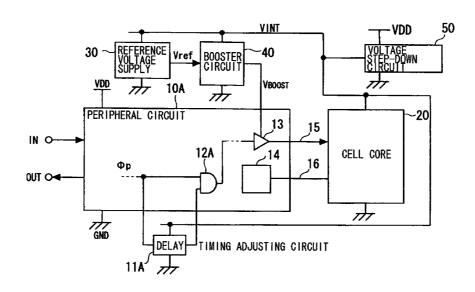

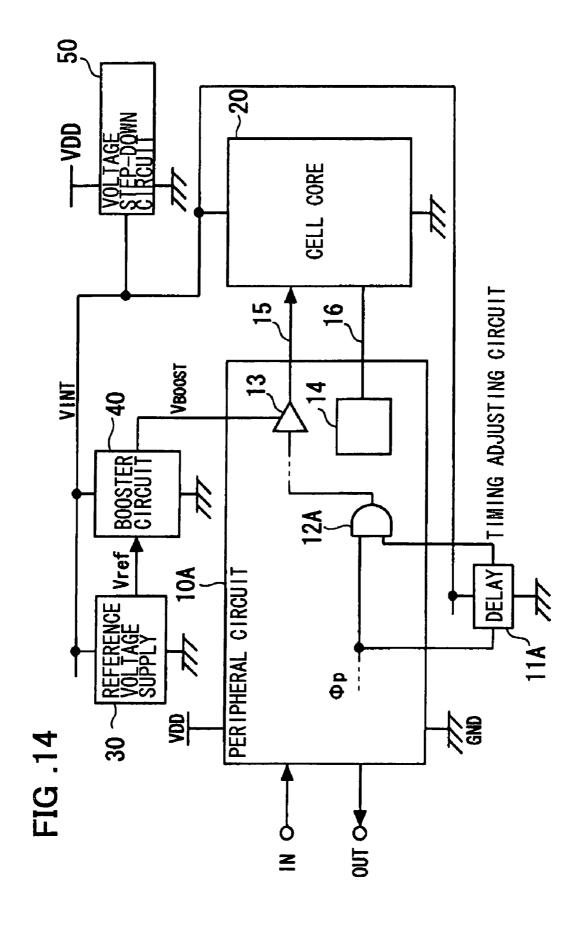

- FIG. 6 is a diagram showing a configuration of a semiconductor memory device according to an embodiment of the present invention;

- FIG. 7 show diagrams for explaining timing operations in the semiconductor memory device according to the embodiment of the present invention;

- FIG. 8 is a diagram showing a configuration example of a boosted voltage generation circuit of the semiconductor memory device according to the embodiment of the present invention;

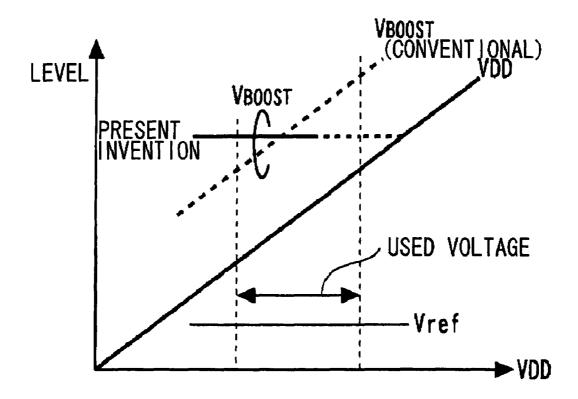

- FIG. 9 is a graph for explaining an operation principle when a power supply voltage has been changed in the semiconductor memory device according to the present invention and an operation of a conventional semiconductor memory device as a comparison example;

- FIG. 10 is a graph for comparing an access time when the power supply voltage has been changed in the semiconductor memory device according to the present invention with an access time of the conventional semiconductor memory device as the comparison example, for explanation;

- FIG. 11 is a graph comparing power supply dependency of the delay time of a delay circuit according to the present invention with power supply dependency of the delay time of a conventional delay circuit as a comparison example, for explanation;

- FIG. 12 is a graph comparing access times when a power supply voltage is set to be low and high in the semiconductor

10

memory device according to the present invention with access times of the conventional semiconductor memory device as the comparison example;

- FIG. 13 is a diagram showing a configuration of a delay circuit according to a fifth embodiment of the present inven-

- FIG. 14 is a diagram showing a configuration of a semiconductor memory device according to a second embodiment of the present invention;

- FIGS. 15A and 15B include diagrams showing a configuration example of the conventional delay circuit;

- FIG. 16 is a diagram schematically showing a driving circuit constituted from a wiring resistance and a parasitic capacitance, for driving a signal line;

- FIG. 17 is a diagram showing an example of a delay circuit proposed in JP Patent Application No. 2001-097083;

- FIG. 18 is a diagram showing an example of a delay circuit proposed in JP Patent Application No. 2001-097083; and

- FIG. 19 is a graph explaining a difference in operation delay circuit in FIG. 15.

### PREFERRED EMBODIMENTS OF THE INVENTION

The preferred embodiments of the present invention will be described with reference to the drawings. A semiconductor device according to a preferred embodiment of the present invention includes a memory cell array (a cell core unit 20 in FIG. 6) in which a plurality of memory cells are arranged in an array form and a word line driving circuit (indicated by reference numeral 13 in FIG. 6) for inputting a constant voltage that does not depend on a provided power supply voltage as a boosted voltage (VBOOST) and driving a selected word line by the constant voltage. The higher voltage level of the amplitude of the selected bit line (indicated by reference numeral 16 in FIG. 6) is the power supply voltage (VDD).

In the present embodiment mode, a sense amplifier (indicated by reference numeral 14 in FIG. 6) amplifies the high potential side of the selected bit line to the power supply voltage. In the semiconductor memory device in its preferred embodiment of the present invention, a peripheral circuit including a circuit for generating a signal for defining the transition timing of a control signal to the memory cell array (the cell core unit 20 in FIG. 6) and/or the pulse width of the control signal has a delay circuit (indicated by reference numeral 11 in FIG. 6). The delay circuit has a characteristic in which its delay time decreases more when the power supply voltage provided to the delay circuit is low than when the power supply voltage is high (refer to FIG. 11).

In the semiconductor memory device according to the embodiment of the present invention, at the time of low voltage driving using the relatively low voltage power supply (VDD), the constant voltage (VBOOST) is constant irrespec-55 tive of the power supply voltage (VDD), and a delay time (tpd) of the control signal is reduced more at the time of the low voltage driving than at the time of high voltage driving using the relatively high power supply voltage (VDD) due to the characteristic of the delay circuit (indicated by reference numeral 11 in FIG. 6). Thus a control mechanism is implemented in which an access time of the memory cell array (cell core unit) is reduced more than in the case of the high voltage driving, and the amount of this reduction (or a difference) cancels out at least part of an increase in the access time due to reduction of the operation speed of the peripheral circuit of the memory cell array caused by the low voltage driving, so that an increase in the delay of the overall access time of the

memory cell array and the peripheral circuit at the time of the low voltage driving is suppressed.

Referring to FIG. 1, the delay circuit in the embodiment of the present invention has one or more delay circuit units each including a CMOS inverter (such as INV1) and a resistor (such as R1), and a MOS capacitor (such as MP203). The CMOS inverter includes a first MOS transistor and a second MOS transistor. The source of the first MOS transistor is connected to a first power supply. The source of the second MOS transistor is connected to a second power supply. The gate of the second MOS transistor and the gate of the first MOS transistor are connected in common to an input terminal. The drain of the second MOS transistor and the drain of the first MOS transistor are connected in common to an output terminal. The second MOS transistor has a conductivity type different from that of the first MOS transistor. One terminal of the resistor is connected to the output terminal of the inverter. The MOS capacitor (such as MP103) is connected between the other terminal of the resistor and the first or second power supply (VDD or GND). In case an input signal is to be output in-phase and delayed according to a desired delay time, the delay circuit includes an even number of the delay circuit units connected in cascade. In case the input signal is to be output in the reverse phase and delayed, the delay circuit includes an odd number of the delay circuit units connected in  $\ ^{25}$ cascade.

When the gate voltage of the MOS capacitor (MP103 or MN103) is the power supply voltage (VDD or GND) to which the MOS capacitor is connected, the MOS capacitor is in an accumulation state. According to a transition of the gate voltage from one power supply voltage (VDD or GND) to the other power supply voltage (GND or VDD) to which the MOS capacitor (such as MP103 or MN103) is connected, a depletion layer or an inversion layer is formed in the surface of a substrate. That is, the MOS capacitor becomes a depletion state or an inversion state.

According to the embodiment of the present invention, one terminal of the resistor is connected to the output terminal of the inverter, and a capacitance element with a capacitance value thereof increasing in response to a transition of the output of the inverter from the one power supply voltage to the other power supply voltage is provided between the other terminal of the resistor and the power supply voltage. The effect of allowing suppression and further reduction of an increase in its delay time with respect to reduction of the power supply voltage (the reverse sensitivity characteristic of power supply voltage dependency) is thereby achieved.

The embodiment of the present invention includes at least a first CMOS inverter (INV1), a first resistor (R1), a first 50 capacitance, a second CMOS inverter (INV2), a second resistor (R2), and a second capacitance. The first CMOS inverter (INV1) inputs an input signal at an input terminal thereof. One terminal of the first resistor (R1) is connected to the output terminal of the first inverter. The first capacitance is 55 constituted from a MOS capacitor (MP103) connected between the other terminal of the first resistor (R1) and the first power supply (VDD). The input terminal of the second CMOS inverter (INV2) is connected to a connection point between the first resistor (R1) and the first capacitance. One 60 terminal of the second resistor (R2) is connected to the output terminal of the second inverter (INV2). The second capacitance is constituted from a MOS capacitor (MN103) connected between the other terminal of the second resistor (R2) and the second power supply (GND). A connection point 65 between the second resistor (R2) and the second capacitance (MN103) is an output terminal (OUT) for a delayed signal. A

12

signal with the transition edge of the input signal delayed is output from the output terminal.

In the present embodiment, the threshold values of a MOS transistor (MN101) of the first inverter (INV1) and a MOS transistor (MP102) of the second inverter (INV2) in the delay circuit for delaying a rising edge for output are set to be low.

In the present embodiment, there is preferably provided a circuit for resetting the output nodes of the inverters in a delay path through a reset path different from the delay path without passage through the delay path. More specifically, referring to FIG. 2, a first switch (MP104) having a control terminal thereof connected to an input terminal (IN) of the first inverter (INV1) and connected between the first power supply and the other terminal of the first resistor (R1) is provided. There are provided a third inverter (INV01) having an input terminal thereof connected to the input terminal (IN) of the first inverter (INV1) and a second switch (MN104) connected between the other terminal of the second resistor (R2) and the second power supply (GND) and having a control terminal thereof connected to the output terminal of the third inverter (INV01).

Referring to FIG. 4, other embodiment of the present invention may include a MOS capacitor (MP203) connected between the other terminal of the first resistor (R1) and the first power supply (VDD), a MOS capacitor (MN203) connected between the other terminal of the first resistor (R1) and the second power supply (GND), a MOS capacitor (MP204) connected between the other terminal of the second resistor (R2) and the first power supply (VDD), and a MOS capacitor (MN204) connected between the other terminal of the second resistor (R2) and the second power supply (GND). With this arrangement, the delay time has the reverse sensitivity characteristic of power supply dependency with respect to rise and fall transitions.

This embodiment may also include the reset circuit. Referring to FIG. 5, for example, a third switch (MP207) connected between the first power supply and the power supply terminal of the first inverter (INV1)(source of a PMOS transistor MP201), which turns on when a control signal for reset (CS) indicates a first logic value, a fourth switch (MN207) connected between the output terminal of the first inverter (INV1) and the second power supply (GND), which turns on when the control signal (CS) indicates a second logic value, and a fifth switch (MN208) connected between the power supply terminal of the second inverter (INV2) (source of the NMOS transistor MN202), which turns on when the control signal (CS) indicates the first logic value are provided.

In the present embodiment, the resistors (such as the first resistor (R1) and the second resistor (R2)) connected to the output terminals of the CMOS inverters are constituted from diffusion resistances on the substrate.

In the semiconductor memory device in its preferred embodiment of the present invention, the delay circuit described in the above embodiments, which has the reverse characteristic in terms of the power supply voltage dependency of the delay time is employed as the delay circuit (indicated by reference numeral 11 in FIG. 6) for generating a signal for defining the transition edge timing or the pulse width of the control signal supplied from the peripheral circuit to a memory cell.

In the semiconductor memory device of the present invention in its preferred embodiment, the power supply voltage VDD for the peripheral circuit including at least one of an X decoder, a Y switch selector, a sense amplifier, and the like is reduced, and the cell core unit (memory cell array) is also driven by the reduced power supply voltage VDD, thereby effecting lower power consumption. As the voltage (boosted

voltage VBOOST) of a control signal supplied to the cell core unit, the constant voltage that does not depend on the power supply voltage is supplied. In the semiconductor memory device in its preferred embodiment of the present invention, the delay circuit for generating the signal for defining the transition edge timing of the control signal supplied from the peripheral circuit to a memory cell and its pulse width is driven by the low voltage power supply.

In the semiconductor memory device in its preferred embodiment of the present invention, by the control signal of which the transition edge or the like is defined by the signal generated by the delay circuit (11), signals for controlling activation of the word line driver for the X decoder and the sense amplifier and a signal for controlling precharging of a bit line are generated. For this reason, even if the peripheral circuit is driven by the low voltage power supply, the delay time of the control signal is not increased compared with driving by the high power supply voltage. Reduction of an access speed (increase in the delay) is thereby suppressed.

In the present embodiment, referring to FIG. 8, a circuit for 20 generating the constant boosted voltage (VBOOST) that does not depend on the power supply voltage includes a circuit (30) for generating a reference voltage Vref that does not depend on the power supply voltage, a comparison circuit (41) for comparing the reference voltage with a divided voltage 25 obtained by voltage-dividing an output boosted voltage, and a step-up converter circuit (40) for receiving the result of comparison and charging a charge pump and performing voltage boosting when it is indicated that the divided voltage is smaller than the reference voltage. The boosted voltage 30 (VBOOST) is supplied as the power supply voltage of the word line driver, and the boosted voltage is supplied to a selected word line. Even when the power supply voltage is reduced, the boosted voltage supplied to the word line is kept to be the same as the boosted voltage when the power supply 35 voltage is high, and reduction of the access speed to a memory cell due to reduction of the power supply voltage is sup-

The peripheral circuit in the memory cell array according to the present invention includes the delay circuit having the 40 reverse sensitivity characteristic with respect to the delay time described above, for example, as the delay circuit driven by the power supply voltage (VDD) supplied to the semiconductor memory device, for generating the signal for defining the delay time of the transition timing of the control signal or 45 the pulse width of the control signal supplied from the peripheral circuit to the memory cell array. The delay circuit (indicated by reference numeral 11A in FIG. 14) is driven by a stepped-down power supply voltage obtained by stepping down the power supply voltage (VDD) supplied to the semi- 50 conductor memory device by a voltage step-down circuit (indicated by reference numeral 50 in FIG. 14). This embodiment as well includes a booster circuit (indicated by reference numeral 40 in FIG. 14) for supplying the constant voltage that does not depend on the power supply voltage as the boosted 55 voltage to be supplied to the memory cell array, based on the reference voltage that does not depend on the power supply voltage. The memory cell array (cell core unit 20) is driven by a stepped-down power supply voltage obtained by stepping down the power supply voltage provided to the semiconduc- 60 tor memory device by the voltage step-down circuit (indicated by reference numeral 50 in FIG. 14).

A delay method according to an embodiment of the present invention is the delay method for delaying the transition edge of a logic signal using one or more inverters connected in 65 cascade. In the circuit configuration in which one terminal of the resistor (indicated by reference numeral R1 or R2 in FIG.

14

1) is connected to the output terminal of one of the one or more inverters and the other terminal of the resistor is connected to the power supply (VDD or GND) through the MOS capacitor (MP103 or MN103 in FIG. 1), the method includes:

(a) a first step of a rising or falling transition signal (transient signal) being supplied to an input terminal of one of the one or more inverters through an input terminal or the other terminal of the resistor with the one terminal connected to the output terminal of the inverter at a preceding stage; and

(b) a second step of the MOS capacitor (indicated by reference numeral MP103 or MN103 in FIG. 1) being changed to an inversion state when the output signal of one of the one or more inverters transitions from one logic value to the other logic value, the one logic value corresponding to the power supply with the MOS capacitor connected thereto, the MOS capacitor corresponding to one of the one or more inverters to which the transition signal has been input.

In the method of controlling a semiconductor memory device according to the embodiment of the present invention, the peripheral circuit (indicated by reference numeral 10 in FIG. 6) including the X decoder, Y switch selector, and sense amplifier is driven by the low voltage power supply. The constant voltage that does not depend on the power supply voltage is supplied as the boosted voltage to be supplied to the memory cell array (indicated by reference numeral 20 in FIG. 6). Then, signal delay by the delay circuit (indicated by reference numeral 11 in FIG. 6) for generation of the pulse signal supplied from the peripheral circuit to a memory cell is performed using the delay method described above.

In a method of controlling a semiconductor memory device according to other embodiment of the present invention, the peripheral circuit is driven by the power supply voltage, and the delay circuit is driven by the stepped-down power supply voltage obtained by stepping down the power supply voltage. The constant voltage that does not depend on the power supply voltage is provided as the boosted voltage to be supplied to the memory cell array. The memory cell array is driven by the stepped-down power supply voltage obtained by stepping down the power supply voltage, and signal delay by the delay circuit (indicated by reference numeral 11 in FIG. 6) for generation of the pulse signal supplied from the peripheral circuit to a memory cell is performed by the delay method described above. Then, the delay circuit is driven by the stepped-down power supply voltage obtained by the stepping down the power supply voltage.

As described above, the semiconductor memory device according to the embodiments of the present invention can achieve the noticeable effect of allowing optimization of a driving power supply (thus power consumption) and an access time in response to the demand for lower power consumption such as speeding up of accesses and reduction of a standby current. The semiconductor memory device according to the embodiments of the present invention avoids an excessive increase in the access time while driving both of the peripheral circuit and the cell core unit by the low voltage power supply, for example. Alternatively, by driving the peripheral circuit by the high power supply voltage and driving the cell core unit by the low voltage power supply, the semiconductor memory device according to the embodiments of the present invention can effect both of speeding up of accesses and suppression of an increase in power consump-

### **EMBODIMENTS**

Embodiments of the present invention will be described below with reference to the drawings so as to describe the

above-mentioned embodiments of the present invention in further detail. FIG. 1 is a diagram showing a configuration of a delay circuit according to an embodiment (a first embodiment) of the present invention.

Referring to FIG. 1, the delay circuit according to the first embodiment includes a CMOS-type first inverter INV1 and a MOS capacitor as a first stage circuit. The CMOS-type first inverter is constituted from a P-channel MOS transistor MP101 with a source thereof connected to a high potential power supply VDD, and an NMOS transistor MN101. The 10 source of the NMOS transistor MN101 is connected to a low potential power supply GND. The gate of the NMOS transistor MN101 and the gate of the PMOS transistor MP101 are connected in common to an input terminal IN. The drain of the NMOS transistor MN101 and the drain of the PMOS 15 transistor MP101 are connected in common to one terminal of a resistor R1. The MOS capacitor is constituted from a PMOS transistor MP103 connected between the other terminal of the resistor R1 and the power supply VDD. The gate of this PMOS transistor MP103 is connected to the other terminal of 20 the resistor R1, and the source and drain of the PMOS transistor MP103 are connected to the power supply voltage VDD, which is also the substrate gate potential of this PMOS

As a second stage circuit, a CMOS-type second inverter 25 INV2 and a MOS capacitor are provided. The CMOS-type second inverter INV2 is constituted from a PMOS transistor MP102 and an NMOS transistor MN102. The source of the PMOS transistor MP102 is connected to the power supply VDD. The NMOS transistor has its source connected to the 30 power supply GND. The gates of the NMOS transistor MN102 and the PMOS transistor MP102 are connected in common to a connection point between the gate of the MOS transistor MP103 and the resistor R1. The drains of the NMOS transistor MN102 and the PMOS transistor MP102 are connected in common to one terminal of a resistor R2. The MOS capacitor is constituted from an NMOS transistor MN103 connected between the other terminal of the resistor R2 and the power supply GND. The gate of this NMOS resistor R2, and the source and the drain of the NMOS transistor MN103 are connected to the ground power supply GND, which is also the substrate gate potential of this NMOS

In the delay circuit according to the first embodiment of the 45 present invention, the first inverter INV1 receives as an input a signal supplied to the input terminal IN and outputs the inverted signal of the input signal, and the second inverter INV2 receives as an input the output of the first inverter INV1 and outputs the inverted signal of the input signal. Then, an 50 in-phase signal which is input to the input terminal IN and delayed is output from an output terminal OUT. Although FIG. 1 shows two stages of inverters, four stages or six stages may be employed. On the other hand, when the delay circuit outputs a signal having a phase opposite to that of the signal 55 input to the input terminal IN, the delay circuit is constituted from an odd number of stages of inverters.

An operation of the delay circuit according to the first embodiment of the present invention will be described below. The circuit including the first inverter INV1 constituted from 60 the transistors MP101 and MN101, MOS capacitor MP103, second inverter INV2 constituted from the transistors MP102 and MN102, and the MOS capacitor MN103 corresponds to the configuration shown in FIG. 17.

The MOS capacitors MP103 and MN103 become from an 65 offstate to an on state (inversion state) in response to transition of the output of the inverter INV1 from the power supply

16

voltage VDD to the ground voltage GND and transition of the output of the inverter INV2 from the ground voltage GND to the power supply voltage VDD, respectively. More specifically, during fall transition of the output signal voltage of the inverter INV1 from the power supply potential to the ground voltage, a depletion layer or an inversion layer are formed in the substrate surface of the MOS capacitor MP103, so that its capacitance value increases with reduction of the output signal voltage of the inverter INV1. When a gate voltage Vg of the MOS capacitor becomes about several times its threshold voltage Vt, the capacitance value of the MOS capacitor becomes close to the capacitance value of a gate insulation film (capacitance in an accumulation state) due to the C-V characteristic of a typical MOS capacitor.

When the output signal voltage of the inverter INV1 has slightly fallen from the power supply voltage VDD, and in the process of transition in which the output signal voltage of the inverter INV1 falls from the power supply voltage VDD to a threshold voltage Vtph of the PMOS capacitor MP103 or less, or equal or less than VDD-|Vtph|, the time constant value of a CR circuit (constituted from the resistor R1 and the MOS capacitor MP103) including the MOS capacitor MP103 on a delay path changes and gradually increases.

On the other hand, during rising transition of the output signal voltage of the inverter INV2 from the ground voltage to the power supply voltage, the inversion layer is formed in the substrate surface of the NMOS capacitor MN103, and its capacitance value increases with an increase in the output signal voltage of the inverter INV2. The time constant value of a CR circuit (constituted from the resistor R2 and the MOS capacitor MN103) including the NMOS capacitor MN103 on the delay path gradually increases, not being time invariant when the output signal voltage of the inverter INV2 has slightly risen from the ground voltage GND, and in the process of transition in which the output signal voltage of the inverter INV2 rises, exceeding a threshold voltage Vthn of the NMOS capacitor MN103.

More specifically, in the first embodiment of the present transistor MN103 is connected to the other terminal of the 40 invention, referring to the falling waveform of the output signal of the inverter INV1, as indicated by a in FIG. 19, the capacitance value of the PMOS capacitor MP103 is small at the beginning of the falling transition. Thus, its time constant is small, and the ratio of decrease of its amplitude value with respect to a change in time is large. When the output signal voltage of the inverter INV1 becomes close to the ground voltage, the capacitance value increases, and the ratio of decrease of its amplitude value with respect to the change in time is reduced (the waveform becomes blunt). This FIG. 19 is a graph for comparing the falling waveform of the inverter in the delay circuit of the present invention with the falling waveform of the inverter the conventional configuration in FIG. 15, for explanation. The horizontal axis indicates time, while the vertical axis indicates voltage.

Referring to FIG. 1, as the delay path at the time of the fall of the output signal of the inverter INV1, the NMOS transistor MN101 of the inverter INV1 is turned on, and at the other terminal (gate terminal) of the capacitance element (PMOS capacitor MP103) with its one terminal connected to the power supply VDD, negative electric charge (-Q) is accumulated from the power supply GND through the resistor R1. At the terminal of the power supply VDD, electric charge (+Q) is accumulated. One terminal of the capacitance element (PMOS capacitor MP103) is brought to the power supply voltage VDD. When the capacitance value of the capacitance element is indicated by C (being substantially time invariant in this case), the terminal voltage of the other terminal (gate

terminal) is indicated by V, and the value of the current that flows through the NMOS transistor MN101 is indicated by I, we have:

$+Q=C\times(VDD-V)$

Using V=R1×I, and dQ/dt=I, the above equation is formulated as:

$R1 \times C(dV/dt) + V = 0$ ,

where when t=0, V=VDD.

Thus, the falling waveform of the other terminal of the capacitance element (gate terminal of the PMOS capacitor MP103) is determined by:

$V = VDD \times \exp\{-t/(R1 \times C)\}$

In the present embodiment, the stray capacitor between the output terminal of the inverter INV1 and the ground power supply GND is ignored.

Referring to the rising waveform of the output signal of the inverter INV2, its time constant is small, and the ratio of increase of its amplitude value with respect to a change in time is large (with the slope being large) at the beginning of the transition. When the output signal voltage of the inverter INV2 becomes close to the power supply voltage VDD, the capacitance value and thus the time constant increases, and the ratio of increase of its amplitude value with respect to the change in time is reduced (the waveform becomes blunt).

Compared with the configuration shown in FIG. 1, in the case of the configuration in FIG. 15, in response to the falling transition of the output signal voltage of the inverter JV1 from 30 the power supply potential VDD to the ground voltage, the gate voltage of the MOS capacitor JN1 transitions from the power supply potential to the ground potential. Then, the MOS capacitor JN1 changes from the inversion state to the depletion state, and its capacitance value decreases with 35 reduction of the output signal voltage of the inverter JV1. The falling waveform of the output signal of the inverter JV1, as indicated by b in FIG. 19, has a large time constant at the beginning of the transition. Thus, the slope of the waveform is gentle, and as the output signal voltage of the inverter JV1 40 becomes close to the ground voltage GND, the capacitance value becomes smaller, and the ratio of the decrease of its amplitude value with respect to the change in time increases.

In the first embodiment of the present invention, the time constant at the start of transition of the falling waveform of the 45 output signal of the inverter INV1 is smaller than in the end of the transition, and the slope of the transition is sharp. Thus, a time tA (refer to FIG. 19) required for falling to the threshold value Vtph of the PMOS transistor MP102 in the inverter INV2 in the next stage or lower, which receives the fall of the 50 output signal of the inverter INV1 becomes shorter than in the case where the time constant is large at the beginning of the transition. The PMOS transistor MP102 in the inverter INV2 in the next stage is turned on when the voltage at the connection point between the resistor R1 and the gate of the MOS 55 capacitor MP103 in the preceding stage becomes equal to or less than VDD-|Vthp|, and starts to charge the MOS capacitor MN103. The rising waveform of the output signal of the inverter INV2, has a time constant at the start of the transition which is smaller than in the end of the transition, so that the 60 time required for the output signal voltage to exceed a predetermined level (such as a logic threshold voltage) becomes shorter than in the case where the time constant is large at the start. On the other hand, in the case of the configuration in FIG. 15, the time constant at the start of transition of the 65 falling waveform of the output signal of the inverter JV1 is larger than in the end of the transition, and the slope is gentle.

18

Thus, the time from the start of the transition to falling to the threshold value Vtph of the PMOS transistor constituting the inverter INV2 (refer to tB in FIG. 19) becomes longer than in the case where the time constant is small at the beginning of the transition.

In the first embodiment of the present invention, due to a sharp fall of the falling waveform of the output signal of the inverter INV1 at the start of the transition, the time for the output signal of the inverter to fall to the threshold value Vtph or lower is short: it contributes more effectively to the effect of suppressing an increase in the delay time when the power supply voltage VDD has been reduced. This effect also constitutes one of the features of the effects of this embodiment.

Further, in the first embodiment of the present invention, when the power supply voltage VDD is reduced, driving currents of the MOS transistors constituting the inverters decrease, and then on resistances increase in appearance, the capacitance values of the MOS capacitors MP103 and MN103 relatively decrease. An increase in the amount of delay is thereby suppressed. More specifically, the amplitude of the gate voltage Vg of the MOS capacitor is set to the power supply voltage VDD. Due to reduction of the power supply voltage VDD, the ratio to the threshold voltage Vt when the gate voltage of the MOS capacitor is the power supply voltage is reduced, so that the capacitance of the MOS capacitor decreases. If the gate voltage of the NMOS capacitor has become from 3Vt to 2Vt, the capacitance of the MOS capacitor decrease. Thus, an increase in the time constant determined from the on resistance of the transistor of the inverters and the MOS capacitor is suppressed because the capacitance of the MOS capacitor is reduced even if the power supply voltage is reduced. An increase in the delay time is thereby suppressed. This effect also constitutes one of the features of the effects of this embodiment.

As described above, in the delay circuit according to the first embodiment of the present invention, an increase in the delay time of the rising transition edge of the input signal to the inverter INV1 due to reduction of the power supply voltage VDD is suppressed.

Further, in the present embodiment, as in the configuration shown in FIG. 18, the threshold voltage Vthn of the NMOS transistor MN101 in the first inverter INV1 is set to a low value, and the threshold voltage Vthp of the NMOS transistor MP101 in the first inverter INV1 is set to a low value (with an absolute value of |Vthp| being small).

With this arrangement, the input threshold value of the first inverter INV1 is decreased and the input threshold value of the second inverter INV2 is increased, when the power supply voltage VDD is reduced. The delay of the rising transition of the input signal to the high level is made to be relatively shorter than the falling transition of the input signal to the low level, when the power supply voltage VDD is reduced. For this reason, dependency of the delay time of the rise of the input signal to the high level on the power supply voltage is suppressed.

In the delay circuit shown in FIG. 1, which is equipped with the MOS capacitor that is changed from the off state to the on state due to transition of signal at the output section of the inverter, the input threshold value of which is controlled, dependency of the delay time of the rising transition of the input signal from the low level to the high level on the power supply voltage (or the characteristic in which the delay time increases with reduction of the power supply voltage) is suppressed, and the slope indicating the sensitivity (dependency) of the delay time with respect to the reduction of the power

supply voltage is controlled to be appreciably flat. This effect also constitutes one of the features of the effects of the present invention.

The resistor R1 is provided between the output of the first inverter INV1 and the gate terminal of the MOS capacitor 5 MP103, and the resistor R2 is provided between the output of the second inverter and the gate terminal of the MOS capacitor MN103. The output of a CR circuit constituted from a resistance R and a capacitance C transitions according to a time constant  $t\tau(=RC)$  for the resistance R and the capacitance C

The rising signal waveform of this CR circuit is expressed by:

amplitude× $\{1-\exp(-t/t\tau)\}$

The falling signal waveform is expressed by:

amplitude $\times exp(-t/t\tau)$

The resistance R is a fixed value irrespective of the power supply voltage VDD. Thus, when the amplitude for use is reduced, the delay time required for reaching a certain level such as a logic threshold value is also shortened. It is clear from the fact as well that when approximation is made by connecting the starting point and the ending point (or two points corresponding to high and low levels) of transition of the rising or falling signal waveform of the CR circuit by a straight line, the time of the transition is also halved if the amplitude is halved. That is, when the power supply voltage VDD is reduced, a fall time tr of the inverter INV1 in the first stage and a rise time tf of the inverter INV2 in the second stage are shortened. A propagation delay time tpd from rise of the input signal to rise of the output signal in the delay circuit is shortened when the power supply voltage is reduced.

Next, the resistors R1 and R2 employed in the present embodiment will be described. As the resistors R1 and R2, 35 diffusion resistances each constituted from an impurity doped diffusion region in the substrate surface are employed, for example. n-type diffusion region or n-diffusion region provided in a P-type substrate or a well (having a same impurity concentration as that of an LDD (Lightly Doped Drain) 40 region, with impurity concentration being controlled in high precision, for example) are employed.

In order to reduce the variation of the propagation delay time tpd of the delay circuit due to variation (reduction) of the power supply voltage, the resistors (R1, R2) connected to the 45 output sections of the inverters should be high. On the other hand, when the high resistance is implemented by the diffusion resistance, its area increases. The resistance values of the resistors (R1, R2) are set based on the range of the power supply voltage to be reduced, the set delay amount of the 50 delay time, and its variation level, and the like. For practicality, the resistance values may be set to several ten kilo ohms, which is about the same as the on resistances of the MOS transistors in the inverter, or in the order to several mega ohms. When the resistance values are set to be about the same 55 as the on-resistances of the transistors, the resistances are formed in the areas that are almost the same as that of the diffusion region of the transistors, so that an increase in the area of a chip is prevented.

Next, a delay circuit in a different embodiment of the 60 present invention will be described. FIG. **2** is a diagram showing a configuration of the delay circuit in a second embodiment of the present invention. Referring to FIG. **2**, same reference numerals are assigned to same components as those in FIG. **1**. In the second embodiment of the present invention, 65 in addition to the delay path, a reset circuit is provided for the delay circuit in the embodiment shown in FIG. **1**. More spe-

20

cifically, referring to FIG. 2, a PMOS transistor MP104, an inverter INV01, and an NMOS transistor MN104 are provided. The source of the PMOS transistor MP104 is connected to the power supply VDD. The drain of the PMOS transistor MP104 is connected to a connection node between the resistor R1 and the gate of the MOS capacitor MP103. The PMOS transistor MP104 receives an input signal at its gate. The inverter INV01 receives the input signal and outputs its inverted signal. The source of the NMOS transistor MN104 is connected to the ground (GND). The drain of the NMOS transistor MN104 is connected to a connection node between the resistor R2 and the gate of the MOS capacitor MN103. The NMOS transistor MN104 receives the output signal of the inverter INV01 at its gate.