(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4689973号

(P4689973)

(45) 発行日 平成23年6月1日(2011.6.1)

(24) 登録日 平成23年2月25日(2011.2.25)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 29/04 | (2006.01) | G 11 C 29/00 | 6 7 5 B |

| G 11 C 11/15 | (2006.01) | G 11 C 11/15 | 1 9 5   |

| G 11 C 13/00 | (2006.01) | G 11 C 13/00 | A       |

請求項の数 4 (全 13 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-171132 (P2004-171132)  |

| (22) 出願日  | 平成16年6月9日 (2004.6.9)          |

| (65) 公開番号 | 特開2005-353145 (P2005-353145A) |

| (43) 公開日  | 平成17年12月22日 (2005.12.22)      |

| 審査請求日     | 平成19年5月17日 (2007.5.17)        |

|           |                                                        |

|-----------|--------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (74) 代理人  | 100101454<br>弁理士 山田 卓二                                 |

| (74) 代理人  | 100081422<br>弁理士 田中 光雄                                 |

| (74) 代理人  | 100098280<br>弁理士 石野 正弘                                 |

| (72) 発明者  | 辻 高晴<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内               |

審査官 酒井 恭信

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配置された複数の正規メモリセルと、前記複数の正規メモリセルの行および列のいずれか一方を共有して配置され、前記複数の正規メモリセルからのデータ読み出し時に読み出しデータ判定の比較対象となる複数のリファレンスセルとを含む複数の抵抗性メモリセルであって、各々が直列に接続されたアクセストランジスタと抵抗素子を含み前記抵抗素子の抵抗値の変化に応じたデータを記憶する、前記複数の抵抗性メモリセル、

前記複数の抵抗性メモリセルの列に対応して設けられる複数のビット線、

前記複数のビット線と前記抵抗性メモリセルを介して接続される複数のソース線、

通常動作時に、前記複数のソース線のうち前記複数のリファレンスセルに接続される第1のソース線を、前記複数の正規メモリセルに接続される第2のソース線と電気的に接続し、試験モード時に、前記第1のソース線と前記第2のソース線とを電気的に切り離すとともに、前記第1のソース線を、リファレンス電流を印加するための試験リファレンス電流印加部に接続するスイッチ回路を備え、

前記試験リファレンス電流印加部は、前記スイッチ回路と接地電圧との間に設けられている半導体記憶装置。

## 【請求項 2】

前記抵抗素子が磁気抵抗素子であることを特徴とする請求項1記載の半導体記憶装置。

## 【請求項 3】

前記抵抗素子がカルコゲナイト材料の相変化素子であることを特徴とする請求項1記載

の半導体記憶装置。

**【請求項 4】**

前記試験リファレンス電流印加部は、当該半導体記憶装置内部に設けられ、一端が前記スイッチ回路に接続され、他端が前記接地電圧に接続されたリファレンス抵抗であり、試験モード時に、前記スイッチ回路によって前記第1のソース線に接続されることを特徴とする請求項1～3のいずれかに記載の半導体記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、磁気記憶装置に関するもので、特に、正規の磁気メモリセルおよびリファレンスセルへのアクセスの比較に基づいてデータを読出する半導体記憶装置に関する。 10

**【背景技術】**

**【0002】**

磁気ランダムアクセス記憶装置（M R A M デバイス）は、トンネル磁気抵抗（T M R ）効果を有する素子（以下、「トンネル磁気抵抗素子」と称する）をメモリセルとして備えている。

**【0003】**

前記トンネル磁気抵抗素子は、磁気トンネル接合構造を有し、磁化方向が固定された第1の磁性体薄膜と、外部からの印加磁界によって磁化方向が書替え可能な第2の磁性体薄膜と、当該第1および第2の磁性体薄膜に挟まれたトンネル絶縁膜とで構成される。 20

**【0004】**

トンネル磁気抵抗素子は、上記第1および第2の磁性体薄膜の磁気モーメントの向きが平行な状態および反平行な状態で、抵抗がそれぞれ最小値  $R_{\min}$  および最大値  $R_{\max}$  となる特徴を有する。

**【0005】**

したがって、トンネル磁気抵抗素子を有する磁気メモリセル（以下、「M T J メモリセル」とも称する）では、トンネル磁気抵抗素子中の磁気モーメントとの平行状態および反平行状態が、記憶データの論理レベル“0”および“1”とそれぞれ対応付けられる。

**【0006】**

M T J メモリセルの記憶データは、磁性体薄膜の磁化方向を反転可能なしきい値レベルを越えるデータ書き込み界の印加によって書替えられるまで、不揮発的に保持される。一般的にM R A M デバイスにおいては、M T J メモリセルの行に対応して設けられた書き選択線であるディジット線および読み出し選択線であるワード線と、M T J メモリセルの列に対応して設けられたデータ線であるビット線とによって、ランダムアクセスが実現される。すなわち、M T J メモリセルは、ビット線およびワード線／ディジット線の交差部分に対応して配列されることになる。 30

**【0007】**

データ読み出時には、ワード線選択に応じて、選択されたM T J メモリセル（以下、「選択メモリセル」と称する）のトンネル磁気抵抗素子が対応するビット線とソース線との間に電気的に接続される。その状態で、ビット線およびソース線間に電位差を与えることによって生じるM T J メモリセルの通過電流（以下、「メモリセル電流」と称する）、すなわちビット線通過電流を検知して、選択メモリセルの記憶データが読み出される。 40

**【0008】**

具体的には、メモリセル電流が、抵抗  $R_{\max}$  に対応するデータを記憶するM T J メモリセルの通過電流  $I_{\min}$  と、抵抗  $R_{\min}$  に対応するデータを記憶するM T J メモリセルの通過電流を  $I_{\max}$  とのいずれであるかを検知する必要がある。

**【0009】**

この際に、当該M T J メモリセルの通過電流との比較対象となる基準電流を、トンネル磁気抵抗素子を用いて構成されたリファレンスセルによって生成する技術が開示されている（たとえば、特許文献1）。 50

**【0010】**

基準電流は、上述した2種類のメモリセル電流 $I_{max}$ および $I_{min}$ の中間値となるように設定される必要がある。したがって、MTJメモリセルと同様のトンネル磁気抵抗素子を用いて基準電流を生成することにより、基準電流を適切なレベルに設定しやすくなるという効果がある。

**【0011】**

また、相変化メモリはカルコゲナイト材料を利用した素子をメモリセルとして備え、この素子は温度プロファイルにより結晶質と非晶質での相変化が生じる。この各相では低抵抗値( $R_{min}$ )の状態と高抵抗値( $R_{max}$ )の状態を持ち、それぞれが記憶データの論理レベルの“0”と“1”に対応付けられる。この相変化メモリは図3のようなメモリセル構成となる。10

**【0012】**

磁気メモリと異なる点は、書き込み方法が電流磁界ではなくメモリ素子内に流れる電流による温度変化を用いるという点である。一方、読み出しにおいてはセルの抵抗値の高低を検知するという点で相変化メモリと磁気メモリは同じであるため、上述のリファレンスセルを用いた読み出し回路構成は同じ構成となる。以下において特に記述が無い限り、磁気メモリと相変化メモリの両方に適用されるものとする。

**【0013】**

【特許文献1】特開2002-222589号公報

**【発明の開示】****【発明が解決しようとする課題】****【0014】**

上述したように、 $R_{min}$ と $R_{max}$ を用いたリファレンス電流生成方法を用いた場合、予め $R_{min}$ と $R_{max}$ の状態をセルに書き込む必要がある。例えば、ウェーハプロセス後の初期状態において全てのセルが $R_{min}$ にあったとき、リファレンスセルに $R_{max}$ を書き込む必要がある。

**【0015】**

しかし、書き込みに必要な電流というのはデバイスによって異なるため、リファレンスセルへの書き込みの前に書き込み電流のチューニングが必要である。書き込み電流のチューニングにおいては、あるセルに所定の電流で書き込みを行いセルの状態が $R_{min}$ か $R_{max}$ かを判定する必要があるが、リファレンスセルが書き込み前に行っているためその判定が困難であるという問題がある。30

**【0016】**

本発明の目的は、リファレンスセルへの書き込み前の試験において正規のリファレンス電流発生方式とは異なるリファレンス電流を発生させるテストモードを備えた抵抗性半導体記憶装置を提供するものである。

**【課題を解決するための手段】****【0017】**

上記目的を達成するため、本発明に係る半導体記憶装置は、行列状に配置された複数の正規メモリセルと、前記複数の正規メモリセルの行および列のいずれか一方を共有して配置され、前記複数の正規メモリセルからのデータ読出し時に読出しデータ判定の比較対象となる複数のリファレンスセルとを含む複数の抵抗性メモリセルであって、各々が直列に接続されたアクセストランジスタと抵抗素子を含み前記抵抗素子の抵抗値の変化に応じたデータを記憶する、前記複数の抵抗性メモリセル、40

前記複数の抵抗性メモリセルの列に対応して設けられる複数のビット線、

前記複数のビット線と前記抵抗性メモリセルを介して接続される複数のソース線、

通常動作時に、前記複数のソース線のうち前記複数のリファレンスセルに接続される第1のソース線を、前記複数の正規メモリセルに接続される第2のソース線と電気的に接続し、試験モード時に、前記第1のソース線と前記第2のソース線とを電気的に切り離すとともに、前記第1のソース線を、リファレンス電流を印加するための試験リファレンス電50

流印加部に接続するスイッチ回路を備え、

前記試験リファレンス電流印加部は、前記スイッチ回路と接地電圧との間に設けられている。

#### 【0018】

本発明において、前記抵抗素子が、磁気抵抗素子または、カルコゲナイト材料の相変化素子であることが好ましい。

また本発明において、前記試験リファレンス電流印加部は、当該半導体記憶装置内部に設けられ、一端が前記スイッチ回路に接続され、他端が前記接地電圧に接続されたリファレンス抵抗であり、試験モード時に、前記スイッチ回路によって前記第1のソース線に接続されることが好ましい。

10

#### 【発明の効果】

#### 【0023】

書き込みを行ったセルの電流を利用したリファレンス電流発生方式を持つ抵抗性メモリにおいて、リファレンスセルへの書き込み前の試験において、書き込みをせずにリファレンス電流を発生させることができる。また、書き込みで  $R_{min}$  と  $R_{max}$  セル抵抗を作り、これらのセルの電流を利用したリファレンス電流発生方式を持つ抵抗性メモリにおいて、リファレンスセルへの書き込みが正常に行えたかどうかを試験することができる。

#### 【発明を実施するための最良の形態】

20

#### 【0024】

実施の形態1.

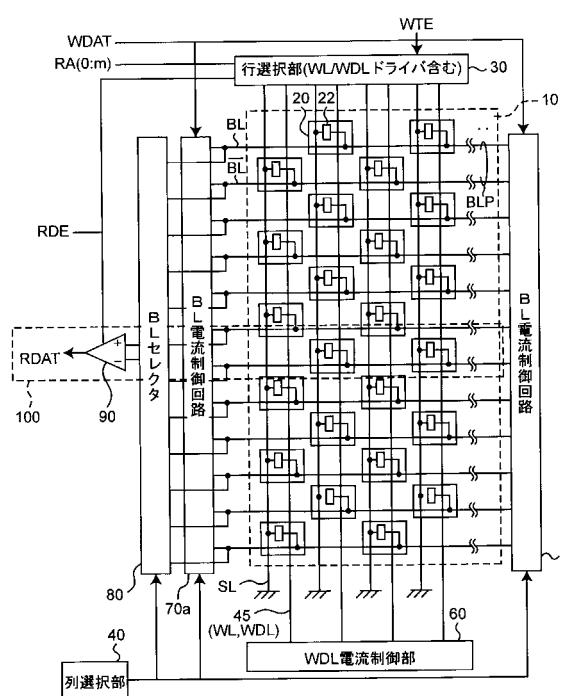

ここでは、磁気メモリのメモリ構成を例にとって説明する。図1は、本発明の実施の形態に従うMRAMデバイス1の全体構成を示すブロック図である。

#### 【0025】

図1を参照して、本発明1の実施の形態に従うMRAMデバイス1は、メモリセルアレイ10と、行選択部30と、列選択部40と、プログラム回路41と、ライトディジット線電流制御部(WDL電流制御部)60と、ビット線電流制御回路(BL電流制御回路)70a、70bと、ビット線セレクタ(BLセレクタ)80と、データ読出アンプ90とを備える。

30

#### 【0026】

メモリセルアレイ10は、ロウアドレス信号RAddおよびコラムアドレス信号CAddによって選択される複数のMTJメモリセル20(以下、「正規メモリセル」とも称する)からなる。後ほど詳細に説明するように、メモリセルアレイ10には、基準電流Irrefを生成するための複数のリファレンスセルおよび当該複数のリファレンスセルを置換するためのスペアセルがさらに配置されている。

#### 【0027】

前記各正規メモリセル20は、トンネル磁気抵抗素子22を含む。トンネル磁気抵抗素子22は、磁気的に書き込まれたデータに応じて抵抗が変化する。MTJメモリセルの抵抗は、記憶データに応じて、 $R_{min}$ または $R_{max}$ となる。なお以下では、抵抗 $R_{max}$ および $R_{min}$ の差を、抵抗差 $R(R=R_{max}-R_{min})$ とも表記する。

40

#### 【0028】

MTJメモリセルの行に対応して、行選択線45が配置される。行選択線45は、データ読出のためのワード線WLおよびデータ書込のためのライトディジット線WDLを総括的に表記したものである。さらに、MTJメモリセル20の列に対応してビット線が配置される。隣接する2本ずつのビット線BLは、ビット線対BLPを構成する。以下においては、同一のビット線対BLPを構成する2本のビット線を、それぞれビット線BLおよび/BLとも称することとする。

#### 【0029】

各メモリセル行において、正規メモリセル20は、ビット線BLおよび/BLの一方と

50

、1行おきに接続される。たとえば、偶数行の正規メモリセル20は、ビット線BLと接続され、奇数行の正規メモリセル20は、ビット線BLと接続されている。

#### 【0030】

この結果、正規メモリセル20は、行選択線45とビット線BL、/BLとの交点に交互配置される。各正規メモリセル20は、対応のビット線BLまたは/BLと、ソース線SLの間に接続される。ソース線SLは、固定電圧(たとえば接地電圧GND)を伝達する。

#### 【0031】

行選択部30は、制御信号RDE、WTEを受けるとともに、入力されたロウアドレス信号に応じて、行選択を実行する。なお、以下では、(m+1)ビット(m:自然数)のアドレスビットRAdd(0)~RAdd(m)で構成される

10

#### 【0032】

ロウアドレスをロウアドレス信号RAdd(0:m)とも表記する。制御信号RDEは、データ読出サイクルに活性状態に設定され、制御信号WTEは、データ書込サイクルに活性状態に限定される。

#### 【0033】

行選択部30は、各ライトディジット線WDLのドライバ機能を含み、データ書込時には、各ライトディジット線WDLの一端側を、ロウアドレス信号RAdd(0:m)に基づく行選択結果に応じた電圧で駆動する。

#### 【0034】

行選択部30は、各ワード線WLのドライバ機能を含み、データ読出時には、ロウアドレス信号RAdd(0:m)に基づく行選択結果に応じて、各ワード線WLの電圧を駆動する。一方WDL電流制御部60は、各ライトディジット線WDLの他端側をアドレス選択結果にかかわらず接地電圧GNDと接続する。

20

#### 【0035】

具体的には、ワード線WLは、データ読出時に選択行において、電源電圧Vccで駆動され、論理ハイレベル(以下、単に「Hレベル」と称する)に設定される。それ以下では、非選択とされて、接地電圧GNDで駆動されて論理ローレベル(以下、単に「Lレベル」と称する)に設定される。

#### 【0036】

同様に、ライトディジット線WDLは、データ書込時に選択行において、選択状態(Hレベル)に設定されて電源電圧Vccで駆動され、それ以外では、非選択状態(Lレベル)に設定されて接地電圧GNDで駆動される。

30

#### 【0037】

この結果、データ書込時において、選択行のライトディジット線WDLには、行選択部30からWDL電流制御部60へ向かう方向へデータ書込電流が供給される。これに対して非選択行のライトディジット線WDLにはデータ書込電流は流されない。

#### 【0038】

一方、データ読出時においては、選択行に対応するワード線WLが選択状態(Hレベル)に設定される一方で非選択行のワード線WLは非選択状態(Lレベル)に維持される。BL電流制御回路70a、70bは、制御信号WDEと、列選択部40によって示される列選択結果と、書込データWDATとに応じて、データ書込時にビット線BL、/BLの両端の電圧を駆動する。具体的には、非選択列のビット線BLの両端が接地電圧GNDで駆動される一方で、選択列のビット線BLは、その一端および他端側を、電源電圧Vccおよび接地電圧GNDの一方ずつでそれぞれ駆動される。

40

#### 【0039】

これにより、書込データWDATのレベルに応じて、BL電流制御回路70aから70bへ向かう方向、あるいはBL電流制御回路70bから70aへ向かう方向にデータ書込電流が供給される。データ書込時以外には、BL電流制御回路70aおよび70bの各々は、各ビット線BL、/BLの両端を電源電圧Vccおよび接地電圧GNDのいずれにも

50

駆動しない。

**【0040】**

データ書込時に、選択メモリセルにおいては、対応のライトディジット線WDLおよび対応のビット線BL（または/NBL）の両方にデータ書込電流が供給されるので、対応のビット線BL（または/NBL）のデータ書込電流に応じた方向にトンネル磁気抵抗素子22が磁化されてデータ書込が実行される。

**【0041】**

BLセレクタ80は、制御信号RDEおよび列選択部40によって示される列選択結果に基づいて、データ読出時に選択列のビット線対BLPを構成するビット線BLおよび/NBLをデータ読出アンプ90と接続する。前記データ読出アンプ90は、選択列のビット線対BLPを構成するビット線BLおよび/NBLの通過電流に基づいて、選択メモリセルからの読出データRDATを生成する。

10

**【0042】**

MRAMデバイス1では、ブロック100に示される、選択されたビット線対BLP、BLセレクタ80およびデータ読出アンプ90によってデータ読出が実行される。

**【0043】**

次に、リファレンスセルの配置について説明する。リファレンスセルの配置としては、上記特許文献に示したようにリファレンスセル列を構成する配置と、リファレンスセルと正規メモリセルとの間でビット線BL、/BLを共有するように、リファレンスセル行を構成する配置とが知られている。以下本明細書においては、リファレンスセル行構成について説明していく。

20

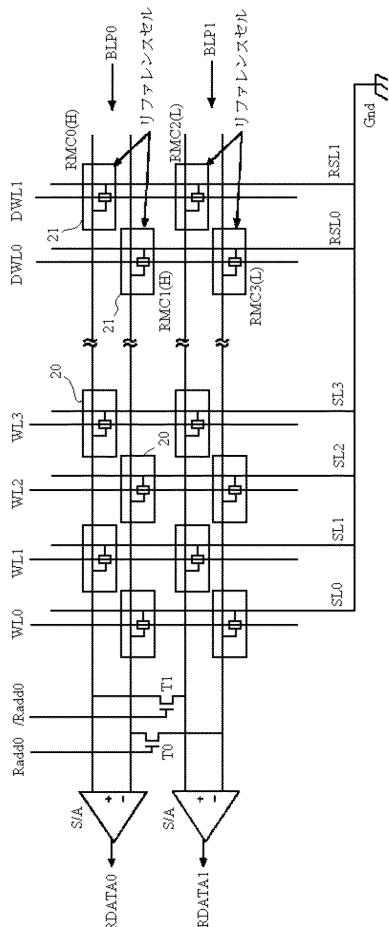

**【0044】**

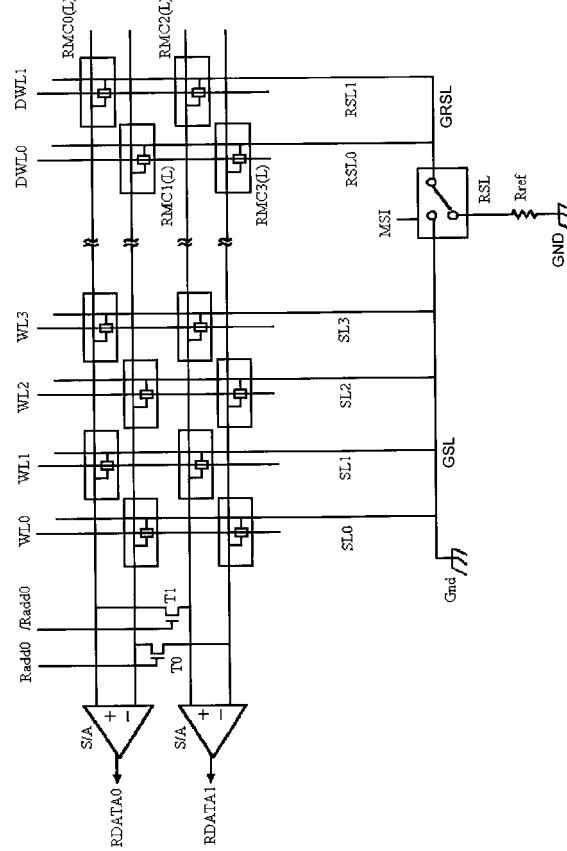

図2は、一般的なリファレンスセル行配置におけるメモリセルアレイ構成およびデータ読出を説明する回路図である。図2には、図1中に示したブロック100の詳細な構成、すなわち、各ビット線対BLPに対応するデータ読出構成が示されている。

**【0045】**

図2を参照して、図1でも説明したように、奇数行のワード線WL1、WL3、…に対応する正規メモリセル20は、ビット線BLと接続されており、偶数行のワード線、WL0、WL2、…に対応する正規メモリセル20は、ビット線/NBLと接続される。

30

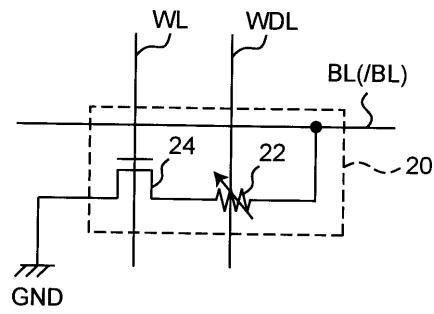

**【0046】**

図3は、各正規メモリセル20の構成を示す回路図である。図3を参照して、正規メモリセル20は、対応のビット線BL（または/NBL）と接地電圧GNDとの間に直列に接続されたトンネル磁気抵抗素子22およびアクセストランジスタ24と、を有する。

**【0047】**

アクセスマスイッチとして設けられるアクセストランジスタ24は、代表的には、N-MOSトランジスタで構成され、そのゲートは対応のワード線WLと接続されている。データ読出時には、対応のワード線WLが選択状態（Hレベル）に設定されるのに応答してアクセストランジスタ24がターンオンして、ビット線BL（または/NBL）から接地電圧GNDに至る経路に、トンネル磁気抵抗素子の抵抗値（RmaxまたはRmin）に応じたメモリセル電流IminまたはImaxが生じる。

40

**【0048】**

データ書込時には、ワード線WLの非選択状態（Lレベル）に応答してアクセストランジスタ24がターンオフされた状態で、対応のライトディジット線WDLおよび対応のビット線BL（または/NBL）に、データ書込電流が供給される。ことによりデータ書込が実行される。

**【0049】**

再び図2を参照して、ビット線BLおよび/NBLには、さらにリファレンスセル21が接続されている。リファレンスセル21は正規メモリセル20と同じセルである。リファレンスセル21は、2つのリファレンスセル行を形成するように配置され、2つのリファ

50

レンスセル行のそれぞれに対応して、ダミーワード線 D W L 0 および D W L 1 が配置される。

#### 【 0 0 5 0 】

ダミーワード線 D W L 0 に対応するリファレンスセル 2 1 は一方のビット線 / B L と接続され、ダミーワード線 D W L 1 に対応するリファレンスセル 2 1 は、もう一方のビット線 B L と接続される。リファレンスセル 2 1 は、各ビット線対 B L P に対応して、同様に設けられている。したがって、リファレンスセル 2 1 は、ダミーワード線 D W L 0 、 D W L 1 とビット線 B L 、 / B L との交点に交互配置される。

#### 【 0 0 5 1 】

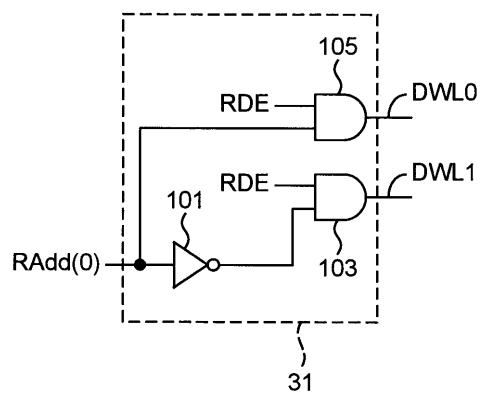

図 4 は、図 1 に示した行選択部 3 0 中の、ダミーワード線 D W L 0 および D W L 1 の制御部分の構成を示す回路図である。

10

#### 【 0 0 5 2 】

図 4 を参照して、行選択部 3 0 中に設けられるダミーワード線制御部 3 1 は、インバータ 1 0 1 と、論理ゲート 1 0 3 および 1 0 5 とを有する。インバータ 1 0 1 は、ロウアドレスの最下位ビット R A d d ( 0 ) を反転して出力する。アドレスビット R A d d ( 0 ) は、偶数行選択時には “ 0 ” ( L レベル ) に設定され、奇数行選択時には 1 ( H レベル ) に設定される。

#### 【 0 0 5 3 】

論理ゲート 1 0 3 は、インバータ 1 0 1 の出力および制御信号 R D E の A N D 演算結果に応じて、ダミーワード線 D W L 1 の電圧を駆動する。同様に、論理ゲート 1 0 5 は、アドレスビット R A d d ( 0 ) および制御信号 R D E の A N D 演算結果に応じて、ダミーワード線 D W L 0 の電圧を駆動する。

20

#### 【 0 0 5 4 】

この結果、偶数行、すなわちワード線 W L 0 、 W L 2 、 . . . が選択されたデータ読出時にはダミーワード線 D W L 1 が選択状態 ( H レベル ) へ設定され、かつ、ダミーワード線 D W L 0 が非選択状態 ( L レベル ) に設定される。これにより、各ビット線対 B L P において、ビット線 / B L に正規メモリセル 2 0 が接続される一方で、ビット線 B L に対してリファレンスセル 2 1 が接続される。

#### 【 0 0 5 5 】

反対に、奇数行、すなわちワード線 W L 1 、 W L 3 、 . . . が選択されたデータ読出時には、ダミーワード線 D W L 0 および D W L 1 の選択および非選択が偶数行選択時に入れ換えられる。これにより、各ビット線対 B L P において、ビット線 B L に正規メモリセル 2 0 が接続される一方で、ビット線 / B L に対してリファレンスセル 2 1 が接続される。

30

#### 【 0 0 5 6 】

図 2 を参照して、データ読み出し時にはビット線対 B L P 0 を構成する B L 、 / B L の一方にメモリセル電流 I m a x または I m i n が生じ、ビット線 B L 、 / B L の他方にはリファレンス電流 I m i n が生じる。ビット線対 B L P 1 を構成する B L 、 / B L の一方にメモリセル電流 I m a x または I m i n が生じ、ビット線 B L 、 / B L の他方にはリファレンス電流 I m a x が生じる。データ線接続トランジスタ T 0 および T 1 のゲートは、 R A d d ( 0 ) および / R A d d ( 0 ) により制御されており、リファレンスセルが接続された 2 つのデータ線をイコライズする。

40

#### 【 0 0 5 7 】

さらに、センスアンプは 2 組用意されており 2 組のデータ線を同時に読み出す構成となっている。リファレンス線はそれぞれのデータ読み出しアンプに接続され、且つイコライズされているため、リファレンス電流 I r e f は平均化され  $I r e f 1 = ( I m a x + I m i n ) / 2$  となる。これにより、データ読み出しアンプは、 B L もしくは / B L の通過電流に基づいて読み出しデータ R D A T を生成することができる。

#### 【 0 0 5 8 】

図 5 は実施の形態 1 に従うリファレンス電流発生テストモードに関する構成図である。正規メモリセルに接続されたソース線 ( S L 0 、 S L 1 、 . . . ) はメモリアレイの外で

50

1本のソース線（G S L）に接続されている。一方リファレンスセルのソース線（R S L 0、R S L 1）はメモリアレイの外部で1本のリファレンスソース線（G R S L）に接続されている。

#### 【0059】

G S LはG n dに接地され、G R S LとG S Lは選択スイッチを介して接続されている。選択スイッチはG R S LとG S Lの接続とG R S Lとリファレンス抵抗R r e fとの接続のどちらかを選択する。

#### 【0060】

通常動作時（M S 1 = L レベル）はG R S LとG S Lの接続が選択され、テストモード時（M S 1 = H レベル）において、G R S LはR r e fと接続される。このとき、リファレンスセルは低抵抗状態であるため、I r e fはR m i n + R r e fで決まるリファレンス抵抗に応じた値となる。すなわち、I m a xとI m i nの平均電流を用いたリファレンス発生方式のアレイ構成を持つメモリにおいて、R m a xの書き込みをせずに中間電流I r e fを発生させることができる。10

#### 【0061】

なお、R r e fはメモリデバイス内に作成された抵抗または試験時にメモリデバイス外で用意された抵抗のどちらでも良い。また、R r e fの代わりに外部に低電流源を接続しても良い。書き込みを行ったセルの電流を利用したリファレンス電流発生方式を持つ抵抗性メモリにおいて、リファレンスセルへの書き込み前の試験において、書き込みをせずにリファレンス電流を発生させることができる。20

#### 【0062】

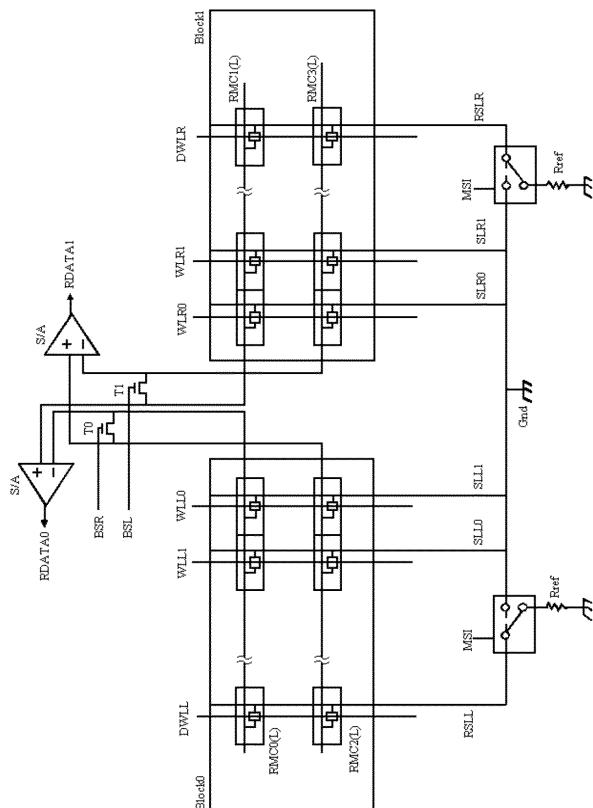

実施の形態2.

実施の形態2を図6に示す。実施の形態1においては1つのブロックで2本のW Lを用いて隣接するB Lペアからデータとリファレンス電流を取り出した。本実施例では、異なる2つのブロックからデータB LとリファレンスB Lを選択し、読み出し回路へ入力していることが第1の実施例とは異なる点である。

#### 【0063】

第1の実施形態と同様にして正規のソース線とリファレンスソース線をスイッチ回路で分離し、試験モード時にはリファレンスソース線に抵抗を付加することができる。書き込みを行ったセルの電流を利用したリファレンス電流発生方式を持つ抵抗性メモリにおいて、リファレンスセルへの書き込み前の試験において、書き込みをせずにリファレンス電流を発生させることができる。30

#### 【0064】

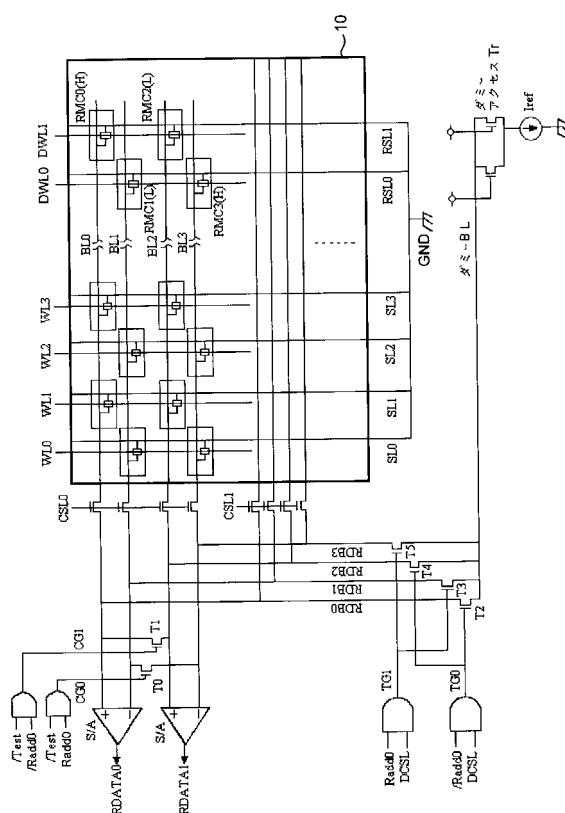

実施の形態3.

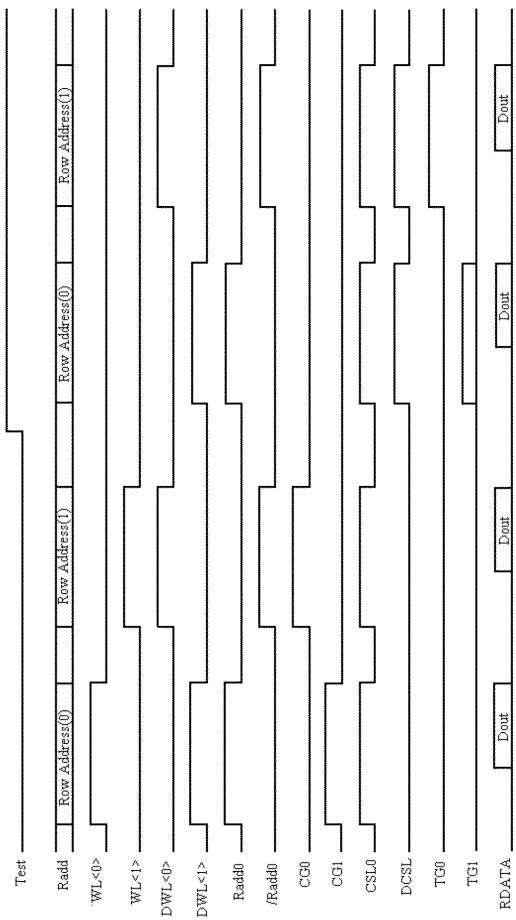

実施の形態3を図7に示す。通常動作では、いずれかのワード線W Lとダミーワード線（D W L）を同時に活性化し、ノーマルセルと複数のリファレンスセルにより発生する平均電流とを比較することで読み出しを行う。図8にこのノーマル動作の信号表を示す。

#### 【0065】

本発明による試験モードにおいては（図9）、W Lは活性化せずノーマルセルに電流を流さない。ダミーW Lは活性化しリファレンス電流は流れるようにする。センスアンプのノーマルセル側の入力はセル電流の代わりにR D B信号線の端に設けられたトランジスタ（T 2～T 5のいずれか）、ダミーB L、ダミーアクセスT r、電流源を介してダミー電流が入力される。40

#### 【0066】

例えば、図10に示した本テストモードの時に、D W L 0が活性化され、C S L 0が選択された場合、R D B 1とR D B 3にC S L 0のゲートT rを介してリファレンスセルの電流が流れ。この場合それぞれのリファレンス電流が平均化されないためにT 0とT 1は共にオフとする。ノーマル動作ではT 0とT 1はどちらかがオンしている。センスアンプの反対側の入力はR D B 0とR D B 2であるが、C S L 0と同じタイミングでD C S Lを活性化することでトランジスタT 2とT 4を介してリファレンス電流が流れることにな50

る。

#### 【0067】

リファレンス電流はデバイス外部からの電流供給である。なお、ダミーBLに接続されているT2～T5はノーマルBLにおけるCSLがゲートに入力された選択ゲートと同じサイズのTrである。また、ダミーアクセストr、ダミーBLはアレイ内のものと同じTr、同じ抵抗値を持つダミーである。また、DCSLのタイミングはノーマルCSLと同じタイミングで活性化される。

#### 【0068】

なお、リファレンス電流は外部印加、もしくはデバイス内部の電流源のどちらでもよい。書き込みでRminとRmaxセル抵抗を作り、これらのセルの電流を利用したリファレンス電流発生方式を持つ抵抗性メモリにおいて、リファレンスセルへの書き込みが正常に行えたかどうかを試験することができる。10

#### 【0069】

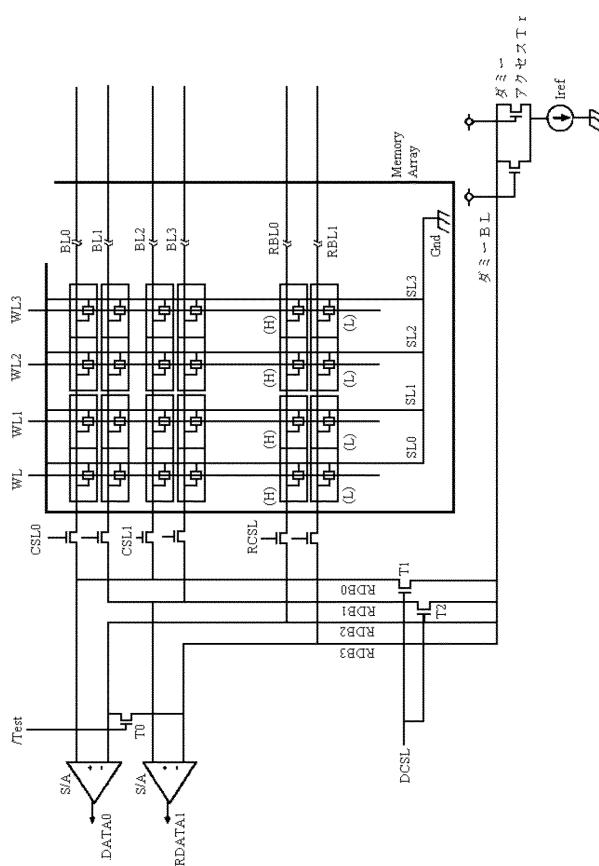

実施の形態4。

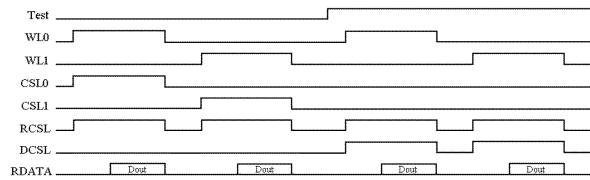

実施の形態4を図11に示す。本実施例は、ノーマルワード線の端にリファレンスピット線を配置し、コラム方向にリファレンスセルを配置したダミーコラム配置である。図12に示すように通常動作([Test=L])では、ワード線(WL0)とコラム選択線(CSL0)を活性化することで、読み出すセルを選択しそれぞれのセンスアンプの一方の入力にピット線電流を入力する。リファレンス側にはリファレンスピット線(RBL)と各ワード線の端に接続されたリファレンスセルの電流が入力される。RBL0はRDB2にRBL1はRDB3に接続される。20

#### 【0070】

例えばRBL0に接続されたセルが高抵抗(Rmax)、RBL1に接続されたセルは低抵抗状態(Rmin)とすると、センスアンプに入力される電流値はトランジスタT0により平均化されて中間の電流値となり、これをリファレンスとして読み出す。

#### 【0071】

試験モード[Test=H]では、ワード線(WL0)とリファレンスコラム選択線(RCSL)を活性化するがコラム選択線(CSL)は活性化しない。その代わりにDCSLを活性化し、試験用のダミーピット線をノーマル側のデータバス(RDB0、RDB1)に接続する。このとき、トランジスタT0は非導通状態とする。30

#### 【0072】

このような選択方法により、リファレンスセルとダミーピット線間の電流差で読み出しを行うことができる。ここで、リファレンス電流は外部印加、もしくはデバイス内部の電流源のどちらでも良い。書き込みでRminとRmaxセル抵抗を作り、これらのセルの電流を利用したリファレンス電流発生方式を持つ抵抗性メモリにおいて、リファレンスセルへの書き込みが正常に行えたかどうかを試験することができる。

#### 【図面の簡単な説明】

#### 【0073】

【図1】本発明による実施の形態に従うMRAMデバイス1の全体構成を示すブロック図。40

【図2】一般的なリファレンスセル行配置におけるメモリセルアレイ構成およびデータ読出を説明する回路図。

#### 【図3】各正規メモリセルの構成を示す回路図。

【図4】図1に示した行選択部30中の、ダミーワード線DWL0およびDWL1の制御部分の構成を示す回路図。

【図5】本発明による実施の形態1に従うリファレンス電流発生テストモードに関する構成図。

【図6】本発明による実施の形態2に従うリファレンス電流発生テストモードに関する構成図。50

【図7】本発明による実施の形態3に従うリファレンス電流発生テストモードに関する構成図。

【図8】本発明による実施の形態3のノーマル動作の信号表。

【図9】本発明による実施の形態3の試験モードの信号表。

【図10】本発明による実施の形態3の書き込み、読み出し動作を示すタイミングチャート。

。

【図11】本発明による実施の形態4に従うリファレンス電流発生テストモードに関する構成図。

【図12】本発明による実施の形態4の書き込み、読み出し動作を示すタイミングチャート。

。

10

#### 【符号の説明】

##### 【0074】

1 M R A M デバイス、 10 メモリセルアレイ、 20 正規メモリセル、 21 リファレンスセル、 22 トンネル磁気抵抗素子、 24 アクセストランジスタ、 30 行選択部、 31 ダミーワード線制御部、 40 列選択部、 41 プログラム回路、 45 行選択線、 60 ライトディジット線電流制御部 (WDL電流制御部)、 70a、 70b ビット線電流制御回路 (BL電流制御回路)、 80 ビット線セレクタ (BLセレクタ)、 90 データ読出アンプ 101 インバータ、 103、 105 論理ゲート。

【図1】

【図2】

【 义 3 】

【図4】

【 図 5 】

【図6】

【図7】

【図8】

| ノーマル動作 |              |            |      |      |    |     |    |     |    |     |

|--------|--------------|------------|------|------|----|-----|----|-----|----|-----|

| Radio0 | WL0,2,4,6... | WL1,3,5... | DWL0 | DWL1 | T0 | T1  | T2 | T3  | T4 | T5  |

| 0      | 選択           | 非選択        | 選択   | 非選択  | 選択 | 非選択 | 選択 | 非選択 | 選択 | 非選択 |

| 1      | 非選択          | 選択         | 選択   | 非選択  | 選択 | 非選択 | 選択 | 非選択 | 選択 | 非選択 |

【図9】

| RDBからの電流印加(ダミーセル試験) |              |            |      |      |     |    |     |    |     |     |

|---------------------|--------------|------------|------|------|-----|----|-----|----|-----|-----|

| Radio0              | WL0,2,4,6... | WL1,3,5... | DWL0 | DWL1 | T0  | T1 | T2  | T3 | T4  | T5  |

| 0                   | 非選択          | 非選択        | 選択   | 非選択  | 非選択 | 選択 | 非選択 | 選択 | 非選択 | 選択  |

| 1                   | 非選択          | 非選択        | 選択   | 非選択  | 非選択 | 選択 | 非選択 | 選択 | 非選択 | 非選択 |

【図11】

【図10】

【図12】

---

フロントページの続き

(56)参考文献 特開2004-062922(JP,A)

特開2004-039184(JP,A)

特開2004-079138(JP,A)

特開2003-059299(JP,A)

特開平11-328987(JP,A)

特開2002-222589(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 29/00 - 29/56

G 11 C 11/15

G 11 C 13/00