(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7548743号

(P7548743)

(45)発行日 令和6年9月10日(2024.9.10)

(24)登録日 令和6年9月2日(2024.9.2)

(51)国際特許分類

H 01 L 23/29 (2006.01)

H 01 L 23/31 (2006.01)

F I

H 01 L 23/30

B

請求項の数 10 (全23頁)

|          |                             |          |                                           |

|----------|-----------------------------|----------|-------------------------------------------|

| (21)出願番号 | 特願2020-124231(P2020-124231) | (73)特許権者 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (22)出願日  | 令和2年7月21日(2020.7.21)        | (74)代理人  | 100105957<br>弁理士 恩田 誠                     |

| (65)公開番号 | 特開2022-20941(P2022-20941A)  | (74)代理人  | 100068755<br>弁理士 恩田 博宣                    |

| (43)公開日  | 令和4年2月2日(2022.2.2)          | (72)発明者  | 村山 啓<br>長野県長野市小島田町80番地 新光電<br>気工業株式会社内    |

| 審査請求日    | 令和5年5月31日(2023.5.31)        | (72)発明者  | 相澤 光浩<br>長野県長野市小島田町80番地 新光電<br>気工業株式会社内   |

|          |                             | (72)発明者  | 金子 周<br>長野県長野市小島田町80番地 新光電<br>気工業株式会社内    |

|          |                             |          | 最終頁に続く                                    |

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

下基板と、

上面に電極パッドを有し、前記下基板の上面に搭載された半導体素子と、

基板本体と、前記基板本体の下面に形成された接着層とを有し、前記半導体素子の上面に

設けられた上基板と、

前記下基板と前記上基板との間に設けられ、前記半導体素子を封止する封止樹脂と、

前記上基板の上面に設けられた配線層と、

前記封止樹脂と同程度の熱膨張係数を有する材料からなり、前記上基板の上面に設けら

れた被覆樹脂と、

前記基板本体及び前記接着層を厚さ方向に貫通して前記電極パッドの上面の一部を露出

する貫通孔と、

前記貫通孔内に形成されるとともに、前記電極パッドと前記配線層とを電気的に接続す

るビア配線と、を有し、

前記被覆樹脂は、前記配線層の側面を被覆しており、

前記半導体素子の上面は、前記接着層によって前記基板本体に接着されており、

前記配線層の厚さは、前記基板本体の厚さよりも大きい半導体装置。

## 【請求項2】

前記被覆樹脂は、前記配線層から露出する前記上基板の上面全面を被覆している請求項

1に記載の半導体装置。

**【請求項 3】**

前記被覆樹脂は、前記配線層の上面を被覆しており、

前記被覆樹脂は、前記配線層の上面の一部を露出する開口部を有している請求項 1 又は請求項 2 に記載の半導体装置。

**【請求項 4】**

前記開口部の底部に露出する前記配線層の上面に設けられた外部接続端子を更に有する請求項 3 に記載の半導体装置。

**【請求項 5】**

前記封止樹脂と前記被覆樹脂とは連続して一体に形成されている請求項 1 から請求項 4 のいずれか一項に記載の半導体装置。

10

**【請求項 6】**

前記封止樹脂は、前記上基板の側面を被覆している請求項 1 から請求項 5 のいずれか一項に記載の半導体装置。

**【請求項 7】**

前記封止樹脂は、前記下基板の側面を被覆し、前記下基板の下面を被覆している請求項 1 から請求項 6 のいずれか一項に記載の半導体装置。

**【請求項 8】**

前記下基板の下面に形成された金属層を更に有する請求項 1 から請求項 7 のいずれか一項に記載の半導体装置。

**【請求項 9】**

前記上基板の平面形状は、前記下基板の平面形状と同じ大きさに形成されている請求項 1 から請求項 8 のいずれか一項に記載の半導体装置。

20

**【請求項 10】**

前記上基板の平面形状は、前記下基板の平面形状よりも小さく形成されている請求項 1 から請求項 8 のいずれか一項に記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置に関するものである。

**【背景技術】**

30

**【0002】**

従来、半導体装置として、電力の制御や電力の供給を行うパワー系の半導体装置（パワー・モジュール）が知られている。この種の半導体装置としては、下基板と上基板との間に搭載された半導体素子と、下基板と上基板との間に設けられて半導体素子を封止する封止樹脂と、半導体素子と電気的に接続され、上基板の上面に形成された配線層とを有するものが知られている。

**【0003】**

なお、上記従来技術に関連する先行技術として、特許文献 1 が開示されている。

**【先行技術文献】****【特許文献】**

40

**【0004】****【文献】特開 2018-120902 号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

ところで、従来の半導体装置では、半導体素子と封止樹脂との熱膨張係数（C T E : Coefficient of Thermal Expansion）の差が大きくなる。これら熱膨張係数の大きな差に起因して、上基板に応力が生じることにより上基板の上面に設けられた配線層にクラックが生じるという問題がある。

**【課題を解決するための手段】**

50

## 【0006】

本発明の一観点によれば、下基板と、上面に電極パッドを有し、前記下基板の上面に搭載された半導体素子と、基板本体と、前記基板本体の下面に形成された接着層とを有し、前記半導体素子の上面に設けられた上基板と、前記下基板と前記上基板との間に設けられ、前記半導体素子を封止する封止樹脂と、前記上基板の上面に設けられた配線層と、前記封止樹脂と同程度の熱膨張係数を有する材料からなり、前記上基板の上面に設けられた被覆樹脂と、前記基板本体及び前記接着層を厚さ方向に貫通して前記電極パッドの上面の一部を露出する貫通孔と、前記貫通孔内に形成されるとともに、前記電極パッドと前記配線層とを電気的に接続するピア配線と、を有し、前記被覆樹脂は、前記配線層の側面を被覆しており、前記半導体素子の上面は、前記接着層によって前記基板本体に接着されており、前記配線層の厚さは、前記基板本体の厚さよりも大きい。

10

## 【発明の効果】

## 【0007】

本発明の一観点によれば、クラックの発生を抑制できるという効果を奏する。

## 【図面の簡単な説明】

## 【0008】

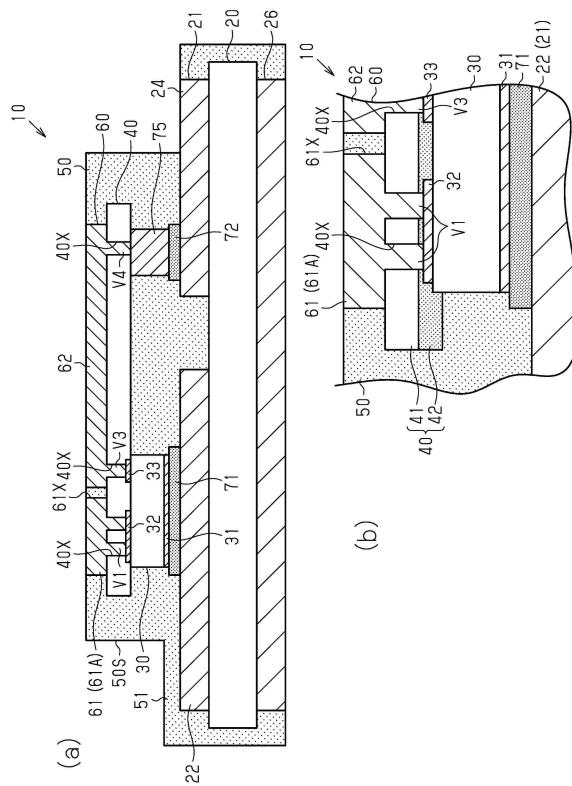

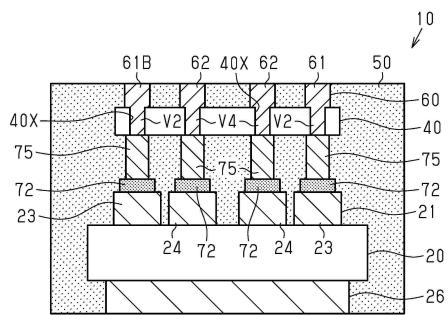

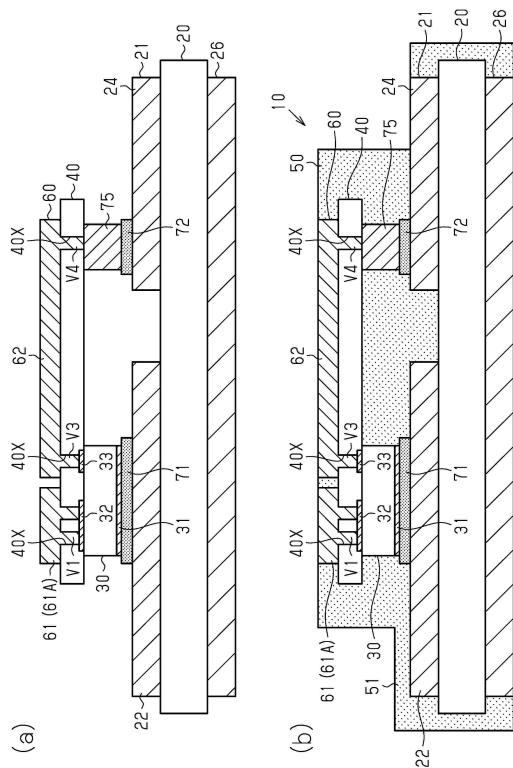

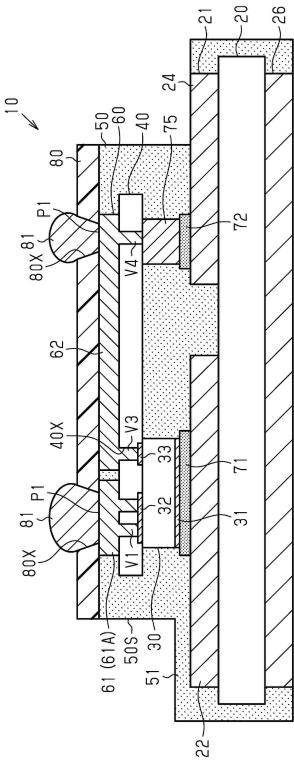

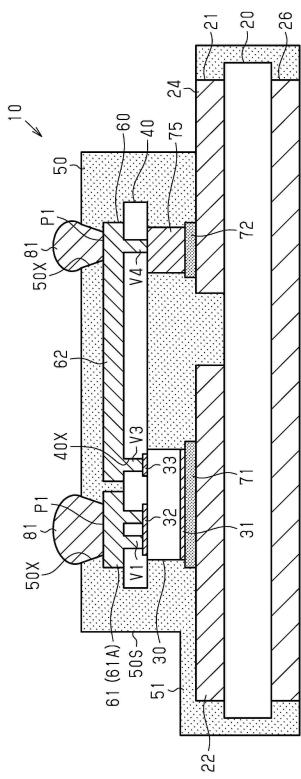

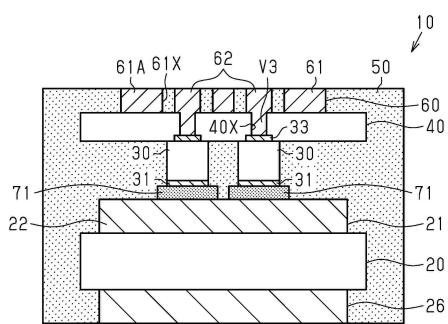

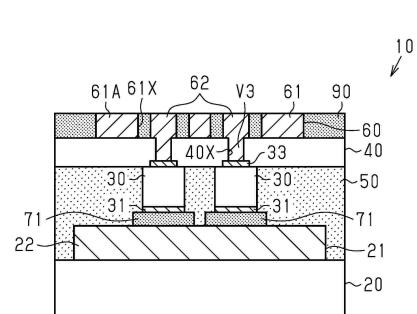

【図1】(a)は、一実施形態の半導体装置を示す概略断面図(図2及び図3における1-1線断面図)、(b)は、図1(a)に示した半導体装置の一部を拡大した拡大断面図である。

20

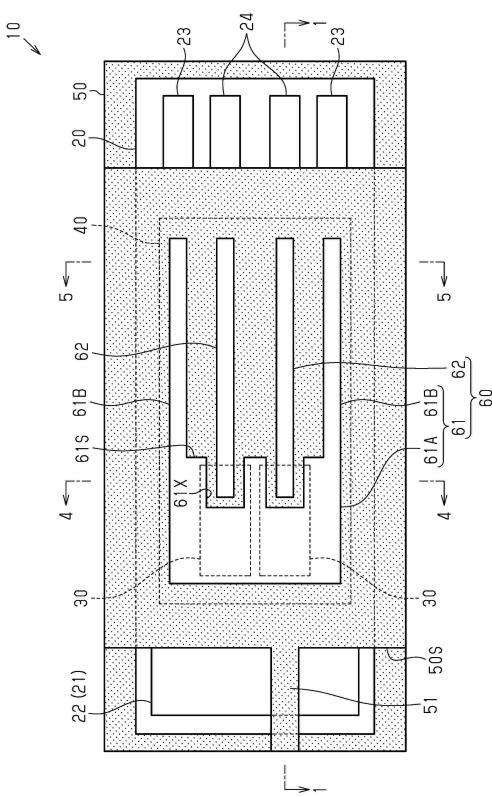

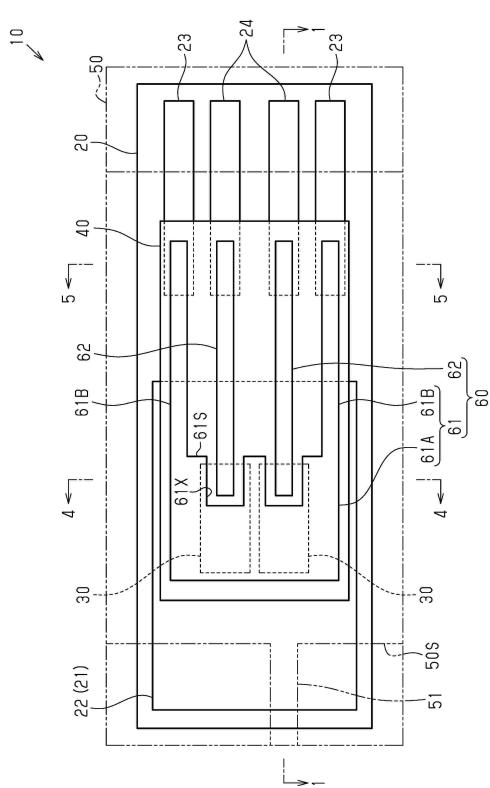

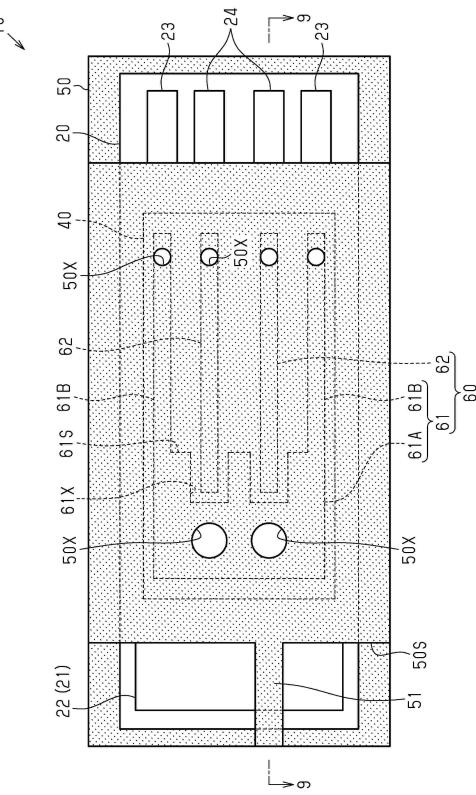

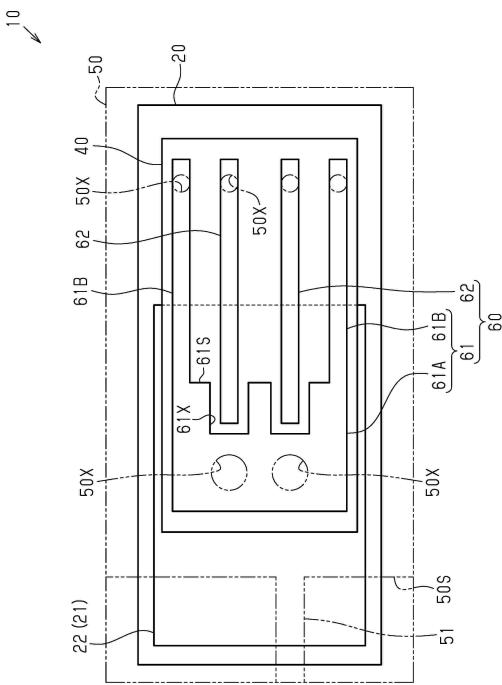

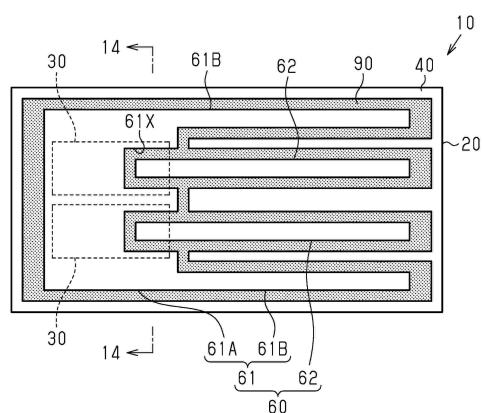

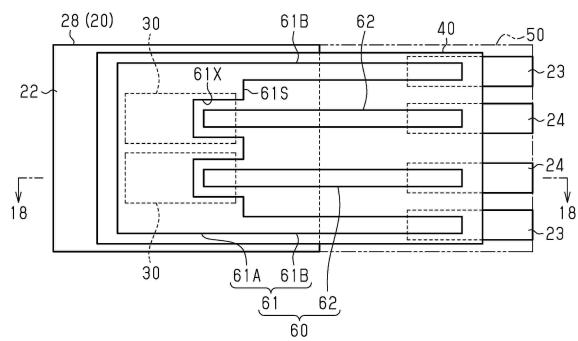

【図2】一実施形態の半導体装置を示す概略平面図である。

【図3】一実施形態の半導体装置を示す概略平面図である。

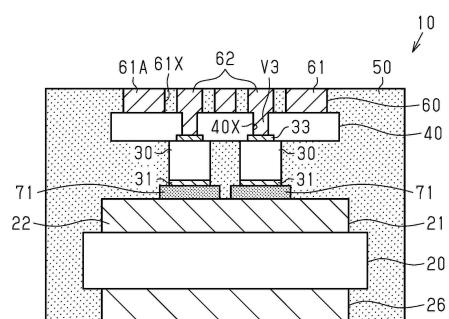

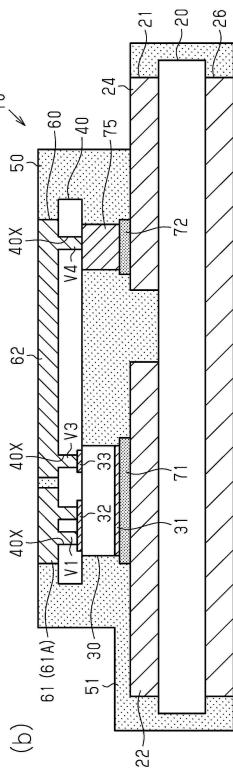

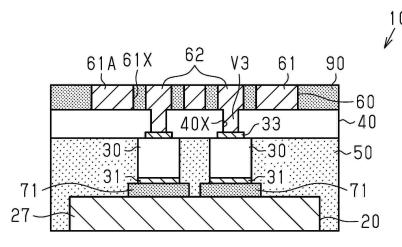

【図4】一実施形態の半導体装置を示す概略断面図(図2及び図3における4-4線断面図)である。

【図5】一実施形態の半導体装置を示す概略断面図(図2及び図3における5-5線断面図)である。

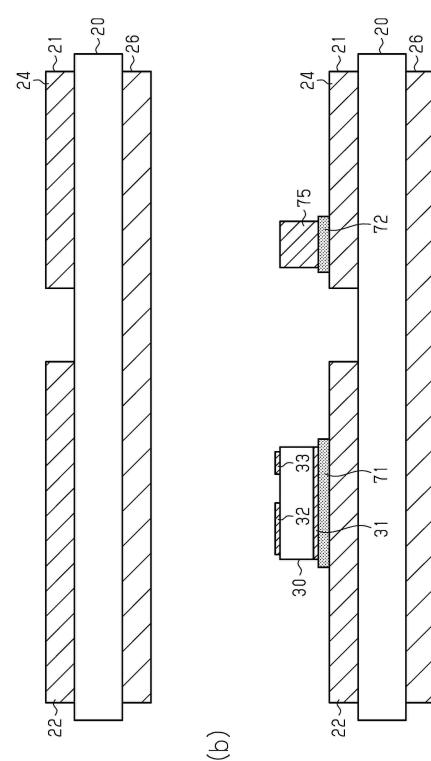

【図6】(a),(b)は、一実施形態の半導体装置の製造方法を示す概略断面図である。

【図7】(a),(b)は、一実施形態の半導体装置の製造方法を示す概略断面図である。

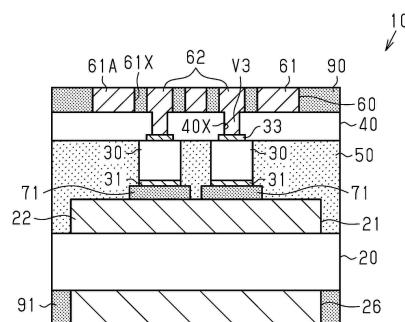

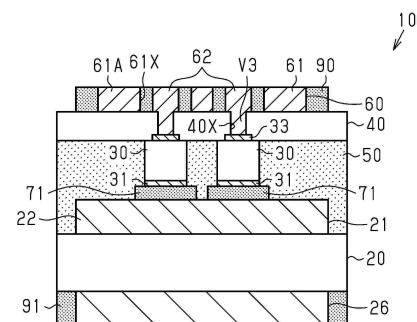

【図8】変更例の半導体装置を示す概略断面図である。

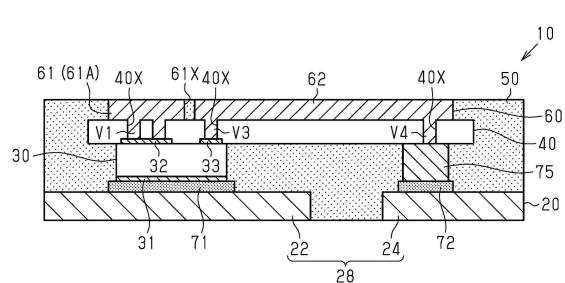

【図9】変更例の半導体装置を示す概略断面図(図10における9-9線断面図)である。

【図10】変更例の半導体装置を示す概略平面図である。

30

【図11】変更例の半導体装置を示す概略平面図である。

【図12】変更例の半導体装置を示す概略断面図である。

【図13】変更例の半導体装置を示す概略断面図である。

【図14】変更例の半導体装置を示す概略断面図(図15における14-14線断面図)である。

【図15】変更例の半導体装置を示す概略平面図である。

【図16】変更例の半導体装置を示す概略断面図である。

【図17】変更例の半導体装置を示す概略断面図である。

【図18】変更例の半導体装置を示す概略断面図(図19における18-18線断面図)である。

40

【図19】変更例の半導体装置を示す概略平面図である。

## 【発明を実施するための形態】

## 【0009】

以下、一実施形態について添付図面を参照して説明する。なお、添付図面は、便宜上、特徴を分かりやすくするために特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが各図面で同じであるとは限らない。断面図では、各部材の断面構造を分かりやすくするために、一部の部材のハッチングを梨地模様に代えて示し、一部の部材のハッチングを省略している。また、本明細書において、「平面視」とは、対象物を図1(a)等の鉛直方向から見ることを言い、「平面形状」とは、対象物を図1(a)等の鉛直方向から見た形状のことを言う。

50

## 【0010】

まず、図1(a)に従って、半導体装置10の構造について説明する。

半導体装置10は、例えば、電力の制御や電力の供給を行うパワー系の半導体装置(パワー モジュール)である。例えば、半導体装置10は、DC-DCコンバータである。半導体装置10は、下基板20と、下基板20の上面に搭載された1つ又は複数(本実施形態では、2つ)の半導体素子30と、半導体素子30の上面に設けられた上基板40とを有している。半導体装置10は、下基板20と上基板40との間に設けられ、半導体素子30を封止する封止樹脂50と、半導体素子30と電気的に接続され、上基板40の上面に設けられた配線層60とを有している。各半導体素子30は、下基板20の上面と上基板40の下面との間に設けられている。半導体装置10では、下基板20と上基板40との間に半導体素子30が内蔵されている。

10

## 【0011】

各半導体素子30は、例えば、シリコン(Si)やシリコンカーバイド(SiC)から形成されている。各半導体素子30は、例えば、パワー系の半導体素子である。例えば、半導体素子30としては、絶縁ゲートバイポーラトランジスタ(IGBT: Insulated Gate Bipolar Transistor)、金属酸化膜半導体電界効果トランジスタ(MOSFET: Metal-Oxide-Semiconductor Field-Effect Transistor)やダイオード等を用いることができる。本実施形態の半導体素子30は、MOSFETである。半導体素子30の平面形状は、任意の形状及び任意の大きさとすることができます。半導体素子30の平面形状は、例えば、矩形状に形成されている。半導体素子30の厚さは、例えば、50μm~600μm程度とすることができます。半導体素子30の熱膨張係数は、例えば、3ppm/~6ppm/程度とすることができます。

20

## 【0012】

半導体素子30は、例えば、電極パッド31と、電極パッド32と、電極パッド33とを有している。電極パッド31は、例えば、半導体素子30の下面に形成されている。例えば、電極パッド31は、半導体素子30の下面全面を被覆するように形成されている。電極パッド32, 33は、例えば、半導体素子30の上面に形成されている。電極パッド32, 33は、半導体素子30の上面において互いに離れて設けられている。電極パッド31は、例えば、MOSFETのドレイン電極である。電極パッド32は、例えば、MOSFETのソース電極である。電極パッド33は、例えば、MOSFETのゲート電極である。

30

## 【0013】

電極パッド31, 32, 33の材料としては、例えば、アルミニウム(Al)や銅(Cu)などの金属、又はこれら金属から選択される少なくとも一種の金属を含む合金を用いることができる。なお、必要に応じて、電極パッド31, 32, 33の表面に表面処理層を形成するようにしてもよい。表面処理層の例としては、金(Au)層、ニッケル(Ni)層/Au層(Ni層とAu層をこの順番で積層した金属層)、Ni層/パラジウム(Pd)層/Au層(Ni層とPd層とAu層をこの順番で積層した金属層)などを挙げることができる。これらAu層、Ni層、Pd層としては、例えば、無電解めっき法により形成された金属層(無電解めっき金属層)を用いることができる。また、Au層はAu又はAu合金からなる金属層、Ni層はNi又はNi合金からなる金属層、Pd層はPd又はPd合金からなる金属層である。

40

## 【0014】

下基板20は、平板状に形成されている。下基板20は、例えば、酸化物系セラミックスや非酸化物系セラミックス等のセラミックスからなるセラミックス基板である。酸化物系セラミックスとしては、例えば、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、ジルコニア(ZrO<sub>2</sub>)などを挙げることができる。非酸化物系セラミックスとしては、例えば、窒化アルミニウム(AlN)、窒化ケイ素(Si<sub>3</sub>N<sub>4</sub>)などを挙げることができる。下基板20の熱膨張係数は、例えば、2ppm/~7ppm/程度とすることができます。

## 【0015】

50

下基板 2 0 の平面形状は、任意の形状及び任意の大きさとすることができます。例えば、下基板 2 0 の平面形状は、矩形状に形成されている。下基板 2 0 の厚さは、例えば、2 0 0 ~ 4 0 0  $\mu\text{m}$  程度とすることができます。

#### 【 0 0 1 6 】

図 2 及び図 3 に示すように、下基板 2 0 の上面には、例えば、配線層 2 1 が形成されている。配線層 2 1 は、例えば、1 つ又は複数（ここでは、1 つ）の配線パターン 2 2 と、1 つ又は複数（ここでは、2 つ）の配線パターン 2 3 と、1 つ又は複数（ここでは、2 つ）の配線パターン 2 4 を有している。なお、図 2 及び図 3 は、図 1 ( a ) に示した半導体装置 1 0 を上方から見た平面図である。また、図 3 では、封止樹脂 5 0 が透視的に描かれている。

10

#### 【 0 0 1 7 】

配線パターン 2 2 , 2 3 , 2 4 の材料としては、例えば、銅や銅合金を用いることができる。なお、必要に応じて、配線パターン 2 2 , 2 3 , 2 4 の表面（上面及び側面、又は上面のみ）に表面処理層を形成するようにしてもよい。表面処理層としては、Au 層、Ni 層 / Au 層、Ni 層 / Pd 層 / Au 層などの金属層を挙げることができる。配線層 2 1 の熱膨張係数は、例えば、15 ppm / ~ 18 ppm / 程度とすることができます。配線パターン 2 2 , 2 3 , 2 4 の厚さは、例えば、100  $\mu\text{m}$  ~ 400  $\mu\text{m}$  程度とすることができます。

#### 【 0 0 1 8 】

図 3 に示すように、配線パターン 2 2 , 2 3 , 2 4 は、下基板 2 0 の上面において互いに離れて設けられている。配線パターン 2 2 , 2 3 , 2 4 の平面形状は、任意の形状及び任意の大きさとすることができます。

20

#### 【 0 0 1 9 】

配線パターン 2 2 の平面形状は、例えば、矩形状に形成されている。配線パターン 2 2 は、例えば、各配線パターン 2 3 , 2 4 の平面形状よりも大きく形成されている。配線パターン 2 2 は、例えば、ベタ状に形成されている。例えば、配線パターン 2 2 は、下基板 2 0 の上面において、図中左側半分の領域に全体的に広がるように形成されている。配線パターン 2 2 は、例えば、その一部が上基板 4 0 と平面視で重なるように設けられている。配線パターン 2 2 は、例えば、半導体素子 3 0 の電極パッド 3 1 ( 図 1 参照 ) と電気的に接続されている。

30

#### 【 0 0 2 0 】

各配線パターン 2 3 の平面形状は、例えば、矩形状に形成されている。各配線パターン 2 3 は、例えば、図中上下方向に所定の幅を有し、図中左右方向に延びる帯状に形成されている。2 つの配線パターン 2 3 は、例えば、図中上下方向において、配線パターン 2 4 よりも外側に設けられている。例えば、2 つの配線パターン 2 3 は、図中上下方向において、2 つの配線パターン 2 4 を挟むように設けられている。各配線パターン 2 3 は、例えば、その一部が上基板 4 0 と平面視で重なるように設けられている。各配線パターン 2 3 は、例えば、半導体素子 3 0 の電極パッド 3 2 ( 図 1 参照 ) と電気的に接続されている。

#### 【 0 0 2 1 】

ここで、本明細書における「上下方向」及び「左右方向」は、各図面において各部材を示す符号が正しく読める向きを正位置とした場合の方向である。

40

各配線パターン 2 4 の平面形状は、例えば、矩形状に形成されている。各配線パターン 2 4 は、例えば、図中上下方向に所定の幅を有し、図中左右方向に延びる帯状に形成されている。各配線パターン 2 4 は、例えば、各配線パターン 2 3 と平行に延びるように形成されている。2 つの配線パターン 2 4 は、例えば、図中上下方向において、配線パターン 2 3 よりも内側に設けられている。各配線パターン 2 4 は、例えば、その一部が上基板 4 0 と平面視において重なるように設けられている。各配線パターン 2 4 は、例えば、半導体素子 3 0 の電極パッド 3 3 ( 図 1 参照 ) と電気的に接続されている。

#### 【 0 0 2 2 】

図 1 ( a ) に示すように、下基板 2 0 の下面には、例えば、金属層 2 6 が形成されてい

50

る。金属層 2 6 の平面形状は、任意の形状及び任意の大きさとすることができます。金属層 2 6 の平面形状は、例えば、矩形状に形成されている。金属層 2 6 は、例えば、ベタ状に形成されている。例えば、金属層 2 6 は、下基板 2 0 の下面のうち外周縁部を除く下面全面に広がるように形成されている。金属層 2 6 は、例えば、下基板 2 0 の反り等を抑制する補強層としての機能を有している。金属層 2 6 は、例えば、放熱部材として機能させることもできる。

#### 【 0 0 2 3 】

金属層 2 6 の材料としては、例えば、銅や銅合金を用いることができる。なお、必要に応じて、金属層 2 6 の表面（下面及び側面、又は下面のみ）に表面処理層を形成するよう 10 にしてもよい。表面処理層としては、Au 層、Ni 層 / Au 層、Ni 層 / Pd 層 / Au 層などの金属層を挙げることができる。金属層 2 6 の厚さは、例えば、100  $\mu\text{m}$  ~ 400  $\mu\text{m}$  程度とすることができます。金属層 2 6 の厚さは、例えば、配線層 2 1 よりも薄く形成されている。

#### 【 0 0 2 4 】

配線パターン 2 2 の上面には、導電性を有する接合部 7 1 を介して半導体素子 3 0 が接合されている。接合部 7 1 は、配線パターン 2 2 に接合されるとともに、電極パッド 3 1 に接合されている。接合部 7 1 は、配線パターン 2 2 と半導体素子 3 0 の電極パッド 3 1 とを電気的に接続している。

#### 【 0 0 2 5 】

図 4 に示すように、接合部 7 1 は、例えば、複数の半導体素子 3 0 に対して共通に設け 20 られている。本実施形態の接合部 7 1 は、2 つの半導体素子 3 0 の電極パッド 3 1 に接合されるとともに、配線パターン 2 2 に接合されている。これにより、2 つの電極パッド 3 1 と配線パターン 2 2 とが接合部 7 1 を介して電気的に接続されている。

#### 【 0 0 2 6 】

各半導体素子 3 0 は、接合部 7 1 を介して配線パターン 2 2 の上面に接合されている。2 つの半導体素子 3 0 は、例えば、半導体装置 1 0 の積層方向（図中上下方向）と直交する平面方向（ここでは、左右方向）において、互いに離れて設けられている。2 つの半導体素子 3 0 は、図中左右方向に沿って並んで設けられている。2 つの半導体素子 3 0 は、例えば、互いに同じ厚さに形成されている。2 つの半導体素子 3 0 の平面形状は、例えば、互いに同じ形状及び同じ大きさに形成されている。図 3 に示すように、各半導体素子 3 0 は、例えば、その全体が配線パターン 2 2 と平面視で重なるように設けられている。各半導体素子 3 0 は、例えば、その全体が上基板 4 0 と平面視で重なるように設けられている。 30

#### 【 0 0 2 7 】

図 5 に示すように、各配線パターン 2 3, 2 4 の上面には、導電性を有する接合部 7 2 が形成されている。各接合部 7 2 の上面には、接続部材 7 5 が形成されている。接合部 7 2 は、配線パターン 2 3 又は配線パターン 2 4 に接合されるとともに、接続部材 7 5 に接合されている。接合部 7 2 は、配線パターン 2 3 と接続部材 7 5 とを電気的に接続している。接合部 7 2 は、配線パターン 2 4 と接続部材 7 5 とを電気的に接続している。

#### 【 0 0 2 8 】

接合部 7 1, 7 2 の材料としては、例えば、金属の焼結材料を用いることができる。焼結材料としては、例えば、銀（Ag）粒子を主成分とする焼結材料（銀シンタリング材料）や銅粒子を主成分とする焼結材料（銅シンタリング材料）を用いることができる。また、接合部 7 1, 7 2 の材料としては、例えば、はんだ、銀ペースト等の導電性ペーストや金属ろう材を用いることもできる。接合部 7 1, 7 2 の厚さは、例えば、20  $\mu\text{m}$  ~ 60  $\mu\text{m}$  程度とすることができます。

#### 【 0 0 2 9 】

接続部材 7 5 は、上基板 4 0 の上面に形成された配線層 6 0 と電気的に接続されている。これにより、配線パターン 2 3, 2 4 は、接合部 7 2 及び接続部材 7 5 を介して配線層 6 0 と電気的に接続されている。接続部材 7 5 は、例えば、半導体装置 1 0 の積層方向（ 50

図中上下方向)に沿って延びる柱状に形成されている。接続部材75は、例えば、金属ポストである。図1(a)に示すように、接続部材75は、例えば、半導体素子30と同じ厚さに形成されている。接続部材75の厚さは、例えば、50μm~600μm程度とすることができる。例えば、接続部材75の上面は、半導体素子30の上面と同一平面上に形成されている。なお、接続部材75の材料としては、例えば、銅や銅合金を用いることができる。

#### 【0030】

上基板40は、半導体素子30の上面及び接続部材75の上面に設けられている。上基板40は、平板状に形成されている。上基板40の平面形状は、任意の形状及び任意の大きさとすることができます。図3に示すように、上基板40の平面形状は、例えば、矩形状に形成されている。上基板40の平面形状は、例えば、下基板20の平面形状よりも小さく形成されている。例えば、上基板40の図中左右方向の寸法は、下基板20の図中左右方向の寸法よりも小さく形成されている。例えば、上基板40の図中上下方向の寸法は、下基板20の図中上下方向の寸法よりも小さく形成されている。上基板40は、例えば、その全体が下基板20と平面視で重なるように設けられている。

10

#### 【0031】

図1(b)に示すように、上基板40は、例えば、基板本体41と、基板本体41の下面に形成された接着層42とを有している。基板本体41の材料としては、例えば、ポリイミド系樹脂やポリエスチル系樹脂などの絶縁性樹脂を用いることができる。接着層42としては、例えば、エポキシ系、ポリイミド系やシリコーン系の接着剤を用いることができる。上基板40の熱膨張係数は、例えば、20ppm/~25ppm/程度とすることができます。基板本体41の厚さは、例えば、30μm~50μm程度とすることができます。接着層42の厚さは、例えば、20μm~40μm程度とすることができます。

20

#### 【0032】

基板本体41は、例えば、接着層42により半導体素子30に接着されている。接着層42は、半導体素子30の上面に接着されるとともに、基板本体41の下面に接着されている。接着層42は、例えば、半導体素子30の一部を内蔵するように設けられている。換言すると、半導体素子30の一部は、接着層42に埋設されている。例えば、半導体素子30の電極パッド32, 33は、接着層42に埋設されている。例えば、半導体素子30の上部は、接着層42に埋設されている。接着層42は、例えば、半導体素子30の上部の側面を被覆するように形成されている。

30

#### 【0033】

上基板40には、上基板40を厚さ方向に貫通する貫通孔40Xが形成されている。貫通孔40Xは、例えば、基板本体41及び接着層42を厚さ方向に貫通して形成されている。貫通孔40Xは、例えば、電極パッド32, 33の上面の一部を露出するように形成されている。図1(a)に示すように、貫通孔40Xは、例えば、接続部材75の上面の一部を露出するように形成されている。

#### 【0034】

配線層60は、上基板40の上面に形成されている。配線層60は、1つ又は複数(ここでは、1つ)の配線パターン61と、1つ又は複数(ここでは、2つ)の配線パターン62とを有している。

40

#### 【0035】

配線パターン61, 62の材料としては、例えば、銅や銅合金を用いることができる。なお、必要に応じて、配線パターン61, 62の表面(上面及び側面、又は上面のみ)に表面処理層を形成するようにしてもよい。表面処理層としては、Au層、Ni層/Au層、Ni層/Pd層/Au層などの金属層を挙げることができる。配線層60の熱膨張係数は、例えば、15ppm/~18ppm/程度とすることができます。配線パターン61, 62の厚さは、例えば、50μm~200μm程度とすることができます。

#### 【0036】

図2及び図3に示すように、配線パターン61, 62は、上基板40の上面において互

50

いに離れて設けられている。配線パターン 6 1, 6 2 の平面形状は、任意の形状及び任意の大きさとすることができます。

【 0 0 3 7 】

配線パターン 6 1 は、例えば、本体部 6 1 A と、本体部 6 1 A から平面方向に延出された延出部 6 1 B とを有している。本体部 6 1 A の平面形状は、例えば、矩形状に形成されている。本体部 6 1 A は、例えば、半導体素子 3 0 と平面視で重なるように設けられている。例えば、本体部 6 1 A は、半導体素子 3 0 の電極パッド 3 2 ( 図 1 ( a ) 参照 ) と平面視で重なるように設けられている。

【 0 0 3 8 】

図 1 ( b ) に示すように、配線パターン 6 1 の本体部 6 1 A は、例えば、電極パッド 3 2 の上面の一部を露出する貫通孔 4 0 X 内に形成されたビア配線 V 1 を介して電極パッド 3 2 と電気的に接続されている。配線パターン 6 1 は、例えば、ビア配線 V 1 と一体に形成されている。本実施形態の配線パターン 6 1 は、複数のビア配線 V 1 と一体に形成されている。複数のビア配線 V 1 は、例えば、平面方向 ( 図中左右方向 ) において互いに離れて設けられている。各ビア配線 V 1 は、例えば、貫通孔 4 0 X を充填するように形成されている。各ビア配線 V 1 は、上基板 4 0 の基板本体 4 1 及び接着層 4 2 を厚さ方向に貫通して形成されている。

【 0 0 3 9 】

図 3 に示すように、本体部 6 1 A のうち配線パターン 6 2 と対向する側の側面 6 1 S には、1 つ又は複数 ( ここでは、2 つ ) の凹部 6 1 X が形成されている。各凹部 6 1 X は、側面 6 1 S から本体部 6 1 A の内方に凹むように形成されている。各凹部 6 1 X は、例えば、本体部 6 1 A のうち各半導体素子 3 0 の電極パッド 3 3 ( 図 4 参照 ) と平面視で重なる部分に設けられている。

【 0 0 4 0 】

各延出部 6 1 B は、例えば、平面視において、本体部 6 1 A の側面 6 1 S から配線パターン 2 3 に向かって延びている。2 つの延出部 6 1 B は、例えば、本体部 6 1 A の図中上下方向の各端部にそれぞれ形成されている。各延出部 6 1 B は、例えば、図中左右方向に沿って延びている。各延出部 6 1 B の先端部は、例えば、配線パターン 2 3 と平面視で重なる位置まで延びるように形成されている。各延出部 6 1 B の平面形状は、例えば、矩形状に形成されている。各延出部 6 1 B の平面形状は、例えば、図中上下方向に所定の幅を有し、図中左右方向に沿って延びる帯状に形成されている。

【 0 0 4 1 】

図 5 に示すように、配線パターン 6 1 の延出部 6 1 B は、例えば、接続部材 7 5 の上面の一部を露出する貫通孔 4 0 X 内に形成されたビア配線 V 2 を介して接続部材 7 5 と電気的に接続されている。配線パターン 6 1 は、例えば、ビア配線 V 2 と一体に形成されている。ビア配線 V 2 は、例えば、貫通孔 4 0 X を充填するように形成されている。配線パターン 6 1 は、ビア配線 V 2 と接続部材 7 5 と接合部 7 2 を介して配線パターン 2 3 と電気的に接続されている。これにより、配線パターン 2 3 は、接合部 7 2 と、接続部材 7 5 と、ビア配線 V 2 と、配線パターン 6 1 と、図 1 ( b ) に示したビア配線 V 1 を介して、半導体素子 3 0 の電極パッド 3 2 ( ソース電極 ) と電気的に接続されている。

【 0 0 4 2 】

図 3 に示すように、各配線パターン 6 2 の平面形状は、例えば、矩形状に形成されている。各配線パターン 6 2 は、例えば、図中上下方向に所定の幅を有し、図中左右方向に延びる帯状に形成されている。各配線パターン 6 2 は、例えば、各配線パターン 6 1 の延出部 6 1 B と平行に延びるように形成されている。2 つの配線パターン 6 2 は、例えば、図中上下方向において、配線パターン 6 1 の延出部 6 1 B よりも内側に設けられている。各配線パターン 6 2 の第 1 端部 ( 図中左端部 ) は、例えば、平面視において、本体部 6 1 A の凹部 6 1 X 内に入り込むように形成されている。各配線パターン 6 2 の第 1 端部は、図 1 ( a ) に示した半導体素子 3 0 の電極パッド 3 3 と平面視で重なる位置に設けられている。

10

20

30

40

50

**【 0 0 4 3 】**

図1 (a) に示すように、各配線パターン62の第1端部は、例えば、電極パッド33の上面の一部を露出する貫通孔40X内に形成されたビア配線V3を介して電極パッド33と電気的に接続されている。配線パターン62は、例えば、ビア配線V3と一緒に形成されている。各ビア配線V3は、例えば、貫通孔40Xを充填するように形成されている。

**【 0 0 4 4 】**

図3に示すように、各配線パターン62の第1端部とは反対側の第2端部(図中右端部)は、例えば、配線パターン24と平面視で重なる位置まで延びるように形成されている。

**【 0 0 4 5 】**

図5に示すように、配線パターン62の第2端部は、例えば、接続部材75の上面の一部を露出する貫通孔40X内に形成されたビア配線V4を介して接続部材75と電気的に接続されている。配線パターン62は、例えば、ビア配線V4と一緒に形成されている。ビア配線V4は、例えば、貫通孔40Xを充填するように形成されている。配線パターン62は、ビア配線V4と接続部材75と接合部72とを介して配線パターン24と電気的に接続されている。これにより、配線パターン24は、接合部72と、接続部材75と、ビア配線V4と、配線パターン62と、図1 (a) に示したビア配線V3とを介して、半導体素子30の電極パッド33(ゲート電極)と電気的に接続されている。

10

**【 0 0 4 6 】**

図1 (a) に示すように、封止樹脂50は、例えば、下基板20と上基板40との間に設けられた半導体素子30、接続部材75及び接合部71, 72を封止するように形成されている。封止樹脂50は、例えば、複数の半導体素子30を一括して封止するように形成されている。封止樹脂50は、例えば、各半導体素子30の側面と、接続部材75の側面と、各半導体素子30から露出する接合部71の上面と、接合部71の側面と、接続部材75から露出する接合部72の上面と、接合部72の側面とを被覆するように形成されている。封止樹脂50は、例えば、上基板40と平面視で重なる部分において、配線層21の側面と、配線層21から露出する下基板20の上面とを被覆するように形成されている。

20

**【 0 0 4 7 】**

封止樹脂50は、例えば、上基板40から露出する配線層21の一部を被覆するように形成されている。封止樹脂50は、例えば、上基板40から露出する配線層21の一部を露出するように形成されている。封止樹脂50は、例えば、上基板40から露出する下基板20の上面の一部を被覆するように形成されている。図2に示すように、封止樹脂50は、例えば、上基板40から露出する下基板20の上面の一部を露出するように形成されている。封止樹脂50は、例えば、下基板20の側面を被覆している。封止樹脂50は、例えば、下基板20の側面全面を被覆している。封止樹脂50は、例えば、下基板20の側面を周囲にわたって被覆している。封止樹脂50は、例えば、下基板20を外側から囲むように形成されている。

30

**【 0 0 4 8 】**

図1 (a) に示すように、封止樹脂50は、例えば、下基板20の下面を被覆するように形成されている。封止樹脂50は、例えば、金属層26から露出する下基板20の下面全面を被覆している。封止樹脂50は、例えば、金属層26の側面を被覆するように形成されている。封止樹脂50は、例えば、金属層26の側面全面を被覆している。封止樹脂50は、例えば、金属層26の下面を露出するように形成されている。封止樹脂50の下面是、例えば、金属層26の下面と同一になるように形成されている。

40

**【 0 0 4 9 】**

封止樹脂50は、例えば、上基板40の側面を被覆するように形成されている。封止樹脂50は、例えば、上基板40の側面全面を被覆している。図2に示すように、封止樹脂50は、例えば、上基板40の側面を周囲にわたって被覆している。封止樹脂50は、例えば、上基板40を外側から囲むように形成されている。

**【 0 0 5 0 】**

50

封止樹脂 5 0 は、例えば、上基板 4 0 の上面を被覆するように形成されている。封止樹脂 5 0 は、例えば、配線層 6 0 から露出する上基板 4 0 の上面全面を被覆している。封止樹脂 5 0 は、例えば、配線層 6 0 の側面を被覆するように形成されている。封止樹脂 5 0 は、例えば、配線層 6 0 の側面全面を被覆している。封止樹脂 5 0 は、例えば、配線層 6 0 の側面に接触している。封止樹脂 5 0 は、例えば、配線パターン 6 1, 6 2 を囲むように形成されている。封止樹脂 5 0 は、例えば、配線パターン 6 1 の凹部 6 1 X を充填するように形成されている。封止樹脂 5 0 は、例えば、配線層 6 0 の上面を露出するように形成されている。封止樹脂 5 0 は、例えば、配線層 6 0 の上面と面一になるように形成されている。

#### 【 0 0 5 1 】

封止樹脂 5 0 は、例えば、上基板 4 0 から露出する配線層 2 1 を覆う部分の側面 5 0 S から平面方向（図中左右方向）に延びる延出部 5 1 を有している。延出部 5 1 は、例えば、配線層 2 1 の配線パターン 2 2 の上面を被覆するように形成されている。図 2 に示すように、延出部 5 1 は、例えば、側面 5 0 S から半導体装置 1 0 の外側面まで延びている。延出部 5 1 は、例えば、図中上下方向に所定の幅を有し、図中左右方向に延びる帯状に形成されている。

#### 【 0 0 5 2 】

封止樹脂 5 0 の材料としては、例えば、熱硬化性樹脂を主成分とする非感光性の絶縁性樹脂を用いることができる。封止樹脂 5 0 の材料としては、例えば、エポキシ系樹脂やポリイミド系樹脂などの絶縁性樹脂、又はこれら樹脂にシリカやアルミナ等のフィラーを混入した樹脂材を用いることができる。封止樹脂 5 0 としては、例えば、モールド樹脂を用いることができる。封止樹脂 5 0 の熱膨張係数は、例えば、5 ppm / ~ 18 ppm / 程度とすることができます。

#### 【 0 0 5 3 】

図 1 ( a ) に示した電極パッド 3 1 は、配線パターン 2 2 を介して封止樹脂 5 0 よりも外側に引き出されている。電極パッド 3 2 は、配線パターン 6 1 及び配線パターン 2 3 ( 図 3 参照 ) を介して封止樹脂 5 0 よりも外側に引き出されている。電極パッド 3 3 は、配線パターン 6 2 及び配線パターン 2 4 を介して封止樹脂 5 0 よりも外側に引き出されている。そして、封止樹脂 5 0 よりも外側に引き出されて封止樹脂 5 0 から露出された配線パターン 2 2, 2 3, 2 4 は、検査用パッドとして機能する。検査用パッドには、例えば、電気特性測定装置のプローブピン ( 図示略 ) が接触される。

#### 【 0 0 5 4 】

##### （ 半導体装置 1 0 の製造方法 ）

次に、半導体装置 1 0 の製造方法について説明する。なお、説明の便宜上、最終的に半導体装置 1 0 の各構成要素となる部分には、最終的な構成要素の符号を付して説明する。

#### 【 0 0 5 5 】

まず、図 6 ( a ) に示す工程では、配線層 2 1 が上面に形成されるとともに、金属層 2 6 が下面に形成された下基板 2 0 を準備する。このとき、配線層 2 1 は、配線パターン 2 2 と配線パターン 2 3 ( 図 3 参照 ) と配線パターン 2 4 とを有している。

#### 【 0 0 5 6 】

次に、図 6 ( b ) に示す工程では、配線層 2 1 の上面に接合部 7 1, 7 2 を形成する。接合部 7 1, 7 2 は、例えば、ペースト状の焼結材料 ( シンタリングペースト ) を印刷法やディスペンサ法により塗布して形成することができる。シンタリングペーストとしては、例えば、銀粒子を有機溶媒に分散させた銀シンタリングペーストを用いることができる。印刷法としては、例えば、スクリーン印刷法やステンシル印刷法を用いることができる。

#### 【 0 0 5 7 】

続いて、接合部 7 1 の上面に半導体素子 3 0 を載置し、接合部 7 2 の上面に接続部材 7 5 を載置する。このとき、半導体素子 3 0 の下面に形成された電極パッド 3 1 が接合部 7 1 の上面に接触するように、半導体素子 3 0 を接合部 7 1 の上面に載置する。

#### 【 0 0 5 8 】

10

20

30

40

50

次いで、接合部 7 1, 7 2 を加熱することにより、接合部 7 1, 7 2 を焼結させる。これにより、配線層 2 1 の配線パターン 2 2 と半導体素子 3 0 の電極パッド 3 1 とが接合部 7 1 により接合され、配線パターン 2 2 上に接合部 7 1 を介して半導体素子 3 0 が接合される。また、配線層 2 1 の配線パターン 2 3, 2 4 ( 図 5 参照 ) と接続部材 7 5 とが接合部 7 2 により接合され、配線パターン 2 3, 2 4 上に接合部 7 2 を介して接続部材 7 5 が接合される。

#### 【 0 0 5 9 】

次に、図 7 ( a ) に示す工程では、半導体素子 3 0 の上面及び接続部材 7 5 の上面に、上基板 4 0 を搭載する。例えば、図 1 ( b ) に示した接着層 4 2 により、半導体素子 3 0 の上面及び接続部材 7 5 の上面に上基板 4 0 を接着する。例えば、半導体素子 3 0 の上面及び接続部材 7 5 の上面にシート状の上基板 4 0 を熱圧着によりラミネートする。

10

#### 【 0 0 6 0 】

続いて、半導体素子 3 0 の電極パッド 3 2, 3 3 の上面の一部が露出されるように上基板 4 0 の所要箇所に貫通孔 4 0 X を形成するとともに、接続部材 7 5 の上面の一部が露出されるように上基板 4 0 の所要箇所に貫通孔 4 0 X を形成する。貫通孔 4 0 X は、例えば、CO<sub>2</sub> レーザや UV - YAG レーザ等によるレーザ加工法によって形成することができる。次いで、貫通孔 4 0 X をレーザ加工法によって形成した場合には、デスマニア処理を行って、貫通孔 4 0 X の底部に露出する電極パッド 3 2, 3 3 及び接続部材 7 5 の露出面に付着した樹脂スミアを除去する。

#### 【 0 0 6 1 】

次に、貫通孔 4 0 X 内にビア配線 V 1 ~ V 4 を形成するとともに、それらビア配線 V 1 ~ V 4 を介して電極パッド 3 2, 3 3 又は接続部材 7 5 と電気的に接続される配線層 6 0 を上基板 4 0 の上面に形成する。このとき、配線層 6 0 は、配線パターン 6 1 と配線パターン 6 2 とを有している。ビア配線 V 1 ~ V 4 及び配線層 6 0 は、例えば、セミアディティブ法などの各種の配線形成方法を用いて形成することができる。

20

#### 【 0 0 6 2 】

次に、図 7 ( b ) に示す工程では、下基板 2 0 と上基板 4 0 との間に設けられた半導体素子 3 0 及び接続部材 7 5 等を封止するとともに、配線層 6 0 の側面に接触してその側面を被覆する封止樹脂 5 0 を形成する。封止樹脂 5 0 は、例えば、上基板 4 0 を全体的に被覆するとともに、下基板 2 0 の側面及び下面を被覆するように形成される。封止樹脂 5 0 は、例えば、樹脂モールド成形法により形成することができる。例えば、封止樹脂 5 0 の材料として熱硬化性を有したモールド樹脂を用いる場合には、1 組の上型及び下型からなる金型の下型の上に図 7 ( a ) に示した構造体を載せ、上方から上型で挟み込むようにして金型内に上記構造体を収容する。続いて、金型のゲート部 ( 図示略 ) から金型内に、圧力 ( 例えば、5 MPa ~ 10 MPa ) を印加して流動化したモールド樹脂を導入する。その後、モールド樹脂を 180 度の温度で加熱して硬化させることにより、封止樹脂 5 0 を形成する。このとき、図示は省略するが、金型には、下基板 2 0 の側面を被覆する封止樹脂 5 0 が形成される領域と、上基板 4 0 を全体的に被覆する封止樹脂 5 0 が形成される領域とを接続する通路が設けられている。この通路にモールド樹脂が導入されることにより、封止樹脂 5 0 に延出部 5 1 が形成される。そして、所要の封止処理を終えると、封止樹脂 5 0 の形成された構造体を上記金型から取り出す。なお、モールド樹脂を充填する方法としては、例えば、ransfer Molding 法、Compression Molding 法やインジェクションモールド法などの方法を用いることができる。

30

#### 【 0 0 6 3 】

以上の製造工程により、本実施形態の半導体装置 1 0 を製造することができる。なお、半導体装置 1 0 は、天地逆の状態で用いることができ、又は任意の角度で配置することができる。

40

#### 【 0 0 6 4 】

次に、本実施形態の作用効果を説明する。

( 1 ) 下基板 2 0 と上基板 4 0 との間に設けられた半導体素子 3 0 を封止する封止樹脂

50

50を、配線層60の側面を被覆するように上基板40の上面にも設けた。この構成によれば、上基板40を上下から封止樹脂50で挟むことができる。このため、半導体素子30と封止樹脂50との熱膨張係数の差に起因して生じる上基板40の歪みを緩和することができる。これにより、上基板40の上面に形成された配線層60にクラックが発生することを抑制できる。

#### 【0065】

(2) また、配線層60の側面を封止樹脂50により被覆するようにした。このため、封止樹脂50によって配線層60の動きを物理的に阻害することができる。これにより、配線層60の歪みを緩和することができるため、配線層60にクラックが発生することを好適に抑制できる。

10

#### 【0066】

(3) 半導体素子30を封止する部分と、配線層60の側面を被覆する部分とを、単層の封止樹脂50により一体に形成した。この構成によれば、同一の封止樹脂50によって上基板40を上下から挟むことができる。このため、半導体素子30と封止樹脂50との熱膨張係数の差に起因して生じる上基板40の歪みを好適に緩和することができる。したがって、上基板40の上面に形成された配線層60にクラックが発生することを好適に抑制できる。

#### 【0067】

(4) 上基板40の側面を被覆するように封止樹脂50を形成した。この構成によれば、封止樹脂50によって上基板40の外周を取り囲むことができる。このため、半導体素子30と封止樹脂50との熱膨張係数の差に起因して生じる上基板40の歪みを好適に緩和することができる。したがって、上基板40の上面に形成された配線層60にクラックが発生することを好適に抑制できる。

20

#### 【0068】

(5) 下基板20の側面を被覆し、下基板20の下面を被覆するように封止樹脂50を形成した。この構成によれば、封止樹脂50によって下基板20の外周を取り囲むことができる。このため、半導体素子30と封止樹脂50との熱膨張係数の差に起因して、下基板20に歪みが発生することを好適に抑制できる。

#### 【0069】

(他の実施形態)

30

上記実施形態は、以下のように変更して実施することができる。上記実施形態及び以下の変更例は、技術的に矛盾しない範囲で互いに組み合わせて実施することができる。

#### 【0070】

・図8に示すように、封止樹脂50の上面に、配線層60の上面を被覆するソルダーレジスト層80を形成してもよい。ソルダーレジスト層80は、例えば、配線層60の上面と面一に形成された封止樹脂50の上面を被覆するように形成されている。ソルダーレジスト層80には、例えば、ソルダーレジスト層80を厚さ方向に貫通し、配線層60の上面の一部を外部接続用パッドP1として露出する開口部80Xが形成されている。

#### 【0071】

この構成によれば、配線層60の上面と封止樹脂50の上面とが面一に形成されているため、それら配線層60及び封止樹脂50の上面に形成されたソルダーレジスト層80の厚さを均一に形成することができる。

40

#### 【0072】

・図8に示すように、開口部80Xの底部に露出する配線層60の上面、つまり外部接続用パッドP1上に、半導体装置10をマザーボード等の実装基板(図示略)に実装する際に使用される外部接続端子81を設けるようにしてもよい。外部接続端子81は、実装基板に設けられたパッドと電気的に接続される接続端子である。外部接続端子81としては、例えば、はんだボールやリードピンを用いることができる。本変更例では、外部接続端子81として、はんだボールを用いている。

#### 【0073】

50

・図9に示すように、配線層60の上面を被覆するように封止樹脂50を形成してもよい。封止樹脂50には、例えば、配線層60の上面の一部を外部接続用パッドP1として露出する開口部50Xが形成されている。外部接続用パッドP1上には、外部接続端子81を設けるようにしてもよい。

#### 【0074】

図10に示すように、開口部50Xは、例えば、配線パターン61の本体部61Aの上面の一部を露出するように形成されている。開口部50Xは、例えば、配線パターン61の各延出部61Bの上面の一部を露出するように形成されている。開口部50Xは、例えば、各配線パターン62の第2端部における上面の一部を露出するように形成されている。各開口部50Xの平面形状は、任意の形状及び任意の大きさに形成することができる。各開口部50Xの平面形状は、例えば、円形状に形成されている。なお、図8に示した開口部80Xも開口部50Xと同様に形成される。

10

#### 【0075】

この構成によれば、封止樹脂50により配線層60の上面が被覆され、その封止樹脂50に開口部50Xが形成されるため、図8に示したソルダーレジスト層80の形成を省略することができる。

#### 【0076】

・図11に示すように、下基板20の上面に形成された配線パターン23, 24を省略してもよい。すなわち、半導体素子30の電極パッド32, 33(図1(a)参照)と電気的に接続された配線パターン61, 62を封止樹脂50の外側に引き出すための配線パターン23, 24を省略してもよい。この場合には、図1(a)に示した接続部材75を省略することができる。また、この場合には、例えば、開口部50Xから露出する配線パターン61, 62を検査用パッドとして利用してもよい。あるいは、開口部50Xとは別に、配線パターン61, 62の上面の一部を検査用パッドとして露出させるための開口部を封止樹脂50やソルダーレジスト層80(図8参照)に設けるようにしてもよい。

20

#### 【0077】

・上記実施形態において、配線パターン22のうち封止樹脂50よりも外側に引き出された部分を省略してもよい。また、配線パターン22のうち上基板40よりも外側に引き出された部分を省略してもよい。

30

#### 【0078】

・上記実施形態では、上基板40を、下基板20よりも平面形状が小さくなるように形成したが、これに限定されない。例えば、上基板40を、下基板20よりも平面形状が大きくなるように形成してもよい。

#### 【0079】

また、例えば図12に示すように、上基板40の平面形状を、下基板20の平面形状と同じ大きさに形成してもよい。例えば、上基板40の平面形状を、下基板20の平面形状と同じ形状及び同じ大きさに形成してもよい。本変更例の上基板40は、平面視において、その全体が下基板20と重なるように設けられている。

#### 【0080】

・上記実施形態では、下基板20と上基板40との間に設けた半導体素子30を封止する封止樹脂50を、配線層60の側面を被覆するように形成した。すなわち、半導体素子30を封止する部分と、配線層60の側面を被覆する部分とを単層の封止樹脂50により一体に形成した。しかし、これに限定されない。

40

#### 【0081】

例えば図13に示すように、半導体素子30を封止する封止樹脂50とは別に、配線層60の側面を被覆する被覆樹脂90を上基板40の上面に設けるようにしてもよい。すなわち、半導体素子30を封止する封止樹脂50と、配線層60の側面を被覆する被覆樹脂90とを別部材で構成するようにしてもよい。このとき、被覆樹脂90の材料としては、封止樹脂50と同程度の熱膨張係数を有する材料を用いることができる。ここで、本明細書において、「同程度の熱膨張係数」の「同程度」は、封止樹脂50の熱膨張係数と被覆

50

樹脂 90 の熱膨張係数との差が 10 ppm / 以下の範囲のことである。被覆樹脂 90 の熱膨張係数は、例えば、5 ppm / ~ 28 ppm / 程度とすることができる。例えば、被覆樹脂 90 の熱膨張係数は、被覆樹脂 90 の熱膨張係数と封止樹脂 50 の熱膨張係数との差が、被覆樹脂 90 の熱膨張係数と半導体素子 30 の熱膨張係数との差よりも小さくなるように設定されている。例えば、被覆樹脂 90 の熱膨張係数は、被覆樹脂 90 の熱膨張係数と封止樹脂 50 の熱膨張係数との差が、被覆樹脂 90 の熱膨張係数と上基板 40 の熱膨張係数との差よりも小さくなるように設定されている。被覆樹脂 90 の材料としては、例えば、封止樹脂 50 と同様の材料を用いることができる。被覆樹脂 90 の材料としては、例えば、熱硬化性樹脂を主成分とする非感光性の絶縁性樹脂を用いることができる。被覆樹脂 90 の材料としては、例えば、エポキシ系樹脂やポリイミド系樹脂などの絶縁性樹脂、又はこれら樹脂にシリカやアルミナ等のフィラーを混入した樹脂材を用いることができる。被覆樹脂 90 としては、例えば、モールド樹脂、アンダーフィル樹脂やポッティング樹脂などを用いることができる。被覆樹脂 90 は、例えば、樹脂モールド成形法やポッティング法により形成することができる。

#### 【0082】

本変更例の被覆樹脂 90 は、配線層 60 の側面全面を被覆している。被覆樹脂 90 は、配線層 60 の側面に接触している。被覆樹脂 90 は、例えば、配線層 60 の上面を露出するように形成されている。被覆樹脂 90 の上面は、例えば、配線層 60 の上面と面一になるように形成されている。被覆樹脂 90 は、例えば、配線層 60 から露出する上基板 40 の上面全面を被覆するように形成されている。

#### 【0083】

この構成によれば、下基板 20 と上基板 40 との間に設けられた半導体素子 30 を封止する封止樹脂 50 と、封止樹脂 50 と同程度の熱膨張係数を有する材料からなり、配線層 60 の側面を被覆する被覆樹脂 90 とによって、上基板 40 を上下から挟むことができる。すなわち、同程度の熱膨張係数を有する封止樹脂 50 及び被覆樹脂 90 によって、上基板 40 を上下から挟むことができる。このため、半導体素子 30 と封止樹脂 50 との熱膨張係数の差に起因して生じる上基板 40 の歪みを緩和することができる。これにより、上基板 40 の上面に形成された配線層 60 にクラックが発生することを抑制できる。

#### 【0084】

また、封止樹脂 50 と被覆樹脂 90 とを別部材で構成したため、封止樹脂 50 及び被覆樹脂 90 の材料選択の自由度を向上させることができる。また、封止樹脂 50 と被覆樹脂 90 とを別部材で構成したため、封止樹脂 50 及び被覆樹脂 90 それぞれの形状の自由度を向上させることができる。

#### 【0085】

・図 13 に示した変更例では、被覆樹脂 90 の上面を配線層 60 の上面と面一になるように形成したが、配線層 60 の上面を被覆するように被覆樹脂 90 を形成してもよい。この場合には、例えば、被覆樹脂 90 に、配線層 60 の上面の一部を外部接続用パッドとして露出する開口部が形成される。

#### 【0086】

また、被覆樹脂 90 の上面を、配線層 60 の上面よりも低い位置に設けるようにしてもよい。この場合の被覆樹脂 90 は、半導体装置 10 の積層方向（図中上下方向）において、配線層 60 の側面の一部を被覆するように形成される。すなわち、被覆樹脂 90 は、半導体装置 10 の積層方向において、配線層 60 の上部における側面を露出するように形成される。この構成であっても、上記実施形態の（1）、（2）の作用効果を得ることができる。

#### 【0087】

・図 13 に示すように、半導体素子 30 を封止する封止樹脂 50 とは別に、下基板 20 の下面を被覆する絶縁樹脂 91 を設けるようにしてもよい。すなわち、半導体素子 30 を封止する封止樹脂 50 と、下基板 20 の下面を被覆する絶縁樹脂 91 とを別部材で構成するようにしてもよい。このとき、絶縁樹脂 91 は、例えば、封止樹脂 50 と同程度の熱膨

10

20

30

40

50

張係数を有している。絶縁樹脂91の熱膨張係数は、例えば、5 ppm / ~ 28 ppm / 程度とすることができる。絶縁樹脂91の材料としては、例えば、被覆樹脂90と同様の材料を用いることができる。絶縁樹脂91は、例えば、樹脂モールド成形法やポッティング法により形成することができる。

#### 【0088】

絶縁樹脂91は、例えば、金属層26の側面を被覆するように形成されている。絶縁樹脂91は、例えば、金属層26の側面全面を被覆している。絶縁樹脂91は、例えば、金属層26の下面を露出するように形成されている。絶縁樹脂91の下面は、例えば、金属層26の下面と面一になるように形成されている。絶縁樹脂91は、例えば、金属層26から露出する下基板20の下面全面を被覆するように形成されている。

10

#### 【0089】

・図13に示した変更例において、金属層26の下面を覆うように絶縁樹脂91を形成するようにしてもよい。

・上記実施形態において、金属層26の下面を覆うように封止樹脂50を形成するようにしてもよい。

#### 【0090】

・図13に示した変更例では、半導体素子30を封止する封止樹脂50と、配線層60の側面を被覆する被覆樹脂90と、下基板20の下面を被覆する絶縁樹脂91とをそれぞれ別部材で構成するようにしたが、これに限定されない。例えば、封止樹脂50と被覆樹脂90と絶縁樹脂91とのうち封止樹脂50と被覆樹脂90とを一体に形成してもよい。また、例えば、封止樹脂50と被覆樹脂90と絶縁樹脂91とのうち封止樹脂50と絶縁樹脂91とを一体に形成してもよい。

20

#### 【0091】

・上記実施形態では、下基板20の側面を被覆するように封止樹脂50を形成したが、これに限定されない。例えば図13に示すように、下基板20の側面を露出するように封止樹脂50を形成してもよい。この場合の封止樹脂50の側面は、例えば、下基板20の側面と面一になるように形成されている。なお、図13に示した変更例では、下基板20の下面を被覆する絶縁樹脂91の側面が下基板20の側面と面一になるように形成されている。

#### 【0092】

・図13に示した変更例において、下基板20の側面を被覆するように絶縁樹脂91を形成してもよい。

30

・上記実施形態では、上基板40の側面を被覆するように封止樹脂50を形成するようにしたが、これに限定されない。例えば図13に示すように、上基板40の側面を露出するように封止樹脂50を形成してもよい。この場合の封止樹脂50の側面は、例えば、上基板40の側面と面一になるように形成されている。なお、図13に示した変更例では、上基板40の上面に形成される被覆樹脂90の側面が上基板40の側面と面一になるように形成されている。

#### 【0093】

・図13に示した変更例において、上基板40の側面を被覆するように被覆樹脂90を形成してもよい。

40

・図13に示した変更例では、被覆樹脂90を、配線層60から露出する上基板40の上面全面を被覆するように形成したが、これに限定されない。

#### 【0094】

例えば図14に示すように、被覆樹脂90を、配線層60から露出する上基板40の上面の一部のみを被覆するように形成してもよい。この場合であっても、被覆樹脂90は、配線層60の側面に接触して配線層60の側面を被覆するように形成されている。

#### 【0095】

例えば図15に示すように、配線パターン61, 62の外周に沿って配線パターン61, 62を囲むように被覆樹脂90を形成するようにしてもよい。被覆樹脂90は、上基板

50

40の上面の一部を露出するように形成されている。

【0096】

このような構成であっても、上記実施形態の(1)、(2)の作用効果を得ることができる。また、被覆樹脂90の樹脂量を減らすことができるため、半導体装置10の製造コストを低減することができる。

【0097】

・図16に示すように、金属層26を省略してもよい。

・図16に示すように、絶縁樹脂91を省略してもよい。また、上記実施形態の封止樹脂50を、下基板20の側面及び下面を露出するように形成してもよい。

【0098】

・図17に示すように、下基板20を、金属板27で構成するようにしてもよい。この場合には、例えば、金属板27の上面に半導体素子30が実装される。金属板27の材料としては、例えば、銅や銅合金を用いることができる。なお、必要に応じて、金属板27の表面に表面処理層を形成するようにしてもよい。表面処理層としては、Au層、Ni層/Au層、Ni層/Pd層/Au層などの金属層を挙げることができる。金属板27の熱膨張係数は、例えば、15 ppm/ ~ 18 ppm/ 程度とすることができる。

【0099】

この構成によれば、下基板20を金属板27で構成したため、半導体装置10全体の放熱性を向上させることができる。

・図17に示した金属板27を配線や電極として利用してもよい。すなわち、下基板20を、配線や電極で構成してもよい。

【0100】

例えば図18及び図19に示すように、下基板20を、配線層28で構成するようにしてもよい。この構成によれば、セラミックス基板からなる下基板20上に配線層を形成する場合に比べて、配線層28自体が下基板20となるため、セラミックス基板等を省略できる。このため、半導体装置10全体を薄型化できる。

【0101】

図19に示すように、配線層28は、例えば、配線パターン22, 23, 24を有している。配線パターン22, 23, 24は、例えば、同一平面上において互いに離れて設けられている。配線パターン22, 23, 24の熱膨張係数は、例えば、15 ppm/ ~ 18 ppm/ 程度とすることができます。本変更例では、配線層28の外側面は、封止樹脂50から露出されるように形成されている。配線パターン22, 23, 24の外側面は、封止樹脂50の外側面と面一になるように形成されている。すなわち、本変更例の配線パターン22, 23, 24は、封止樹脂50よりも外側に引き出されるように形成されていない。これにより、半導体装置10全体の平面形状を小型化することができる。

【0102】

図18に示すように、本変更例の配線層28の下面は、封止樹脂50から露出されるように形成されている。配線層28の下面は、封止樹脂50の下面と面一になるように形成されている。これにより、配線層28の側面及び下面が封止樹脂50から露出されるため、半導体装置10全体の放熱性を向上させることができる。

【0103】

・図18に示した変更例において、配線層28の外側面を覆うように封止樹脂50を形成してもよい。

・図18に示した変更例において、配線パターン22, 23, 24を、封止樹脂50よりも外側に引き出すように形成してもよい。

【0104】

・図18に示した変更例において、配線層28の下面を覆うように封止樹脂50を形成してもよい。また、配線層28の下面を覆うソルダーレジスト層を形成してもよい。この場合には、配線層28の下面の一部を電極パッドとして露出する開口部を封止樹脂50又はソルダーレジスト層に設けるようにしてもよい。

10

20

30

40

50

## 【0105】

・上記実施形態では、下基板20の上面に、2つの半導体素子30を実装するようにしたが、半導体素子30の個数は特に限定されない。例えば、下基板20の上面に1つの半導体素子30を実装するようにしてもよい。また、下基板20の上面に3つ以上の半導体素子30を実装するようにしてもよい。

## 【0106】

・上記実施形態では、上基板40の基板本体41を単層構造に具体化したが、これに限定されない。例えば、基板本体41を、1層又は複数層の配線層と複数層の絶縁層とを積層した積層構造に具体化してもよい。

## 【0107】

・上記実施形態では、半導体装置10をパワー系の半導体装置に具体化したが、これに限定されない。例えば、半導体装置10をパワー系以外の各種の半導体装置に具体化してもよい。例えば、半導体装置10としては、下基板20と上基板40との間に設けられた半導体素子30を封止する封止樹脂50と、上基板40の上面に形成された配線層60とを有していれば、その他の構造や機能等は特に限定されない。

## 【0108】

・上記実施形態では、半導体素子30をパワー系の半導体素子に具体化したが、これに限定されない。例えば、半導体素子30をパワー系以外の各種の半導体素子に具体化してもよい。

## 【0109】

・上記実施形態では、3つの電極パッド31, 32, 33を有する半導体素子30に具体化したが、電極パッド31, 32, 33の数は特に限定されない。例えば、2つの電極パッドを有する半導体素子に具体化してもよい。この場合に、2つの電極パッドが半導体素子の上面のみに設けられる場合には、配線パターン22を省略することができる。この場合には、例えば、下基板20の上面に、接合部71を介して半導体素子30が実装される。

## 【符号の説明】

## 【0110】

10 半導体装置

20 下基板

26 金属層

30 半導体素子

40 上基板

50 封止樹脂

50X 開口部

60 配線層

81 外部接続端子

90 被覆樹脂

10

20

30

40

50

【図面】

【図 1】

【 図 2 】

【 図 3 】

【図4】

【図5】

【図6】

10

20

【図7】

【図8】

30

40

50

【 囮 9 】

【図10】

### 【図 1 1】

【図12】

【図13】

【図14】

【図15】

【図16】

10

20

30

40

50

【図17】

【図18】

10

【図19】

20

30

40

50

---

フロントページの続き

気工業株式会社内

(72)発明者 大井 淳

長野県長野市小島田町 80 番地 新光電気工業株式会社内

審査官 河合 俊英

(56)参考文献 米国特許出願公開第 2017 / 0064808 ( U.S. , A1 )

特開 2019 - 083234 ( JP , A )

特開 2018 - 181959 ( JP , A )

特開 2010 - 103231 ( JP , A )

特開 2012 - 191010 ( JP , A )

(58)調査した分野 (Int.Cl. , DB名)

H01L 23 / 29