US008008745B2

# (12) United States Patent Bertin et al.

## (54) LATCH CIRCUITS AND OPERATION CIRCUITS HAVING SCALABLE NONVOLATILE NANOTUBE SWITCHES AS ELECTRONIC FUSE REPLACEMENT ELEMENTS

(75) Inventors: Claude L. Bertin, Venice, FL (US);

Thomas Rueckes, Rockport, MA (US); Jonathan W. Ward, Fairfax, VA (US); Frank Guo, Danville, CA (US); Steven L. Konsek, Boston, MA (US); Mitchell Meinhold, Arlington, MA (US)

(73) Assignee: Nantero, Inc., Woburn, MA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 618 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 11/835,583(22) Filed: Aug. 8, 2007

(65) Prior Publication Data

US 2008/0159042 A1 Jul. 3, 2008

#### Related U.S. Application Data

- (63) Continuation-in-part of application No. 11/280,786, filed on Nov. 15, 2005, now Pat. No. 7,781,862, and a continuation-in-part of application No. 11/280,599, filed on Nov. 15, 2005, now Pat. No. 7,394,687, and a continuation-in-part of application No. 11/274,967, filed on Nov. 15, 2005, now Pat. No. 7,479,654.

- (60) Provisional application No. 60/679,029, filed on May 9, 2005, provisional application No. 60/692,765, filed on Jun. 22, 2005, provisional application No. 60/692,918, filed on Jun. 22, 2005, provisional application No. 60/692,891, filed on Jun. 22, 2005, provisional application No. 60/836,437, filed on Aug. 8, 2006, provisional application No. 60/836,343, filed on Aug. 8, 2006, provisional application No. 60/840,586, filed on Aug. 28, 2006, provisional application No. 60/855,109, filed on Oct. 27, 2006, provisional application No. 60/918,388, filed on Mar. 16, 2007.

# (10) Patent No.:

US 8,008,745 B2

(45) **Date of Patent:**

\*Aug. 30, 2011

(51) Int. Cl. *H01L 23/52* (2006.01)

(56) References Cited

U.S. PATENT DOCUMENTS

3,922,648 A 11/1975 Buckley (Continued)

FOREIGN PATENT DOCUMENTS

GB 2 364 933 A 2/2002 (Continued)

OTHER PUBLICATIONS

Cui, J.B., et al. "Carbon Nanotube Memory Devices of High Charge Storage Stability." Appl. Phys. Lett., vol. 81, No. 17 (Oct. 21, 2002): pp. 3260-3262.\*

(Continued)

Primary Examiner — Matthew W Such

(74) Attorney, Agent, or Firm — Wilmer Cutler Pickering

Hale and Dorr LLP

(57) ABSTRACT

A non-volatile latch circuit is provided. The non-volatile latch circuit includes a nanotube switching element capable of switching between resistance states and non-volatilely retaining the resistance state. The non-volatile latch circuit includes a volatile latch circuit is capable of receiving and volatilely storing a logic state. When the nanotube switching element is a resistance state, the volatile latch circuit retains a corresponding logic state and outputs that corresponding logic state at an output terminal. A non-volatile register file configuration circuit for use with a plurality of non-volatile register files is also provided. The non-volatile register file configuration circuit includes a selection circuitry and a plurality of nanotube fuse elements, each in electrical communication with one of a plurality of non-volatile register files. The selection circuitry is capable of applying electrical stimulus to each of the selected nanotube fuse elements to selectively bypass the corresponding register file.

## 22 Claims, 45 Drawing Sheets

| U.S. PATENT DOCUMENTS                                                              |               | WO                                                                                                                                 | WO-2006/122111                                                      | 11/2006                                                                              |  |

|------------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| 5,005,158 A 4/1991 McClure et al.                                                  |               | WO<br>WO                                                                                                                           | WO-2007/001642                                                      | 1/2007<br>2/2008                                                                     |  |

| 5,345,110 A 9/1994 Renfro et al.                                                   |               | WO                                                                                                                                 | WO-2008/021912                                                      |                                                                                      |  |

| 5,416,737 A 5/1995 Lingstaedt et al.<br>5,491,655 A 2/1996 Hirose et al.           |               |                                                                                                                                    | OTHER P                                                             | UBLICATIONS                                                                          |  |

| 5,768,196 A 6/1998 Bloker et al.                                                   | Bloker et al. |                                                                                                                                    | Avouris, "Carbon nanotube electronics", Chemical Physics, vol. 281, |                                                                                      |  |

| 5,912,937 A 6/1999 Goetting et al.                                                 |               |                                                                                                                                    | pp. 429-445, 2002.                                                  |                                                                                      |  |

| 5,956,282 A 9/1999 Casper<br>6,008,523 A 12/1999 Narayan et al.                    |               |                                                                                                                                    | Bachtold, A. et al., "Logic Circuits with Carbon Nanotube Transis-  |                                                                                      |  |

| 6,128,214 A 10/2000 Kuekes et al.                                                  |               |                                                                                                                                    |                                                                     | ol. 294, pp. 1317-1320.                                                              |  |

| 6,256,767 B1 7/2001 Kuekes et al.                                                  |               |                                                                                                                                    | •                                                                   | rbon nanotube transistors with charge                                                |  |

| 6,259,644 B1 7/2001 Tran et al.<br>6,314,019 B1 11/2001 Kuekes et al.              |               |                                                                                                                                    | doping", Applied Phy -3, 2005.                                      | esics Letters, vol. 86, pp. 123108-1-                                                |  |

| 6,385,075 B1 5/2002 Taussig et al.                                                 |               |                                                                                                                                    |                                                                     | Carbon Nanotube Transistors with                                                     |  |

| 6,422,450 B1 7/2002 Zhou et al.                                                    |               |                                                                                                                                    |                                                                     | <i>M</i> , pp. 29.4.1-29.4.4, 2004.                                                  |  |

| 6,423,583 B1 7/2002 Avouris et al.<br>6,445,006 B1 9/2002 Brandes et al.           |               |                                                                                                                                    |                                                                     | ing Carbon Nanotubes and Nanotube                                                    |  |

| 6,493,272 B1 12/2002 Fujii et al.                                                  |               |                                                                                                                                    | -                                                                   | kdown", Science, vol. 292, pp. 706-                                                  |  |

| 6,528,020 B1 3/2003 Dai et al.<br>6,548,841 B2 4/2003 Frazier et al.               |               |                                                                                                                                    | r. 27, 2001.                                                        | 4                                                                                    |  |

| 6,570,802 B2 5/2003 Ohtsuka et al.                                                 |               |                                                                                                                                    |                                                                     | doping and carrier injection in carbon <i>Physics Letters</i> , vol. 80, No. 15, pp. |  |

| 6,570,806 B2 5/2003 Bertin et al.                                                  |               |                                                                                                                                    | 775, Apr. 15, 2002.                                                 | 1 nystes Letters, vol. 60, 110. 15, pp.                                              |  |

| 6,624,499 B2 9/2003 Kothandaraman et al. 6,707,098 B2 3/2004 Hofmann et al.        |               | Derycke                                                                                                                            | e, V., et al., "Carbon                                              | Nanotube Inter- and Intramolecular                                                   |  |

| 6,750,802 B1 6/2004 Olen                                                           |               |                                                                                                                                    |                                                                     | ep. 2001, vol. 1, No. 9, pp. 453-456.                                                |  |

| 6,759,693 B2 7/2004 Vogeli et al.                                                  |               |                                                                                                                                    | · · · · · · · · · · · · · · · · · · ·                               | emory and Programmable Logic from <i>Nano Letters</i> , vol. 0, No. 0, pp. A-D,      |  |

| 6,803,840 B2 10/2004 Hunt et al.<br>6,808,746 B1 10/2004 Dai et al.                |               | 2002.                                                                                                                              | ic-Gated Nanownes , 1                                               | vano Letters, vol. 0, No. 0, pp. A-D,                                                |  |

| 6,809,465 B2 10/2004 Jin                                                           |               | Heinze,                                                                                                                            | S. et al., "Carbon Nan                                              | notubes as Schottky Barrier Transist-                                                |  |

| 6,831,856 B2 12/2004 Pashmakov                                                     |               |                                                                                                                                    |                                                                     | vol. 89, No. 10, pp. 16801-1-106801-                                                 |  |

| 6,888,773 B2 5/2005 Morimoto                                                       |               | 4, 2002                                                                                                                            |                                                                     | nal Properties of Carbon Nanotubes",                                                 |  |

| 6,890,780 B2 5/2005 Lee<br>6,899,945 B2 5/2005 Smalley et al.                      |               |                                                                                                                                    |                                                                     | ol. Phys., vol. 80, pp. 273-286, 2001.                                               |  |

| 6,905,892 B2 6/2005 Esmark et al.                                                  |               |                                                                                                                                    |                                                                     | s and Computation from Assembled                                                     |  |

| 6,918,284 B2 * 7/2005 Snow et al                                                   | 73/31.05      |                                                                                                                                    | -                                                                   | Science, Nov. 9, 2001, vol. 294, pp.                                                 |  |

| 6,919,592 B2 7/2005 Segal et al.                                                   |               | 1313-13                                                                                                                            |                                                                     | estable Eigld Effect Translators with                                                |  |

| 6,919,740 B2 7/2005 Snider<br>6,921,575 B2 7/2005 Horiuchi et al.                  |               |                                                                                                                                    |                                                                     | notube Field-Effect Transistors with I High-k Gate Dielectrics", Nano Let-           |  |

| 6,990,009 B2 1/2006 Bertin et al.                                                  |               | _                                                                                                                                  | l. 4, No. 3, pp. 447-450                                            | _                                                                                    |  |

| 7,015,500 B2 3/2006 Choi et al.                                                    |               |                                                                                                                                    |                                                                     | ctrics for advanced carbon-nanotube                                                  |  |

| 7,115,901 B2 10/2006 Bertin et al.                                                 |               |                                                                                                                                    |                                                                     | ature Materials, vol. 1, pp. 241-246,                                                |  |

| 7,115,960 B2 10/2006 Bertin<br>7,161,403 B2 1/2007 Bertin                          |               | Dec. 20<br>Javey A                                                                                                                 |                                                                     | tube Transistor Arrays for Multistage                                                |  |

| 7,781,862 B2 * 8/2010 Bertin et al                                                 | 257/529       |                                                                                                                                    |                                                                     | ng Oscillators," Nano Letters, 2002,                                                 |  |

| 2001/0010656 A1* 8/2001 Mattison                                                   | 365/240       | vol. 2,                                                                                                                            | No. 9, pp. 929-932.                                                 |                                                                                      |  |

| 2001/0023986 A1 9/2001 Mancevski<br>2002/0027819 A1* 3/2002 Tomanek et al          | 365/215       |                                                                                                                                    |                                                                     | ellow unrolls blueprint for nano",                                                   |  |

| 2002/0175390 A1 11/2002 Goldstein et al.                                           | 303/213       |                                                                                                                                    | s, Mar. 6, 2006, .<br>ticle.jhtml?articleID=1                       | 3 pages, http://www.eetimes.com/<br>81500304                                         |  |

| 2003/0200521 A1 10/2003 DeHon et al.                                               |               |                                                                                                                                    | ,                                                                   | ference and Ballistic Transmission in                                                |  |

| 2004/0022085 A1 2/2004 Parkinson et al.                                            |               | Nanotul                                                                                                                            | oe Electron Waveguide                                               | es", The American Physical Society,                                                  |  |

| 2004/0031975 A1 2/2004 Kern et al.<br>2004/0066669 A1* 4/2004 Ooishi               | 365/173       |                                                                                                                                    |                                                                     | 106801-4, Sep. 3, 2001.                                                              |  |

| 2004/0132070 A1 7/2004 Star et al.                                                 | 505,175       |                                                                                                                                    | 1. et al., "Novel Carbon", <i>IEDM</i> , pp. 29.2.1 <b>-</b> 29     | Nanotube FET Design with Tunable                                                     |  |

| 2004/0266106 A1 12/2004 Lee                                                        |               |                                                                                                                                    |                                                                     | anotube Field-Effect Transistors and                                                 |  |

| 2005/0056877 A1 3/2005 Rueckes et al.<br>2005/0212014 A1 9/2005 Horibe et al.      |               |                                                                                                                                    |                                                                     | n. 10-12, 2002, vol. 7.4, pp. 94-98.                                                 |  |

| 2006/0044878 A1 3/2006 Perner                                                      |               |                                                                                                                                    |                                                                     | duction of singly dispersed carbon                                                   |  |

| 2006/0128071 A1* 6/2006 Rankin et al                                               |               |                                                                                                                                    | es with prescribed len<br>303, 2005.                                | ngths," Nanotechnology, vol. 16, pp.                                                 |  |

| 2006/0215439 A1* 9/2006 Bill et al                                                 | 365/148       |                                                                                                                                    |                                                                     | volatile Molecular Memory Elements                                                   |  |

| 2006/0237537 A1 10/2006 Empedocles et al.<br>2006/0250843 A1 11/2006 Bertin et al. |               |                                                                                                                                    |                                                                     | e Field Effect Transistors", Nano Let-                                               |  |

| 2006/0250856 A1 11/2006 Bertin et al.                                              |               |                                                                                                                                    | l. 2, No. 7, pp. 761-764                                            |                                                                                      |  |

| 2006/0258122 A1 11/2006 Whitefield et al.                                          |               |                                                                                                                                    |                                                                     | antotube-Based Nonvolatile Random r Computing," <i>Science</i> , Jul. 7, 2000,       |  |

| 2006/0264053 A1 11/2006 Yates                                                      |               |                                                                                                                                    | pp. 94-97.                                                          | Computing, Science, Jul. 7, 2000,                                                    |  |

| 2006/0281256 A1 12/2006 Carter et al.<br>2006/0281287 A1 12/2006 Yates et al.      |               |                                                                                                                                    |                                                                     | and Electrical Characterization of Top                                               |  |

| 2006/0292716 A1 12/2006 Gu et al.                                                  |               |                                                                                                                                    | •                                                                   | otube Field-Effect Transistors", Nov.                                                |  |

| 2008/0012047 A1 1/2008 Bertin                                                      |               | 2002, 1-                                                                                                                           |                                                                     | aling of outbon paratiles 6-14 sec-4                                                 |  |

| 2008/0142850 A1 6/2008 Bertin<br>2008/0157126 A1 7/2008 Bertin                     |               |                                                                                                                                    |                                                                     | aling of carbon nanotube field-effect rodes", <i>Applied Physics Letters</i> , vol.  |  |

| 2008/0157126 A1 //2008 Bertin<br>2008/0159042 A1 7/2008 Bertin                     |               |                                                                                                                                    | 20, pp. 3817-3819, Ma                                               |                                                                                      |  |

|                                                                                    |               | Langer,                                                                                                                            | Langer, L., et al., "Electrical Resistance of a Carbon Nanotube     |                                                                                      |  |

| FOREIGN PATENT DOCUMENTS                                                           |               | Bundle," J. Mater. Res., vol. 9, No. 4, Apr. 1994, 6 pages.<br>Pradhan, B. et al., "Electrial Bistability and Memory Phenomenon in |                                                                     |                                                                                      |  |

| WO WO-00/48195 8/2000<br>WO WO-01/03208 A1 1/2001                                  |               |                                                                                                                                    |                                                                     | Polymer Matrixes," J. Phys. Chem.                                                    |  |

| WO WO-2005/041204 5/2005                                                           |               |                                                                                                                                    | 5, 110, 8274-8277.                                                  | ,, <i>1 My 0.</i> 2 Marin                                                            |  |

|                                                                                    |               |                                                                                                                                    |                                                                     |                                                                                      |  |

Supplementary European Search Report for corresponding European Patent Application No. EP 07840800 mailed Jul. 1, 2009.

European Search Report for corresponding European Patent Application No. EP 09159276 mailed Jul. 17, 2009.

European Search Report for corresponding European Patent Application No. EP 09159271 mailed Jul. 3, 2009.

Fuhrer, M.S. et al., "High-Mobility Nanotube Transistor Memory," Nano Letters, 2002, vol. 2, No. 7, pp. 755-759.

Novak, J.P. et al., "Nerve agent detection using networks of single-walled carbon nanotubes," Applied Physics Letters, vol. 83, No. 19, Nov. 10, 2003, pp. 4026-4028.

Snow, E.S. et al., "Random networks of carbon nanotubes as an electronic material," Applied Physics Letters, vol. 82, No. 13, Mar. 31, 2003, pp. 2145-2147.

Star, A. et al., "Nanoelectronic Carbon Dioxide Sensors," Adv. Mater. 2004, 16, No. 22, Nov. 18, pp. 2049-2052.

Star, A. et al., "Nanotube Optoelectronic Memory Devices," Nano Letters, 2004, vol. 4, No. 9, pp. 1587-1591.

Zhou, Y. et al., "p-Channel, n-Channel Thin Film Transistors and p-n Diodes Based on Single Wall Carbon Nanotube Networks," Nano Letters, 2004, vol. 4, No. 10, pp. 2031-2035.

Awano, Y., "Graphene for VLSI: FET and Interconnect Applications" IEDM 2009 Technical Digest, pp. 10.1.1-10.1.4.

Brown, K.M. "System in package "The Rebirth of SIP"," 2004 IEEE Custom Integrated Circuits Conference, May 2004.

Crowley, M. et al., "512 Mb PROM with 8 layers of antifuse/Diode cells," IEEE International Solid-State Circuits Conference, vol. XLVI, pp. 284-285, Feb. 2003.

Huai, Y. "Spin-Transfet Torque MRAM (STT-MTAM): Challenges and Prospects". AAPS Bulletin Dec. 2008, vol. 18, No. 6, pp. 33-40. Jiang, Y. et al., "Performance Breakthrough in 8nm Gate-All-Around Length Gate-All-Around Nanowire Transistors using Metallic Nanowire Contacts" 2008 Symposium on VLSI Technology Digest of Technical Papers, pp. 34-35.

Kianian, S. et al., "A 3D Stackable Carbon Nanotube-based Nonvolatile Memory (NRAM)," ESSDERC, Jun. 14, 2010, Nantero, Inc. Servalli, G. "A 45nm Generation Phase Change Memory Technology," IEDM 2009 Technical Digest, pp. 5.7.1-5.7.4.

Baker, R.J., CMOS: Circuit Design, Layout, and Silulation, IEEE Press, Series in Microelectronic Systems, 1998, pp. 226, 2 pages.

Baker, R.J., CMOS: Circuit Design, Layout, and Silulation, IEEE Press, Series in Microelectronic Systems, 1998, pp. 427-433, 8 pages.

Baker, R.J., CMOS: Circuit Design, Layout, and Silulation, IEEE Press, Series in Microelectronic Systems, 1998, pp. 579-595, 18 pages.

Baker, R.J., CMOS: Circuit Design, Layout, and Silulation, IEEE Press, Series in Microelectronic Systems, 1998, pp. 579-591, 14 pages.

Baker, R.J., CMOS: Circuit Design, Layout, and Silulation, IEEE Press, Series in Microelectronic Systems, 1998, pp. 607-608, 3 pages.

Bakoglu, H.B., "Circuits, Interconnections, and Packaging for VLSI," Addison-Wesley Publishing Company, Inc., 1990, pp. 152, 2 pages.

Bakoglu, H.B., "Circuits, Interconnections, and Packaging for VLSI," Addison-Wesley Publishing Company, Inc., 1990, pp. 338-349, 13 pages.

Bakoglu, H.B., "Circuits, Interconnections, and Packaging for VLSI," Addison-Wesley Publishing Company, Inc., 1990, pp. 171-178, 9 pages.

Itoh, K., "VLSI Memory Chip Design," Springer Series in Advanced Microelectronics, Springer-Verlag Berlin Heidelberg 2001, pp. 178-183, 7 pages.

Itoh, K., "VLSI Memory Chip Design," Springer Series in Advanced Microelectronics, Springer-Verlag Berlin Heidelberg 2001, pp. 358-3637 pages.

Itoh, K., "VLSI Memory Chip Design," Springer Series in Advanced Microelectronics, Springer-Verlag Berlin Heidelberg 2001, pp. 41-44, 5 pages.

International Search Report and Written Opinion of the International Searching Authority, The United States Patent and Trademark Office, for International Application No. PCT/US2007/075521, dated Apr. 1, 2008, 8 pages.

\* cited by examiner

FIGURE 3B

FIGURE 3A

C = C C B

URZ OFF ON

OPF OPF

FIGURE 3C

30 S TR1 /INV2

⋖

മ

Cycling Yield (%)

**FIGURE 10C**

FIGURE 11

FIG. 13A

Figure 14A

|      | Median I <sub>READ</sub> | Median                |

|------|--------------------------|-----------------------|

| VWL0 | @ 1 Volt                 | Corresponding         |

| (V)  | (uA)                     | I <sub>SAT</sub> (uA) |

| 0.9  | 0.52                     | 3.48                  |

| 96.0 | 9.0                      | 4.02                  |

| 1.02 | 0.7                      | 4.69                  |

| 1.08 | 0.8                      | 5.36                  |

| 1.16 | 0.9                      | 6.03                  |

| 1.22 | 1.0                      | 6.7                   |

| 1.28 | 1.1                      | 7.37                  |

| 1.4  | 1.2                      | 8.04                  |

Figure 23B

Figure 28B

## LATCH CIRCUITS AND OPERATION CIRCUITS HAVING SCALABLE NONVOLATILE NANOTUBE SWITCHES AS ELECTRONIC FUSE REPLACEMENT ELEMENTS

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the benefit under 35 U.S.C. §119(e) of the following applications, the entire contents of which are incorporated herein by reference:

U.S. Provisional Patent Application No. 60/836,343, entitled "Scalable Nonvolatile Nanotube Switches as Electronic Fuse Replacement Elements," filed on Aug. 8, 2006;

U.S. Provisional Patent Application No. 60/836,437 entitled "Nonvolatile Nanotube Diode," filed on Aug. 8, 2006;

U.S. Provisional Patent Application No. 60/840,586 entitled "Nonvolatile Nanotube Diode," filed on Aug. 28, 20 2006:

U.S. Provisional Patent Application No. 60/855,109 entitled "Nonvolatile Nanotube Cubes," filed on Oct. 27, 2006; and

U.S. Provisional Patent Application No. 60/918,388, 25 entitled "Memory Elements and Cross Point Switches and Arrays of Same Using Nonvolatile Nanotube Blocks," filed on Mar. 16, 2007.

This application is a continuation-in-part of and claims priority under 35 U.S.C. §120 to the following applications, 30 the entire contents of which are incorporated by reference:

U.S. patent application Ser. No. 11/280,786, entitled "Two-Terminal Nanotube Devices And Systems And Methods Of Making Same," filed Nov. 15, 2005;

U.S. patent application Ser. No. 11/274,967, entitled 35 "Memory Arrays Using Nanotube Articles With Reprogrammable Resistance," filed Nov. 15, 2005; and

U.S. patent application Ser. No. 11/280,599, entitled "Non-Volatile Shadow Latch Using A Nanotube Switch," filed Nov. 15, 2005.

This application is related to the following applications, the entire contents of which are incorporated by reference:

U.S. patent application Ser. No. 11/835,612, entitled "Non-volatile Resistive Memories Having Scalable Two-terminal Nanotube Switches," filed concurrently herewith;

U.S. patent application Ser. No. 11/835,613, entitled "Memory Elements and Cross Point Switches and Arrays of Same Using Nonvolatile Nanotube Blocks," filed concurrently herewith;

U.S. patent application Ser. No. 11/835,651, entitled "Non-50 volatile Nanotube Diodes and Nonvolatile Nanotube Blocks and Systems Using Same and Methods of Making Same," filed concurrently herewith;

U.S. patent application Ser. No. 11/835,759, entitled "Non-volatile Nanotube Diodes and Nonvolatile Nanotube Blocks 55 and Systems Using Same and Methods of Making Same," filed concurrently herewith;

U.S. patent application Ser. No. 11/835,845, entitled "Non-volatile Nanotube Diodes and Nonvolatile Nanotube Blocks and Systems Using Same and Methods of Making Same," 60 filed concurrently herewith;

U.S. patent application Ser. No. 11/835,852, entitled "Non-volatile Nanotube Diodes and Nonvolatile Nanotube Blocks and Systems Using Same and Methods of Making Same," filed concurrently herewith;

U.S. patent application Ser. No. 11/835,856, entitled "Non-volatile Nanotube Diodes and Nonvolatile Nanotube Blocks

2

and Systems Using Same and Methods of Making Same," filed concurrently herewith; and

U.S. patent application Ser. No. 11/835,865, entitled "Non-volatile Nanotube Diodes and Nonvolatile Nanotube Blocks and Systems Using Same and Methods of Making Same," filed concurrently herewith.

#### BACKGROUND

#### Technical Field

The present application is generally related to the field of nanotube switching elements.

Scalable Nonvolatile Latch Circuits

The semiconductor industry uses fuses or antifuses for nonvolatile storage of a logic state. The nonvolatile resistive state of a fuse (or antifuse) in a conducting state or nonconducting state is used to indicate a first or second logical state. The latch circuit converts the fuse (or antifuse) nonvolatile resistive state into a corresponding electrical voltage level indicative of a logical 1 or 0.

In one type of fuse, sometimes referred to as a laser fuse, a fuse element is formed of metallic or polysilicon material. The fuse is programmed (blown, or made nonconducting) by laser ablation and a corresponding latch circuit reads the nonvolatile state of the fuse as described, for example, in U.S. Pat. No. 5,345,110, the entire contents of which are incorporated herein by reference.

The semiconductor industry has been replacing laser fuses with more flexible and denser electrically programmable fuse (e-fuse) elements, however, e-fuses typically require programming currents in the milli-Ampere range and are difficult to scale to smaller physical dimensions and lower programming current levels for new denser technology nodes such as 90 nm, 65 nm, 45 nm, and denser.

The semiconductor industry has also replaced laser fuses with more flexible and denser electrically programmable antifuse (a-fuse) elements. Antifuses reduce programming currents to the low micro-Ampere range such as 1-10 uA, for example, however, programming voltages are typically in the 8 to 12 volt range. Antifuses are difficult to scale to smaller physical dimensions and lower programming voltage levels for new denser technology nodes. Latches using fuses and antifuses are illustrated in Bertin et al., U.S. Pat. No. 6,570, 806, the entire contents of which are incorporated herein by reference.

It would be desirable to provide a scalable element that may be used as a fuse, or as an antifuse, or as both fuse and antifuse, or an element able to toggle between fuse and antifuse multiple times, or more generally between ON and OFF states multiple times, and corresponding latch circuits that integrates easily with silicon technology, is scalable to smaller physical dimensions, programs using low current values in nano-Ampere or low micro-Ampere range, and is scalable to lower programming voltage of 5 volts and below.

In certain applications, it would be desirable to provide a scalable element that may be used to switch between ON and OFF states to select or deselect (bypass) register file stages in a series of register files. If such a scalable element is used as a fuse, a corresponding register file stage may be delected (bypassed) to eliminate a defective register file stage from a series.

In certain applications, it would also be desirable to provide a scalable element that may be used to switch between ON and OFF states to provide informational states in a memory cell. Further, in other applications, a scalable element that may be used to switch among multiple conductivity

states to provide multiple informational states in a memory cell may be desirable. Integrating such elements with existing memory technology would be further desirable. Existing commercially available technologies are generally either nonvolatile, but not randomly accessible and have a low density, high production cost and a limited ability to allow multiple writes with high reliability of the circuit's function; or are volatile, and have complicated system design or have a low density. An ideal non-volatile memory, for at least some purposes, is one that enables the nonvolatile storage of multiple informational states where memory cells can be selectively activated and accurately programmed to an informational state.

#### SUMMARY OF THE INVENTION

The present invention provides scalable latch circuits, non-volatile memories and operation circuits based on nanofabric materials and scalable nonvolatile nanotube switches.

According to one aspect of the invention, a non-volatile 20 latch circuit is provided. The non-volatile latch circuit includes an input terminal capable of inputting a logic state, an output terminal capable of outputting a logic state and a nanotube switching element having a nanotube fabric article disposed between and in electrical communication with two 25 conductive contacts. The nanotube switching element is capable of switching between a relatively low resistance state and a relatively high resistance state and is capable of nonvolatilely retaining the relatively low or the relatively high resistance state. The non-volatile latch circuit includes a volatile latch circuit having at least one semiconductive element electrically disposed between the input terminal and the nanotube switching element and is capable of receiving and volatilely storing a logic state inputted to the input terminal. When the nanotube switching element is in the relatively low 35 resistance state, the volatile latch circuit retains a first logic state and outputs the first logic state at the output terminal. When the nanotube switching element is in the relatively high resistance state, the volatile latch circuit retains a second logic state outputted at the output terminal.

In one embodiment of the invention, the electronic latch circuit includes an inverter circuit comprising a plurality of field effect transistors.

In another embodiment of the invention, the nanotube switching element is capable of switching between the relatively low resistance state and the relatively high resistance state multiple times.

In another embodiment of the invention, the electronic latch circuit converts the relatively low resistance state of the nanotube switching element to a relatively high voltage level 50 corresponding to the first logic state outputted at the output terminal. The electronic latch circuit converts the relatively high resistance state of the nanotube switching element to a relatively low voltage level corresponding to the second logic state outputted at the output terminal.

In another embodiment of the invention, the non-volatile latch circuit is in electrical communication with a memory cell. When the non-volatile latch circuit outputs the first logic state, the memory cell is active and when the non-volatile latch circuit outputs the second logic state, the memory cell is 60 inactive.

In another embodiment of the invention, the non-volatile latch circuit comprises a redundancy circuit for the memory cell and is capable of bypassing the memory cell when the memory cell is inoperable.

In another embodiment of the invention, the non-volatile latch circuit is in electrical communication with a memory 4

cell and is capable of storing first and second memory states. The first memory state is inputted to the input terminal as a first logic state and is non-volatilely retained and outputted by the non-volatile latch circuit as the first logic state. The second memory state is inputted to the input terminal as a second logic state and is non-volatilely retained and outputted by the non-volatile latch circuit as a second logic state.

In another embodiment of the invention, the non-volatile latch circuit comprises a redundancy circuit for the memory cell and is capable of non-volatilely retaining the first and the second logic state corresponding, respectively, to the first and the second memory state.

In another embodiment of the invention, the memory cell comprises a cell in an NRAM array.

In another embodiment of the invention, the non-volatile latch circuit retains one of the first and the second logic states to correct for an error in the memory cell.

In another embodiment of the invention, the non-volatile latch circuit is in electrical communication with a memory circuit. The electrical stimulus inputted at the input terminal includes a time-varying electrical stimulus. The electrical stimulus outputted at the output terminal includes a time-varying electrical stimulus. The non-volatile latch circuit controls operation of the memory circuit by creating a controllable delay between the time-varying electrical stimulus at the input terminal and at the output terminal.

In another embodiment of the invention, the non-volatile latch circuit creates a controllable delay that includes a substantially bi-modal signal with a substantially selected rise time and a substantially selected fall time.

In another embodiment of the invention, the nanotube switching element comprises a one-time programmable fuse capable of switching from only the relatively low resistance state to the relatively high resistance state.

According to another aspect of the invention, a non-volatile register file configuration circuit for use with a plurality of non-volatile register files is provided. The non-volatile register file configuration circuit includes an input voltage terminal, a selection circuitry and a plurality of nanotube fuse elements in electrical communication with the input voltage terminal. Each nanotube fuse element is in electrical communication with one of the plurality of non-volatile register files and with the selection circuitry. Each of the nanotube fuse elements includes a nanotube fabric article and two conductive contacts, the nanotube fabric article disposed between and in electrical communication with the two conductive contacts. The nanotube fuse element is capable of switching from an on state to an off state, the on state corresponding to a relatively low resistance between the first and second terminals and the off state corresponding to a relatively low resistance between the two conductive contacts in response to electrical stimulus. When the nanotube fuse element is in the on state, the corresponding non-volatile register file is active 55 and responsive to electrical stimulus at the input voltage terminal. When the nanotube fuse element is in the off state, the corresponding non-volatile register file is inactive and not responsive to electrical stimulus at the input voltage terminal. The selection circuitry is capable of applying electrical stimulus to each of the selected nanotube fuse elements to selectively bypass the corresponding register file.

In another embodiment of the invention, the selection circuit selectively bypasses one of the plurality of register files in response to the register file being defective.

In another embodiment of the invention, when one of the plurality of nanotube fuse elements is in the on state, the corresponding non-volatile register file is capable of operat-

ing with a plurality of informational states in response to electrical stimuli at the input voltage terminal.

In another embodiment of the invention, the nanotube fuse element is one-time programmable.

According to another aspect of the invention, a non-volatile memory includes a bit line, a word line, and at least one non-volatile memory cell. Each memory cell has a two-terminal nanotube switching device comprising first and second conductive terminals and a nanotube fabric article disposed between and in electrical communication with the first and second conductive terminals. Each memory cell also has a cell selection circuit in electrical communication with the bit line and the word line to select the two-terminal nanotube switching device for read and write operations in response to activation of at least one of the bit line and the word line. The non-volatile memory includes write control circuitry, responsive to a control signal, for supplying write signals to a selected memory cell to induce a change in the resistance of the nanotube fabric article so that the value of the resistance of 20 the nanotube fabric article corresponds to an informational state of the memory cell. The non-volatile memory includes resistance sensing circuitry in communication with a selected nonvolatile memory cell, for sensing the resistance of the nanotube fabric article and providing the control signal to the 25 write control circuitry. And, the non-volatile memory includes read circuitry in communication with a selected nonvolatile memory cell for reading the corresponding informational state of the memory cell.

In another embodiment of the invention, the first conductive terminal of the nanotube switching device is in electrical communication with the cell selection circuit and the second conductive terminal of the nanotube switching device is in electrical communication with a reference voltage line.

In another embodiment of the invention, the write control 35 circuitry is in electrical communication with the bit line and the word line.

In another embodiment of the invention, the first conductive terminal of the nanotube switching device receives the write signals supplied by the write control circuitry and the 40 second conductive terminal of the nanotube switching device is in electrical communication with at least one of the word line and the bit line.

In another embodiment of the invention, supplying write signals comprises supplying an electrical stimulus having a 45 selected voltage.

In another embodiment of the invention, supplying write signals comprises supplying an electrical stimulus having a selected current.

In another embodiment of the invention, the nanotube 50 switching element further comprises first and second insulator regions disposed on substantially opposite sides of the nanotube fabric article.

In another embodiment of the invention, at least one of the first and second insulator regions includes a dielectric mate- 55 rial

In another embodiment of the invention, at least a portion of the nanotube fabric article is separated from at least a portion of one of the first and second insulator regions by a gap.

In another embodiment of the invention, the informational state of the memory cell is capable of being programmed and erased multiple times.

In another embodiment of the invention, write control circuitry includes circuitry for writing at least three write signals, each of the at least three write signals being a signal capable of inducing a corresponding resistance value in the

6

nanotube fabric article that is different than the resistance values corresponding to the other write signals.

In another embodiment of the invention, the corresponding resistance values induced by the at least three write signals include multiple low resistance values and one high resistance value.

In another embodiment of the invention, the multiple low resistance values each are in the range of approximately one kilo-Ohm to approximately one mega-Ohm and wherein the high resistance value is at least one-hundred mega-Ohms.

In another embodiment of the invention, the write control circuitry includes circuitry for writing four write signals so that the memory cell is capable of storing one of a first informational state, a second informational state, a third informational state, and a fourth informational state.

In another embodiment of the invention, the resistance sensing circuitry comprises feedback circuitry in electrical communication with the selected non-volatile memory cell and with a reference resistance value, the feedback circuitry capable of comparing the resistance of the nanotube fabric article of the selected non-volatile memory cell to the reference resistance value and selectively blocking write signals to the selected non-volatile memory cell.

In another embodiment of the invention, the value of the resistance of the nanotube fabric article is selected from one of a relatively low resistance value and a relatively high resistance value.

In another embodiment of the invention, the relatively low resistance value corresponds to a first informational state and the relatively high resistance value corresponds to a second informational state.

In another embodiment of the invention, supplying write signals comprises supplying a plurality of sequential, incrementally varying voltage pulses at selected intervals.

In another embodiment of the invention, the feedback circuitry senses the resistance of the nanotube fabric article and compares the resistance of the nanotube fabric article to the reference resistance value after each voltage pulse is supplied by the write control circuitry.

In another embodiment of the invention, the non-volatile memory is capable of a first write operation in which the voltage pulses are applied until the feedback circuitry senses a relatively low resistance value as the resistance of the nanotube fabric article and selectively blocks write signals.

In another embodiment of the invention, the non-volatile memory is capable of a second write operation in which the voltage pulses are applied until the feedback circuitry senses a relatively high resistance value as the resistance of the nanotube fabric article and selectively blocks write signals.

In another embodiment of the invention, the nanotube switching element comprises a one-time programmable nanotube fuse, the nanotube fabric article capable of only switching from the relatively low resistance value to the relatively high resistance value.

In another embodiment of the invention, the write control circuitry selects the reference resistance value from a range of resistance values.

In another embodiment of the invention, the feedback circuitry selectively blocks write signals on the bit line to the 60 nanotube switching device of the selected nonvolatile memory cell when the resistance value of the nanotube switching article is approximately equal to the reference resistance value.

In another embodiment of the invention, the read circuitry includes a sense amplifier circuit and the resistance sensing circuitry is in electrical communication with the sense amplifier circuit and the resistance sensing circuitry is responsive to

the sense amplifier circuit to provide the control signal to the write control circuitry to selectively stop the write control circuitry from supplying write signals to the selected non-volatile memory cell.

In another embodiment of the invention, the control signal 5 provided by the sense amplifier circuitry to the resistance sensing circuitry selectively stops the write control circuitry from inducing a change in the resistance of the nanotube fabric article.

In another embodiment of the invention, the value of the resistance of the nanotube fabric article is selected from one of a plurality of resistance values including multiple low resistance values and a relatively high resistance value.

In another embodiment of the invention, supplying write signals includes supplying a plurality of sequential, incrementally varying voltage pulses at selected intervals.

In another embodiment of the invention, the sense amplifier circuit detects the resistance value of the nanotube fabric article after each voltage pulse is supplied by the write control 20 circuitry.

In another embodiment of the invention, the non-volatile memory is capable of a first write operation wherein the voltage pulses are supplied to the selected non-volatile memory cell until at least one of the multiple low resistance 25 values is detected by the sense amplifier circuit.

In another embodiment of the invention, when the sense amplifier circuit detects at least one of the multiple low resistance values in the selected memory cell, the resistance sensing circuitry is responsive to the sense amplifier circuit to <sup>30</sup> selectively stop the write control circuitry from writing the informational state of the selected memory cell.

In another embodiment of the invention, the non-volatile memory is capable of a second write operation wherein the voltage pulses are supplied to the selected non-volatile <sup>35</sup> memory cell until the relatively high resistance value is detected.

In another embodiment of the invention, when the sense amplifier circuit detects the relatively high resistance value in the selected non-volatile memory cell, the resistance sensing 40 circuitry is responsive to the sense amplifier circuit to selectively stop the write control circuitry from writing the informational state of the selected memory cell.

In another embodiment of the invention, the nanotube switching element comprises a one-time programmable <sup>45</sup> nanotube fuse having a nanotube fabric article capable of only switching from a first resistance value to a second resistance value.

## BRIEF DESCRIPTION OF THE DRAWINGS

In the drawings:

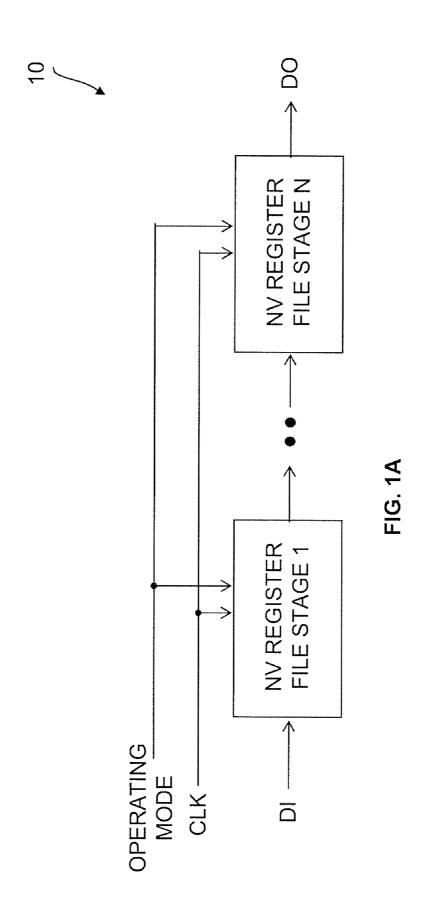

FIG. 1A is an illustration of an embodiment of a nonvolatile register file schematic.

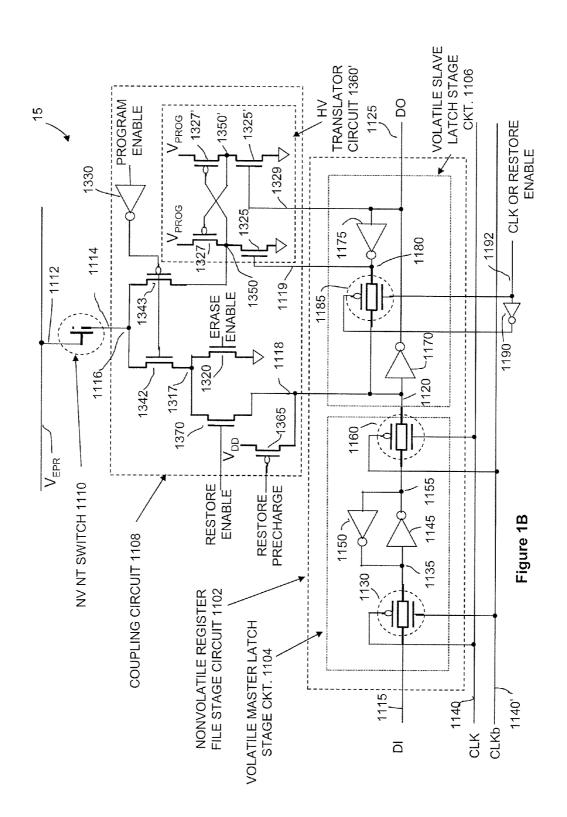

FIG. 1B is an illustration of an embodiment of a nonvolatile 55 register file stage circuit.

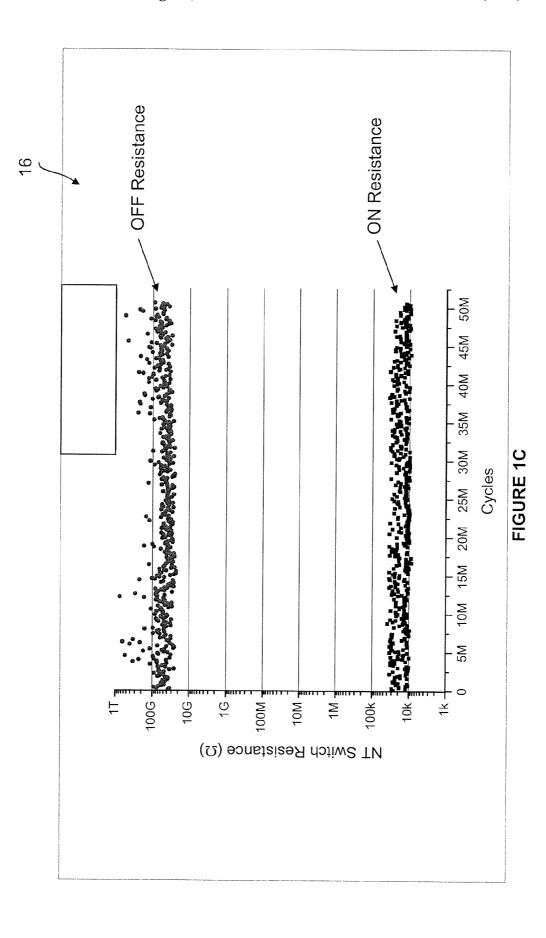

FIG. 1C is an illustration of the results of cycling data for a nonvolatile nanotube switch, according to one embodiment of the invention.

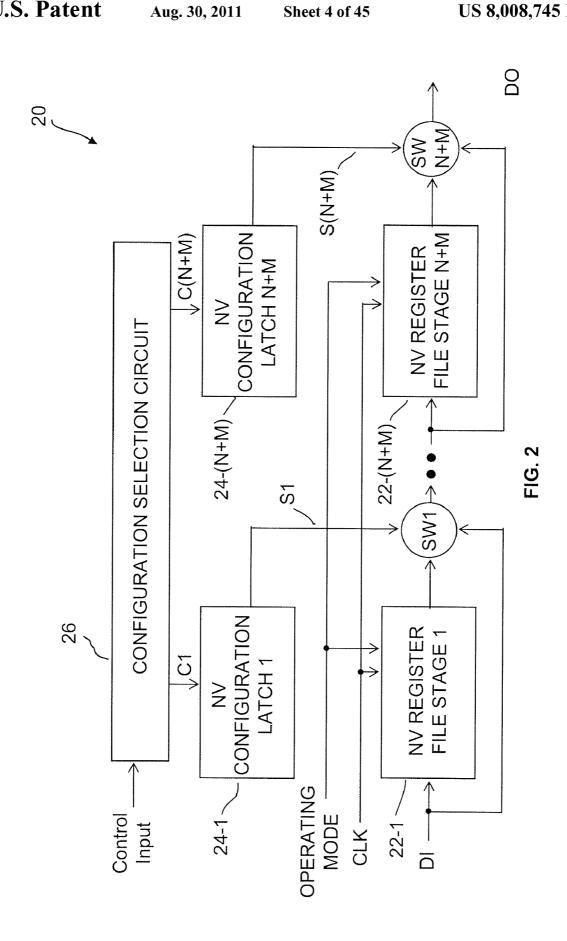

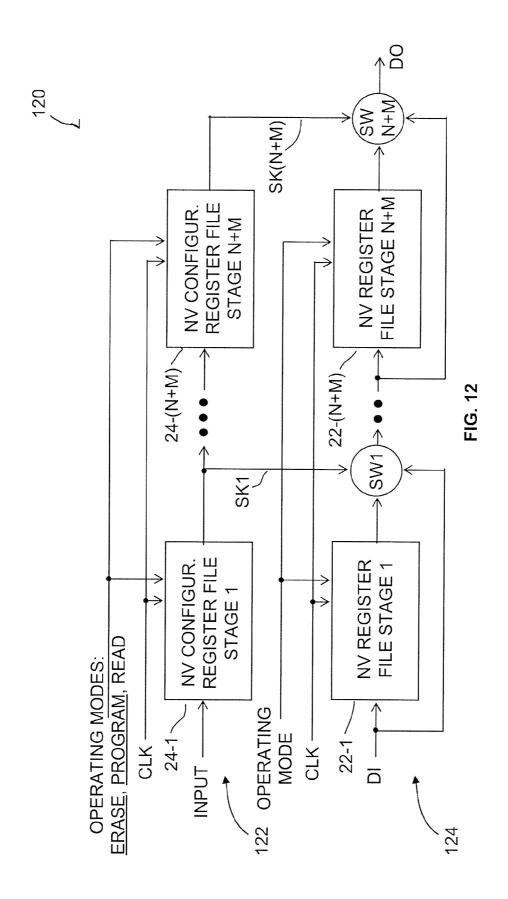

FIG. 2 is a schematic representation of the nonvolatile 60 register file of FIG. 1A with additional redundant nonvolatile register file stages and corresponding selection circuitry, according to another embodiment of the invention.

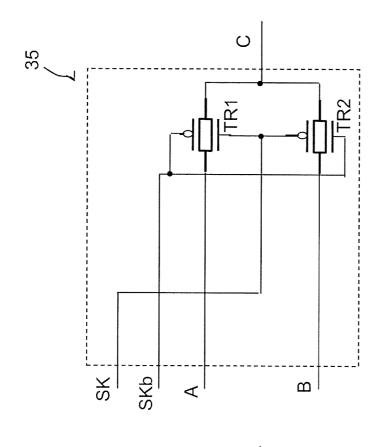

FIGS. 3A-3C are schematic representations of switches used to select or deselect (bypass) nonvolatile register file 65 stages when forming the final nonvolatile register file, according to other embodiments of the invention.

8

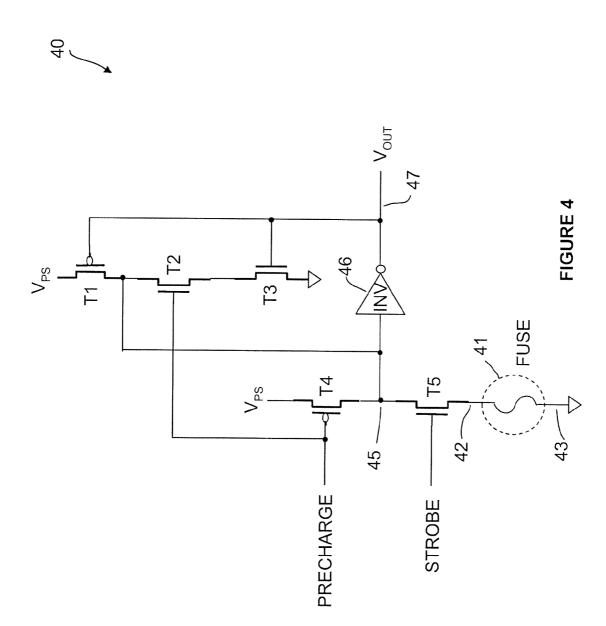

FIG. 4 is a latch circuit schematic of a laser fuse latch that may be used as part of the nonvolatile register file circuit described in FIG. 2, according to another embodiment of the invention.

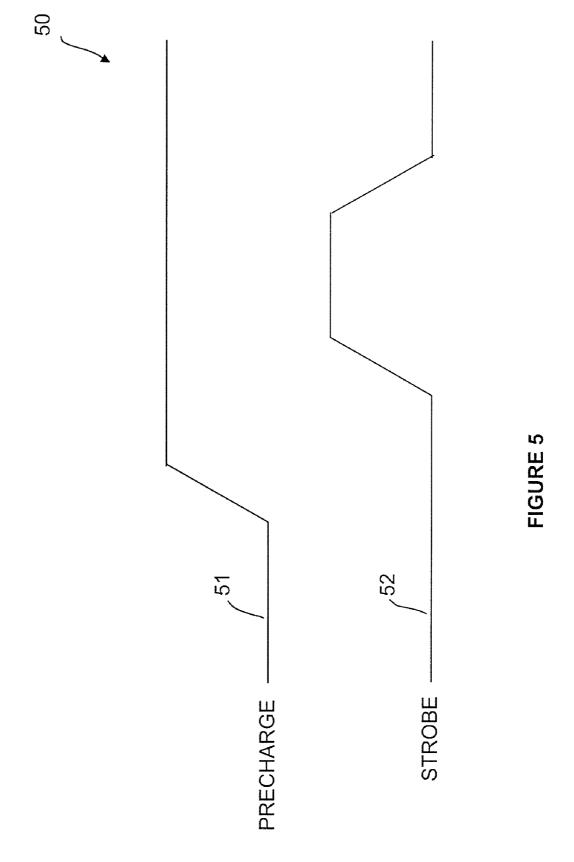

FIG. 5 is a representation of waveforms used in the operation of the latch circuit described in FIG. 4, according to another embodiment of the invention.

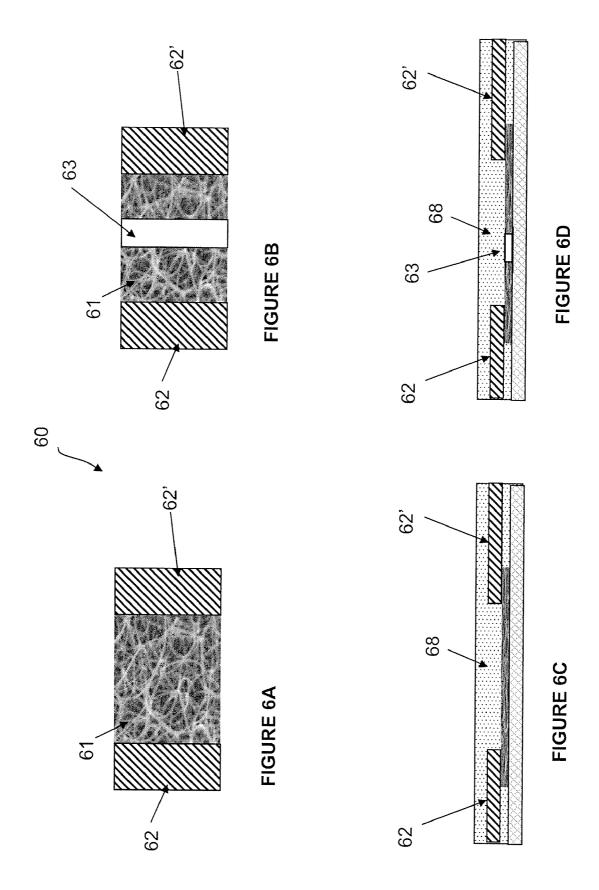

FIGS. **6**A-**6**D are illustrations of patterned nanofabric resistors, according to other embodiments of the invention.

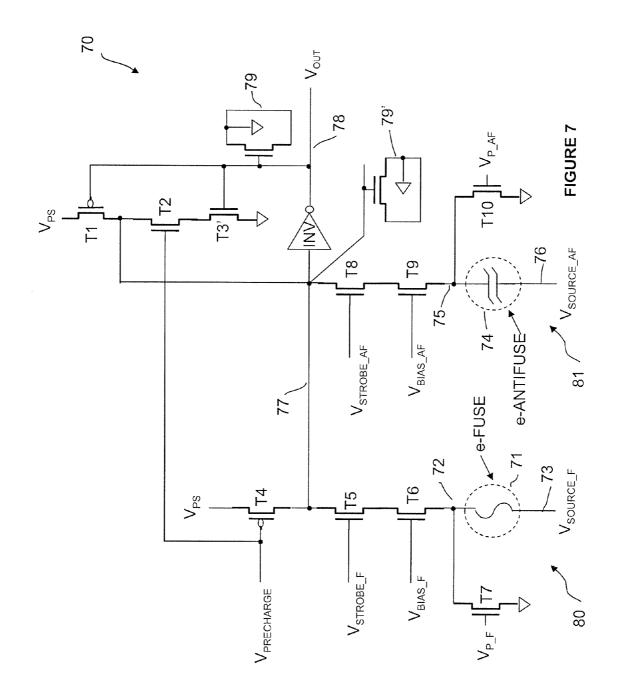

FIG. 7 is an illustration of a latch circuit using electronic fuses or electronic antifuses that may be used as part of the nonvolatile register file circuit described in FIG. 2, according to another embodiment of the invention.

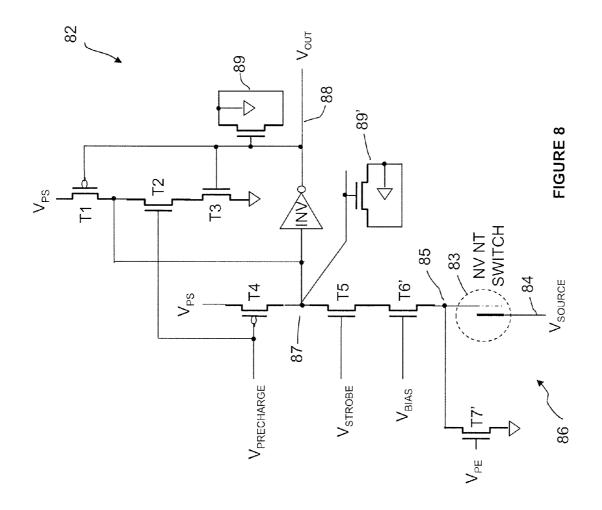

FIG. 8 is an illustration of a latch circuit using a nonvolatile nanotube switch as a programming element useable as part of the nonvolatile register file circuit described in FIG. 2, according to another embodiment of the invention.

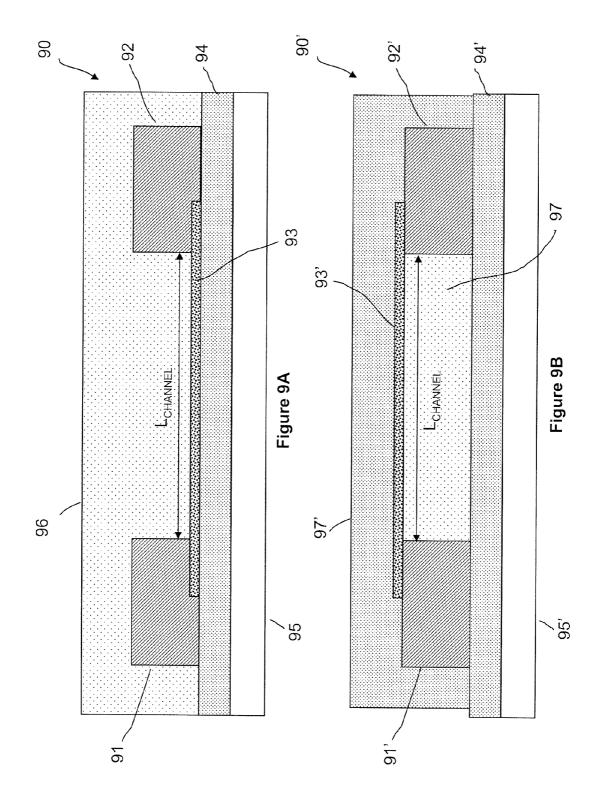

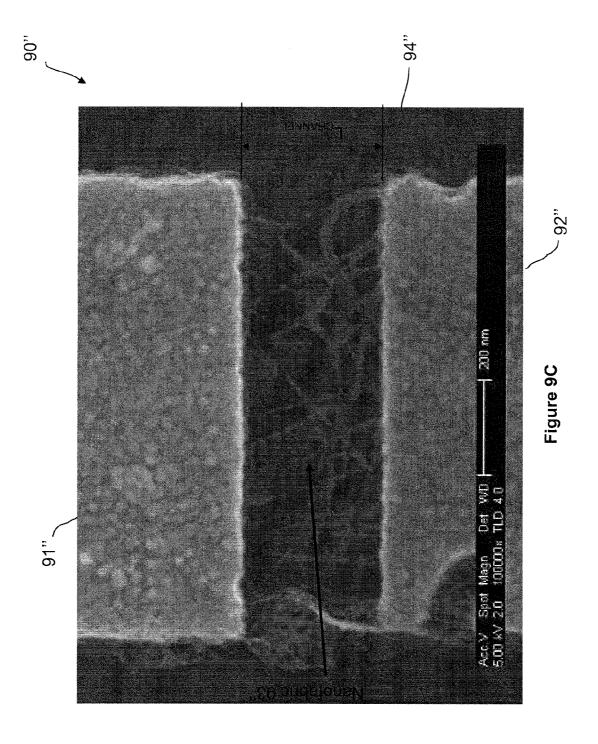

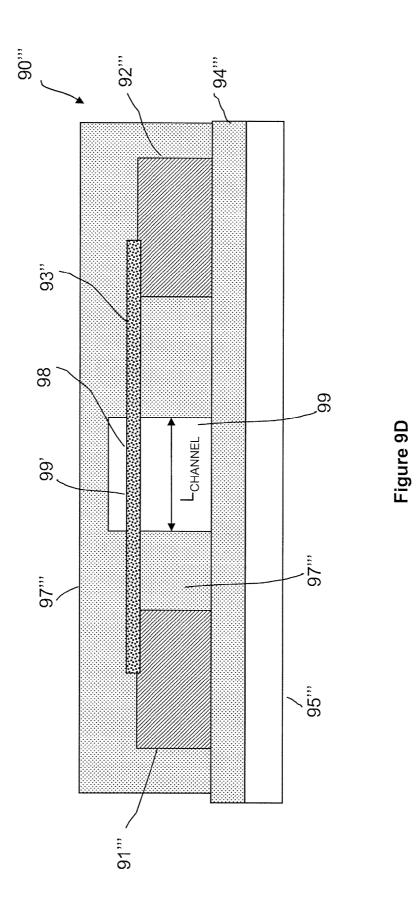

FIGS. **9**A-D are illustrations of cross sections and a SEM planar view of a nonvolatile nanotube switch, according to other embodiments of the invention.

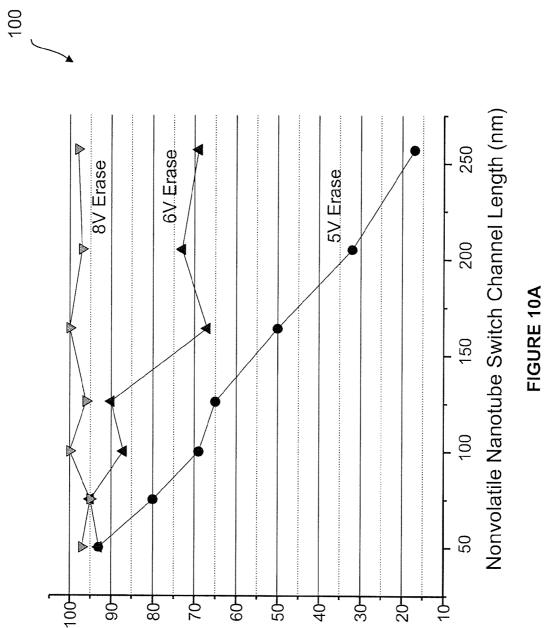

FIG. 10A is a graphical representation of several nonvolatile nanotube switches of varying channel length illustrating the scaling of erase voltages, according to another embodiment of the invention.

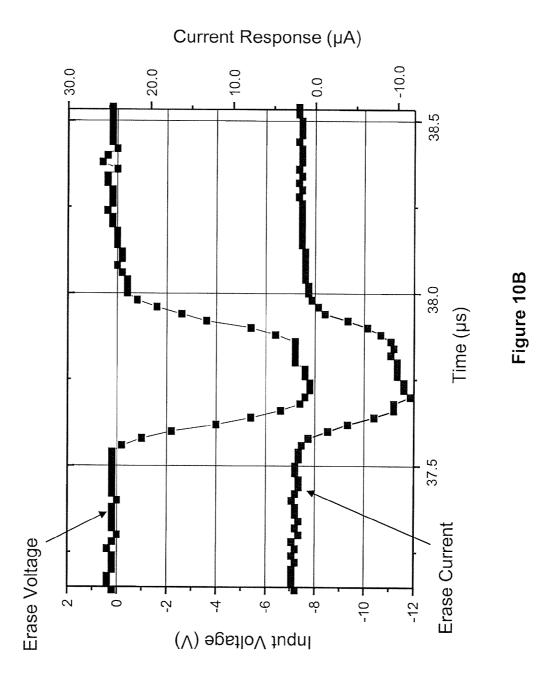

FIG. 10B is graphical representation of a nonvolatile nanotube switch illustrating erase voltage and erase current as a function of time, according to another embodiment of the invention.

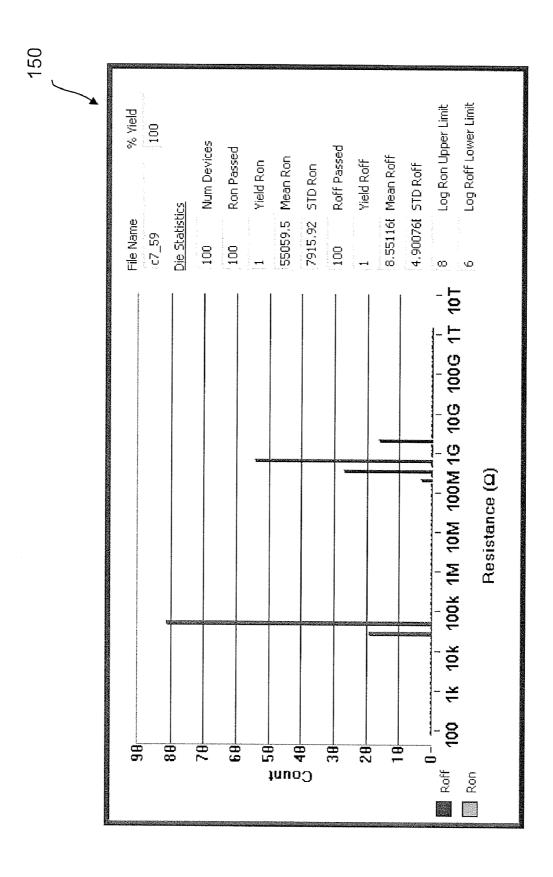

FIG. 10C is a graphical representation of a nanotube switch illustrating the ON state resistance and OFF state resistance measured during 100 cycles, according to another embodiment of the invention.

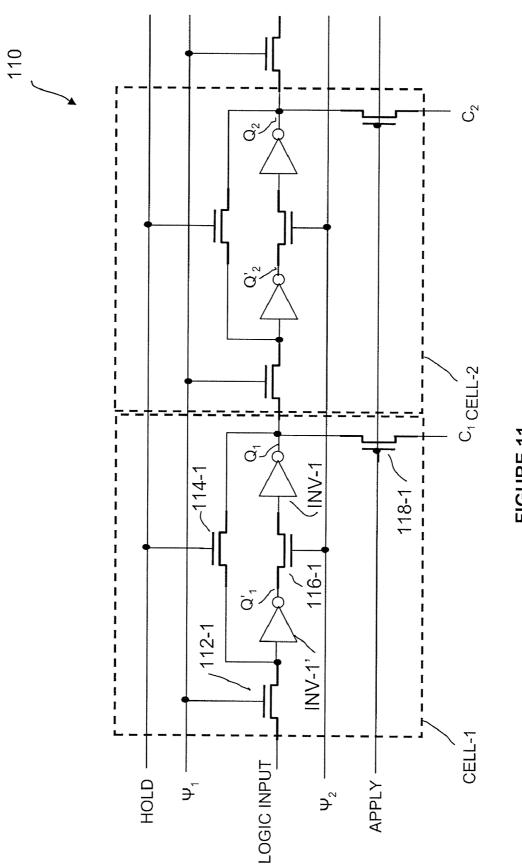

FIG. 11 is a schematic representation of a configuration control register, according to another embodiment of the invention.

FIG. 12 is an alternative (to FIG. 2) schematic representation of the nonvolatile register file of FIG. 1A with additional redundant nonvolatile register file stages and corresponding selection circuitry, according to another embodiment of the invention

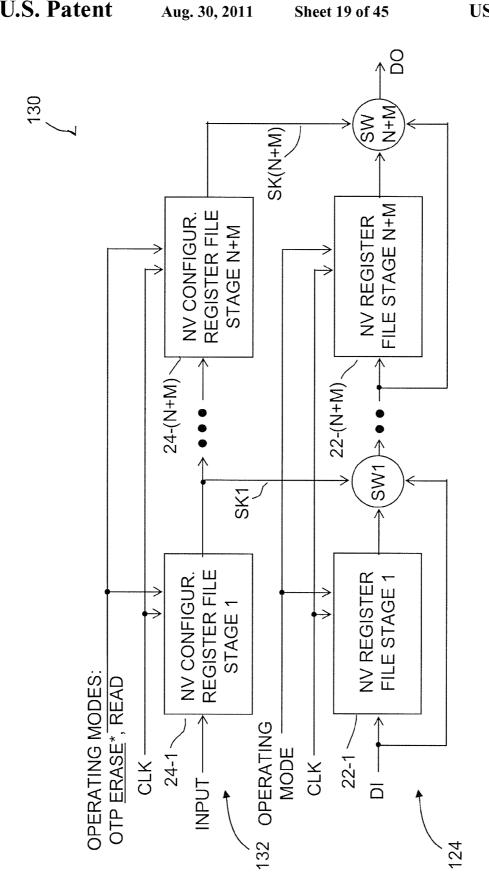

FIG. 13A is an alternative (to FIG. 12) schematic representation of the nonvolatile register file of FIG. 1A with additional redundant nonvolatile register file stages and corresponding selection circuitry, according to another embodiment of the invention.

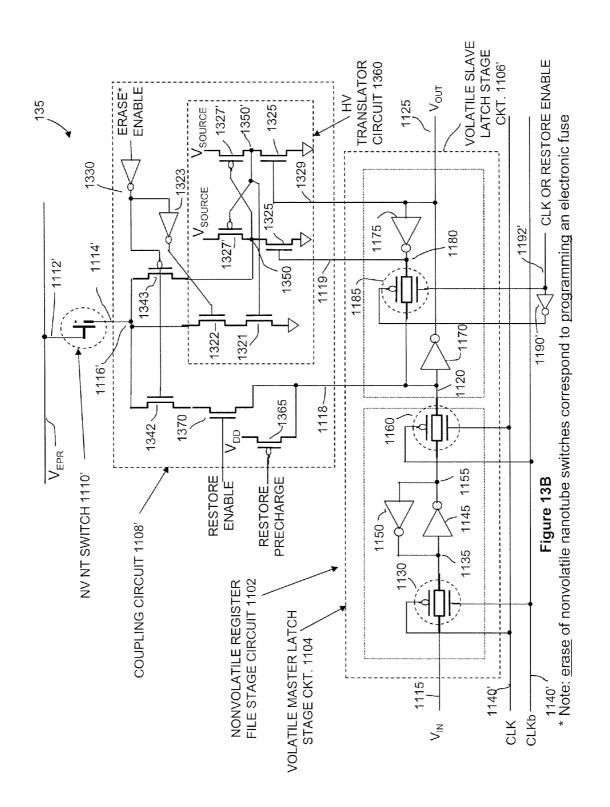

FIG. 13B is a circuit representation of nonvolatile configuration control register used in FIG. 13A, according to this embodiment of the invention.

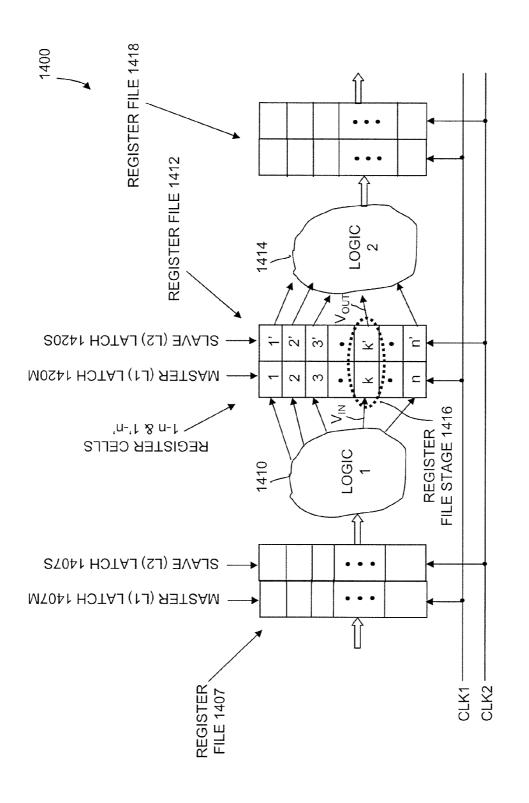

FIG. 14A illustrates a synchronized register file architec-50 ture application, according to another embodiment of the invention.

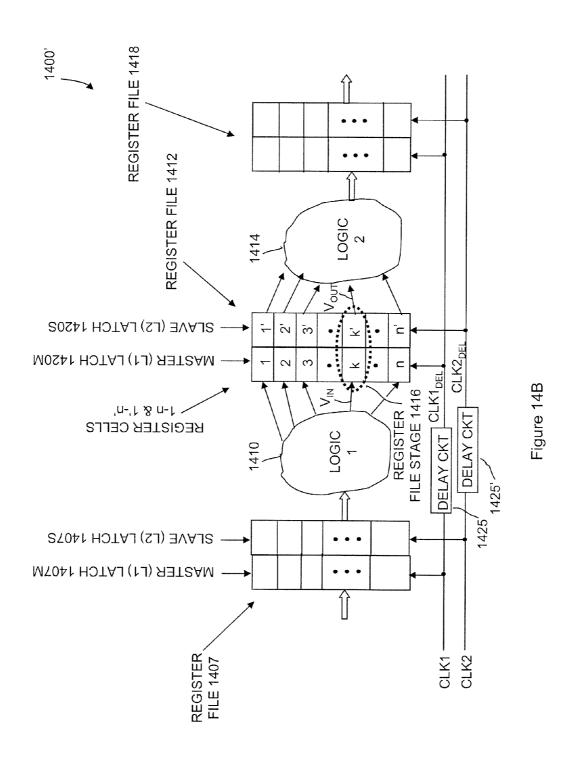

FIG. 14B illustrates synchronized register file architecture with controlled delay circuits to optimize clock timing, according to another embodiment of the invention.

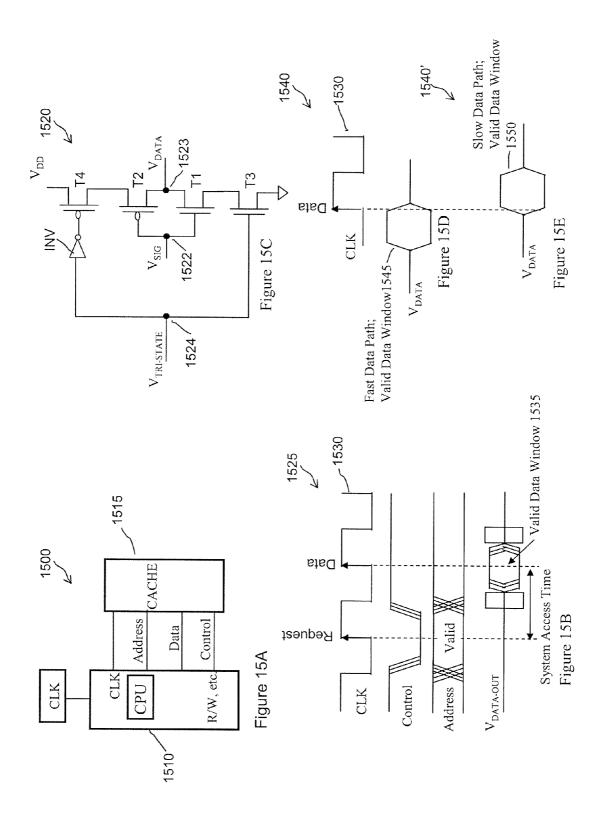

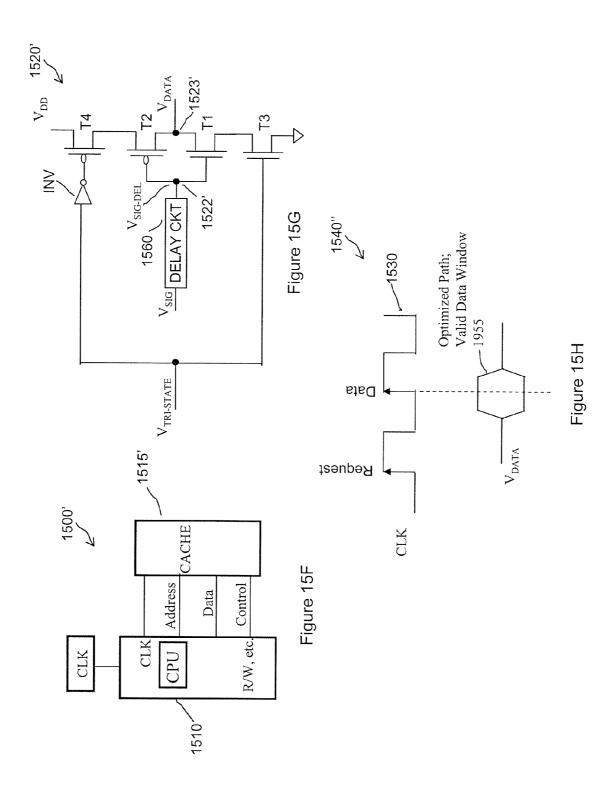

FIGS. **15**A-E illustrate a example of critical synchronized timing between a CPU and cache, according to other embodiments of the invention.

FIGS. **15**F-H illustrate optimized timing between a CPU and cache using a controllable delay circuit, according to other embodiments of the invention.

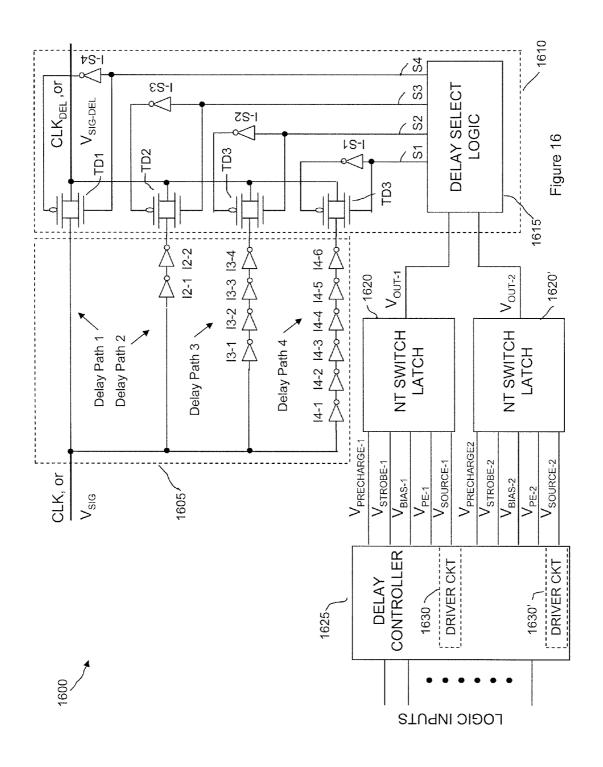

FIG. 16 illustrates a delay control circuit that uses nonvolatile nanotube switch-based latches for timing control, according to another embodiment of the invention.

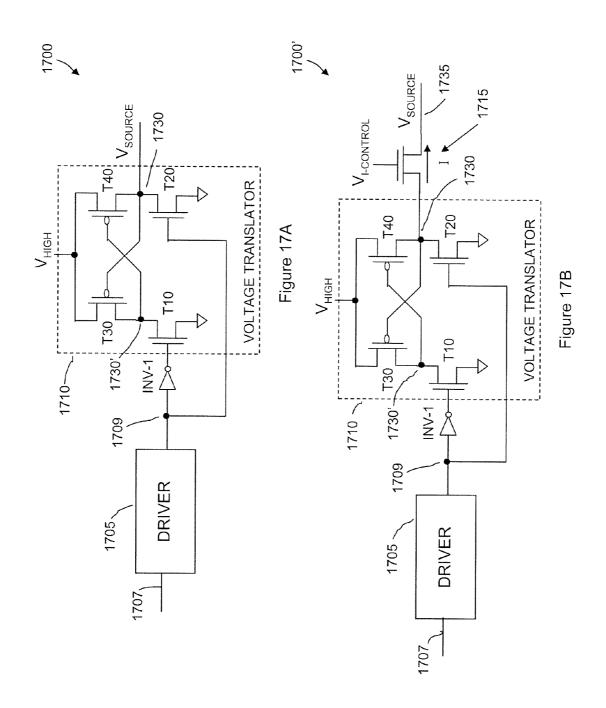

FIG. 17A illustrates a driver circuit used to change the state of nonvolatile nanotube switches in latch circuits using a voltage source, according to another embodiment of the invention.

- FIG. 17B illustrates a driver circuit used to change the state of nonvolatile nanotube switches in latch circuits using a voltage source with current limits, according to another embodiment of the invention.

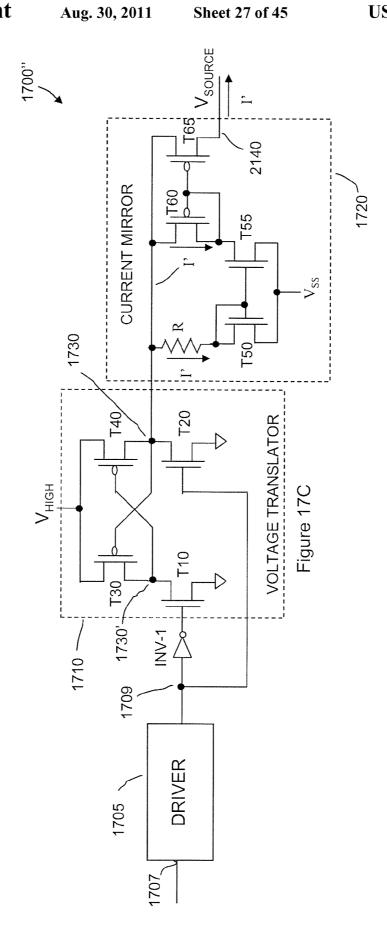

- FIG. 17C illustrates a driver circuit used to change the state of nonvolatile nanotube switches in latch circuits using a voltage source with current controlled by a current mirror, according to another embodiment of the invention.

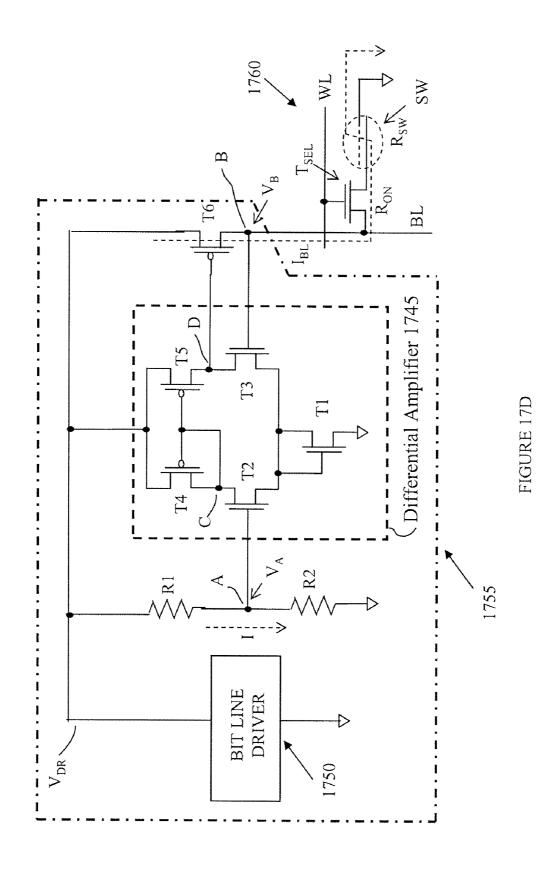

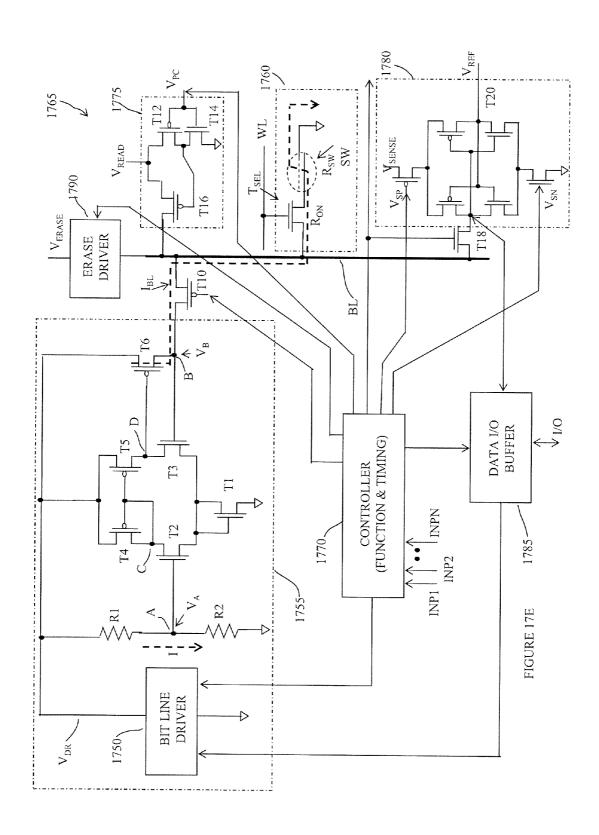

- FIG. 17D illustrates a nonvolatile nanotube switch resistance control circuit that drives an NRAM array cell to a 10 predetermined resistance value, according to another embodiment of the invention.

- FIG. 17E illustrates the circuit of FIG. 17D integrated in an NRAM memory system, according to another embodiment of the invention

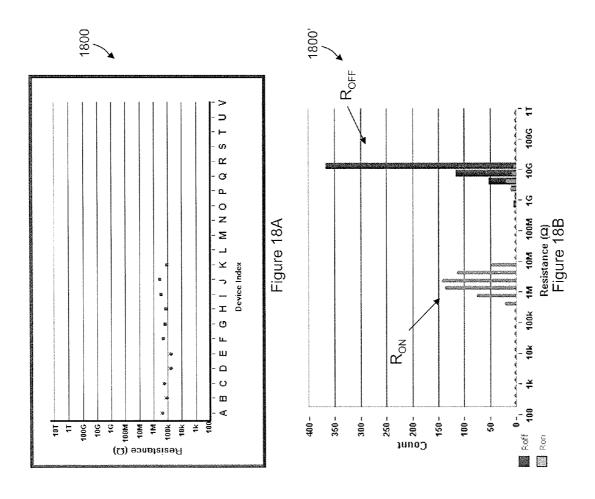

- FIG. **18**A illustrates ON resistance values of as-fabricated nonvolatile nanotube switches, according to another embodiment of the invention.

- FIG. **18**B illustrates ON and OFF resistance values of nonvolatile nanotube switches after fifty cycles, according to 20 another embodiment of the invention;

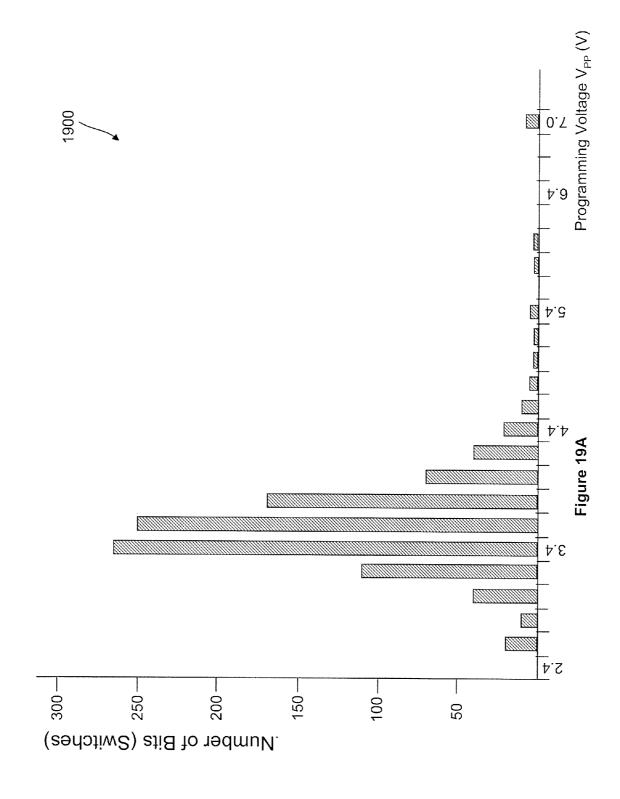

- FIG. 19A illustrates an example of the number of nanotube switches programmed at selected voltage levels, according to another embodiment of the invention.

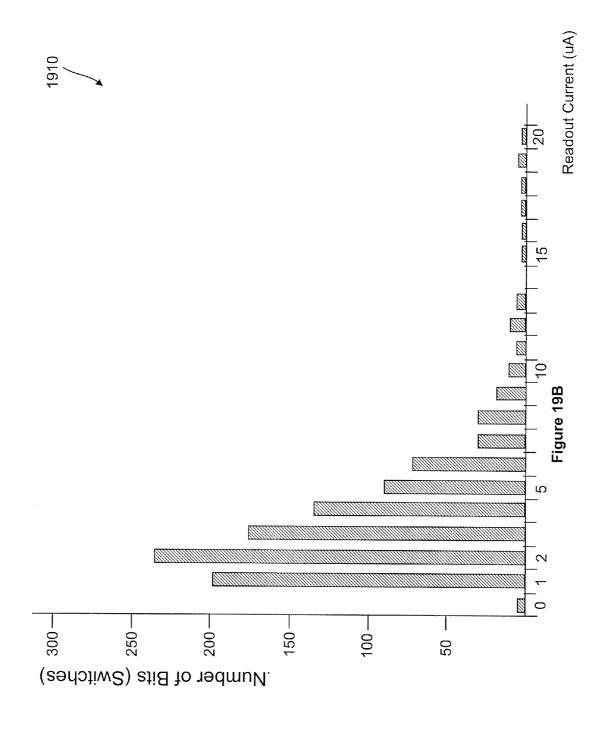

- FIG. **19**B illustrates an example of the number of programmed nanotube switches at various readout currents corresponding to a one volt bit line readout voltage, according to another embodiment of the invention.

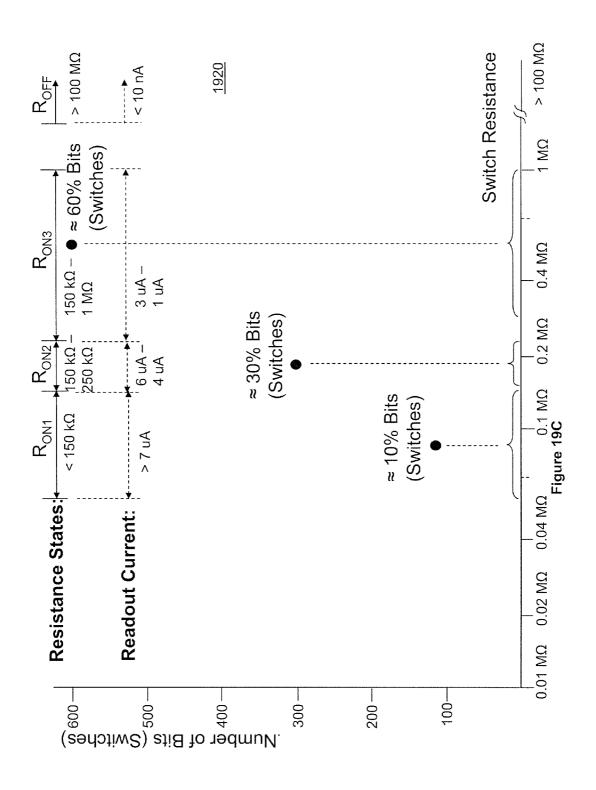

- FIG. 19C illustrates an example of the number of nanotube switches operating within selected resistance ranges, where 30 resistance values correspond to FIG. 19B readout current at one volt, according to the present embodiment of the invention.

- FIG. **19**D illustrates an example of median current levels and corresponding saturation current levels at selected voltage levels, according to the present embodiment of the invention.

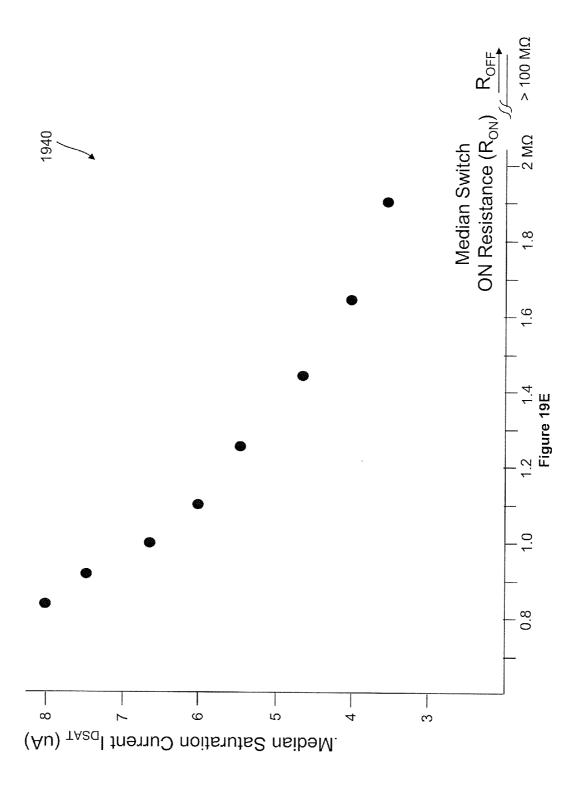

- FIG. 19E illustrates an example of median saturation current levels at selected median switch ON-state resistance levels, according to the present embodiment of the invention. 40

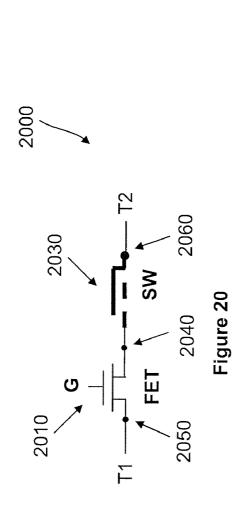

- FIG. **20** illustrates a series circuit, according to an embodiment of the invention.

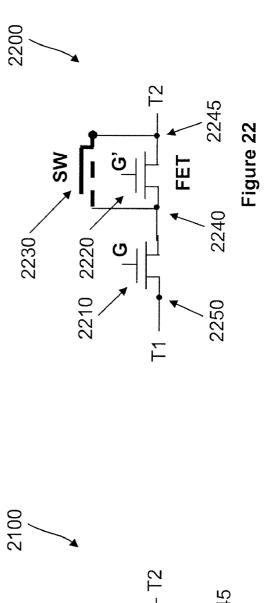

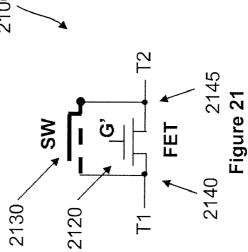

- FIG. 21 illustrates a parallel circuit, according to another embodiment of the invention.

- FIG. 22 illustrates a combined series/parallel circuit, 45 according to another embodiment of the invention.

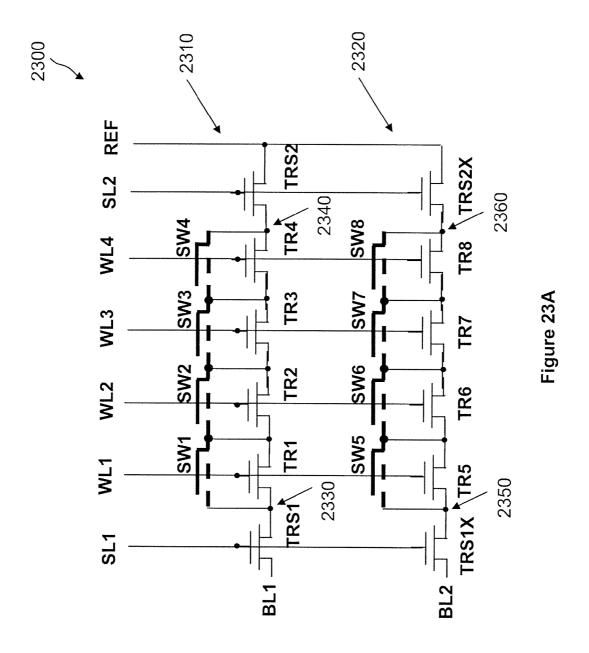

- FIG. 23A illustrates a NFlash memory schematic, according to another embodiment of the invention.

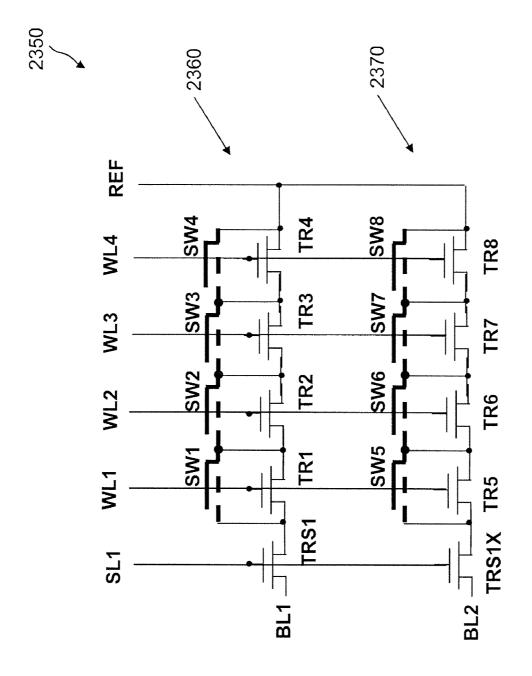

- FIG. 23B illustrates a NFlash memory schematic, according to another embodiment of the invention.

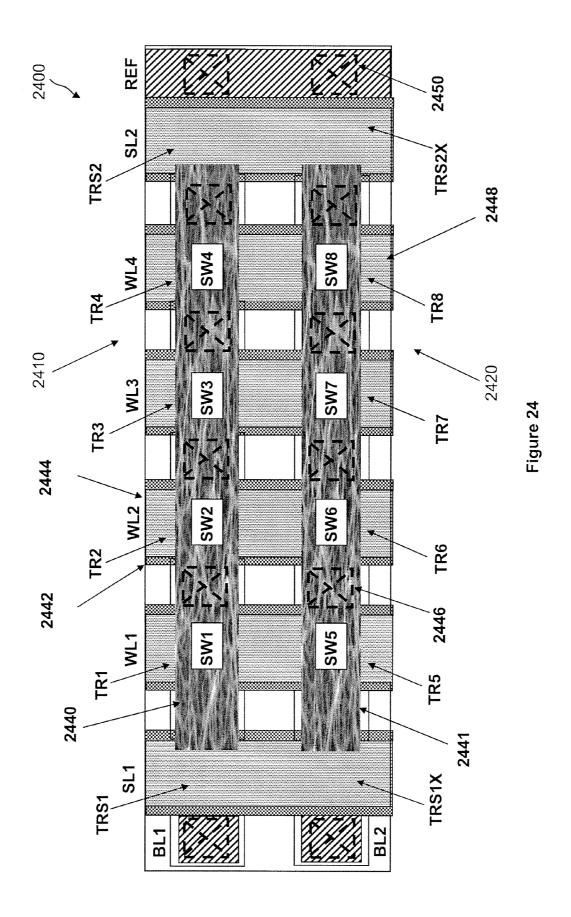

- FIG. **24** illustrates a plan view corresponding to a NFlash memory, according to another embodiment of the invention.

- FIG. 25 illustrates a cross sectional view of a NAND subarray, according to another embodiment of the invention.

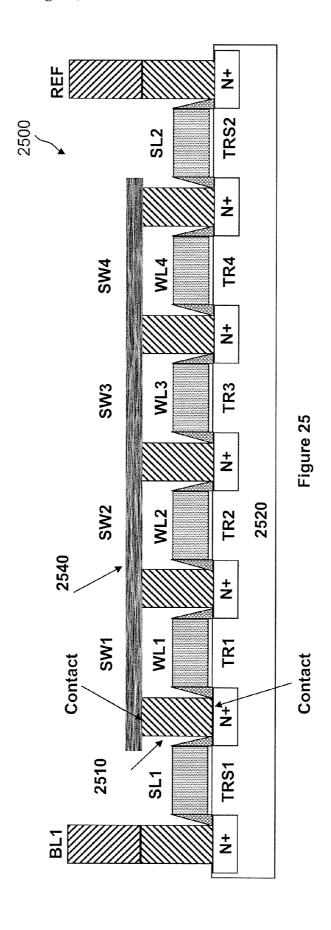

- FIG. **26**A illustrates an electronically controlled series 55 resistance network in which a nanotube series resistor network is electronically formed and tuned using program or erase operations, according to another embodiment of the invention.

- FIG. **26**B illustrates a nanotube series resistor equivalent 60 circuit, according to another embodiment of the invention.

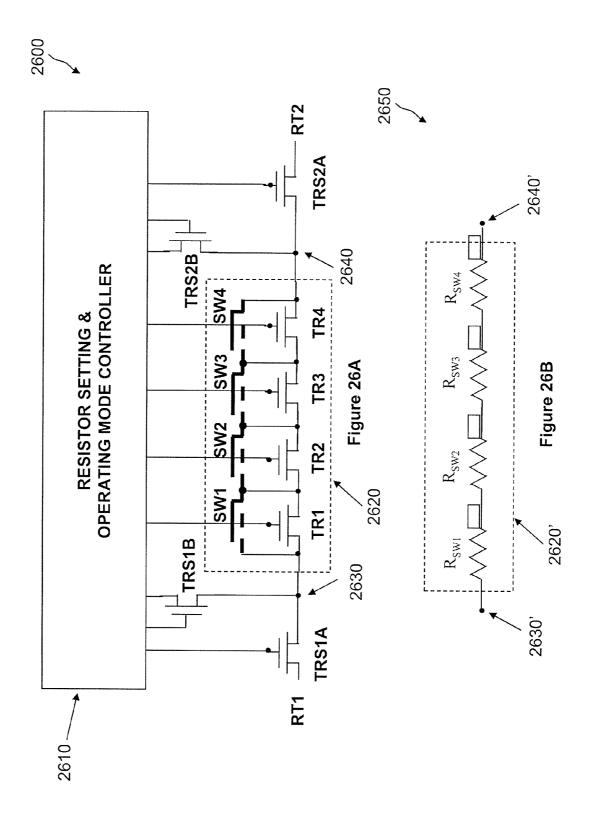

- FIG. 27 illustrates a nanotube-based electronically tuned on-chip voltage regulator, according to another embodiment of the invention.

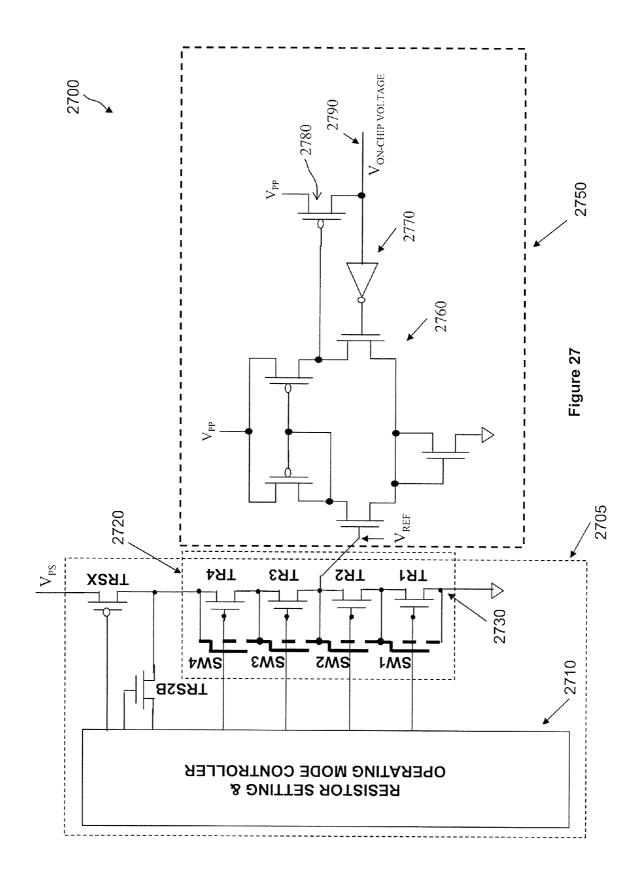

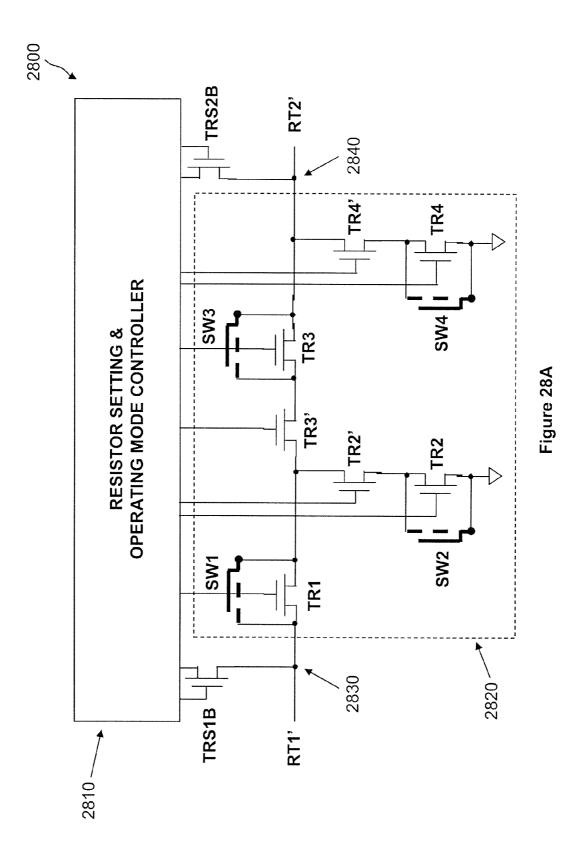

- FIG. **28**A illustrates an electronically formed and tuned 65 combination series/parallel resistance network, according to another embodiment of the invention.

10

- FIG. **28**B illustrates a combination series/parallel resistor equivalent circuit, according to another embodiment of the invention.

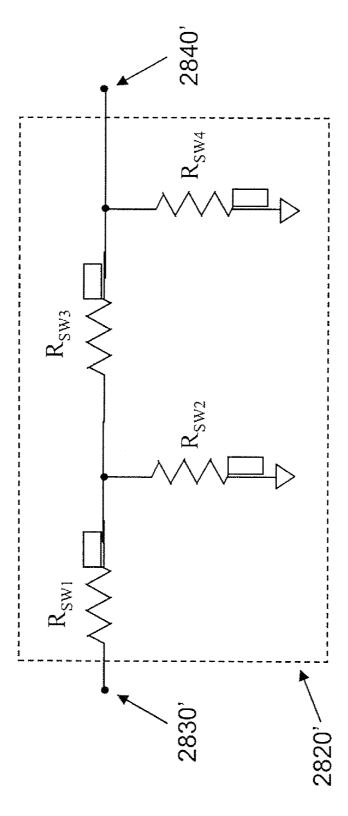

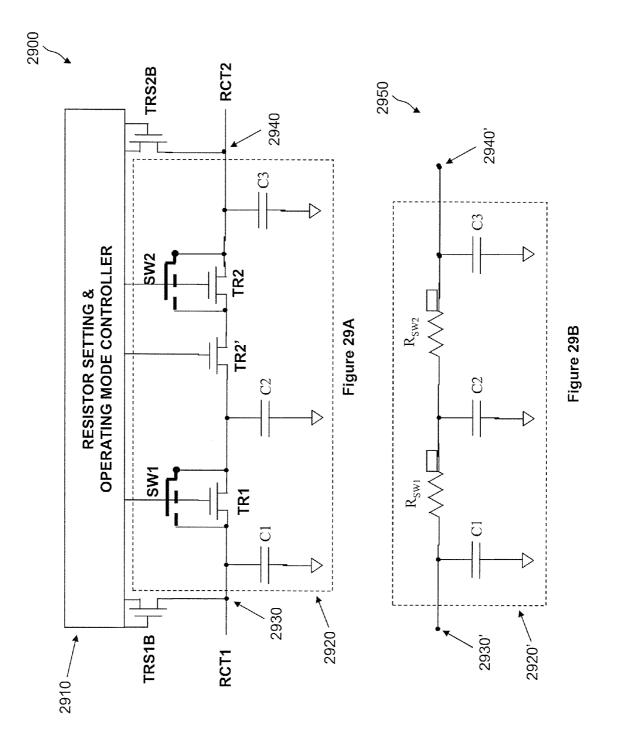

- FIG. **29**A illustrates an electronically formed and tuned resistance/capacitor network, according to another embodiment of the invention.

- FIG. **29**B illustrates a combined series/parallel resistor/capacitor equivalent circuit, according to another embodiment of the invention.

### DETAILED DESCRIPTION

## Nonvolatile Register File

The present invention provides scalable latch circuits and memory cells based on nanofablic material and scalable nonvolatile nanotube switches.

The present invention also provides nonvolatile register files, and more specifically nonvolatile register files formed by selecting a smaller subset of individual nonvolatile register file stages from a larger set that includes redundant stages for yield enhancement purposes.

The present invention also provides high speed asynchronous logic and synchronous logic and memory circuits in which clock timing and signal timing is improved using new scalable latch circuits based on nanofabric material and scalable nonvolatile nanotube switches for higher performance at higher yield.

It is often desirable for fuse latch circuits to be able to store a logic state indicative of the logical state of a corresponding fuse (or antifuse) so that when the latch is connected to other circuits, it may provide programming information for other electronic circuits such as address relocation for redundant memory elements, operating mode configuration, to store a tracking code pertaining to manufacture date or other conditions, for example. One such latch application is in the field of yield enhancement for nonvolatile register files.

FIG. 1A illustrates a serial nonvolatile register file 10 of N stages, having N repeated and essentially the same individual nonvolatile stages beginning with stage 1 and ending with stage N. Nonvolatile register files are described in more detail in U.S. patent application Ser. No. 11/280,599.

Data inputs DI is supplied to the input of NV register file stage 1. The data output of stage 1 drives the data input of NV register file stage 2, and so on, until the output of NV register file stage N-1 drives the input of NV register file stage N. The output of NV register file stage N provides data output DO.

Nonvolatile register file 10 operates in a synchronous mode with clock CLK supplied to each stage of the register file 10. Each stage of nonvolatile register file 10 includes a volatile master latch that drives a nonvolatile slave latch, in which the nonvolatile slave latch includes a volatile latch and a corresponding coupled nonvolatile nanotube switch for storing the latch logic state in a nonvolatile mode when power is removed or lost. The logical state at the time power is removed or lost is restored prior to resuming register file 10 operation. Register file 10 operates in a normal volatile mode at full speed and at voltage levels  $V_{DD}$  corresponding to the selected technology node.  $V_{DD}$  may be 1.5 to 2.5 volts, for example. Clock frequencies may be in 1 to 10 GHz range or more, for example.

If a portion of the chip including nonvolatile register file 10 is to be de-powered (power supply is removed or lost), then data (the logic state) from the volatile portion of each stage of nonvolatile register file 10 may be transferred to a nonvolatile nanotube switch as described in U.S. patent application Ser. No. 11/280,599. Clock CLK is stopped, then operating mode

pulses are used to save the state of each latch in a corresponding nonvolatile nanotube switch just prior to power shutdown. Next, power may be removed from nonvolatile register file 10 and associated logic and memory circuits.

11

If normal register file 10 operation is to be restored, then the 5 portion of the chip that has been de-powered, or the entire chip if all power is removed or lost, is then re-powered. Next, operating mode pulses may be used to transfer data (logic state) of each nonvolatile nanotube switch to its corresponding nonvolatile register file stage of nonvolatile register file 10 as described in U.S. patent application Ser. No. 11/280,599. Next, clock CLK is started and high speed operation begins. Program modes such as erase, program, and read are described in patent application Ser. No. 11/280,599. Nonvolatile nanotube switch fabrication, integration into semi- 15 conductor processes, electrical characteristics, and operating modes and operating conditions are described in U.S. patent application Ser. No. 11/280,786.

Nonvolatile Register File Stage Circuit

FIG. 1B illustrates an embodiment of a nonvolatile register 20 file stage circuit 15 described in U.S. patent application Ser. No. 11/280,599, that corresponds to any one of nonvolatile register file stages 1 . . . N in FIG. 1A. U.S. patent application Ser. No. 11/280,599 describes various nonvolatile register file stage circuits, some with register file stage circuits coupled to 25 a nonvolatile nanotube switch by a coupling circuit, and others with register file stage circuits directly coupled to a nonvolatile nanotube switch. In this example, register file stage circuit 1102 is coupled to nonvolatile nanotube switch 1110 by circuit 1108.

Nonvolatile register file stage 15 has two modes of operation, a normal run mode and a zero power logic state (or data state) nonvolatile retention mode in which power may be disconnected. Volatile master latch stage circuit 1104 and volatile slave latch stage circuit 1106 form one stage of a 35 register file stage circuit 1102 that may also be referred to as an LSSD register stage.

As illustrated in FIG. 1B, input node 1115 of volatile master latch stage circuit 1104 receives data input signal DI and drives storage node 1135 formed by cross coupled CMOS inverters 1145 and 1150. CMOS transfer gate 1130 uses both NMOS and PMOS devices instead of an NMOS-only transfer gate, for example, to ensure that both logic "1" and logic "0" states transition between full power supply and ground volt- 45 age levels by eliminating device threshold voltage drops. Clock CLK 1140, and complementary clock CLKb 1140' are used to enable or block input signal DI on input node 1115 from driving storage node 1135; by turning CMOS transfer gate 11300N and OFF, thereby determining the logic storage 50 state of cross coupled CMOS inverters 1145 and 1150. Note that the inverters in the present illustration are CMOS inverters unless otherwise specified. CMOS inverters include a PMOS pull-up device connected to a power supply, and a NMOS pull-down device connected to ground and operates 55 as discussed in the reference by H. B. Bakoglu, "Circuits, Interconnections, and Packaging for VLSI", Addison-Wesley Publishing Company, Inc, 1990, pp. 152, the entire contents of which are incorporated herein by reference. Cross coupled inverters 1145 and 1150 drive storage node 1155 which is 60 connected to CMOS transfer gate 1160. Clock CLK and complementary clock CLKb are used to enable or block stored logic state node 1155 from driving slave latch stage circuit 1106 input node 1120 by turning CMOS transfer gate 11600N and OFF.

As illustrated in FIG. 1B, input node 1120 of volatile slave latch stage circuit 1106, which is also the output node of master latch stage circuit 1104, drives inverter 1170. The output of inverter 1170 is data output signal DO on output node 1125, and also drives the input of inverter 1175. The output 1180 of inverter 1175 is connected to CMOS transfer gate 1185. Clock CLK, and complementary clock CLKb are used to enable or block the presence of a feedback loop that cross couples inverters 1170 and 1175 when enabled. During normal high speed operation, clock CLK switches at high speed, 3 GHz clock rate, for example, for the 130 nm CMOS technology node. Inverter 1190 produces the complement CLKb or the complement of RESTORE ENABLE. When storing data, CMOS transfer gate 1185 is ON and inverters 1170 and 1175 form a cross coupled storage device with node 1120 acting as a storage node. When CMOS transfer gate 1185 is OFF, then inverters 1170 and 1175 are not cross

12

As illustrated in FIG. 1B, nonvolatile nanotube switch 1110 is connected to power supply voltage  $V_{EPR}$ , which supplies erase voltage pulse (or pulses) corresponding to the operating mode selected using coupling circuit 1108. Nonvolatile nanotube switch 1110 is also connected to node 1116 of coupling circuit 1108 using electrical connection 1114. Coupling circuit 1108 is connected to volatile slave latch stage circuit 1106, where electrical connections 1119 and 1329 connected to nodes 1180 and 1125, respectively, are used in program mode, and electrical connection 1118 is used in restore mode.

coupled and do not form a storage device. Slave latch stage

circuit 1106 is coupled to nonvolatile nanotube switch 1110

by coupling circuit 1108.

As illustrated in FIG. 1B, coupling circuit 1108 includes an erase function. The erase circuit includes NMOS transistor 1320 with drain connected to common node 1317, source connected to ground, and input gate connected to an erase enabling pulse. During an erase operation, transistor 1342 is activated by a program enable pulse at zero volts, and common node 1317 is connected to common node 1116, which is connected to nonvolatile nanotube switch 1110 in order to enable an erase operation

As illustrated in FIG. 1B, coupling circuit 1108 also and drives CMOS transfer gate 1130, which is connected to 40 includes a programming function including PMOS transistor 1343 with drain connected to common node 1116, source connected to common node 1350, and gate connected to output of inverter 1330, with the input of inverter 1330 connected to a program enable input. Common node 1350 is connected to cross coupled NMOS transistors 1325 and 1325' and PMOS transistors 1327 and 1327' forming high voltage translation circuit 1360'. The sources of NMOS transistors 1325 and 1325' are connected to ground, and the sources of PMOS transistors 1327 and 1327' are connected to program voltage  $V_{PROG}$ . Complementary inputs 1119 and 1329 are connected to high voltage translator circuit 1360' input NMOS transistor 1325 and NMOS 1325', respectively, such that the logic state of high voltage translator circuit 1360' corresponds to the state of volatile slave latch stage 1106.  $V_{PROG}$  voltage may be much higher than volatile slave latch stage voltage circuit 1106. Programming voltage is applied to common node 1350 through PMOS transistor 1327, which is in turn applied to common node 1116 and nonvolatile nanotube switch 1110 through PMOS transistor 1343. If common node 1350 is held at ground by NMOS transistor 1325, then no programming voltage is applied to common node 1350, and nonvolatile nanotube switch 1110 is not programmed.

As illustrated in FIG. 1B, coupling circuit 1108 also includes a restore function including PMOS transistor 1365 with source connected to  $V_{DD}$ , and drain connected to volatile slave latch stage circuit 1106 input 1120 by connector 1118. During a restore operation, PMOS transistor 1365 is used to

pre-charge input node 1120 to  $V_{DD}$ , and then is turned OFF. NMOS transistor 1370 has source connected to input 1120 by connector 1118, drain connected to common node 1317, and gate connected to a restore enable input. NMOS transistor 1342 which is in the ON state during a restore operation, and provides a discharge path between input node common node 1317 and  $V_{EPR}$ , through nonvolatile nanotube switch 1110.  $V_{EPR}$  is at zero volts during a restore operation. When transistor 1370 is activated by a restore enable input, if nonvolatile nanotube switch 1110 is ON, then input node 1120 is discharged; if nonvolatile switch 1110 is OFF, then input node remains at  $V_{DD}$ . The state of volatile slave latch stage circuit 1106 is restored to a state corresponding to the nonvolatile state of nonvolatile nanotube switch 1110.

While in normal run mode, coupling circuit 1108 is inactive, and nonvolatile nanotube switch 1110 is not powered by  $V_{EPR}$  and is also decoupled from volatile slave latch stage circuit 1106. Hence, volatile master latch stage circuit 1104 and volatile slave latch stage circuit 1106 operate in a normal (conventional) synchronized logic master/slave register run 20 mode of operation at high speed clock rates, typically 3 GHz, with  $V_{DD}$ =1.3 volts, for logic products fabricated using the 130 nm technology node.

In normal run mode, at the beginning of a clock cycle, clock CLK 1140 transitions from high to low voltage and remains at 25 low voltage for the first half the clock cycle, and complementary clock CLKb 1140' transitions from low to high voltage and remains at high voltage for the first half of the clock cycle. CMOS transfer device 1130 turns ON coupling input node 1115 voltage  $V_{IV}$  to storage node 1135. CMOS transfer 30 device 1160 turns OFF and isolates the output of volatile master latch stage circuit 1104 from the input node 1120 of volatile slave latch stage circuit 1106. In normal run mode, clock CLK is connected to mode input 1192 of volatile slave latch stage circuit 1106, clock CLK is connected to CMOS transfer device 1185, and complementary clock CLKb output of inverter 1190 is also connected to CMOS transfer device 1185, such that CMOS transfer device also turns OFF breaking the feedback path between the output 1180 of inverter 1175 and the input 1120 of inverter 1170 such that node 1120 40 does not act as a storage node. DI signal may transition to a voltage value corresponding to the correct logic state any time prior to the end of the first half of the clock cycle, providing sufficient time remains for cross coupled inverters 1145 and 1150 to store the corresponding logic state on storage node 45 1155 prior to clock transition at the beginning of the second half of the clock cycle.