(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6601667号

(P6601667)

(45) 発行日 令和1年11月6日(2019.11.6)

(24) 登録日 令和1年10月18日(2019.10.18)

(51) Int.Cl.

F 1

|        |       |           |        |       |         |

|--------|-------|-----------|--------|-------|---------|

| G 11 C | 19/28 | (2006.01) | G 11 C | 19/28 | 2 3 0   |

| G 09 G | 3/20  | (2006.01) | G 09 G | 3/20  | 6 2 2 E |

| G 09 G | 3/36  | (2006.01) | G 09 G | 3/36  |         |

| G 09 G | 3/30  | (2006.01) | G 09 G | 3/30  | J       |

|        |       |           | G 09 G | 3/20  | 6 1 1 A |

請求項の数 11 (全 21 頁) 最終頁に続く

(21) 出願番号 特願2015-156162 (P2015-156162)

(22) 出願日 平成27年8月6日(2015.8.6)

(65) 公開番号 特開2016-110684 (P2016-110684A)

(43) 公開日 平成28年6月20日(2016.6.20)

審査請求日 平成30年7月26日(2018.7.26)

(31) 優先権主張番号 特願2014-244762 (P2014-244762)

(32) 優先日 平成26年12月3日(2014.12.3)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 303018827

Tianma Japan 株式会社

神奈川県川崎市幸区鹿島田一丁目1番2号

(74) 代理人 100114557

弁理士 河野 英仁

(72) 発明者 野中 義弘

神奈川県川崎市中原区下沼部1753番地

NLTテクノロジー株式会社内

審査官 津幡 貴生

最終頁に続く

(54) 【発明の名称】シフトレジスタ回路及びゲートドライバ並びに表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

单一導電型トランジスタで構成されたシフトレジスタ回路であって、

出力端子と第1の電源とをつなぐ第1の出力トランジスタを有するシフトレジスタ部と

、

前記第1の出力トランジスタのゲート端子にその出力端子が接続された第1のゲート制御回路とを含み、

前記第1のゲート制御回路が、タイミング生成部とバッファ部とで構成され、

前記バッファ部は、ブーストストラップ回路であり、

入力信号が入力される前記タイミング生成部の出力を前記バッファ部の入力とし、前記バッファ部の出力を前記第1のゲート制御回路の出力としており、

前記バッファ部が、少なくとも、

前記バッファ部の出力と第1のクロック信号とをつなぐ第2のトランジスタと、

前記第2のトランジスタのゲート端子と前記タイミング生成部の出力とをつなぎ、第2のクロック信号によりゲート制御される第3のトランジスタと、

前記バッファ部の出力と前記第1の電源とをつなぎ、前記第2のクロック信号によりゲート制御される第4のトランジスタとを含むブーストストラップ回路である

ことを特徴とするシフトレジスタ回路。

## 【請求項 2】

前記タイミング生成部が、

前記第1のゲート制御回路の入力によりゲート制御され、前記第1の電源と前記バッファ部の入力とをつなぐ第5のトランジスタと、

前記バッファ部の入力と前記第2のクロック信号とを接続する第1の容量とで構成される

ことを特徴とする請求項1に記載のシフトレジスタ回路。

**【請求項3】**

前記タイミング生成部が、

前記第1のゲート制御回路の入力によりゲート制御され、前記第1の電源と前記バッファ部の入力とをつなぐ第6のトランジスタと、

前記バッファ部の入力と第2の電源とをつなぎ、ゲート端子を前記第2の電源に接続した第7のトランジスタとで構成される

ことを特徴とする請求項1に記載のシフトレジスタ回路。

**【請求項4】**

单一導電型トランジスタで構成されたシフトレジスタ回路であって、

出力端子と第1の電源とをつなぐ第1の出力トランジスタを有するシフトレジスタ部と

前記第1の出力トランジスタのゲート端子にその出力端子が接続された第1のゲート制御回路とを含み、

前記第1のゲート制御回路が、タイミング生成部とバッファ部とで構成され、

前記バッファ部は、ブーストストラップ回路であり、

入力信号が入力される前記タイミング生成部の出力を前記バッファ部の入力とし、前記バッファ部の出力を前記第1のゲート制御回路の出力としており、

前記シフトレジスタ部が、

ソース端子に前記シフトレジスタ回路の出力端子を接続し、ドレイン端子に第2の電源を接続した第8の出力トランジスタと、

ゲート端子に第1のクロック信号を入力し、ドレイン端子に前記入力信号とは異なる別の入力信号を入力し、ソース端子を前記第8の出力トランジスタのゲート端子に接続した第9のトランジスタとを含む

ことを特徴とするシフトレジスタ回路。

**【請求項5】**

单一導電型トランジスタで構成されたシフトレジスタ回路であって、

出力端子と第1の電源とをつなぐ第1の出力トランジスタを有するシフトレジスタ部と

前記第1の出力トランジスタのゲート端子にその出力端子が接続された第1のゲート制御回路とを含み、

前記第1のゲート制御回路が、タイミング生成部とバッファ部とで構成され、

前記バッファ部は、ブーストストラップ回路であり、

入力信号が入力される前記タイミング生成部の出力を前記バッファ部の入力とし、前記バッファ部の出力を前記第1のゲート制御回路の出力としており、

前記シフトレジスタ部が、前記出力端子と前記第1の電源とをつなぐ第10の出力トランジスタを含み、

前記第10の出力トランジスタのゲート端子にその出力端子が接続された第2のゲート制御回路を含み、

前記第2のゲート制御回路が、タイミング生成部とバッファ部とで構成され、

入力信号が入力される前記タイミング生成部の出力を前記バッファ部の入力とし、前記バッファ部の出力を前記第2のゲート制御回路の出力とする

ことを特徴とするシフトレジスタ回路。

**【請求項6】**

請求項5に記載のシフトレジスタ回路を複数段連結させたゲートドライバであって、

第n-2(nは3以上の整数)段目の前記シフトレジスタ回路の出力を第n-1段目の

10

20

30

40

50

前記シフトレジスタ部および前記第1又は第2のゲート制御回路の入力とし、

第n-1段目の前記第1又は第2のゲート制御回路の出力を、第n-1段目の前記シフトレジスタ部および第n段目の前記シフトレジスタ部の入力とする

ことを特徴とするゲートドライバ。

**【請求項7】**

前記第1のゲート制御回路の前記バッファ部が、少なくとも、第2の出力を有し、

前記バッファ部の第2の出力と前記第1の電源とをつなぐ第11のトランジスタと、

前記バッファ部の第2の出力と前記バッファ部の第1の出力とをつなぐ第12のトランジスタと、

前記第12のトランジスタのゲート端子と第n+2段目のシフトレジスタの出力をつなぐ第13のトランジスタとを含み、

前記第11のトランジスタが前記第2のクロック信号に制御され、

前記第13のトランジスタが第2の電源で制御されるブーストストラップ回路である

ことを特徴とする請求項1に記載のシフトレジスタ回路。

**【請求項8】**

前記第1の出力トランジスタのゲート端子にその第2の出力端子が接続された請求項7

に記載の第1のゲート制御回路を含む

ことを特徴とするシフトレジスタ回路。

**【請求項9】**

請求項7に記載のシフトレジスタ回路を複数段連結させたゲートドライバであって、

第n-2(nは3以上の整数)段目の前記シフトレジスタ回路の出力を第n-1段目の

前記シフトレジスタ部および前記第1のゲート制御回路の入力とし、

第n+2段目の前記シフトレジスタ回路の出力を前記第n-1段目の第1のゲート制御

回路の入力とし、

前記第n-1段目のゲート制御回路の前記第1の出力を、第n-1段目の前記シフトレジスタ部および第n段目の前記シフトレジスタ部の入力とし、

第n-1段目の前記第1のゲート制御回路の前記第2の出力を、第n段目の前記シフトレジスタ部の入力とする

ことを特徴とするゲートドライバ。

**【請求項10】**

請求項6または請求項9に記載のゲートドライバを搭載したマトリクス型表示装置であつて、

複数のゲート線と複数のデータ線との交差部に画素素子を配置した表示部を備え、

前記ゲートドライバの出力を前記ゲート線に接続し、

前記ゲート線の複数本を同時に選択する期間を有するオーバーラップ走査とし、

前記ゲート線の選択期間がスタート信号のパルス幅により制御される

ことを特徴とする表示装置。

**【請求項11】**

单一導電型トランジスタで構成されたシフトレジスタ回路であって、

出力端子と第1の電源とをつなぐ第1の出力トランジスタを有するシフトレジスタ部と

、

前記第1の出力トランジスタのゲート端子にその出力端子が接続された第1のゲート制御回路とを含み、

前記第1のゲート制御回路が、タイミング生成部とバッファ部とで構成され、

前記バッファ部は、ブーストストラップ回路であり、

入力信号が入力される前記タイミング生成部の出力を前記バッファ部の入力とし、前記

バッファ部の出力を前記第1のゲート制御回路の出力としており、

前記バッファ部が、少なくとも、

前記バッファ部の出力と第1のクロック信号とをつなぐ第2のトランジスタと、

前記第2のトランジスタのゲート端子と前記タイミング生成部の出力とをつなぐ第3の

10

20

30

40

50

トランジスタとで構成されたブートストラップ回路であり、

前記第1のゲート制御回路の前記バッファ部が、少なくとも、第2の出力を有し、

前記バッファ部の第2の出力と前記バッファ部の第1の出力とをつなぐ第12のトランジスタと、

前記第12のトランジスタのゲート端子と第n+2段目のシフトレジスタの出力とをつなぐ第13のトランジスタとを含み、

前記第13のトランジスタが第2の電源で制御されるブートストラップ回路であることを特徴とするシフトレジスタ回路。

#### 【発明の詳細な説明】

##### 【技術分野】

10

##### 【0001】

本発明は、シフトレジスタ回路及び当該シフトレジスタ回路を備えるゲートドライバ並びに当該ゲートドライバを搭載した表示装置に関する。

##### 【背景技術】

##### 【0002】

スイッチ素子としてトランジスタをマトリクス状に配列したアクティブマトリクス型半導体装置は、小型、低電力で信頼性の高い装置を実現できるため、広く利用されている。例えば、液晶やEL（エレクトロルミネッセンス）材料を用いた表示装置やフォトダイオードなどの受光素子を備えたセンサー装置は、薄型、軽量などの特性から、携帯型情報端末機器などの入出力インターフェースとして広く活用されている。近年では、表示画素を駆動するスイッチ素子や微弱な感受信号を増幅する素子として薄膜トランジスタ（TFT：Thin Film Transistor）を絶縁基板であるアレイ基板に配置するとともに、アレイ配置されたTFTを駆動する周辺回路、例えば走査線駆動回路や信号線駆動回路をスイッチ素子と同じ基板上にTFTで形成するアクティブマトリクス型装置の開発が盛んである。その特徴は、アレイ基板に周辺回路を集積化することで、表示または感受部アクティブマトリクスの有効面積を広げることができ、また周辺回路に要していたコストを削減することができるのことである。

20

##### 【0003】

前出のアレイ配置されたTFTはN型あるいはP型の単一導電性トランジスタであることが多く、周辺回路についても同じ単一導電性トランジスタのみで構成すると、その製造工程においてマスク露光や不純物注入などの工程をアレイ配置されたTFTと共に通化することが可能なため、製造コストの低減につながる。周辺回路のうち、走査線駆動回路（ゲートドライバ）を単一導電性トランジスタのみで構成したシフトレジスタの連結により実現した例は特許文献1に開示されている。

30

##### 【0004】

近年の表示画面の大型化高精細化に伴い、ゲート線の持つ負荷容量、負荷抵抗は増加し、一方でゲート線を選択している時間、一般には1水平期間は短縮しているため、ゲートドライバのゲート線駆動能力への要求が高まっている。それに対して、複数のゲート線で選択期間を重ねるオーバーラップ走査を実施することで選択期間を延ばし、駆動能力要求を緩和する方法が特許文献1や2に開示されている。その方法は、非オーバーラップのクロック信号CLK1とCLK3の2相クロックで動作する第1のゲートドライバと、非オーバーラップのクロック信号CLK2とCLK4の2相クロックで動作する第2のゲートドライバとを独立に設け、CLK1、CLK3とCLK2、CLK4の間にオーバーラップ区間を与えることで実現している。ここでゲートドライバはN型トランジスタのみで構成されている。しかしながら、特許文献1や2に開示されている方法では、複数のゲート線の選択期間をオーバーラップして各々のゲート線を選択している期間を延ばすためには、クロック信号の数を増やしていく必要がある。

40

##### 【0005】

また、オーバーラップ走査において、ゲート選択開始、すなわち単一導電性をN型とした場合のゲート線電圧の立ち上げに時間が掛かり遅延することは、ゲート選択期間の延長

50

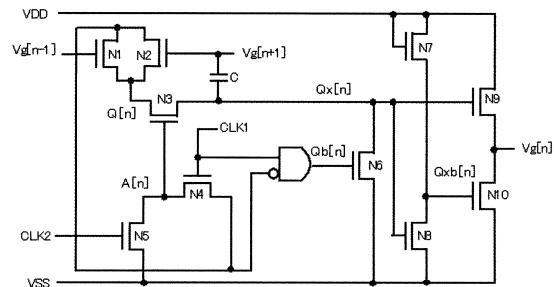

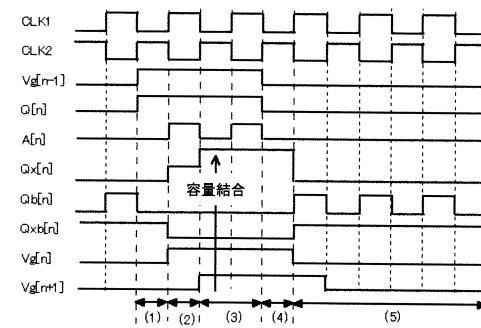

により緩和される。一方で、ゲート選択終了、すなわちゲート線電圧の立ち下げについては、遅延を緩和させる効果がなく、画素に書き込むデータ電圧の切り換わり（データアイドリング）時間を超えて立ち下げ時間が遅延すると、データクロストーク、すなわち次の画素に書き込まれるデータ電圧と混同した電圧が書き込まれる問題が発生してしまう。非特許文献1には、クロック信号を2相のみでオーバーラップ走査を実行するゲートドライバが開示されている。図17はこの従来のゲートドライバのシフトレジスタ回路の回路図、図18はこのシフトレジスタ回路の動作波形を示すタイミングチャート図である。図17に示すように、ゲートドライバ出力の立ち下げを、出力トランジスタN10とそれを制御するインバータ（トランジスタN7とN8とで構成）により行っている。ここで示されたインバータは、トランジスタN7とN8を介して、電源VDDからVSSに貫通電流が流れれる課題がある。特にゲートドライバ出力の立ち下げを高速に行うためには、トランジスタN10、N7、N8のすべてを、大電流を流せるように大きなサイズ（トランジスタチャネル幅）で構成する必要があり、貫通電流が消費電力の増大を招く。

#### 【先行技術文献】

##### 【特許文献】

###### 【0006】

【特許文献1】特開2006-106394号公報

【特許文献2】WO2012/073467号公報

【特許文献3】特開2009-181612号公報

【特許文献4】特開2008-299941号公報

##### 【非特許文献】

###### 【0007】

【非特許文献1】Eunji Song and Hyoungsik Nam、SID2013 Digest、35.4 (2013)

##### 【発明の概要】

##### 【発明が解決しようとする課題】

###### 【0008】

単一導電性トランジスタのみで構成されるゲートドライバで、オーバーラップ走査を行うためにクロック信号数が増加すると、クロックバスラインの駆動に必要な消費電力の増加、端子数の増加、高振幅のクロック信号を生成するレベルシフト回路の増加が課題となる。また、ゲート線の選択を終了するゲート線電圧の立ち下げを高速に行うための消費電力の増加も課題となる。

###### 【0009】

本発明は、高速動作及び低消費電力を実現できる、単一導電性トランジスタで構成されたシフトレジスタ回路及びゲートドライバ並びに表示装置を提供することを目的とする。特に、クロック信号数を増やすずにオーバーラップ走査を行い、無効な貫通電流を回避した省電力の、単一導電性トランジスタで構成されたシフトレジスタ回路及びゲートドライバ並びに表示装置を提供することを目的とする。

##### 【課題を解決するための手段】

###### 【0010】

第1の発明のシフトレジスタ回路は、単一導電型のトランジスタで構成されたシフトレジスタ回路であり、少なくとも前記シフトレジスタ回路の出力端子と第1の電源VSSとをつなぐ第1の出力トランジスタM1を有するシフトレジスタ部と、前記第1の出力トランジスタM1のゲート端子にその出力端子が接続された第1のゲート制御回路とを含み、前記第1のゲート制御回路が、タイミング生成部とバッファ部とで構成され、前記バッファ部がブーストストラップ回路であり、入力O[n-2]が入力される前記タイミング生成部の出力をバッファ部の入力とし、バッファ部の出力を第1のゲート制御回路の出力とするシフトレジスタ回路である。

###### 【0011】

第2の発明のシフトレジスタ回路では、前記第1のゲート制御回路の前記バッファ部が、少なくとも、第1のクロック信号XCLKと出力Q[n]とをつなぐ第2のトランジス

10

20

30

40

50

タM11と、前記第2のトランジスタM11のゲート端子と前記タイミング生成部の出力端子とをつなぐ第3のトランジスタM12とで構成されたブーストストラップ回路である。

#### 【0012】

第3の発明のシフトレジスタ回路では、前記第1のゲート制御回路のバッファ部が、少なくとも、前記バッファ部の出力Q[n]と前記第1のクロック信号XCLKとをつなぐ第2のトランジスタM11と、前記バッファ部の入力Q1と第2のトランジスタM11のゲート端子Q2とをつなぎ、第2のクロック信号CLKによりゲート制御される第3のトランジスタM12と、前記バッファ部の出力Q[n]と第1の電源VSSとをつなぎ、前記第2のクロック信号CLKによりゲート制御される第4のトランジスタM13とを含む。

10

#### 【0013】

第4の発明のシフトレジスタ回路では、前記第1のゲート制御回路のタイミング生成部が、前記第1のゲート制御回路の入力O[n-2]によりゲート制御され、前記第1の電源VSSと前記バッファ部の入力Q1とをつなぐ第5のトランジスタM14と、前記バッファ部の入力Q1と前記第2のクロック信号CLKとをつなぐ第1の容量C1とで構成される。

#### 【0014】

第5の発明のシフトレジスタ回路では、前記第1のゲート制御回路のタイミング生成部が、前記第1のゲート制御回路の入力O[n-2]によりゲート制御され、前記第1の電源VSSと前記バッファ部の入力Q1とをつなぐ第6のトランジスタM15と、前記バッファ部の入力Q1と前記第2の電源VDDとをつなぎ、ゲート端子を前記第2の電源VDDに接続した第7のトランジスタM16とで構成される。

20

#### 【0015】

第6の発明のシフトレジスタ回路では、前記シフトレジスタ部が、ソース端子に前記シフトレジスタ回路の出力端子を接続し、ドレイン端子に前記第2の電源VDDを接続した第8の出力トランジスタM2と、ゲート端子に前記第1のクロック信号XCLKを入力し、ドレイン端子に入力O[n-1]を接続し、ソース端子を前記第8の出力トランジスタM2のゲート端子P[n]に接続した第9のトランジスタM3とを含む。

#### 【0016】

第7の発明のシフトレジスタ回路は、単一導電型のトランジスタで構成されたシフトレジスタ回路であり、少なくとも、前記シフトレジスタ回路の出力端子と第1の電源VSSとをつなぐ第1の出力トランジスタM1を有するシフトレジスタ部と、前記第1の出力トランジスタM1のゲート端子にその出力端子が接続された第1のゲート制御回路とを含み、前記シフトレジスタ部が、前記シフトレジスタの出力端子と前記第1の電源VSSとをつなぐ第10の出力トランジスタM4を含み、第10の出力トランジスタM4のゲート端子にその出力端子が接続された第2のゲート制御回路を含み、前記各ゲート制御回路が、タイミング生成部とバッファ部とで構成され、入力O[n-2]又は入力O[n-1]が入力される前記タイミング生成部の出力をバッファ部の入力とし、バッファ部の出力を第2のゲート制御回路の出力とするシフトレジスタ回路である。

30

#### 【0017】

第8の発明のシフトレジスタ回路では、前記第1のゲート制御回路を構成するバッファ部が前記第1のクロック信号を出力するブーストストラップ回路であり、前記第2のゲート制御回路を構成するバッファ部が前記第2のクロック信号を出力するブーストストラップ回路である。

40

#### 【0018】

第9の発明のゲートドライバは、前記第7の発明のシフトレジスタ回路を複数段つなげたゲートドライバであり、第n-2(nは3以上の整数)段目の前記シフトレジスタ回路の出力O[n-2]を第n-1段目の前記シフトレジスタ部および前記第1又は第2のゲート制御回路の入力とし、第n-1段目の前記第1又は第2のゲート制御回路の出力Q[n]を、前記第n-1段目の前記シフトレジスタ部および第n段目の前記シフトレジスタ

50

部に入力する（第 $n - 1$ 段目の前記シフトレジスタ回路の出力 $O[n - 1]$ を第 $n$ 段目の前記シフトレジスタ部および前記第2又は第1のゲート制御回路の入力とし、第 $n$ 段目の前記第2又は第1のゲート制御回路の出力 $Q[n + 1]$ を、前記第 $n$ 段目の前記シフトレジスタ部および第 $n + 1$ 段目の前記シフトレジスタ部に入力する）ゲートドライバである。

#### 【0019】

第10の発明のシフトレジスタ回路では、前記第1のゲート制御回路を構成するバッファ部が、少なくとも、第2の出力 $Q_2[n]$ を有し、出力 $Q_2[n]$ と前記第1の電源 $V_{SS}$ とをつなぐ第11の出力トランジスタM17と、出力 $Q_2[n]$ と前記出力 $Q[n]$ とをつなぐ第12のトランジスタM18と、前記第12のトランジスタM18のゲート端子と第 $n + 2$ 段目のシフトレジスタの出力をつなぐ第13のトランジスタM19とを含み、前記第11の出力トランジスタM17が前記第2のクロック信号 $C_{LK}$ に制御され、前記第13のトランジスタM19が前記第2の電源 $V_{DD}$ で制御されるブーストストラップ回路であり、このブーストストラップ回路を前記第3の発明のバッファ部に追加している。

10

#### 【0020】

第11の発明のシフトレジスタ回路では、前記第1の出力トランジスタM1のゲート端子に、第10の発明のゲート制御回路の第2の出力 $Q_2[n]$ を接続している。

#### 【0021】

第12の発明のゲートドライバは、前記第10の発明のシフトレジスタ回路を複数段連結させたゲートドライバであり、第 $n - 2$ （ $n$ は3以上の整数）段目の前記シフトレジスタ回路の出力 $O[n - 2]$ を第 $n - 1$ 段目の前記シフトレジスタ部および前記第10の発明のゲート制御回路の入力とし、第 $n + 2$ 段目の前記シフトレジスタ回路の出力 $O[n + 2]$ を前記第 $n - 1$ 段目のゲート制御回路の入力とし、前記第 $n - 1$ 段目のゲート制御回路の第1の出力を、第 $n - 1$ 段目の前記シフトレジスタ部および第 $n$ 段目の前記シフトレジスタ部の入力とし、前記第 $n - 1$ 段目のゲート制御回路の第2の出力を、第 $n$ 段目の前記シフトレジスタ部の入力とするゲートドライバである。

20

#### 【0022】

第13の発明の表示装置は、前記第9又は第12の発明のゲートドライバを搭載したマトリクス型表示装置であり、ゲートドライバには2相のクロック信号を入力し、ゲートドライバの初段のシフトレジスタの入力としてスタート信号 $S_T$ を入力し、ゲート線の選択期間がスタート信号 $S_T$ のパルス幅により制御され、同時に複数のゲート線が重なって選択されるオーバーラップ走査とする表示装置である。

30

#### 【発明の効果】

#### 【0023】

本発明のシフトレジスタ回路では、各シフトレジスタの出力パルスの幅は、クロック信号のパルス幅ではなく、入力パルス、例えば、前段のシフトレジスタ回路の出力パルスの幅で決まる。そのため、シフトレジスタ回路を複数段連結してゲートドライバを構成した際、オーバーラップ走査でもクロック信号は2相で良い。

#### 【0024】

本発明によれば、高速かつ、低消費電力なゲートドライバが実現される。なぜならば、ゲート線の電位を高速に立ち下げるための出力トランジスタのゲート制御を、バッファ部であるクロック駆動のブーストストラップ回路で行うため、大きな負荷の駆動を、貫通電流などの消費電力を回避して高速に行うことができるからである。また、ゲート制御回路を省面積とすることができます。なぜならば、ブーストストラップ回路をバッファ部とするため、ゲート制御回路を構成するタイミング生成部のトランジスタサイズや容量サイズを小さくできるからである。また、ブーストストラップ回路を駆動するクロック信号は外部入力信号とすることで、高速動作が可能となる。

40

#### 【0025】

また、本発明によれば、ゲート制御回路のうちタイミング生成部のタイミングマージンを拡大でき、高速動作の要求を緩和できる。なぜならば、タイミング生成部の信号の伝達

50

には、クロック半周期期間のタイミングマージンが与えられ、タイミング生成部の出力立ち上がり時間が直接シフトレジスタ回路の出力立下り時間に反映しないからである。

#### 【0026】

また、本発明によれば、トランジスタの閾値シフトによる信頼性低下を抑えることができる。なぜならば、出力トランジスタのゲート端子には、ゲート制御回路により、2相のクロック信号に同期した電圧が印加されるため、出力トランジスタの長期間導通状態を避け、閾値シフトを緩和できるからである。

#### 【0027】

また、本発明によれば、クロック信号の負荷および消費電力を抑えることができる。なぜならば、ゲート制御回路の出力Q<sub>2[n]</sub>の反転は、1本のゲート線が駆動される、1フレームに1回程度に限られるからである。すなわちQ<sub>2[n]</sub>にゲート端子を制御される出力トランジスタM<sub>1</sub>のゲート負荷容量の充放電回数が限られ、その充放電を行うクロック信号の負荷および消費電力が抑えられる。

#### 【0028】

本発明のゲートドライバを搭載したマトリクス型表示装置では、狭額縁の表示装置が可能となる。なぜならば、表示画面の周辺に配置するゲートドライバの構成要素であるタイミング生成部を省面積にすることができ、ゲートドライバを駆動するクロック信号線が2本であるため、その配線レイアウト面積を小さくできるからである。

#### 【0029】

本発明のマトリクス型表示装置では、ゲート電位の高振幅を有するクロック信号が2本と少ないため、高振幅信号を生成するレベルシフト回路の個数を低減し、部材コストを抑えることができる。

#### 【図面の簡単な説明】

#### 【0030】

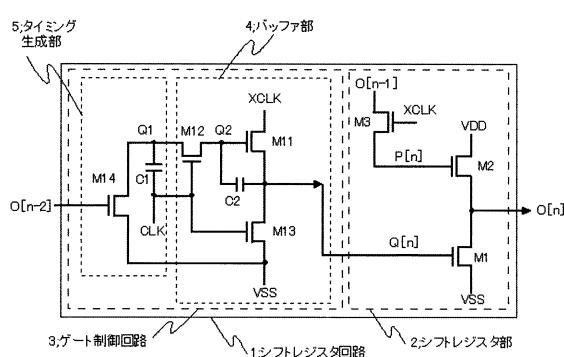

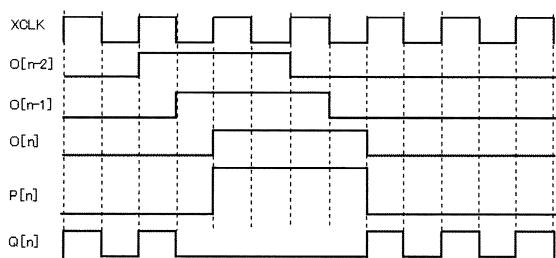

【図1】本発明の第1の実施の形態のシフトレジスタ回路の回路図である。

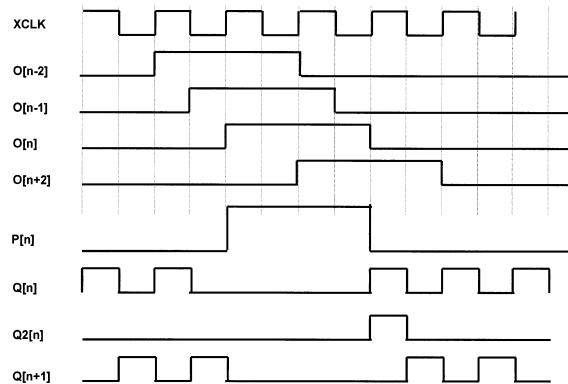

【図2】本発明の第1の実施の形態のシフトレジスタ回路の動作波形を示すタイミングチャート図である。

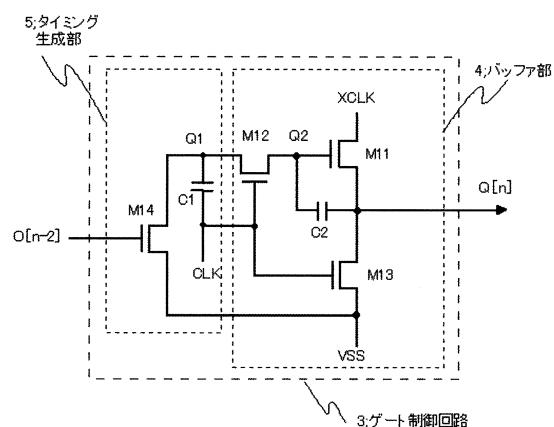

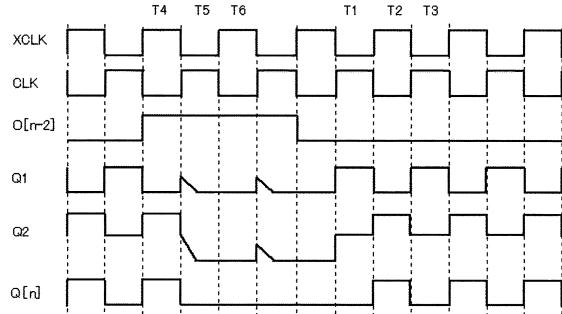

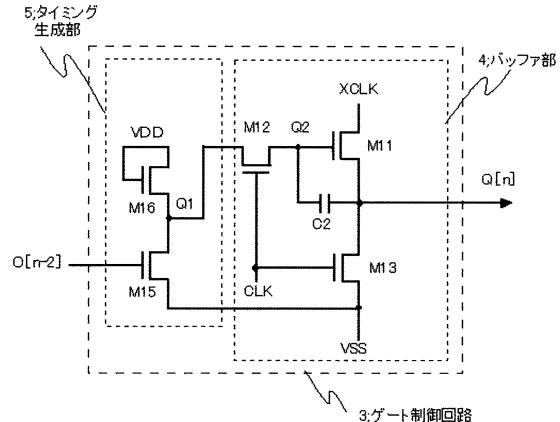

【図3】本発明の第1の実施の形態のゲート制御回路の回路図である。

【図4】本発明の第1の実施の形態のゲート制御回路の動作波形を示すタイミングチャート図である。

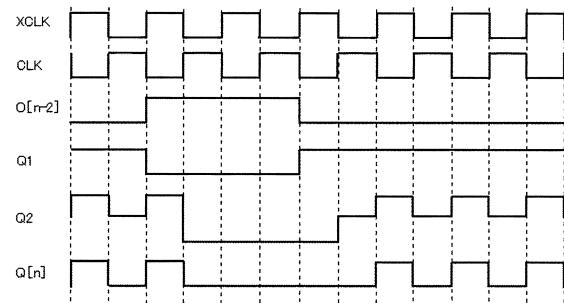

【図5】本発明の第2の実施の形態のゲート制御回路の回路図である。

【図6】本発明の第2の実施の形態のゲート制御回路の動作波形を示すタイミングチャート図である。

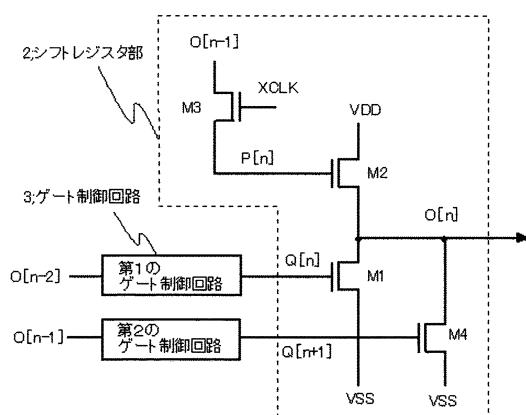

【図7】本発明の第3の実施の形態のシフトレジスタ回路の回路図である。

【図8】本発明の第3の実施の形態のシフトレジスタ回路の動作波形を示すタイミングチャート図である。

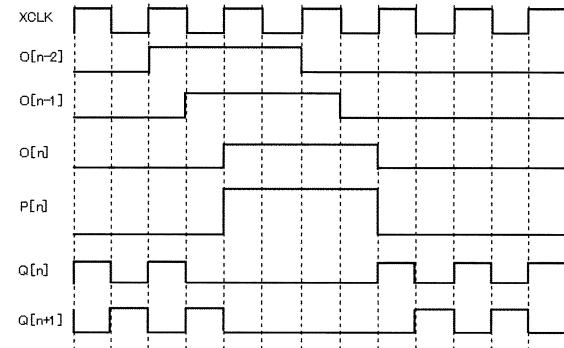

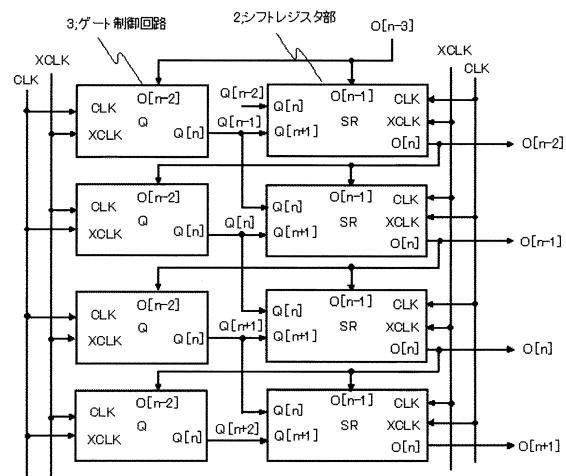

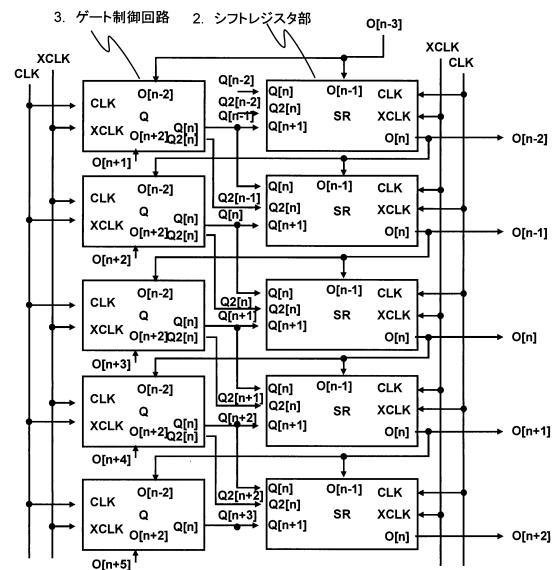

【図9】本発明の第4の実施の形態のゲートドライバの回路図である。

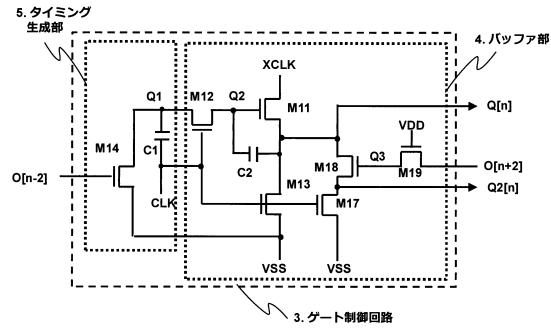

【図10】本発明の第5の実施の形態のゲート制御回路の回路図である。

【図11】本発明の第5の実施の形態のゲート制御回路の動作波形を示すタイミングチャート図である。

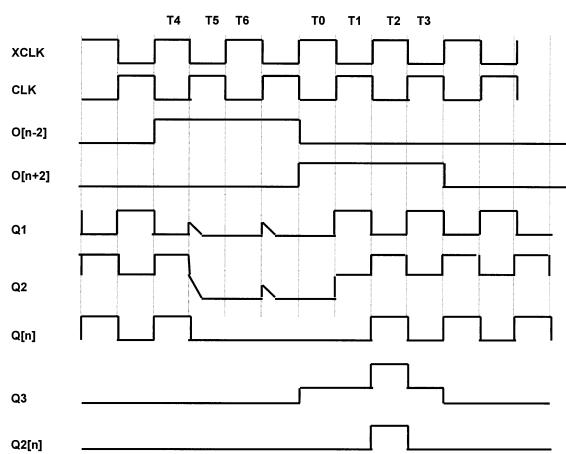

【図12】本発明の第6の実施の形態のシフトレジスタ回路の回路図である。

【図13】本発明の第6の実施の形態のシフトレジスタ回路の動作波形を示すタイミングチャート図である。

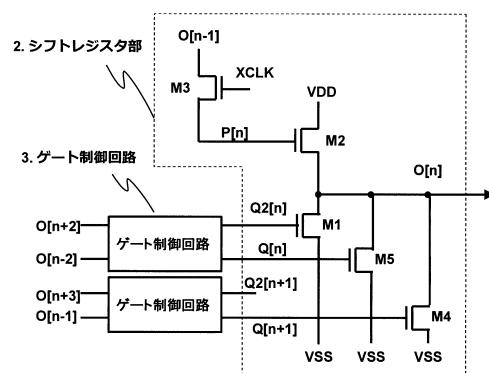

【図14】本発明の第7の実施の形態のゲートドライバの回路図である。

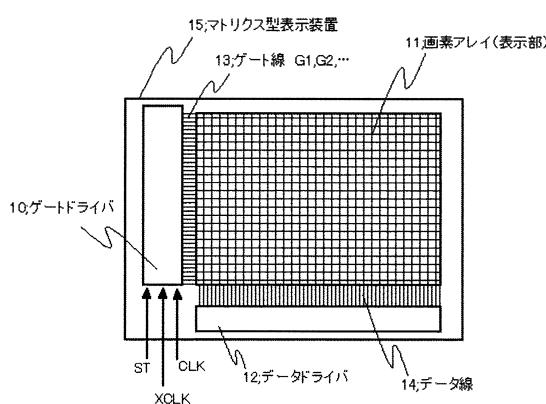

【図15】本発明の第8の実施の形態のマトリクス型表示装置を示す図である。

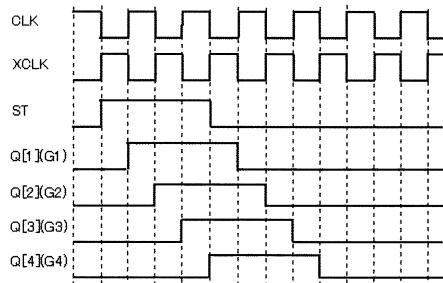

【図16】本発明の第8の実施の形態のマトリクス型表示装置におけるゲートドライバの動作波形を示すタイミングチャート図である。

【図17】従来のシフトレジスタ回路の回路図である。

【図18】従来のシフトレジスタ回路の動作波形を示すタイミングチャート図である。

#### 【発明を実施するための形態】

10

20

30

40

50

**【0031】**

次に、本発明の実施の形態について図面を参照して詳細に説明する。

**【0032】****[第1の実施の形態]**

図1は、第1の実施の形態のシフトレジスタ回路の構成を示す図である。図1に示すように、本実施の形態のシフトレジスタ回路1は、単一導電型（本実施の形態ではN型）トランジスタで構成されたシフトレジスタ回路であって、第1の電源VSSとシフトレジスタ回路1の出力O[n]とを結ぶ出力トランジスタM1、第2の電源VDDとシフトレジスタ回路1の出力O[n]とを結ぶ出力トランジスタM2、出力トランジスタM2のゲート端子でブートストラップノードの出力P[n]と前段のシフトレジスタ回路の出力O[n-1]とを結ぶトランジスタM3から構成されるシフトレジスタ部2、および出力トランジスタM1のゲート端子にその出力を接続したゲート制御回路3からなる。ゲート制御回路3は、タイミング生成部5とバッファ部4にて構成される。

10

**【0033】**

シフトレジスタ回路1の動作を説明するために動作波形を図2に示す。シフトレジスタ回路1の出力O[n-1]がロウレベルであると、クロック信号XCLKのレベルがロウからハイに反転した際、ブートストラップノードの出力P[n]は、トランジスタM3によりロウレベルに固定され、出力トランジスタM2は非導通になる。一方、ゲート制御回路3の出力Q[n]がハイレベルとなるとき、出力トランジスタM1が導通して、シフトレジスタ回路1の出力O[n]はロウレベル（第1の電源VSS）に固定される。

20

**【0034】**

シフトレジスタ回路1の出力O[n-1]がハイレベルに反転した後、クロック信号XCLKがハイレベルに反転すると、ノードの出力P[n]はハイレベルに向かって上昇し、出力トランジスタM2のゲート・ソース間電圧を広げ、それにより出力トランジスタM2が導通状態となる。すると、第2の電源VDDからの電流供給により、シフトレジスタ回路1の出力O[n]のレベルが第2の電源VDDまで上昇し、ブートストラップ効果により、ノードの出力P[n]の電位は第2の電源VDD以上にまで達する。このとき、出力の上昇を妨害せず、第2の電源VDDから第1の電源VSSへの貫通電流を流さないように、出力トランジスタM1は非導通状態であることが望ましく、ゲート制御回路3の出力Q[n]がロウレベルを保つようにタイミング生成部5で信号を生成する。

30

**【0035】**

再びシフトレジスタ回路1の出力O[n-1]がロウレベルに反転した後、クロック信号XCLKがハイレベルに反転すると、ノードの出力P[n]はロウレベルに固定されるため、出力トランジスタM2は非導通になる。一方、ゲート制御回路3の出力Q[n]がハイレベルに再び反転することで、出力トランジスタM1を介してシフトレジスタ回路1の出力O[n]はロウレベルである第1の電源VSSまで立ち下げられる。

**【0036】**

次に、本実施の形態のゲート制御回路3について、図3を用いて詳細に説明する。

**【0037】**

まず、ゲート制御回路3を構成するバッファ部4について説明する。バッファ部4は、少なくとも、ゲート制御回路3の出力Q[n]とクロック信号XCLKとをつなぐトランジスタM11と、バッファ部4の入力端子Q1とトランジスタM11のゲート端子Q2とをつなぎ、クロック信号CLKによりゲート制御されるトランジスタM12と、ゲート制御回路3の出力Q[n]と第1の電源VSSとをつなぎ、クロック信号CLKによりゲート制御されるトランジスタM13とで構成されるブートストラップ回路である。ここで、クロック信号XCLKとCLKとは互いに相反する2相のクロック信号である。なお、トランジスタM11のブートストラップ効果を高めるために、トランジスタM11のゲート・ソース端子間に容量C2を設けても良い。

40

**【0038】**

次に、ゲート制御回路3を構成するタイミング生成部5について説明する。タイミング

50

生成部5は、ゲート制御回路3の入力O[n-2]によりゲート制御され、第1の電源VSSとタイミング生成部5の出力Q1とをつなぐトランジスタM14と、タイミング生成部5の出力Q1とクロック信号CLKとをつなぐ容量C1とで構成される。

#### 【0039】

図3に示したゲート制御回路3の動作について、図4に示した動作波形を基に以下に説明する。ゲート制御回路3の入力、すなわち、前々段のシフトレジスタ回路の出力O[n-2]がロウレベルであるとき、タイミング生成部5の出力Q1は、容量C1によるカップリングでクロック信号CLKに同期する。クロック信号CLKとタイミング生成部5の出力Q1とがハイレベルにある期間T1では、トランジスタM12を介してトランジスタM11のゲートQ2はハイレベルよりもトランジスタM12の閾値電圧程度低い電位まで引き上げられる。この電位は容量C2により保持される。一方、クロック信号XCLKはロウレベルであるから、トランジスタM11を介してゲート制御回路3の出力Q[n]はロウレベルに固定される。同様に、トランジスタM13によつても、ゲート制御回路3の出力Q[n]はロウレベルに固定される。

10

#### 【0040】

次にクロック信号が反転し、CLKがロウレベルに、XCLKがハイレベルに変わる期間T2に移ると、トランジスタM12およびM13は非導通状態となる。一方で、容量C2およびトランジスタM11のゲート・ソース間容量に保持された電位差によってトランジスタM11は導通状態を保ち、ブートストラップ効果によりトランジスタM11のゲートQ2の電位はクロック信号のハイレベル以上に上昇し、ゲート制御回路3の出力Q[n]はクロック信号XCLKのハイレベルまで上昇する。そして、再びクロック信号が反転する期間T3に移ると、トランジスタM11およびM13により、ゲート制御回路3の出力Q[n]はロウレベルに引き下げられる。すなわち、バッファ部4は、クロック信号XCLKをトランジスタM11を介して出力するブートストラップ回路として働く。この動作は、前々段のシフトレジスタ回路の出力O[n-2]がロウレベルである間、繰り返される。

20

#### 【0041】

一方、前々段のシフトレジスタ回路の出力O[n-2]がハイレベルとなる期間T4に入ると、トランジスタM14が導通し続けるため、タイミング生成部5の出力Q1はクロック信号CLKには同期せず、ロウレベルに固定される。クロック信号CLKがハイレベルとなる期間T5では、トランジスタM12を介してバッファ部4のノードQ2はロウレベルに固定される。よつて、トランジスタM11のドレイン端子であるクロック信号XCLKはロウレベル、ソース端子であるゲート制御回路3の出力Q[n]もロウレベルであるが、ゲート端子であるQ2もロウレベルであるため、トランジスタM11は非導通状態を保つ。また、トランジスタM11のゲート・ソース間、ゲート・ドレイン間の容量にも電荷は充電されていない。そのため、期間T6に移り、クロック信号XCLKが反転し、ハイレベルに上昇した際にもブートストラップ効果は働かず、トランジスタM11のゲート端子Q2およびソース端子はクロック信号CLKに追従しない。この動作は、前々段のシフトレジスタの出力O[n-2]がハイレベルである間継続し、ゲート制御回路3の出力Q[n]はロウレベルのままである。また、クロック信号CLKがハイレベルに反転する期間T5において、容量C1との結合のために瞬間にノードQ1が上昇し、あるいは容量C2に充電されていた電荷を放電し、ノードQ2をロウレベルへ低下させる動作が緩やかであったとしても、期間T6に移る前までにそれぞれをロウレベルに低下させておけば、期間T6ではブートストラップ効果は働かない。

30

40

#### 【0042】

図3に示したゲート制御回路3の出力Q[n]は、図1に示したゲート制御回路3の出力Q[n]に合致しており、n番目のシフトレジスタ回路の出力O[n]がハイレベルに上昇する際に、それを阻害しないように、出力トランジスタM1を非導通とする、所望の波形となる。また、同波形は図3に示したタイミング生成部5により生成され、タイムシフトされた結果である。

50

## 【0043】

このように、ゲート線の電位を高速に立ち下げるための出力トランジスタのゲート制御を、バッファ部であるクロック駆動のブートストラップ回路で行うため、大きな負荷の駆動を、貫通電流などの消費電力を回避して高速に行うことができる。また、ブートストラップ回路をバッファ部とするため、ゲート制御回路3を構成するタイミング生成部5のトランジスタサイズや容量サイズを小さくでき、ゲート制御回路3を省面積とすることができます。また、ブートストラップ回路を駆動するクロック信号を外部入力信号とすることで、高速動作が可能となる。

## 【0044】

## [第2の実施の形態]

10

次に、本発明の第2の実施の形態について図5を用いて説明する。第1の実施の形態との違いは、タイミング生成部5の構成にある。タイミング生成部5は、ゲート制御回路3の入力O[n-2]によりゲート制御され、第1の電源VSSとタイミング生成部5の出力Q1とをつなぐトランジスタM15と、タイミング生成部5の出力Q1と第2の電源VDDとをつなぎ、そのゲート端子が第2の電源VDDに接続されたトランジスタM16と、で構成される。

## 【0045】

図5に示したゲート制御回路3の動作について、図6に示した動作波形を基に以下に説明する。ゲート制御回路3の入力、すなわち、前々段のシフトレジスタ回路の出力O[n-2]がロウレベルであるとき、タイミング生成部5の出力Q1は、ダイオード接続されたトランジスタM15により、ハイレベルよりもトランジスタM15の閾値電圧分低いハイレベルに保たれる。一方、前々段のシフトレジスタ回路の出力O[n-2]がハイレベルであると、タイミング生成部5の出力Q1はロウレベルに保たれる。すなわち、タイミング生成部5は、ゲート制御回路3の入力O[n-2]の反転信号を出力するインバータとして働く。

20

## 【0046】

タイミング生成部5の出力Q1がハイレベルに保たれ、クロック信号CLKがハイレベルにあると、トランジスタM12を介して、トランジスタM11のゲートQ2はハイレベルよりもトランジスタM12の閾値電圧程度低い電位まで引き上げられる。一方、クロック信号XCLKはロウレベルであるから、トランジスタM11を介してゲート制御回路3の出力Q[n]はロウレベルに固定される。同様に、トランジスタM13によってもロウレベルに固定される。次に、クロック信号が反転し、CLKがロウレベルに、XCLKがハイレベルにそれぞれ変わると、トランジスタM12およびM13は非導通状態となる。一方で、トランジスタM11は導通状態を保ち、ブートストラップ効果により、トランジスタM11のゲートQ2の電位はクロック信号のハイレベル以上に上昇し、ゲート制御回路3の出力Q[n]はクロック信号XCLKのハイレベルまで上昇する。そして、再びクロック信号が反転すると、トランジスタM11およびM13により、ゲート制御回路3の出力Q[n]はロウレベルに引き下げられる。この動作は、前々段のシフトレジスタ回路1の出力O[n-2]がロウレベルである間、繰り返される。

30

## 【0047】

40

一方、タイミング生成部5の出力Q1がロウレベルに保たれると、クロック信号CLKがハイレベルのとき、トランジスタM12を介してバッファ部4のノードQ2はロウレベルに固定される。よって、トランジスタM11のドレイン端子であるクロック信号XCLKはロウレベル、ソース端子であるゲート制御回路3の出力Q[n]もロウレベルであるが、ゲート端子であるQ2もロウレベルであるため、トランジスタM11は非導通状態を保つ。また、トランジスタM11のゲート・ソース間、ゲート・ドレイン間の容量にも電荷は充電されていない。そのため、クロック信号XCLKが反転し、ハイレベルに上昇した際にもブートストラップ効果は働かず、トランジスタM11のゲート端子Q2およびソース端子は追従しない。この動作は、前々段のシフトレジスタ回路1の出力O[n-2]がハイレベルである間継続し、ゲート制御回路3の出力Q[n]はロウレベルのままである

50

る。

#### 【0048】

本実施の形態の特徴は、シフトレジスタ回路1の出力トランジスタのゲートを制御するゲート制御回路3に、クロック駆動のブートストラップ回路をバッファ部4として設けている点である。これにより、ゲート制御回路3は、クロック信号をトランジスタM11を介して、振幅の低減もなく、遅延もなく出力することができる。

#### 【0049】

従来技術で説明した公知例の中には、ゲート制御回路3を本発明のタイミング生成部5のみで構成している例が開示されている。すなわち、図3に示した容量とトランジスタで構成されたタイミング生成部5や、図5に示したインバータを用いたタイミング生成部5を直接シフトレジスタ回路の出力トランジスタのゲートに接続している例が、特許文献3や非特許文献1に開示されている。シフトレジスタ回路1の出力トランジスタM1を駆動する、特に導通させるということは、そのゲート容量負荷Cgの充電を行い、ゲート電位を高電位にすることであり、高速動作にはゲート容量負荷Cgの高速かつ高電位への充電が必要になる。

10

#### 【0050】

特許文献3でも示された容量C1とトランジスタM14で構成されたタイミング生成部5でシフトレジスタ回路1の出力トランジスタM1を直接駆動する場合、ゲート充電電圧の電位劣化が問題となる。すなわち、ゲート充電電位は、タイミング生成部5の容量C1と出力トランジスタM1のゲート容量Cgの分圧比で決まるため、高電圧を得るためにC1 > > Cgが要求される。その容量C1を得るために出力トランジスタM1以上のレイアウト面積が必要となる。

20

#### 【0051】

また、非特許文献1にも示されたインバータ（図5のトランジスタM15とM16）で構成されたタイミング生成部5を用いる場合、消費電流が問題となる。すなわち、ゲート容量負荷Cgを高速に充電するためには、トランジスタM16は大電流を流せるように大きなサイズが必要となる。一方で、トランジスタM15を導通させたときには、トランジスタM16とM15を介して第2の電源VDDと第1の電源VSSとの間に貫通電流が流れれる。また、出力トランジスタM1のゲート電位をロウレベルとするために、トランジスタM16とM15のサイズ関係はM15 > M16が必要となる。よって、共に大きなサイズのトランジスタM15とM16を介して大きな貫通電流が流れることを回避できない。

30

#### 【0052】

同様に、バッファ部4をインバータとした例が、特許文献4の図2に示されている。すなわち、トランジスタT13とT14とで構成されるインバータをバッファ部4とし、トランジスタT11bとT12bとで構成される回路をタイミング生成部5とした例である。ここでの課題は、トランジスタT16のゲート端子に出力B点をつないだインバータでトランジスタT16のゲート容量負荷を高速に充電するために、非特許文献1と同様にインバータに大きな貫通電流が流れれる点である。

#### 【0053】

公知例にあるように、タイミング生成部5の出力で直接シフトレジスタ回路1の出力トランジスタM1のゲートを駆動する場合には、上記の他に高速動作時のタイミングマージンに課題がある。すなわち、タイミング生成部5の入力信号の反転が、直接シフトレジスタ回路1の出力トランジスタのゲート電位の反転につながる。よってタイミング生成部5には動作遅延が許されない。

40

#### 【0054】

一方、本発明の場合、出力トランジスタのゲート電位の反転は、クロック駆動のブートストラップのバッファ部4によって行われる。タイミング生成部5はその半クロック周期前の期間T5で反転動作を行い、バッファ部4が動作する期間T6に移る前までに反転を完了していれば良いため、最大で半クロック周期期間の反転動作マージンが許されている。このように、タイミング生成部5の出力立ち上がり時間が直接シフトレジスタ回路1の

50

出力立下り時間に反映しないため、高速動作の要求を緩和できる。

#### 【0055】

##### [第3の実施の形態]

次に、本発明の第3の実施の形態について図7を用いて説明する。本実施の形態は単一導電型のトランジスタで構成されたシフトレジスタ回路であり、以下のように構成される。シフトレジスタ回路1の出力O[n]と第1の電源VSSとをつなぐ出力トランジスタM1と、シフトレジスタ回路1の出力O[n-2]を入力とし、その出力Q[n]を出力トランジスタ回路1のゲート端子に接続した第1のゲート制御回路3と、シフトレジスタ回路1の出力O[n]と第1の電源VSSとをつなぐ第2の出力トランジスタM4と、シフトレジスタ回路1の出力O[n-1]を入力とし、その出力Q[n+1]を出力トランジスタM4のゲート端子に接続した第2のゲート制御回路3とを含む。さらに、シフトレジスタ回路1の出力O[n]と第2の電源VDDとをつなぐ出力トランジスタM2と、そのゲート端子P[n]とシフトレジスタ回路1の出力O[n-1]とをつなぎ、クロック信号XCLKにてゲート制御されるトランジスタM3にて構成される。ここで、複数段のシフトレジスタ回路1は出力O[n-2]、O[n-1]、O[n]の順に連結されているとする。第1及び第2のゲート制御回路3は、第1又は第2の実施の形態に記載のゲート制御回路3と同様の構成で良い。本実施の形態と第1の実施の形態との違いは、出力トランジスタM4とそれを制御する第2のゲート制御回路3とが追加されている点である。

#### 【0056】

本実施の形態の動作について図8に示した動作波形を用いて説明する。第1のゲート制御回路3の出力Q[n]と第2のゲート制御回路3の出力Q[n+1]は、それぞれの入力信号がロウレベルである間、クロック信号XCLKに同期し、互いに半周期シフトしたクロック信号である。すなわち、第1のゲート制御回路3を構成するバッファ部がクロック信号XCLKを出力するブーストストラップ回路となり、第2のゲート制御回路3を構成するバッファ部がクロック信号CLKを出力するブーストストラップ回路となる。これにより、出力トランジスタM1あるいはM4のいずれか一方が導通状態となるため、シフトレジスタ回路1の出力O[n]はロウレベルに固定されることとなる。一方、入力信号がハイレベルに反転すると、ゲート制御回路3の出力Q[n]とQ[n+1]はロウレベルに固定されるため、シフトレジスタ回路1の出力O[n]は出力トランジスタM1およびM4によりロウレベルに固定されることはない。その間にシフトレジスタ部2の出力トランジスタM2およびM3が機能して、シフトレジスタ回路1の出力O[n]はハイレベルに反転する。その詳細については第1の実施の形態と同様である。

#### 【0057】

本実施の形態により、シフトレジスタ回路1の出力O[n]をハイレベルとする期間以外は、2つのゲート制御回路3により、シフトレジスタ回路1の出力O[n]が安定してロウレベルに固定されるシフトレジスタが提供される。

#### 【0058】

##### [第4の実施の形態]

次に、本発明の第4の実施の形態について図9を用いて説明する。本実施の形態は、第3の実施の形態のシフトレジスタ回路1を複数段連結したゲートドライバ10であり、第n-2段目(nは3以上の整数)のシフトレジスタ回路1の出力O[n-2]を、第n-1段目のシフトレジスタ部2およびゲート制御回路3の入力とし、第n-1段目のゲート制御回路3の出力Q[n]を、第n-1段目のシフトレジスタ部2および第n段目のシフトレジスタ部2それぞれに入力している。すなわち、ゲート制御回路3の出力Q[n]を2つの連続するシフトレジスタ部2で共有している点が特徴である。この構成により、ゲートドライバの回路規模の縮減が図れる。なぜならば、図7に示した1段分のシフトレジスタ回路1では2つのゲート制御回路3を記載しているが、複数の連続するシフトレジスタ回路1間でゲート制御回路3を共有することで、ゲート制御回路3の個数を減らせるからである。

#### 【0059】

10

20

30

40

50

[第5の実施の形態]

次に、本発明の第5の実施の形態について図10を用いて説明する。本実施の形態は、第1の実施形態に示されたゲート制御回路3のバッファ部4に第2の出力Q<sub>2</sub>[n]を追加したゲート制御回路である。以下、図10に示したゲート制御回路3の追加部について説明する。バッファ部4には、少なくとも、ゲート制御回路3の第2の出力Q<sub>2</sub>[n]と第1の電源VSSとをつなぐトランジスタM17と、第2の出力Q<sub>2</sub>[n]と第1の出力Q[n]をつなぐトランジスタM18と、トランジスタM18のゲート端子と第n+2段目のシフトレジスタの出力O[n+2]とをつなぐトランジスタM19が追加され、トランジスタM17のゲート端子はクロック信号CLKにより制御される。

【0060】

10

図10に示したゲート制御回路3の動作について、図11に示した動作波形を基に、以下に説明する。後々段のシフトレジスタ回路の出力O[n+2]がハイレベルとなる期間T0では、トランジスタM19のゲートおよびドレインがハイレベルとなるため、ソース端子であるQ3はハイレベルよりトランジスタM19の閾値電圧程度低い電位まで引き上げられ、トランジスタM18が導通状態となる。ただし、期間T0では第1の出力Q[n]はロウレベルであるため、トランジスタM18を介して第2の出力Q<sub>2</sub>[n]もロウレベルとなる。

【0061】

次に、期間T1に移りクロック信号が反転し、CLKがハイレベルに、XCLKがロウレベルに変わると、トランジスタM13およびM17の導通により、Q[n]およびQ<sub>2</sub>[n]は第1の電源VSSのロウレベルへの固定が継続する。

20

【0062】

次に、期間T2に移りクロック信号が反転し、CLKがロウレベルに、XCLKがハイレベルに変わると、出力Q[n]はクロック信号XCLKのハイレベルまで上昇する。それに伴い、導通状態を保っていたトランジスタM18のソース端子である第2の出力Q<sub>2</sub>[n]もハイレベルまで引き上げられる。その際、ブートストラップ効果により、トランジスタM18のゲート端子であるQ3のレベルはハイレベル以上に上昇するが、トランジスタM19ではその上昇を妨げることができない。なぜならば、トランジスタM19のソース端子が後々段のシフトレジスタ出力O[n+2]へ、ドレン端子がQ3へと入れ替わり、ゲート端子とソース端子が同じハイレベルであるため、トランジスタM19が非導通状態となるからである。

30

【0063】

次に、期間T3に移りクロック信号が反転し、CLKがハイレベルに、XCLKがロウレベルに変わると、トランジスタM13およびM17の導通により、Q[n]およびQ<sub>2</sub>[n]は第1の電源VSSのロウレベルに固定される。

【0064】

期間T3以降では、後々段のシフトレジスタ回路の出力O[n+2]がロウレベルとなるため、トランジスタM19の導通により、トランジスタM18のゲート端子であるQ3はロウレベルに固定され、トランジスタM18が非導通となるため、第2の出力Q<sub>2</sub>[n]は、第1の出力Q[n]に同期してハイレベルに上昇することなく、トランジスタM17とクロック信号CLKにより逐次ロウレベルにリセットされる。

40

【0065】

図10に示したゲート制御回路3の第2の出力Q<sub>2</sub>[n]は、図1に示したシフトレジスタ部のトランジスタM1のゲートに、Q[n]の代わりに用いることができる。すなわちn番目のシフトレジスタ回路の出力O[n]をロウレベルに反転させるよう、出力トランジスタM1を導通とさせるためのゲート信号として、Q<sub>2</sub>[n]は十分な信号である。

【0066】

Q[n]の代わりにQ<sub>2</sub>[n]を用いる利点は、クロック信号の負荷軽減と消費電力の低減である。ゲート線の電位を高速に立ち下げるための出力トランジスタは、チャネルサイズの大きなトランジスタであり、そのゲート容量も大きい。そのため出力トランジスタ

50

のゲート容量負荷を充放電するためには、大きな電力を要する。出力トランジスタのゲート制御に  $Q[n]$  を用いた場合、ゲート線の電位を立ち下げる時以外のタイミング、すなわちゲート線の電位をロウレベルに固定する時にも、クロック信号に同期してゲート容量負荷を充放電することになる。そのための電力はゲート制御回路 3 を通してクロック信号から供給され、クロック信号の負荷が大きくなる。

#### 【0067】

一方、ゲート容量負荷の大きな出力トランジスタのゲート制御に  $Q_2[n]$  を用いた場合、図 11 に示すようにゲート容量負荷の充放電は、ゲート線の電位を立ち下げる期間  $T_2$  に限定される。それ以外の期間ではクロック信号と同期しないため、ゲート容量負荷の充放電は行わず、クロック信号からの電力供給もない。出力トランジスタの大きなゲート容量負荷の充放電回数を軽減することで、クロック信号の負荷および消費電力を軽減することができる。

10

#### 【0068】

##### [第 6 の実施の形態]

次に、本発明の第 6 の実施の形態について図 12 を用いて説明する。本実施の形態は、シフトレジスタ回路 1 の出力  $O[n]$  と第 1 の電源  $VSS$  とをつなぐ出力トランジスタ  $M_5$  を追加し、出力トランジスタ  $M_1$ 、 $M_4$ 、 $M_5$  のゲート制御を、第 1 の実施形態のゲート制御回路の代わりに第 5 の実施形態のゲート制御回路で行う点で、第 3 の実施形態と異なる。出力トランジスタ  $M_1$  のゲート制御は、第 1 のゲート制御回路の第 2 の出力  $Q_2[n]$ 、出力トランジスタ  $M_4$  のゲート制御は、第 2 のゲート制御回路の第 1 の出力  $Q[n+1]$ 、出力トランジスタ  $M_5$  のゲート制御は、第 1 のゲート制御回路の第 1 の出力  $Q[n]$  にて行う。

20

#### 【0069】

本実施の形態の動作について、図 13 に示した動作波形を用いて説明する。本実施の形態は、第 1 のゲート制御回路 3 の第 2 の出力  $Q_2[n]$  により出力トランジスタ  $M_1$  をゲート制御している点で、第 3 の実施形態と異なる。第 2 の出力  $Q_2[n]$  は、入力信号  $O[n+2]$  がハイレベルである間、第 1 の出力  $Q[n]$  に同期していることが特徴である。すなわち  $Q_2[n]$  がハイレベルに反転するのは、シフトレジスタ回路の出力  $O[n]$  をハイレベルからロウレベルへ立ち下げる時のみである。 $Q_2[n]$  によりゲート制御される出力トランジスタ  $M_1$  が導通するのは、出力  $O[n]$  を立ち下げる時に限られる。一方、第 1 および第 2 のゲート制御回路 3 の第 1 の出力  $Q[n]$ 、 $Q[n+1]$  にゲート制御される出力トランジスタ  $M_4$  および  $M_5$  は、出力  $O[n]$  がハイレベルを出力しない期間はいずれか一方が導通し、出力  $O[n]$  をロウレベルに固定する。

30

#### 【0070】

出力トランジスタのチャネルサイズに関しては、出力トランジスタ  $M_1$  は高速にゲート線の電位を立ち下げるために、大きなチャネル幅が必要となるが、出力トランジスタ  $M_4$ 、 $M_5$  はゲート線の電位をロウレベルに固定することが目的であるため、大きなチャネル幅は必要ではない。

#### 【0071】

##### [第 7 の実施の形態]

次に、本発明の第 7 の実施の形態について、図 14 を用いて説明する。本実施の形態は、第 5 の実施の形態のシフトレジスタ回路 1 を複数段連結したゲートドライバ 10 である。第  $n-2$  段目 ( $n$  は 3 以上の整数) のシフトレジスタ回路 1 の出力  $O[n-2]$  を、第  $n-1$  段目のシフトレジスタ部 2 およびゲート制御回路 3 の入力とする。第  $n-1$  段目のゲート制御回路 3 の第 1 の出力  $Q[n]$  を、第  $n-1$  段目のシフトレジスタ部 2 および第  $n$  段目のシフトレジスタ部 2 それぞれに入力している。さらに第  $n-1$  段目のゲート制御回路 3 の第 2 の出力  $Q_2[n]$  を、第  $n$  段目のシフトレジスタ部 2 に入力している。すなわち、ゲート制御回路 3 の出力  $Q[n]$  を 2 つの連続するシフトレジスタ部 2 で共有している点が特徴である。この構成により、ゲートドライバの回路規模の縮減が図れる。なぜならば、図 12 に示した 1 段分のシフトレジスタ回路 1 では、2 つのゲート制御回路 3 を

40

10

20

30

40

50

記載しているが、複数の連続するシフトレジスタ回路1箇でゲート制御回路3を共有することで、ゲート制御回路3の個数を減らせるからである。

#### 【0072】

##### [第8の実施の形態]

次に、本発明の第8の実施の形態について図15及び図16を用いて説明する。本実施の形態は第4の実施の形態または第7の実施の形態のゲートドライバ10を搭載したマトリクス型表示装置15であり、図15に示すように複数のゲート線13と複数のデータ線14とその交差部に配置された画素素子で構成された画素アレイ(表示部)11の、複数のゲート線G1、G2、…を前出のゲートドライバ10の出力O[1]、O[2]、…に接続している。また、ゲートドライバ10にはCLKとXCLKの2相のクロック信号を10

入力し、ゲートドライバ10の初段のシフトレジスタ回路1の入力としてスタート信号STを入力する。ゲートドライバ10は図16に示した波形のように動作し、複数の連続したゲート線13が同時に選択される(ハイレベルになる)期間を有するオーバーラップ走査を行う。各ゲート線13の選択期間は、スタート信号STのパルス幅によって制御される。また、各ゲート線選択期間の時間差はクロック信号CLK、XCLKの半周期で制御される。

#### 【0073】

本実施の形態のマトリクス型表示装置では、ゲート電位の高振幅を有するクロック信号が2本と少ないため、高振幅信号を生成するレベルシフト回路の個数を低減し、部材コストを抑えることができる。また、クロック信号線の配線レイアウト面積を小さくすることができ、狭額縁の表示装置が可能となる。20

#### 【0074】

なお、本発明は上記実施の形態に限られたものではなく、本発明の趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、実施の形態に示したトランジスタはN型に限っているが、P型トランジスタへ置き換えるても良く、それぞれのトランジスタとしては、多結晶シリコントランジスタやアモーファスシリコントランジスタあるいはシリコン以外の酸化物半導体や有機半導体であっても良い。

#### 【0075】

本発明は、シフトレジスタ回路及び当該シフトレジスタ回路を備えるゲートドライバ並びに当該ゲートドライバを搭載した表示装置に利用可能である。30

#### 【符号の説明】

#### 【0076】

- 1 シフトレジスタ回路

- 2 シフトレジスタ部

- 3 ゲート制御回路

- 4 バッファ部

- 5 タイミング生成部

- 10 ゲートドライバ

- 11 画素アレイ(表示部)

- 12 データドライバ

- 13 ゲート線

- 14 データ線

- 15 マトリクス型表示装置

- CLK、XCLK クロック信号

- VSS 第1の電源

- VDD 第2の電源

- M1、M2、M3、M4、M5、M11、M12、M13、M14、M15、M16、

M17、M18、M19 トランジスタ

- C1、C2 容量

- O[n]、O[n-1]、O[n-2] シフトレジスタ出力

10

20

30

40

50

P [ n ] ブートストラップノード

Q [ n ]、Q [ n + 1 ] ゲート制御回路出力

S T スタート信号

Q 2 [ n ]、Q 2 [ n + 1 ] ゲート制御回路第 2 の出力

【図 1】

【図 3】

【図 2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 8 0 G |

| G 0 9 G | 3/20 | 6 2 2 G |

(56)参考文献 特開2013-211088(JP, A)

国際公開第2014/073362(WO, A1)

米国特許出願公開第2008/0279327(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 1 1 C 1 9 / 2 8