(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7674513号

(P7674513)

(45)発行日 令和7年5月9日(2025.5.9)

(24)登録日 令和7年4月28日(2025.4.28)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3233(2016.01) | F I | G 0 9 G | 3/3233       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 2 1 F |

| H 1 0 K | 59/123(2023.01) |     | G 0 9 G | 3/20 6 4 2 A |

|         |                 |     | G 0 9 G | 3/20 6 4 1 D |

|         |                 |     | G 0 9 G | 3/20 6 2 4 B |

請求項の数 16 (全18頁) 最終頁に続く

(21)出願番号 特願2023-566837(P2023-566837)

(86)(22)出願日 令和4年12月23日(2022.12.23)

(65)公表番号 特表2024-530557(P2024-530557)

A)

(43)公表日 令和6年8月23日(2024.8.23)

(86)国際出願番号 PCT/CN2022/141297

(87)国際公開番号 WO2024/021465

(87)国際公開日 令和6年2月1日(2024.2.1)

審査請求日 令和5年10月30日(2023.10.30)

(31)優先権主張番号 202210898918.7

(32)優先日 令和4年7月28日(2022.7.28)

(33)優先権主張国・地域又は機関

中国(CN)

(73)特許権者 521141718

惠科股 分 有限公司

H K C C o r p o r a t i o n L i m

i t e d

中華人民共和国広東省深セン市宝安区石

岩街道石龍社区工業二路1号惠科工業園

厂房1棟一層至三層、五至七層，6棟七

層

1 F - 3 F , 5 F - 7 F o f F a

c t o r y B u i l d i n g 1 , 7 F

o f F a c t o r y B u i l d i n

g 6 , H u i k e I n d u s t r i

a l 2 n d R o a d , S h i l o n g

C o m m u n i t y , S h i y a n S

最終頁に続く

(54)【発明の名称】 画素駆動回路及び表示パネル

## (57)【特許請求の範囲】

## 【請求項1】

画素駆動回路であって、

前記画素駆動回路は発光素子の発光を駆動するように構成されており、前記発光素子の第1端は基準電圧を受けるように構成されており、前記画素駆動回路は、1フレームの表示周期において順にリセット段階、データ書き込み段階及び発光段階で動作し、前記画素駆動回路は、駆動トランジスタ、エネルギー蓄積キャパシタ、エネルギー蓄積キャパシタリセットループ、ブートストラップキャパシタ、プリチャージループ、データ書き込みループ及び発光ループを含み、

前記駆動トランジスタは、制御端、第1接続端及び第2接続端を備え、前記第1接続端は駆動電圧を受けるように構成されており、前記第2接続端は前記発光素子の第2端に電気的に接続されており、

前記エネルギー蓄積キャパシタの第1端は、前記駆動トランジスタの制御端に電気的に接続されており、前記エネルギー蓄積キャパシタの第2端は、電圧値が一定の第1電圧を受けるように構成されており、

前記エネルギー蓄積キャパシタリセットループは、前記リセット段階でオンになって、第1リセット電圧を受けて、前記エネルギー蓄積キャパシタの第1端の電圧が前記第1リセット電圧の値に達するように、前記エネルギー蓄積キャパシタの第1端の電圧をリセットするように構成されており、

前記ブートストラップキャパシタの第1端は、前記駆動トランジスタの第1接続端に電

気的に接続されており、前記ブートストラップキャパシタの第2端は、前記リセット段階でゼロ電位の電圧を受け、前記データ書き込み段階でデータ電圧を受けるように構成されており、

前記プリチャージループは、前記リセット段階でオンになって、前記駆動電圧を受けて前記ブートストラップキャパシタを充電することにより、前記ブートストラップキャパシタの第1端の電圧が前記駆動電圧の値に達するように前記ブートストラップキャパシタの第1端の電圧を調整し、前記ブートストラップキャパシタの第2端の電圧がゼロ電位の値に達するように前記ブートストラップキャパシタの第2端の電圧をリセットすることで、前記ブートストラップキャパシタの第1端の電圧と第2端の電圧の間の差値を前記駆動電圧の値に達させるように構成されており、

前記データ書き込みループは、直列接続された前記ブートストラップキャパシタ、前記駆動トランジスタ及び前記エネルギー蓄積キャパシタを含み、前記データ書き込みループは、前記データ書き込み段階でオンになって、前記ブートストラップキャパシタの第2端で前記データ電圧を受けて、前記ブートストラップキャパシタのブートストラップ効果に基づいて前記エネルギー蓄積キャパシタを充電することにより、前記駆動トランジスタの制御端の電圧が前記第1リセット電圧の値から第2電圧の値に達するように、前記駆動トランジスタの制御端の電圧を調整するように構成されており、前記駆動トランジスタは、その制御端の電圧が第2電圧に等しくなったら、臨界オン状態となり、前記第2電圧は、前記駆動電圧と前記データ電圧と前記駆動トランジスタの閾値電圧との和に等しく、

前記発光ループは、直列接続された前記駆動トランジスタ及び前記発光素子を含み、前記発光ループは、前記発光段階でオンになって、前記駆動トランジスタの第1接続端で前記駆動電圧を受けて、前記発光素子の発光を駆動するように構成されている、

ことを特徴とする画素駆動回路。

### 【請求項2】

前記プリチャージループは、直列接続された第1スイッチングトランジスタ、前記ブートストラップキャパシタ及び第2スイッチングトランジスタを含み、

前記第1スイッチングトランジスタの第1接続端は、前記駆動電圧を受けるように構成されており、前記第1スイッチングトランジスタの第2接続端は、前記ブートストラップキャパシタの第1端に電気的に接続されており、

前記第2スイッチングトランジスタの第1接続端は、接地端に電気的に接続されて前記ゼロ電位の電圧を受けるように構成されており、前記第2スイッチングトランジスタの第2接続端は、前記ブートストラップキャパシタの第2端に電気的に接続されており、

前記リセット段階で、前記第1スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになり、前記第2スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記プリチャージループはオンになる、

ことを特徴とする請求項1に記載の画素駆動回路。

### 【請求項3】

前記データ書き込みループは、直列接続された第3スイッチングトランジスタ、前記ブートストラップキャパシタ、前記駆動トランジスタ、第4スイッチングトランジスタ及び前記エネルギー蓄積キャパシタを含み、

前記第3スイッチングトランジスタの第1接続端は、前記データ電圧を受けるように構成されており、前記第3スイッチングトランジスタの第2接続端は、前記ブートストラップキャパシタの第2端に電気的に接続されており、

前記第4スイッチングトランジスタは、前記駆動トランジスタの第2接続端と前記エネルギー蓄積キャパシタの第1端との間に電気的に接続されており、

前記データ書き込み段階で、前記第3スイッチングトランジスタ及び前記第4スイッチングトランジスタはいずれも、それぞれの制御端で受けた走査信号に応答してオンになり、これにより、前記データ書き込みループはオンになる、

ことを特徴とする請求項2に記載の画素駆動回路。

### 【請求項4】

10

20

30

40

50

前記発光ループは、直列接続された前記第1スイッチングトランジスタ、前記駆動トランジスタ、第5スイッチングトランジスタ及び前記発光素子を含み、

前記第1スイッチングトランジスタの第2接続端は、前記駆動トランジスタの第1接続端に電気的に接続されており、

前記第5スイッチングトランジスタは、前記駆動トランジスタの第2接続端と前記発光素子の第2端との間に電気的に接続されており、

前記発光段階で、前記第1スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになり、前記第5スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記発光ループはオンになる、

ことを特徴とする請求項3に記載の画素駆動回路。

10

【請求項5】

前記エネルギー蓄積キャパシタリセットループは、直列接続された前記エネルギー蓄積キャパシタと第6スイッチングトランジスタを含み、前記第6スイッチングトランジスタの第1接続端は、前記第1リセット電圧を受けるように構成されており、前記第6スイッチングトランジスタの第2接続端は、前記エネルギー蓄積キャパシタの第1端に電気的に接続されており、

前記リセット段階で、前記第6スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記エネルギー蓄積キャパシタリセットループはオンになる、

ことを特徴とする請求項4に記載の画素駆動回路。

20

【請求項6】

前記画素駆動回路は、発光素子リセットループをさらに含み、前記発光素子リセットループは、直列接続された第7スイッチングトランジスタと前記発光素子を含み、前記第7スイッチングトランジスタの第1接続端は、第2リセット電圧を受けるように構成されており、前記第7スイッチングトランジスタの第2接続端は、前記発光素子の第2端と電気的に接続されており、

前記リセット段階で、前記第7スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記発光素子リセットループはオンになり、前記発光素子の第2端の電圧が前記第2リセット電圧の値に達するように前記発光素子の第2端の電圧をリセットする、

ことを特徴とする請求項5に記載の画素駆動回路。

30

【請求項7】

前記第1スイッチングトランジスタ、前記第2スイッチングトランジスタ、前記第3スイッチングトランジスタ、前記第4スイッチングトランジスタ、前記第5スイッチングトランジスタ、前記第6スイッチングトランジスタ、前記第7スイッチングトランジスタ及び前記駆動トランジスタは、いずれもローレベルでオンになるトランジスタである、

ことを特徴とする請求項6に記載の画素駆動回路。

【請求項8】

前記エネルギー蓄積キャパシタの第2端で受けられる前記第1電圧は、前記駆動電圧又は前記ゼロ電位の電圧を含む、

40

ことを特徴とする請求項1に記載の画素駆動回路。

【請求項9】

前記発光段階で、前記駆動トランジスタのソースとドレインとの間の電流  $I_{d,s}$  は次の数式を満たし、

$$I_{d,s} = (K/2) (V_{data})^2$$

$K = C_o \times \mu \times W/L$ 、 $C_o$  は単位面積当たりのゲート容量であり、 $\mu$  はチャネル内の電子移動度であり、 $W/L$  は前記駆動トランジスタのチャネルの幅と長の比である、

ことを特徴とする請求項1に記載の画素駆動回路。

【請求項10】

表示パネルであって、

50

前記表示パネルは、基板と幾つかの画素駆動回路を含み、前記基板は表示領域を有し、前記幾つかの画素駆動回路は前記基板の表示領域内にアレイ状に配列されており、

前記画素駆動回路は発光素子の発光を駆動するように構成されており、前記発光素子の第1端は基準電圧を受けるように構成されており、前記画素駆動回路は、1フレームの表示周期において順にリセット段階、データ書き込み段階及び発光段階で動作し、前記画素駆動回路は、駆動トランジスタ、エネルギー蓄積キャパシタ、エネルギー蓄積キャパシタリセットループ、ブートストラップキャパシタ、プリチャージループ、データ書き込みループ及び発光ループを含み、

前記駆動トランジスタは、制御端、第1接続端及び第2接続端を備え、前記第1接続端は駆動電圧を受けるように構成されており、前記第2接続端は前記発光素子の第2端に電気的に接続されており、

前記エネルギー蓄積キャパシタの第1端は、前記駆動トランジスタの制御端に電気的に接続されており、前記エネルギー蓄積キャパシタの第2端は、電圧値が一定の第1電圧を受けるように構成されており、

前記エネルギー蓄積キャパシタリセットループは、前記リセット段階でオンになって、第1リセット電圧を受けて、前記エネルギー蓄積キャパシタの第1端の電圧が前記第1リセット電圧の値に達するように、前記エネルギー蓄積キャパシタの第1端の電圧をリセットするように構成されており、

前記ブートストラップキャパシタの第1端は、前記駆動トランジスタの第1接続端に電気的に接続されており、前記ブートストラップキャパシタの第2端は、前記リセット段階でゼロ電位の電圧を受け、前記データ書き込み段階でデータ電圧を受けるように構成されており、

前記プリチャージループは、前記リセット段階でオンになって、前記駆動電圧を受けて前記ブートストラップキャパシタを充電することにより、前記ブートストラップキャパシタの第1端の電圧が前記駆動電圧の値に達するように前記ブートストラップキャパシタの第1端の電圧を調整し、前記ブートストラップキャパシタの第2端の電圧がゼロ電位の値に達するように前記ブートストラップキャパシタの第2端の電圧をリセットすることで、前記ブートストラップキャパシタの第1端の電圧と第2端の電圧の間の差値を前記駆動電圧の値に達させるように構成されており、

前記データ書き込みループは、直列接続された前記ブートストラップキャパシタ、前記駆動トランジスタ及び前記エネルギー蓄積キャパシタを含み、前記データ書き込みループは、前記データ書き込み段階でオンになって、前記ブートストラップキャパシタの第2端で前記データ電圧を受けて、前記ブートストラップキャパシタのブートストラップ効果に基づいて前記エネルギー蓄積キャパシタを充電することにより、前記駆動トランジスタの制御端の電圧が前記第1リセット電圧の値から第2電圧の値に達するように、前記駆動トランジスタの制御端の電圧を調整するように構成されており、前記駆動トランジスタは、その制御端の電圧が第2電圧に等しくなったら、臨界オン状態となり、前記第2電圧は、前記駆動電圧と前記データ電圧と前記駆動トランジスタの閾値電圧との和に等しく、

前記発光ループは、直列接続された前記駆動トランジスタ及び前記発光素子を含み、前記発光ループは、前記発光段階でオンになって、前記駆動トランジスタの第1接続端で前記駆動電圧を受けて、前記発光素子の発光を駆動するように構成されている、

ことを特徴とする表示パネル。

#### 【請求項 1 1】

前記プリチャージループは、直列接続された第1スイッチングトランジスタ、前記ブートストラップキャパシタ及び第2スイッチングトランジスタを含み、

前記第1スイッチングトランジスタの第1接続端は、前記駆動電圧を受けるように構成されており、前記第1スイッチングトランジスタの第2接続端は、前記ブートストラップキャパシタの第1端に電気的に接続されており、

前記第2スイッチングトランジスタの第1接続端は、接地端に電気的に接続されて前記ゼロ電位の電圧を受けるように構成されており、前記第2スイッチングトランジスタの第

10

20

30

40

50

2接続端は、前記ポートストラップキャパシタの第2端に電気的に接続されており、前記リセット段階で、前記第1スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになり、前記第2スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記プリチャージループはオンになる、ことを特徴とする請求項10に記載の表示パネル。

【請求項12】

前記データ書き込みループは、直列接続された第3スイッチングトランジスタ、前記ポートストラップキャパシタ、前記駆動トランジスタ、第4スイッチングトランジスタ及び前記エネルギー蓄積キャパシタを含み、

前記第3スイッチングトランジスタの第1接続端は、前記データ電圧を受けるように構成されており、前記第3スイッチングトランジスタの第2接続端は、前記ポートストラップキャパシタの第2端に電気的に接続されており、

前記第4スイッチングトランジスタは、前記駆動トランジスタの第2接続端と前記エネルギー蓄積キャパシタの第1端との間に電気的に接続されており、

前記データ書き込み段階で、前記第3スイッチングトランジスタ及び前記第4スイッチングトランジスタはいずれも、それぞれの制御端で受けた走査信号に応答してオンになり、これにより、前記データ書き込みループはオンになる、

ことを特徴とする請求項11に記載の表示パネル。

【請求項13】

前記発光ループは、直列接続された前記第1スイッチングトランジスタ、前記駆動トランジスタ、第5スイッチングトランジスタ及び前記発光素子を含み、

前記第1スイッチングトランジスタの第2接続端は、前記駆動トランジスタの第1接続端に電気的に接続されており、

前記第5スイッチングトランジスタは、前記駆動トランジスタの第2接続端と前記発光素子の第2端との間に電気的に接続されており、

前記発光段階で、前記第1スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになり、前記第5スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記発光ループはオンになる、

ことを特徴とする請求項12に記載の表示パネル。

【請求項14】

前記エネルギー蓄積キャパシタリセットループは、直列接続された前記エネルギー蓄積キャパシタと第6スイッチングトランジスタを含み、前記第6スイッチングトランジスタの第1接続端は、前記第1リセット電圧を受けるように構成されており、前記第6スイッチングトランジスタの第2接続端は、前記エネルギー蓄積キャパシタの第1端に電気的に接続されており、

前記リセット段階で、前記第6スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記エネルギー蓄積キャパシタリセットループはオンになる、

ことを特徴とする請求項13に記載の表示パネル。

【請求項15】

前記画素駆動回路は、発光素子リセットループをさらに含み、前記発光素子リセットループは、直列接続された第7スイッチングトランジスタと前記発光素子を含み、前記第7スイッチングトランジスタの第1接続端は、第2リセット電圧を受けるように構成されており、前記第7スイッチングトランジスタの第2接続端は、前記発光素子の第2端と電気的に接続されており、

前記リセット段階で、前記第7スイッチングトランジスタはその制御端で受けた走査信号に基づいてオンになることで、前記発光素子リセットループはオンになり、前記発光素子の第2端の電圧が前記第2リセット電圧の値に達するように前記発光素子の第2端の電圧をリセットする、

ことを特徴とする請求項14に記載の表示パネル。

10

20

30

40

50

### 【請求項 16】

前記発光段階で、前記駆動トランジスタのソースとドレインとの間の電流  $I_{d,s}$  は次の式を満たし、

$$I_{d,s} = (K/2) (V_{data})^2$$

$K = C_o \times \mu \times W/L$ 、 $C_o$  は単位面積当たりのゲート容量であり、 $\mu$  はチャネル内の電子移動度であり、 $W/L$  は前記駆動トランジスタのチャネルの幅と長の比である、ことを特徴とする請求項 10 に記載の表示パネル。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

関連出願の参照

10

本出願は、発明の名称を「画素駆動回路及び表示パネル」とする、2022年7月28日に出願された中国特許出願第202210898918.7号の優先権を主張し、そのすべての内容が引用として本出願に組み込まれる。

#### 【0002】

本出願は、表示技術分野に関し、特に、画素駆動回路及び表示パネルに関する。

#### 【背景技術】

#### 【0003】

ここで記述は、本出願に関する背景情報のみを提供するものであり、従来技術を必ずしも構成するものではない。有機発光ダイオード (Organic Light-Emitting Diode、OLED) ディスプレイは、消費電力が低い、応答速度が速い、表示視野角が広いなどの利点を有するため、応用が広がりつつある。OLED ディスプレイの OLED アレイにおいて、OLED ごとに応用する画素駆動回路を備える。画素駆動回路は、通常、複数の薄膜トランジスタ (Thin Film Transistor、TFT) で構成される。しかし、異なる画素駆動回路の TFT のパラメータが異なる。例えば、閾値電圧  $V_{th}$  (即ち、TFT を臨界オフ状態又は臨界オン状態にするゲート・ソース間のバイアス電圧)、移動度等が異なる。従って異なる OLED が発する光線の明るさに差が生じ、その差は人間の目に感知される。この現象は、ムラ現象と呼ばれる。ムラ現象は、表示装置の表示性能を低下させる。

20

#### 【0004】

従来技術では、異なる画素駆動回路の TFT の閾値電圧の違いによる表示輝度ムラを改善するために、通常、6T (トランジスタ) 1C (キャパシタ)、7T1C、8T1C 等の画素駆動回路のような補償機能を有する画素駆動回路が設計され、画素駆動回路が順次にリセット段階、データ書き込み段階、発光段階で動作するようにする。従来の画素駆動回路において、データ書き込み段階で TFT の閾値電圧  $V_{th}$  が補償された後、OLED の表示輝度はデータ電圧  $V_{data}$  及び駆動電圧  $V_{DD}$  と相關するが TFT の閾値電圧  $V_{th}$  と相關しなくなる。しかしながら、駆動電圧  $V_{DD}$  を伝送するための電源線自体がインピーダンスを有するため、電源チップとの距離が異なる画素駆動回路によって受けられる駆動電圧  $V_{DD}$  は異なる。そうになると、電源チップとの距離が異なる OLED の表示輝度に差が生じ、ムラ現象は、徹底的に解決されることができなく、また、OLED ディスプレイの大型化に伴って顕著になり、ユーザの視覚体験に大きく影響する。

30

#### 【発明の概要】

#### 【0005】

本出願において、画素駆動回路が提供される。画素駆動回路は発光素子の発光を駆動するように構成されており、発光素子の第 1 端は基準電圧を受けるように構成されており、画素駆動回路は、1 フレームの表示周期において順にリセット段階、データ書き込み段階及び発光段階で動作し、画素駆動回路は、駆動トランジスタ、エネルギー蓄積キャパシタ、エネルギー蓄積キャパシタリセットループ、ブーストトラップキャパシタ、プリチャージループ、データ書き込みループ及び発光ループを含む。駆動トランジスタは、制御端、第 1 接続端及び第 2 接続端を備え、第 1 接続端は駆動電圧を受けるように構成されており

40

50

、第2接続端は発光素子の第2端に電気的に接続されている。エネルギー蓄積キャパシタの第1端は、駆動トランジスタの制御端に電気的に接続されており、エネルギー蓄積キャパシタの第2端は、電圧値が一定の第1電圧を受けるように構成されている。エネルギー蓄積キャパシタリセットループは、リセット段階でオンになって、第1リセット電圧を受けて、エネルギー蓄積キャパシタの第1端の電圧が第1リセット電圧の値に達するよう、エネルギー蓄積キャパシタの第1端の電圧をリセットするように構成されている。ブートストラップキャパシタの第1端は、駆動トランジスタの第1接続端に電気的に接続されており、ブートストラップキャパシタの第2端は、リセット段階でゼロ電位の電圧を受け、データ書き込み段階でデータ電圧を受けるように構成されている。プリチャージループは、リセット段階でオンになって、駆動電圧を受けてブートストラップキャパシタを充電することにより、ブートストラップキャパシタの第1端の電圧が駆動電圧の値に達するようブートストラップキャパシタの第1端の電圧を調整し、ブートストラップキャパシタの第2端の電圧をリセットすることで、ブートストラップキャパシタの第1端の電圧と第2端の電圧の間の差値を駆動電圧の値に達させるように構成されている。データ書き込みループは、直列接続されたブートストラップキャパシタ、駆動トランジスタ及びエネルギー蓄積キャパシタを含み、データ書き込みループは、データ書き込み段階でオンになって、ブートストラップキャパシタの第2端でデータ電圧を受けて、ブートストラップキャパシタのブートストラップ効果に基づいてエネルギー蓄積キャパシタを充電することにより、駆動トランジスタの制御端の電圧が第1リセット電圧の値から第2電圧の値に達するように、駆動トランジスタの制御端の電圧を調整するように構成されており、駆動トランジスタは、その制御端の電圧が第2電圧に等しくなったら、臨界オン状態となり、第2電圧は、駆動電圧とデータ電圧と駆動トランジスタの閾値電圧との和に等しい。発光ループは、直列接続された駆動トランジスタ及び発光素子を含み、発光ループは、発光段階でオンになって、駆動トランジスタの第1接続端で駆動電圧を受けて、発光素子の発光を駆動するように構成されている。10

#### 【0006】

本出願で提供される画素駆動回路は、リセット段階で、プリチャージループを介して、ブートストラップキャパシタの第1端の電圧が駆動電圧の値に達するようブートストラップキャパシタを充電し、データ書き込み段階で、ブートストラップキャパシタの第2端を介してデータ電圧を受けて、ブートストラップキャパシタのブートストラップ効果に基づいて、エネルギー蓄積キャパシタを充電することで、駆動トランジスタの制御端の電圧を第2電圧に調整し、第2電圧の電圧値は、駆動電圧、データ電圧及び駆動トランジスタの閾値電圧の和と等しく、また、発光段階で、駆動トランジスタにその制御端で受けた第2電圧及びその第1接続端で受けた駆動電圧とに基づいて、発光素子の発光を駆動させて、発光素子を流れる電流が駆動電圧及び駆動トランジスタの閾値電圧と相關しなくなることで、異なる画素駆動回路における駆動トランジスタの閾値電圧の違いによる表示パネルの表示輝度ムラを解消するだけでなく、異なる画素駆動回路によって受けられた駆動電圧の違いによる表示パネルの表示輝度ムラを解消することもできる。30

#### 【0007】

本出願において、表示パネルがさらに提供される。表示パネルは、基板と幾つかの画素駆動回路を含み、基板は表示領域を有し、幾つかの画素駆動回路は基板の表示領域内にアレイ状に配列されている。画素駆動回路は発光素子の発光を駆動するように構成されており、発光素子の第1端は基準電圧を受けるように構成されており、画素駆動回路は、1フレームの表示周期において順にリセット段階、データ書き込み段階及び発光段階で動作し、画素駆動回路は、駆動トランジスタ、エネルギー蓄積キャパシタ、エネルギー蓄積キャパシタリセットループ、ブートストラップキャパシタ、プリチャージループ、データ書き込みループ及び発光ループを含む。駆動トランジスタは、制御端、第1接続端及び第2接続端を備え、第1接続端は駆動電圧を受けるように構成されており、第2接続端は発光素子の第2端に電気的に接続されている。エネルギー蓄積キャパシタの第1端は、駆動トランジスタの制御端に接続され、第2端は、駆動電圧を受けるように構成されている。40

10

20

30

40

50

ンジスタの制御端に電気的に接続されており、エネルギー蓄積キャパシタの第2端は、電圧値が一定の第1電圧を受けるように構成されている。エネルギー蓄積キャパシタリセットループは、リセット段階でオンになって、第1リセット電圧を受けて、エネルギー蓄積キャパシタの第1端の電圧が第1リセット電圧の値に達するように、エネルギー蓄積キャパシタの第1端の電圧をリセットするように構成されている。ブートストラップキャパシタの第1端は、駆動トランジスタの第1接続端に電気的に接続されており、ブートストラップキャパシタの第2端は、リセット段階でゼロ電位の電圧を受け、データ書き込み段階でデータ電圧を受けるように構成されている。プリチャージループは、リセット段階でオンになって、駆動電圧を受けてブートストラップキャパシタを充電することにより、ブートストラップキャパシタの第1端の電圧が駆動電圧の値に達するようにブートストラップキャパシタの第1端の電圧を調整し、ブートストラップキャパシタの第2端の電圧がゼロ電位の値に達するようにブートストラップキャパシタの第2端の電圧をリセットすることで、ブートストラップキャパシタの第1端の電圧と第2端の電圧の間の差値を駆動電圧の値に達させるように構成されている。データ書き込みループは、直列接続されたブートストラップキャパシタ、駆動トランジスタ及びエネルギー蓄積キャパシタを含み、データ書き込みループは、データ書き込み段階でオンになって、ブートストラップキャパシタの第2端でデータ電圧を受けて、ブートストラップキャパシタのブートストラップ効果に基づいてエネルギー蓄積キャパシタを充電することにより、駆動トランジスタの制御端の電圧が第1リセット電圧の値から第2電圧の値に達するように、駆動トランジスタの制御端の電圧を調整するように構成されており、駆動トランジスタは、その制御端の電圧が第2電圧に等しくなったら、臨界オン状態となり、第2電圧は、駆動電圧とデータ電圧と駆動トランジスタの閾値電圧との和に等しい。発光ループは、直列接続された駆動トランジスタ及び発光素子を含み、発光ループは、発光段階でオンになって、駆動トランジスタの第1接続端で駆動電圧を受けて、発光素子の発光を駆動するように構成されている。10

#### 【0008】

本出願の追加的な態様及び利点について、一部は以下の説明において紹介され、一部は以下の説明を介して明らかになり、又は本出願の実践を通じて理解される。20

#### 【図面の簡単な説明】

#### 【0009】

【図1】図1は、本出願の実施形態に係るパネルの構成を示す概略図である。30

【図2】図2は、従来の画素駆動回路の構成を示す概略図である。

【図3】図3は、本出願の実施形態に係る画素駆動回路の構成を示す概略図である。

【図4】図4は、図3に示された画素駆動回路の動作を示すタイミングチャートである。

【図5a】図5aは、図3に示された画素駆動回路がA段階にあるときの回路概略図である。

【図5b】図5bは、図3に示された画素駆動回路がB段階にあるときの回路概略図である。

【図5c】図5cは、図3に示された画素駆動回路がC段階にあるときの回路概略図である。

#### 【発明を実施するための形態】

#### 【0010】

以下、本出願の実施形態の図面を参照しながら本出願の実施形態の技術的解決策を明晰に、全面的に説明する。明らかに、説明される実施形態は、本出願の一部の実施形態のみであり、全ての実施形態ではない。本出願における実施形態に基づいて、当業者が創造的な努力なしに得られるすべての他の実施形態は、皆本出願の保護範囲に属する。40

#### 【0011】

本出願の説明において、用語「上」、「下」、「左」、「右」などによって示される方向又は位置関係は図面に基づいて示される方向又は位置関係であり、単に本出願を説明し、説明を簡略化するためのものであり、指される装置又は要素が必ず特定の方向を有し、特定の方向で構成され又は動作されることを示したり暗示したりするためのものではなく50

、従って本出願に対する制限と理解されることはできない。また、用語「第1」、「第2」などは、説明のためだけに使用され、相対的な重要性を示したり暗示したりするためのものと理解されることはできない。

【0012】

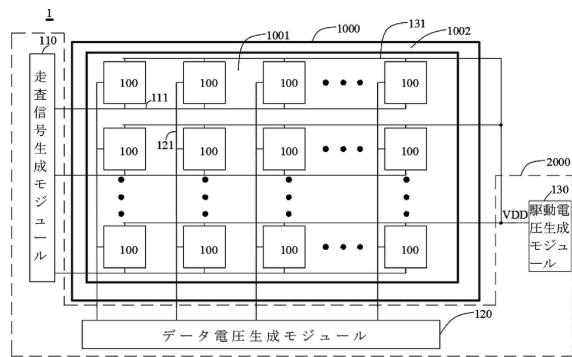

図1を参照すると、本出願で表示パネル1が提供され、表示パネル1は、互いに電気的に接続された基板1000及びメイン駆動回路2000を備え、基板1000は、表示領域1001及び非表示領域1002を有する。表示領域1001内には、幾つかの画素駆動回路100がアレイ状に配列して設けられている。メイン駆動回路2000は、走査信号生成モジュール110、データ電圧生成モジュール120及び駆動電圧生成モジュール130を備える。走査信号生成モジュール110は、複数の走査線111を介して複数行の画素駆動回路100に別々に電気的に接続されており、各々の行の画素駆動回路100に対応する走査信号を生成するように構成されている。データ電圧生成モジュール120は、複数のデータ線121を介して複数列の画素駆動回路100に別々に電気的に接続されており、各々の列の画素駆動回路100に対応するデータ電圧Vdataを生成するように構成されている。駆動電圧生成モジュール130は、複数の電源電圧線131を介して複数行の画素駆動回路100に別々に電気的に接続されており、各々の行の画素駆動回路100に駆動電圧VDDを生成するように構成されている。

10

【0013】

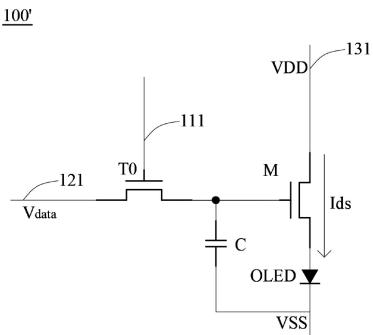

図2を参照すると、図2は、2T(トランジスタ)1C(キャパシタ)構成を有する従来の画素駆動回路100'を示す。画素駆動回路100'は、走査トランジスタT0、駆動トランジスタM、エネルギー蓄積キャパシタC及び発光素子を含む。

20

【0014】

画素駆動回路100'は、発光素子の発光を駆動するように構成されている。本出願の実施形態では、発光素子は有機発光ダイオード(Organic Light-Emitting Diode、OLED)であり、発光素子の第1端はOLEDのカソードに対応し、発光素子の第2端はOLEDのアノードに対応している。別の実施形態では、発光素子は、発光ダイオード(Light-Emitting Diode、LED)であってもよく、マイクロLED(MicroLED)又はミニLED(MiniLED)であってもよい。この発光素子OLEDのカソードは、基準電圧端に電気的に接続されて基準電圧Vssを受けるように構成されている。駆動トランジスタMのソースは、電源電圧線131に電気的に接続されて駆動電圧VDDを受けるように構成されており、駆動トランジスタMのドレインは、発光素子OLEDのアノードに電気的に接続されており、駆動トランジスタMのゲートは、走査トランジスタT0のドレインに電気的に接続されている。走査トランジスタT0のソースは、データ線121に電気的に接続されてデータ電圧Vdataを受けるように構成されている。走査トランジスタT0のゲートは、走査線111と電気的に接続されて走査信号を受けるように構成されている。エネルギー蓄積キャパシタCの第1端は駆動トランジスタMのゲートに電気的に接続されており、エネルギー蓄積キャパシタCの第2端は発光素子OLEDのカソードに電気的に接続されている。例えば、走査信号がオン信号であるとき、走査トランジスタT0がオンになり、データ線121上のデータ電圧Vdataが走査トランジスタT0を介してエネルギー蓄積キャパシタCを充電することで、エネルギー蓄積キャパシタCの第1端の電圧がデータ電圧Vdataの値に達するように、エネルギー蓄積キャパシタCの第1端の電圧を調整し、駆動トランジスタMは、そのゲートで受けたデータ電圧Vdataと、そのソースで受けた駆動電圧VDDとに基づいて発光素子OLEDの発光を駆動する。このとき、駆動トランジスタMのゲート・ソース間電圧Vgs = Vg - Vs = Vdata - VDD。発光素子OLEDを流れる電流Idsと駆動トランジスタMのゲート・ソース間電圧Vgsには、次の関係がある。

30

[数式1]

$$I_{ds} = (K/2) (V_{gs} - V_{th})^2 = (K/2) (V_{data} - V_{DD} - V_{th})^2$$

40

50

## 【0015】

$K = C_o \times \mu \times W / L$ 。 $C_o$ は単位面積当たりのゲート容量であり、 $\mu$ はチャネル内の電子移動度であり、 $W / L$ は駆動トランジスタMのチャネルの幅と長の比であり、 $V_{th}$ は駆動トランジスタMの閾値電圧である。

## 【0016】

発光素子OLEDの輝度は、発光素子OLEDを流れる電流 $I_{ds}$ に正比例し、即ち、データ電圧 $V_{data}$ 、駆動電圧 $V_{DD}$ 及び駆動トランジスタMの閾値電圧 $V_{th}$ と相関している。異なる駆動トランジスタMの閾値電圧 $V_{th}$ の違いによる表示パネルの表示輝度ムラを避けるために、従来の表示パネルにおいて、画素駆動回路100'は閾値補償機能を有する駆動回路（図示せず）として設計されている。それゆえ、駆動回路は順に、リセット段階、データ書き込み段階及び発光段階で動作し、データ書き込み段階でエネルギー蓄積キャパシタCを充電してその第1端の電圧が（ $V_{data} + V_{th}$ ）の値に達するよう<sup>10</sup>にその第1端の電圧を調整する。このとき、駆動トランジスタMのゲート・ソース間電圧 $V_{gs} = V_g - V_s = (V_{data} + V_{th}) - V_{DD}$ 。発光素子OLEDを流れる電流 $I_{ds}$ と駆動トランジスタMのゲート・ソース間電圧 $V_{gs}$ には、次の数式の関係が満たされる。

## [ 数式 2 ]

$$I_{ds} = (K/2) (V_{gs} - V_{th})^2 = (K/2) (V_{data} - V_{DD})^2$$

## 【0017】

上記の数式から明らかなように、発光素子OLEDの輝度は、データ電圧 $V_{data}$ 及び駆動電圧 $V_{DD}$ と相関するが、駆動トランジスタMの閾値電圧 $V_{th}$ と相関していない。これにより、異なる駆動トランジスタMの閾値電圧 $V_{th}$ の違いによる表示パネル1の表示輝度ムラを解消することができる。しかしながら、駆動電圧 $V_{DD}$ を伝送するための電源電圧線131自体が回線インピーダンスを有するため、駆動電圧生成モジュール130との距離が異なる画素駆動回路100によって受けられる駆動電圧 $V_{DD}$ は異なる。それゆえ、駆動電圧生成モジュール130との距離が異なる発光素子OLEDの間に表示輝度の差が生じることで、ムラ現象は、徹底的に解決されることはできなく、また、表示パネル1の大型化に伴って顕著になり、ユーザの視覚体験に大きく影響する。

## 【0018】

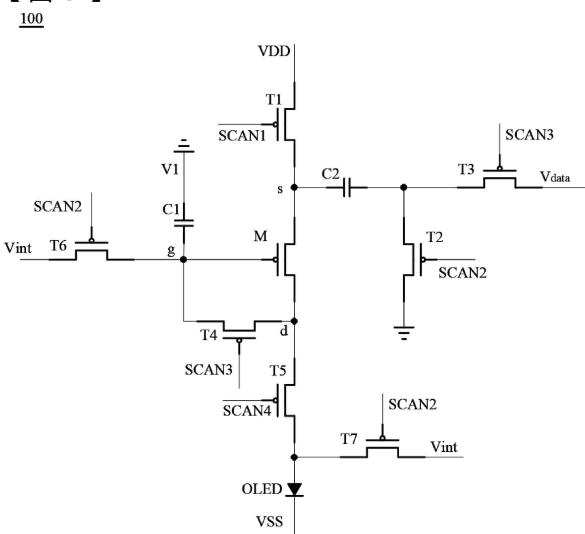

図3を参照すると、従来の画素駆動回路において電源電圧線131の回線インピーダンスによる表示パネル1の表示輝度ムラを解消するために、本出願で発光素子OLEDの発光を駆動するための画素駆動回路100が提供される。

## 【0019】

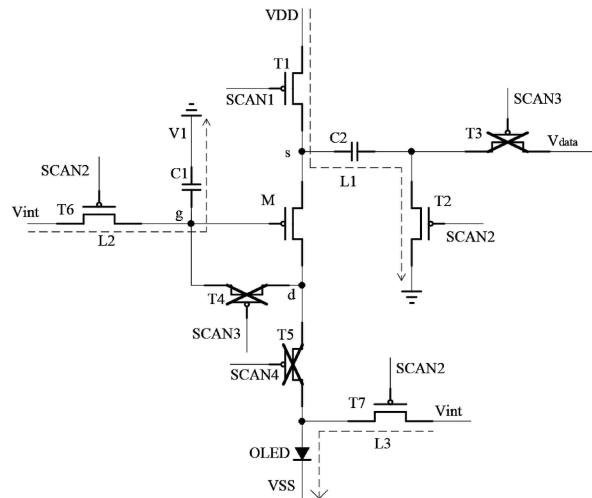

画素駆動回路100は、エネルギー蓄積キャパシタC1、ブートストラップキャパシタC2、駆動トランジスタM、第1スイッチングトランジスタT1、第2スイッチングトランジスタT2、第3スイッチングトランジスタT3、第4スイッチングトランジスタT4、第5スイッチングトランジスタT5及び第6スイッチングトランジスタT6を含む。スイッチングトランジスタT1～T6（即ち、スイッチングトランジスタT1、T2、T3、T4、T5、T6）の各々の制御端は、走査信号生成モジュール110に電気的に接続されており、スイッチングトランジスタT1～T6は、三極管（triode）又は金属酸化物半導体（Metal Oxide Semiconductor、MOS）トランジスタのうちの少なくとも一種を用いることができる。本実施形態では、スイッチングトランジスタT1～T6及び駆動トランジスタMは、いずれもPチャネル金属酸化物半導体（P-channel Metal-Oxide Semiconductor、PMOS）トランジスタなどのローレベルでオンになるトランジスタ（Low-Level Conduction Transistor）である。別の実施形態では、スイッチングトランジスタT1～T6及び駆動トランジスタMは、いずれもNチャネル金属酸化物半導体（N-channel Metal-Oxide Semiconductor、NMOS）トランジスタなどのハイレベルでオンになるトランジスタ（High-Level Conduction Transistor）である。スイッチングトランジスタT1～T6を、<sup>20</sup><sup>40</sup><sup>50</sup>

同一タイプのトランジスタとして設計することは、基板 1000 の製造工程の簡素化、加工の難しさの低減及び生産コストの低減に有利であることが理解される。当然ながら、別の実施形態では、スイッチングトランジスタ T1 ~ T6 及び駆動トランジスタ M は異なるタイプのトランジスタを採用することもでき、ここでは限定されない。なお、本出願におけるスイッチングトランジスタ T1 ~ T6 及び駆動トランジスタ M は、アモルファスシリコン薄膜トランジスタ (Amorphous Silicon Thin Film Transistor, a-Si TFT)、低温ポリシリコン薄膜トランジスタ (Low-Temperature Polysilicon TFT, LTPS TFT)、又は酸化物半導体薄膜トランジスタ (Oxide Semiconductor TFT, Oxide TFT) を採用することができる。このうち、Oxide TFT の活性層としては、酸化インジウムガリウム亜鉛 (Indium Gallium Zinc Oxide, IGZO) 等の酸化物半導体 (Oxide) を用いることができる。例示的に、スイッチングトランジスタ T1 ~ T6 は Oxide TFT を採用し、駆動トランジスタ M は低温ポリシリコントランジスタを採用する。低温ポリシリコントランジスタの移動度が高いことで、駆動トランジスタ M がオンになる速度を向上させることができ、ひいては画素駆動回路 100 の反応速度を向上させることができ、表示パネル 1 の表示効果を向上させることができる。

#### 【0020】

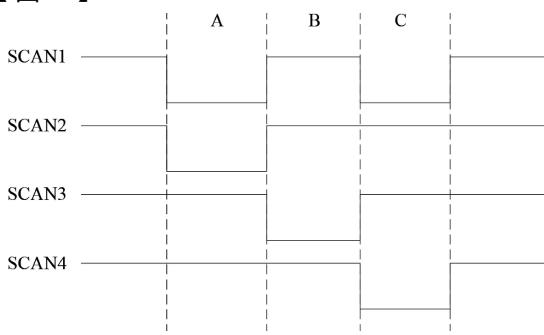

画素駆動回路 100 の回路構成及びその動作原理をより明確に説明するために、図 4、図 5a ~ 図 5c を併せて参照されたい。

#### 【0021】

図 4 に示すように、画素駆動回路 100 は、1 フレームの表示周期において、順にリセット段階 (A 段階)、データ書き込み段階 (B 段階) 及び発光段階 (C 段階) で動作する。

#### 【0022】

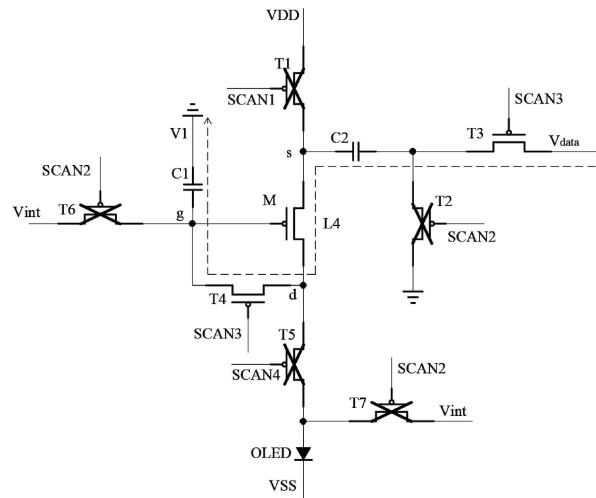

図 5a に示すように、画素駆動回路 100 は、プリチャージループ L1 とエネルギー蓄積キャパシタリセットループ L2 を備える。プリチャージループ L1 は、順に直列接続された第 1 スイッチングトランジスタ T1、ブートストラップキャパシタ C2 及び第 2 スイッチングトランジスタ T2 を含む。第 1 スイッチングトランジスタ T1 の第 1 接続端は、駆動電圧 VDD を受けるように構成されており、第 1 スイッチングトランジスタ T1 の第 2 接続端は、ブートストラップキャパシタ C2 の第 1 端に電気的に接続されている。第 2 スイッチングトランジスタ T2 の第 1 接続端は、接地端に電気的に接続されてゼロ電位の電圧を受けるように構成されており、第 2 スイッチングトランジスタ T2 の第 2 接続端は、ブートストラップキャパシタ C2 の第 2 端に電気的に接続されている。プリチャージループ L1 は、リセット段階でオンになって (即ち、第 1 スイッチングトランジスタ T1 と第 2 スイッチングトランジスタ T2 がいずれもオンになる)、駆動電圧 VDD を受けてブートストラップキャパシタ C2 を充電することにより、ブートストラップキャパシタ C2 の第 1 端の電圧が駆動電圧 VDD の値に達するようにブートストラップキャパシタ C2 の第 2 端の電圧がゼロ電位に達するようにブートストラップキャパシタ C2 の第 2 端の電圧をリセットすることで、ブートストラップキャパシタ C2 の第 1 端の電圧と第 2 端の電圧の間の差値を駆動電圧 VDD の値に達させるように構成されている。これにより、ブートストラップキャパシタ C2 は、第 2 のスイッチングトランジスタ T2 を介して前の 1 フレームの表示周期の残留電荷を接地端に放電することができることで、ブートストラップキャパシタ C2 の第 2 端の電圧がゼロ電位に達するようにブートストラップキャパシタ C2 の第 2 端の電圧をリセットして、表示パネル 1 の表示効果の均一性を確保することができる。

#### 【0023】

エネルギー蓄積キャパシタリセットループ L2 は、直列接続されたエネルギー蓄積キャパシタ C1 と第 6 スイッチングトランジスタ T6 を備える。第 6 スイッチングトランジスタ T6 の第 1 接続端は、第 1 リセット電圧を受けるように構成されており、第 6 スイッチングトランジスタ T6 の第 2 接続端は、エネルギー蓄積キャパシタ C1 の第 1 端に電気的

10

20

30

40

50

に接続されている。エネルギー蓄積キャパシタC1の第1端は、さらに駆動トランジスタMの制御端（即ち、ゲートg）に電気的に接続されている。エネルギー蓄積キャパシタC1の第2端は、電圧値が一定の第1電圧V1を受けるように構成されている。エネルギー蓄積キャパシタリセットループL2は、リセット段階でオンになって（即ち、第6スイッチングトランジスタT6がオンになる）、第1リセット電圧を受けて、エネルギー蓄積キャパシタC1の第1端の電圧をリセットするように構成されている。即ち、エネルギー蓄積キャパシタC1を充電して、その第1端の電圧が第1リセット電圧の値に達するようにその第1端の電圧をリセットする。これにより、前の1フレームの表示周期における発光段階の残留電荷がエネルギー蓄積キャパシタC1の電圧に与える影響をなくすことができる。各々の1フレームの表示周期のデータ書き込み段階で、エネルギー蓄積キャパシタC1の第1端の電圧は同じ初期値、即ち第1リセット電圧の値を有し、表示パネル1の表示効果の均一性が確保される。本実施形態では、エネルギー蓄積キャパシタC1の第2端が受ける第1電圧V1はゼロ電位の電圧であり、他の実施形態では、第1電圧V1は駆動電圧VDDであってもよい。

#### 【0024】

さらに、発光素子OLEDの第1端は基準電圧VSSを受けるように構成されており、発光素子OLEDの第2端は駆動トランジスタMの第2接続端（即ちドレインd）に電気的に接続されている。

#### 【0025】

選択的に、画素駆動回路100は、発光素子リセットループL3をさらに含む。発光素子リセットループL3は、直列接続された第7スイッチングトランジスタT7と発光素子OLEDを備える。第7スイッチングトランジスタT7の第1接続端は、第2リセット電圧を受けるように構成されており、第7スイッチングトランジスタT7の第2接続端は、発光素子OLEDの第2端に電気的に接続されている。発光素子リセットループL3は、リセット段階でオンになって（即ち、第7スイッチングトランジスタT7がオンになる）、発光素子OLEDの第2端の電圧が第2リセット電圧の値に達するように、発光素子OLEDの第2端の電圧をリセットするように構成されている。これにより、前の1フレームの表示周期における発光段階の残留電荷が発光素子OLEDの第2端の電圧に与える影響をなくすことができることで、各々の1フレームの表示周期における発光段階で、発光素子OLEDの第2端の電圧は同じ初期値、即ち第2リセット電圧の値を有し、表示パネル1の表示効果の均一性がさらに向上することができる。例示的に、第1リセット電圧の電圧値及び第2リセット電圧の電圧値は、いずれもリセット電圧Vintに等しく、 $Vint < VSS$ 。これにより、リセット段階で、第2リセット電圧が発光素子OLEDの誤発光をもたらさない。当然ながら、他の実施形態では、第1リセット電圧の電圧値と第2リセット電圧の電圧値は等しくなくてもよい。

#### 【0026】

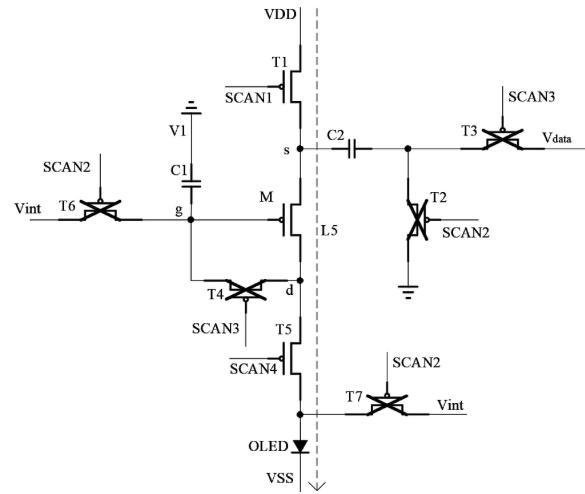

図5bに示すように、画素駆動回路100は、データ書き込みループL4をさらに含む。データ書き込みループL4は、順に直列接続された第3スイッチングトランジスタT3、ブートストラップキャパシタC2、駆動トランジスタM、第4スイッチングトランジスタT4及びエネルギー蓄積キャパシタC1を備える。具体的には、第3スイッチングトランジスタT3の第1接続端はデータ電圧Vdataを受けるうように構成されており、第3スイッチングトランジスタT3の第2接続端はブートストラップキャパシタC2の第2端に電気的に接続されおり、ブートストラップキャパシタC2の第1端はさらに駆動トランジスタMの第1接続端（即ちソースs）に電気的に接続されている。第4スイッチングトランジスタT4は、駆動トランジスタMの第2接続端とエネルギー蓄積キャパシタC1の第1端の間に電気的に接続されている。データ書き込みループL4は、データ書き込み段階でオンになって、第3スイッチングトランジスタT3の第1接続端を介してデータ電圧Vdataを受け、且つブートストラップキャパシタC2のブートストラップ効果に基づいてエネルギー蓄積キャパシタC1を充電することにより、駆動トランジスタMの制御端の電圧が第1リセット電圧の値から第2電圧の値に達するように、駆動トランジスタMの

制御端の電圧を調整するように構成されている。駆動トランジスタMは、その制御端の電圧が第2電圧に等しくなると、臨界オン状態となる。第2電圧の電圧値は、駆動電圧VDDとデータ電圧と駆動トランジスタMの閾値電圧との和に等しい。なお、リセット段階で、第3スイッチングトランジスタT3は、第2スイッチングトランジスタT2を介して前の1フレームの表示周期における残留電荷を接地端に放電することができることで、前の1フレームの表示周期における残留電荷の影響を受けることができる。

#### 【0027】

具体的には、前述したように、ブートストラップキャパシタC2の第1端の電圧と第2端の電圧の間の差値が駆動電圧VDDの値である。ブートストラップキャパシタC2は、データ電圧Vdataを受けると、その第2端の電圧がゼロ電位からVdataの値に変化し、即ちブートストラップキャパシタC2の第2端の電位がVdataの値だけ変化する。ブートストラップキャパシタC2のブートストラップ効果により、ブートストラップキャパシタC2の第1端（即ち駆動トランジスタMのソース電圧Vs）の電位も変化して（Vdata + VDD）の値に達する。データ書き込み段階で、駆動トランジスタMは、エネルギー蓄積キャパシタC1を充電する開始タイミングにおいて、ゲート電圧Vg = Vin、ソース電圧Vs = Vdata + VDD、このとき、ゲート・ソース間電圧Vgs = Vg - Vs = Vin - Vdata < Vth、従って、駆動トランジスタMがオンになる。Vthは駆動トランジスタMの閾値電圧であり、Vgs < Vthの場合、駆動トランジスタMはオンになり、Vgs > Vthの場合、駆動トランジスタMはオフになる。ソース電圧Vsは、オンになったデータ書き込みループL4を介してエネルギー蓄積キャパシタC1を充電して、エネルギー蓄積キャパシタC1の第1端の電圧を引き続き上昇させる。エネルギー蓄積キャパシタC1の第1端の電圧がVg = Vdata + VDD + Vthまで上昇すると、Vgs = (Vdata + VDD + Vth) - (Vdata + VDD) = Vthとなり、駆動トランジスタMが臨界オン状態となり、エネルギー蓄積キャパシタC1の第1端の電圧は上昇しなくなる。第2電圧の電圧値は（Vdata + VDD + Vth）となる。なお、ブートストラップキャパシタC2のブートストラップ効果により、データ電圧Vdataがエネルギー蓄積キャパシタC1に伝達される速度が速く、ひいてはデータ書き込み段階の時間長を縮め、1フレームの表示周期の時間長を低くすることができ、表示パネル1のリフレッシュレートを高めることに有利である。

#### 【0028】

図5cに示すように、画素駆動回路100は、発光ループL5をさらに含む。発光ループL5は、順に直列接続された第1スイッチングトランジスタT1、駆動トランジスタM、第5スイッチングトランジスタT5及び発光素子OLEDを備える。第5スイッチングトランジスタT5は、駆動トランジスタMの第2接続端と発光素子OLEDの第2端の間に電気的に接続されている。発光ループL5は、発光段階でオンになって、駆動トランジスタMの第1接続端で駆動電圧VDDを受けて、発光素子OLEDの発光を駆動するよう構成されている。

#### 【0029】

具体的には、発光段階で、駆動トランジスタMはオン状態を継続する。第1スイッチングトランジスタT1と第5スイッチングトランジスタT5は、いずれも線形領域で動作する一方、駆動トランジスタMは飽和領域で動作するため、発光素子OLEDを流れる電流の大きさは、駆動トランジスタMのソースとドレインとの間の電流Idsに主に依存する。スイッチングトランジスタの動作特性に基づいて、電流Idsとゲート・ソース間電圧Vgsとの間には、次の数式の関係が満たされていることが分かる。

##### [数式3]

$$I_{ds} = (K/2) (V_{gs} - V_{th})^2 = (K/2) (V_{data})^2$$

#### 【0030】

$K = C_o \times \mu \times W/L$ 、 $C_o$ は単位面積当たりのゲート容量であり、 $\mu$ はチャネル内の電子移動度であり、 $W/L$ は駆動トランジスタMのチャネルの幅と長の比である。

#### 【0031】

10

20

30

40

50

上記の数式から明らかなように、データ書き込みループ L 4 が補償電圧を駆動トランジスタ M に提供することができることで、発光素子 O L E D を流れる電流 I d s が駆動トランジスタ M の閾値電圧 V t h 及び駆動電圧 V D D と相関しなくなる。即ち、データ電圧 V d a t a の書き込み精度を保証すれば、発光素子 O L E D の発光輝度を高精度に制御することができる。従って、本出願で提供される画素駆動回路 1 0 0 は、異なる画素駆動回路 1 0 0 における駆動トランジスタ M の閾値電圧の違いによる表示パネル 1 の表示輝度ムラだけでなく、異なる画素駆動回路 1 0 0 によって受けられた駆動電圧 V D D の違いによる表示パネル 1 の表示輝度ムラを解消することができる。また、発光素子 O L E D を流れる電流 I d s は、駆動電圧 V D D と相関していない。発光素子 O L E D の第 1 端と第 2 端の間の電圧差が変わらなければその発光輝度が変化しないという特性により、駆動電圧 V D D の電圧値を適量に低下させて、画素駆動回路 1 0 0 の消費電力を低減することができる。10

#### 【 0 0 3 2 】

前述したように、本実施形態では、スイッチングトランジスタ T 1 ~ T 7 と駆動トランジスタ M はいずれもローレベルでオンになるトランジスタである。次に、図 3 ~ 図 5 c に合わせて、本出願で提供される画素駆動回路 1 0 0 が 1 フレームのスキャン周期における動作フローについて、詳細に説明する。

#### 【 0 0 3 3 】

本出願の実施形態では、第 1 スイッチングトランジスタ T 1 の制御端が受ける走査信号は、第 1 走査信号 S C A N 1 である。第 2 スイッチングトランジスタ T 2 、第 6 スイッチングトランジスタ T 6 及び第 7 スイッチングトランジスタ T 7 の制御端が受ける走査信号は、いずれも第二走査信号 S C A N 2 である。第 3 スイッチングトランジスタ T 3 及び第 4 スイッチングトランジスタ T 4 の制御端が受ける走査信号は、いずれも第 3 走査信号 S C A N 3 である。第 5 スイッチングトランジスタ T 5 の制御端が受ける走査信号は、第 4 走査信号 S C A N 4 である。同一の導通タイミングを有するスイッチングトランジスタは同一の走査信号によって制御されることで、基板 1 0 0 0 の配線構造が簡素化されることができる。当然ながら、他の実施形態では、スイッチングトランジスタ毎に別々に 1 つの走査信号を設けてスイッチングトランジスタを制御することができ、ここで限定されない。20

#### 【 0 0 3 4 】

リセット段階 ( A 段階 ) では、第 1 走査信号 S C A N 1 と第 2 走査信号 S C A N 2 がいずれもローレベルであり、第 3 走査信号 S C A N 3 と第 4 走査信号 S C A N 4 がいずれもハイレベルである。従って、スイッチングトランジスタ T 1 、 T 2 、 T 6 、 T 7 が共にオンになり、スイッチングトランジスタ T 3 ~ T 5 が共にオフになる。これにより、プリチャージループ L 1 はオンになって、ブートストラップキャパシタ C 2 の第 1 端の電圧が駆動電圧 V D D の値に達するようにブートストラップキャパシタ C 2 の第 1 端の電圧を調整し、ブートストラップキャパシタ C 2 の第 2 端の電圧がゼロ電位に達するようにブートストラップキャパシタ C 2 の第 2 端の電圧をリセットする。エネルギー蓄積キャパシタリセットループ L 2 はオンになって、エネルギー蓄積キャパシタ C 1 の第 1 端の電圧が第 1 リセット電圧の値に達するようにエネルギー蓄積キャパシタ C 1 の第 1 端の電圧をリセットする。発光素子リセットループ L 3 は共にオンになって、発光素子 O L E D の第 2 端の電圧が第 2 リセット電圧の値に達するように発光素子 O L E D の第 2 端の電圧をリセットする。また、データ書き込みループ L 4 及び発光ループ L 5 はオフになる。30

#### 【 0 0 3 5 】

データ書き込み段階 ( B 段階 ) では、第 3 走査信号 S C A N 3 はローレベルであり、第 1 走査信号 S C A N 1 、第 2 走査信号 S C A N 2 及び第 4 走査信号 S C A N 4 はいずれもハイレベルである。従って、スイッチングトランジスタ T 3 、 T 4 及び駆動トランジスタ M は共にオンになり、スイッチングトランジスタ T 1 、 T 2 、 T 5 、 T 6 、 T 7 は共にオフになる。これにより、データ書き込みループ L 4 はオンになって、駆動トランジスタ M の制御端の電圧が第 1 リセット電圧の値から第 2 電圧の値に達するように、駆動トランジスタ M の制御端の電圧を調整する。プリチャージループ L 1 、エネルギー蓄積キャパシタリセットループ L 2 はオフになる。40

リセットループ L 2、発光素子リセットループ L 3 及び発光ループ L 5 はいずれもオフになる。

【 0 0 3 6 】

発光段階 ( C 段階 ) では、第 1 走査信号 S C A N 1 と第 4 走査信号 S C A N 4 がいずれもローレベルであり、第 2 走査信号 S C A N 2 と第 3 走査信号 S C A N 3 がいずれもハイレベルである。これにより、スイッチングトランジスタ T 1、T 5 及び駆動トランジスタ M が共にオンになり、スイッチングトランジスタ T 2、T 3、T 4、T 6、T 7 が共にオフになることで、発光ループ L 5 はオンになって、駆動電圧 V D D を受けて発光素子 O L E D の発光を駆動し、プリチャージループ L 1、エネルギー蓄積キャパシタリセットループ L 2、発光素子リセットループ L 3 及びデータ書き込みループ L 4 は共にオフになる。

10

【 0 0 3 7 】

本出願で提供される画素駆動回路 1 0 0 は、リセット段階で、プリチャージループ L 1 を介して、ブートストラップキャパシタ C 2 の第 1 端の電圧が駆動電圧 V D D の値に達するようにブートストラップキャパシタ C 2 を充電し、データ書き込み段階で、ブートストラップキャパシタ C 2 の第 2 端を介してデータ電圧 V d a t a を受けて、ブートストラップキャパシタ C 2 のブートストラップ効果に基づいて、エネルギー蓄積キャパシタ C 1 を充電することで、駆動トランジスタ M の制御端の電圧を第 2 電圧に調整し、第 2 電圧の電圧値は、駆動電圧 V D D 、データ電圧 V d a t a 及び駆動トランジスタ M の閾値電圧 V t h の和と等しく、また、発光段階で、駆動トランジスタ M にその制御端で受けた第 2 電圧及びその第 1 接続端で受けた駆動電圧 V D D に基づいて、発光素子 O L E D の発光を駆動させて、発光素子 O L E D を流れる電流が駆動電圧 V D D 及び駆動トランジスタ M の閾値電圧 V t h と相関しなくなることで、異なる画素駆動回路 1 0 0 における駆動トランジスタ M の閾値電圧の違いによる表示パネル 1 の表示輝度ムラを解消するだけでなく、異なる画素駆動回路 1 0 0 によって受けられた駆動電圧 V D D の違いによる表示パネル 1 の表示輝度ムラを解消することもできる。

20

【 0 0 3 8 】

以上、本出願の実施形態は既に示されて説明されているが、本出願の原理や要旨を逸脱しない範囲でこれらの実施形態に様々な改変、修正、置換、変形を行うことができ、本出願の範囲は、特許請求の範囲とその均等物によって限定されることは当業者に理解されることができる。

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5 a】

100

【図5b】

100

【図 5 c】

100

10

20

30

40

50

## フロントページの続き

(51)国際特許分類

F I

G 09 G 3/20 611H

G 09 G 3/20 611J

H 10 K 59/123

t r e e t , B a o a n D i s t r i c t , S h e n z h e n , C h i n a

(74)代理人 100079108

弁理士 稲葉 良幸

(74)代理人 100109346

弁理士 大貫 敏史

(74)代理人 100117189

弁理士 江口 昭彦

(74)代理人 100134120

弁理士 内藤 和彦

(72)発明者 周仁杰

中華人民共和国広東省深セン市宝安区石岩街道石龍社区工業二路1号恵科工業園厂房1棟一層至三層、五至七層，6棟七層

(72)発明者 李榮榮

中華人民共和国広東省深セン市宝安区石岩街道石龍社区工業二路1号恵科工業園厂房1棟一層至三層、五至七層，6棟七層

審査官 西島 篤宏

(56)参考文献 中国特許出願公開第112908258(CN, A)

特開2006-091923(JP, A)

特開2019-066517(JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

H 10 K 59 / 123