#### (19) World Intellectual Property Organization

International Bureau

US

(43) International Publication Date 4 January 2007 (04.01.2007)

(51) International Patent Classification: HOlL 21/471 (2006.01)

(21) International Application Number:

PCT/US2006/020508

(22) International Filing Date: 26 May 2006 (26.05.2006)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/167,526 27 June 2005 (27.06.2005)

- (71) Applicant (for all designated States except US): AP¬ PLIED MATERIALS, INC. [US/US]; 3050 Bowers Avenue, Santa Clara, California 95054 (US).

- (71) Applicant and

- (72) Inventor: OLSEN, Christopher, S. [US/US]; 4024 RaIson Common, Fremont, California 94538 (US).

- (74) Agents: PATTERSON, B., Todd et al.; PATTERSON & SHERIDAN LLP, 3040 Post Oak Blvd., Suite 1500, Houston, Texas 77056 (US).

## (10) International Publication Number WO 2007/001709 A2

- (81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW

- (84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

[Continued on next page]

(54) Title: IMPROVED MANUFACTURING METHOD FOR TWO-STEP POST NITRIDATION ANNEALING OF PLASMA NITRIDED GATE DIELECTRIC

(57) Abstract: A method of forming a silicon oxynitride gate dielectric. The method includes incorporating nitrogen into a dielectric film using a plasma nitridation process to form a silicon oxynitride film. The silicon oxynitride film is annealed in a first ambient. The first ambient comprises an inert ambient with a first partial pressure of oxygen at a first temperature. The silicon oxynitride film is then annealed in a second ambient comprising a second partial pressure of oxygen at a second temperature. The second partial pressure of oxygen is greater than the first partial pressure of oxy-

####

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# IMPROVED MANUFACTURING METHOD FOR TWO-STEP POST NITRIDATION ANNEALING OF PLASMA NITRIDED GATE DIELECTRIC

# **BACKGROUND OF THE INVENTION**

#### Field of the Invention

[0001] Embodiments of the present invention generally relate to the field of semiconductor manufacturing. More specifically, the present invention relates to a method of forming a silicon oxynitride (SiO<sub>x</sub>Ny) gate dielectric and integrating it into a gate stack using plasma nitridation and a two-step post plasma nitridation annealing (PNA) process.

### **Description of the Related Art**

[0002] Integrated circuits are made up of literally millions of active and passive devices that function as basic components such as transistors, capacitors and resistors. A transistor generally includes a source, a drain, and a gate stack. The gate stack consists of the substrate (silicon) on top of which is grown a dielectric (usually silicon dioxide: SiO2) and this is capped with an electrode (such as polycrystalline silicon).

[0003] As integrated circuit sizes and the sizes of the transistors thereon decrease, the gate drive current required to increase the speed of the transistor has increased. Because the drive current increases as the gate capacitance increases, and capacitance is inversely proportional to the gate dielectric thickness, decreasing the dielectric thickness is one method of increasing the drive current.

[0004] Attempts have been made to reduce the thickness of Si $\theta$  2 gate dielectrics below 20 A. However, it has been found that the use of thin Si $\theta$  2 gate dielectrics below 20 A often results in undesirable effects on gate performance and durability. For example, boron from a boron doped gate electrode can penetrate through a thin Si $\theta$  2 gate dielectric into the underlying silicon substrate. Also, there is typically an increase in gate leakage, *i.e.*, tunneling, with thin dielectrics that increases the

amount of power consumed by the gate. Thin  $Si\theta 2$  gate dielectrics may be susceptible to hot carrier damage, in which high energy carriers traveling across the dielectric can damage or destroy the gate. Thin  $Si\theta 2$  gate dielectrics may also be susceptible to negative bias temperature instability (NBTI), wherein the threshold voltage or drive current drifts with operation of the gate.

[0005] Consequently, there is a need for an alternative gate dielectric material that can be used in a large enough physical thickness to reduce current leakage density and still provide a high gate capacitance. In order to achieve this, the alternative gate dielectric material must have a dielectric constant that is higher than that of silicon dioxide. Typically, the thickness of such an alternative dielectric material layer is expressed in terms of the equivalent oxide thickness (EOT). Thus, the EOT of an alternative dielectric layer in a particular capacitor is the thickness that the alternative dielectric layer would have if its dielectric constant were that of silicon dioxide.

[0006] One method that has been used to address the problems with thin SiO2 gate dielectrics is to incorporate nitrogen into the SiO2 layer to form a  ${\rm SiO}_{\rm x}$  Ny gate dielectric. Incorporating nitrogen into the SiO2 layer blocks boron penetration into the underlying silicon substrate and raises the dielectric constant of the gate dielectric, allowing the use of a thicker dielectric layer.

[0007] Thermally grown silicon oxynitride has been used as gate dielectrics for several years from the 0.2  $\mu$ m to 0.13  $\mu$ m device generations. As the device technology has advanced from 0.2  $\mu$ m to 0.1  $\mu$ m the gate oxide has thinned from > 25 A to < 12 A. In order to block boron and reduce gate leakage the amount of nitrogen in the film has been increased from <3% for 25 A SiO $_{\rm x}$ Ny layers to 5-10% for 12 A SiO $_{\rm x}$ Ny layers. When nitric oxide (NO) and nitrous dioxide (N $_{\rm 2}$ O) are used to grow the oxynitride gate dielectric the nitrogen gets incorporated in the dielectric film simultaneously as the oxynitride grows, hence nitrogen is distributed evenly in the film. If NO or N $_{\rm 2}$ O are used to form silicon oxynitride by annealing an existing SiO $_{\rm 2}$  layer at elevated temperatures, the nitrogen is incorporated by growing SiON at

the Si-substrate/Oxide interface. The amount of Nitrogen in the latter case (<2%) is less than in the former case (4-5%).

[0008] More recently, plasma nitridation (PN) has been used to nitride (to incorporate nitrogen into) the gate oxide. This technique results in high nitrogen concentration at the poly gate/oxide interface, which prevents boron penetration into the oxide dielectric. At the same time, the bulk of the oxide dielectric gets lightly doped with unassociated nitrogen during the plasma nitridation process, which reduces the electrical oxide thickness (EOT) over the starting oxide. This allows one to achieve a gate leakage reduction at the same EOT higher than conventional thermal processes. Scaling this dielectric in the EOT < 12 A range while preserving good channel mobility and drive current (Idsat) has been the industry challenge.

[0009] Post Nitridation Annealing (PNA) of the silicon oxynitride at high temperature has been shown as a method of improving the peak transconductance as a proxy for channel mobility, at the expense of the EOT increasing. These results are demonstrated in U.S. Patent Application Publication No. 2004/0175961, filed on March 4, 2004, entitled "Two-Step Post Nitridation Annealing For Lower EOT Plasma Nitrided Gate Dielectrics," assigned to Applied Materials, Inc., which is herein incorporated by reference to the extent it does not conflict with this application.

[0010] At low pressure and high temperature,  $SiO_2$  will breakdown into SiO which desorbs from the silicon surface resulting in a phenomenon called pitting.

[0011] Thus, there remains a need for an improved post anneal method for depositing a silicon oxynitride gate dielectric that has thinner EOTs with improved mobility while accounting for the problem of silicon monoxide desorption.

# SUMMARY OF THE INVENTION

[0012] Embodiments of the present invention generally provide a method of forming a  $SiO_x$  Ny gate dielectric. The method comprises incorporating nitrogen into a dielectric film using a plasma nitridation process to form a silicon oxynitride film.

The silicon oxynitride film is then subjected to a two-step post plasma anneal. The first step involves annealing the silicon oxynitride film in a first ambient comprising an inert ambient with a first partial pressure of oxygen at a first temperature. The second step involves annealing the silicon oxynitride film in a second ambient comprising a second partial pressure of oxygen at a second temperature wherein the second partial pressure of oxygen is greater than the first partial pressure of oxygen. In one embodiment, the first partial pressure of oxygen is between about 1 mTorr and 100 mTorr and the second partial pressure of oxygen is between about 0.1 Torr and IOO Torr.

[0013] In another embodiment, a gate electrode is deposited on the silicon oxynitride film after the two-step post plasma annealing. In one embodiment the gate electrode comprises a polysilicon film. In another embodiment, the gate electrode comprises an amorphous silicon film. In another embodiment, the gate electrode comprises a metal electrode.

Embodiments of the invention also provide a method of forming a SiO<sub>x</sub> Ny [0014] gate dielectric in an integrated processing system. A silicon substrate is introduced into a first processing chamber of the integrated processing system where a silicon dioxide film is formed on the substrate. The substrate is transferred to a second processing chamber of the integrated processing system where the substrate is exposed to a plasma comprising a nitrogen source. The substrate is then transferred to a third processing chamber of the integrated processing system where the substrate is subjected to a two-step post plasma anneal. The first step involves annealing the silicon oxynitirde film in a first ambient comprising an inert ambient with a first partial pressure of oxygen at a first temperature. The second step involves annealing the silicon oxynitride film in a second ambient comprising a second partial pressure of oxygen at a second temperature wherein the second partial pressure of oxygen is greater than the first partial pressure of oxygen. another embodiment, the plasma nitridation process includes decoupled plasma nitridation.

[0015] In another embodiment, a SiO Ny gate dielectric is formed by a method

comprising heating a structure comprising a silicon oxide film on a silicon substrate in an atmosphere comprising NH3 to incorporate nitrogen into the silicon oxide film, and then exposing the structure to a plasma comprising a nitrogen source to form a SiO, Ny gate dielectric on the substrate.

# BRIEF DESCRIPTION OF THE DRAWINGS

[0016] So that the manner in which the above recited features of the present invention can be understood in detail, a more particular description of the invention, briefly summarized above, may be had by reference to embodiments, some of which are illustrated in the appended drawings. It is to be noted, however, that the appended drawings illustrate only typical embodiments of this invention and are therefore not to be considered limiting of its scope, for the invention may admit to other equally effective embodiments.

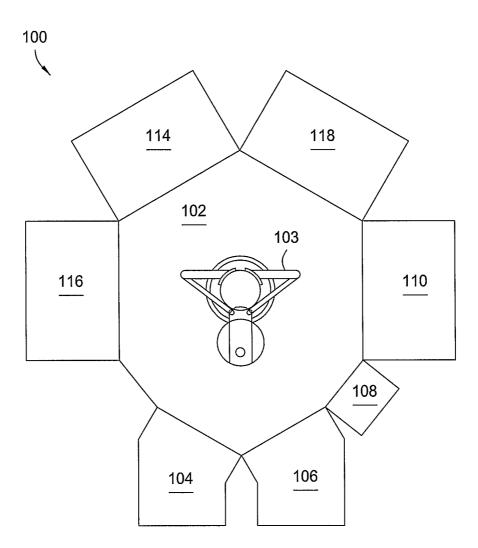

[0017] Figure 1 is a top schematic view of an integrated processing system.

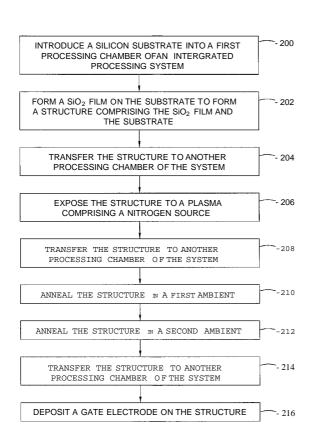

[0018] Figure 2 is a flow chart depicting an embodiment of the invention.

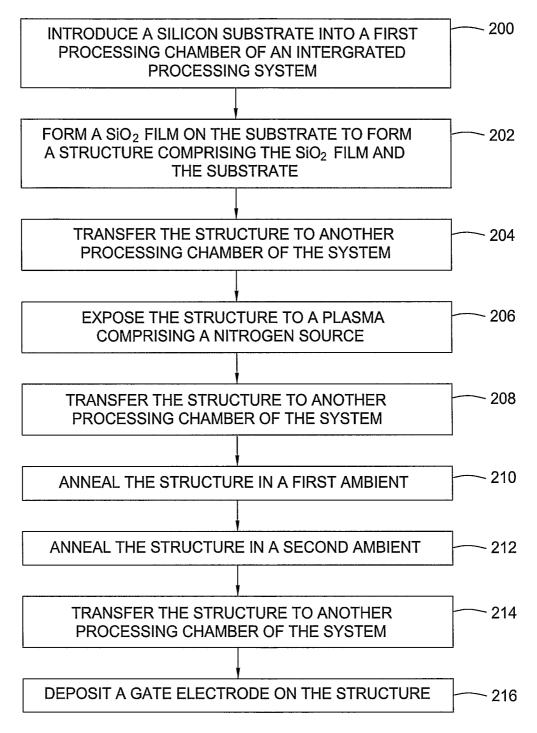

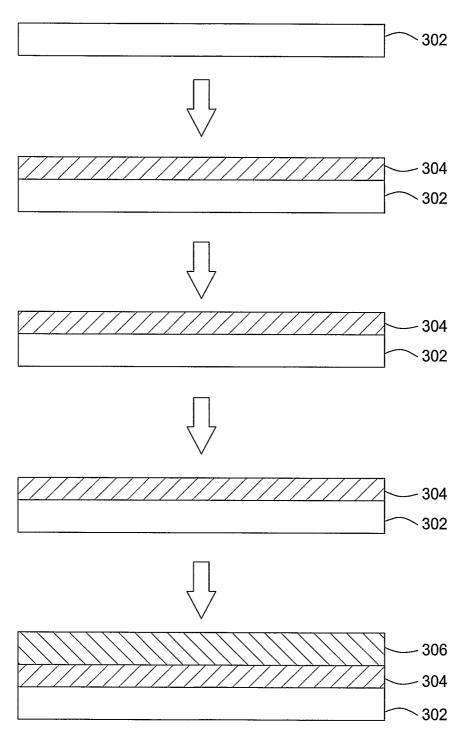

[0019] Figure 3 illustrates an exemplary sequence of forming a gate stack in accordance with the embodiments of the present invention.

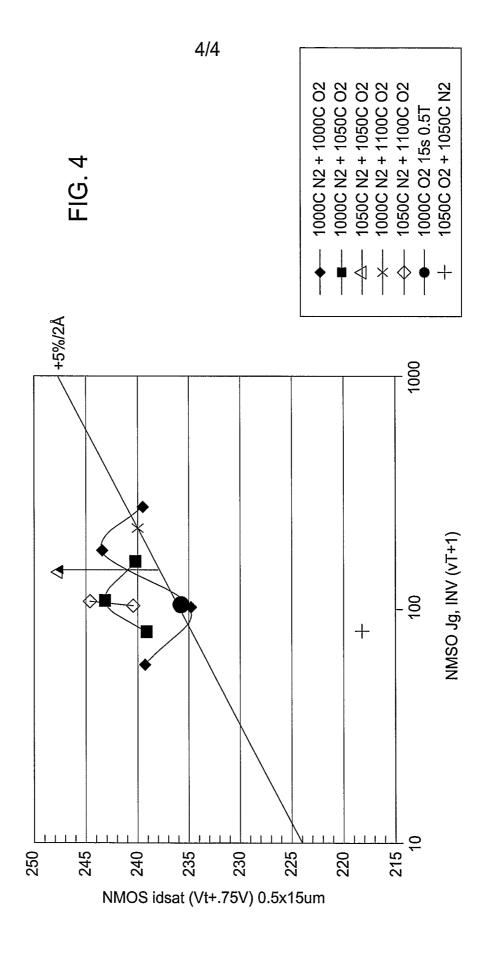

[0020] Figure 4 is a graph showing Negative Channel Metal Oxide Semiconductor (NMOS) drive current relative to NMOS gate leakage for gate stacks comprising SiO, Ny gate dielectrics.

# **DETAILED DESCRIPTION**

[0021] Embodiments of the invention include a method of forming a dielectric that includes nitrogen, such as  ${\rm SiON}$  or  ${\rm SiO}_{\rm x}$  Ny (silicon oxynitride) using a nitrogen plasma (or plasma nitridation) process. The silicon oxynitride is then subjected to a two-step post plasma nitridation annealing processes. The embodiments allow for the control of the EOT and the nitrogen concentration profile of the silicon oxynitride film.

5

[0022] In the following description, for purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be evident, however, to one skilled in the art that the present invention may be practiced without these specific details. In other instances, specific apparatus structures and methods have not been described so as not to obscure the present invention. The following description and drawings are illustrative of the invention and are not to be construed as limiting of the invention.

[0023] In one embodiment, there is provided a method of forming a silicon oxynitride dielectric film using a plasma nitridation process such as Decoupled Plasma Nitridation (DPN). After the plasma nitridation, the silicon oxynitride is subjected to a two-step post plasma nitridation annealing (PNA) process. A first PNA step is performed using an inert agent in combination with a trace amount of oxygen to densify the silicon oxynitride. A second PNA step is performed with an oxidizing agent to modify the nitrogen concentration profile. The two-step PNA process moves nitrogen towards the surface of the silicon oxynitride and the substrate thus blocking Boron more efficiently. In addition, the concentration profile of nitrogen tends to peak at the surface of the silicon oxynitride.

[0024] In another embodiment, there is provided a method of integrating the silicon oxynitride film formed using a plasma nitridation process followed by a two-step PNA process into a gate stack for forming a semiconductor device such as a transistor.

[0025] In another embodiment, a substrate having a silicon dioxide film formed thereon is subjected to a plasma nitridation process to convert the silicon dioxide film into silicon oxynitride film. In one embodiment, the plasma nitridation process used is Decoupled Plasma Nitridation (DPN), which is known in the art. DPN is a technology using inductive coupling to generate nitrogen plasma and incorporate a high level of nitrogen into an oxide film. In DPN, a surface film, e.g., an SiO<sub>2</sub> film, is bombarded with nitrogen ions which break the SiO<sub>2</sub> film forming a silicon oxynitride film. In one embodiment, DPN is performed in a chamber with pressure ranging from about 5-20 mTorr or 10-20 mTorr, with a plasma power of 200-800 Watt. The

nitrogen gas may be flown into the chamber at a flow rate ranging from about 100-200 seem. In one embodiment, the DPN uses a pulse radio frequency plasma process at about 10-20 MHz and pulse at about 5-15 kHz. The DPN process parameters can be modified depending on the chamber size and volume, and the desired thickness of the dielectric film.

[0026] Other details of the Decoupled Plasma Nitridation chamber are described in U.S. Patent Application Publication No. 2004/0242021, entitled "Method And Apparatus For Plasma Nitridation Of Gate Dielectrics Using Amplitude Modulated Radio Frequency Energy," assigned to Applied Materials, Inc., and herein incorporated by reference to the extent not inconsistent with the invention. Examples of suitable DPN chambers include the DPN Centura<sup>TM</sup>, which is commercially available from Applied Materials, Inc., Santa Clara, CA.

[0027] In one embodiment, the silicon oxynitride film is annealed twice. In the first annealing step, the silicon oxynitride is annealed to densify the nitrogen concentration. The first annealing step is carried out in an inert ambient, using an inert gas such as N<sub>2</sub>, He, Ar, or a combination thereof combined with a trace amount of oxygen. In one embodiment, the first annealing step is carried out immediately after the plasma nitridation process. In one embodiment, the first PNA step is performed at a temperature between about 700 °C and about 1100 °C, such as a temperature between about 950 °C and 1100 °C for 1-120 seconds at a pressure ranging from about 100 mTorr to about 800 Torr with the trace amount of oxygen at a partial pressure ranging from about 1 mTorr to about 100 mTorr, such as a partial pressure between about 1 mTorr and 50 Torr. In another embodiment, the trace amount of oxygen is at a partial pressure ranging from about 1 mTorr to about 30 mTorr. The second PNA step follows the first PNA step. In one embodiment, after the first PNA step, the annealing ambient is changed over to one which contains an oxidizing agent (or an oxygen comprising agent) such as O2, O2/N2, O2/Ar, O2/He, N2O, or NO. The second PNA step is carried out at reduced pressure ranging from about 10 mTorr to about 100 Torr and at a temperature between about 900 °C and about 1100°C or between about 1000°C and 1050°C. The second PNA step can be carried out for about 1-120 seconds. In one embodiment, the temperature, time,

and pressure of the second PNA step are controlled to achieve a 0.1 A to 2 A increase in the EOT of the silicon oxynitride.

[0028] In one embodiment, both the first PNA step and the second PNA step are performed in a single wafer rapid thermal processing (RTP) chamber configured to carry out the rapid thermal annealing (RTA) process. A commercially available reduced pressure (RTP) chamber hardware such as XE, XE Plus or Radiance made by Applied Materials, Inc. can be used to carry out the first and second PNA processes.

[0029] Preferably, the  $\mathrm{SiO}_{x}$  Ny gate dielectric described herein comprises at least 5 atomic percent nitrogen. In one embodiment, the  $\mathrm{SiO}_{x}$  Ny gate dielectric comprises between about 5 atomic percent nitrogen and about 15 atomic percent nitrogen.

[0030] After the structure is exposed to the plasma and annealed, a gate electrode, such as a polysilicon layer, an amormphous silicon layer, or a metal layer may be deposited on the  $SiO_x$  Ny gate dielectric to complete a gate stack.

### [0031] Integrated Processing Sequence

In a further embodiment, a SiO<sub>x</sub> Ny gate dielectric may be formed on a substrate in an integrated processing system, such as an integrated semiconductor processing system, in a method in which the substrate is not removed from the integrated processing system until after the SiO<sub>x</sub> Ny gate dielectric is formed. An example of an integrated processing system 100 that may be used is the Gate Stack Centura® system, available from Applied Materials, Inc. of Santa Clara, CA, which is shown in Figure 1. The integrated processing system 100 includes a central transfer chamber 102, a transfer robot 103, load locks 104, 106, a cool down chamber 108, a deposition chamber 110, a plasma processing chamber 114, and two rapid thermal processing (RTP) chambers 116 and 118. The deposition chamber 110 can be a conventional chemical or physical vapor deposition that can be used to form a film or a layer as is know in the art. In one embodiment, CVD processing chamber 110 is a

low pressure chemical vapor deposition chamber (LPCVD), such as a POLYgen chamber, available from Applied Materials. The RTP chambers 116 and 118 are chambers that can run a rapid thermal annealing (RTA) process at a reduced or ultra-low pressure (e.g., about equal to or less than 10 Torr).

[0033] In another embodiment, a substrate is introduced into an integrated processing system and a silicon oxide film, a  $\mathrm{SiO}_{\mathrm{x}}$  Ny gate dielectric, and a gate electrode are deposited on the substrate without removing the substrate from the integrated processing system. This embodiment will be described below with respect to Figures 1 and 2.

[0034] The processing conditions for embodiments in which the SiO<sub>x</sub> Ny gate dielectric is formed in an integrated processing system are the same as the processing conditions described above for the formation of the silicon oxide film and the SiO, Ny gate dielectric. A silicon substrate is introduced into the integrated processing system 100 via a load lock 104 or 106 and placed in RTP chamber 116, where a silicon oxide film is formed on the silicon substrate, as shown in steps 200 and 202 of Figure 2. The structure, including the substrate and the silicon oxide film is then transferred to a plasma processing chamber 114, where it is exposed to a plasma comprising a nitrogen source to incorporate nitrogen into the silicon oxide film and form the  $\mathrm{SiO}_{\mathrm{x}}\,\mathrm{Ny}$  gate dielectric, as shown in steps 204 and 206. The structure is transferred to RTP chamber 116 as shown in step 208 where the structure is annealed, as shown in steps 210 and 212. The structure is then transferred to CVD processing chamber 110, as shown in step 214, and a gate electrode, such as a polysilicon layer or an amorphous silicon layer is deposited on the structure, as shown in step 216. The structure is then removed from the integrated processing system 100 via a load lock 104 or 106.

[0035] In the embodiment described above with respect to Figures 1 and 2, the silicon oxide film is formed on the substrate in RTP chamber 116 in one step and the structure is annealed in RTP chamber 118 in another step. In an alternative embodiment, a single RTP chamber is configured to form the silicon oxide film and

to also perform the two-step post plasma anneal.

[0036] In another embodiment a structure comprising a silicon dioxide film on a silicon substrate is heated in an atmosphere comprising IMH3 in a first processing chamber of the integrated processing system to incorporate nitrogen into the silicon oxide film. Because the substrate is exposed to an atmosphere comprising NH3 within an enclosed integrated processing system, contaminating oxygen is typically not incorporated into the structure during the heating in an atmosphere comprising NH3. The structure is then transferred to a second processing chamber of the integrated processing system and exposed to a plasma comprising a nitrogen source in the second processing chamber. After exposing the structure to the plasma, the structure is transferred to a third processing chamber of the integrated processing system and annealed in the third processing chamber.

[0037] It is believed that heating the structure in an atmosphere comprising NH3 prior to treating the structure with a plasma comprising nitrogen smoothens the interface between the gate dielectric and the underlying silicon substrate, resulting in enhanced device performance and reliability. It is also believed that the formation of a slightly thicker oxide film by heating the structure first in an atmosphere comprising NH3 prior to plasma treating the structure enhances the performance characteristics of a PMOS device.

[0038] Figure 3 illustrates an exemplary sequence of forming a gate stack in accordance with embodiments of the present invention. The substrate 302 can be a monocrystalline silicon or a semiconductor wafer typically used in making semiconductor devices. In one embodiment, the SiO<sub>2</sub> film 304 has a physical thickness of about 4-1 5 A.

[0039] In one embodiment, the  ${\rm SiO}_2$  film 304 is grown using a reduced pressure RTP chamber such as the RTP chamber 116 of the integrated processing system 100 (Fig. 1). The  ${\rm SiO}_2$  film 304 is formed by a rapid thermal oxidation, which is an oxidation process where the chamber uses lamps to quickly heat and dry a substrate surface to form an oxidized layer in the presence of oxygen. The rapid

thermal oxidation of a silicon substrate (or a wafer) is carried out using a dry process rapid thermal oxidation with the presence of O2,  $O_2+N_2$ , O2+Ar, N2O, or  $N_2O+N_2$  gas mixtures. The gas or gas mixtures can have a total flow rate of about 1-5 slm. Alternatively, the rapid thermal oxidation of a silicon substrate is carried out using a wet process such as In-Situ Steam Generation (ISSG) with the presence of  $O_2+H_2$ ,  $O_2+H_2+N_2$ , or  $N_2O+H_2$  having, for example, a total flow rate of about 1-5 slm with 1-13%  $H_2$ . In one embodiment, the rapid thermal oxidation process used to form the  $SiO_2$  dielectric film is performed at a processing temperature of about 750-1000  $^0$ C and a processing pressure of about 0.5-50 Torr for about 5-90 seconds which results in an  $SiO_2$  dielectric film having a thickness in the range of about 4-15 A.

In one embodiment, after the  ${\rm SiO}_2$  film 304 is formed in the RTP chamber 116, the substrate 302 is transferred to the DPN chamber 114 of the integrated processing system 100 under an inert (e.g.,  ${\rm N}_2$  or Ar) environment with the transfer chamber pressure being approximately at the same pressure for the plasma nitiridation process. The plasma nitridation process exposes the  ${\rm SiO}_2$  film 304 to nitrogen plasma and incorporates nitrogen into the  ${\rm SiO}_2$  film 304 to form a silicon oxynitride film 304. In one embodiment, the DPN chamber 114 is a reduced pressure inductively coupled RF plasma reactor that can accommodate an inert gas such as  ${\rm N}_2$ , He, or Ar.

[0041] The silicon oxynitride film 304 is then subjected to a two-step post nitridation anneal (PNA) process in an RTP chamber, e.g. the RTP chamber 118 of the integrated processing system 100. The RTP chamber 118 can be a reduced pressure chamber reactor such as an Applied Materials reactor XE, XE Plus, or Radiance. The PNA occurs, first in a mild oxidizing ambient (inert ambient) to densify the nitrogen plasma treated film (the silicon oxynitride film 304) at a temperature of about equal to or greater than  $700\,^{\circ}$ C, followed by a second anneal in an oxidizing ambient at a temperature of about equal to or greater than  $900\,^{\circ}$ C. For the first PNA step, an inert gas (e.g.,  $N_2$  or Ar) with a trace amount of  $O_2$  is flown into the RTP chamber to densify the silicon oxynitride film 304. In one embodiment the first PNA includes heating up the substrate having the silicon oxynitride film 304 to the appropriate annealing temperature of about equal to or greater than  $700\,^{\circ}$ C at

less than or equal to about 5 Torr total pressure. In one embodiment, the inert gas such as  $N_2$  gas of about 1 slm is flown into the RTP chamber for about 60-120 seconds and a trace amount of oxygen is flown into the chamber at a flow rate of about 30 seem and a pressure of about 5 Torr. Following the first PNA, the RTP chamber is evacuated of the inert gas and an oxidizing gas such as  $O_2$  is flown into the RTP chamber for the second PNA. The temperature may be changed to about or greater than  $900\,^{0}$ C. The oxidizing gas is flown into the RTP chamber at about 1 slm total flow rate for about 15 seconds. It is to be appreciated that the flow rates mentioned are examples only for a particular reactor or process chamber size (e.g., a 200 mm reactor). The flow rates are proportionately adjusted (increased or decreased) for other size reactors owing to the difference in volume.

In one embodiment following the two-step PNA process, the silicon oxynitride film 304 is capped with a conductive layer such as a polysilicon film 306. The polysilicon film 306 can be formed in a deposition chamber such as the deposition chamber 110 of the integrated processing system 100 (Fig. 1). Instead of polysilicon, the film 306 can be an amorphous silicon film or other suitable conductive material. Further, metals such as titanium, titanium nitride, tantalum, tantalum nitride, tungsten, tungsten nitride, and other refractory metals or other suitable electrode materials may be deposited thereover. The deposition chamber 110 can be a low-pressure chemical vapor deposition chamber (LPCVD) that can be incorporated into the integrated processing system 100. After the formation of the polysilicon film 306, the gate stack is transferred to a cool down chamber 108 and then transferred to a storage area such as the load locks 104 and 106 for further processing, testing, or other processes known in the art.

It is to be appreciated that the gate stack that includes the gate dielectric film and the polysilicon cap film can be formed in several processing chambers not necessarily incorporated into the integrated processing system 100 previously described. For instance, the  $\mathrm{SiO}_2$  film can be formed first in one chamber. The  $\mathrm{SiO}_2$  film can be converted into silicon oxynitride in a plasma nitridation chamber. The silicon oxynitride chamber is then annealed in a two-step PNA process using an RTP chamber. And the polysilicon film is formed over a  $\mathrm{SiO}_x\mathrm{Ny}$  film in the

same RTP chamber.

# [0044] Performance of the Post Annealed SiOxNy gate dielectrics

[0045] As shown in Figure 4, including a trace amount of oxygen in the first step of a two-step post anneal of silicon oxynitride improves NMOS drive current relative to NMOS gate leakage. In Figure 4, the x-axis represents NMOS gate leakage and the y-axis represents NMOS drive current. For an example, a Si $\theta_2$  film of about 10 A is used as the base oxide. After plasma nitridation, various post-annealing conditions were used to anneal the film. For instance, a first step involving annealing at 1000°C for 30 seconds at 15 mTorr partial pressure of oxygen in the presence of nitrogen gas is followed by a second step at 1000 °C for 15 seconds at 10 Torr of oxygen. In another instance, a first step involving annealing at 1000 °C for 15 seconds at 15 mTorr in the presence of nitrogen gas is followed by a second step at 1050 °C for 15 seconds at 1.5 Torr of oxygen. In another instance, a first step involving annealing at 1050 °C for 30 seconds at 15 mTorr in the presence of nitrogen gas is followed by a second step at 1050 °C for 15 seconds at 0.5 Torr. In another instance, a first step involving annealing at 1000 °C for 30 seconds at 0.015 mTorr in the presence of nitrogen gas is followed by a second step at 1100°C for 5 seconds at 0.05 Torr. As shown in Figure 1, the two-step post anneal containing a trace amount of oxygen in the first step exhibits a 4% improvement in NMOS Idsat over a two-step post anneal without a trace amount of oxygen in the first step.

[0046] Without intending to be limited to any particular theory of invention, it is believed that the addition of a trace amount of oxygen to the first step of the two-step post plasma nitridation anneal prevents SiO formation that will etch and damage the dielectric.

[0047] While the foregoing is directed to embodiments of the present invention, other and further embodiments of the invention may be devised without departing from the basic scope thereof, and the scope thereof is determined by the claims that follow.

### Claims:

1. A method of forming a silicon oxynitride gate dielectric, comprising:

incorporating nitrogen into a dielectric film using a plasma nitridation process to form a silicon oxynitride film;

annealing the silicon oxynitride film in a first ambient comprising an inert ambient with a first partial pressure of oxygen at a first temperature; and

annealing the silicon oxynitride film in a second ambient comprising a second partial pressure of oxygen at a second temperature wherein the second partial pressure of oxygen is greater than the first partial pressure of oxygen.

- 2. The method of claim 1, wherein the first temperature ranges between about  $700^{\circ}$ C and  $1100^{\circ}$ C and the second temperature ranges between about  $900^{\circ}$ C and  $1100^{\circ}$ C.

- 3. The method of claim 2, wherein the first partial pressure of oxygen is between about 1 mTorr and 100 mTorr and the second partial pressure of oxygen is between about 0.1 Torr and 100 Torr.

- 4. The method of claim 3, wherein the annealing the silicon oxynitride film in a first ambient occurs at the first partial pressure of oxygen of about 15 mTorr, at the first temperature of about 1050°C for a first time period of about 30 seconds and the annealing the silicon oxynitride film in a second ambient occurs at the second partial pressure of oxygen of about 0.5 Torr at a second temperature of about 1050°C for a second time period of about 15 seconds.

- 5. The method of claim 1, wherein the annealing of the silicon oxynitride film in a second ambient comprises annealing the silicon oxynitride film with oxygen or oxygen comprising gas.

- 6. The method of claim 1, wherein the dielectric film is silicon dioxide.

7. The method of claim 1, wherein the nitrogen incorporated into the dielectric film forms a nitrogen concentration peak that occurs at a top surface of the silicon oxynitride gate dielectric.

- 8. The method of claim 1, wherein the nitrogen incorporated into the dielectric film has a nitrogen concentration equal to or greater than 5%.

- 9. A method of forming a silicon oxynitride gate dielectric, comprising:

providing a structure comprising a silicon dioxide film formed on a silicon substrate;

exposing the structure to a plasma comprising a nitrogen source to form a silicon oxynitride film on the substrate;

annealing the silicon oxynitride film in a first ambient comprising an inert ambient with a first partial pressure of oxygen at a temperature ranging between about 700°C and 1100°C;

annealing the silicon oxynitride film in a second ambient comprising a second partial pressure of oxygen at a temperature ranging between about 900°C and 1100°C, wherein the second partial pressure is greater than the first partial pressure; and

depositing a gate electrode on the silicon oxynitride film.

- 10. The method of claim 9, wherein the first partial pressure of oxygen is between about 1 mTorr and 100 mTorr and the second partial pressure of oxygen is between about 0.1 Torr and 100 Torr.

- 11. The method of claim 10, wherein the annealing the silicon oxynitride film in a first ambient occurs at the first partial pressure of oxygen of about 15 mTorr, at the first temperature of about 1050°C for a first time period of about 30 seconds and the annealing the silicon oxynitride film in a second ambient occurs at the second partial pressure of oxygen of about 0.5 Torr at a second temperature of about 1050°C for a

second time period of about 15 seconds.

12. The method of claim 9, wherein the nitrogen incorporated in the exposing the structure to a plasma has a nitrogen concentration equal to or greater than 5%.

- 13. The method of claim 9, wherein the annealing the silicon oxynitride film in a first ambient includes annealing the silicon oxynitride film in an inert gas or a mixture of inert gas.

- 14. The method of claim 9, wherein the annealing in a second ambient comprising a second partial pressure of oxygen includes annealing the silicon oxynitride film with oxygen or oxygen comprising gas.

- 15. The method of claim 9, wherein a thickness of the silicon oxynitride gate dielectric is equal to or less than about 9 A.

- 16. The method of claim 9, wherein the gate electrode is one of a polysilicon film, an amorphous silicon film, or a metal electrode.

- 17. A method of forming a silicon oxynitride gate dielectric in an integrated processing system comprising:

introducing a substrate comprising silicon into a first processing chamber of an integrated processing system;

forming a silicon dioxide film on the silicon substrate;

transferring the substrate to a second processing chamber of the integrated processing system;

exposing the substrate to a plasma comprising a nitrogen source;

transferring the substrate to a third processing chamber of the integrated processing system;

annealing the substrate in a first ambient comprising an inert ambient with a first partial pressure of oxygen at a temperature ranging between about 700 °C and

1100°C; and

annealing the substrate in a second ambient comprising a second partial pressure of oxygen at a temperature between about 900°C and 1100°C wherein the second partial pressure of oxygen is greater than the first partial pressure of oxygen.

18. The method of claim 17, further comprising:

transferring the substrate to a fourth processing chamber of the integrated processing system; and

depositing a polysilicon layer on the substrate.

19. The method of claim 17, further comprising:

transferring the substrate to a fourth processing chamber external to the integrated processing system after exposing the substrate to a second plasma; and depositing a polysilicon layer on the substrate.

20. The method of claim 1, wherein the plasma nitridation process includes decoupled plasma nitridation.

1/4

FIG. 1

FIG. 2

FIG. 3