(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년06월27일

(11) 등록번호 10-1120838

(24) 등록일자 2012년02월20일

(51) 국제특허분류(Int. C1.)

*G11C 11/401* (2006.01) *G11C 11/403*

(2006.01)

*G11C 11/406* (2006.01) *G11C 11/407* (2006.01)

(21) 출원번호 10-2005-0009640

(22) 출원일자 2005년02월02일

심사청구일자 2010년01월18일

(65) 공개번호 10-2006-0041602

(43) 공개일자 2006년05월12일

(30) 우선권주장

JP-P-2004-00026999 2004년02월03일 일본(JP)

(56) 선행기술조사문헌

JP09259080 A\*

WO2003005368 A1\*

JP2004005821 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

르네사스 일렉트로닉스 가부시키가이샤

일본 가나가와Ken 가와사끼시 나카하라구 시모누마베 1753

(72) 발명자

미끼 다께오

일본 도쿄도 지요다구 마루노우찌 2조메 4-1 가부시끼가이샤 르네사스 테크놀로지 내

사와다 세이지일본 도쿄도 지요다구 마루노우찌 2조메 4-1 가부시끼가이샤 르네사스 테크놀로지 내

쓰꾸테 마사끼

일본 도쿄도 지요다구 마루노우찌 2조메 4-1 가부시끼가이샤 르네사스 테크놀로지 내

(74) 대리인

이중희, 장수길

전체 청구항 수 : 총 5 항

심사관 : 장진환

(54) 발명의 명칭 휴대 단말기에 탑재하기 적합한 반도체 기억 장치

### (57) 요 약

트리거 생성 회로(104)는 트리거 신호를 출력한다. 지연 회로(110)는 트리거 신호를 받아, 트리거 신호를 지연시킨 지연 신호를 출력한다. 클럭 카운터(106)는 클럭을 받아, 트리거 신호를 받고 나서 지연 신호를 받을 때까지 동안, 받은 클럭의 수를 카운트하고, 카운트 결과를 출력한다. 판정 회로(107)는 클럭의 수와 레이턴시의 대응 관계를 기억하고, 클럭 카운터로부터 출력되는 카운트 결과에 대응하는 레이턴시를 판정한다. 레이턴시용 레지스터(108)는 판정된 레이턴시를 보유한다. WAIT 제어 회로(109)는 레이턴시용 레지스터(108)에 보유된 레이턴시에 기초하여, 외부에 WAIT 신호를 출력한다.

### 대 표 도

## 특허청구의 범위

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

클럭에 동기하여 동작하고, 버스트 모드에서의 액세스를 행하고, 판독 신호 또는 기입 신호가 생성되기에 앞서서, 로우 어드레스 및 컬럼 어드레스를 취득하는 반도체 기억 장치로서,

행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와,

외부로부터 받은 제어 신호에 의해서 판독 신호 또는 기입 신호가 생성된 제1 클럭에 동기하여, 선택된 로우의 로우 액세스 처리와, 선두로부터 1개 이상 또한 버스트 길이 이하인 제1 개수의 컬럼의 컬럼 액세스 처리를 행하고, 레이턴시로 규정되는 제2 클럭 이후의 클럭에 동기하여, 버스트 모드 액세스의 남은 제2 개수의 컬럼의 컬럼 액세스 처리를 행하도록 제어하는 제어 회로

를 포함하는 반도체 기억 장치.

청구항 8

제7항에 있어서,

상기 반도체 기억 장치는,

상기 메모리 셀에 접속된 비트선 쌍의 전위를 증폭하는 센스 앰프 회로와,

상기 컬럼을 선택하는 컬럼 디코더

를 포함하고,

상기 제어 회로는,

상기 센스 앰프 회로를 활성화시키는 신호가 생성된 후의 타이밍에서, 상기 제1 클럭에 동기하여 활성화되는 로우 활성화 신호에 따라 컬럼 인에이블 신호를 생성하는 제1 제어 회로와,

상기 컬럼 인에이블 신호에 따라, 상기 제1 개수의 컬럼을 활성화시키는 제1 지시 신호를 상기 컬럼 디코더에 출력하고, 상기 제2 클럭 이후의 클럭에 동기하여 상기 제2 개수의 컬럼을 활성화시키는 제2 지시 신호를 상기 컬럼 디코더에 출력하는 제2 제어 회로

를 포함하는 반도체 기억 장치.

**청구항 9**

제8항에 있어서,

상기 제어 회로는, 상기 제1 클럭에 동기하여 컬럼 액세스 처리가 행하여져 출력되는 선두의 데이터의 타이밍을 외부에 통지하는 신호를 생성하는 회로를 포함하는 반도체 기억 장치.

**청구항 10**

제8항에 있어서,

상기 제어 회로는, 상기 제2 클럭 이후의 클럭에 동기하여 컬럼 액세스 처리가 행하여져 출력되는 선두의 데이터의 타이밍을 외부에 통지하는 신호를 생성하는 회로를 포함하는 반도체 기억 장치.

**청구항 11**

제8항에 있어서,

리프레시 동작, 판독 동작, 또는 기입 동작의 실행중에, 판독 또는 기입 요구 신호가 생성되었을 때에는, 상기 동작의 실행 종료후의 다음 클럭을 상기 제1 클럭으로서 동작시키기 위한 시프트 회로를 포함하는 반도체 기억 장치.

**청구항 12**

삭제

**청구항 13**

삭제

**청구항 14**

삭제

**청구항 15**

삭제

**청구항 16**

삭제

**청구항 17**

삭제

**청구항 18**

삭제

**청구항 19**

삭제

**청구항 20**

삭제

**청구항 21**

삭제

**청구항 22**

삭제

청구항 23

삭제

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

[0085] 본 발명은 반도체 기억 장치에 관한 것으로, 특히, 휴대 단말기에 탑재하기 적합한 반도체 기억 장치에 관한 것이다.

[0086] 휴대 전화 등의 휴대 단말기에서 이용되는 반도체 기억 장치는, 대용량 및 제어의 간이성을 실현하기 위해서 의사 SRAM이 이용되고 있다. 의사 SRAM(Static Random Access Memory)에서는, 내부의 메모리 셀로서는 DRAM(Dynamic Random Access Memory) 셀이 이용되고, 입력되는 제어 신호 및 어드레스 신호 등을 규정하는 외부 인터페이스로서는, SRAM과 유사한 클럭에 동기하지 않는 비동기의 인터페이스가 이용되고 있다. 그리고, 리프레시 동작은 외부로부터의 신호에 의해서 제어되는 것이 아니라, 내부에서 자동적으로 행해진다(예를 들면, 일본 특허 공개 2002-352577호 공보)

[0087] 또한, 보다 고속화를 실현하기 위해서, 예를 들면 Cellular RAM<sup>TM</sup> Memory, 인터넷 <URL:<http://www.micron.com/products/psram/cellularram/>>에 기재되어 있는 Cellular RAM(R)과 같이, 의사 SRAM에, 동기식의 인터페이스를 추가한 동기식 의사 SRAM이 실용화되어 있다. 이 동기식 의사 SRAM에서는 SRAM과 유사한 클럭에 동기하지 않는 비동기식의 인터페이스 외에, 클럭에 동기한 동기식의 인터페이스를 구비한다.

[0088] 그런데, 동기식의 의사 SRAM에서는, 판독 또는 기입 요구를 받고 나서, 데이터가 출력되기까지의 클럭 수인 커맨드 레이턴시 CL이 경과할 때까지와, 셀프 리프레시를 행하고 있는 동안에는, 외부로부터 액세스할 수 없음을 WAIT 신호에 의해 통지한다. 종래 커맨드 레이턴시 CL은 외부로부터 주어지는데, 동기식의 의사 SRAM에서는 내부로부터 WAIT 신호에 의해 액세스가 불가능하다는 취지를 통지할 수 있으므로, 외부로부터 부여할 필요가 없다고 할 수 있다. 오히려, 동기식 의사 SRAM의 내부에서, 그 때의 상태에 따라서 커맨드 레이턴시 CL을 설정하는 것이, 외부로부터 설정하는 것보다도 적절한 값으로 설정할 수 있다고 할 수 있다.

[0089] 이에 대하여, 일본 특허 공개 2001-155484호 공보에는, 클럭 주파수에 의해서 레이턴시 조정이 가능한 레이턴시 결정 회로가 개시되어 있다. 이 레이턴시 결정 회로는, 클럭 신호에 동기하여 레이턴시 결정을 시작하는 레이턴시 결정 개시 신호의 활성화에 응답하여 내부 개시 신호를 발하는 레이턴시 결정 지시 입력부와, 레이턴시 결정 개시 신호에 응답하여 클럭 신호의 엣지마다 소정의 레이턴시 결정 구간 신호를 발하는 레이턴시 구간 정의 회로와, 내부 개시 신호를 소정 시간 지연시켜 레이턴시를 조정하도록 지연 신호를 발하는 지연부와, 지연 신호의 활성화 시점에서 레이턴시 결정 개시 신호 및 레이턴시 결정 구간 신호에 응답하여 레이턴시 수를 결정하는 레이턴시 지시 회로를 구비한다. 이러한 레이턴시 결정 회로에 의해서, 레이턴시를 외부로부터의 지시에 의하지 않고, 내부에서 결정할 수 있다.

[0090] 또한, 예를 들면, 일본 특허 공개 평성 07-226077호 공보에는, 의사 SRAM이 복수 개의 뱅크를 갖는 경우에는, 셀프 리프레시와 판독 또는 기입을 동시 실행하는 방법이 개시되어 있다. 즉, 일본 특허 공개 평성 07-226077호 공보의 단락 [0020]에는, 제1 내지 제4 로우 어드레스 래치 회로 및 버퍼(80 ~ 83)는, 제1 내지 제4 셀 뱅크(10 ~ 13)의 내의 어떤 하나의 셀 뱅크가 리프레시 모드에 있다고 해도, 남은 3개의 셀 뱅크 측에 로우 어드레스 래치 회로(70)에 의해 래치된 제2 로우 어드레스 신호 A<sub>0</sub> ~ A<sub>n-2</sub>를 전송하여 리프레시 모드중에도 데이터의 액세스를 가능하게 할 수 있다.

[0091] 그러나, 전술한 문헌에 기재된 방법에서는 이하와 같은 문제가 있다.

[0092] 우선, 일본 특허 공개 2001-155484호 공보에는, 내부에서 레이턴시를 설정하는 방법에 대하여 기재되어 있지 만, 레이턴시를 설정하는 타이밍에 대해서는 기재되어 있지 않다.

- [0093] 또한, 일본 특허 공개 평성 07-226077호 공보에는, 리프레시하는 뱅크와 판독 또는 기입을 행하는 뱅크가 서로 다를 때에, 리프레시와 판독 또는 기입을 동시에 행하는 방법에 대하여 기재되어 있지만, 판독 또는 기입을 행하는 뱅크와 겹쳐지지 않도록, 리프레시하는 뱅크를 정하는 방법에 대해서는 기재되어 있지 않다.

- [0094] 또한, 복수 개의 의사 SRAM을 1개의 패키지에 수용했을 때에, 각각이 서로 다른 타이밍에서 리프레시를 행하므로, 각각이 출력하는 WAIT 신호가 경합한다고 하는 문제가 있다.

- [0095] 또한, 커맨드 레이턴시 CL에 의해 규정되는 타이밍보다도 빠른 타이밍에서 데이터를 출력할 수 없다고 하는 문제가 있다.

- [0096] 또한, 동기 모드와 비동기식 모드 등과 같이 복수의 모드를 갖고, 1개의 모드를 선택하여 동작하는 경우에는, 어떤 모드에서는 적절하게 동작하는 프리 앰프이더라도, 다른 모드에서는 적절하게 동작하지 않아, 증폭이 정상적으로 행해지지 않는 경우가 있다.

- [0097] 또한, 연속 판독 또는 기입의 도중에, 다음 로우로 이행하는 경우에, 외부로부터는, WAIT 신호에 의해서, 다음 로우로 이행하기 위한 처리(이행전의 워드선의 비활성화, 이행후의 워드선의 활성화, 및 센스 앰프에 의한 증폭 등)가 종료되었음을 알고 나서, 바이트 마스크 신호를 부여하여야 한다고 하는 문제가 있다.

- [0098] 또한, 비트선 쌍을 프리차지시키기 위해서, 외부로부터 칩 인에이블 신호를 비활성으로 하여야 하여, 외부로부터의 제어를 요한다고 하는 문제가 있다.

- [0099] 또한, Cellular RAM(R)과 같은 반도체 기억 장치에서는, 저 주파수의 클럭으로 또한 동기식으로 동작시킬 수 없다고 하는 문제가 있다.

- [0100] 또한, 스탠바이 상태 또는 다른 칩에 액세스중에, 비활성으로 되어 있는 칩에 있어서, 입출력 버퍼가 계속 동작하여, 쓸데 없이 전류를 소비한다는 문제가 있다.

### **발명이 이루고자 하는 기술적 과제**

- [0101] 본 발명의 목적은 적절한 타이밍에서 내부에서 레이턴시를 설정하는 반도체 기억 장치를 제공하는 것이다.

- [0102] 또한, 본 발명의 다른 목적은, 판독 또는 기입을 행하는 뱅크와 겹쳐지지 않도록, 리프레시하는 뱅크를 적절하게 정하는 반도체 기억 장치를 제공하는 것이다.

- [0103] 또한, 본 발명의 또 다른 목적은, 복수 개의 의사 SRAM을 1개의 패키지에 수용했을 때에, 동일한 타이밍에서 리프레시를 행할 수 있는 반도체 기억 장치를 제공하는 것이다.

- [0104] 또한, 본 발명의 또 다른 목적은, 커マン드 레이턴시 CL에 의해 규정되는 타이밍보다도 빠른 타이밍에서 데이터를 출력할 수 있는 반도체 기억 장치를 제공하는 것이다.

- [0105] 또한, 본 발명의 또 다른 목적은, 복수의 모드를 갖고, 1개의 모드를 선택하여 동작하는 경우에는, 모든 모드에서 프리 앰프가 적절하게 동작하는 반도체 기억 장치를 제공하는 것이다.

- [0106] 또한, 본 발명의 또 다른 목적은, 연속 판독 또는 기입 도중에, 다음 로우로 이행하는 경우에 있어서도, 외부로부터는, 다음 로우로 이행하지 않는 경우와 마찬가지로 하여 바이트 마스크 신호를 부여할 수 있는 반도체 기억 장치를 제공하는 것이다.

- [0107] 또한, 본 발명의 또 다른 목적은, 외부로부터의 제어를 요하지 않고, 내부의 제어만으로 비트선 쌍을 프리차지시킬 수 있는 반도체 기억 장치를 제공하는 것이다.

- [0108] 또한, 본 발명의 또 다른 목적은, 저 주파수의 클럭으로 또한 동기식으로 동작시킬 수 있는 반도체 기억 장치를 제공하는 것이다.

- [0109] 또한, 본 발명의 또 다른 목적은, 비활성으로 되어 있는 칩에 있어서, 입출력 버퍼가 계속 동작하여, 쓸데 없이 전류를 소비하는 것을 방지한 반도체 기억 장치를 제공하는 것이다.

### **발명의 구성 및 작용**

- [0110] 본 발명의 하나의 국면에 의한 반도체 기억 장치는, 클럭에 동기하여 동작하는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 트리거 신호를 출력하는 트리거 생성 회로와, 트리거 신호를 받아, 트리거 신호를 지연시킨 지연 신호를 출력하는 지연 회로와, 클럭을 받아, 트리거 신호를

받고 나서 지연 신호를 받을 때까지 동안, 받은 클럭의 수를 카운트하여, 카운트 결과를 출력하는 클럭 카운터와, 클럭의 수와 레이턴시의 대응 관계를 기억하고, 클럭 카운터로부터 출력되는 카운트 결과에 대응하는 레이턴시를 판정하는 판정 회로와, 판정된 레이턴시를 보유하는 레지스터와, 레지스터에 보유된 레이턴시에 기초하여, 외부에 웨이트 신호를 출력하는 웨이트 제어 회로를 구비한다.

[0111] 본 발명의 다른 국면에 의한 반도체 기억 장치는, 행렬 형상으로 배치된 복수의 다이내믹 랜덤 액세스 메모리의 메모리 셀을 갖고, 1도의 리프레시의 단위로 되는 뱅크를 복수 개 갖는 메모리 어레이와, 리프레시의 트리거를 출력하는 회로와, 리프레시 트리거를 받았을 때에, 외부로부터 지시된 동작을 실행 중일 때에, 동작을 실행 중인 뱅크와 서로 다른 뱅크를 선택하여, 선택한 뱅크의 어드레스를 출력하는 뱅크 선택 회로와, 받은 어드레스의 뱅크의 리프레시를 실행하는 리프레시 제어 회로를 구비하고, 뱅크 선택 회로는, 리프레시가 실시 완료된 뱅크의 어드레스를 보유하고, 모든 뱅크의 어드레스가 보유되면, 보유되어 있는 모든 어드레스가 소거되는 레지스터와, 리프레시 트리거를 받았을 때에, 레지스터를 참조하여 리프레시가 미실시된 뱅크의 어드레스를 특정하는 특정 회로와, 미실시된 뱅크 어드레스와, 동작을 실행중인 뱅크 어드레스를 비교하여, 서로 다른 경우에, 미실시된 뱅크 어드레스를 출력하는 비교 회로를 포함한다.

[0112] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 행렬 형상으로 배치된 복수의 다이내믹 랜덤 액세스 메모리의 메모리 셀을 갖는 메모리 어레이와, 리프레시의 타이밍을 규정하는 제1 신호를 생성하는 제1 회로와, 제1 신호를 출력하는 출력 단자와, 외부로부터 리프레시의 타이밍을 규정하는 제2 신호를 받는 입력 단자와, 제1 신호 및 제2 신호를 받아, 어느 하나의 신호를 출력하는 스위치와, 스위치로부터 출력되는 신호를 받아, 해당 신호에 기초하여 리프레시 제어를 행하는 제2 회로를 구비한다.

[0113] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 클럭에 동기하여 동작하고, 버스트 모드에서의 액세스를 행하고, 판독 신호 또는 기입 신호가 생성되는 데에 앞서서, 로우 어드레스 및 컬럼 어드레스를 취득하는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 외부로부터 받은 제어 신호에 의해서 판독 신호 또는 기입 신호가 생성된 제1 클럭에 동기하여, 선택된 로우의 로우 액세스 처리와, 선두로부터 1개 이상 또한 버스트 길이 이하인 제1 개수의 컬럼의 컬럼 액세스 처리를 행하고, 레이턴시에 의해 규정되는 제2 클럭 이후의 클럭에 동기하여, 버스트 모드 액세스의 남은 제2 개수의 컬럼의 컬럼 액세스 처리를 행하도록 제어하는 제어 회로를 구비한다.

[0114] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 외부 신호의 조합에 의해서, 복수의 동작 모드 중 어느 하나의 모드로 설정되는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 메모리 셀에 각각 접속된 비트선 쌍과, 비트선 쌍의 전위를 증폭하는 제1 증폭 회로와, 복수의 비트선 쌍에 접속된 IO선 쌍과, 각 모드에 응답하여 어느 하나가 활성화되어, IO선 쌍의 전위를 증폭하는 2 종류 이상의 제2 증폭 회로를 구비한다.

[0115] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 클럭에 동기하여 동작하는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 외부로부터 바이트 마스크 신호를 받아, 바이트 마스크 신호에 기초하여 바이트 마스크 처리를 제어하는 바이트 마스크 제어 회로와, 메모리 셀로부터 출력된 데이터를 받아, 바이트 마스크 제어 회로에 의한 지시에 따라서, 메모리 셀로부터 출력된 데이터의 바이트 마스크 신호에 대응하는 바이트의 출력을 행하지 않는 출력 회로를 구비하고, 바이트 마스크 제어 회로는, 연속 판독 또는 연속 기입이 제1 로우와 제2 로우의 2개의 로우에 걸치는 경우, 도중에 제1 로우의 최후 컬럼에 달했기 때문에 제2 로우로의 이행을 위해서 로우 액세스 처리를 행하고 있는 동안에, 외부로부터 바이트 마스크 신호를 받았을 때에, 바이트 마스크 신호에 대응하는 바이트의 마스크 처리를, 로우 액세스가 종료하고, 다음 비트의 데이터가 출력되는 타이밍까지 연장한다.

[0116] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 클럭에 동기하여 동작하는 동기 모드와, 비동기로 동작하는 비동기 모드를 갖는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 동기 고정 모드와, 비동기 고정 모드와, 동기 및 비동기의 혼재 모드 중 어느 하나로 설정 가능한 설정 회로와, 혼재 모드 시에, 외부 칩 인에이블 신호가 어서트되고 나서, 외부 클럭의 상승까지의 시간이 소정값 이상인지 여부를 조사하여, 소정값 이상일 때에, 비동기 고정 모드로 이행하는 비동기 이행 회로와, 동기 고정 모드 또는 혼재 모드로 설정되었을 때에 동기 동작을 제어하는 동기 제어 회로와, 비동기 고정 모드 혹은 혼재 모드로 설정되었을 때, 또는 비동기 고정 모드로 이행했을 때에, 비동기 동작을 제어하는 비동기 제어 회로를 구비하고, 비동기 이행 회로는 설정 회로의 출력에 따라서 비활성화된다.

[0117] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 클럭에 동기하여 동작하는 반도체 기억 장치로서, 행렬

형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 외부 칩 인에이블 신호를 받아 내부 칩 인에이블 신호를 생성하는 칩 인에이블 버퍼와, 외부 클럭을 받아 내부 클럭을 생성하는 클럭 버퍼와, 외부 어드레스 신호를 받아 내부 어드레스 신호를 생성하는 어드레스 버퍼와, 외부 칩 인에이블 신호 이외의 외부 제어 신호를 받아 내부 제어 신호를 생성하는 제어 버퍼를 구비하고, 클럭 버퍼, 어드레스 버퍼 및 제어 버퍼는, 내부 칩 인에이블 신호를 받아, 내부 칩 인에이블 신호가 칩의 비활성을 나타낼 때에, 그 동작을 정지하고, 클럭 버퍼, 어드레스 버퍼, 및 제어 버퍼는, 내부 칩 인에이블 신호가 활성화를 도시할 때에, 동작을 실행하고, 제어 버퍼는, 외부 어드레스 취득 신호를 받아, 내부 어드레스 취득 신호를 생성하고, 반도체 기억 장치는 또한, 내부 어드레스 취득 신호를 소정의 지연량만큼 지연시키는 지연 회로와, 지연 회로의 출력과 내부 클럭을 받아, 내부의 클럭에 동기하여, 지연 회로의 출력을 보유하는 데이터 보유 회로와, 데이터 보유 회로의 출력과 내부 클럭의 논리곱 신호를 출력하는 논리 회로와, 논리곱 신호의 선두 펄스에 기초하여, 로우 어드레스 스트로브 신호를 활성화하는 회로를 구비하고, 논리곱 신호의 선두 펄스가, 외부 어드레스 취득 신호가 활성화되고 있는 동안에 상승하는 외부 클럭 펄스로부터 생성된 내부 클럭 펄스로 되도록, 지연 회로의 소정의 지연량이 정해져 있다.

[0118] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 복수의 동작 모드의 어느 하나의 모드로 설정되는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 메모리 셀에 각각 접속된 비트선 쌍과, 비트선 쌍의 전위를 증폭하는 제1 증폭 회로와, 복수의 비트선 쌍에 접속된 IO선 쌍과, IO선 쌍에 접속되고, 열 방향으로 배치되는 2 이상의 서로 다른 종류의 제2 증폭 회로를 구비하고, IO선 쌍은 2 이상이 서로 다른 종류의 제2 증폭 회로끼리 접속한다.

[0119] 본 발명의 또 다른 국면에 의한 반도체 기억 장치는, 복수의 동작 모드 중 어느 하나의 모드로 설정되는 반도체 기억 장치로서, 행렬 형상으로 배치된 복수의 메모리 셀을 갖는 메모리 어레이와, 메모리 셀에 각각 접속된 비트선 쌍과, 비트선 쌍의 전위를 증폭하는 제1 증폭 회로와, 복수의 비트선 쌍에 접속된 IO선 쌍과, IO선 쌍에 접속되고, 행 방향으로 배치되는 2 이상의 서로 다른 종류의 제2 증폭 회로를 구비한다.

[0120] 본 발명의 또 다른 목적, 특징, 국면 및 이점은, 첨부하는 도면과 관련하여 이해되는 발명에 관한 이하의 상세한 설명에 의해서 분명해질 것이다.

[0121] 이하, 본 발명의 실시예에 대하여, 도면을 이용하여 설명한다.

[제1 실시예]

[0123] 본 실시예는 레이턴시를 적절한 타이밍에서 내부에서 자동적으로 적절한 값으로 설정하는 동기식 의사 SRAM에 관한 것이다.

[0124] (구성)

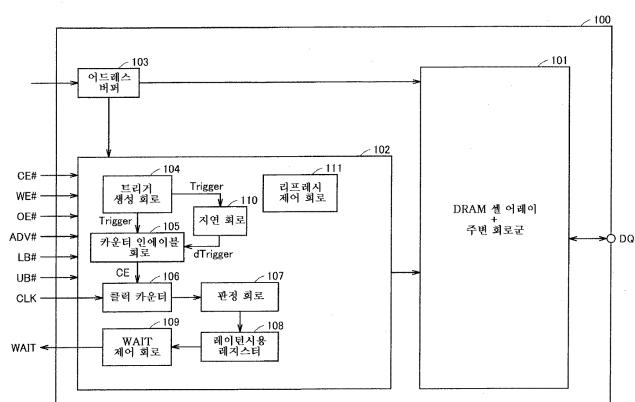

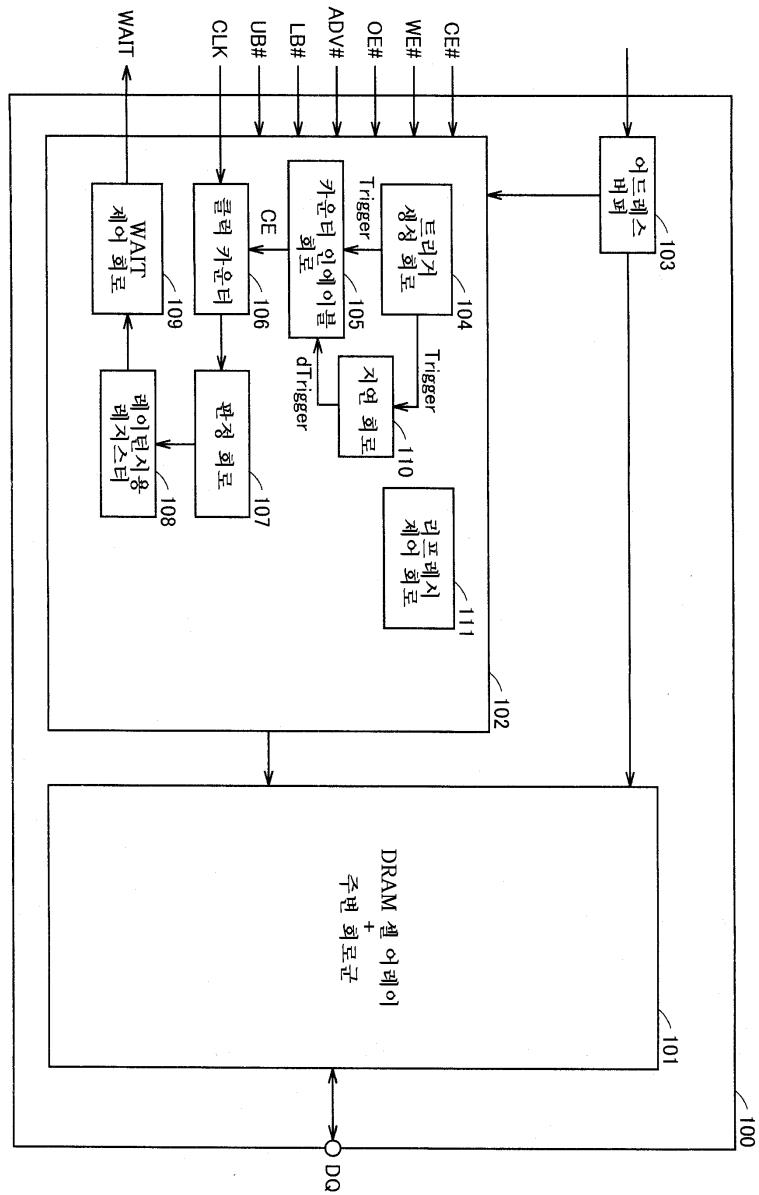

[0125] 도 1은 본 실시예에 따른 동기식 의사 SRAM(100)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(100)는, DRAM 셀 어레이+주변 회로군(101)과, 어드레스 버퍼(103)와, 제어 회로(102)를 포함한다.

[0126] DRAM 셀 어레이+주변 회로군(101)의 DRAM 셀 어레이는, 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다. 주변 회로군(101)은, 글로벌 입출력선 쌍 GIOP(GIO 및 /GIO)와, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앰프와, 프리 앰프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다.

[0127] 어드레스 버퍼(103)는 외부 어드레스 신호 ADD[21:0]를 받아, 내부 어드레스 신호를 생성한다.

[0128] 제어 회로(102)는, 트리거 생성 회로(104)와, 카운터 인에이블 회로(105)와, 클럭 카운터(106)와, 판정 회로(107)와, 레이턴시용 레지스터(108)와, WAIT 제어 회로(109)와, 지연 회로(110)와, 리프레시 제어 회로(111)를 포함한다.

[0129] 리프레시 제어 회로(111)는 도시하지 않은 내부의 리프레시 타이머에 기초하여, DRAM 셀 어레이의 셀프 리프레시 동작을 제어한다.

[0130] 트리거 생성 회로(104), 레이턴시의 설정의 트리거로 되는 트리거 신호 Trigger를 출력한다.

[0131] 지연 회로(110)는 복수 단의 인버터로 이루어지고, 트리거 신호 Trigger를 받아, 지연 트리거 신호 Trigger를 출력한다.

[0132] 카운터 인에이블 회로(105)는 트리거 신호 Trigger가 입력되고 나서, 지연 트리거 신호 Trigger가 입력될 때

까지 동안, 카운터 인에이블 신호 CE를 「H」로 한다.

[0133] 클럭 카운터(106)는, 카운터 인에이블 신호 CE가 「H」인 동안, 입력되는 외부 클럭 CLK의 수를 카운트한다. 카운트 수는, 입력되는 외부 CLK의 수와, 카운터 인에이블 신호 CE가 「H」의 기간, 즉 지연 회로(110)에서의 트리거 신호 Trigger의 지연량에 의존한다. 지연 회로(110)에서의 지연량은 온도 등의 주위 환경에 의존한다.

[0134] 판정 회로(107)는, 클럭의 카운트 수와, 그 카운트 수로 동작 가능한 최소의 레이턴시의 대응 관계를 기억한다. 대응 관계는 클럭의 카운트 수가 많을수록, 최소의 레이턴시가 커지도록 정해진다. 판정 회로(107)는 이 대응 관계에 기초하여, 클럭 카운터(106)로부터 출력되는 카운트 수에 따른 최소의 레이턴시를 판정하여, 레이턴시용 레지스터(108)에 출력한다.

[0135] 레이턴시용 레지스터(108)는 판정 회로(107)로부터 보내지는 최소의 레이턴시를 보존한다.

[0136] WAIT 제어 회로(109)는 레이턴시용 레지스터(108)에 보존되어 있는 최소의 레이턴시에 따른 기간만, WAIT 신호를 「L」로 한다.

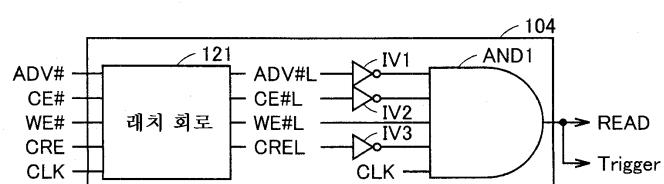

[0137] 도 2는 트리거 생성 회로(104)의 상세한 구성을 도시한다. 동도에 도시한 바와 같이, 트리거 생성 회로(104)는, 래치 회로(121)와, 인버터 IV1, IV2, IV3과, 논리곱 회로 AND1로 이루어진다.

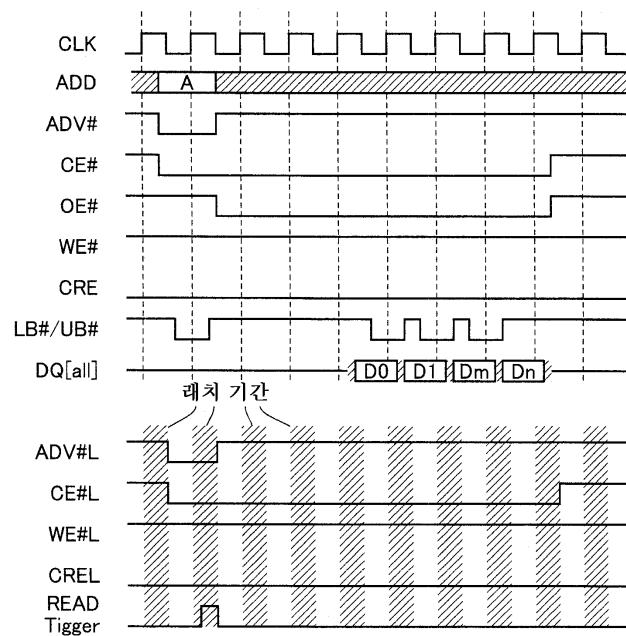

[0138] 도 3은 트리거 생성 회로(104)에서 생성되는 신호의 타이밍차트이다. 동도를 참조하여, 래치 회로(121)는, 외부 어드레스 취득 신호 ADV#를 래치하여, 어드레스 취득 래치 신호 ADV#L을 출력한다. 래치 회로(121)는 외부 칩 인에이블 신호 CE#를 래치하여, 칩 인에이블 래치 신호 CE#L을 출력한다. 래치 회로(121)는 외부 라이트 인에이블 신호 WE#를 래치하여, 라이트 인에이블 래치 신호 WE#L을 출력한다. 래치 회로(121)는 외부 컨피규레이션 레지스터 인에이블 신호 CRE#를 래치하여, 컨피규레이션 레지스터 인에이블 래치 신호 CRE#L을 출력한다. AND 회로 AND1은, 어드레스 취득 래치 신호 ADV#L이 「L」, 칩 인에이블 래치 신호 CE#L이 「L」, 기입 래치 신호 WE#L이 「H」, 컨피규레이션 레지스터 인에이블 래치 신호 CRE#L이 「L」, 또한 외부 클럭 CLK 가 「H」일 때에, 판독 신호 READ를 「H」로 활성화함과 함께, 트리거 신호 Trigger를 「H」로 한다.

[0139] 이러한 트리거 신호 생성 회로(104)에 의해, 외부 신호의 논리치의 조합에 의해서 판독 신호 READ가 생성되어 판독이 행해질 때에, 트리거 신호 Trigger도 동시에 생성되며, 레이턴시의 설정이 행하여진다.

[0140] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, 판독 신호 READ가 생성되고, 실제로 판독 처리를 위해서 커맨드 레이턴시를 필요로 하는 타이밍에서, 입력되는 외부 클럭 CLK의 주파수 및 온도 등의 주위 환경하에서 동작 가능한 최소의 값으로 레이턴시를 설정할 수 있다.

[0141] 또한, 본 실시예에서는, 지연 회로(110)는 복수 개의 인버터로 구성되는 것으로 했지만, 이것에 한정되는 것이 아니라, 예를 들면, 특정한 회로를 모의적으로 재현한 리플리커 회로(a replica circuit) 등을 이용해도 된다. 또한, 클럭 카운터(106)는 외부 클럭 CLK를 받는 것은 아니고, 내부 클럭을 받는 것으로 해도 된다.

[0142] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니고, 클럭에 동기하여 동작하는 반도체 기억 장치이면 어떠한 것에도 적용할 수 있다.

[0143] [제1 실시예의 변형 예]

[0144] 제1 실시예에 있어서, 트리거 생성 회로(104)는, 판독 신호 READ가 생성되었음을 검지하여, 트리거 신호 Trigger를 생성하였지만, 이것에 한정되는 것은 아니다. 예를 들면, 이하와 같은 경우에, 트리거 신호 Trigger를 생성하는 것으로 하여도 된다.

[0145] (1) 기입 신호 WRITE 등의 다른 동작 지시 신호가 입력되었음을 검지하여, 트리거 신호 Trigger를 생성한다.

[0146] (2) 전원 투입 검지 회로에 의해 전원이 투입되었음을 검지했을 때에, 트리거 신호 Trigger를 생성한다.

[0147] (3) 동작 모드 설정 커맨드 판정 회로에 의해 외부 신호에 의해 레이턴시, 버스트 길이 등의 모드 설정이 행하여졌음을 판정했을 때에, Trigger 신호를 생성한다.

[0148] (4) 온도 변화 검지 회로에 의해 온도 변화를 검지했을 때에, 트리거 신호 Trigger를 생성한다.

[0149] (5) 내부 발신 회로에 의해, 일정 주기로 트리거 신호 Trigger를 생성한다.

[0150] [제2 실시예]

- [0151] 본 실시예는 셀프 리프레시하는 뱅크를 적절하게 전환하여, WAIT 기간을 짧게 한 동기식 의사 SRAM에 관한 것이다.

- [0152] (구성)

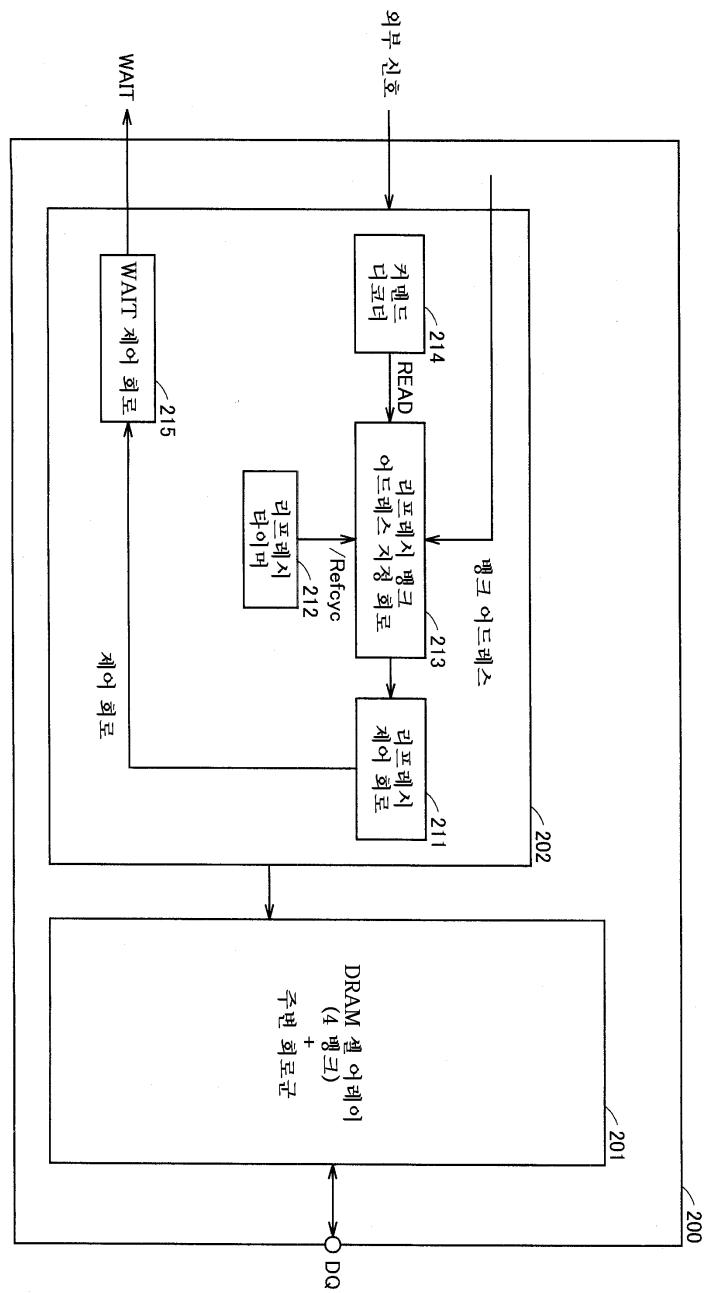

- [0153] 도 4는 본 실시예에 따른 동기식 의사 SRAM(200)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(200)은 DRAM 셀 어레이+주변 회로군(201)과, 제어 회로(202)를 구비한다.

- [0154] DRAM 셀 어레이+주변 회로군(201)의 DRAM 셀 어레이는, 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이고, 4개의 뱅크를 갖는다. 뱅크는 DRAM 셀 어레이를 분할한 메모리 셀군이고, 한 번의 리프레시 동작의 단위로 된다. 즉, 한 번의 리프레시에서는 1개의 뱅크가 리프레시된다.

- [0155] 주변 회로군은 글로벌 입출력선 쌍 GIOP(GIO 및 /GIO)과, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앰프와, 프리 앰프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다.

- [0156] 제어 회로(202)는 커맨드 디코더(214)와, 리프레시 뱅크 어드레스 지정 회로(213)와, 리프레시 타이머(212)와, 리프레시 제어 회로(211)와, WAIT 제어 회로(215)를 구비한다.

- [0157] 커맨드 디코더(214)는 외부 제어 신호로부터 생성된 내부 제어 신호의 논리 레벨의 조합에 따라서, 로우 활성화 신호 ACT, 판독 신호 READ, 및 기입 신호 WRITE를 생성한다.

- [0158] 리프레시 타이머(212)는 링 발진기로 구성되며 주기적으로 활성화된 리프레시 사이클 신호 /Refcyc를 출력한다.

- [0159] 리프레시 뱅크 어드레스 지정 회로(213)는, 리프레시 사이클 신호 /Refcyc와, 판독 신호 READ 또는 기입 신호 WRITE와, 뱅크 어드레스를 받아, 리프레시하는 뱅크의 어드레스 및 그 리프레시의 타이밍을 지정한다.

- [0160] 리프레시 제어 회로(211)는, 리프레시 뱅크 어드레스 지정 회로(213)로부터 뱅크 어드레스만을 받으면, 바로 그 어드레스의 뱅크의 리프레시 동작을 제어한다. 또한, 리프레시 제어 회로(211)는, 리프레시 뱅크 어드레스 지정 회로(213)로부터 뱅크 어드레스와 함께, 그 뱅크 어드레스의 뱅크의 판독 동작 종료 후에 리프레시를 행하는 취지의 명령을 받으면, 소정의 시간이 경과한 후, 그 뱅크의 리프레시 동작을 제어한다.

- [0161] WAIT 제어 회로(215)는, 리프레시 제어 회로(211)가 리프레시 동작을 제어하고 있는 동안, WAIT 신호의 레벨 「L」로 한다.

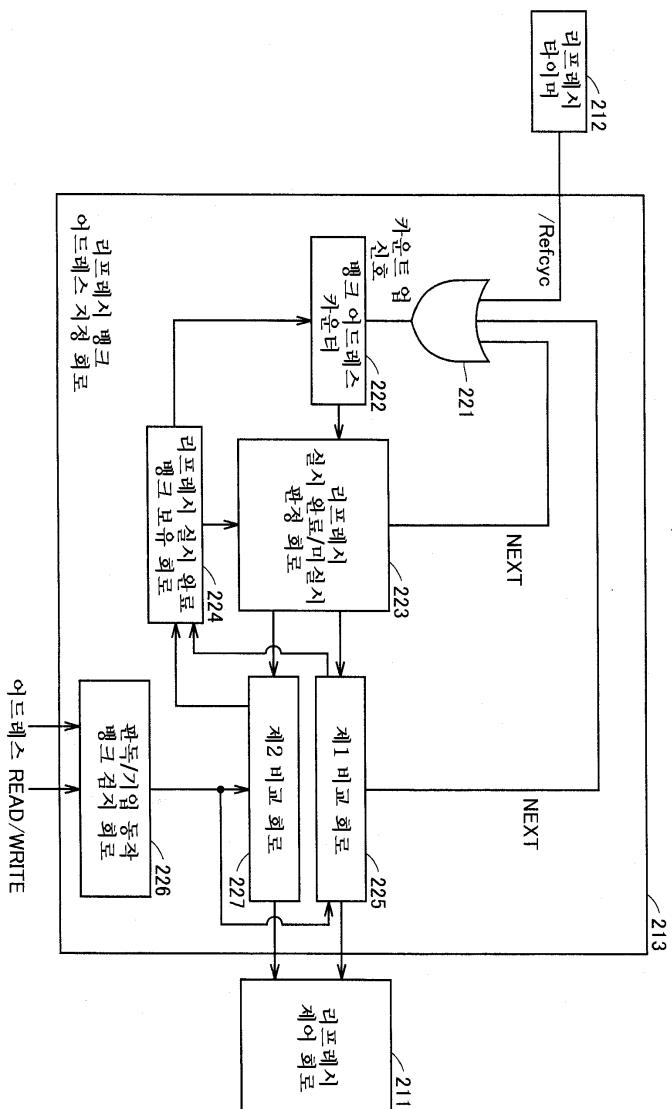

- [0162] 도 5는 리프레시 뱅크 어드레스 지정 회로(213)의 상세한 구성을 도시한다. 동도를 참조하여, 리프레시 뱅크 어드레스 지정 회로(213)는, OR 회로(221)와, 뱅크 어드레스 카운터(222)와, 리프레시 실시 완료/미실시 판정 회로(223)와, 리프레시 실시 완료 뱅크 보유 회로(224)와, 제1 비교 회로(225)와, 제2 비교 회로(227)와, 판독/기입 동작 뱅크 검지 회로(226)를 구비한다.

- [0163] OR 회로(221)는 리프레시 타이머(212)로부터 리프레시 사이클 신호 /Refcyc, 리프레시 실시 완료/미실시 판정 회로(223)로부터 다음의 뱅크를 지시하는 신호 NEXT, 또는 제1 비교 회로(225)로부터 다음의 뱅크를 지시하는 신호 NEXT를 받으면, 카운트 업 신호를 출력한다.

- [0164] 뱅크 어드레스 카운터(222)는, 카운트 업 신호를 받으면, 「1」 내지 「4」의 범위에서 카운트를 업한다. 단, 카운트치의 초기치는 「0」으로 하고, 카운트 「4」의 다음은 카운트 「1」로 한다.

- [0165] 리프레시 실시 완료 뱅크 보유 회로(224)는, 리프레시를 실시 완료한 뱅크 어드레스를 보유한다. 리프레시 실시 완료 뱅크 보유 회로(224)는, 「1」 내지 「4」의 뱅크 어드레스가 전부 보유되었을 때에는, 보유하고 있는 뱅크 어드레스를 전부 소거함과 함께, 뱅크 어드레스 카운터(222)의 카운트치를 「0」으로 리셋시킨다. 따라서, 4회의 리프레시로, 뱅크 1 내지 뱅크 4의 모든 리프레시가 완료된다.

- [0166] 리프레시 실시 완료/미실시 판정 회로(223)는, 뱅크 어드레스 카운터(222)의 카운터치의 뱅크 어드레스가, 리프레시 실시 완료 뱅크 보유 회로(224)에 보유되어 있는지의 여부를 조사한다. 리프레시 실시 완료/미실시 판정 회로(223)는, 카운터치의 뱅크 어드레스가 보유되고 있지 않은 경우에는, 미실시라고 판정하여, 그 뱅크 어드레스를 제1 비교 회로(225) 또는 제2 비교 회로(227) 중 어느 하나에 출력한다. 여기서, 리프레시 실시 완료/미실시 판정 회로(223)는, 출력하는 뱅크 어드레스가 리프레시 실시 완료 뱅크 보유 회로(224)에 보유되고 있지 않은, 최후의 1개의 뱅크 어드레스일 때에는, 제2 비교 회로(227)에 그 뱅크 어드레스를 출력한다. 리프레시 실시 완료/미실시 판정 회로(223)는, 상기 이외의 경우에는, 제1 비교 회로(225)에 그 뱅크 어드레스를 출력한다.

- [0167] 리프레시 실시 완료/미실시 판정 회로(223)는, 카운터치의 뱅크 어드레스가 보유되고 있는 경우에는, 실시 완료라고 판정하여, 다음의 뱅크 어드레스를 지시하는 신호 NEXT를 출력한다.

- [0168] 판독/기입 동작 뱅크 검지 회로(226)는, 판독 신호 READ 또는 기입 신호 WRITE를 받았을 때에, 입력되는 뱅크 어드레스(판독 또는 기입을 행하고 있는 뱅크의 어드레스)를 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다.

- [0169] 제1 비교 회로(225)는, 판독/기입 동작 뱅크 검지 회로(226) 및 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 2개의 뱅크 어드레스가 동일한지 여부를 조사한다. 제1 비교 회로(225)는, 2개의 뱅크 어드레스가 서로 다를 때에는, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스를 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 그 뱅크 어드레스를 출력하여 보유시킨다. 제1 비교 회로(225)는 2개의 뱅크 어드레스가 동일한 때에는, 다음의 뱅크 어드레스를 지시하는 신호 NEXT를 출력한다.

- [0170] 제2 비교 회로(227)는, 판독/기입 동작 뱅크 검지 회로(226) 및 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 2개의 뱅크 어드레스가 동일한지 여부를 조사한다. 제2 비교 회로(227)는, 2개의 뱅크 어드레스가 서로 다를 때에는, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스를 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 그 뱅크 어드레스를 출력하여 보유시킨다. 제2 비교 회로(227)는 2개의 뱅크 어드레스가 동일한 때에는, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스와, 그 뱅크 어드레스의 뱅크의 판독 동작 종료 후에 리프레시를 행하는 취지의 명령을 리프레시 제어 회로(211)에 보낸다.

- [0171] (배경 기술의 동기식 의사 SRAM의 동작 예)

- [0172] 우선, 본 실시예에 따른 동기식 의사 SRAM(200)의 동작의 비교를 위해서, 배경 기술의 동기식 의사 SRAM의 동작을 설명한다.

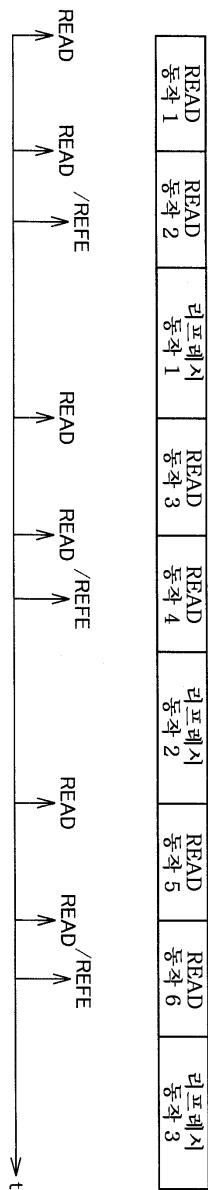

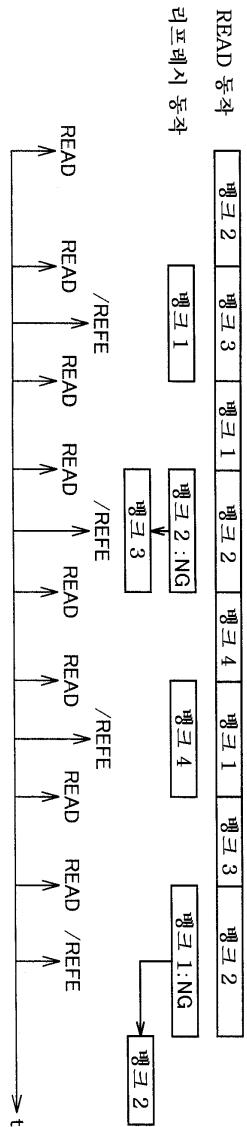

- [0173] 도 6은 배경 기술의 동기식 의사 SRAM의 동작을 설명하기 위한 도면이다. 동도에 도시한 바와 같이, 외부寄せ에 의한 판독 신호 READ에 기초하여, 판독 동작이 행해지고 있는 도중에, 리프레시 타이머가, 리프레시 사이클 신호 /Refcyc를 출력했을 때에는, 리프레시 제어 회로는, 실행중인 판독 동작의 종료 후에, 리프레시 동작의 제어를 개시한다. 또한 WAIT 제어 회로는, 리프레시 동작을 실행중에는 외부에 WAIT 신호를 출력한다.

- [0174] 따라서, 종래의 동기식 의사 SRAM에서는, 판독 동작의 타이밍과 셀프 리프레시의 타이밍이 중첩된 경우에, 셀프 리프레시의 타이밍이 지연됨과 함께, 외부로부터는, 셀프 리프레시가 종료될 때까지, 판독 지시를 보낼 수 없다.

- [0175] (본 실시예의 동기식 의사 SRAM(200)의 동작 예 1)

- [0176] 도 7은 본 실시예에 따른 동기식 의사 SRAM(200)의 동작 예를 설명하기 위한 도면이다.

- [0177] 우선, 외부로부터의 뱅크 2를 지정한 판독 신호 READ에 기초하여, 뱅크 2의 판독 동작이 행하여진다.

- [0178] 다음으로, 외부로부터의 뱅크 3을 지정한 판독 신호 READ에 기초하여, 뱅크 3의 판독 동작이 행하여진다. 뱅크 3의 판독 동작중에, 리프레시 타이머(212)는, 리프레시 사이클 신호 /Refcyc를 출력한다. 리프레시 뱅크 어드레스 지정 회로(213) 내의 OR 회로(221)는, 리프레시 사이클 신호 /Refcyc를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는 뱅크 어드레스의 카운트치를 「1」로 한다. 리프레시 실시 완료/미실시 판정 회로(223)는, 리프레시 실시 완료 뱅크 보유 회로(224)에 아직 아무 것도 보유되어 있지 않기 때문에, 미실시라고 판정하여, 뱅크 어드레스 「1」을 제1 비교 회로(225)에 출력한다. 판독/기입 동작 뱅크 검지 회로(226)는, 판독 신호 READ 및 뱅크 어드레스 「3」을 받아, 뱅크 어드레스 「3」을 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다. 제1 비교 회로(225)는, 받은 2개의 뱅크 어드레스가 서로 다르기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스 「1」을 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 뱅크 어드레스 「1」을 출력하여 보유시킨다. 리프레시 제어 회로(211)는, 뱅크 어드레스 「1」을 받으면 뱅크 1의 리프레시 동작을 제어한다.

- [0179] 이어서, 외부로부터의 뱅크 1을 지정한 판독 신호 READ에 기초하여, 뱅크 1의 판독 동작이 행하여진다.

- [0180] 다음으로, 외부로부터의 뱅크 2를 지정한 판독 신호 READ에 기초하여, 뱅크 2의 판독 동작이 행하여진다. 뱅크 2의 판독 동작중에, 리프레시 타이머(212)는, 리프레시 사이클 신호 /Refcyc를 출력한다. 리프레시 뱅크 어드레스 지정 회로(213) 내 OR 회로(221)는, 리프레시 사이클 신호 /Refcyc를 받으면 카운트 업 신호를 출력

한다. 뱅크 어드레스 카운터(222)는 뱅크 어드레스의 카운트치를 「2」로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」만이 보유되고, 뱅크 어드레스 「2」가 보유되고 있지 않기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 미실시라고 판정하여, 뱅크 어드레스 「2」를 제1 비교 회로(225)에 출력한다. 판독/기입 동작 뱅크 검지 회로(226)에는, 판독 신호 READ 및 뱅크 어드레스 「2」를 받아, 뱅크 어드레스 「2」를 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다. 제1 비교 회로(225)는 받은 2개의 뱅크 어드레스가 동일하기 때문에, 다음의 뱅크를 지시하는 신호 NEXT를 출력한다.

[0181] OR 회로(221)는 다음의 뱅크를 지시하는 신호 NEXT를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는 뱅크 어드레스의 카운트치를 「3」으로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」만이 보유되고, 뱅크 어드레스 「3」이 보유되고 있지 않기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 미실시라고 판정하여, 뱅크 어드레스 「3」을 제1 비교 회로(225)에 출력한다. 판독/기입 동작 뱅크 검지 회로(226)에는, 판독 신호 READ 및 뱅크 어드레스 「2」를 받아, 뱅크 어드레스 「2」를 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다. 제1 비교 회로(225)는, 받은 2개의 뱅크 어드레스가 서로 다르기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스 「3」을 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 뱅크 어드레스 「3」을 출력하여 보유시킨다. 리프레시 제어 회로(211)는, 뱅크 어드레스 「3」을 받으면 뱅크 3의 리프레시 동작을 제어한다.

[0182] 다음에, 외부로부터의 뱅크 4를 지정한 판독 신호 READ에 기초하여, 뱅크 4의 판독 동작이 행하여진다.

[0183] 다음으로, 외부로부터의 뱅크 1을 지정한 판독 신호 READ에 기초하여, 뱅크 1의 판독 동작이 행하여진다. 뱅크 1의 판독 동작중에, 리프레시 타이머(212)는 리프레시 사이클 신호 /Refcyc를 출력한다. 리프레시 뱅크 어드레스 지정 회로(213) 내의 OR 회로(221)는, 리프레시 사이클 신호 /Refcyc를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는 뱅크 어드레스의 카운트치를 「4」로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」 및 「3」만이 보유되고, 뱅크 어드레스 「4」가 보유되고 있지 않기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 미실시라고 판정하여, 뱅크 어드레스 「4」를 제1 비교 회로(225)에 출력한다. 판독/기입 동작 뱅크 검지 회로(226)에는, 판독 신호 READ 및 뱅크 어드레스 「1」을 받아, 뱅크 어드레스 「1」을 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다. 제1 비교 회로(225)는, 받은 2개의 뱅크 어드레스가 서로 다르기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스 「4」를 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 뱅크 어드레스 「4」를 출력하여 보유시킨다. 리프레시 제어 회로(211)는 뱅크 어드레스 「4」를 받으면 뱅크 4의 리프레시 동작을 제어한다.

[0184] 다음으로, 외부로부터의 뱅크 3을 지정한 판독 신호 READ에 기초하여, 뱅크 3의 판독 동작이 행하여진다.

[0185] 다음으로, 외부로부터의 뱅크 4를 지정한 판독 신호 READ에 기초하여, 뱅크 4의 판독 동작이 행하여진다. 뱅크 4의 판독 동작중에, 리프레시 타이머(212)는 리프레시 사이클 신호 /Refcyc를 출력한다. 리프레시 뱅크 어드레스 지정 회로(213) 내의 OR 회로(221)는, 리프레시 사이클 신호 /Refcyc를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는, 뱅크 어드레스의 카운트치를 「1」(순환적으로 갱신)로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」, 「3」 및 「4」가 보유되고 있기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 실시라고 판정하여, 다음의 뱅크를 지시하는 신호 NEXT를 출력한다.

[0186] OR 회로(221)는 다음의 뱅크를 지시하는 신호 NEXT를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는 뱅크 어드레스의 카운트치를 「2」로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」, 「3」, 「4」가 보유되고, 뱅크 어드레스 「2」가 보유되고 있지 않기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 미실시라고 판정하여, 뱅크 어드레스 「2」를 제2 비교 회로(227)에 출력한다. 여기서, 뱅크 어드레스 「2」를 제1 비교 회로(225)가 아니라, 제2 비교 회로(227)에 출력한 것은, 뱅크 어드레스 「1」 내지 「4」 중, 이 뱅크 어드레스 「2」가 미실시된 최후 뱅크이기 때문이다. 판독/기입 동작 뱅크 검지 회로(226)에는, 판독 신호 READ 및 뱅크 어드레스 「4」를 받아, 뱅크 어드레스 「4」를 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다. 제2 비교 회로(227)는 받은 2개의 뱅크 어드레스가 서로 다르기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스 「2」를 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 뱅크 어드레스 「2」를 출력하여 보유시킨다. 리프레시 제어 회로(211)는 뱅크 어드레스 「2」를 받으면 뱅크 2의 리프레시 동작을 제어한다.

- [0187] 리프레시 실시 완료 뱅크 보유 회로(224)는, 모든 뱅크 어드레스 「1」 내지 「4」를 보유하면, 보유하고 있는 뱅크 어드레스를 소거함과 함께, 뱅크 어드레스 카운터(222)에, 뱅크 어드레스의 카운트치를 「0」으로 리셋시킨다.

- [0188] (리프레시 뱅크 어드레스 명령 회로의 동작 예 2)

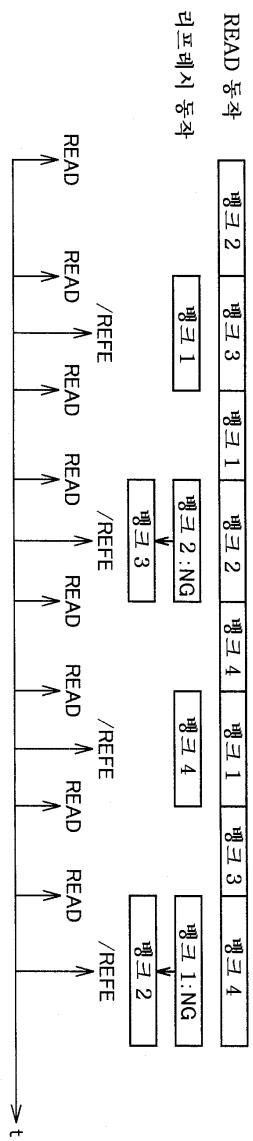

- [0189] 도 8은 본 실시예에 따른 동기식 의사 SRAM(200)의 다른 동작 예를 설명하기 위한 도면이다.

- [0190] 동작 예 1의 최후의 단계에서, 외부로부터의 뱅크 4를 지정한 판독 신호 READ의 대신에 뱅크 2를 지정한 판독 신호 READ가 입력되었을 때의 처리에 대하여 설명한다.

- [0191] 외부로부터의 뱅크 2를 지정한 판독 신호 READ에 기초하여, 뱅크 2의 판독 동작이 행하여진다. 뱅크 2의 판독 동작중에, 리프레시 타이머(212)는, 리프레시 사이클 신호 /Refcyc를 출력한다. 리프레시 뱅크 어드레스 지정 회로(213) 내의 OR 회로(221)는, 리프레시 사이클 신호 /Refcyc를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는, 뱅크 어드레스의 카운트치를 「1」(순환적으로 갱신)로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」, 「3」 및 「4」가 보유되고 있기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 실시라고 판정하여, 다음의 뱅크를 지시하는 신호 NEXT를 출력한다.

- [0192] OR 회로(221)는 다음의 뱅크를 지시하는 신호 NEXT를 받으면 카운트 업 신호를 출력한다. 뱅크 어드레스 카운터(222)는 뱅크 어드레스의 카운트치를 「2」로 한다. 리프레시 실시 완료 뱅크 보유 회로(224)에는, 뱅크 어드레스 「1」, 「3」, 「4」가 보유되고, 뱅크 어드레스 「2」가 보유되고 있지 않기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)는, 미실시라고 판정하여, 뱅크 어드레스 「2」를 제2 비교 회로(227)에 출력한다.

- [0193] 여기서, 뱅크 어드레스 「2」를 제1 비교 회로(225)가 아니고, 제2 비교 회로(227)에 출력한 것은, 뱅크 어드레스 「1」 내지 「4」 중, 이 뱅크 어드레스 「2」가 미실시된 최후 뱅크이기 때문이다. 판독/기입 동작 뱅크 검지 회로(226)에는, 판독 신호 READ 및 뱅크 어드레스 「2」를 받아, 뱅크 어드레스 「2」를 제1 비교 회로(225) 및 제2 비교 회로(227)에 출력한다. 제2 비교 회로(227)는, 받은 2개의 뱅크 어드레스가 동일하기 때문에, 리프레시 실시 완료/미실시 판정 회로(223)로부터 받은 뱅크 어드레스 「2」와, 뱅크 2의 판독 동작 종료 후에 리프레시를 행하는 취지의 명령을 리프레시 제어 회로(211)에 전송함과 함께, 리프레시 실시 완료 뱅크 보유 회로(224)에 뱅크 어드레스 「2」를 출력하여 보유시킨다. 리프레시 제어 회로(211)는, 뱅크 어드레스 「2」와, 뱅크 2의 판독 동작 종료 후에 리프레시를 행하는 취지의 명령을 받으면, 소정의 시간 경과한 후, 뱅크 2의 리프레시 동작을 제어한다.

- [0194] 리프레시 실시 완료 뱅크 보유 회로(224)는, 모든 뱅크 어드레스 「1」 내지 「4」를 보유하면, 보유하고 있는 뱅크 어드레스를 소거함과 함께, 뱅크 어드레스 카운터(222)에, 뱅크 어드레스의 카운트치를 「0」으로 리셋시킨다.

- [0195] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, 판독 또는 기입을 행하는 뱅크와 겹쳐지지 않고, 또한 리프레시가 미실시된 뱅크가 리프레시하는 뱅크가 정해지기 때문에, 셀프 리프레시의 타이밍이 지연되는 일없이, 또한 공평한 빈도로 리프레시를 행할 수 있다.

- [0196] 또한, 본 실시예에서는 1회 내지 4회, 및 5회 내지 8회 등의 각 4회의 셀프 리프레시에 있어서, 4개의 뱅크 모두의 리프레시를 완료하는 것으로 했지만, 이것에 한정되는 것은 아니다. 예를 들면, 8회의 셀프 리프레시마다 4개 모두의 리프레시를 완료하는 것으로 하여도 된다. 이 경우에는, 동작 예 2에서는 4회째의 뱅크 2의 셀프 리프레시의 타이밍을 늦추지 않도록 할 수 있다. 또한, 외부의 시스템 측이 판독 신호 READ에 앞서서, 판독하는 뱅크 어드레스의 스케줄을 지정할 수 있는 것으로 해도 된다. 이 경우에는, 스케줄 지정된 뱅크 어드레스의 판독과 겹쳐지지 않고, 또한 리프레시 횟수가 모든 뱅크에서 균등해지도록, 리프레시하는 뱅크 어드레스의 스케줄을 설정할 수 있다.

- [0197] 또한, 본 실시예의 동작 예에서는, 판독 동작중에 리프레시 요구가 발생하는 경우에 대하여 설명했지만, 기입 동작중에 리프레시 요구가 발생하는 경우에 대해서도, 마찬가지로 하여 처리된다.

- [0198] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니고, 클럭에 동기하여 동작하지 않는 의사 SRAM에도 적용 가능하다.

- [0199] [제3 실시예]

- [0200] 본 실시예는 복수 개의 동기식 의사 SRAM을 1개의 패키지에 수용하고, 복수 개의 동기식 의사 SRAM의 리프레

시의 타이밍을 동일하게 하는 구성에 관한 것이다.

[0201] (구성)

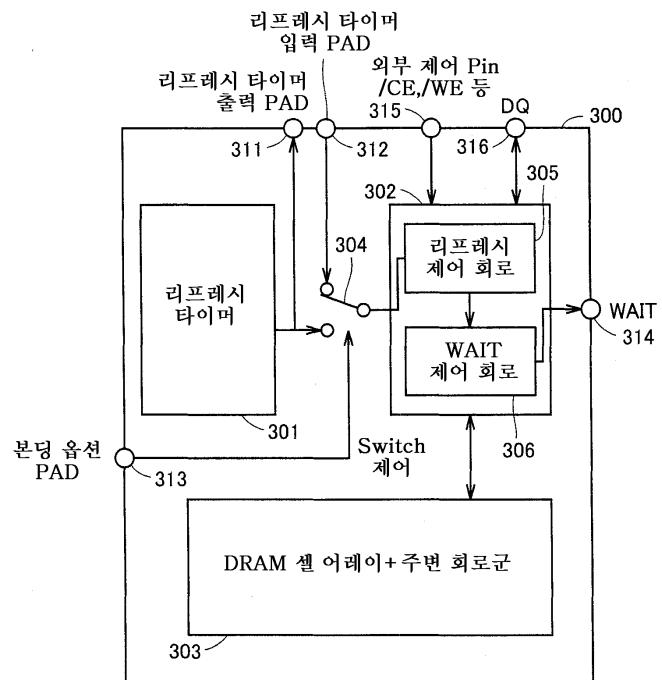

도 9는 본 실시예에 따른 1개의 패키지에 수용되는 각 동기식 의사, SRAM(300)의 구성을 도시한다. 이 동기식 의사 SRAM(300)은, 리프레시 타이머(301)와, 제어 회로(302)와, DRAM 셀 어레이+주변 회로군(303)과, 스위치(304)를 포함한다.

[0203] DRAM 셀 어레이+주변 회로군(303)의 DRAM 셀 어레이는, 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다. 주변 회로군은, 클로벌 입출력선 쌍 GIOP(GIO 및 /GIO)과, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앰프와, 프리 앰프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다.

[0204] 제어 회로(302)는 제어 신호 단자(315)를 통하여 외부 제어 신호를 받음과 함께, 데이터 입출력 단자(316)를 통하여 DRAM 셀 어레이에의 기입 데이터를 받아, 이들에 기초하여, 이 동기식 의사 SRAM(300) 전체의 처리를 제어함과 함께, 데이터 입출력 단자(316)를 통하여, DRAM 셀 어레이로부터의 관독 데이터를 출력한다. 또한, 제어 회로(302)는 리프레시 제어 회로(305)와, WAIT 제어 회로(306)를 포함한다.

[0205] 리프레시 타이머(301)는 링 발진기로 구성되며 주기적으로 활성화된 리프레시 사이클 신호 /Refcyc를 스위치(304) 및 리프레시 타이머 출력 PAD(311)에 출력한다. 리프레시 타이머 출력 PAD(311)에 부여된 리프레시 사이클 신호 /Refcyc는, 다른 동기식 의사 SRAM에 보내진다.

[0206] 리프레시 타이머 입력 PAD(312)는 다른 동기식 의사 SRAM의 리프레시 타이머로부터의 리프레시 사이클 신호 /Refcyc를 받는다.

[0207] 본딩 옵션 PAD(313)은 인가되는 전위에 따라서 스위치(304)를 제어한다.

[0208] 스위치(304)는 리프레시 타이머(301)로부터의 리프레시 사이클 신호 /Refcyc 및 리프레시 타이머 입력 PAD(312)으로부터의 리프레시 사이클 신호 /Refcyc를 받는다. 2개의 리프레시 사이클 신호 /Refcyc는 주기는 동일하지만, 타이밍이 서로 다르다.

[0209] 스위치(304)는 본딩 옵션 PAD(313)의 인가 전위에 따라서, 받은 리프레시 사이클 신호 /Refcyc 중 어느 하나를 리프레시 제어 회로(305)에 출력한다. 즉, 스위치(304)는, 본딩 옵션 PAD(313)에 접지 전위가 인가되었을 때에, 리프레시 타이머 입력 PAD(312)로부터의 리프레시 사이클 신호 /Refcyc를 출력하고, 접지 전위 이외의 전위가 인가되었을 때에, 리프레시 타이머(301)로부터의 리프레시 사이클 신호 /Refcyc를 출력한다.

[0210] 리프레시 제어 회로(305)는 셀프 리프레시의 제어를 행한다.

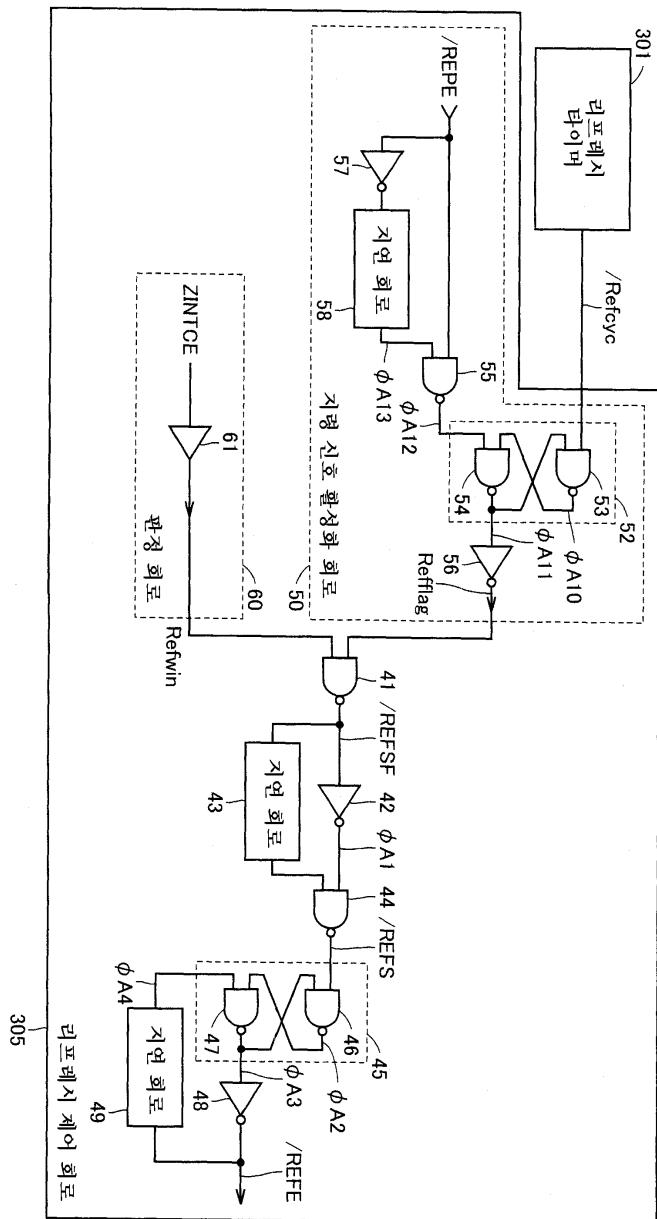

[0211] 도 10은 리프레시 제어 회로(305)의 상세한 구성을 도시한다. 동도를 참조하여, 리프레시 제어 회로(305)는, 명령 신호 활성화 회로(50)와, 판정 회로(60)와, NAND 게이트(41, 44)와, 인버터(42)와, 버퍼(48)와, 지연 회로(43, 49)와, 플립플롭(45)을 포함한다.

[0212] 명령 신호 활성화 회로(50)는 리프레시 명령 신호 /REFE를 활성화시키기 위해서 리프레시 플래그 신호 Refflag를 출력한다. 판정 회로(60)는 리프레시 플래그 신호 Refflag에 의해 활성화된 리프레시 명령 신호 /REFE를 출력할지의 여부를 판정하기 위해 판정 신호 Refwin을 출력한다.

[0213] NAND 게이트(41)는, 리프레시 플래그 신호 Refflag와 판정 신호 Refwin을 받아, 리프레시 플래그 신호 Refflag와 판정 신호 Refwin의 논리곱을 연산하고, 그 연산 결과를 반전한 신호를 반전 논리곱 신호 /REFSF로서 출력한다.

[0214] 인버터(42)는 NAND 게이트(41)로부터 출력된 신호 /REFSF를 받아 반전한 신호 φA1을 출력한다. 또한, 지연 회로(43)는 반전 논리곱 신호 /REFSF를 받아 일정 시간 지연시킨다.

[0215] NAND 게이트(44)는 인버터(42)의 출력 신호 φA1과 지연 회로(43)의 출력 신호를 받아, 신호 φA1과 지연 회로(43)의 출력 신호의 논리곱을 연산하고, 그 연산 결과를 반전한 신호 /REFS를 출력한다.

[0216] 플립플롭(45)은 NAND 게이트(46 및 47)로 구성된다. NAND 게이트(46)는 신호 /REFS와 NAND 게이트(47)로부터 출력된 출력 신호 φA3을 받아, 신호 /REFS와 신호 φA3의 논리곱을 연산하고, 그 연산 결과를 반전한 신호 φA2를 출력한다. NAND 게이트(47)는 NAND 게이트(46)로부터 출력된 신호 φA2와 지연 회로(49)로부터 출력된 신호 φA4를 받아, 신호 A2와 신호 A4와의 논리곱을 연산하고, 그 연산 결과를 반전한 신호를 리프레시 명령 신호 /REFE로서 출력한다. 리프레시 명령 신호 /REFE의 활성화에 응답하여, 리프레시 동작이 행하여진다.

- [0217] 지연 회로(49)는 플립플롭(45)으로부터 출력된 리프레시 명령 신호 /REFE를 받아 일정 시간 지연시킨 신호  $\phi$  A4를 출력한다.

- [0218] 버퍼(48)는 신호  $\phi$  A3을 받아 리프레시 명령 신호 /REFE를 출력한다.

- [0219] 명령 신호 활성화 회로(50)는, 플립플롭(52)과, NAND 게이트(55)와, 인버터(56 및 57)와, 지연 회로(58)를 포함한다.

- [0220] 플립플롭(52)은 NAND 게이트(53 및 54)로 구성된다. NAND 게이트(53)는 리프레시 사이클 신호 /Refcyc와 NAND 게이트(54)의 출력 신호  $\phi$  A11을 받아, 리프레시 사이클 신호 /Refcyc와 신호  $\phi$  A11의 논리곱을 연산하고, 그 연산 결과를 반전한 신호  $\phi$  A10을 출력한다. 또한, NAND 게이트(54)는, NAND 게이트(53)로부터 출력된 출력 신호  $\phi$  A10과, NAND 게이트(55)로부터 출력된 출력 신호  $\phi$  A12를 받아, 신호  $\phi$  A10과 신호  $\phi$  A12의 논리곱을 연산하고, 그 연산 결과를 반전한 신호  $\phi$  A11을 출력한다.

- [0221] 인버터(56)는 플립플롭(52)으로부터 출력된 신호  $\phi$  A11을 받아 반전하고, 반전한 신호를 리프레시 플래그 신호 Refflag로서 출력한다.

- [0222] 인버터(57)는 리프레시 명령 신호 /REFE를 받아 반전한다. 또한, 지연 회로(58)는, 인버터(57)에 의해 반전된 리프레시 명령 신호 /REFE를 받아, 반전된 리프레시 명령 신호 /REFE를 일정 시간 지연시킨 신호  $\phi$  A13을 출력한다.

- [0223] NAND 게이트(55)는 리프레시 명령 신호 /REFE와 지연 회로(58)로부터 출력된 신호  $\phi$  A13을 받아, 리프레시 명령 신호 /REFE와 신호  $\phi$  A13의 논리곱을 연산하고, 그 연산 결과를 반전한 신호  $\phi$  A12를 출력한다.

- [0224] 판정 회로(60)는 버퍼 회로(61)로 구성된다. 버퍼 회로(61)는 내부 칩 인에이블 신호 ZINTCE를 받아, 판정 신호 Refwin을 출력한다.

- [0225] 재차, 도 9를 참조하여, WAIT 제어 회로(306)는, 리프레시 제어 회로(305)의 제어에 의해 리프레시 제어가 행해지고 있는 동안, WAIT 단자(314)를 통하여 출력하는 WAIT 신호의 레벨을 「L」로 한다.

- [0226] (꽤키지)

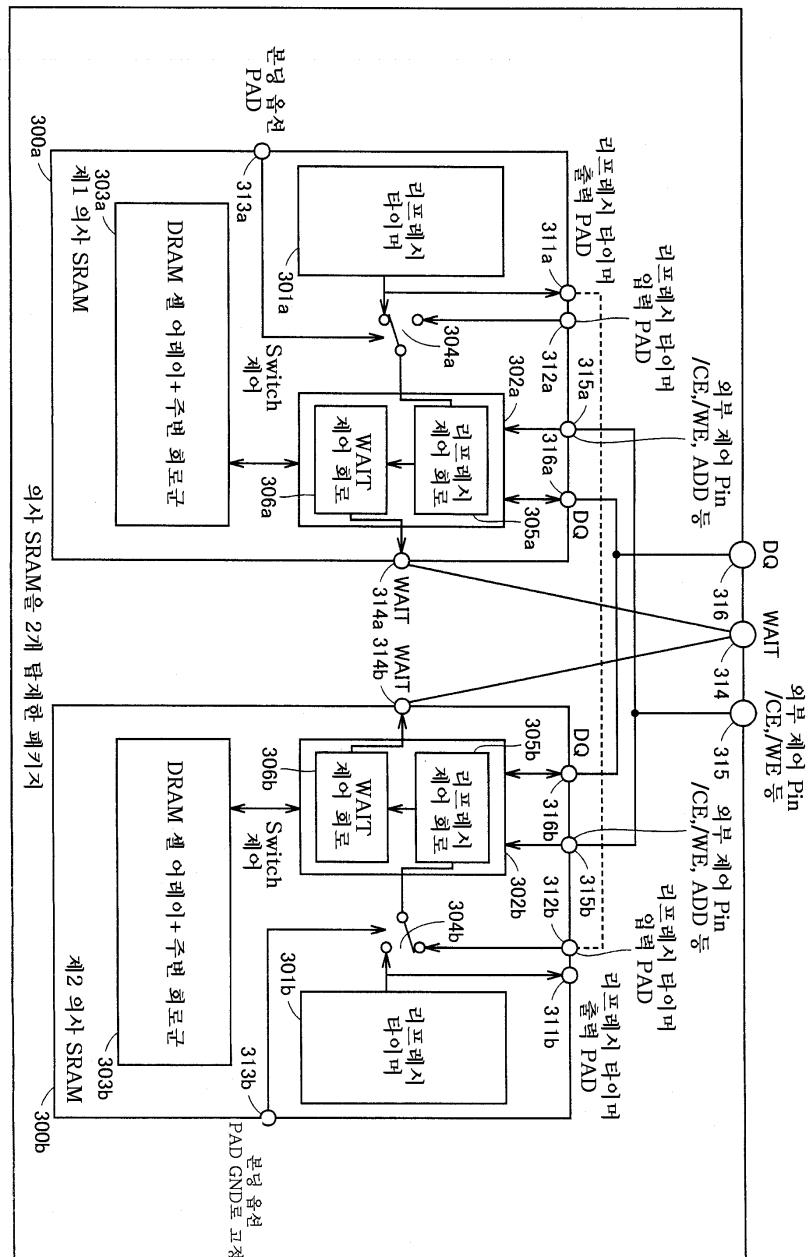

- [0227] 도 11은 본 실시예에 따른 2개의 동기식 의사 SRAM을 수납한 패키지의 구성을 도시한다. 동도를 참조하여, 제1 동기식 의사 SRAM(300a) 및 제2 동기식 의사 SRAM(300b)는 각각, 도 9의 동기식 의사 SRAM과 마찬가지의 구조이다. 제1 동기식 의사 SRAM(300a)의 본딩 옵션 PAD(313a)는 개방되어 있고, 스위치(304a)는 리프레시 타이머(301a)로부터 출력된 리프레시 사이클 신호 /Refcyc를 리프레시 제어 회로(305a)에 보낸다.

- [0228] 한편, 제2 동기식 의사 SRAM(300b)의 본딩 옵션 PAD(313b)는, 접지 전위가 공급되고, 스위치(304b)는, 리프레시 타이머 입력 PAD(312b)를 통하여 받은 제1 동기식 의사 SRAM(300a)의 리프레시 타이머(301a)로부터 출력된 리프레시 사이클 신호 /Refcyc를 리프레시 제어 회로(305b)에 보낸다. 이에 의해, 리프레시 제어 회로(305a 및 305b)는 어느 것이나 리프레시 타이머(301a)의 리프레시 사이클 신호 /Refcyc에 의해 동작하기 때문에, 제1 및 제2 동기식 의사 SRAM(300a 및 300b)의 리프레시 타이밍이 동일해진다.

- [0229] WAIT 제어 회로(306a)는 WAIT 단자(314a 및 314)를 통하여 WAIT 신호를 출력하고, WAIT 제어 회로(306b)는 WAIT 단자(314b 및 314)를 통하여 WAIT 신호를 출력한다. 리프레시 제어 회로(305a 및 305b)의 리프레시 타이밍이 동일해지기 때문에, 각 WAIT 신호가 「L」로 변화하는 타이밍도 동일해진다.

- [0230] 이상과 같이, 복수 개의 동기식 의사 SRAM에 있어서, 리프레시 중에 의해, 외부로부터 지시된 동작을 접수할 수 없다는 취지를 알리는 WAIT의 레벨 변화의 타이밍을 동일하게 할 수 있다.

- [0231] 또한, 본 실시예에서는, 2개의 동기식 의사 SRAM을 탑재한 패키지를 예로 하여 설명하였지만, 2개 이상의 임의의 개수의 동기식 의사 SRAM을 탑재시키는 것으로 하여도 된다.

- [0232] 또한, 본 실시예에서는, 복수의 동기식 의사 SRAM에서, 리프레시 사이클 신호 /Refcyc를 공용하는 것으로 하고, 리프레시 타이머 출력 PAD를 통하여 자기의 리프레시 사이클 신호 /Refcyc를 출력하고, 리프레시 타이머 입력 PAD를 통하여, 다른 동기식 의사 SRAM의 리프레시 사이클 신호 /Refcyc를 받았지만, 이것에 한정되는 것은 아니다. 예를 들면, 복수의 동기식 의사 SRAM에서 리프레시 플래그 신호 Refflag, 반전 논리곱 신호 /REFSF, 또는 리프레시 명령 신호 /REFE를 공용하는 것으로 하고, 리프레시 타이머 출력 PAD 및 리프레시 타

이미 입력 PAD를 통하여, 신호의 수수를 행하는 것으로 하여도 무방하다.

[0233] 또한, 본 실시예에서는 복수의 동기식 의사 SRAM이 각각의 WAIT 신호를 출력했지만, 이것에 한정되는 것은 아니다. 예를 들면, WAIT 제어 회로(306a)와 WAIT 단자(314a)의 사이, 및 WAIT 제어 회로(306b)와 WAIT 단자(314b)의 사이에, 각각 본딩 옵션 PAD에 의해 제어할 수 있는 스위치를 마련하고, 한쪽의 스위치만, WAIT 단자와 WAIT 제어 회로가 접속하도록 제어함으로써, 1개의 동기식 의사 SRAM에서만 WAIT 신호를 출력하는 것으로 하여도 된다.

[0234] 또한, 복수 개의 동기식 의사 SRAM이 WAIT 신호를 출력하지 않는 경우, 즉, 셀프 리프레시의 타이밍과, 외부로부터의 판독 신호 READ 또는 기입 신호 WRITE의 타이밍이 중첩되었을 때에, 판독 신호 READ 또는 기입 신호 WRITE를 보유해 놓고, 셀프 리프레시 완료 후에, 판독 동작 또는 기입 동작을 행하는 경우에 있어서는, 리프레시 사이클 신호 /Refcyc만을 공용하는 것으로 하여도 된다. 즉, WAIT의 제어는 행하지 않는다. 이 경우에도 복수 개의 동기식 의사 SRAM이 동시에 리프레시를 행하므로, 신호의 간섭이 발생하기 어렵다고 하는 일정한 효과가 있다.

[0235] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니라, 클럭에 동기하여 동작하지 않는 의사 SRAM에도 적용 가능하다.

[제4 실시예]

[0237] 본 실시예는, 버스트 판독/기입에 있어서, 판독 또는 기입 신호가 생성된 제1 클럭에 따라서 선두부터 수 개의 비트의 판독/기입을 행하고, 커맨드 레이턴시 CL에 의해 규정되는 제2 클럭 이후의 클럭에 따라서, 남은 비트의 판독/기입을 행하는 동기식 의사 SRAM에 관한 것이다.

[0238] (구성)

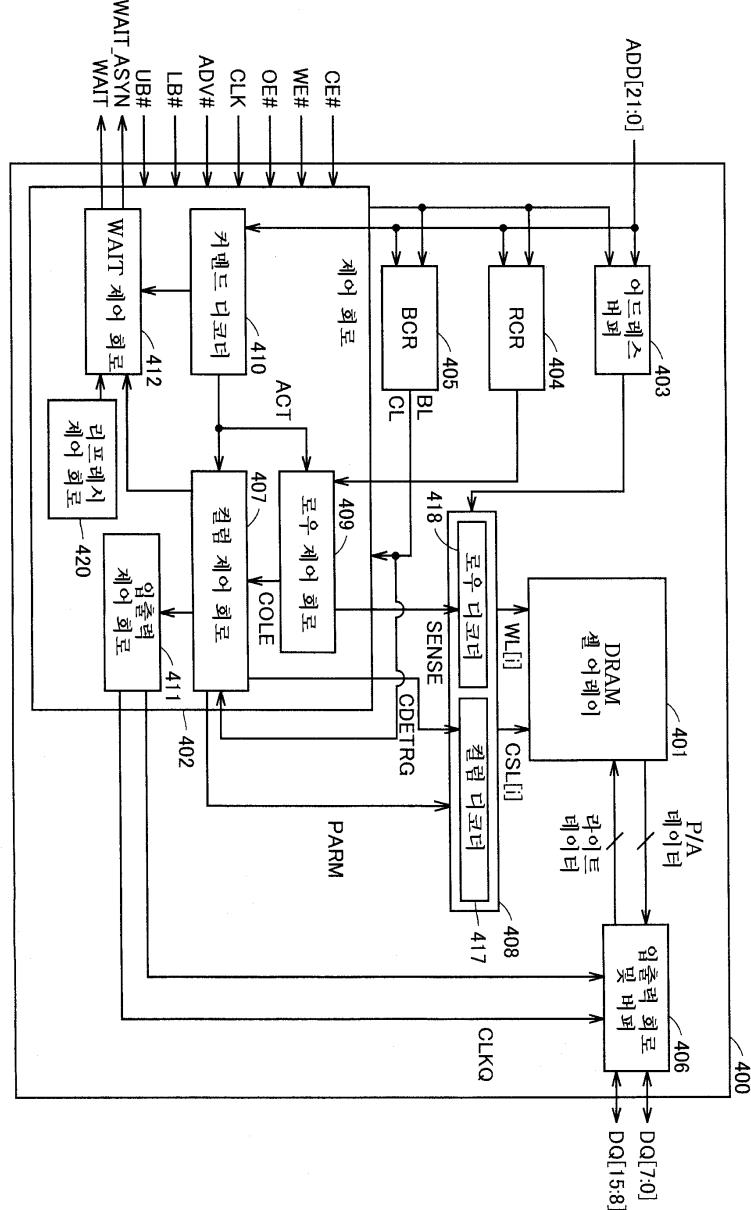

[0239] 도 12는 본 실시예에 따른 동기식 의사 SRAM(400)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(400)은, DRAM 셀 어레이(401)와, 제어 회로(402)와, 어드레스 버퍼(403)와, RCR(Refresh Configuration Register)(404)과, BCR(405)(Bus Configuration Register)과, 입출력 회로 및 버퍼(406)를 구비한다.

[0240] DRAM 셀 어레이(401)는 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다.

[0241] 입출력 회로 및 버퍼(406)는, 데이터 입출력 단자 DQ를 통하여, 외부의 시스템 측과의 사이에서 데이터의 입출력을 행한다. 입출력 회로 및 버퍼(406)는 입출력 제어 회로(411)로부터 공급되는 클럭 신호 CLKQ에 동기하여, DRAM 셀로부터 출력된 데이터를 출력한다.

[0242] RCR(404)은 셀프 리프레시의 방법을 규정한다.

[0243] BCR(405)은 외부의 시스템과의 인터페이스, 예를 들면, 버스트 길이 BL 및 커맨드 레이턴시 CL 등을 기억한다.

[0244] 어드레스 버퍼(403)는 외부 어드레스 신호 ADD[21:0]를 받아, 내부 어드레스 신호를 생성한다. 동기식 의사 SRAM에서는, 어드레스 버퍼(403)는, 외부 어드레스 취득 신호 ADV#가 「L」일 때에, 외부 어드레스 신호 ADD[21:0]를 취득한다. 외부 어드레스 취득 신호 ADV#가 「L」로 되는 타이밍은, 판독 신호 READ 또는 기입 신호 WRITE가 생성되는 타이밍보다도 빠르다. 그리고, 이 때 공급되는 외부 어드레스 신호 ADD[21:0]는, 로우 어드레스뿐만 아니라 컬럼 어드레스도 포함한다. 따라서, 로우 어드레스 및 컬럼 어드레스는, 판독 신호 READ 또는 기입 신호 WEITE가 생성되는 것보다도 앞서서, 취득된다.

[0245] 이와 같이, 로우 어드레스뿐만 아니라 컬럼 어드레스도, 판독 신호 READ 또는 기입 신호가 생성되는 데 앞장선 취득을 할 수 있기 때문에, 로우 액세스의 후, 커맨드 레이턴시 CL에 의해 규정되는 클럭이 입력될 때까지 대기하지 않고서, 컬럼 액세스를 개시할 수 있다. 본 실시예에서는 이러한 특징을 이용하여, 판독 신호 READ 또는 기입 신호가 생성되었을 때의 클럭(제1 클럭이라고 함)에 따라서, 버스트 액세스의 선두 컬럼의 데이터를 판독하기 위한 컬럼 액세스 처리를 행한다. 그리고, 커맨드 레이턴시 CL에 의해 규정되는 클럭(제2 클럭이라는)에 따라서, 버스트 액세스의 남은 컬럼의 데이터를 판독하기 위한 컬럼 액세스 처리를 행한다.

[0246] 제어 회로(402)는, 커맨드 디코더(410)와, 입출력 제어 회로(411)와, 로우 제어 회로(409)와, 컬럼 제어 회로(407)와, WAIT 제어 회로(412)와, 리프레시 제어 회로(420)를 포함한다.

[0247] 커맨드 디코더(410)는 외부 제어 신호로부터 생성된 내부 제어 신호의 논리 레벨의 조합에 따라서, 로우 활성화 신호 ACT, 판독 신호 READ, 및 기입 신호 WRITE를 생성한다.

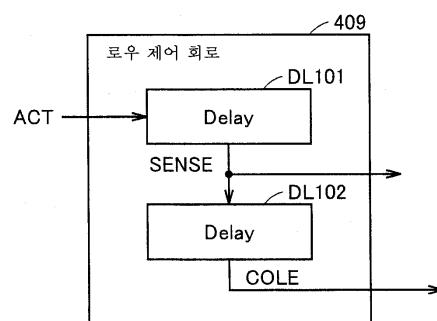

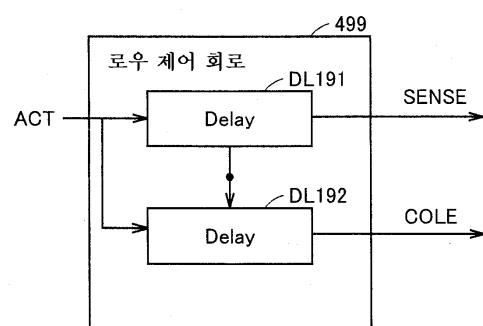

- [0248] 로우 제어 회로(409)는, 컬럼 인에이블 신호 COLE, 메모리 셀과 글로벌 비트선 쌍 GIO, ZGIO의 사이에 마련된 비트선 쌍 BL, ZBL에 접속된 센스 앰프를 활성화시키는 센스 앰프 활성화 신호 SENSE를 생성한다. 도 13은 로우 제어 회로(409)의 구성을 도시한다. 동도를 참조하여, 지연 회로(Delay) DL101은, 판독 신호 READ 또는 기입 신호 WRITE가 생성된 클럭인 제1 클럭 CLK0의 상승에 응답하여 활성화되는 로우 활성화 신호 ACT를 받는다. 지연 회로(Delay) DL101은 로우 활성화 신호 ACT를 지연시킨 센스 앰프 활성화 신호 SENSE를 출력한다. 지연 회로(Delay) DL102는 센스 앰프 활성화 신호 SENSE를 받아, 센스 앰프 활성화 신호 SENSE를 지연시킨 컬럼 인에이블 신호 COLE를 생성한다.

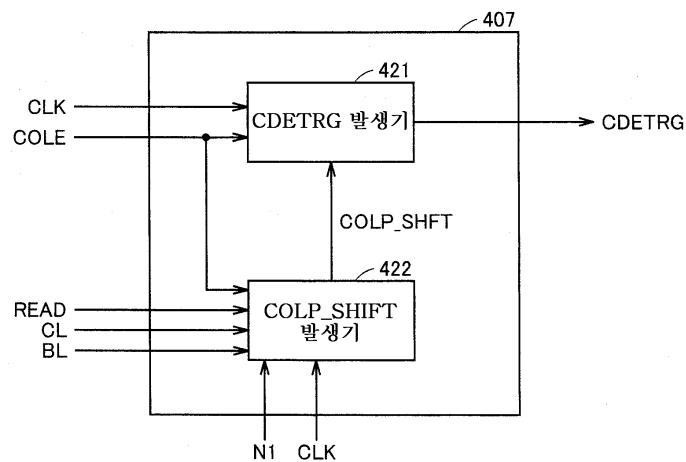

- [0249] 컬럼 제어 회로(407)는, 글로벌 비트선 쌍 GIO, ZGIO에 접속된 프리 앰프를 활성화시키는 프리 앰프 활성화 신호 PARM과, 컬럼 디코더 활성화 트리거 신호 CDETRG를 생성한다. 도 14는 컬럼 제어 회로(407)의 구성을 일부를 도시한다. 동도를 참조하여, 컬럼 제어 회로(407)는 COLP\_SHFT 발생기(422)와, CDETRG 발생기(421)를 구비한다.

- [0250] COLP\_SHFT 발생기(422)는, 외부 클럭 CLK, 판독 신호 READ(또는 기입 신호 WRITE), 커맨드 레이턴시 CL, 판독 신호 READ(또는 기입 신호 WRITE)가 생성되었을 때의 클럭인 제1 클럭 CLK0에서 판독하는 비트 수 N1(본 실시 예에서는 「1」임), 및 버스트 길이 BL에 기초하여, 컬럼 시프트 신호 COLP\_SHFT를 생성한다. 즉, COLP\_SHFT 발생기(422)는, 판독 신호 READ(또는 기입 신호 WRITE)가 생성되었을 때의 클럭 후의, (CL-N1)개째의 클럭 CLK의 하강에 응답하여, 컬럼 시프트 신호 COLP\_SHFT를 활성화하고, 버스트 길이 카운터의 카운터치가 버스 길이 BL로 된 것에 응답하여, 컬럼 시프트 신호 COLP\_SHFT를 비활성화한다.

- [0251] CDETRG 발생기(421)는 컬럼 시프트 신호 COLP\_SHFT, 외부 클럭 CLK, 및 컬럼 인에이블 신호 COLE에 기초하여, 컬럼 디코더 활성화 트리거 신호 CDETRG를 생성한다.

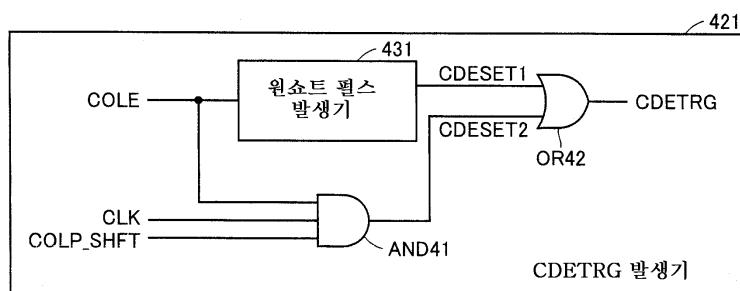

- [0252] 도 15는 CDETRG 발생기(421)의 상세한 구성을 도시한다. 동도를 참조하여, CDETRG 발생기(421)는, 원쇼트 펄스 발생기(431)와, 논리곱 회로 AND41과, 논리합 회로 OR42를 구비한다. 원쇼트 펄스 발생기(431)는 컬럼 인에이블 신호 COLE의 상승에서, 레벨이 「H」의 원쇼트 펄스를 생성한다. 이 원쇼트 펄스는 제1 클럭 CLK0에 동기하여 액세스되는 제1번째의 컬럼을 활성화시키는 신호로 된다.

- [0253] 논리곱 회로 AND41은, 컬럼 인에이블 신호 COLE가 「H」이고, COLP\_SHFT가 「H」일 때에, 레벨이 「H」의 클럭 펄스를 출력한다. 이 클럭 펄스가, 제2 클럭 CLK2 이후의 클럭에 동기하여 액세스되는 제2번째 내지 제4번째의 컬럼을 활성화시키는 신호로 된다.

- [0254] 논리합 회로 OR42는 원쇼트 펄스 발생기(431)로부터 출력되는 원쇼트 펄스, 및 논리곱 회로 AND41로부터 출력되는 클럭 펄스를 합성한다. 합성된 펄스가 컬럼 디코더 활성화 트리거 신호 CDETRG의 펄스로 된다.

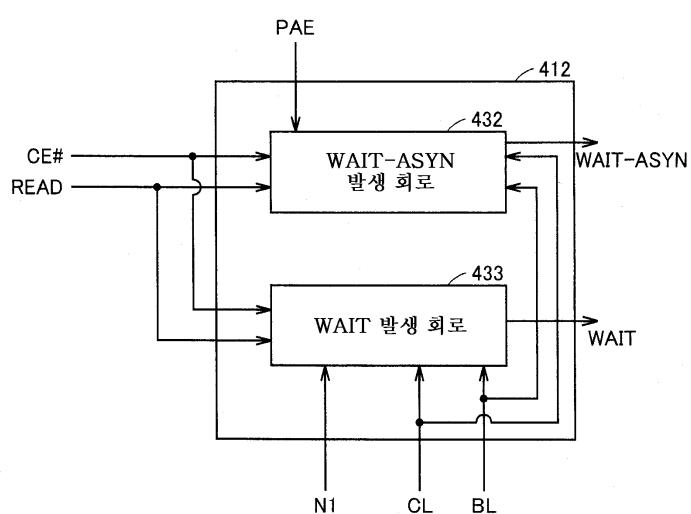

- [0255] 도 16은 WAIT 제어 회로(412)의 구성을 도시한다. 동도를 참조하여, 이 WAIT 제어 회로(412)는 WAIT\_ASYNC 발생 회로(432)와, WAIT 발생 회로(433)를 구비한다.

- [0256] WAIT\_ASYNC 발생 회로(432)는, 커맨드 디코더(410)로부터 판독 신호 READ 또는 기입 신호 WRITE가 입력되고, 또한 외부 칩 인에이블 신호 CE#가 「L」로 활성화되어 있는 것에 응답하여, WAIT\_ASYNC 신호를 「L」로 한다. 그 후, WAIT\_ASYNC 발생 회로(432)는, 프리 앰프 활성화 신호 PAE를 받은 후, 선두 비트의 데이터 D0이 데이터 출력 단자 DQ로부터 출력되는 데 요하는 소정 시간의 경과 후, WAIT\_ASYNC 신호를 「H」로 한다. 그 후, WAIT\_ASYNC 발생 회로(432)는 외부 칩 인에이블 신호 CE#가 「H」로 비활성화된 것에 응답하여, WAIT\_ASYNC 신호를 Hi-Z로 한다.

- [0257] WAIT 발생 회로(433)는 커맨드 디코더(410)로부터 판독 신호 READ 또는 기입 신호 WRITE가 입력되고, 또한 외부 칩 인에이블 신호 CE#가 「L」로 활성화되어 있는 것에 응답하여, WAIT 신호를 「L」로 한다. 그 후, WAIT 발생 회로(433)는, (CL-1)+(판독 신호 READ 또는 기입 신호 WRITE가 생성되었을 때의 클럭인 제1 클럭 CLK0에서 판독하는 비트 수 N1)의 개수의 클럭을 받은 후, WAIT 신호를 「H」로 활성화한다. 그 후, WAIT 발생 회로(433)는, 외부 칩 인에이블 신호 CE#가 「H」로 비활성화된 것에 응답하여, WAIT 신호를 Hi-Z로 한다.

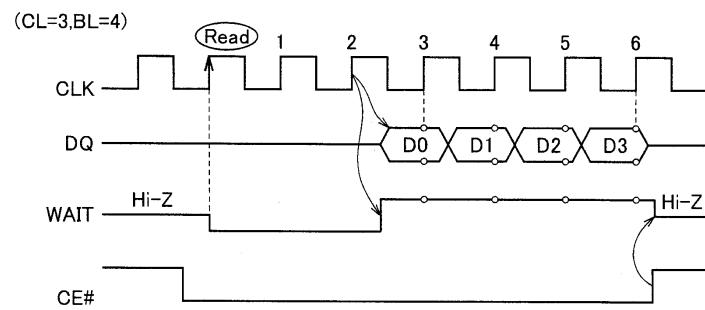

- [0258] (배경 기술의 동기식 의사 SRAM의 WAIT 신호의 타이밍)

- [0259] 도 17은 배경 기술의 동기식 의사 SRAM의 WAIT 신호의 타이밍을 도시하는 도면이다. 동도에 도시하는 바와 같이, 판독 신호 READ가 입력되고, 또한 외부 칩 인에이블 신호 CE#가 「L」로 활성화되어 있는 것에 응답하여, WAIT 신호는 「L」로 된다. 그 후, (CL-1)(CL=3)의 개수의 클럭을 받은 후, WAIT 신호가 「H」로 된다.

그 후, 외부 칩 인에이블 신호 CE#가 「H」로 비활성화된 것에 응답하여, WAIT 신호는 Hi-Z로 된다.

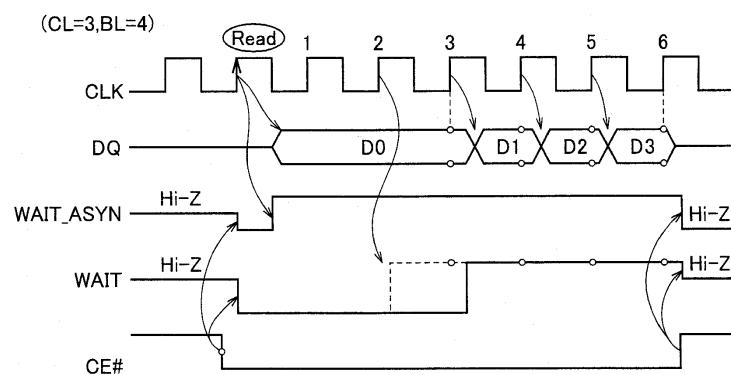

[0260] (본 실시예의 동기식 의사 SRAM(400)의 WAIT\_ASYN 신호 및 WAIT 신호의 타이밍)

도 18은 본 실시예의 동기식 의사 SRAM(400)의 WAIT\_ASYN 신호 및 WAIT 신호의 타이밍을 도시하는 도면이다. 동도에 도시한 바와 같이, 판독 신호 READ가 입력되고, 또한 외부 칩 인에이블 신호 CE#가 「L」로 활성화되어 있는 것에 응답하여, WAIT\_ASYN 신호는 「L」로 된다. 그 후, 프리 앰프 활성화 신호 PAE를 받은 후, 선두 비트의 데이터 D0이 데이터 출력 단자 DQ로부터 출력되는 데 요하는 소정 시간의 경과 후, WAIT\_ASYN 신호는 「H」로 된다. 이에 의해, 클럭 CLK0에 따라서 컬럼 액세스가 행하여지는 선두 비트의 데이터 D0이 출력되는 타이밍을 외부의 시스템 측에 통지할 수 있다. 그 후, 외부 칩 인에이블 신호 CE#가 「H」로 비활성화된 것에 응답하여, WAIT\_ASYN 신호는 Hi-Z로 된다.

[0262] 또한, 동도에 도시한 바와 같이, 판독 신호 READ가 입력되고, 또한 외부 칩 인에이블 신호 CE#가 「L」로 활성화되어 있는 것에 응답하여, WAIT 신호는 「L」로 된다. 그 후, (CL-1+N1)(CL=3, N1=1)의 개수의 클럭을 받은 후, WAIT 신호가 「H」로 된다. 이에 의해, 커맨드 레이턴시 CL에 기초하여 정해지는 클럭에 동기하여 컬럼 액세스가 행하여지는 선두 비트의 데이터 D1이 출력되는 타이밍을 외부의 시스템 측에 통지할 수 있다. 그 후, 외부 칩 인에이블 신호 CE#가 「H」로 비활성화된 것에 응답하여, WAIT 신호는 Hi-Z로 된다.

[0263] 재차, 도 12를 참조하여, 주변 회로군(408)은, 로우 디코더(418)와, 컬럼 디코더(417)와, 도시하지 않은 센스 앰프와, 도시하지 않은 프리 앰프를 포함한다.

[0264] 로우 디코더(418)는 선택된 워드선을 활성화한다.

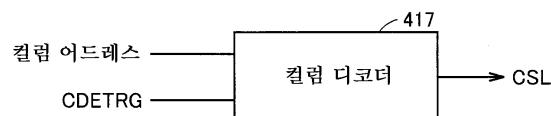

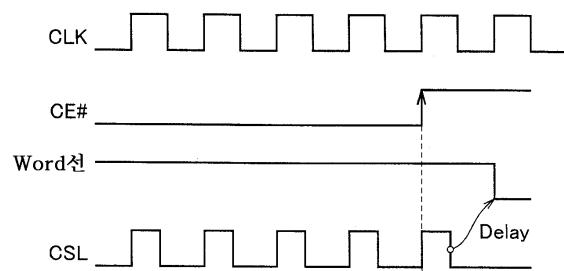

[0265] 도 19는 컬럼 디코더(417)의 구성을 도시한다. 동도에 도시한 바와 같이, 컬럼 디코더 활성화 트리거 신호 CDETRG가 활성화되었을 때에, 입력된 컬럼 어드레스에 대응하는 컬럼 선택 신호 CSL을 활성화한다.

[0266] 도시하지 않은 센스 앰프는 제1 증폭 회로이고, 비트선 쌍 BL, ZBL 사이의 전위차를 증폭한다.

[0267] 도시하지 않은 프리 앰프는 제2 증폭 회로이고, 복수의 비트선 쌍 BL, ZBL에 접속된 글로벌 비트선 쌍 GIO, ZGIO 사이의 전위차를 확대한다.

[0268] 도 12의 리프레시 제어 회로(420)는 도시하지 않은 내부의 리프레시 타이머에 기초하여, DRAM 셀 어레이의 셀 프 리프레시 동작을 제어한다.

[0269] (본 실시예의 동기식 의사 SRAM의 동작)

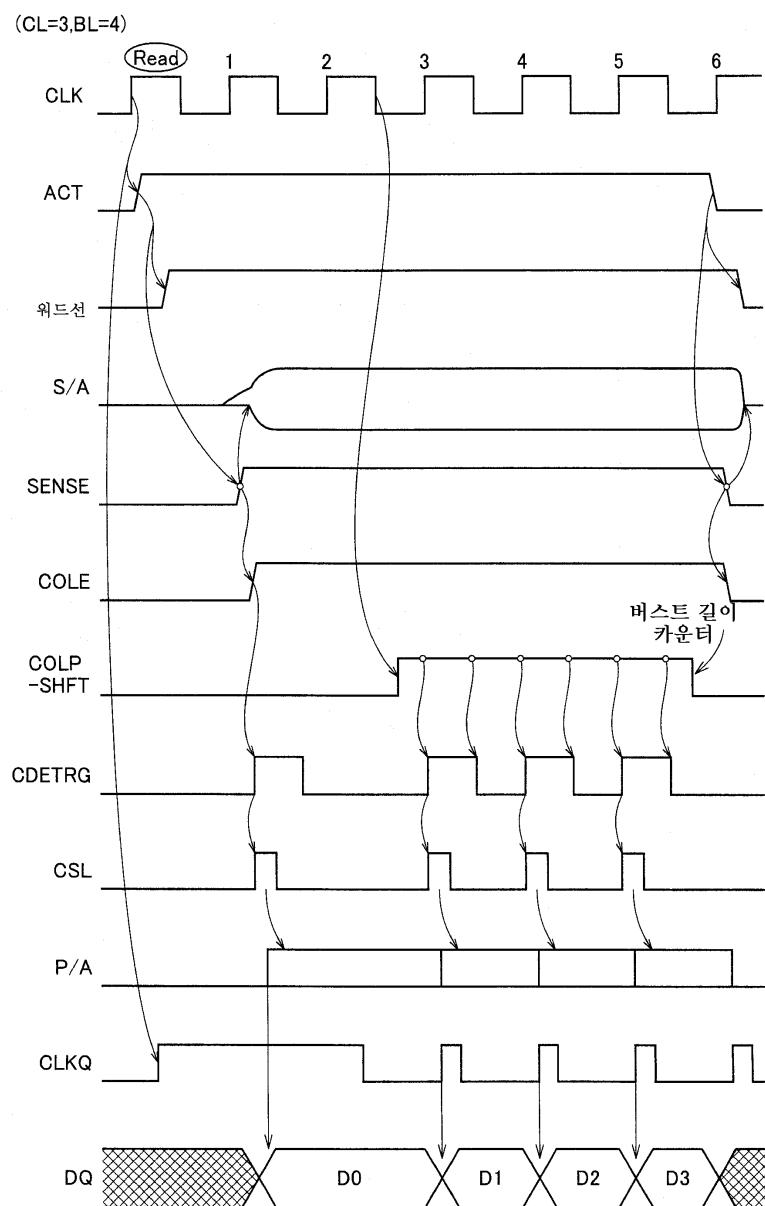

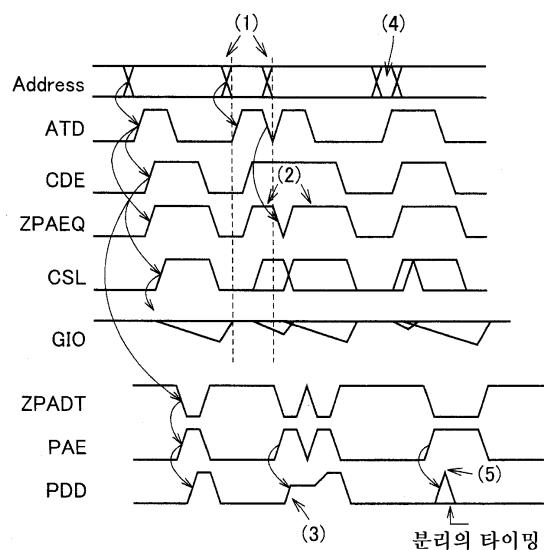

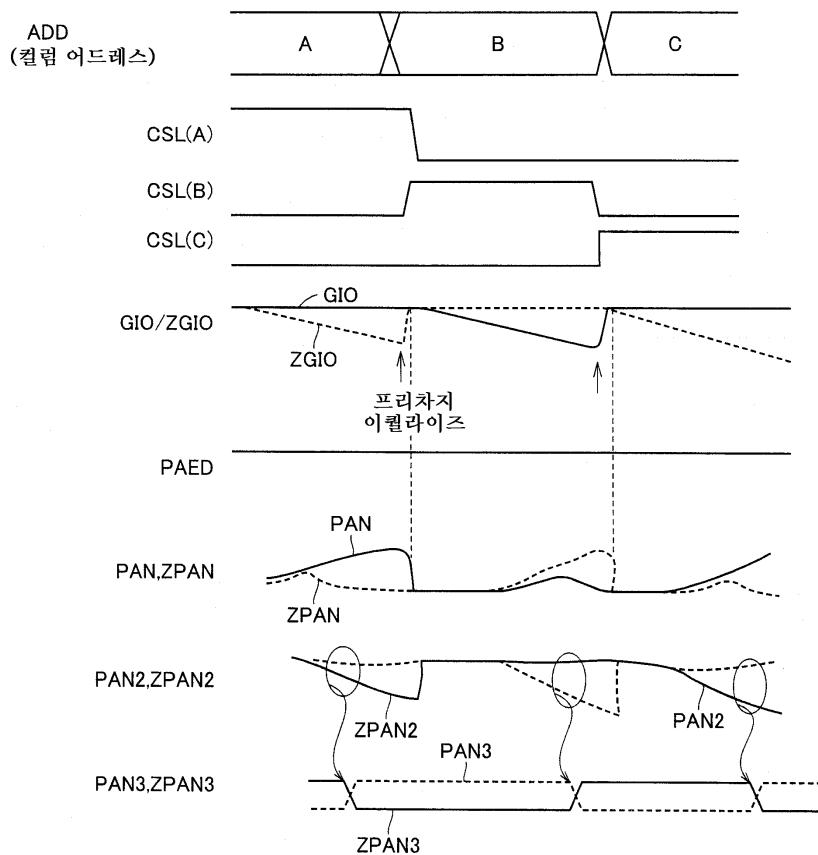

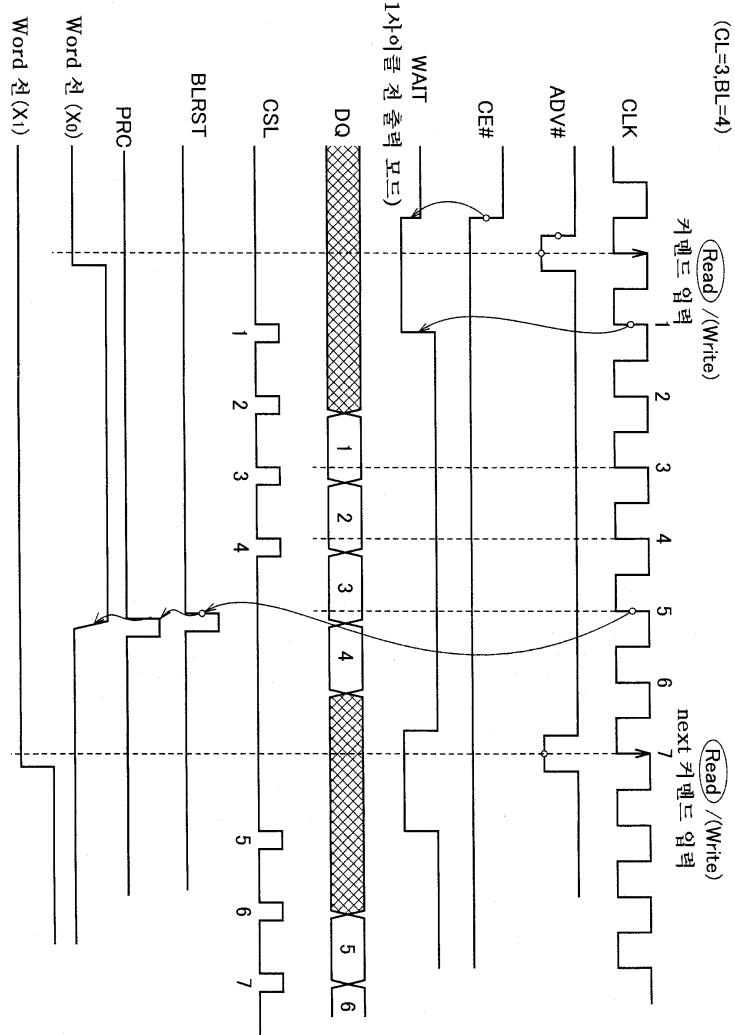

[0270] 도 20은 본 실시예의 동기식 의사 SRAM(400)의 동작을 도시하는 타이밍차트이다. 동도를 참조하여, 우선, 판독 신호 READ가 생성된 클럭 CLK0(제1 클럭)의 상승에 동기하여, 이하와 같이 로우 액세스 처리가 행하여진다.

[0271] 커맨드 디코더(410)는 클럭 CLK0에 동기하여 활성화된 로우 활성화 신호 ACT를 출력한다.

[0272] 로우 디코더(418)는 어드레스 버퍼(403)로부터 보내지는 로우 어드레스에 기초하여, 워드선을 선택하고, 선택한 워드선을 활성화한다.

[0273] 로우 제어 회로(409)는 로우 활성화 신호 ACT를 지연시켜 센스 앰프 인에이블 신호 SENSE가 활성화한다. 이에 의해, 주변 회로군(408) 내의 도시하지 않은 센스 앰프가 비트선 쌍의 증폭을 행한다.

[0274] 로우 제어 회로(409)는 센스 앰프 인에이블 신호 SENSE를 지연시켜, 컬럼 인에이블 신호 COLE를 활성화한다.

[0275] 다음에, 제1 클럭 CLK0의 상승에 동기하여, 제1번째의 컬럼의 컬럼 액세스 처리가 행하여진다.

[0276] CDETRG 발생기(421)는 컬럼 인에이블 신호 COLE의 상승으로부터, 원쇼트 펄스를 생성한다. 이것이 컬럼 디코더 활성화 트리거 신호 CDETRG의 제1번째의 펄스로 된다.

[0277] 컬럼 디코더(417)는 컬럼 디코더 활성화 트리거 신호 CDETRG의 제1번째의 펄스에 응답하여, 입력된 제1번째의 컬럼의 컬럼 어드레스에 대응하는 컬럼 선택 신호 CSL을 활성화한다.

[0278] 컬럼 선택 신호 CSL로 선택된 제1번째의 컬럼의 비트선 쌍의 전위가 주변 회로군(408) 내의 도시하지 않은 프리 앰프에 보내져, 증폭이 행하여진다.

[0279] 프리 앰프에서 증폭된 제1번째의 컬럼의 데이터는 입출력 회로 및 버퍼(406)에 전송된다. 한편, 입출력 제어 회로(411)는 외부 클럭 CLK를 받아 내부 클럭 신호 CLKQ를 출력한다. 여기서, 제1 클럭 CLK0의 상승에 응답

하여, 선두의 클럭 신호 CLKQ의 펄스가 생성된다.

[0280] 입출력 회로 및 버퍼(406)는 클럭 신호 CLKQ에 동기하여, 제1 번째의 컬럼으로부터 출력된 데이터 D0을 데이터 출력 단자 DQ를 통하여 외부로 출력한다.

[0281] 다음으로, 제1 클럭 CLK0으로부터 (CL-N1)=2개째의 클럭 CLK2(제2 클럭) 이후의 클럭에 동기하여, 제2번째 내지 제4번째의 컬럼의 컬럼 액세스 처리가 행하여진다.

[0282] COLP\_SHFT 발생기(422)는, 클럭 CLK2(제2 클럭)의 하강에 응답하여, 컬럼 시프트 신호 COLPSHFT를 활성화하고, 버스트 길이 카운터의 카운터치가 버스트 길이 BL로 된 것에 응답하여, 컬럼 시프트 신호 COLPSHFT를 비활성화한다.

[0283] CDETRG 발생기(421)는 컬럼 시프트 신호 COLP\_SHFT가 「H」인 기간에 포함되는 3개의 클럭 펄스를 추출한다. 이들이 컬럼 디코더 활성화 트리거 신호 CDETRG의 제2번째 내지 제4번째의 펄스로 된다.

[0284] 컬럼 디코더(417)는 컬럼 디코더 활성화 트리거 신호 CDETRG의 제2번째 내지 제4번째의 펄스에 응답하여, 입력된 제2번째 내지 제4번째의 컬럼의 컬럼 어드레스에 대응하는 컬럼 선택 신호 CSL을 활성화한다.

[0285] 컬럼 선택 신호 CSL로 선택된 제2번째 내지 제4번째의 컬럼의 비트선 쌍의 전위가 주변 회로군(408) 내의 도시하지 않은 프리 앰프에 전송되고, 증폭이 행하여진다.

[0286] 프리 앰프에서 증폭된 제2번째 내지 제4번째의 컬럼의 데이터는 입출력 회로 및 버퍼(406)에 보내진다. 한편, 입출력 제어 회로(411)는 외부로부터 클럭 신호 CLK를 받아 내부 클럭 신호 CLKQ를 출력한다. 클럭 신호 CLKQ의 제2번째 내지 제4번째의 펄스의 타이밍은, 통상 그대로의 타이밍이다.

[0287] 입출력 회로 및 버퍼(406)는 클럭 신호 CLKQ의 제2번째 내지 제4번째의 펄스에 동기하여, 제2번째 내지 제4번째의 컬럼으로부터 출력된 데이터 D1 내지 D3을 데이터 출력 단자 DQ를 통하여 외부로 출력한다.

[0288] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, 커맨드 레이턴시 CL에 의해 규정되는 타이밍보다도 빠른 시기에 데이터를 출력하기 때문에, 시스템 측에서는 데이터를 빠르게 수취할 수 있고, 처리를 빠르게 개시할 수 있다. 또한, 버스가 불확정한 시간을 짧게 할 수 있다.

[0289] 본 실시예에서는 제1 클럭 CLK0에 동기하여 1개의 데이터를 출력했지만, 이것에 한정하는 것이 아니고, 2개 또는 3개의 데이터를 출력하는 것으로 하여도 무방하다. 제1 클럭 CLK0에 동기하여 출력하는 데이터의 개수는, 시스템 측의 형편에 따라 정하면 된다.

[0290] 또한, 본 실시예에서는 외부 칩 인에이블 신호 CE#가 「H」로 비활성화된 것에 응답하여, WAIT\_ASYN 신호는 Hi-Z로 되는 것으로 했지만, 이것에 한정되는 것은 아니다. 예를 들면, WAIT 신호가 「H」로 된 것에 응답하여, WAIT\_ASYN 신호는 Hi-Z로 되는 것으로 해도 된다.

[0291] 또한, 제1 클럭 CLK0에서 판독하는 비트 수 N1은, 고정치이더라도, 외부 신호에 의해서 레지스터에 값이 설정되는 것이어도 된다.

[0292] 또한 본 실시예에서는, 제1 클럭 CLK0에서 판독하는 비트 수 N1이 「1」이기 때문에, 원쇼트 펄스 발생기(431)를 이용하여, 제1 클럭 CLK0에 동기하여 액세스되는 1개의 컬럼을 활성화시키는 신호를 생성했지만, N1이 2 이상인 경우에는, 생성한 원쇼트 펄스를 1 사이클마다 시프트한 펄스를 N1개 출력하는 회로를 추가하면 된다.

[0293] 또한, 로우 제어 회로는 도 13에 도시하는 것에 한정되는 것이 아니고, 예를 들면, 도 21에 도시한 바와 같은 것이어도 무방하다. 도 21을 참조하여, 지연 회로(Delay) DL191 및 지연 회로(Delay) DL192는, 판독 신호 READ 또는 기입 신호 WRITE가 생성된 클럭인 제1 클럭 CLK0의 상승에 응답하여 활성화되는 로우 활성화 신호 ACT를 수신한다. 지연 회로(Delay) DL191은 로우 활성화 신호 ACT를 지연시킨 센스 앰프 활성화 신호 SENSE를 출력한다. 지연 회로(Delay) DL192는 로우 활성화 신호 ACT를 지연시킨 컬럼 인에이블 신호 COLE를 생성한다.

[0294] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니고, 플래시 메모리 등 같은 것이어도 되고, 클럭에 동기하여 동작하는 반도체 기억 장치이면 어떠한 것에도 적용할 수 있다. 특히, 고집적, 고속이 요구가 높은 동기식 의사 SRAM에의 응용이 적합하다.

[0295] 또한, 본 실시예의 동작 예에서는 외부 신호에 의해서 판독 신호 READ가 생성되었을 때의 동작을 설명했지만,

외부 신호에 의해서 기입 신호 WRITE가 생성되었을 때도 마찬가지로 동작한다.

[0296] [제4 실시예의 변형 예]

본 변형 예는, 리프레시 동작중에 판독 신호 READ 또는 기입 신호 WRITE가 생성되었을 때에도, 제4 실시예와 마찬가지로, 버스트 판독/기입에 있어서, 제1 클럭에 따라서 선두로부터 수 개의 비트를 판독/기입, 커맨드 레이턴시 CL에 의해 규정되는 제2 클럭 이후의 클럭에 따라서, 남은 비트를 판독/기입하는 동기식 의사 SRAM에 관한 것이다.

본 변형 예는 리프레시 동작중에 판독 신호 READ 또는 기입 신호 WRITE가 생성되었을 때에 있어서도 대응할 수 있도록, 제4 실시예의 제어 회로(402)에 커맨드 시프트 회로(480)를 추가한다.

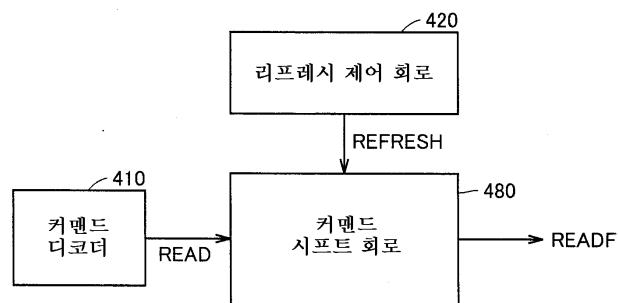

도 22는 커맨드 시프트 회로(480)의 입출력 신호를 도시하는 도면이다. 커맨드 시프트 회로(480)에는, 커マン드 디코더(410)로부터 판독 신호 READ와, 리프레시 제어 회로(420)로부터 리프레시 동작 신호 REFRESH가 입력되고, 수정 판독 신호 READF를 출력한다. 이 수정 판독 신호 READF는 판독 신호 READ가 전송되고 있는 회로에, 판독 신호 READ 대신에 보내진다.

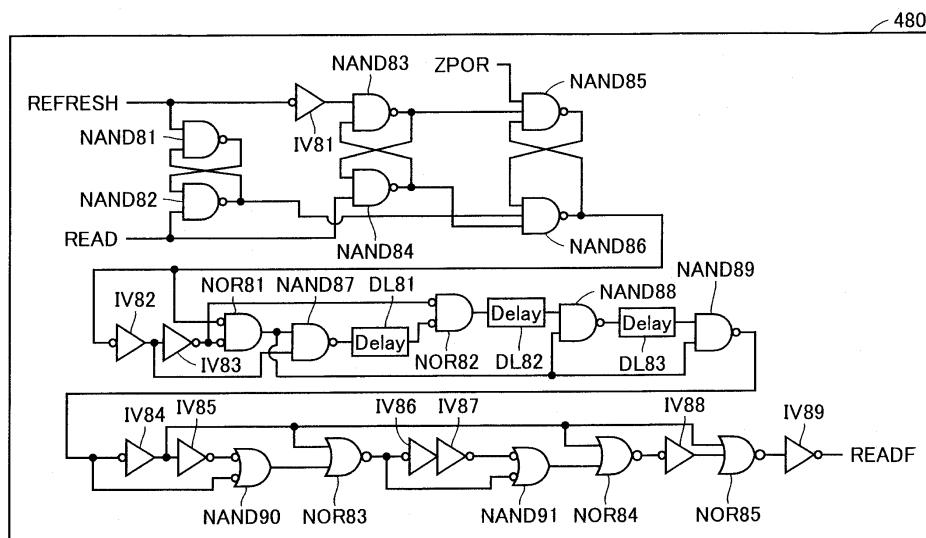

도 23은 커マン드 시프트 회로(480)의 상세한 구성을 도시한다. 동도를 참조하여, 리프레시 동작 신호 REFRESH를 받는 반전 논리곱 회로 NAND81과, 판독 신호 READ를 받는 반전 논리곱 회로 NAND82는, 플립플롭을 구성한다. 인버터 IV81은 리프레시 동작 신호 REFRESH를 반전한다.

인버터 IV81의 출력을 받는 반전 논리곱 회로 NAND83과, 판독 신호 READ를 받는 반전 논리곱 회로 NAND84는, 플립플롭을 구성한다.

반전 논리곱 회로 NAND83의 출력 및 리셋 신호 ZPOR을 받는 반전 논리곱 회로 NAND85와, 반전 논리곱 회로 NAND82의 출력 및 반전 논리곱 회로 NAND84의 출력을 받는 반전 논리곱 회로 NAND86은, 플립플롭을 구성한다. 리셋 신호 ZPOR은 전원이 온으로 되면 「H」로 활성화된다.

인버터 IV82는, 반전 논리곱 회로 NAND86의 출력을 받는다. 인버터 IV83은 인버터 IV82의 출력을 받는다. 반전 논리합 회로 NOR81은 반전 논리곱 회로 NAND86의 출력과 인버터 IV83의 출력을 받는다.

반전 논리곱 회로 NAND87은 반전 논리합 회로 NOR81의 출력과 인버터 IV82의 출력을 받는다. 지연 회로 DL81은 반전 논리곱 회로 NAND87의 출력을 지연시킨다. 반전 논리합 회로 NOR82는 인버터 IV83의 출력과 지연 회로 DL81의 출력을 받는다. 지연 회로 DL82는 반전 논리합 회로 NOR82의 출력을 지연시킨다.

반전 논리곱 회로 NAND88은 지연 회로 DL82의 출력과 반전 논리합 회로 NOR81의 출력을 받는다. 지연 회로 DL83은 반전 논리곱 회로 NAND88의 출력을 지연시킨다. 반전 논리곱 회로 NAND89은 지연 회로 DL83의 출력과 반전 논리합 회로 NOR81의 출력을 받는다.

인버터 IV84는 반전 논리곱 회로 NAND89의 출력을 받는다. 인버터 IV85는 인버터 IV(84)의 출력을 받는다. 반전 논리곱 회로 NAND90은 인버터 IV85의 출력과 반전 논리곱 회로 NAND89의 출력을 받는다. 반전 논리합 회로 NOR83은 반전 논리곱 회로 NAND90의 출력과 인버터 IV(84)의 출력을 받는다. 인버터 IV86은 반전 논리합 회로 NOR83의 출력을 반전한다. 인버터 IV87은 인버터 IV86의 출력을 반전한다.

반전 논리곱 회로 NAND91은 반전 논리합 회로 NOR83의 출력과 인버터 IV87의 출력을 받는다. 반전 논리합 회로 NOR84는 반전 논리곱 회로 NAND91의 출력과 인버터 IV84의 출력을 받는다. 인버터 IV88은 반전 논리합 회로 NOR84의 출력을 반전한다. 반전 논리합 회로 NAND85는 인버터 IV84의 출력과 인버터 IV88의 출력을 받는다. 인버터 IV89는 반전 논리합 회로 NAND85의 출력을 반전하여 수정 판독 신호 READF를 출력한다.

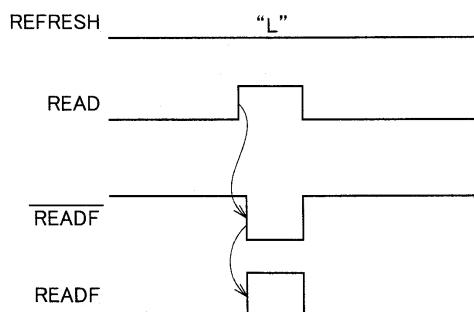

도 24a는 리프레시 동작이 행하여지고 있지 않을 때에 판독 신호 READ가 입력되었을 때의 수정 판독 신호 READF를 도시하는 도면이다. 동도에 도시한 바와 같이, 리프레시 동작이 행하여지고 있지 않을 때, 리프레시 동작 신호 REFRESH는 「L」이다. 커マン드 시프트 회로(480)에서 생성된 수정 판독 신호 READF가 활성화되는 타이밍은, 판독 신호 READ가 활성화되는 타이밍과 거의 동일하다. 따라서, 이 수정 판독 신호 READF를 판독 신호 READ의 대신에 이용하여도, 제4 실시예와 마찬가지의 동작을 행할 수 있다.

도 24b는 리프레시 동작중에 판독 신호 READ가 입력되었을 때의 수정 판독 신호 READF를 도시하는 도면이다. 동도에 도시한 바와 같이, 리프레시 동작이 행하여지고 있을 때에, 리프레시 동작 신호 REFRESH는 「H」이지만, 리프레시 동작이 종료하면 「L」로 된다. 커マン드 시프트 회로(480)에서 생성된 수정 판독 신호 READF가 활성화되는 타이밍은, 리프레시 동작 신호 REFRESH의 하강, 리프레시의 종료 직후로 된다. 따라서, 이 수정

판독 신호 READF를 판독 신호 READ의 대신에 이용하면, 리프레시 완료 후부터 즉시 제4 실시예와 마찬가지의 동작을 행할 수 있다. 즉, 도 20에서는 판독 신호 READ가 생성되었을 때의 클럭 CLK0을 기점으로 하여 일련의 처리가 행하여졌지만, 본 변형 예는 수정 판독 신호 READF가 입력되었을 때의 클럭을 기점으로 하여 일련의 처리가 행하여지게 된다.

[0310] 또한, 본 변형 예에서는 리프레시 동작중에 판독 신호 READ 또는 기입 신호 WRITE가 생성된 경우에 대해 설명했지만, 판독 또는 기입 동작 등의 실행중에, 새로운 판독 신호 READ 또는 기입 신호 WRITE가 생성된 경우에 대해해도, 마찬가지로 적용할 수 있다. 특히, 이 새로운 판독 또는 기입을 행하는 워드선이, 그 전의 판독 또는 기입을 행하고 있던 워드선과 서로 다를 때에는, 원래의 워드선의 비활성화, 새로운 워드선의 활성화, 및 센스 앰프에 의한 증폭 등의 처리가 필요하다는 점에서, 본 변형은 유효하다고 말할 수 있다.

[0311] 또한 본 변형 예에서는, 커맨드 시프트 회로(480)는 판독 신호 READ에 의해서 수정 판독 신호 READ를 생성하는 것으로 했지만, 이것에 한정하는 것이 아니라, 기입 신호 WRITE에 의해서 수정 기입 신호 WRITEF를 생성하는 것이어도 된다.

[제5 실시예]

[0313] 본 실시예는 동기 모드와 비동기 모드의 양방의 모드를 갖고, 각각의 모드에 적합한 제2 증폭 회로인 프리 앰프를 갖는 동기식 의사 SRAM에 관한 것이다. 또한, 제1 증폭 회로인 센스 앰프는 비트선 쌍 BL, ZBL의 전위를 증폭하는 것이고, 제2 증폭 회로인 프리 앰프는 복수의 비트선 쌍 BL, ZBL에 접속된 글로벌 비트선 쌍 GIO, ZGIO의 전위를 증폭하는 것이다.

[0314] (구성)

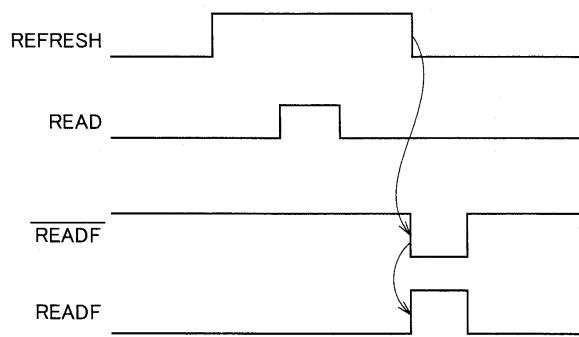

[0315] 도 25는 본 실시예에 따른 동기식 의사 SRAM(500)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(500)는, DRAM 셀 어레이(501)와, 제어 회로(502)와, 주변 회로군(504)과, 어드레스 버퍼(503)를 포함한다.

[0316] DRAM 셀 어레이(501)는 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다.

[0317] 어드레스 버퍼(503)는 외부 어드레스 신호 ADD[21:0]를 받아, 내부 어드레스 신호를 생성한다.

[0318] 제어 회로(502)는, 컬럼 제어 회로(505)와, 커맨드 디코더(506)와, 공통 신호 생성 회로(507)와, 동기 대응 프리 앰프 제어 회로(508)와, 비동기 대응 프리 앰프 제어 회로(509)와, 리프레시 제어 회로(510)와, WAIT 제어 회로(511)를 구비한다.

[0319] 컬럼 제어 회로(505)는 입력되는 어드레스에 기초하여, 컬럼 선택 신호 CSL을 출력한다.

[0320] 리프레시 제어 회로(510)는 도시하지 않은 내부의 리프레시 타이머에 기초하여, DRAM 셀 어레이의 셀프 리프레시 동작을 제어한다.

[0321] WAIT 제어 회로(511)는 리프레시 제어 회로(510)의 제어에 의해 리프레시 제어가 행하여지고 있는 동안, WAIT 단자를 통하여 출력하는 WAIT 신호의 레벨을 「L」로 한다.

[0322] 커맨드 디코더(506)는 외부 제어 신호로부터 생성된 내부 제어 신호의 논리 레벨의 조합에 따라서, 로우 활성화 신호 ACT, 판독 신호 READ, 및 기입 신호 WRITE를 생성한다.

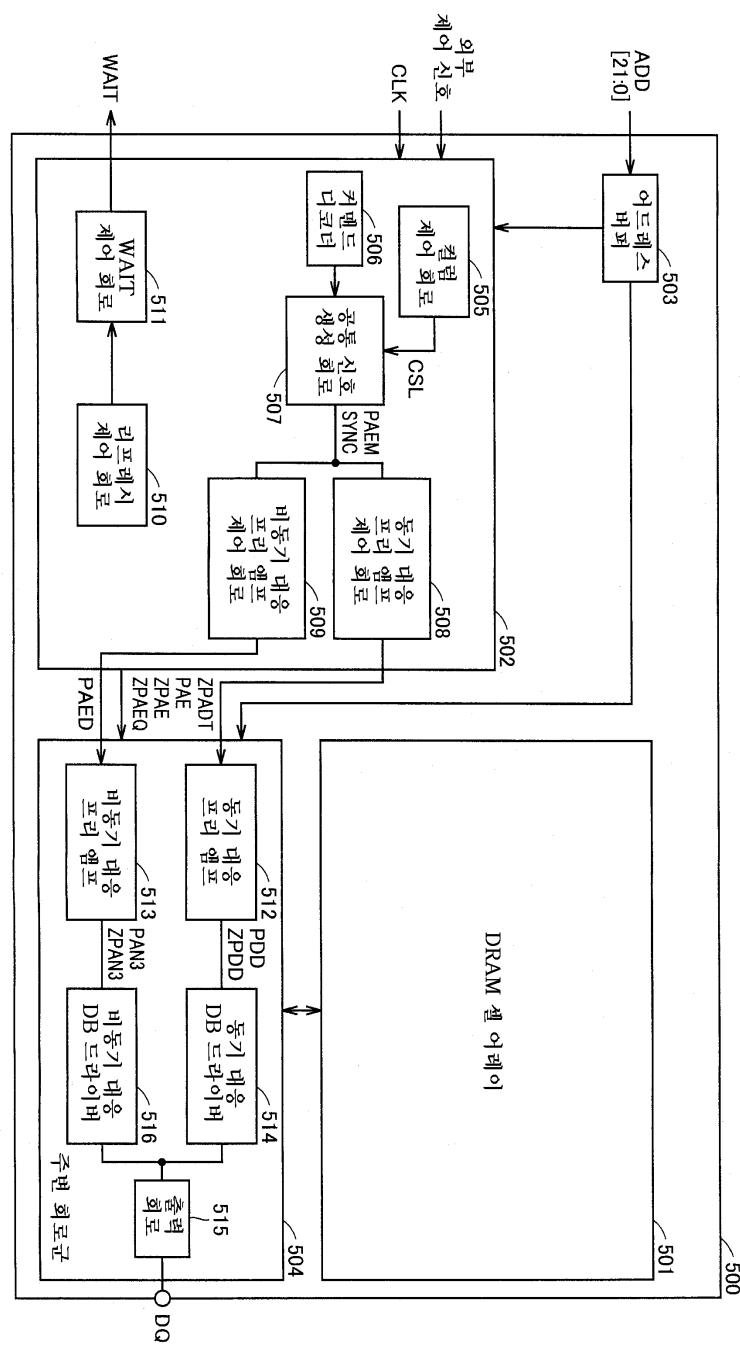

[0323] 도 26은 공통 신호 생성 회로(507)의 구성을 도시한다. 동도를 참조하여, 공통 신호 생성 회로(507)는, 프리 앰프 활성화 준비 신호 발생기(523)와, 동기 지시 신호 발생기(524)를 포함한다. 동도에 도시한 바와 같이, 프리 앰프 활성화 준비 신호 PAEM은, 컬럼 제어 회로(505)로부터 보내진 컬럼 선택 신호 CSL을 지연 회로(Delay) DL53에서  $\alpha$  시간만큼 지연시켜 생성된다. 프리 앰프 활성화 준비 신호 PAEM은, 동기 대응 프리 앰프 제어 회로(508)와 비동기 대응 프리 앰프 제어 회로(509)에 전송된다.

[0324] 동기 지시 신호 발생기(524)는, 외부 칩 인에이블 신호 CE#를 받는 인버터 IV54와, 인버터 IV54의 출력과 외부 클럭 CLK를 받는 반전 논리곱 회로 NAND53과, 외부 칩 인에이블 신호 CE#를 받는 인버터 IV53과, 인버터 IV53의 출력을  $\beta$  시간만큼 지연시키는 지연 회로(Delay) DL51과, 외부 칩 인에이블 신호 CE#와 지연 회로(Delay) DL51의 출력을 받는 반전 논리곱 회로 NAND54와, 반전 논리곱 회로 NAND53의 출력과 반전 논리곱 회로 NAND55의 출력을 받는 반전 논리곱 회로 NAND58과, 반전 논리곱 회로 NAND54의 출력과 반전 논리곱 회로 NAND58의 출력을 받는 반전 논리곱 회로 NAND55를 구비한다.

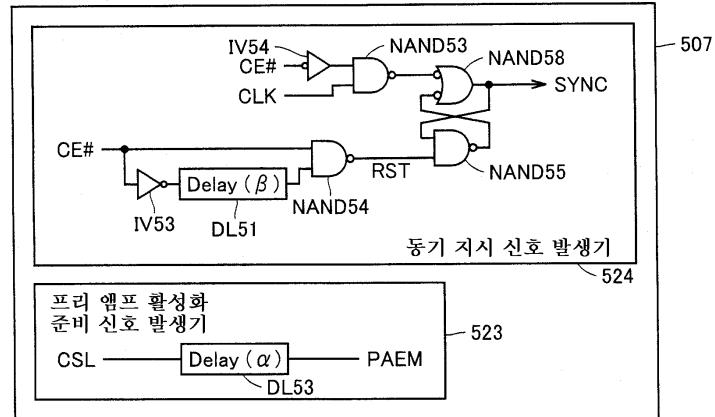

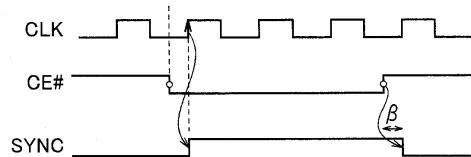

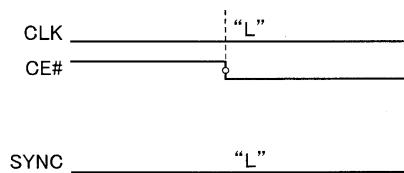

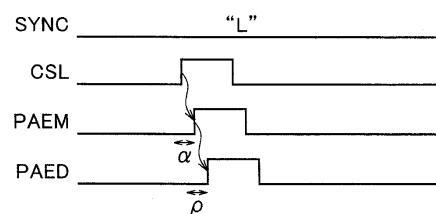

- [0325] 도 27a 및 도 27b는 동기 지시 신호 SYNC가 생성되는 타이밍차트를 도시한다.

- [0326] 도 27a를 참조하여, 외부 클럭 CLK가 입력되고 있을 때에는, 동기 지시 신호 SYNC는, 외부 칩 인에이블 신호 CE#가 「L」로 활성화된 후, 최초의 클럭 CLK의 상승에서 동기 모드를 나타내는 「H」로 되고, 그 후, 외부 칩 인에이블 신호 CE#가 「H」로 비활성화되어 지연 회로(Delay) DL51에 의한  $\beta$  시간만큼 지연후에 「L」로 된다.

- [0327] 도 27b를 참조하여, 외부 클럭 CLK가 입력되지 않을 때에, 동기 지시 신호 SYNC는 비동기 모드를 나타내는 「L」로 된다.

- [0328] 동기 지시 신호 SYNC는 동기 대응 프리 앰프 제어 회로(508)와 비동기 대응 프리 앰프 제어 회로(509)에 보내진다.

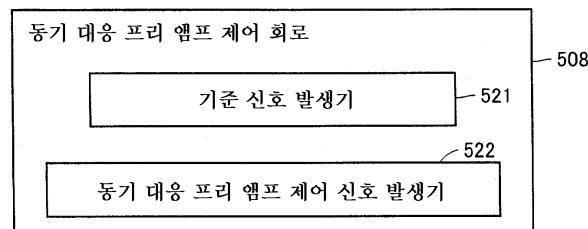

- [0329] 도 28은 동기 대응 프리 앰프 제어 회로(508)의 구성을 도시한다. 동도에 도시한 바와 같이, 동기 대응 프리 앰프 제어 회로(508)는, 기준 신호 발생기(521)와, 동기식 동작용 프리 앰프 제어 신호 발생기(522)를 포함한다.

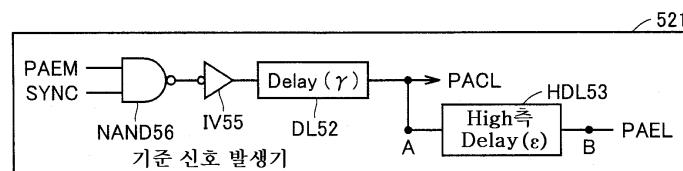

- [0330] 도 29는 기준 신호 발생기(521)의 구성을 도시한다. 동도에 도시한 바와 같이, 기준 신호 발생기(521)는, 프리 앰프 활성화 준비 신호 PAEM 및 동기 지시 신호 SYNC를 받는 반전 논리곱 회로 NAND56과, 반전 논리곱 회로 NAND56의 출력을 받는 인버터 IV55와, 인버터 IV55의 출력을  $\gamma$  시간만큼 지연시키는 지연 회로(Delay) DL52와, 지연 회로(Delay) DL52의 출력의 「H」 레벨 측을  $\varepsilon$  시간만큼 지연시키는 지연 회로(High 측 Delay) HDL53을 구비한다. 지연 회로(Delay) DL52의 출력이 제1 기준 신호 PACL이고, 지연 회로(High 측 Delay) HDL53의 출력이 제2 기준 신호 PAEL이다.

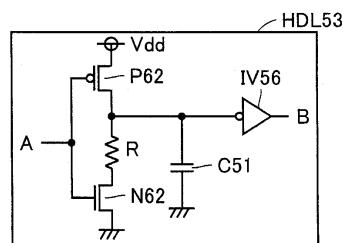

- [0331] 도 30은 High 측 Delay의 일례를 도시하는 도면이다. High 측 Delay는, P 채널 MOS 트랜지스터 P62와, N 채널 MOS 트랜지스터 N62와, 저항 R과, 컨덴서 C51과, 인버터 IV56을 구비한다. High 측 Delay의 노드 B가 「L」로부터 「H」로 변화하는 타이밍은, 노드 A가 「L」로부터 「H」로 변화하는 타이밍보다도 지연되지만, 노드 B가 「H」로부터 「L」로 변화하는 타이밍은, 노드 A가 「H」로부터 「L」로 변화하는 타이밍과 동일해진다.

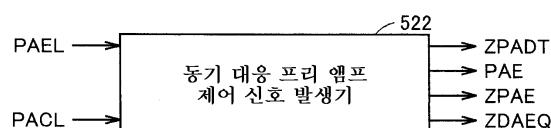

- [0332] 도 31은 동기 대응 프리 앰프 제어 신호 발생기(522)의 구성을 도시한다. 동도에 도시한 바와 같이, 동기 대응 프리 앰프 제어 신호 발생기(522)는, 제1 기준 신호 PAEL 및 제2 기준 신호 PACL을 받아, 반전 프리 앰프 접속 신호 ZPADT, 프리 앰프 활성화 신호 PAE, 반전 프리 앰프 활성화 신호 ZPAE, 반전 프리 앰프 이퀄라이즈 신호 ZPAEQ를 생성한다.

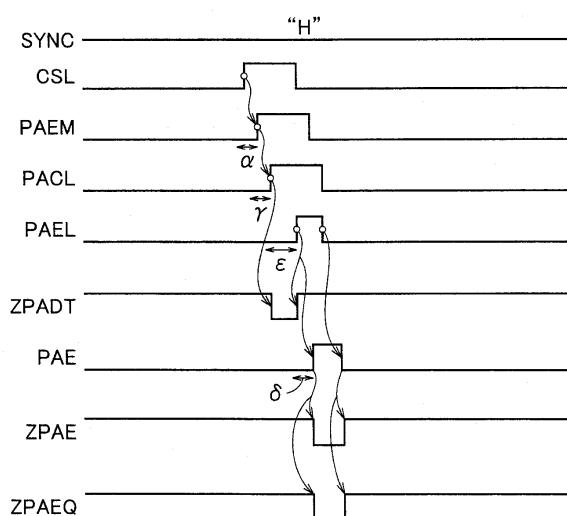

- [0333] 도 32는 동기 대응 프리 앰프(512)에 관련된 신호가 생성되는 타이밍을 도시한다. 동도를 참조하여, 동기 모드를 지시할 때에는, 도 27(a)에서 설명한 바와 같이, 동기 지시 신호 SYNC가 「H」로 된다. 컬럼 선택 신호 CSL은 적절한 타이밍에서 「H」로 활성화된다.

- [0334] 프리 앰프 활성화 준비 신호 PAEM은 컬럼 선택 신호 CSL을  $\alpha$  시간만큼 지연시켜 생성된다.

- [0335] 프리 앰프 활성화 준비 신호 PAEM 및 동기 지시 신호 SYNC가 기준 신호 발생기(521)의 반전 논리곱 회로 NAND56에 입력되고, 프리 앰프 활성화 준비 신호 PAEM에서  $\gamma$  시간만큼 지연된 제1 기준 신호 PACL이 생성된다.

- [0336] 또한, 이 제1 기준 신호 PACL의 펄스의 선두가  $\varepsilon$  시간만큼 지연된 제2 기준 신호 PAEL이 생성된다.

- [0337] 동기 대응 프리 앰프 제어 신호 발생기(522)는, 제1 기준 신호 PACL이 「H」, 또한 제2 기준 신호 PAEL이 「L」일 때에, 반전 프리 앰프 접속 신호 ZPADT를 「L」로 활성화한다. 또한, 동기 대응 프리 앰프 제어 신호 발생기(522)는, 제2 기준 신호 PAEL을 5 시간만큼 지연시켜, 프리 앰프 활성화 신호 PAE를 생성한다. 또한, 동기 대응 프리 앰프 제어 신호 발생기(522)는, 프리 앰프 활성화 신호 PAE를 반전시켜, 반전 프리 앰프 활성화 신호 ZPAE 및 반전 프리 앰프 이퀄라이즈 신호 ZPAEQ를 생성한다.

- [0338] 한편, 동기 지시 신호 SYNC가 비동기 모드를 나타내는 「L」일 때에는, 제1 기준 신호 PACL 및 제2 기준 신호 PAEL이 활성화되지 않으며, 그 결과, 반전 프리 앰프 접속 신호 ZPADT, 프리 앰프 활성화 신호 PAE, 반전 프리 앰프 활성화 신호 ZPAE, 및 반전 프리 앰프 이퀄라이즈 신호 ZPAEQ가 활성화되지 않는다.

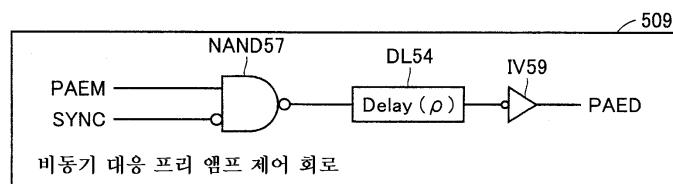

- [0339] 도 33은 비동기 대응 프리 앰프 제어 회로(509)의 구성을 도시한다. 동도에 도시한 바와 같이, 비동기 대응 프리 앰프 제어 회로(509)는, 프리 앰프 활성화 준비 신호 PAEM 및 동기 지시 신호 SYNC의 반전을 받는 반전

논리곱 회로 NAND57과, 반전 논리곱 회로 NAND57의 출력을  $\rho$  시간만큼 지연시키는 지연 회로(Delay) DL54와, 지연 회로(Delay) DL54의 출력을 받는 인버터 IV59를 구비한다. 인버터 IV59의 출력이 프리 앰프 활성화 신호 PAED이다.

- [0340] 도 34는 비동기 대응 프리 앰프(513)에 관련된 신호가 생성되는 타이밍을 도시한다. 동도를 참조하여, 비동기 모드를 지시할 때에는, 도 27(b)에서 설명한 바와 같이, 동기 지시 신호 SYNC가 「L」로 된다. 컬럼 선택 신호 CSL은 적절한 타이밍에서 「H」로 활성화된다.

- [0341] 프리 앰프 활성화 준비 신호 PAEM은 컬럼 선택 신호 CSL을  $\alpha$  시간만큼 지연시켜 생성된다.

- [0342] 프리 앰프 활성화 준비 신호 PAEM 및 동기 지시 신호 SYNC가 비동기 대응 프리 앰프 제어 회로(509)에 보내지고, 프리 앰프 활성화 준비 신호 PAEM이  $\rho$  시간만큼 지연된 프리 앰프 활성화 신호 PAED가 생성된다.

- [0343] 한편, 동기 지시 신호 SYNC가 동기 모드를 나타내는 「H」일 때에는, 프리 앰프 활성화 신호 PAED는 활성화되지 않는다.

- [0344] 재차, 도 25를 참조하여, 주변 회로군(504)은, 동기 대응 프리 앰프(512)와, 비동기 대응 프리 앰프(513)와, 동기 대응 DB 드라이버(514)와, 비동기 대응 DB 드라이버(516)와, 출력 회로(515)를 포함한다.

- [0345] (동기 대응 프리 앰프(512))

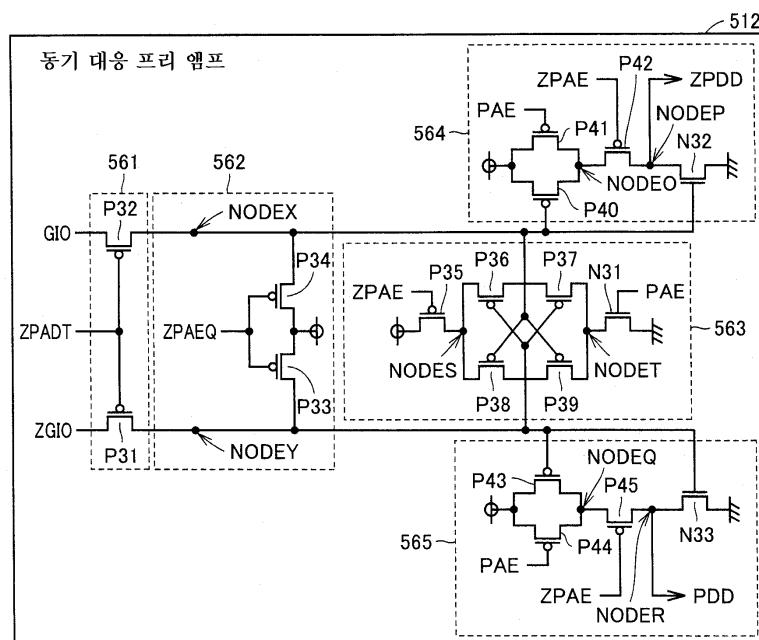

- [0346] 도 35는 동기 대응 프리 앰프(512)의 구성을 도시한다. 동도에 도시한 바와 같이, 이 동기 대응 프리 앰프(512)는, 반전 프리 앰프 접속 신호 ZPADT에서 제어되는 스위치부(561)와, 반전 프리 앰프 이퀄라이즈 신호 ZPAEQ에서 제어되는 이퀄라이즈부(562)와, 프리 앰프 활성화 신호 PAE 및 반전 프리 앰프 활성화 신호 ZPAE에서 제어되는 증폭부(563)와, 프리 앰프 활성화 신호 PAE 및 반전 프리 앰프 활성화 신호 ZPAE에서 제어되는 버퍼부(564, 565)를 구비한다.

- [0347] 스위치부(561)는 P 채널 MOS 트랜지스터 P32와 P 채널 MOS 트랜지스터 P31을 포함한다. P 채널 MOS 트랜지스터 P32는 글로벌 입출력선 GIO와 NODEX의 사이에 배치된다. P 채널 MOS 트랜지스터 P31은 반전 글로벌 입출력선 ZGIO와 NODEY의 사이에 배치된다. P 채널 MOS 트랜지스터 P32 및 P 채널 MOS 트랜지스터 P31의 게이트에는, 반전 프리 앰프 접속 신호 ZPADT가 인가된다.

- [0348] 이퀄라이즈부(562)는 P 채널 MOS 트랜지스터 P34와 P 채널 MOS 트랜지스터 P33을 포함한다. P 채널 MOS 트랜지스터 P34는 NODEX와 전원의 사이에 배치된다. P 채널 MOS 트랜지스터 P33은 NODEY와 전원의 사이에 배치된다. P 채널 MOS 트랜지스터 P34 및 P 채널 MOS 트랜지스터 P33의 게이트에는, 반전 프리 앰프 이퀄라이즈 신호 ZPAEQ가 인가된다.

- [0349] 증폭부(563)는 P 채널 MOS 트랜지스터 P35 내지 P39와, N 채널 MOS 트랜지스터 N31을 포함한다. NODES와 NODET 사이에는 직렬로 접속된 P 채널 MOS 트랜지스터 P36 및 P 채널 MOS 트랜지스터 P37이 놓이고, 이와 병렬로, 직렬로 접속된 P 채널 MOS 트랜지스터 P38 및 P 채널 MOS 트랜지스터 P39가 배치된다. P 채널 MOS 트랜지스터 P36 및 P37의 게이트는 NODEY와 접속된다. P 채널 MOS 트랜지스터 P38 및 P39의 게이트는 NODEX와 접속된다. P 채널 MOS 트랜지스터 P35는 전원과 NODES의 사이에 배치된다. N 채널 MOS 트랜지스터 N31은 NODET와 그랜드의 사이에 배치된다. P 채널 MOS 트랜지스터 P35의 게이트에는, 반전 프리 앰프 활성화 신호 ZPAE가 인가되고, N 채널 MOS 트랜지스터 N31의 게이트에는, 프리 앰프 활성화 신호 PAE가 인가된다.

- [0350] 버퍼(564)는 P 채널 MOS 트랜지스터 P40 내지 P42와, N 채널 MOS 트랜지스터 N32를 포함한다. P 채널 MOS 트랜지스터 P40 및 P 채널 MOS 트랜지스터 P41은, 전원과 NODEO의 사이에 배치된다. P 채널 MOS 트랜지스터 P40의 게이트는 NODEX와 접속된다. P 채널 MOS 트랜지스터 P41의 게이트는 프리 앰프 활성화 신호 PAE가 인가된다. P 채널 MOS 트랜지스터 P42는 NODEO와 NODEP의 사이에 배치된다. P 채널 MOS 트랜지스터 P42의 게이트에는, 반전 프리 앰프 활성화 신호 ZPAE가 인가된다. N 채널 MOS 트랜지스터 N32는 NODEP와 그랜드의 사이에 배치된다. N 채널 MOS 트랜지스터 N32의 게이트는 NODEX와 접속된다. NODEX로부터 반전 프리 앰프 출력 데이터 ZPDD가 출력된다.

- [0351] 버퍼(565)는 P 채널 MOS 트랜지스터 P43 내지 P45와, N 채널 MOS 트랜지스터 N33을 포함한다. P 채널 MOS 트랜지스터 P43 및 P 채널 MOS 트랜지스터 P44는, 전원과 NODEQ의 사이에 배치된다. P 채널 MOS 트랜지스터 P43의 게이트는 NODEY와 접속된다. P 채널 MOS 트랜지스터 P44의 게이트는 프리 앰프 활성화 신호 PAE가 인가된다. P 채널 MOS 트랜지스터 P45는 NODEQ과 NODER의 사이에 배치된다. P 채널 MOS 트랜지스터 P45의 게이트에는, 반전 프리 앰프 활성화 신호 ZPAE가 인가된다. N 채널 MOS 트랜지스터 N33은 NODER와 그랜드의 사이에 배치된다.

이에 배치된다. N 채널 MOS 트랜지스터 N33의 게이트는 NODEY와 접속된다. NODEY로부터 프리 앰프 출력 테이터 PDD가 출력된다.

[0352] 이 동기 대응 프리 앰프(512)는, 스위치부(561)를 갖기 때문에, 반전 프리 앰프 접속 신호 ZPADT에 의해 적당한 타이밍에서 글로벌 입출력 쌍 GIO, ZGIO를 증폭부(563)로부터 분리할 수 있다. 이에 의해, 증폭부(563)는 글로벌 입출력 쌍 GIO, ZGIO의 전위를 한번 취득하면, 그 후의 변화에 좌우되지 않고 증폭을 행한다고 하는, 소위 폐쇄식 증폭(confined amplification)이 가능해져, 증폭을 고속화할 수 있다. 또한, 글로벌 입출력 쌍 GIO, ZGIO가 증폭부(563)로부터 분리되기 때문에, 증폭부(563)에서의 증폭과 동시에, 이퀄라이즈부(562)에서 프리차지 처리를 행할 수 있어, 프리 앰프 전체의 처리도 고속화할 수 있다.

[0353] 또한, 특히 클럭에 동기한 판독 처리가 행해질 때에는, 일정한 타이밍에서 어드레스가 변화하고, 랜덤한 타이밍에서는 어드레스는 변화하지 않기 때문에, 어드레스가 변화하지 않는 타이밍에서 스위치부(561)에 의한 분리를 행하면, 글로벌 입출력선 쌍 GIO, ZGIO의 데이터를 놓치는 일이 없다.

[0354] 이상으로부터, 이 동기 대응 프리 앰프(512)는 클럭에 동기한 판독 동작에 적합하다고 할 수 있다.

[0355] 한편, 이 동기 대응 프리 앰프(512)는 이하에 도시한 바와 같이, 클럭에 동기하지 않는, 비동기의 판독 동작에는 적합하지 않다.

[0356] 도 36은 동기 대응 프리 앰프(512)가 비동기 판독에는 적합하지 않음을 설명하기 위한 도면이다. 동도에 도시한 바와 같이, 비동기 판독에서는 어드레스의 변화에 따라서, 판독 처리가 행해진다.

[0357] 동도의 (1)에 도시한 바와 같이, 컬럼 어드레스가 변화한 후, 더욱 단기간에 컬럼 어드레스가 변화했을 때에는, 각각의 변화에 대응하여, 반전 프리 앰프 이퀄라이즈 신호 ZPAQ가 활성화되지만, 동도의 (2)에 도시한 바와 같이, 이를 활성화되는 타이밍이 접근한다. 그 결과, 프리차지가 충분히 행해지지 않는다. 그리고, 프리차지가 행하여지지 않는 채로, 증폭이 행하여지기 때문에, 동도의 (3)에 도시한 바와 같이, 프리 앰프의 출력 데이터 PDD에 왜곡이 발생한다. 이러한 문제를 회피하기 위해서는, 프리차지 기간을 충분히 마련한 후, 다음 컬럼의 액세스를 행할 필요가 있으며, 동기 대응 프리 앰프(512)에 의한 처리가 늦어진다.

[0358] 또한, 동도의 (4)의 도시한 바와 같이, 노이즈 등의 영향으로 불필요한 어드레스 변화가 발생한 경우에, 글로벌 입출력선 쌍 GIO, ZGIO에는, 불필요한 컬럼 어드레스 변화의 컬럼 데이터가 출력된 후, 올바른 컬럼 어드레스 변화의 컬럼 데이터가 출력된다. 이 경우, 글로벌 입출력선 쌍 GIO, ZGIO와 증폭부(563)의 분리의 타이밍이 빠르면, 동도의 (5)에 도시한 바와 같이, 불필요한 데이터를 증폭하고, 올바른 데이터를 증폭하지 않는다. 이러한 문제를 회피하기 위해서는, 글로벌 입출력선 쌍 GIO, ZGIO와 증폭부(563)의 분리의 타이밍을 느리게 할 필요가 있으며, 동기 대응 프리 앰프(512)에 의한 처리가 늦어진다.

[0359] 이상과 같이, 이 동기 대응 프리 앰프(512)를 비동기의 판독에 이용한 경우, 처리가 늦어져, 적절하지 않다고 할 수 있다.

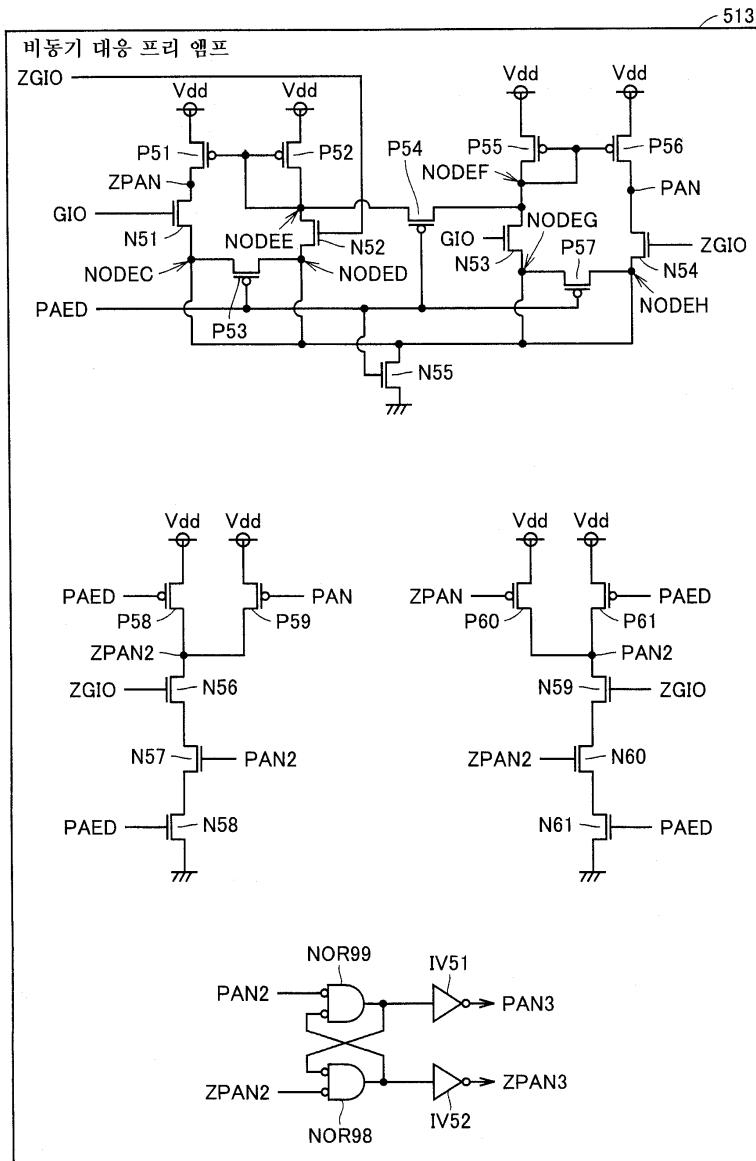

[0360] (비)동기 대응 프리 앰프(513))

[0361] 도 37은 비동기 대응 프리 앰프(513)의 구성을 도시한다. 동도에 도시한 바와 같이, 이 비동기 대응 프리 앰프(513)는 차동식의 전류 미러 타입의 증폭기이다.

[0362] 도 37을 참조하여, P 채널 MOS 트랜지스터 P51 및 P52는 전류 미러 회로를 구성한다. N 채널 MOS 트랜지스터 N51은 노드 ZPAN과 NODEC의 사이에 배치된다. N 채널 MOS 트랜지스터 N52는 NODEE와 NODED 사이에 배치된다. N 채널 MOS 트랜지스터 N51의 게이트는 글로벌 입출력선 GIO와 접속된다. N 채널 MOS 트랜지스터 N52의 게이트는 반전 글로벌 입출력선 ZGIO와 접속된다. P 채널 MOS 트랜지스터 P53은 NODEC과 NODED의 사이에 배치된다. P 채널 MOS 트랜지스터 P53의 게이트에는 프리 앰프 활성화 신호 PAED가 인가된다.

[0363] P 채널 MOS 트랜지스터 P55 및 P56은 전류 미러 회로를 구성한다. N 채널 MOS 트랜지스터 N54는 노드 PAN과 NODEH 사이에 배치된다. N 채널 MOS 트랜지스터 N53은 NODEF와 NODEG의 사이에 배치된다. N 채널 MOS 트랜지스터 N54의 게이트는 반전 글로벌 입출력선 ZGIO와 접속된다. N 채널 MOS 트랜지스터 N53의 게이트는 글로벌 입출력선 GIO와 접속된다. P 채널 MOS 트랜지스터 P57은 NODEG과 NODEH의 사이에 배치된다. P 채널 MOS 트랜지스터 P57의 게이트에는 프리 앰프 활성화 신호 PAED가 인가된다.

[0364] N 채널 MOS 트랜지스터 N55는 NODED와 그랜드의 사이에 배치된다. N 채널 MOS 트랜지스터 N55의 게이트에는 프리 앰프 활성화 신호 PAED가 인가된다. P 채널 MOS 트랜지스터 P54는 NODEE와 NODEF의 사이에 배치된다.

P 채널 MOS 트랜지스터 P54의 게이트에는 프리 앰프 활성화 신호 PAED가 인가된다.

[0365] 또한, 전원과 노드 ZPAN2의 사이에 P 채널 MOS 트랜지스터 P58과 P 채널 NOS 트랜지스터 P59가 병렬로 배치되는, P 채널 MOS 트랜지스터 P58의 게이트에는, 프리 앰프 활성화 신호 PAED가 입력되고, P 채널 MOS 트랜지스터 P59의 게이트는 노드 PAN과 접속된다.

[0366] 노드 ZPAN2와 그랜드의 사이에, N 채널 MOS 트랜지스터 N56, N 채널 MOS 트랜지스터 N57, 및 N 채널 MOS 트랜지스터 N58이 직렬로 접속된다. N 채널 MOS 트랜지스터 N56의 게이트는 반전 글로벌 입출력선 ZGIO와 접속된다. N 채널 MOS 트랜지스터 N57의 게이트는 노드 PAN2와 접속된다. N 채널 MOS 트랜지스터 N58의 게이트에는, 프리 앰프 활성화 신호 PAED가 입력된다.

[0367] 또한, 전원과 노드 PAN2 사이에 P 채널 MOS 트랜지스터 P60과 P 채널 NOS 트랜지스터 P61이 병렬로 배치되는, P 채널 MOS 트랜지스터 P61의 게이트에는, 프리 앰프 활성화 신호 PAED가 입력되고, P 채널 MOS 트랜지스터 P60의 게이트는, 노드 ZPAN과 접속된다.

[0368] 노드 PAN2와 그랜드의 사이에, N 채널 MOS 트랜지스터 N59, N 채널 MOS 트랜지스터 N60, 및 N 채널 MOS 트랜지스터 N61이 직렬로 접속된다. N 채널 MOS 트랜지스터 N59의 게이트는 반전 글로벌 입출력선 ZGIO와 접속된다. N 채널 MOS 트랜지스터 N60의 게이트는 노드 ZPAN2와 접속된다. N 채널 MOS 트랜지스터 N61의 게이트에는 프리 앰프 활성화 신호 PAED가 입력된다.

[0369] 또한, 노드 PAN2와 접속하는 반전 논리합 회로 NOR99와, 노드 ZPAN2와 접속하는 반전 논리합 회로 NOR98은, 플립플롭을 구성한다. 인버터 IV51은 반전 논리합 회로 NOR99의 출력을 반전하여 프리 앰프 출력 신호 PAN3을 출력한다. 인버터 IV52는 반전 논리합 회로 NOR98의 출력을 반전하여 반전 프리 앰프 출력 신호 ZPAN3을 출력한다.

[0370] 도 38은 비동기 대응 프리 앰프(513)의 각 노드의 전위의 시간 변화를 도시하는 도면이다.

[0371] 이 비동기 대응 프리 앰프(513)는 동기 대응 프리 앰프(512)와 같은 스위치부를 갖지 않는, 소위 비폐쇄식의 프리 앰프이다. 따라서, 비동기 대응 프리 앰프(513)는 증폭중에, 글로벌 입출력선 GIO, ZGIO와 분리되는 일이 없기 때문에, 어드레스 변화에 따라서 판독이 행해지는 비동기의 판독에 적합하다.

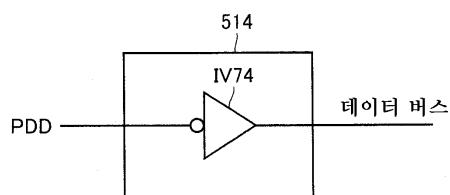

[0372] 재차, 도 25를 참조하여, 동기 대응 DB 드라이버(514)는 받은 전위를 데이터 버스 DB에 출력한다. 도 39는 동기 대응 DB 드라이버(514)의 구성을 도시한다. 동도에 도시한 바와 같이, 이 동기 대응 DB 드라이버(514)는 동기 대응 프리 앰프(512)의 출력 PDD를 받아, 그것을 반전하여 데이터 버스 DB에 출력하는 인버터 IV74로 구성된다.

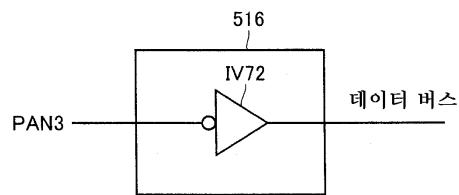

[0373] 비동기 대응 DB 드라이버(516)는 받은 전위를 데이터 버스 DB에 출력한다. 도 40은 비동기 대응 DB 드라이버(516)의 구성을 도시한다. 이 비동기 대응 DB 드라이버(516)는 비동기 대응 프리 앰프(513)의 출력 PAN3을 받아, 그것을 반전하여 데이터 버스 DB에 출력하는 인버터 IV72로 구성된다.

[0374] 도 25의 출력 회로(515)는 데이터 버스 DB의 데이터를 받아 데이터 출력 단자 DQ를 통하여 외부로 출력한다.

[0375] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, 동기 모드에서 적절하게 동작하는 프리 앰프와, 비동기 모드에서 적절하게 동작하는 프리 앰프를 갖기 때문에, 모든 모드에서 정상적으로 글로벌 입출력선 GIO, ZGIO의 전위차를 증폭할 수 있다.

[0376] 또한, 본 실시예에서는 동기 동작용의 프리 앰프와 비동기 대응의 프리 앰프로 나누었지만, 이것에 한정하는 것이 아니고, 버스트 모드용의 프리 앰프와 랜덤 액세스 모드용의 프리 앰프를 마련하여도 된다. 이 경우에는, 반도체 기억 장치는 동기 모드와 비동기 모드를 갖는 것이 아니라, 버스트 모드와 랜덤 액세스 모드를 갖게 된다. 버스트 모드용으로서는, 미리 읽기 동작 및 파이프라인 동작을 효율적으로 실행할 수 있도록, 프리 앰프(512)와 같은 폐쇄식의 증폭이 가능한 프리 앰프가 적합하다.

[0377] 본 실시예는 동기 지시 신호 SYNC에 의해서, 동기 모드와 비동기 모드가 전환되는 것으로 했지만, 이것에 한정하는 것이 아니고, 본딩 옵션 PAD를 갖고, 그것에 인가하는 전위에 의해서, 동기 모드와 비동기 모드를 전환하는 것으로 해도 된다.

[0378] 또한, 본 실시예에서는 동기 대응 DB 드라이버(514)와 비동기 대응 DB 드라이버(516)를 갖는 것으로 했지만, 동기와 비동기에서 대응한 DB 드라이버를 이용하는 것으로 해도 무방하다.

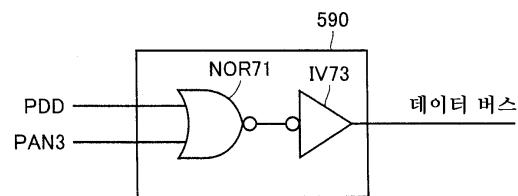

[0379] 도 41은 동기 대응 DB 드라이버(514)와 비동기 대응 DB 드라이버(516)를 겹치는 공용 DB 드라이버(590)의 구

성을 도시한다. 동도에 도시한 바와 같이, 이 공용 DB 드라이버(590)는, 동기 대응 프리 앰프(512)의 출력 PDD와 비동기 대응 프리 앰프(513)의 출력 PAN3을 받는 반전 논리합 회로 NOR71과, 반전 논리합 회로 NOR71의 출력을 반전하여 데이터 버스 DB에 출력하는 인버터 IV73으로 구성된다.

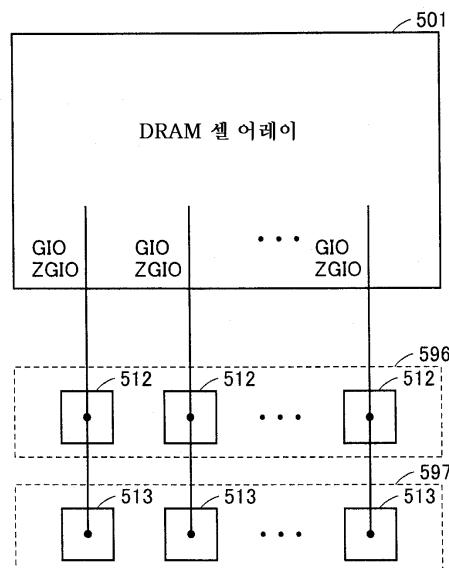

[0380] 도 42는 동기 대응 프리 앰프(512) 및 비동기 대응 프리 앰프(513)의 레이아웃을 도시하는 도면이다. 동도에 도시한 바와 같이, 동기 대응 프리 앰프 배치 영역(596)에는 동기 대응 프리 앰프(512)가 놓이고, 비동기 대응 프리 앰프 배치 영역(597)에는 비동기 대응 프리 앰프(513)가 배치되어 있다.

[0381] 각 글로벌 입출력선 쌍 GIO, ZGIO와 접속하는 동기 대응 프리 앰프(512)와 비동기 대응 프리 앰프(513)는, 컬럼 방향으로 나란히 배치된다. 글로벌 입출력선 쌍 GIO, ZGIO의 배치층과 프리 앰프의 배치층이 서로 다르고, 글로벌 입출력선 쌍 GIO, ZGIO는 분기를 갖지 않고서, 동기 대응 프리 앰프(512) 및 비동기 대응 프리 앰프(513)와 접속된다.

[0382] 이상과 같이, 도 42에 도시하는 레이아웃에서는, 글로벌 입출력선 쌍 GIO, ZGIO를 분기시킬 필요가 없으며, 글로벌 입출력선 쌍 GIO, ZGIO의 배선이 용이하다. 또한, 이 레이아웃은 컬럼 방향으로 동기식 의사 SRAM(500)의 사이즈를 크게 취할 수 있는 경우에 적합하다.

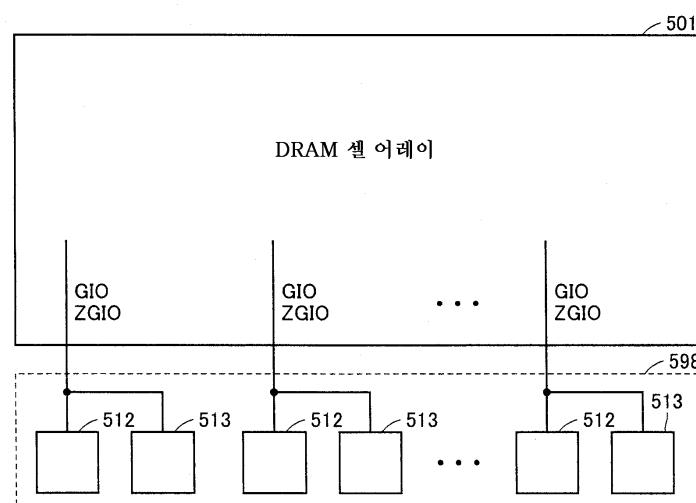

[0383] 도 43은 동기 대응 프리 앰프(512) 및 비동기 대응 프리 앰프(513)의 다른 레이아웃을 도시하는 도면이다. 동도에 도시한 바와 같이, 동기/비동기 대응 프리 앰프 배치 영역(598)에는 동기 대응 프리 앰프(512)와 비동기 대응 프리 앰프(513)가 배치되어 있다.

[0384] 각 글로벌 입출력선 쌍 GIO, ZGIO와 접속하는 동기 대응 프리 앰프(512)와 비동기 대응 프리 앰프(513)는, 로우 방향으로 나란히 배치된다. 글로벌 입출력선 쌍 GIO, ZGIO는 분기를 갖고, 분기한 한쪽이 동기 대응 프리 앰프(512)에 접속되고, 분기한 다른 쪽이 비동기 대응 프리 앰프(513)와 접속된다.

[0385] 이상과 같이, 도 43에 도시하는 레이아웃에서는, 글로벌 입출력선 쌍 GIO, ZGIO를 분기시킬 필요가 있다. 또한 이 레이아웃은 로우 방향으로 동기식 의사 SRAM(500)의 사이즈를 크게 취할 수 있는 경우에 적합하다.

#### [제6 실시예]

[0387] 본 실시예는 바이트 마스크 기능을 갖는 동기식 의사 SRAM에 관한 것이다. 동기식 의사 SRAM에는 상위 바이트 또는 하위 바이트의 마스크를 행함으로써, 메모리 셀로부터 판독한 데이터를 외부로 출력시키지 않도록 할 수 있다. 그런데, 버스트 모드에 있어서 노랩 모드(a no-wrap mode)라는 것이 있다. 노랩 모드에서는, 버스트 판독 또는 기입 도중에 최후의 컬럼에 달하면, 다음의 로우로 이행한다. 이 경우, 선택하고 있던 워드 선의 불활성화, 새롭게 선택하는 워드선의 활성화, 및 센스 앤프에 의한 증폭 처리 등의 로우 액세스 처리가 필요하다. 로우 액세스 처리가 행하여지고 있는 동안, 외부에 대하여 WAIT 신호가 출력된다. 외부의 시스템 측은 이 WAIT 신호가 해제되고 나서, 바이트 마스크 신호를 부여하면 되지만, 외부의 시스템에 있어서는, 이러한 다음 로우로 이행하기 위한 로우 액세스 처리의 유무에 상관없이, 동일한 방법으로 바이트 마스크의 설정을 할 수 있는 것이 바람직하다. 본 실시예는 버스트 판독 또는 버스트 기입이 제1 로우와 제2 로우의 2개의 로우에 걸쳐, 도중에서 제1 로우의 최후 컬럼에 달했기 때문에 제2 로우로 이행하는 경우에도, 외부로부터는 2개의 로우에 걸치지 않는 경우와 마찬가지로 하여 바이트 마스크 신호를 부여하는 것을 가능하게 하는 동기식 의사 SRAM을 제공한다.

#### (구성)

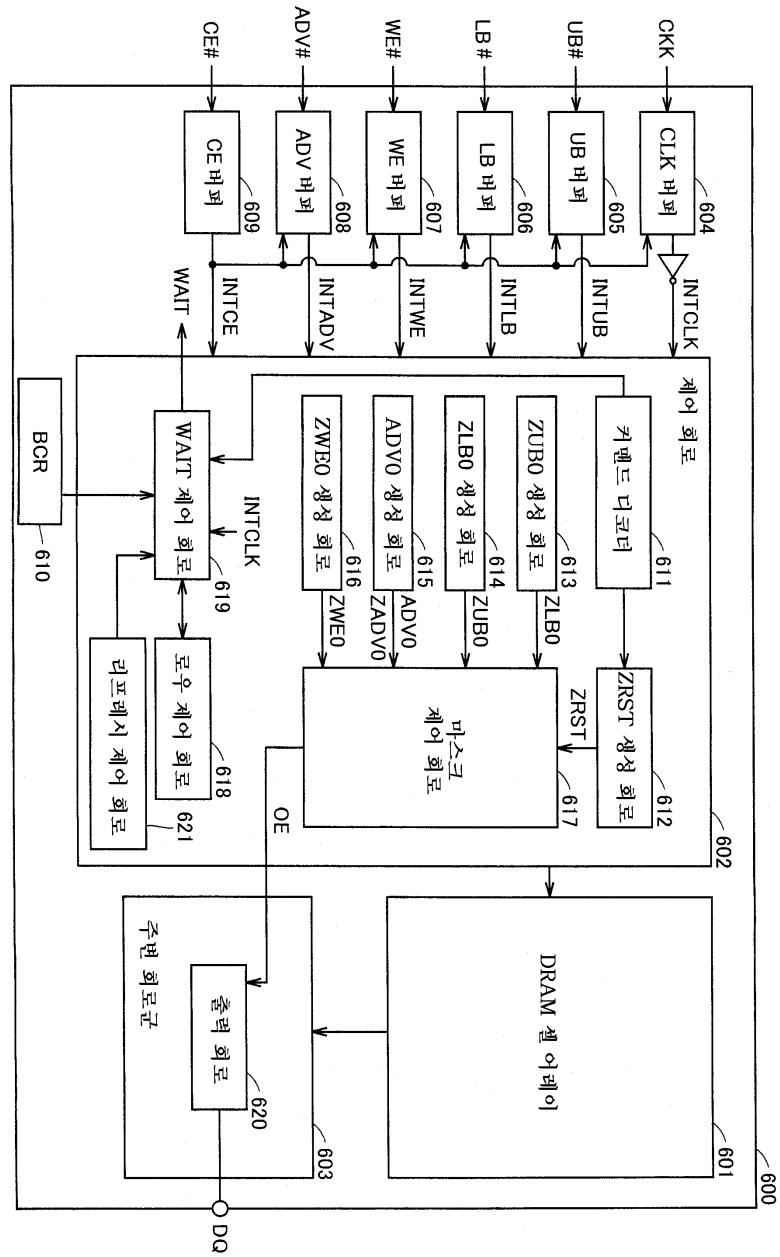

[0389] 도 44는 본 실시예에 따른 동기식 의사 SRAM(600)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(600)은, DRAM 셀 어레이(601)와, CLK 버퍼(604)와, UB 버퍼(605)와, LB 버퍼(606)와, WE 버퍼(607)와, ADV 버퍼(608)와, 제어 회로(602)와, 주변 회로군(603)과, BCR(Bus Configuration Register)(610)을 구비한다.

[0390] DRAM 셀 어레이(601)는 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다.

[0391] 주변 회로군(603)은, 도시하지 않은 글로벌 입출력선 쌍 GIOP(GIO 및 /GIO)와, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앤프와, 프리 앤프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다. 주변 회로군(603)은 또한 출력 회로(620)를 포함한다.

[0392] 출력 회로(620)는 DRAM 셀 어레이(601)로부터 출력된 데이터를 보유한다. 출력 회로(620)는 상위 바이트 및 하위 바이트마다 출력 인에이블 신호 OE를 받는다. 출력 회로(620)는, 상위 바이트의 출력 인에이블 신호 OE가 인에이블 「H」를 나타낼 때에, 보유하고 있는 데이터 상위 바이트를 데이터 입출력 단자 DQ를 통하여 외

부에 출력한다. 출력 회로(620)는, 하위 바이트의 출력 인에이블 신호 OE가 인에이블 「H」를 나타낼 때에, 보유하고 있는 데이터의 하위 바이트를 데이터 입출력 단자 DQ를 통하여 외부에 출력한다.

[0393] BCR(610)은 외부의 시스템과의 인터페이스, 예를 들면, 버스트 길이 BL, 및 커맨드 레이턴시 CL 등을 기억한다.

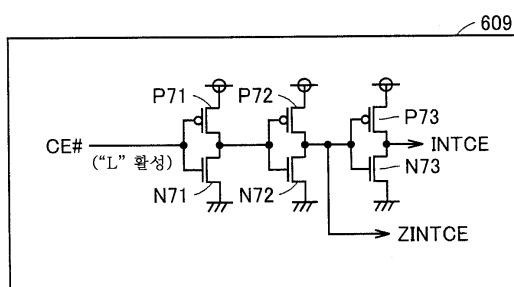

[0394] 도 45는 CE 버퍼(609)의 상세한 구성을 도시한다. 동도를 참조하여, CE 버퍼(608)는, 외부 칩 인에이블 신호 CE#가 입력되는, P 채널 MOS 트랜지스터 P71 및 N 채널 MOS 트랜지스터 N71로 구성되는 인버터 1파, 그 인버터 1에 접속되는, P 채널 MOS 트랜지스터 P72 및 N 채널 MOS 트랜지스터 N72로 구성되는 인버터 2와, 그 인버터 2에 접속되는, P 채널 MOS 트랜지스터 P73 및 N 채널 MOS 트랜지스터 N73으로 구성되는 인버터 3을 포함한다. 인버터 2의 출력이 반전 내부 칩 인에이블 신호 ZINTCE이고, 인버터 3의 출력이 내부 칩 인에이블 신호 INTCE이다.

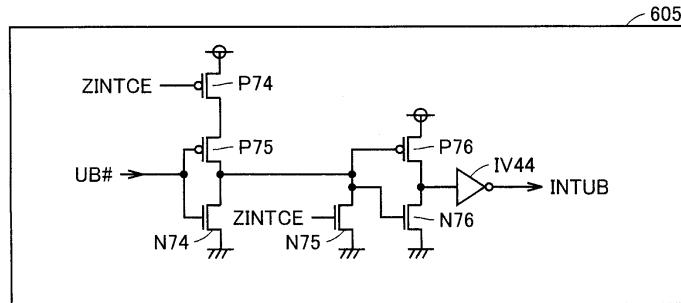

[0395] 도 46은 UB 버퍼(605)의 상세한 구성을 도시한다. 동도를 참조하여, UB 버퍼(605)는, 외부 상위 바이트 마스크 신호 UB#가 입력되는, P 채널 MOS 트랜지스터 P75 및 N 채널 MOS 트랜지스터 N74로 구성되는 인버터 1파, 그 인버터 1에 접속되는, P 채널 MOS 트랜지스터 P76 및 N 채널 MOS 트랜지스터 N76으로 구성되는 인버터 2와, 그 인버터 2에 접속되는, 인버터 IV44를 포함한다. 인버터 IV44의 출력이 내부 상위 바이트 마스크 신호 INTUB로 된다. 또한, 전원과 P 채널 MOS 트랜지스터 P75 사이에 P 채널 MOS 트랜지스터 P74를 배치한다. 인버터 1과 인버터 2의 접속 노드와 그랜드의 사이에, N 채널 MOS 트랜지스터 N75를 배치한다.

[0396] P 채널 M의 S 트랜지스터 P74의 게이트 및 N 채널 MOS 트랜지스터 N75의 게이트에는, 반전 내부 칩 인에이블 신호 ZINTCE가 입력된다. 칩이 활성화되어 있을 때, 반전 칩 인에이블 신호 ZINTCE가 「L」로 된다. 이 때에는 P 채널 MOS 트랜지스터 P75가 전원과 접속됨과 함께, 인버터 1과 인버터 2의 접속 노드가 접지되지 않는다. 따라서, 통상의 동작이 행하여진다.

[0397] 한편, 칩이 비활성화되어 있을 때, 반전 칩 인에이블 신호 ZINTCE가 「H」로 된다. 이 때에는, P 채널 MOS 트랜지스터 P75가 전원과 절단됨과 함께, 인버터 1과 인버터 2의 접속 노드가 접지된다. 따라서, 내부 상위 바이트 마스크 신호 INTUB는 항상 「L」 그대로로 된다.

[0398] 그 밖의 입력 버퍼 CLK 버퍼(604), LB 버퍼(606), WE 버퍼(607), ADV 버퍼(608)의 구성은, UB 버퍼(605)의 구성과 동일하기 때문에, 설명은 반복하지 않는다.

[0399] 재차, 도 44를 참조하여, 제어 회로(602)는, 커맨드 디코더(611)와, ZRST 생성 회로(612)와, ZUB0 생성 회로(613)와, ZLB0 생성 회로(614)와, ADVO 생성 회로(615)와, ZWE0 생성 회로(616)와, 마스크 제어 회로(617)와, 로우 제어 회로(618)와, WAIT 제어 회로(619)와, 리프레시 제어 회로(621)를 구비한다.

[0400] 커맨드 디코더(611)는 외부 제어 신호로부터 생성된 내부 제어 신호의 논리 레벨의 조합에 따라서, 로우 활성화 신호 ACT, 및 판독 신호 READ를 생성한다.

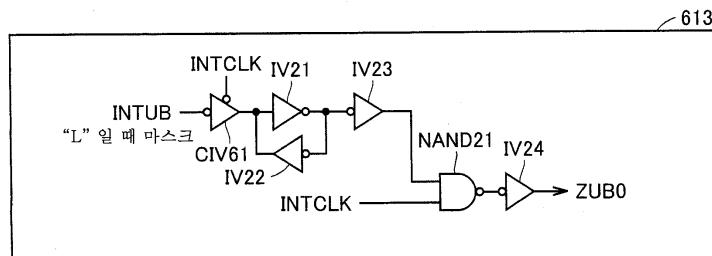

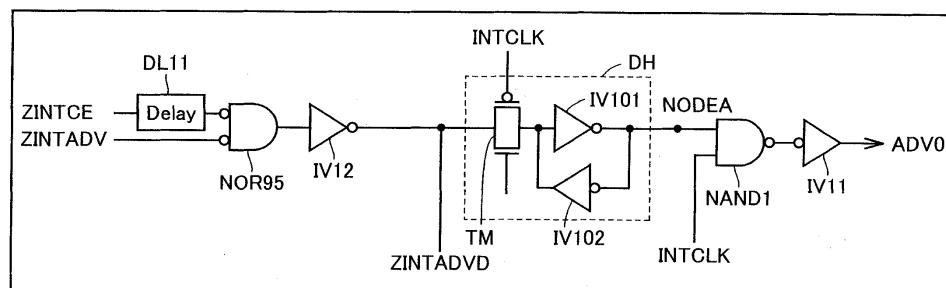

[0401] 도 47은 ZUB0 생성 회로(613)의 상세한 구성을 도시한다. 동도를 참조하여, 클럭드 인버터 CIV61에는, 내부 상위 바이트 마스크 신호 INTUB를 받는다. 클럭드 인버터 CIV61의 출력이 인버터 IV21과 인버터 IV22로 이루어지는 쌍 안정 회로에 보내진다. 쌍 안정 회로의 출력이 인버터 IV23에 보내진다. 인버터 IV23의 출력 및 내부 클럭 INTCLK가 반전 논리곱 회로 NAND21에 전송된다. 반전 논리곱 회로 NAND21의 출력이 인버터 IV24에 보내지고, 인버터 IV24의 출력이 ZUB0으로 된다.

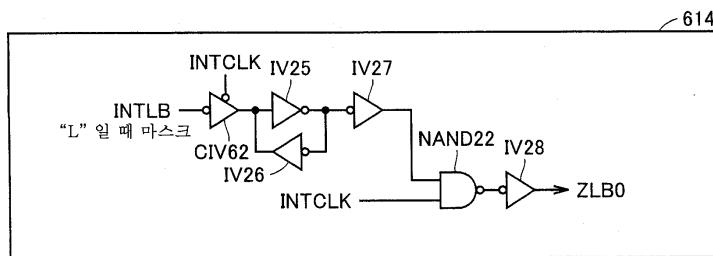

[0402] 도 48은 ZLB0 생성 회로(614)의 상세한 구성을 도시한다. 동도를 참조하여, 클럭드 인버터 CIV62에는 내부 하위 바이트 마스크 신호 INTLB를 받는다. 클럭드 인버터 CIV62의 출력이 인버터 IV25와 인버터 IV26으로 이루어지는 쌍 안정 회로에 보내진다. 쌍 안정 회로의 출력이 인버터 IV27에 보내진다. 인버터 IV27의 출력 및 내부 클럭 INTCLK가 반전 논리곱 회로 NAND22에 전송된다. 반전 논리곱 회로 NAND22의 출력이 인버터 IV28에 보내지고, 인버터 IV28의 출력이 ZLB0으로 된다.

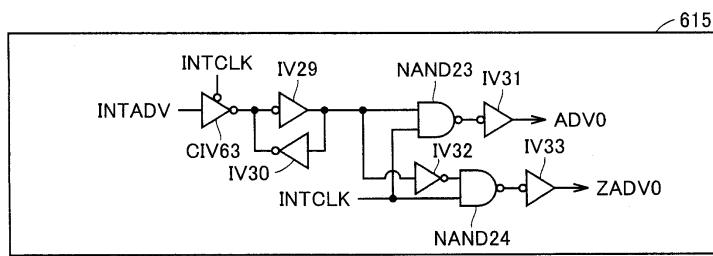

[0403] 도 49는 ADVO 생성 회로(615)의 상세한 구성을 도시한다. 동도를 참조하여, 클럭드 인버터 CIV63에는, 내부 어드레스 취득 신호 INTADV를 받는다. 클럭드 인버터 CIV63의 출력이 인버터 IV29와 인버터 IV30으로 이루어지는 쌍 안정 회로에 보내진다. 쌍 안정 회로의 출력 및 내부 클럭 INTCLK가 반전 논리곱 회로 NAND23에 보내진다. 반전 논리곱 회로 NAND23의 출력이 인버터 IV31에 보내지고, 인버터 IV31의 출력이 ADVO으로 된다. 한편, 쌍 안정 회로의 출력이 인버터 IV32에 보내진다. 인버터 IV32의 출력 및 내부 클럭 INTCLK가 반전 논리곱 회로 NAND24에 보내진다. 반전 논리곱 회로 NAND24의 출력이 인버터 IV33에 보내지고, 인버터 IV33의

출력이 ZADVO으로 된다.

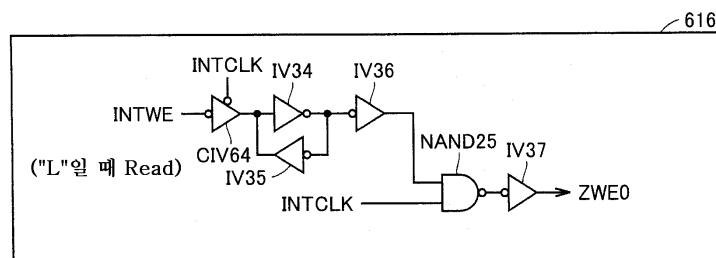

[0404] 도 50은 ZWE0 생성 회로(616)의 상세한 구성을 도시한다. 동도를 참조하여, 클럭드 인버터 CIV64에는 내부 라이트 인에이블 신호 INTWE를 받는다. 클럭드 인버터 CIV64의 출력이 인버터 IV34와 인버터 IV35로 이루어지는 쌍 안정 회로에 보내진다. 쌍 안정 회로의 출력이 인버터 IV36에 보내진다. 인버터 IV36의 출력 및 내부 클럭 INTCLK가 반전 논리곱 회로 NAND25에 보내진다. 반전 논리곱 회로 NAND25의 출력이 인버터 IV37에 보내지고, 인버터 IV37의 출력이 ZWE0으로 된다.

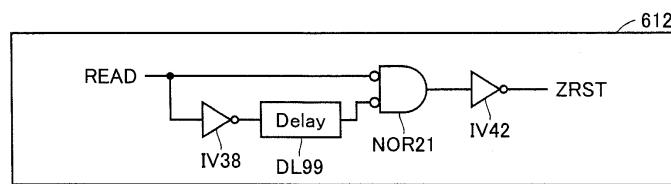

[0405] 도 51은 ZRST 생성 회로(612)의 상세한 구성을 도시한다. 동도를 참조하여, 인버터 IV38은 판독 신호 READ를 받는다. 지연 회로(Delay) DL99는 인버터 IV99의 출력을 지연시킨다. 반전 논리합 회로 NOR21은 판독 신호 READ와 지연 회로(Delay) DL99의 출력을 받는다. 인버터 IV42는 반전 논리합 회로 NOR21의 출력을 받는다. 인버터 IV42의 출력이 반전 리셋 신호 ZRST로 된다.

[0406] 도 52는 반전 리셋 신호 ZRST가 생성되는 타이밍을 도시하는 도면이다. 동도에 도시한 바와 같이, 반전 리셋 신호 ZRST는, 판독 신호 READ가 「L」로 비활성화될 때에, 활성화되어 「L」 레벨의 펄스로 된다.

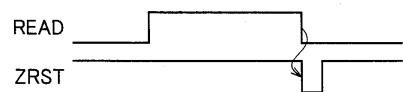

[0407] 도 53은 마스크 제어 회로(617)의 상세한 구성을 도시한다. 동도는 하위 층(LB)만을 도시하고 있지만, 상위 층(UB)도 이와 마찬가지이다. 도 53을 참조하여, 제1 제어 회로(631)에 있어서, 반전 논리곱 회로 NAND26은 ADV0, ZLB0 및 ZWE0을 받는다. 반전 논리곱 회로 NAND29 및 반전 논리곱 회로 NAND30은 플립플롭을 구성한다. 반전 논리곱 회로 NAND29는 반전 논리곱 회로 NAND26의 출력을 받는다. 반전 논리곱 회로 NAND30은 반전 리셋 신호 ZRST를 받는다. 인버터 IV39는 반전 논리곱 회로 NAND29의 출력을 받는다. 인버터 IV39의 출력은 제1 출력 인에이블 신호 OE1로 된다. 이러한 구성에 의해, 제1 제어 회로(631)는, 외부 바이트 마스크 신호 LB#가 버스트 액세스의 선두 비트의 바이트 마스크를 행하는 것을 나타낼 때에는, 외부 바이트 마스크 신호 LB#가 「H」로 된 클럭 CLK로부터, 출력 회로(620)로부터 선두의 비트가 출력되는 타이밍을 포함하는 시점까지, 제1 출력 인에이블 신호 OE1을 「L」로 한다.

[0408] 제2 제어 회로(632)에 있어서, 반전 논리곱 회로 NAND27은 ZADVO, ZLB0 및 ZWE0을 받는다. 반전 논리곱 회로 NAND31 및 반전 논리곱 회로 NAND32는 플립플롭을 구성한다. 반전 논리곱 회로 NAND31은 반전 논리곱 회로 NAND27의 출력을 받는다. 반전 논리곱 회로 NAND31은 반전 리셋 신호 ZRST를 받는다. 반전 논리곱 회로 NAND35는 ZWAIT 신호 및 반전 논리곱 회로 NAND31의 출력을 받는다. 반전 논리곱 회로 NAND35의 출력은 제2 출력 인에이블 신호 OE2로 된다. 이러한 구성에 의해, 제2 제어 회로(632)는, 외부 바이트 마스크 신호 LB#가, 선두의 비트 이외의 비트의 바이트 마스크를 행하는 것을 나타낼 때에, 다음 로우로의 이행을 위한 로우 액세스 처리가 행하여지지 않는다. 이 경우, 그 비트가 출력 회로(620)로부터 출력될 때에 WAIT 신호가 「H」이면, 통상대로 제2 출력 인에이블 신호 OE2를 「L」로 하고, 이 때 WAIT 신호가 「L」이면, 제2 출력 인에이블 신호 OE2를 「L」로 하지 않고, 바이트 마스크 신호에 기초하여 생성된 신호(즉, 반전 논리곱 회로 NAND27의 출력)를 제3 제어 회로(633)에 출력한다.

[0409] 제3 제어 회로(633)에 있어서, 인버터 IV41은 ZWAIT 신호를 받는다. 지연 회로(Delay) DL21은 인버터 IV41의 출력을 지연시킨다. 반전 논리곱 회로 NAND28은 ZWAIT 신호와 지연 회로(Delay) DL21의 출력을 받는다. 반전 논리곱 회로 NAND33 및 반전 논리곱 회로 NAND34는, 플립플롭을 구성한다. 반전 논리곱 회로 NAND33은 반전 논리곱 회로 NAND27의 출력을 받는다. 반전 논리곱 회로 NAND34, 반전 리셋 신호 ZRST 및 반전 논리곱 회로 NAND28의 출력을 받는다. 인버터 IV40은 ZWAIT 신호를 받는다. 반전 논리곱 회로 NAND36은, 인버터 IV40의 출력과, 반전 논리곱 회로 NAND33의 출력을 받는다. 반전 논리곱 회로 NAND36의 출력은 제3 출력 인에이블 신호 OE3으로 된다. 이러한 구성에 의해, 제3 제어 회로(633)는 바이트 마스크 신호에 기초하여 생성된 신호를 받아 보유하고, WAIT 신호가 「L」로부터 「H」로 되었을 때에, 제3 출력 인에이블 신호 OE3을 「L」로 한다.

[0410] 반전 논리곱 회로 NAND60은 제1 출력 인에이블 신호 OE1, 제2 출력 인에이블 신호 OE2, 및 제3 출력 인에이블 신호 OE3을 받는다. 인버터 IV43은 반전 논리곱 회로 NAND60의 출력을 받아, 출력 인에이블 신호 OE를 출력한다. 반전 논리곱 회로 NAND60 및 인버터 IV43에 의해서, 제1 출력 인에이블 신호 OE1, 제2 출력 인에이블 신호 OE2, 및 제3 출력 인에이블 신호 OE3 중의 적어도 1개가 「L」일 때에, 출력 인에이블 신호 OE는 「L」로 된다.

[0411] 제44를 참조하여, 로우 제어 회로(618)는 로우 액세스 처리(워드선의 활성화, 센스 앰프에 의한 증폭 등)를 제어한다.

- [0412] 리프레시 제어 회로(621)는 도시하지 않은 내부의 리프레시 타이머에 기초하여, DRAM 셀 어레이의 셀프 리프레시 동작을 제어한다.

- [0413] WAIT 제어 회로(619)는, 리프레시 제어 회로(621)의 제어에 의해 리프레시 제어가 행하여지고 있는 동안, 및 노랩 모드로 버스트 판독의 도중에 최후의 컬럼에 달했기 때문에, 다음 로우로의 이행을 위한 로우 액세스 처리(원래의 로우의 워드선의 비활성화, 새로운 로우의 워드선의 활성화, 및 센스 앤프에 의한 증폭 등)를 행하고 있는 동안에, WAIT 단자를 통하여 출력하는 WAIT 신호의 레벨을 「L」로 한다. 즉, WAIT 신호가 「L」에 의해서, 데이터가 출력될 때까지 대기하는 것을 외부에 알린다.

- [0414] (다음 로우로의 이행을 수반하지 않을 때의 액세스 동작)

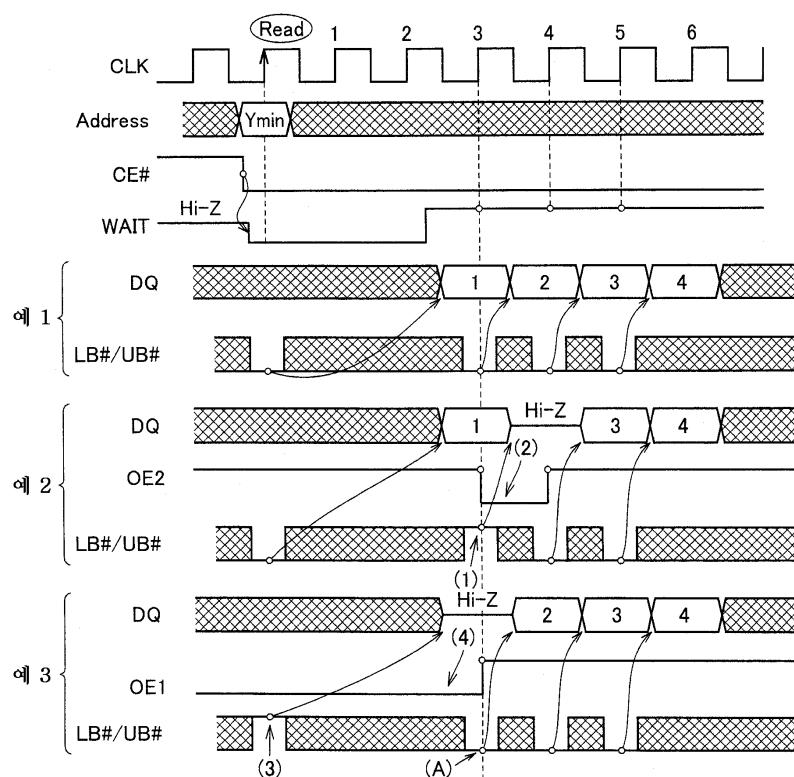

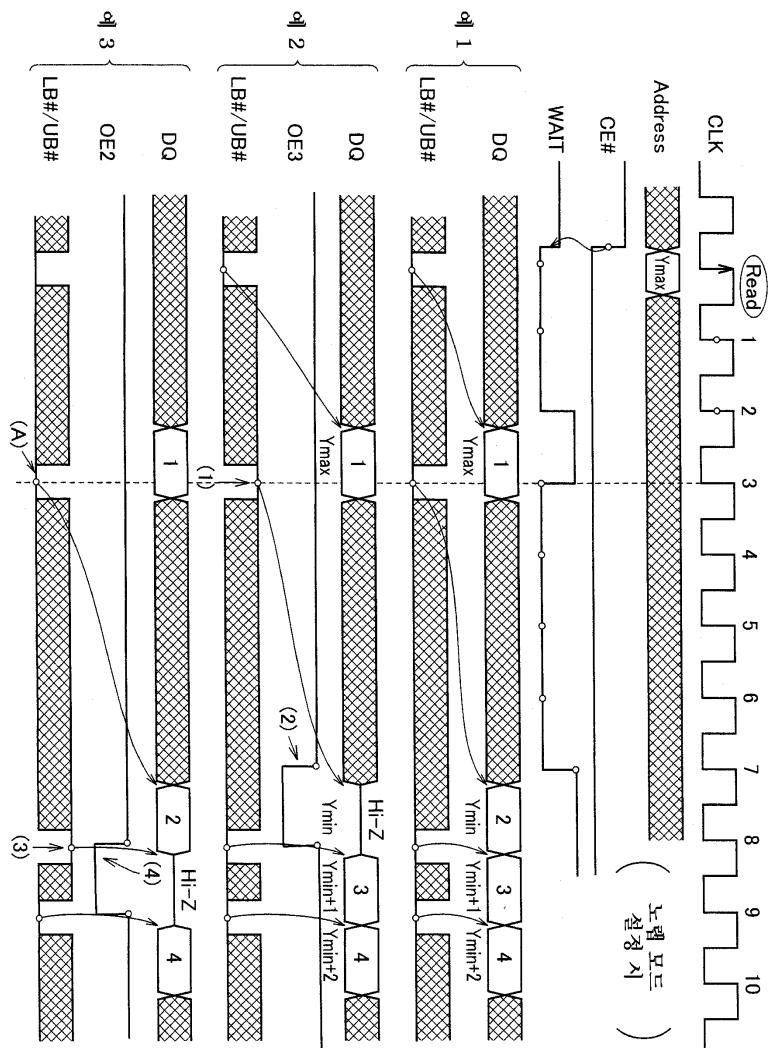

- [0415] 도 54는 본 실시예의 동기식 의사 SRAM(600)에 있어서의 버스트 판독 시에 다음 로우로의 이행을 수반하지 않을 때의 신호의 변화를 나타내는 타이밍차트이다. 동도를 참조하여, 예 1 내지 예 3의 동작을 설명한다.

- [0416] (예 1) 마스크가 없을 때

- [0417] 외부 바이트 마스크 신호 LB#, UB#는, 「H」로 되는 일이 없다. 이 경우에는, 제1 출력 인에이블 신호 OE1, 제2 출력 인에이블 신호 OE2, 및 제3 출력 인에이블 신호 OE3은 전 기간 「H」로 된다.

- [0418] (예 2) 제2 비트를 마스크할 때

- [0419] 외부 바이트 마스크 신호 LB#, UB#는, 동도의 (1)에 있어서 「H」로 된다. 이 경우에는, 제1 출력 인에이블 신호 OE1 및 제3 출력 인에이블 신호 OE3은, 전 기간 「H」로 된다. 한편, 제2 출력 인에이블 신호 OE2는, 동도의 (2)에 도시한 바와 같이, 제2 비트가 출력 회로(620)로부터 출력되는 타이밍(클럭 CLK3의 상승으로부터 클럭 CLK4의 상승까지)에 있어서 「L」로 된다.

- [0420] (예 3)

- [0421] 제1 비트를 마스크할 때 외부 바이트 마스크 신호 LB#, UB#는, 동도의 (3)에 있어서 「H」로 된다. 이 경우에는, 제2 출력 인에이블 신호 OE2 및 제3 출력 인에이블 신호 OE3은, 전 기간 「H」로 된다. 제1 출력 인에이블 신호 OE1은 동도의 (4)에 도시한 바와 같이, 외부 바이트 마스크 신호 LB#, UB#가 「H」로 된 클럭 CLK로부터, 제1 비트가 출력 회로(620)로부터 출력되는 타이밍을 포함하는 시점까지(클럭 CLK0의 상승으로부터 클럭 CLK3의 상승까지), 「L」로 된다.

- [0422] (노랩 모드에 있어서, 다음 로우로의 이행을 수반할 때의 액세스 동작)

- [0423] 도 55는 본 실시예의 동기식 의사 SRAM(600)에 있어서의 노랩 모드 설정 시에, 버스트 판독 시에 다음 로우로의 이행을 수반할 때의 변화를 나타내는 타이밍차트이다. 동도를 참조하여, 예 1 내지 예 3의 동작을 설명한다.

- [0424] (예 1) 마스크가 없을 때

- [0425] 외부 바이트 마스크 신호 LB#, UB#는 「H」로 되는 일이 없다. 제1 출력 인에이블 신호 OE1, 제2 출력 인에이블 신호 OE2, 및 제3 출력 인에이블 신호 OE3은, 전 기간 「H」로 된다.

- [0426] (예 2)

- [0427] 제2 비트를 마스크할 때(다음 로우로의 이행 처리를 수반함)

- [0428] 외부 바이트 마스크 신호 LB#, UB#는, 동도의 (1)에 있어서 「H」로 된다. 이 경우에는, 제1 출력 인에이블 신호 OE1 및 제2 출력 인에이블 신호 OE2는, 전 기간 「H」로 된다. 제3 출력 인에이블 신호 OE3은 동도의 (3)에 도시한 바와 같이, WAIT 신호가 「H」로 되었을 때의 타이밍(클럭 CLK7의 상승으로부터 클럭 CLK8의 상승까지)에 있어서 「L」로 된다.

- [0429] 이에 의해, 제2 비트의 마스크 처리는 다음 로우의 로우 액세스 처리가 종료되어 WAIT 신호가 「H」로 되는 시점까지 연장된다.

- [0430] (예 3)

- [0431] 제3 비트를 마스크할 때 외부 바이트 마스크 신호 LB#, UB#는, 동도의 (3)에 있어서 「H」로 된다. 이 경우, 제1 출력 인에이블 신호 OE1 및 제3 출력 인에이블 신호 OE3은, 전 기간 「H」로 된다. 제2 출력 인에이블 신호 OE2는 동도의 (4)에 도시한 바와 같이, 제3 비트가 출력 회로(620)로부터 출력되는 타이밍(클럭 CLK8의

상승으로부터 클럭 CLK9의 상승까지)에 있어서 「L」로 된다.

[0432] (예 4)

[0433] 제1 비트를 마스크할 때

[0434] 도시하지 않지만, 도 54의 (예 3)일 때 동일하다.

[0435] 이상의 설명으로부터 분명한 바와 같이, 제2 비트의 바이트 마스크 신호의 설정 타이밍, 즉, 외부 바이트 마스크 신호 LB#, UB#를 부여하는 타이밍은, 도 54 및 도 55의 어느 하나의 (A)로 표시되는 타이밍이다. 따라서, 베스트 판독 또는 베스트 기입의 도중에, 다음 로우로 이행하는 경우에도, 외부로부터는, 다음 로우로 이행하지 않는 경우와 마찬가지로 해서 바이트 마스크 신호를 부여할 수 있다.

[0436] 또한, 본 실시예는 노랩 모드에만 적용할 수 있는 것이 아니라, 칩 인에이블 신호가 비활성으로 될 때까지 연속하여 판독/기입을 행하는 콘티뉴어스 모드에 있어서도 유효하다.

[0437] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니라, 클럭에 동기하여 동작하는 반도체 기억 장치이면 어떠한 것에도 적용할 수 있다.

[0438] [제7 실시예]

[0439] 본 실시예는 모바일 RAM과 셀룰러 RAM의 양방의 기능을 구비한 모바일/셀룰러 겸용 RAM에 관한 것이다. 여기서, 셀룰러 RAM이란, Cellular RAM<sup>TM</sup> Memory에 기재되어 있는 동기형의 의사 SRAM이다. 모바일 RAM은 휴대 전화용의 특유의 기능을 구비한 의사 SRAM이다.

[0440] (구성)

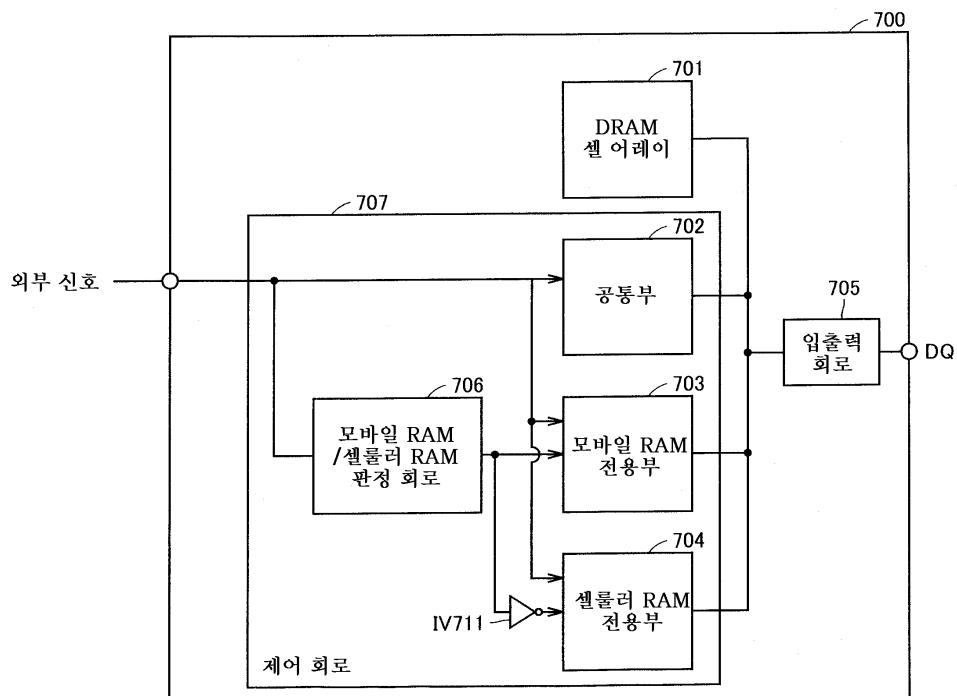

[0441] 도 56은 본 실시예의 모바일/셀룰러 겸용 RAM(700)의 구성을 도시한다. 동도를 참조하여, 이 모바일/셀룰러 겸용 RAM(700)은, DRAM 셀 어레이(701)와, 제어 회로(707)와, 입출력 회로(705)를 구비한다.

[0442] DRAM 셀 어레이(701)는 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다.

[0443] 입출력 회로(705)는 데이터 출력 단자 DQ를 통하여 외부로부터 데이터를 받음과 함께, 외부에 데이터를 출력한다.

[0444] 제어 회로(707)는, 공통부(702)와, 모바일 RAM 전용부(703)와, 셀룰러 RAM 전용부(704)와, 모바일 RAM/셀룰러 RAM 판정 회로(706)를 포함한다.

[0445] 모바일 RAM/셀룰러 RAM 판정 회로(706)는 외부 신호에 응답하여, 공통부(702), 모바일 RAM 전용부(703), 및 셀룰러 RAM 전용부(704)의 어느 것을 동작시킬지를 판정하여, 동작시킨다.

[0446] 공통부(702)는 모바일 RAM과 셀룰러 RAM에 공통의 기능을 실행한다.

[0447] 모바일 RAM 전용부(703)는 모바일 RAM만이 갖는 기능을 실행한다.

[0448] 셀룰러 RAM 전용부(704)는 셀룰러 RAM만이 갖는 기능을 실행한다.

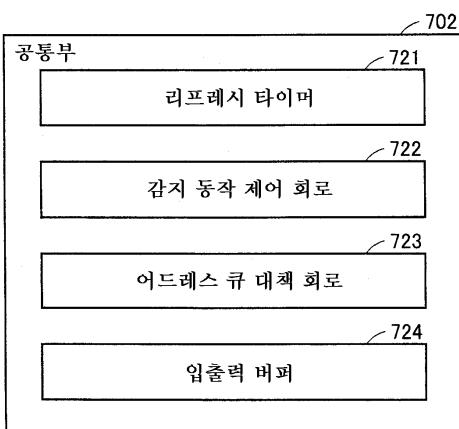

[0449] 도 57은 공통부(702)의 구성을 도시한다. 동도에 도시한 바와 같이, 공통부(702)는, 리프레시 타이머(721)와, 감지 동작 제어 회로(722)와, 어드레스 큐 대책 회로(723)와, 입출력 버퍼(724)를 구비한다.

[0450] 리프레시 타이머(721)는 셀프 리프레시를 행하는 타이밍 신호를 출력한다.

[0451] 감지 동작 제어 회로(722)는 센스 앰프의 동작을 제어한다.

[0452] 어드레스 큐 대책 회로(723)는 어드레스 큐가 발생하지 않도록 제어하는 회로이다.

[0453] 입출력 버퍼(724)는 외부 제어 신호, 외부 어드레스 신호, 외부 클럭 등을 받아 보유하고, 내부 제어 신호, 내부 어드레스 신호, 내부 클럭 등을 생성함과 함께, 외부로 출력하는 데이터를 보유한다.

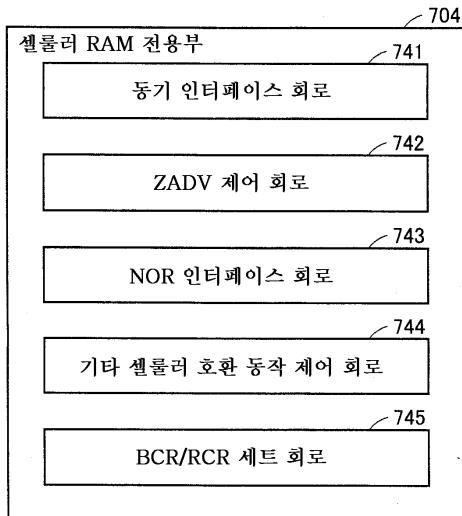

[0454] 도 58은 셀룰러 RAM 전용부(704)의 구성을 도시한다. 동도에 도시한 바와 같이, 셀룰러 RAM 전용부(704)는, 동기 인터페이스 회로(741)와, ZADV 제어 회로(742)와, NOR 인터페이스 회로(743)와, 기타 셀룰러 호환 동작 제어 회로(744)와, BCR/RCR 세트 회로(745)를 구비한다.

[0455] 동기 인터페이스 회로(741)는 클럭에 동기한 동작을 제어한다.

- [0456] ZADV 제어 회로(742)는 외부 어드레스 취득 신호 ADV#에 기초하여, 외부 어드레스의 취득을 제어한다.

- [0457] NOR 인터페이스 회로(743)는 NOR형 플래시 메모리와의 인터페이스를 제어한다.

- [0458] 기타 셀룰러 호환 동작 제어 회로(744)는, 예를 들면 SRAM 호환의 인터페이스를 제어한다.

- [0459] BCR/RCR 세트 회로(745)는 BCR 및 RCR을 세트한다.

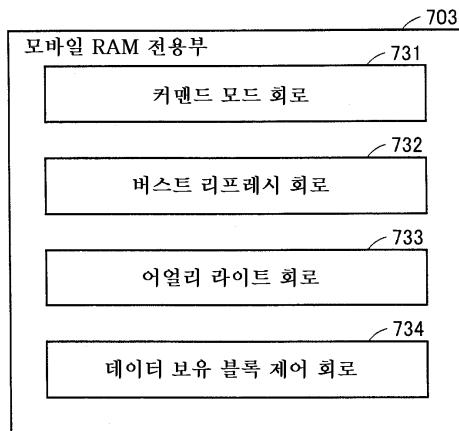

- [0460] 도 59는 모바일 RAM 전용부(703)의 구성을 도시한다. 동도에 도시한 바와 같이, 모바일 RAM 전용부(703)는, 커맨드 모드 회로(731)와, 버스트 리프레시 회로(732)와, 어얼리 라이트 회로(Early write circuit)(733)와, 데이터 보유 블록 제어 회로(734)를 구비한다.

- [0461] 커맨드 모드 회로(731)는 외부 신호의 조합에 의해서, 내부의 레지스터의 세트 및 리셋을 행한다.

- [0462] 버스트 리프레시 회로(732)는 리프레시 요구를 내부 카운터에 보유해 놓고, 어떤 일정한 타이밍이 입력되었을 때에, 연속하여 리프레시 동작을 행한다.

- [0463] 어얼리 라이트 회로(733)는, 라이트 동작의 타이밍을 빠르게 한 어얼리 라이트 동작을 제어한다.

- [0464] 데이터 보유 블록 제어 회로(734)는, 선택한 블록만 리프레시를 행하도록 제어함으로써, 선택한 블록의 데이터만 보유한다.

- [0465] 이상과 같이, 본 실시예에 따른 RAM에 따르면, 셀룰러 RAM과 모바일 RAM의 양방의 기능을 효율적으로 실현하도록 구성했기 때문에, 생산 관리를 효율화할 수 있고, 제품 전환 시기에 있어서의 재고의 저감을 방지하고, 또한 개발 비용을 착감할 수 있다.

- [0466] [제8 실시예]

- [0467] 본 실시예는 버스트 길이 카운터를 이용하여 프리차지를 실행하는 동기식 의사 SRAM에 관한 것이다.

- [0468] (구성)

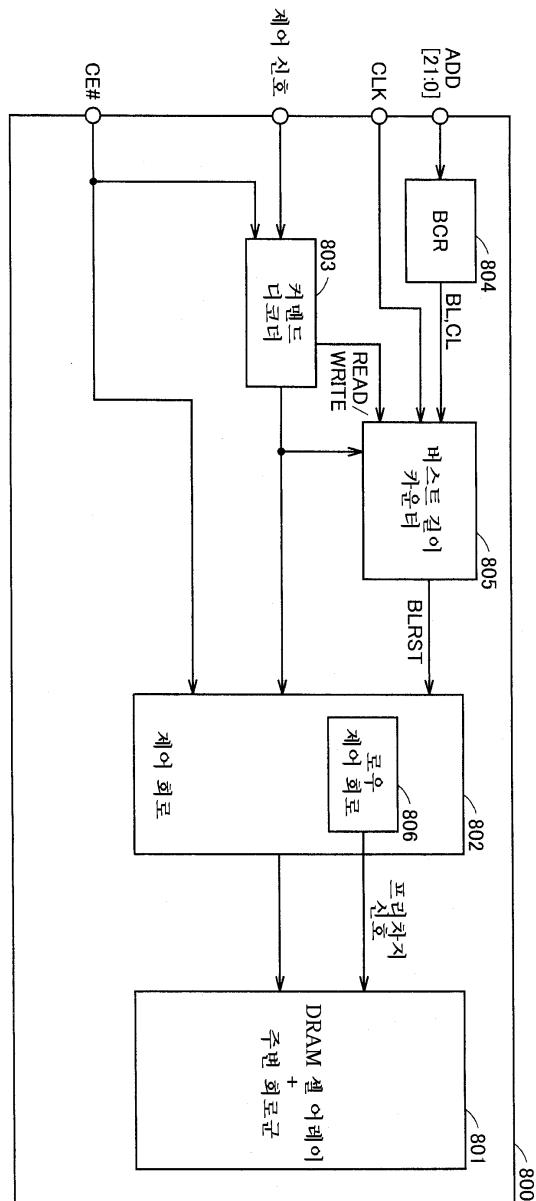

- [0469] 도 60은 본 실시예에 따른 동기식 의사 SRAM(800)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(800)은, DRAM 셀 어레이+주변 회로군(801)과, 제어 회로(802)와, 커맨드 디코더(803)와, BCR(Burst Configuration Register)(804)과, 버스트 길이 카운터(805)를 구비한다.

- [0470] DRAM 셀 어레이+주변 회로군(801)의 DRAM 셀 어레이는, 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다. 주변 회로군은, 글로벌 입출력선 쌍 GIOP(GIO 및 /GIO)과, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앰프와, 프리 앰프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다.

- [0471] 커맨드 디코더(803)는 외부 제어 신호로부터 생성된 내부 제어 신호의 논리 레벨의 조합에 따라서, 로우 활성화 신호 ACT, 판독 신호 READ, 및 기입 신호 WRITE를 생성한다.

- [0472] BCR(804)은 외부 시스템과의 인터페이스, 예를 들면, 버스트 길이 BL 및 커맨드 레이턴시 CL 등을 기억한다.

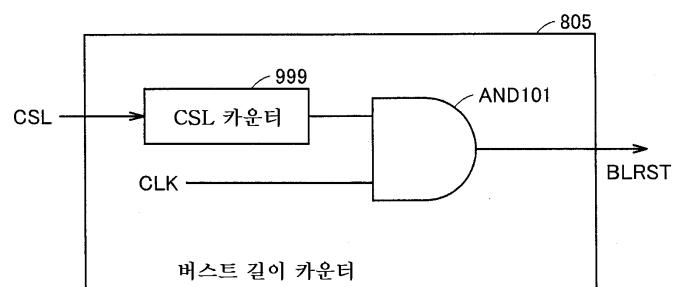

- [0473] 도 61은 버스트 길이 카운터(805)의 상세한 구성을 도시한다. 동도를 참조하여, 버스트 길이 카운터(805)는, CSL 카운터(999)와, 논리곱 회로 AND101을 포함한다. CSL 카운터(999)는 컬럼 선택 신호 CSL을 받는다. CSL 카운터(999)는 버스트 길이 BL개의 컬럼 선택 신호 CSL의 펄스를 카운트하면, 「H」를 출력한다. 논리곱 회로 AND101은, 외부 클럭 CLK 및 CSL 카운터(999)의 출력을 받아, CSL 카운터(999)의 출력이 「H」로 된 후의 최초의 클럭 CLK가 입력된 타이밍에서, 버스트 길이 리셋 신호 BLRST를 「H」로 활성화한다.

- [0474] 제어 회로(802)는 로우 제어 회로(806)를 포함한다. 로우 제어 회로(806)는 버스트 길이 리셋 신호 BLRST를 받으면, 프리차지 신호 PRC를 활성화한다. 이 프리차지 신호 PRC에 의해서, 워드선이 비활성화되고, 비트선 쌍이 프리차지된다.

- [0475] (동작)

- [0476] 도 62는 워드선이 비활성화되는 타이밍차트를 도시한다. 동도에 도시한 바와 같이, 판독 신호 READ 또는 기입 신호 WRITE를 받은 클럭의 타이밍을 클럭 CLK0으로 했을 때에, 커맨드 레이턴시 CL=2, 버스트 길이 BL=4로부터, 버스트 액세스의 최후의 컬럼의 선택을 위한 컬럼 선택 신호 CSL이 클럭 CLK4의 타이밍에서 활성화된다. 버스트 길이 카운터(805)는 CLK0으로부터 (CL+BL-1)=5개후의 클럭인 클럭 CLK5의 타이밍에서, 버스트 길이 리셋 신호 BLRST를 「H」로 활성화한다. 그리고, 이 버스트 길이 리셋 신호 BLRST에 기초하여,

프리차지 신호 PRC가 활성화되고, 선택되어 있던 워드선(X<sub>o</sub>)이 비활성화되고, 비트선 쌍이 프리차지된다.

[0477] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, 버스트 길이 카운터(805)는, 버스트 길이 BL개의 컬럼 선택 신호 CSL의 펄스를 카운트하면, 버스트 길이 리셋 신호 BLRST를 활성화하기 때문에, 외부 칩 인에 이를 신호 CE#를 「H」로 되돌리지 않더라도, 워드선을 비활성화할 수 있다.

[0478] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, 외부 제어에 의해서, 워드선을 비활성화하는 것이 아니라, 내부 제어에 의해 워드선을 비활성화하기 때문에, 제어가 간이해진다.

[0479] 또한, 외부 어드레스 취득 신호 ADV#의 하강을 기점으로 리셋 신호를 발생시키고, 이 리셋 신호에 의해서 프리차지 신호 PRC를 발생하도록 하여도 된다.

[0480] 또한, 본 실시예에서는 버스트 길이 리셋 신호 BLRST에 기초하여, 워드선의 비활성화를 행하였지만, 이것에 한정하는 것이 아니고, 예를 들면, 판독도 기입도 행하여지고 있지 않은 스탠바이 상태로 하는 것으로 해도 된다.

[0481] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니라, 클럭에 동기하여 동작하는 반도체 기억 장치이면 어떠한 것에도 적용할 수 있다.

[제9 실시예]

[0483] 본 실시예는 동기 모드 고정의 모드를 갖는 동기식 의사 SRAM에 관한 것이다.

[0484] (배경 기술의 동기 모드/비동기 모드의 설정)

[0485] 우선, 배경 기술의 Cellular RAM(R)의 동기/비동기 모드의 설정에 대하여 설명한다.

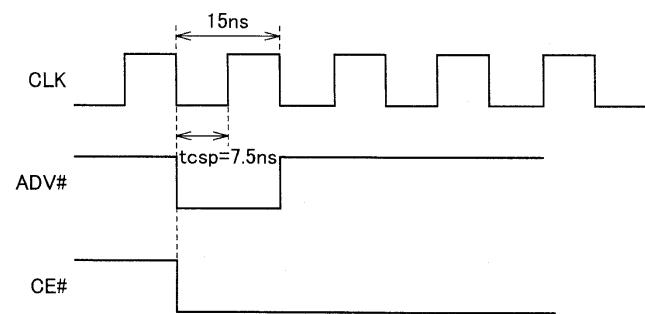

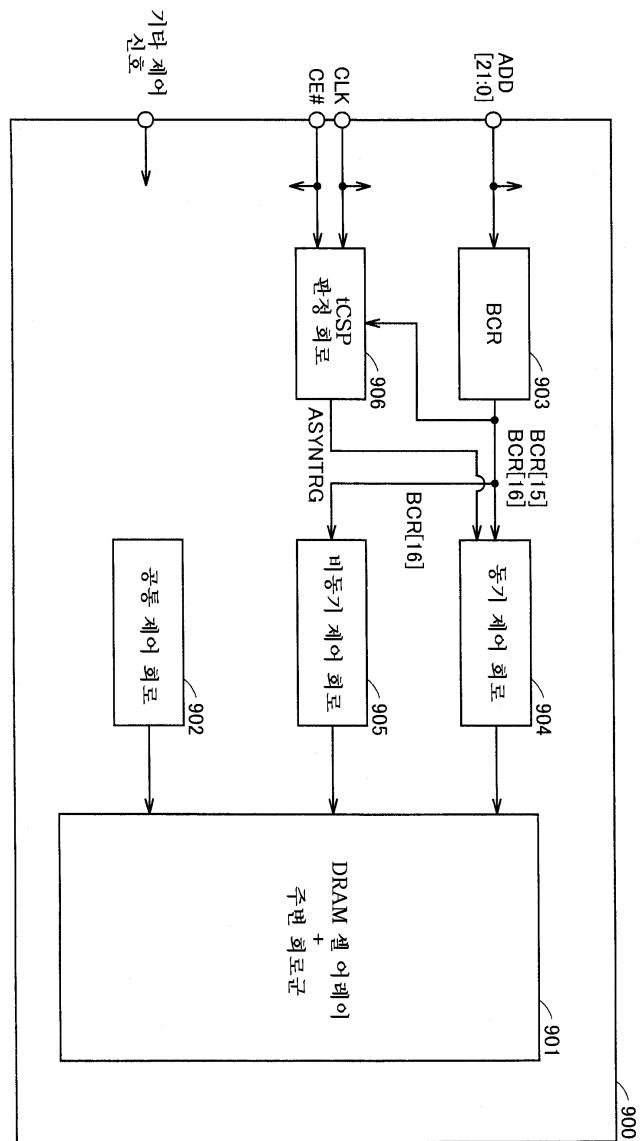

[0486] 도 63은 배경 기술의 동기/비동기 모드의 설정 방법을 도시하는 도면이다. 동도에 도시한 바와 같이, tCSP가 20ns 이상일 때에는, BCR(Bus Configuration Register)의 제15 비트째인 BCR[15]의 값에 상관없이, 비동기 고정 모드로 설정된다. tCSP가 20ns 미만일 때에는, BCR[15]의 값에 의해서 모드가 설정된다. tCSP란, 외부 칩 인에 이를 신호 CE#의 하강으로부터 외부 클럭 CLK가 상승하기까지의 시간이다.

[0487] 도 64a 및 64B는 tCSP의 값에 의한 모드의 설정을 설명하기 위한 도면이다. 도 64a에서는 tCSP는 7.5ns이다. 이 경우, tCSP가 20ns 미만이기 때문에, BCR[15]의 값이 참조되며, 값이 0일 때에는, 동기/비동기 혼합 모드로 설정되고, 값이 1일 때에는, 비동기 고정 모드로 설정된다.

[0488] 도 64b에서는 tCSP는 22.5ns이다. 이 경우, tCSP가 20ns 이상이기 때문에, 외부 클럭 CLK의 하강으로부터 20 ns로 된 시점에서, BCR[15]의 값에 상관없이, 비동기 고정 모드로 설정된다.

[0489] 이상의 설명으로부터 분명한 바와 같이, 도 64b와 같이, 클럭 주파수가 낮을 때에는, 강제적으로 비동기 고정 모드로 설정된다. 따라서, 저속의 클럭 주파수로 또한 동기 모드로 동작시킬 수 없다.

[0490] 따라서, 본 실시예는, tCSP가 20ns 이상과 같이 클럭 주파수가 낮을 때이더라도, 동기 모드로 설정할 수 있는 동기식 의사 SRAM을 제공한다.

[0491] (본 실시예의 동기/비동기 모드의 설정)

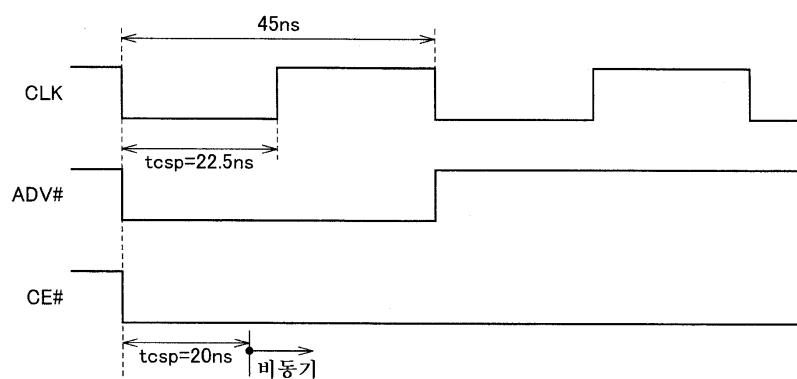

[0492] 도 65는 본 실시예의 동기/비동기 모드의 설정 방법을 도시하는 도면이다. 동도에 도시한 바와 같이, BCR[16]의 값이 0일 때에는, tCSP, 및 BCR[15]의 값에 상관없이, 동기 고정 모드로 설정된다. 한편, BCR[16]의 값이 1일 때에는, tCSP 및 BCR[15]의 값에 따라서 종래와 같이 설정된다.

[0493] (구성)

[0494] 도 66은 본 실시예에 따른 동기식 의사 SRAM(900)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(900)은, DRAM 셀 어레이+주변 회로군(901)과, BCR(Bus Configuration Register)(903)과, tCSP 판정 회로(906)와, 동기 제어 회로(904)와, 비동기 제어 회로(905)와, 공통 제어 회로(902)를 포함한다.

[0495] DRAM 셀 어레이+주변 회로군(901)의 DRAM 셀 어레이는, 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다. 주변 회로군은, 글로벌 입출력선 쌍 GIOP(GIO 및 /GIO)와, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앰프와, 프리 앰프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다.

- [0496] BCR(903)은 외부의 시스템과의 인터페이스를 규정한다.

- [0497] tCSP 판정 회로(906)는, 외부 칩 인에이블 신호 CE#의 하강으로부터 외부 클럭 CLK가 상승하기까지의 시간이 20ns 이상으로 된 시점에서, 비동기 제어 신호 ASYNTRG를 어서트한다. tCSP 판정 회로(906)는 BCR[15]과 BCR[16]을 받아, BCR[15]=1일 때 또는 BCR[16]=0일 때에는, tCSP를 판정하는 처리를 행하지 않는다. 왜냐하면, BCR[16]=0일 때에는, 동기 고정 모드이고, BCR[16]=1 또한 BCR[15]=1일 때에는 비동기 고정 모드이므로, tCSP를 판정할 필요가 없기 때문이다.

- [0498] 동기 제어 회로(904)는, BCR[16], 비동기 제어 신호 ASYNTRG, BCR[15]를 받아, 이들 조합이 도 65에 도시하는 동기 고정 모드 또는 동기/비동기 혼합 모드를 나타낼 때에, 활성화한다. 즉, 동기 제어 회로(904)는, BCR[16]=0일 때와, BCR[16]=1, 비동기 제어 신호 ASYNTRG가 비활성화, 또한 BCR[15]=0일 때에 활성화하고, 그 이외일 때에는 비활성화한다. 동기 제어 회로(904)는, 활성화하고 있을 때에, 동기식 의사 SRAM(900)의 외부 클럭 CLK에 동기한 동작을 제어한다.

- [0499] 비동기 제어 회로(905)는, BCR[16], 비동기 제어 신호 ASYNTRG, 및 BCR[15]을 받아, 이들 조합이 도 65에 도시하는 비동기 고정 모드 또는 동기/비동기 혼합 모드를 나타낼 때에, 활성화하고, 그 이외일 때에는 비활성화한다. 즉, 비동기 제어 회로(905)는, BCR[16]=1일 때에 활성화하고, BCR[16]=0일 때에 비활성화한다. 비동기 제어 회로(905)는 활성화하고 있을 때에, 동기식 의사 SRAM(900)의 외부 클럭 CLK에 동기하지 않는 동작을 제어한다.

- [0500] 공통 제어 회로(902)는 외부 클럭 CLK의 동기 유무에 상관없는 동작을 제어한다.

- [0501] 이상과 같이, 본 실시예에 따른 동기식 의사 SRAM에 따르면, tCSP의 값에 상관없이 동기 고정 모드로 설정할 수 있으므로, 클럭 주파수가 저속이라도, 클럭에 동기하여 동작할 수 있다.

- [0502] 본 실시예에서는, BCR[15], BCR[16]과 같이 인접하는 비트를 이용하여, 동기 모드/비동기 모드의 설정을 하므로, 회로 접속을 용이하게 할 수 있다.

- [0503] 또한, 본 실시예에서는 BCR[16]의 값에 의해서 동기 고정 모드로 설정하는 것으로 했지만, 이것에 한정되는 것은 아니다. 예를 들면, BCR의 다른 비트, 다른 레지스터의 비트, 본딩 옵션, 또는 외부 신호 등에 의해서, 동기 고정 모드로 설정하는 것으로 하여도 무방하다.

- [0504] 또한, 본 실시예는 동기식 의사 SRAM에 한정하여 적용되는 것이 아니라, 클럭에 동기하여 동작하는 동기 모드 와, 클럭에 대하여 비동기로 동작하는 비동기 모드를 갖는 반도체 기억 장치이면 어떠한 것에도 적용할 수 있다.

- [0505] [제10 실시예]

- [0506] 본 실시예는, 외부 칩 인에이블 신호 CE#에 의해서, 입력 버퍼의 활성/비활성을 제어함과 함께, 외부 칩 인에이블 신호 CE#를 클럭에 동기하지 않고서 활성화했을 때의 문제를 회피하는 동기식 의사 SRAM에 관한 것이다.

- [0507] (구성)

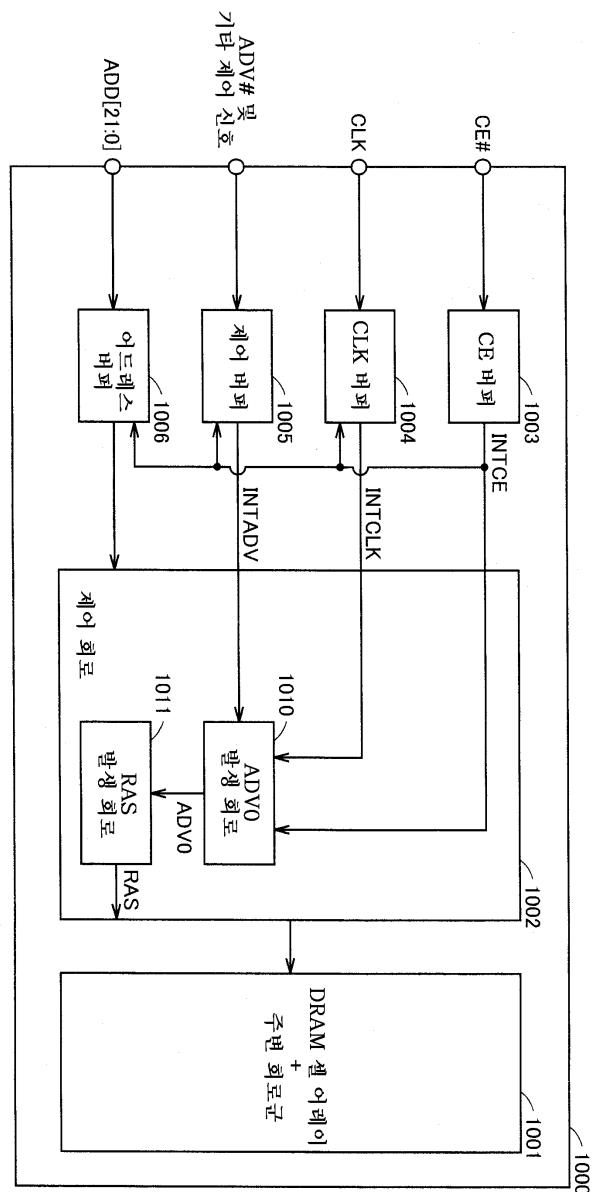

- [0508] 도 67은 본 실시예에 따른 동기식 의사 SRAM(1000)의 구성을 도시한다. 동도를 참조하여, 이 동기식 의사 SRAM(1000)은, DRAM 셀 어레이+주변 회로군(1001)과, 제어 회로(1002)와, CE 버퍼(1003)와, CLK 버퍼(1004)와, 제어 버퍼(1005)와, 어드레스 버퍼(1006)를 포함한다.

- [0509] DRAM 셀 어레이+주변 회로군(1001)의 DRAM 셀 어레이는, 다이내믹 랜덤 액세스 메모리(DRAM)의 셀로 구성되는 메모리 어레이이다. 주변 회로군은, 글로벌 입출력선 쌍 GIOP(GIO 및 /GIO)과, 각 열에 대응하여 마련된 열 선택선과, 열 선택 게이트와, 센스 앰프와, 프리 앰프와, 라이트 드라이버와, 로우 디코더, 컬럼 디코더 등을 포함한다.

- [0510] 어드레스 버퍼(1006)는 외부 어드레스 신호 ADD[21:0]를 받아, 내부 어드레스 신호를 생성한다.

- [0511] CE 버퍼(1003)는 외부 칩 인에이블 신호 CE#를 받아, 내부 칩 인에이블 신호 INTCE를 생성한다. 내부 칩 인에이블 신호 INTCE는, CLK 버퍼(1004), 제어 버퍼(1005), 및 어드레스 버퍼(1006)에 전송된다. 이들 입력 버퍼는, 내부 칩 인에이블 신호 INTCE가 칩의 비활성화를 나타내는 「L」 일 때에는, 동작을 정지하고, 내부 칩 인에이블 신호 INTCE가 칩의 활성화를 나타내는 「H」 일 때에는, 통상의 동작을 행한다. 이들 입력 버퍼는, 동작의 정지중에는, 외부로부터의 신호를 받더라도, 보유할 수 없어, 내부 신호를 출력할 수 없다.

- [0512] CLK 버퍼(1004)는 외부 클럭 CLK를 받아, 버퍼 클럭 BUFFCLK로서 보유하고, 내부 클럭 INTCLK를 생성한다.

- [0513] 제어 버퍼(1005)는, 외부 칩 인에이블 신호 CE#를 제외한 제어 신호(어드레스 취득 신호 ADV#를 포함함)를 받아, 내부 제어 신호를 생성한다. 예를 들면, 제어 버퍼(1005)는, 외부 어드레스 취득 신호 ADV#를 받았을 때에는, 내부 어드레스 취득 신호 INTADV를 생성한다.

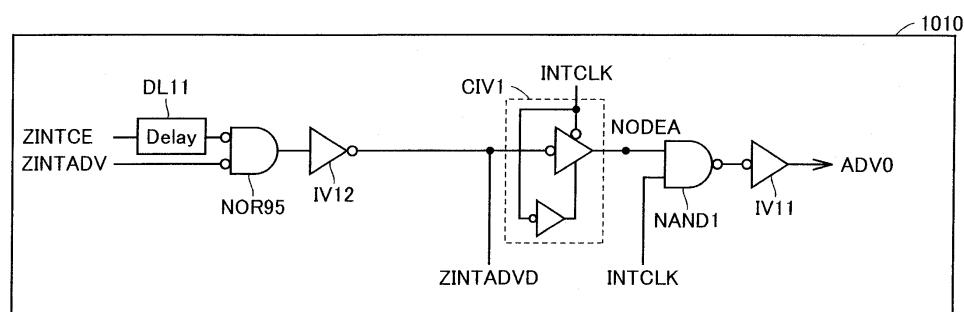

- [0514] 제어 회로(1002)는 ADV0 발생 회로(1010)와 RAS 발생 회로(1011)를 포함한다.

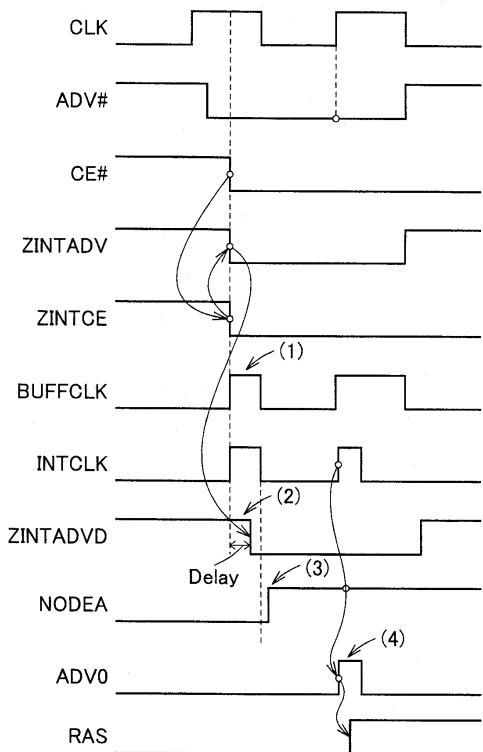

- [0515] ADV0 발생 회로(1010)는, 내부 칩 인에이블 신호 INTCE, 내부 클럭 INTCLK, 및 반전 내부 어드레스 취득 신호 ZINTADV에 의해, 어드레스 취득 트리거 신호 ADV0을 생성한다.

- [0516] RAS 발생 회로(1011)는 어드레스 취득 트리거 신호 ADV0에 의해, 로우 어드레스 스트로브 신호 RAS를 생성한다.

- [0517] (배경 기술의 ADV0 발생 회로)

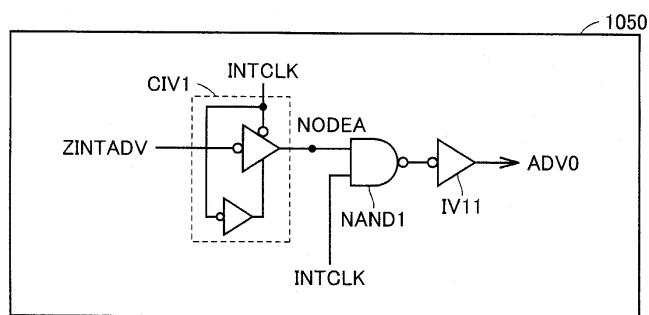

- [0518] 도 68은 배경 기술의 ADV0 발생 회로(1050)의 구성을 도시한다. 동도를 참조하여, 반전 내부 어드레스 취득 신호 ZINTADV가 클럭드 인버터 CIV1에 입력된다. 클럭드 인버터 CIV1의 출력과, 내부 클럭 INTCLK가 반전 논리곱 회로 NAND1에 입력되고, 반전 논리곱 회로 NAND1의 출력이 인버터 IV1에 입력된다. 인버터 IV1의 출력이 어드레스 취득 트리거 신호 ADV0으로 된다.

- [0519] (배경 기술의 동작)

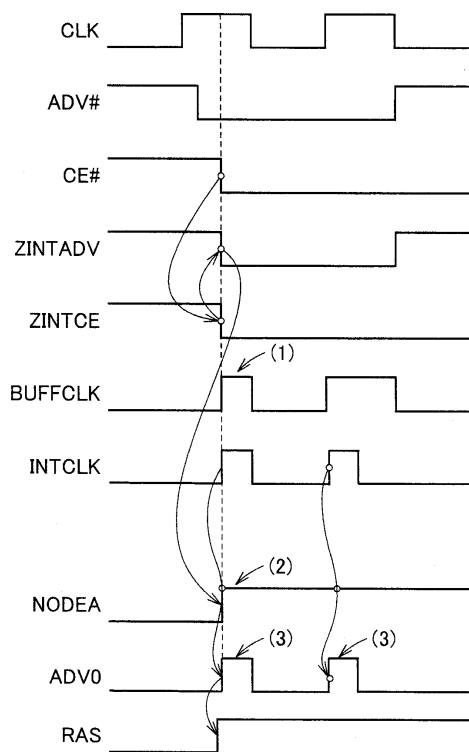

- [0520] 종래의 ADV0 발생 회로를 이용한 경우에, 외부 클럭 CLK과 동기하지 않고서, 비동기로 외부 칩 인에이블 신호 CE#를 변화시켰을 때에 발생하는 문제에 대하여 설명한다.

- [0521] 도 69는 배경 기술의 ADV0 발생 회로(1050)를 이용했을 때의 각 신호의 변화 타이밍을 도시하는 도면이다. 동도를 참조하여, 외부 클럭 CLK, 외부 어드레스 취득 신호 ADV#, 및 외부 칩 인에이블 신호 CE#가 도 69에 도시한 바와 같이 공급된다. 외부 칩 인에이블 신호 CE#가 「H」일 때에는, CLK 버퍼(1004) 및 제어 버퍼(1005)가 정지중이고, 외부 칩 인에이블 신호 CE#만이 CE 버퍼(1003)에 취득되어, 내부 칩 인에이블 신호 INTCE가 생성된다. 외부 칩 인에이블 신호 CE#가 「L」로 활성화되는 것에 응답하여, 반전 내부 칩 인에이블 신호 ZINTCE가 「L」로 된다.