(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5143431号

(P5143431)

(45) 発行日 平成25年2月13日(2013.2.13)

(24) 登録日 平成24年11月30日(2012.11.30)

|                              |                |

|------------------------------|----------------|

| (51) Int.Cl.                 | F 1            |

| <b>H03F</b> 3/45 (2006.01)   | H03F 3/45 A    |

| <b>G09G</b> 3/36 (2006.01)   | H03F 3/45 B    |

| <b>G09G</b> 3/20 (2006.01)   | G09G 3/36      |

| <b>G02F</b> 1/1345 (2006.01) | G09G 3/20 623B |

| <b>G02F</b> 1/133 (2006.01)  | G09G 3/20 621M |

請求項の数 10 (全 13 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2007-4775 (P2007-4775)      |

| (22) 出願日     | 平成19年1月12日 (2007.1.12)        |

| (65) 公開番号    | 特開2007-189699 (P2007-189699A) |

| (43) 公開日     | 平成19年7月26日 (2007.7.26)        |

| 審査請求日        | 平成22年1月5日 (2010.1.5)          |

| (31) 優先権主張番号 | 10-2006-0003962               |

| (32) 優先日     | 平成18年1月13日 (2006.1.13)        |

| (33) 優先権主張国  | 韓国 (KR)                       |

|           |                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeon<br>gton-gu, Suwon-si, G<br>yeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100064908<br>弁理士 志賀 正武                                                                                                                                                 |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                                                                                                  |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                                                                                                 |

最終頁に続く

(54) 【発明の名称】出力偏差の改善された出力バッファ及びこれを備えた平板表示装置用のソースドライバ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の表示セルが配列されている表示パネルに階調表示用のデータ信号を発生させる平板表示装置のソースドライバにおいて、

外部から提供されるデジタルのデータ信号を保存する保存部と、

前記保存部からデジタルのデータ信号を入力して、アナログの階調表示用のデータ信号に変換するデジタルアナログ変換部と、

前記階調表示用のデータ信号を前記表示パネルに提供する出力バッファ部と、を備え、

前記出力バッファ部は、複数の出力バッファを備えるが、各出力バッファは、互いに異なる駆動能を有する複数のトランジスタから構成され、

前記複数のトランジスタの一部は、薄膜のゲート絶縁膜を備える低電圧トランジスタを含み、残りは、厚膜のゲート絶縁膜を備える高電圧トランジスタを含み、

前記各出力バッファは、

第1差動入力信号と、第2差動入力信号として前記階調表示用のデータ信号とを入力する信号入力部と、

前記出力バッファの増幅等級を選択する増幅選択部と、

第1電源端子と前記信号入力部との間に連結される第1電流ミラーと、

第2電源端子と前記信号入力部との間に連結される第2電流ミラーと、

前記信号入力部及び前記増幅選択部の動作によって前記出力信号を発生させる出力部と、を備え、

10

20

前記信号入力部、前記増幅選択部、前記第1及び第2電流ミラー、及び前記出力部は、それぞれ複数のトランジスタから構成され、

前記第1及び第2電流ミラーを構成するトランジスタは、薄膜のゲート絶縁膜を備える低電圧トランジスタを含み、前記信号入力部、前記増幅選択部、及び前記出力部を構成するトランジスタは、厚膜のゲート絶縁膜を備える高電圧トランジスタを含む

ことを特徴とする平板表示装置用のソースドライバ。

**【請求項2】**

前記出力バッファ部に提供される電源電圧が12Vであると仮定する時、前記複数のトランジスタのうち低電圧トランジスタの動作領域は、2V以下である

ことを特徴とする請求項1に記載の平板表示装置用のソースドライバ。 10

**【請求項3】**

前記表示パネルは、液晶パネルである

ことを特徴とする請求項1に記載の平板表示装置用のソースドライバ。

**【請求項4】**

前記複数のトランジスタは、半導体基板上に形成されたMOSトランジスタまたは平板表示パネル用の基板上に形成された薄膜トランジスタを含む

ことを特徴とする請求項1に記載の平板表示装置用のソースドライバ。

**【請求項5】**

前記平板表示装置は、SOGタイプである

ことを特徴とする請求項1に記載の平板表示装置用のソースドライバ。 20

**【請求項6】**

複数のゲートライン、複数のソースライン、及び前記複数のゲートラインと複数のソースラインとに連結された複数の表示セルが配列されている表示パネルと、

複数のゲート駆動信号を発生させ、前記表示パネルの前記複数のゲートラインに前記複数のゲート駆動信号をそれぞれ印加するゲートドライバと、

デジタルの入力データ信号に基づいて、前記表示パネルに配列された表示セルを駆動するのに使われるアナログ階調電圧信号を発生させるソースドライバと、

前記ゲートドライバ及びソースドライバを制御し、前記ソースドライバに前記入力データ信号を提供する制御部と、を備え、

前記ソースドライバ回路は、 30

前記デジタルの入力データ信号をアナログのデータ信号に変換して、前記アナログの階調電圧信号を発生させるデジタルアナログ変換部と、

前記デジタルアナログ変換部で発生した前記階調入力電圧を前記複数のソースラインを介して前記表示パネルに提供する複数の出力バッファを備えた出力バッファ部と、を備え、

各出力バッファは、複数のトランジスタから構成されるが、前記複数のトランジスタは、互いに異なる駆動能を有するトランジスタから構成され、

前記複数のトランジスタの一部は、低電圧駆動能を有するトランジスタを含み、残りは、高電圧駆動能を有するトランジスタを含み、

前記各出力バッファは、 40

第1差動入力信号と、第2差動入力信号として前記階調電圧信号とを入力する信号入力部と、

前記出力バッファの増幅等級を選択する増幅選択部と、

第1電源端子と前記信号入力部との間に連結される第1電流ミラーと、

第2電源端子と前記信号入力部との間に連結される第2電流ミラーと、

前記信号入力部及び前記増幅選択部の動作によって前記出力信号を発生させる出力部と、を備え、

前記信号入力部、前記増幅選択部、前記第1及び第2電流ミラー、及び前記出力部は、それぞれ複数のトランジスタから構成され、

前記第1及び第2電流ミラーを構成するトランジスタは、薄膜のゲート絶縁膜を備える 50

低電圧トランジスタを含み、前記信号入力部、前記増幅選択部、及び前記出力部を構成するトランジスタは、厚膜のゲート絶縁膜を備える高電圧トランジスタを含むことを特徴とする平板表示装置。

【請求項 7】

前記増幅部に提供される電源電圧が 12V であると仮定する時、前記複数のトランジスタのうち低電圧駆動能を有するトランジスタの動作領域は、2V 以下であることを特徴とする請求項 6 に記載の平板表示装置。

【請求項 8】

前記表示パネルは、液晶パネルであることを特徴とする請求項 6 に記載の平板表示装置。

10

【請求項 9】

前記複数のトランジスタは、半導体基板上に形成された MOS トランジスタまたは平板表示パネル用の基板上に形成された薄膜トランジスタを含むことを特徴とする請求項 6 に記載の平板表示装置。

【請求項 10】

前記平板表示装置は、SOG タイプであることを特徴とする請求項 6 に記載の平板表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

20

本発明は、平板表示装置用のソースドライバに係り、さらに詳細には、出力偏差の改善された出力バッファ及びこれを備えた平板表示装置用のソースドライバに関する。

【背景技術】

【0002】

一般的な液晶表示装置 (LCD) は、二枚の基板間に介在した液晶層を備え、前記液晶層に印加される電圧の強度を調節して、前記液晶層を通過する光の透過率を調節することで所望の画像を表示する。このような液晶表示装置は、液晶層をスイッチングするためのスイッチング素子として薄膜トランジスタを利用した薄膜トランジスタ液晶表示装置 (TFT-LCD) が主に使われている。TFT-LCD のうち、ポリシリコン TFT-LCD は、ガラス基板上に MOS トランジスタからなる回路を内蔵できるということが最も大きい長所である。現在では、LTPS (Low Temperature Poly crystalline Silicon) 工程を利用して、ドライバをガラス基板上に集積することが可能であり、さらに、制御部を含むシステム全体をガラス基板上に集積する SOG (System On Glass) が可能になった。

30

【0003】

TFT-LCD は、液晶パネルに配列された液晶セルを駆動するためのソースドライバを備える。ソースドライバは、階調表現のための電圧信号を液晶パネルに提供するために複数の出力バッファを備え、各出力バッファは、トランジスタから構成された演算増幅器から構成される。演算増幅器をトランジスタで構成する場合、同じ入力データに対応して出力される出力電圧の間には、大きい偏差が発生する。このような差をオフセット電圧と言い、オフセット電圧は、トランジスタの特性差によって激しく変動される。ソースドライバに同じデータ電圧が印加されても、出力バッファから発生する出力信号に偏差が発生して液晶パネルに同じ階調電圧が提供されない。したがって、同じ入力データに対してソースドライバから液晶パネルに異なる階調データが提供され、これによって誤動作または信号歪曲を招いて液晶パネルの画質低下をもたらす。

40

【0004】

このように、ソースドライバの出力バッファで発生する出力信号の偏差は、トランジスタのしきい電圧の偏差に起因する。トランジスタのしきい電圧は、前記トランジスタをオンまたはオフさせるための電圧であって、ゲート電極とチャンネル領域との間に存在するゲート絶縁膜の厚さ、チャンネル領域のドーピング濃度などの関数として表現される。前

50

記ゲート絶縁膜の厚さまたはチャンネル領域のドーピング濃度は、工程偏差によって変化する。したがって、従来には、出力バッファを構成するトランジスタをいずれも同一に形成したので、すなわち、出力バッファを構成するあらゆるトランジスタのゲート絶縁膜をいずれも同じ厚さを有するように形成したので、しきい電圧の変化による出力信号の偏差が引き起こされた。

【0005】

これを解決するために、出力バッファにオフセット補償回路などを追加する方法が提案された。しかし、オフセット補償回路の追加は、面積の増加をもたらすため望ましくない。

【特許文献1】米国特許第6924690号明細書

10

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明が解決しようとする技術的課題は、出力バッファを互いに異なる駆動能を有するトランジスタから構成して、出力バッファで発生する出力信号の偏差を改善した出力バッファを提供することである。

【0007】

また、本発明の技術的課題は、出力偏差の改善された出力バッファを備えた平板表示装置用のソースドライバを提供することである。

【課題を解決するための手段】

20

【0008】

前記本発明の技術的課題を達成するために、本発明の実施形態による出力バッファは、第1入力信号が提供される第1入力端子と、第2入力信号が提供される第2入力端子と、前記第2入力信号に基づいて出力信号を発生させるが、前記出力信号は、前記第1入力信号として提供される出力端子と、第1電源が提供される第1電源端子と、第2電源が提供される第2電源端子と、前記第1入力信号と第2入力信号とを差動増幅して、前記出力信号を前記第1電源にプルアップまたは前記第2電源にプルダウンさせ、互いに異なる複数のトランジスタを備える増幅部とを備える。

【0009】

前記増幅部は、互いに異なる駆動能を有する複数のトランジスタから構成される。前記複数のトランジスタの一部は、薄膜のゲート絶縁膜を備える低電圧トランジスタを含み、残りは、厚膜のゲート絶縁膜を備える高電圧トランジスタを含む。前記増幅部に提供される電源電圧が12Vであると仮定する時、前記複数のトランジスタのうち低電圧駆動能を有するトランジスタの動作領域は、2V以下である。前記複数のトランジスタは、MOSトランジスタまたは薄膜トランジスタを含む。第1電源は、電源電圧であり、前記第2電源は接地電圧である。

30

【0010】

前記増幅部は、前記第1差動入力信号と、第2差動入力信号として前記出力信号とを入力する信号入力部と、前記増幅部の増幅等級を選択する増幅選択部と、前記第1電源端子と前記信号入力部との間に連結される第1電流ミラーと、前記第2電源端子と前記信号入力部との間に連結される第2電流ミラーと、前記信号入力部及び前記増幅選択部の動作によって前記出力信号を発生させる出力部とを備える。

40

【0011】

前記信号入力部、前記増幅選択部、前記第1及び第2電流ミラー、及び前記出力部は、それぞれ複数のトランジスタから構成され、前記第1及び第2電流ミラーを構成するトランジスタは、薄膜のゲート絶縁膜を備える低電圧トランジスタを含み、前記信号入力部、前記増幅選択部、及び前記出力部を構成するトランジスタは、厚膜のゲート絶縁膜を備える高電圧トランジスタを含む。

【0012】

また、本発明の他の見地によれば、複数の表示セルが配列されている表示パネルに階調

50

表示用のデータ信号を発生させる平板表示装置のソースドライバを提供する。前記ソースドライバは、外部から提供されるデジタルのデータ信号を保存する保存部と、前記保存部からデジタルのデータ信号を入力してアナログの階調表示用のデータ信号に変換するデジタルアナログ変換部と、前記階調表示用のデータ信号を前記表示パネルに提供する出力バッファ部とを備える。前記出力バッファ部は、複数の出力バッファを備えるが、各出力バッファは、互いに異なる複数のトランジスタから構成される。

【0013】

また、本発明の他の見地によれば、平板表示装置は、複数のゲートライン、複数のソースライン、及び前記複数のゲートラインと複数のソースラインとに連結された複数の表示セルが配列されている表示パネルと、前記表示パネルの前記複数のゲートラインにゲート駆動信号を発生させるゲートドライバと、デジタルの入力データ信号に基づいて、前記表示パネルに配列された表示セルを駆動するためのアナログ階調電圧信号を出力するソースドライバと、前記ゲートドライバ及びソースドライバを制御し、前記ソースドライバに前記入力データ信号を提供する制御部とを備える。

10

【0014】

前記ソースドライバ回路は、前記デジタルの入力データ信号をアナログのデータ信号に変換して、前記アナログの階調電圧信号を発生させるデジタルアナログ変換部と、前記デジタルアナログ変換部で発生した前記階調入力電圧を前記複数のソースラインを介して前記液晶パネルに提供する複数の出力バッファを備えた出力バッファ部とを備える。各出力バッファは、複数のトランジスタから構成されるが、前記複数のトランジスタは、互いに異なる駆動能を有するトランジスタから構成される。

20

【発明の効果】

【0015】

平板表示装置用のソースドライバ回路に使われる出力バッファ回路において、出力偏差に大きく影響を及ぼすトランジスタをゲート絶縁膜の厚さが薄い低電圧トランジスタから構成し、残りのトランジスタは、ゲート絶縁膜の厚さが厚い高電圧トランジスタから構成する。これにより、出力バッファの面積を増加させずにMOSトランジスタのしきい電圧の変化による出力バッファの出力偏差を改善することができる。また、本発明の異なる駆動能を有するトランジスタから構成される出力バッファは、多様な平板表示装置のドライバ回路に適用可能である。

30

【発明を実施するための最良の形態】

【0016】

以下、添付した図面に基づき、本発明の望ましい実施形態を説明する。しかし、本発明の実施形態は、色々な他の形態に変形でき、本発明の範囲が後述する実施形態によって限定されると解釈されてはならない。本発明の実施形態は、当業者に本発明をさらに完全に説明するために提供されるものである。したがって、図面での要素の形状などは、さらに明確な説明を強調するために誇張したものであり、図面上で同一符号で表示された要素は同一要素を意味する。

【0017】

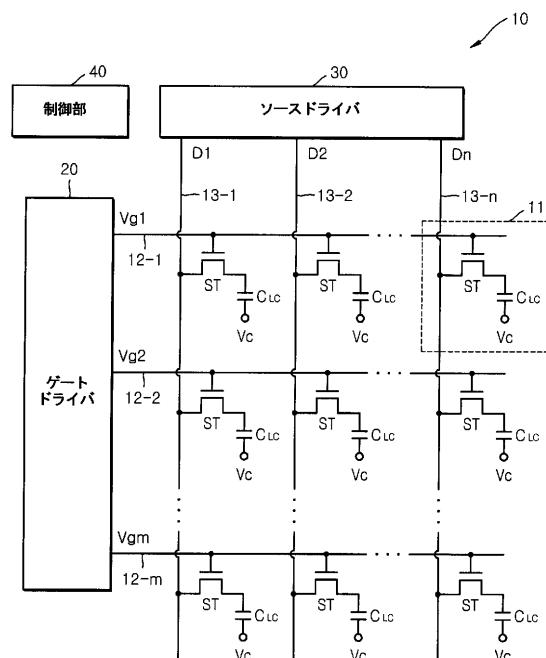

図1は、本発明のTFT-LCDの構成図である。図1を参照すれば、TFT-LCDは、セルアレイが配列される液晶パネル10、ゲートドライバ20、ソースドライバ30、及び制御部40を備える。前記液晶パネル10は、それぞれゲート駆動電圧Vg1~Vgmが提供される複数のゲートライン12-1~12-m、前記複数のゲートライン12-1~12-mと交差するように配列され、それぞれ階調電圧D1~Dnが提供される複数のソースライン13-1~13-n、前記複数のゲートライン12-1~12-m及び前記複数のデータライン13-1~13-nにそれぞれ連結される複数の液晶セル11を備える。

40

【0018】

前記各液晶セル11は、前記各ゲートライン12-1~12-mにゲートが連結され、ドレインにソースライン13-1~13-nが連結されるスイッチング素子である薄膜ト

50

ランジスタ S T と、前記薄膜トランジスタ S T のソースに一端が連結され、他端に共通電圧  $V_c$  が提供される液晶キャパシタ  $C_{Lc}$  とを備える。図示されていないが、各液晶セル 11 は、前記液晶キャパシタ  $C_{Lc}$  と並列連結されるストレージキャパシタ  $C_{st}$  をさらに備えてもよい。

【0019】

前記ゲートドライバ 20 は、前記液晶パネル 10 に配列された前記液晶セル 11 の薄膜トランジスタ S T のゲートをオンまたはオフさせるゲート駆動信号  $V_{g1} \sim V_{gm}$  をそれぞれのゲートライン 12-1 ~ 12-m に発生させる。前記ソースドライバ 30 は、入力データによる階調電圧  $D_1 \sim D_n$  をそれぞれのソースライン 13-1 ~ 13-n に提供する。前記制御部 40 は、外部から提供される制御信号を入力して、前記ゲートドライバ 20 及びソースドライバ 30 を制御するための制御信号（図示せず）を発生させる。 10

【0020】

前記ゲートドライバ 20 及び前記ソースドライバ 30 は、液晶パネル 10 の外部に配置されるか、または COG (Chip On Glass) タイプの場合に液晶パネル 10 上に配置されうる。また、前記ゲートドライバ 20 及びソースドライバ 30 は、前記液晶パネル 10 のセルアレイをガラス基板上に製作するときに共に製作されてもよい。前記制御部 40 は、液晶パネル 10 の外部に配置されるか、または SOG タイプの場合に前記液晶パネル 10 上に配置されうる。

【0021】

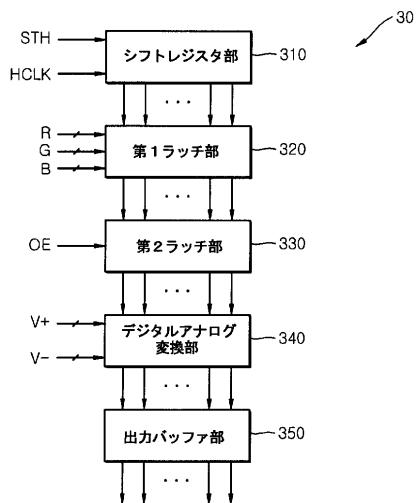

図 2 は、本発明の実施形態によるソースドライバ 30 の概略的なブロック図である。図 2 を参照すれば、ソースドライバ 30 は、シフトレジスタ部 310、第 1 ラッチ部 320、第 3 ラッチ部 330、デジタルアナログ変換部 340、及び出力バッファ部 350 を備える。前記シフトレジスタ部 310 は、前記制御部 40 から提供されるデータクロック信号  $HCLK$  と水平同期スタート信号  $STH$  を入力して、前記水平同期スタート信号  $STH$  を順次にシフトさせて前記第 1 ラッチ部 320 に出力する。 20

【0022】

前記第 1 ラッチ部 320 は、前記シフトレジスタ部 310 から提供される出力信号に応答して、前記制御部 40 から提供される所定のビット、例えば 8 ビットの R、G、B データ信号を順次に入力して保存する。前記制御部 40 から提供される R、G、B データ信号は、一定の階調値を有するデジタル信号である。前記第 1 ラッチ部 320 に前記複数のソースライン 13-1 ~ 13-n に伝送される R、G、B データ信号が全部保存されれば、前記第 1 ラッチ部 320 に保存された R、G、B データ信号は、同時に前記第 2 ラッチ部 330 に伝送される。 30

【0023】

前記第 2 ラッチ部 330 に保存された R、G、B データ信号は、出力イネーブル信号  $OE$  に応答してデジタルアナログ変換部 340 に提供される。デジタルアナログ変換部 340 は、階調電圧発生部（図示せず）に発生する階調電圧  $V_+ \sim V_-$  のうち、前記第 2 ラッチ部 330 から提供される R、G、B データ信号に対応する階調電圧信号を選択して出力する。したがって、デジタルアナログ変換部 340 は、前記第 2 ラッチ部 330 から提供されるデジタル信号の R、G、B データ信号を入力し、前記 R、G、B データ信号に相応するアナログ信号の階調電圧信号に変換する。前記デジタルアナログ変換部 340 は、図示されていないが、複数のデジタルアナログ変換器、例えば、n 個のデジタルアナログ変換器を備え、複数のデジタルアナログ変換器は、それぞれアナログ階調電圧信号  $DAC_1 \sim DAC_n$  を前記出力バッファ部 350 に提供する。 40

【0024】

図示されていないが、ソースドライバ 30 は、前記第 2 ラッチ部 330 と前記デジタルアナログ変換部 340 との間に配列されるレベルシフト部をさらに備えてもよい。前記レベルシフト部は、前記制御部 40 から提供されて前記第 2 ラッチ部 330 に保存された R、G、B データ信号を液晶パネル 10 を駆動するのに適した高電圧レベルの R、G、B データ信号に変換させる。 50

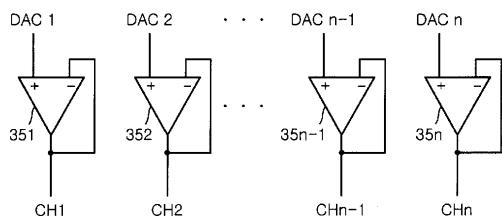

## 【0025】

前記出力バッファ部350は、前記デジタル-アナログ変換部340の出力を前記ソースライン13-1～13-nを介して液晶パネル10に提供する。前記出力バッファ部350は、図3を参照すれば、前記デジタルアナログ変換部340の複数のデジタルアナログ変換器から、階調電圧信号D A C 1～D A C nをそれぞれ前記液晶パネル10の複数のソースライン13-1～13-nにそれぞれ提供するための複数の出力バッファ、例えば、n個の出力バッファ351～35nを備える。

## 【0026】

各出力バッファ351～35nは、非反転入力端子(+)に前記デジタルアナログ変換部340の各デジタルアナログ変換器から提供される階調電圧信号D A C 1～D A C nが提供され、反転入力端子(-)に出力信号C H 1～C H nがフィードバックされる差動増幅器から構成される。前記各出力バッファ351～35nは、前記各階調電圧信号D A C 1～D A C nを増幅して、出力信号C H 1～C H nを前記ソースライン13-1～13-nを介して液晶パネル10に提供する。

## 【0027】

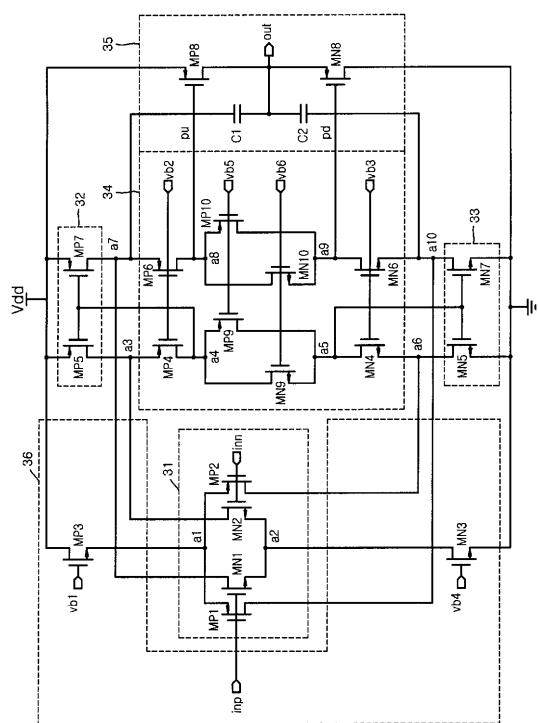

図4は、図3に示された出力バッファ351～35nの詳細図であって、MOSトランジスタでもって具現した一例を示す。各出力バッファ351～35nは、同じ構成を有する。図4を参照すれば、各出力バッファ351～35nは、差動増幅部、増幅選択部34、出力部35、及びイネーブル部36を備える。前記差動増幅部は、信号入力部31、第1電流ミラー32、及び第2電流ミラー33を備える。前記信号入力部31は、前記デジタルアナログ変換部340の各デジタルアナログ変換器から提供される階調電圧信号D A C 1～D A C nを第1差動入力端子を介して第1差動入力信号i n pとして入力し、出力端子outを介して出力される出力信号C H 1～C H nを第2差動入力端子を介して第2差動入力信号i n nとして入力する。前記第1差動入力信号i n pを入力する第1差動入力端子は、図3の非反転入力端子(+)に対応し、前記第2差動入力信号i n nを入力する第2差動入力端子は、図3の反転入力端子(-)に対応する。

## 【0028】

前記信号入力部31は、第1差動入力信号i n pと第2差動入力信号i n nとをそれぞれ入力する第1及び第2NMOSトランジスタM N 1、M N 2及び第1及び第2PMOSトランジスタM P 1、M P 2を備える。前記第1及び第2NMOSトランジスタM N 1、M N 2は、ゲートに第1及び第2差動入力信号i n p、i n nがそれぞれ印加され、ソースが第2ノードa 2に共通連結され、ドレインが第7ノードa 7及び第3ノードa 3にそれぞれ連結される。前記第1及び第2PMOSトランジスタM P 1、M P 2は、ゲートに前記第1及び第2差動入力i n p、i n nが提供され、ソースに前記第1ノードa 1が共通連結され、ドレインがそれぞれ第10ノードa 10及び第6ノードa 6に連結される。第1電流ミラー32は、第5及び第7PMOSトランジスタM P 5、M P 7を備える。前記第5及び7MOSトランジスタM P 5、M P 7は、ゲートが第4ノードa 4に共通連結され、ソースに第1電源端子が連結され、ドレインが前記第3ノードa 3及び第7ノードa 7にそれぞれ連結される。前記第1電源端子には、電源電圧V d dが提供される。

## 【0029】

第2電流ミラー33は、第5及び第7NMOSトランジスタM N 5、M N 7を備える。前記第5及び7MOSトランジスタM P 5、M P 7は、ゲートが第5ノードa 5に共通連結され、ソースに第2電源端子が連結され、ドレインが前記第6ノードa 6及び第10ノードa 10にそれぞれ連結される。前記第2電源端子には、接地電圧V s sが提供される。

## 【0030】

増幅選択部34は、前記出力バッファ351～35nが前記デジタルアナログ変換部340から階調電圧信号D C A 1～D C A nを増幅するとき、増幅等級を選択するためのものである。例えば、前記増幅選択部34は、外部から提供される第5及び第6バイアス電圧v b 5、v b 6によって、A級、B級またはA B級のうち一つを選択して、前記各出力

10

20

30

40

50

バッファ351～35nの増幅部が、選択された等級に第1及び第2差動入力信号 $i_{np}$ 、 $i_{nn}$ を増幅できるようにする。前記増幅選択部34は、第4、第6、第9及び第10PMOSトランジスタMP4、MP6、MP9、MP10及び第4、第6、第9及び第10NMOSトランジスタMN4、MN6、MN9、MN10を備える。

#### 【0031】

前記第4及び第6PMOSトランジスタMP4、MP6は、ゲートに第2バイアス電圧 $v_{b2}$ が印加され、ソースが前記第3ノードa3及び第7ノードa7にそれぞれ連結され、ドレインが第4ノードa4及び第8ノードa8にそれぞれ連結される。前記第4及び第6NMOSトランジスタMN4、MN6は、ゲートに第3バイアス電圧 $v_{b3}$ が提供され、ソースが前記第6ノードa6及び第10ノードa10にそれぞれ連結され、ドレインが第5ノードa5及び第9ノードa9にそれぞれ連結される。前記第9及び第10PMOSトランジスタMP9、MP10は、ゲートに第5バイアス電圧 $v_{b5}$ が印加され、ソースが前記第4ノードa4及び第8ノードa8にそれぞれ連結され、ドレインが前記第5ノードa5及び第9ノードa9にそれぞれ連結される。前記第9及び第10NMOSトランジスタMN9、MN10は、ゲートに第6バイアス電圧 $v_{b6}$ が印加され、ドレインが前記第4ノードa4及び第8ノードa8にそれぞれ連結され、ソースが前記第5ノードa5及び第9ノードa9にそれぞれ連結される。

#### 【0032】

前記出力部35は、第8PMOSトランジスタMP8及び第8NMOSトランジスタMN8と、第1及び第2キャパシタC1、C2とを備える。前記第8PMOSトランジスタMP8及び第8NMOSトランジスタMN8は、ゲートがそれぞれ第8ノードa8と第9ノードa9とに連結され、ソースがそれぞれ第1電源端子Vdd及び第2電源端子Vssにそれぞれ連結され、ドレインが出力端子outに共通連結される。前記第8PMOSトランジスタMP8及び第8NMOSトランジスタMN8のゲートには、それぞれ第8ノードa8及び第9ノードa9を通じてプルアップ信号pu及びプルダウン信号pdが提供される。前記第1及び第2キャパシタC1、C2は、一端がそれぞれ第7ノードa7と第10ノードa10とに連結され、他端が前記出力端子outに共通連結される。

#### 【0033】

前記イネーブル部36は、前記増幅部を構成する信号入力部31をイネーブルさせるための第3PMOSトランジスタMP3と第3NMOSトランジスタMN3とを備える。前記第3PMOSトランジスタMP3と第3NMOSトランジスタMN3とは、ゲートに第1バイアス電圧 $v_{b1}$ と第4バイアス電圧 $v_{b4}$ とがそれぞれ印加され、ソースは、それぞれ第1電源端子Vddと第2電源端子Vssとに連結され、ドレインがそれぞれ第1ノードa1と第2ノードa2とに連結される。前記第1ないし第6バイアス電圧 $v_{b1} \sim v_{b6}$ は、外部から提供される一定電圧である。

#### 【0034】

前記各出力バッファ351～35nは、第1差動入力信号 $i_{np}$ と第2差動入力信号 $i_{nn}$ とを入力し、前記第1バイアス電圧 $v_{b1}$ 及び前記第4バイアス電圧 $v_{b4}$ によって前記第3PMOSトランジスタMP3及び第3NMOSトランジスタMN3をイネーブルさせる。前記増幅部は、第1差動入力信号 $i_{np}$ と第2差動入力信号 $i_{nn}$ とを差動増幅して、前記第7ノードa7及び第10ノードa10に提供する。前記増幅選択部34は、第5及び第6バイアス電圧 $v_{b5}$ 、 $v_{b6}$ が印加される第10PMOSトランジスタMP10及び第10NMOSトランジスタMN10によって前記増幅部の増幅等級を決定して、プルアップ信号pu及びプルダウン信号pdを前記出力部35に提供する。前記出力部35は、前記プルアップ信号pu及びプルダウン信号pdによって、前記第8PMOSトランジスタMP8及び第8NMOSトランジスタMN8が駆動されて出力信号outを発生させる。

#### 【0035】

図示されてはいないが、前記ソースドライバ30は、液晶パネル10を反転駆動方式、例えば、ドット反転駆動方式を利用して駆動する場合、前記デジタルアナログ変換部34

10

20

30

40

50

0は、階調電圧信号D A C 1～D A C nとしてポジティブ階調電圧信号とネガティブ階調電圧信号とを前記出力バッファ部350に提供する。したがって、前記ソースドライバ30は、極性反転制御部をさらに備えて、極性反転制御部が前記デジタルアナログ変換部340から提供されるポジティブ階調電圧信号とネガティブ階調電圧信号とのうち一つが前記各出力バッファ351～35nに提供されるように制御することができる。

#### 【0036】

前記各出力バッファ351～35nの出力信号outで発生する出力偏差は、各出力バッファ351～35nを構成するMOSトランジスタのしきい電圧Vthの不均一に起因するが、前記しきい電圧Vthの偏差を数式で表現すれば、次の通りである。

#### 【0037】

#### 【数1】

$$S(\Delta Vth) = \frac{Avt}{\sqrt{W \times L}} = \frac{q \times \sqrt{Nt}}{Cox \times \sqrt{W \times L}}$$

#### 【0038】

数式1において、Ntは、チャネル領域のドーピング濃度を示し、Coxは、ゲート絶縁膜のキャパシタンスを示し、W及びLは、それぞれMOSトランジスタの幅及び長さを示す。qは、電荷量である。

#### 【0039】

前記数式1から、MOSトランジスタの幅と長さが同一であり、チャネル領域のドーピング濃度が同一であれば、しきい電圧Vthの偏差S(Vth)は、ゲート絶縁膜の厚さによって変化するということが分かる。したがって、ゲート絶縁膜の厚さが大きければ大きいほど、しきい電圧Vthの偏差S(Vth)が増加するということが分かる。

#### 【0040】

前記出力バッファ351～35nを構成するMOSトランジスタの各ノードの電圧を表1に示す。表1は、電源電圧Vddが12Vである場合、各入力電圧Vin、すなわち、第1差動入力信号inpの電圧レベルによる各ノードの電圧を示す。各出力バッファ351～35nの出力信号outの出力偏差に大きく影響を及ぼすのは、前記出力バッファを構成する複数のトランジスタMP1～MP10、MN1～MN10のうち、低い動作電圧を有するトランジスタである。例えば、電源電圧Vddが12Vである場合、出力偏差に大きく影響を及ぼすトランジスタは、12Vの電源電圧と0Vの接地電圧とに対して2V以下の動作領域を有するトランジスタである。入力電圧Vinに関係なく2V以下の動作電圧を維持するノードは、a3、a6、a7、a10となる。すなわち、第3ノードa3及び第7ノードa7に連結される第1電流ミラー32のPMOSトランジスタMP5、MP7は、12Vの電源電圧の動作電圧に対して2V以下の低い動作電圧を有する。一方、ノードa6及びa10は、接地電圧に対して2V以下の低い動作電圧を維持する。第6ノードa6及び第10ノードa10に連結される第2電流ミラー33のNMOSトランジスタMN5、MN7は、0Vの接地電圧に対して2V以下の動作電圧を有する。しかし、ノードa5及びa9は、電源電圧及び接地電圧に対して2V以下の低い動作電圧を維持しない。

#### 【0041】

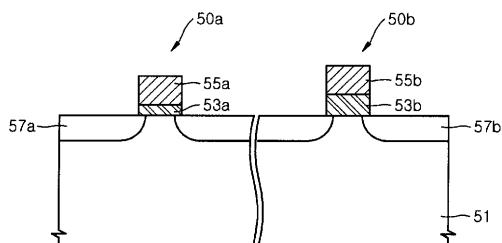

出力バッファ351～35nの出力信号outの出力偏差を減少させるためには、前記ノードa3、a6、a7、a10に連結された第5及び第7PMOSトランジスタMP5、MP7及び第5及び第7NMOSトランジスタMN5、MN7は、ゲート絶縁膜の厚さを残りのトランジスタに比べて薄く形成することが望ましい。したがって、図5に示すように、各出力バッファを構成するMOSトランジスタのうち、低い動作電圧を有する前記第5及び第7PMOSトランジスタMP5、MP7及び第4及び第5NMOSトランジスタMN5、MN7は、薄膜のゲート絶縁膜を有する低電圧トランジスタ50aで構成し

10

20

30

40

50

、残りのトランジスタは、厚膜のゲート絶縁膜を有する高電圧トランジスタ 50b で構成する。

【0042】

【表1】

| 入力電圧<br>ノード | 0. 2V  | 4V     | 11. 8V | 8V     |

|-------------|--------|--------|--------|--------|

| a 1         | 3. 95  | 6. 91  | 12. 00 | 9. 93  |

| a 2         | 0      | 1. 95  | 7. 63  | 4. 80  |

| a 3         | 10. 98 | 10. 95 | 10. 95 | 10. 95 |

| a 4         | 10. 59 | 10. 54 | 10. 53 | 10. 54 |

| a 5         | 1. 53  | 1. 46  | 1. 36  | 1. 46  |

| a 6         | 0. 45  | 0. 47  | 0. 47  | 0. 47  |

| a 7         | 11. 11 | 11. 06 | 11. 04 | 11. 06 |

| a 8         | 11. 05 | 11. 00 | 10. 97 | 10. 99 |

| a 9         | 1. 11  | 1. 12  | 1. 03  | 1. 08  |

| a 10        | 0. 45  | 0. 47  | 0. 47  | 0. 47  |

10

20

30

【0043】

図5を参照すれば、低電圧トランジスタ 50a は、基板 51 上に形成された薄膜のゲート絶縁膜 53a、ゲート電極 55a、及びソース／ドレイン領域 57a を備える。一方、高電圧トランジスタ 50b は、前記基板 51 上に形成された厚膜のゲート絶縁膜 53b、ゲート電極 55b 及びソース／ドレイン領域 57b を備える。前記低電圧トランジスタ 50a のゲート絶縁膜 53a の厚さは、前記高電圧トランジスタ 50b のゲート絶縁膜 53b より薄い。前記各出力バッファ 351～35n を構成するMOSトランジスタの構造は、図5に限定されず、多様な構造を有することができる。

【0044】

前記ソースドライバ 30 が、前記液晶パネル 10 のセルアレイと共に集積される場合、前記基板 51 は、ガラス基板、プラスチック基板または金属基板のような平板表示パネルの製造に使われる基板を含み、低電圧トランジスタ 50a 及び高電圧トランジスタ 50b は、例えば、低温ポリシリコン工程を利用したN型またはP型薄膜トランジスタとして具現する。一方、前記ソースドライバ 30 が、前記液晶パネル 10 のセルアレイとは別途に製作される場合には、前記基板 51 は、シリコン基板のような半導体集積回路の製造に使われる半導体基板を含み、前記低電圧トランジスタ 50a 及び高電圧トランジスタ 50b は、一般的なMOSトランジスタとして具現する。

40

【0045】

本発明の実施形態において、各出力バッファ 351～35n を構成するMOSトランジスタのうち、低電圧MOSトランジスタとして具現される動作領域の範囲は、12Vの電源電圧において2V以下に限定されるものではなく、多様な値を有してもよい。

【0046】

以上、本発明を望ましい実施形態を挙げて詳細に説明したが、本発明は、前記実施形態に限定されず、本発明の技術的思想の範囲内で当業者によって多様な変形が可能である。

【産業上の利用可能性】

50

## 【0047】

本発明は、表示装置関連の技術分野に好適に用いられる。

## 【図面の簡単な説明】

## 【0048】

【図1】本発明の薄膜トランジスタ液晶表示装置（TFT-LCD）の構成図である。

【図2】本発明の薄膜トランジスタ液晶表示装置用ソースドライバの概略的な構成図である。

【図3】本発明の薄膜トランジスタ液晶表示装置用ソースドライバの出力バッファ部の構成図である。

【図4】本発明の薄膜トランジスタ液晶表示装置用ソースドライバの出力バッファの一例 10

を示す図である。

【図5】図4に示す出力バッファを構成するトランジスタの断面図である。

## 【符号の説明】

## 【0049】

|             |             |    |

|-------------|-------------|----|

| 1 0         | 液晶パネル       | 20 |

| 1 1         | 液晶セル        |    |

| 2 0         | ゲートドライバ     |    |

| 3 0         | ソースドライバ     |    |

| 3 1         | 信号入力部       |    |

| 3 2         | 第1電流ミラー     |    |

| 3 3         | 第2電流ミラー     |    |

| 3 4         | 增幅選択部       |    |

| 3 5         | 出力部         |    |

| 3 6         | イネーブル部      |    |

| 4 0         | 制御部         |    |

| 5 0 a       | 低電圧トランジスタ   |    |

| 5 0 b       | 高電圧トランジスタ   |    |

| 5 1         | 基板          |    |

| 5 3 a、5 3 b | ゲート絶縁膜      | 30 |

| 5 5 a、5 5 b | ゲート電極       |    |

| 5 7 a、5 7 b | ソース／ドレイン領域  |    |

| 3 1 0       | シフトレジスタ部    |    |

| 3 2 0、3 3 0 | ラッチ部        |    |

| 3 4 0       | デジタルアナログ変換部 |    |

| 3 5 0       | 出力バッファ部     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

## フロントページの続き

(51)Int.Cl.

F I

|         |        |         |

|---------|--------|---------|

| G 0 9 G | 3/20   | 6 8 0 G |

| G 0 9 G | 3/20   | 6 1 2 E |

| G 0 9 G | 3/20   | 6 2 3 G |

| G 0 9 G | 3/20   | 6 2 3 F |

| G 0 9 G | 3/20   | 6 4 1 C |

| G 0 9 G | 3/20   | 6 1 1 H |

| G 0 9 G | 3/20   | 6 4 2 A |

| G 0 2 F | 1/1345 |         |

| G 0 2 F | 1/133  | 5 5 0   |

| G 0 2 F | 1/133  | 5 7 5   |

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 張 東烈

大韓民国京畿道水原市靈通區靈通洞 1153 番地 灵通アイパークアパートウエスト棟 2602 號

(72)発明者 李 受哲

大韓民国ソウル特別市江南區道谷 1 洞 895-8 番地 驛三韓信アパート 1 洞 603 號

審査官 高橋 義昭

(56)参考文献 特開2001-015609 (JP, A)

特開2003-188652 (JP, A)

特開2005-260168 (JP, A)

特開2005-321510 (JP, A)

特開平06-326529 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| H 0 3 F | 3 / 4 5     |

| G 0 2 F | 1 / 1 3 3   |

| G 0 2 F | 1 / 1 3 4 5 |

| G 0 9 G | 3 / 2 0     |

| G 0 9 G | 3 / 3 6     |