(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294422

(P2005-294422A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 21/28

H01L 21/288

H01L 21/3205

H01L 21/8234

F 1

H01L 29/78

H01L 21/28

H01L 21/288

H01L 27/08

H01L 27/08

301G

A

Z

331E

102C

テーマコード(参考)

4M104

5F033

5F048

5F140

審査請求 有 請求項の数 5 O L (全 19 頁) 最終頁に続く

(21) 出願番号

特願2004-105301 (P2004-105301)

(22) 出願日

平成16年3月31日 (2004.3.31)

(出願人による申告) 国等の委託研究の成果に係る特許出願(平成15年度新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基盤技術開発」委託研究、産業活力再生特別措置法第30条の適用を受けるもの)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100080001

弁理士 筒井 大和

(72) 発明者

門島 勝

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】 MISトランジスタのゲート電極の材料に金属を用いた場合に、熱プロセスによって、金属とゲート絶縁膜とが反応すること、あるいは、剥離することを防止し、かつ、MISトランジスタのしきい値の制御を可能にする。

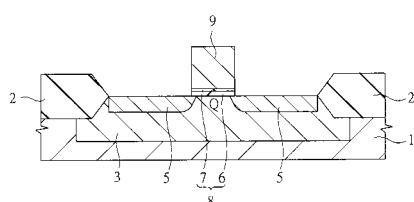

【解決手段】 半導体基板1と、半導体基板1上に形成されたゲート絶縁膜8と、ゲート絶縁膜8上に形成され、第1金属(例えば、タンタル)を含む材料(例えば、窒化タンタル膜)よりなるゲート電極9とを有し、ゲート絶縁膜8は、第1絶縁物(例えば、酸化シリコン膜)6と第2絶縁物(例えば、酸化タンタル層)7とからなり、第2絶縁物7は、第1金属と同一種類の第2金属の酸化物層とする。

【選択図】 図1

図1

1: 半導体基板

6: 第1絶縁物(酸化シリコン膜)

7: 第2絶縁物(酸化タンタル層)

8: ゲート絶縁膜

9: ゲート電極(窒化タンタル膜)

Q: MISトランジスタ(p型MISトランジスタ)

## 【特許請求の範囲】

## 【請求項 1】

金属を含む材料からなる導電体膜で形成されたゲート電極を有するMISトランジスタを備える半導体装置であって、

前記MISトランジスタのゲート絶縁膜は、前記ゲート電極との界面に、前記金属の酸化物からなる層を有することを特徴とする半導体装置。

## 【請求項 2】

第1ゲート電極および第1ゲート絶縁膜を含む第1MISトランジスタと、第2ゲート電極および第2ゲート絶縁膜を含む第2MISトランジスタと、を備える半導体装置であって、

前記第1ゲート電極および前記第2ゲート電極は、金属を含む材料からなる同一の導電体膜で形成され、

前記第1ゲート絶縁膜は、前記第1ゲート電極との界面に、前記金属の酸化物からなる層を有することを特徴とする半導体装置。

## 【請求項 3】

請求項2記載の半導体装置であって、

前記金属の酸化物からなる層の厚さは、0.1nm以上、2.0nm以下であることを特徴とする半導体装置。

## 【請求項 4】

金属を含む材料からなる導電体膜で形成されたゲート電極と、第1絶縁物および第2絶縁物を含むゲート絶縁膜と、を有するMISトランジスタを備える半導体装置の製造方法であって、

(a) 半導体基板の主面上にダミー電極を形成する工程と、

(b) 前記ダミー電極に自己整合で、前記半導体基板内の領域に不純物拡散領域を形成する工程と、

(c) 前記ダミー電極を除去する工程と、

(d) 前記不純物拡散領域を活性化する工程と、

(e) 前記半導体基板の主面上に前記第1絶縁物を形成する工程と、

(f) 前記第1絶縁物上に、前記第2絶縁物となる、前記金属の酸化物からなる層を形成する工程と、

(g) 前記第2絶縁物を高温で熱処理する工程と、

(h) 前記第2絶縁物上に、前記ゲート電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

## 【請求項 5】

第1ゲート電極と、第1絶縁物および第2絶縁物を含む第1ゲート絶縁膜と、を有する第1MISトランジスタと、

第2ゲート電極と、前記第1絶縁物を含む第2ゲート絶縁膜と、を有する第2MISトランジスタと、

を備える半導体装置の製造方法であって、

(a) 半導体基板の主面上に前記第1MISトランジスタの第1ダミー電極、および、第2MISトランジスタの第2ダミー電極を形成する工程と、

(b) 前記第1ダミー電極に自己整合で、前記半導体基板内の第1領域に第1不純物拡散領域を形成する工程と、

(c) 前記第2ダミー電極に整合して、前記半導体基板内の第2領域に第2不純物拡散領域を形成する工程と、

(d) 前記第1ダミー電極および前記第2ダミー電極を除去する工程と、

(e) 前記第1不純物拡散領域および前記第2不純物拡散領域を活性化する工程と、

(f) 前記半導体基板の主面上に、前記第1MISトランジスタの前記第1絶縁物を形成する工程と、

(g) 前記半導体基板の主面上に、前記第2MISトランジスタの前記第1絶縁物を形

成する工程と、

(h) 前記第1MISトランジスタの前記第1絶縁物上に、前記第2絶縁物となる、第1金属の酸化物からなる層を形成する工程と、

(i) 前記第2絶縁物を高温で熱処理する工程と、

(j) 前記第1MISトランジスタの前記第2絶縁物上に、前記第1ゲート電極となる、前記第1金属と同一の第2金属を含む材料からなる導電体膜、を形成する工程と、

(k) 前記第2MISトランジスタの前記第1絶縁物上に、前記第2ゲート電極となる、前記第1金属と同一の第2金属を含む材料からなる導電体膜、を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、半導体装置およびその製造技術に関し、特に、MISトランジスタおよびその製造技術に適用して有効な技術に関するものである。

【背景技術】

【0002】

従来、シリコン(Si)基板を用いたCMOS(Complementary Metal Oxide Semiconductor)トランジスタのnチャネル型のMISトランジスタ(以下、n型MISトランジスタ)とpチャネル型のMISトランジスタ(以下、p型MISトランジスタ)の両方において、n型MISトランジスタとp型MISトランジスタのゲート電極材料にポリシリコン膜が用いられている。このポリシリコン膜に対して、それぞれn型不純物とp型不純物を導入することにより、n型MISトランジスタのゲート電極材料の仕事関数(フェルミ準位)をSiの伝導帯近傍(4.05eV近傍)にするとともにp型MISトランジスタのゲート電極材料の仕事関数(フェルミ準位)をSiの価電子帯近傍(5.17eV近傍)にして、それぞれのMISトランジスタのしきい値電圧の低下を図っている。

20

【0003】

しかし、近年CMOSトランジスタの微細化に伴い、ゲート絶縁膜の薄膜化が進み、ポリシリコン膜をゲート電極に使用した場合におけるゲート電極の空乏化が無視できなくなっている。すなわち、微細化によって、酸化シリコン(SiO<sub>2</sub>)膜等よりなるゲート絶縁膜の酸化シリコン換算膜厚を2.0nm以下程度にすることが必要となるが、ゲート電極の空乏化によりゲート電極内に生じる寄生容量が、ゲート絶縁膜の容量に対して直列に形成されるため、ゲート容量が著しく低下することになる。したがって、ポリシリコン膜ではなく、ゲート電極材料に金属膜(メタルゲート)を使用することが検討されている(例えば、特許文献1および2参照)。

30

【特許文献1】特開2001-203276号公報

【特許文献2】特開2002-118175号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、n型MISトランジスタおよびp型MISトランジスタ、それぞれのゲート電極材料に仕事関数等が同一種類の金属を用いる場合(シングルメタルゲート)は、それぞれのゲート電極に仕事関数等が異なる金属を用いる場合(デュアルメタルゲート)と比較して、工程数などの点から有利である。シングルメタルゲートにおいて、閾値低減のために、n又はp型MISトランジスタの一方のゲート電極にイオン注入を行う方法があるが、以下のような問題があると考えられる。

40

【0005】

同一種類の金属からなる導電体膜(金属膜)を形成し、その後n型あるいはp型どちらか一方のMISトランジスタのゲート電極となる導電体膜にイオン注入することで、n型MISトランジスタのゲート電極と、p型MISトランジスタのゲート電極の仕事関数とを異ならせるようにする。しかし、イオン注入によるダメージによって、ゲート絶縁膜等

50

の信頼性が低下するという問題が考えられる。

【0006】

C M O Sトランジスタの製造工程は、通常、ゲート電極形成後に、ソース領域およびドレイン領域（不純物拡散領域）、を形成し、そのソース領域およびドレイン領域を形成する際には、イオン注入法で導入された不純物の活性化のため、高温の熱処理（活性化アニール）が行われる。C M O Sトランジスタにデュアルメタルゲートを用いた場合、この活性化アニールによって、n型側に用いられる金属材料（4.05eV近傍の仕事関数を有する金属材料）は、熱的安定性に乏しいためゲート絶縁膜と反応したり、p型側に用いられる金属材料（5.17eV近傍の仕事関数を有する金属材料）は、ゲート絶縁膜と密着性が悪いため剥離したり、さらには、ゲート絶縁膜、半導体基板へ金属原子が拡散してしまい、M I Sトランジスタの電気的特性が劣化するという問題が考えられる。

10

【0007】

本発明の目的は、M I Sトランジスタの信頼性や特性を向上させることができ半導体装置およびその製造技術を提供することにある。

【0008】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

20

【0010】

本発明による半導体装置は、金属を含む材料からなる導電体膜で形成されたゲート電極を有するM I Sトランジスタを備える半導体装置であって、ゲート絶縁膜が、前記ゲート電極との界面に、前記金属と同一の金属の酸化物からなる層を有する、ことを特徴とするものである。

20

【0011】

また、本発明による半導体装置の製造方法は、金属を含む材料からなる導電体膜で形成されたゲート電極と、第1絶縁物および第2絶縁物を含むゲート絶縁膜と、を有するM I Sトランジスタを備えた半導体装置の製造方法であって、前記半導体基板の主面上にダミー電極を形成する工程と、前記ダミー電極に自己整合で前記半導体基板内の領域に不純物拡散領域を形成する工程と、前記ダミー電極を除去する工程と、前記不純物拡散領域を活性化する工程と、前記半導体基板の主面上に前記第1絶縁物を形成する工程と、前記第1絶縁物上に、前記第2絶縁物となる、前記金属と同一の金属の酸化物からなる層を形成する工程と、前記第2絶縁物を高温で熱処理する工程と、前記第2絶縁物上に前記ゲート電極を形成する工程と、を有することを特徴とするものである。

30

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

40

【0013】

ゲート絶縁膜等の信頼性を向上することができ、かつ、M I Sトランジスタのしきい値を制御することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0015】

（実施の形態1）

50

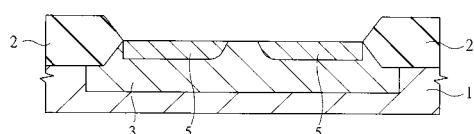

本発明の実施の形態1では、しきい値電圧を抑制することができるMISトランジスタ、および、その製造方法について図1～図5を用いて説明する。

【0016】

図1は、本実施の形態1におけるMISトランジスタQの断面図である。半導体基板1上には素子を分離するための素子分離領域2が形成されており、この素子分離領域2で分離された活性領域には、p型あるいはn型のウェル3が形成されている。このウェル3内には、不純物拡散領域5が形成される。

【0017】

このウェル3上には、MISトランジスタQが形成されている。このMISトランジスタQを構成するゲート絶縁膜8は、第1絶縁物6および第2絶縁物7を有しており、この第2絶縁物7は、第1絶縁物6上に形成されている。

【0018】

この第1絶縁物6は、例えば、酸化シリコン( $SiO_2$ )膜であり、第2絶縁物7は、金属の酸化物からなる層であり、例えば、酸化タンタル( $TaO_x$ )層である。なお、本実施の形態1では、第1絶縁物6に、酸化シリコン膜を用いたが、窒化シリコン( $SiN$ )膜、酸窒化シリコン( $SiON$ )膜であっても良い。

【0019】

また、第2絶縁物7は、ゲート電極材料の構成元素となる希土類金属の酸化物層であり、本実施の形態1では、タンタルの酸化物( $TaO_x$ )から形成されている。なお、第2絶縁物7の厚さは、MISトランジスタQを微細化する観点から、0.1nm～2.0nm程度であることが望ましい。

【0020】

このゲート絶縁膜8上には、ゲート電極9が形成されている。このゲート電極9は、金属を含む材料からなる導電体膜(金属膜)から形成され、本実施の形態1では、タンタル( $Ta$ )を含む電極材料となる窒化タンタル( $TaN$ )から形成されている。この窒化タンタルの仕事関数は、4.4eV程度であり、Siの伝導帯近傍(4.05eV近傍)と価電子帯近傍(5.17eV近傍)の間にあり、熱的安定性を備えているとともに、導電体膜としての密着性もよい。このため、TaN膜9が、ゲート絶縁膜8と反応したり、あるいは、剥離したり、さらには、金属原子( $Ta$ )が、ゲート絶縁膜8、半導体基板1へ拡散して、MISトランジスタQの電気的特性が劣化することを防止することができる。

【0021】

このように、本実施の形態1では、MISトランジスタQのゲート電極9の材料にTaN(窒化タンタル)を用いて、そのTaNを構成する金属であるTaと同一種類の金属(Ta)の酸化物層である酸化タンタル( $TaO_x$ )層(第2絶縁物7)と、酸化シリコン膜(第1絶縁物6)と、を含むゲート絶縁膜8を有するMISトランジスタQについて説明している。

【0022】

ここで、本実施の形態1で示す、酸化シリコン膜(第1絶縁物)6と酸化タンタル層(第2絶縁物)7とからなるゲート絶縁膜8を有するMISトランジスタQと、酸化シリコン膜(第1絶縁物)のみからなるゲート絶縁膜を有するMISトランジスタとの電気特性を比較したところ、本実施の形態1で示すMISトランジスタQのフラットバンド電圧が、酸化シリコン膜のみからなるゲート絶縁膜を有するMISトランジスタのフラットバンド電圧に対して、0.3V程度正方向にシフトさせることができた。よって、金属の酸化物層(本実施の形態1では、酸化タンタル層)を含む、あるいは、含まないゲート絶縁膜からなるMIS構造を選択することで、MISトランジスタのしきい値電圧を制御することができるといえる。なお、フラットバンド電圧が正方向にシフトする理由として、酸化タンタル層7とゲート電極9との界面に形成される電気的ダイポールや酸化タンタル層7中に存在する負の固定電荷が影響しているものと考えることができる。

【0023】

以上のことから、第1絶縁物(本実施の形態1では、酸化シリコン膜を示した)のみか

10

20

30

40

50

らなるゲート絶縁膜をn型MISトランジスタに、第1絶縁物（本実施の形態1では、酸化シリコン膜を示した）と第2絶縁物（本実施の形態1では、酸化タンタルを示した）とを含むゲート絶縁膜をp型MISトランジスタに適用することで、n型MISトランジスタとp型MISトランジスタとを備えた半導体装置を形成することができる。

## 【0024】

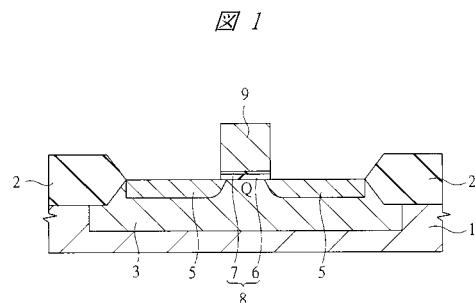

次に、MISトランジスタQの製造方法について、p型MISトランジスタに適用し、図面を参照しながら説明する。

## 【0025】

まず、図2に示すように、例えば、単結晶シリコンにボロン（B）などのp型不純物を導入した半導体基板1を用意する。次に、半導体基板1の主面上に素子分離領域2を形成する。素子分離領域2は、例えば、酸化シリコン膜よりなり、STI（Shallow Trench Isolation）法やLOCOS（Local Oxidation Of Silicon）法などによって形成される。図2では、窒化シリコン膜の耐酸化性を利用して半導体基板1の所定領域を選択酸化するLOCOS法によって形成された素子分離領域2を示している。

## 【0026】

続いて、半導体基板1内にn型ウェル3を形成する。n型ウェル3は、例えば、イオン注入法を使用して、リンやヒ素などのn型不純物を半導体基板1内に導入することにより形成される。

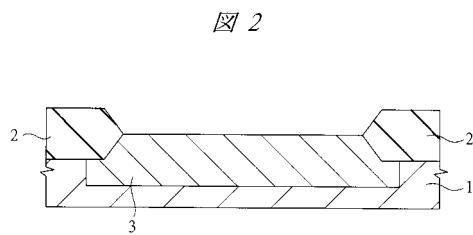

## 【0027】

続いて、図3に示すように、半導体基板1上に、例えば、CVD（Chemical Vapor Deposition）法を使用してポリシリコンやアモルファスシリコンのようなシリコン膜を形成した後、このシリコン膜に対して、露光・現像をすることによりパターニングし、半導体基板1上にダミー電極4を形成する。このときパターニングは、ダミー電極4を形成する領域にシリコン膜が残るようにする。なお、ダミー電極4を酸化シリコン膜から形成するようにしたが、これに限らず窒化シリコン膜、レジスト膜などから形成してもよい。

## 【0028】

続いて、ダミー電極4に、自己整合で半導体領域であるp型不純物拡散領域5を形成する。p型不純物拡散領域5は、例えば、イオン注入法を使用してボロンなどのp型不純物を半導体基板1内に導入することにより形成することができる。

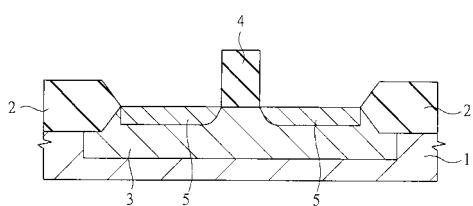

## 【0029】

次に、図4に示すように、ダミー電極4を除去して、半導体基板1を洗浄した後、p型不純物拡散領域5に導入した不純物を活性化するための活性化アニールを行う。この活性化アニールは、例えば、850～1050程度の高温で実施される。

## 【0030】

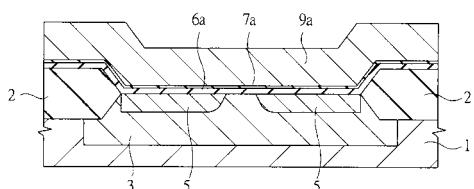

次に、図5に示すように、熱酸化法を使用して半導体基板1上に酸化シリコン膜6aを形成する。

## 【0031】

次に、酸化シリコン膜6a上に、原子層あるいは分子層レベルで堆積することができる方法、例えば、原子層制御成膜法（ALD：Atomic Layer Deposition法）を使用して、酸化タンタル層7aを5程度形成する。この酸化タンタル層7aの形成方法を以下に示す。

## 【0032】

まず、金属原料ガス、例えば、Ta（OC<sub>2</sub>H<sub>5</sub>）<sub>5</sub>を約300に加熱した半導体基板1に導入する。そして、窒素ガスにて排気した後、酸素反応ガスである水蒸気（H<sub>2</sub>O）を半導体基板1に導入し、窒素ガスで排気する。このようにして、約5の酸化タンタル層7aを形成する。なお、酸化タンタル層7aの形成に、ALD法を使用する例を示したが、これに限らず、間欠型CVD（Chemical Vapor Deposition）法などを使用して形成してもよい。

## 【0033】

続いて、酸素雰囲気中にて、この酸化タンタル層7aを高温、例えば、800程度で

10

20

30

40

50

アニール処理する。なお、本実施の形態1では、酸素雰囲気中でアニール処理を行ったが、不活性雰囲気中で行ってもよい。また、本実施の形態1では、酸化タンタル層7aを800程度でアニール処理を行ったが、熱処理温度は、600～900程度の範囲が好ましい。

【0034】

次に、例えば、CVD法を使用して、400～600程度に加熱された半導体基板1上に、窒化タンタル膜9aを形成する。なお、窒化タンタル膜9aの形成に、CVD法を使用する例を示したが、これに限らず、スパッタリング法、ALD法などを使用して形成してもよい。

【0035】

その後、図1に示したように、フォトリソグラフィ技術およびエッチング技術を使用して、酸化シリコン膜6および酸化タンタル層7からなるゲート絶縁膜8を形成し、このゲート絶縁膜8上に窒化タンタル膜9aよりなるゲート電極9を形成する。ここまで工程によってn型ウェル3にp型MISトランジスタQを形成することができる。

【0036】

また、本実施の形態1で示したMISトランジスタの製造方法では、ゲート電極9に高温の熱負荷が係らないため、以下に示すような効果が得られる。

【0037】

活性化アニール時のように高温の熱負荷が金属膜からなるゲート電極にかかると、ゲート電極とその下層に形成されているゲート絶縁膜が反応してしまい、反応により新たな絶縁物（酸化物）がゲート絶縁膜とゲート電極の間に形成される場合がある。この場合、ゲート電極の下層に形成されているゲート絶縁膜の膜厚が実質的に増加してしまい、駆動電流の低下やしきい値電圧の変動など、MISトランジスタの電気的特性が変動してしまうこととなる。しかし、本実施の形態1では、活性化アニールの後に金属膜よりなるゲート電極9を形成しているため、ゲート電極9には高温の熱負荷がかからず、ゲート電極9とゲート絶縁膜8との反応を防止することができる。したがって、本実施の形態1によれば、p型MISトランジスタQの電気的特性の変動を抑制することができる。

【0038】

また、ゲート電極に高温の熱負荷をかけると、ゲート電極に生ずる応力が増加するとともに界面における界面準位が増加する傾向が考えられる。しかし、本実施の形態1では、ゲート電極9の形成後に活性化アニールのような高温の熱処理を加えないため、応力の増加を抑制でき、応力や界面準位に起因したしきい値の変動およびキャリアの移動度の低下を抑制することができる。

【0039】

また、ゲート電極に高温の熱負荷をかけると、ゲート電極を構成する金属元素がゲート電極からゲート絶縁膜中や半導体基板内に拡散する場合がある。この場合、ゲート絶縁膜中に金属元素が拡散するとゲート絶縁膜の絶縁耐性が低下するとともにリーキ電流が増加すると考えられる。一方、ゲート絶縁膜を突き抜けて半導体基板内に金属元素が拡散すると、しきい値電圧の変動を引き起こすことになる。しかし、本実施の形態1ではゲート電極9の形成後に活性化アニールのような高温の熱処理を加えないため、ゲート電極9を形成する金属元素がゲート絶縁膜8や半導体基板1内へ拡散することを抑制することができる。

【0040】

また、ゲート絶縁膜上にゲート電極を形成し、ゲート電極に高温の熱負荷がかかると、MISトランジスタのしきい値がシフトする場合がある。この場合、熱負荷により、ゲート絶縁膜とゲート電極の界面に酸化物の層ができる、MISトランジスタのしきい値をシフトさせるものと考えられる。しかし、本実施の形態1ではゲート電極9の形成後に活性化アニールのような高温の熱処理を加えないため、しきい値をシフトさせることなく、安定したしきい値設定をすることができる。

【0041】

10

20

30

40

50

また、本実施の形態1では、ゲート電極9にタンタルを構成元素とする窒化タンタルを適用し、ゲート絶縁膜8にタンタルの酸化物である酸化タンタル層を含む構造とするMISトランジスタQを示し、このMISトランジスタQのフラットバンド電圧が、酸化タンタル層を含まない構造のMISトランジスタのそれに対し、正方向にシフトすることを例示した。一方、例えば、ゲート電極材料を構成する金属に、ニッケル(Ni)、コバルト(Co)を用いて、MISトランジスタQのゲート絶縁膜8に含まれる金属の酸化物層7に、酸化ニッケル(NiO)、酸化コバルト(CoO)を用いた場合には、これら金属の酸化物層を含まない構造のMISトランジスタのフラットバンド電圧に対し、負方向にシフトさせることができる。

【0042】

10

(実施の形態2)

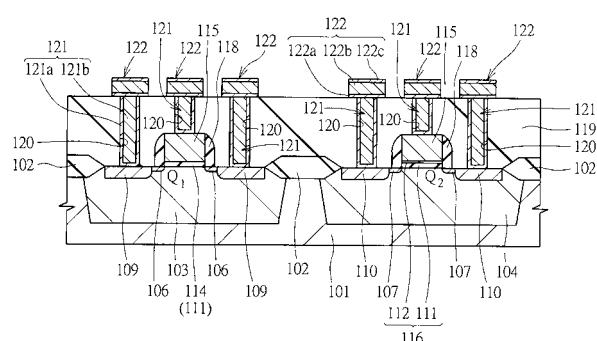

本発明の実施の形態2では、ゲート電極材料の構成元素となる金属と、同一の金属の酸化物層を有するゲート絶縁膜を備えたMISトランジスタ、および、その製造技術について、図6～図14を用いて説明する。

【0043】

20

図6は、本実施の形態2におけるn型MISトランジスタQ<sub>1</sub>およびp型MISトランジスタQ<sub>2</sub>を備えた半導体装置の断面図である。図6において、半導体基板101上には素子を分離するための素子分離領域102が形成されており、この素子分離領域102で分離された活性領域にはp型ウェル103とn型ウェル104とが形成されている。

【0044】

30

p型ウェル103上にはn型MISトランジスタQ<sub>1</sub>が形成されており、n型ウェル104上にはp型MISトランジスタQ<sub>2</sub>が形成されている。

【0045】

このn型MISトランジスタQ<sub>1</sub>は、例えば、酸化シリコン膜111よりなるゲート絶縁膜114を有しており、このゲート絶縁膜114上にゲート電極115を有している。このゲート電極115は、例えば、窒化タンタル(TaN)膜から構成されている。この窒化タンタルの仕事関数は、4.4eV程度であり、シリコンの伝導帯近傍(4.05eV近傍)と価電子帯近傍(5.17eV近傍)の間にあり、熱的安定性を備えているとともに膜の密着性もよい。なお、ゲート電極材料の例として、TaNを使用する例を示したが、これに限らず、Ta、TiN、Ti、HfN、Hf、ZrN、Zr、Alおよび希土類金属およびこれら金属材料中にSiを有する材料を使用することができる。

【0046】

40

また、ゲート電極115の側壁には、絶縁膜よりなるサイドウォール118が形成されており、サイドウォール118下のp型ウェル103内には半導体領域である低濃度n型不純物拡散領域106が形成されている。この低濃度n型不純物拡散領域106の外側には低濃度n型不純物拡散領域106より不純物密度が高い高濃度n型不純物拡散領域109が形成されている。低濃度n型不純物拡散領域106および高濃度n型不純物拡散領域109によりn型MISトランジスタQ<sub>1</sub>のソース領域およびドレイン領域が形成される。

【0047】

また、p型MISトランジスタQ<sub>2</sub>は、例えば、酸化シリコン膜111および金属の酸化物層(酸化金属物層)112からなるゲート絶縁膜116を有しており、このゲート絶縁膜116上にゲート電極115を有している。このゲート電極115は、n型MISトランジスタQ<sub>1</sub>と同一のゲート電極材料からなり、本実施の形態1では、窒化タンタル(TaN)膜から構成されている。また、酸化金属物層112は、ゲート電極材料の構成元素となる金属の酸化物層であり、本実施の形態1では、Taの酸化物層(酸化タンタル層)である。なお、酸化金属物層112の厚さは、MISトランジスタを微細化する観点から、例えば、0.1nm～2.0nm程度であることが望ましい。

【0048】

50

また、p型MISトランジスタQ<sub>2</sub>のゲート電極115の側壁には、絶縁膜よりなるサ

イドウォール 118 が形成されており、サイドウォール 118 下の n 型ウェル 104 内には半導体領域である低濃度 p 型不純物拡散領域 107 が形成されている。この低濃度 p 型不純物拡散領域 107 の外側には低濃度 p 型不純物拡散領域 107 より不純物密度が高い高濃度 p 型不純物拡散領域 110 が形成されている。低濃度 p 型不純物拡散領域 107 および高濃度 p 型不純物拡散領域 110 により p 型 MIS トランジスタ Q<sub>2</sub> のソース領域およびドレイン領域が形成される。

【0049】

また、半導体基板 101 に形成された n 型 MIS トランジスタ Q<sub>1</sub> および p 型 MIS トランジスタ Q<sub>2</sub> 上には、層間絶縁膜 119 が形成されており、この層間絶縁膜 119 には、n 型 MIS トランジスタ Q<sub>1</sub>、および、p 型 MIS トランジスタ Q<sub>2</sub> のソース領域、ドレイン領域に貫通するコンタクトホール 120 が形成されている。

【0050】

このコンタクトホール 120 の内壁には、チタン / 窒化チタン膜 121a が形成されており、このチタン / 窒化チタン膜 121a を介してコンタクトホール 120 にはタングステン膜 121b が埋め込まれ、プラグ 121 が形成されている。チタン / 窒化チタン膜 121a は、例えば、タングステンの拡散を抑制する機能および下地との密着性を向上させる機能を有している。

【0051】

また、層間絶縁膜 119 上には、チタン / 窒化チタン膜 122a、アルミニウム膜 122b、チタン / 窒化チタン膜 122c よりなるパターニングされた配線 122 が形成されている。なお、図示はしないが、配線上には、層間絶縁膜を貫通するプラグを介して多層配線が形成されている。

【0052】

以上述べたように、本実施の形態 2 で示す、n 型 MIS トランジスタ Q<sub>1</sub> と p 型 MIS トランジスタ Q<sub>2</sub> を備えた半導体装置において、酸化シリコン膜 111 のみからなるゲート絶縁膜 114 を n 型 MIS トランジスタに、酸化シリコン膜 111 と酸化タンタル層 112 を含むゲート絶縁膜 116 を p 型 MIS トランジスタに、適用することができる。

【0053】

また、本実施の形態 2 では、ゲート電極材料膜に対してイオン注入を行っていない。すなわち、n 型および p 型用のゲート電極材料膜を形成し、その後、一方の MIS トランジスタのゲート電極材料膜にイオン注入することで、n 型と p 型とのゲート電極の仕事関数とを異ならせるようなシングルメタルゲートで問題となる、イオン注入によるゲート絶縁膜等へのダメージの影響を受けることなく、MIS トランジスタのゲート絶縁膜を形成することができる。

【0054】

また、本実施の形態 2 で示した n 型 MIS トランジスタと p 型 MIS トランジスタとを備えた半導体装置は、別の種類の電極材料をそれぞれ n 型および p 型のゲート電極材料として、あるいは、同一種類の電極材料を処理して n 型および p 型のゲート電極材料として、用いていない。しかし、同一種類の材料を n 型および p 型のゲート電極材料とし、p 型あるいは n 型のゲート絶縁膜のゲート電極との界面に、金属の酸化物層を含むことで、例えば、CMOS トランジスタを提供することができる。

【0055】

また、本実施の形態 2 で示す、5 程度の厚さの酸化タンタル層 112 は、高誘電率の誘電体層でもあるため、酸化シリコン膜 111 と酸化タンタル層 112 とからなるゲート絶縁膜 116 の酸化シリコン換算膜厚 (EOT : Equivalent Oxide Thickness) の増加を抑えることができる。

【0056】

次に、上記の n 型 MIS トランジスタと p 型 MIS トランジスタとを備えた半導体装置の製造方法について、図面を参照しながら説明する。

10

20

30

40

50

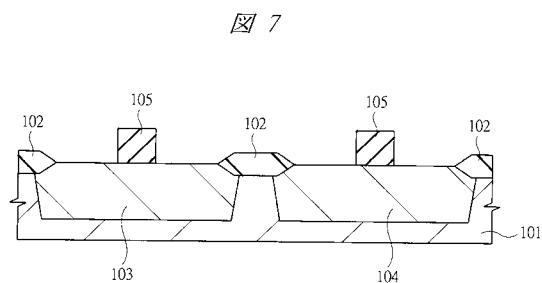

## 【0057】

まず、図7に示すように、例えば、単結晶シリコンにボロン(B)などのp型不純物を導入した半導体基板101を用意する。次に、半導体基板101の主面上に素子分離領域102を形成する。素子分離領域102は、例えば、酸化シリコンからなり、STI(Shallow Trench Isolation)法やLOCOS(Local Oxidization Of Silicon)法などによって形成される。図7では、窒化シリコン膜の耐酸化性を利用して半導体基板101の所定領域を選択酸化するLOCOS法によって形成された素子分離領域102を示している。

## 【0058】

続いて、半導体基板101内にp型ウェル103を形成する。p型ウェル103は、例えば、フォトリソグラフィ技術およびイオン注入法を利用して、ボロンやフッ化ボロンなどのp型不純物を半導体基板101内に導入することにより形成される。同様に、半導体基板101内にn型ウェル104を形成する。n型ウェル104は、例えば、フォトリソグラフィ技術およびイオン注入法を使用して、リンやヒ素などのn型不純物を半導体基板101内に導入することにより形成される。

## 【0059】

次に、半導体基板101の主面上に、例えば、CVD法を使用してポリシリコンやアモルファスシリコンのようなシリコン膜を形成した後、このシリコン膜に対して、露光・現像をすることによりパターニングし、半導体基板101上にダミー電極105を形成する。このときパターニングは、ダミー電極105を形成する領域にシリコン膜が残るようにする。なお、ダミー電極105をシリコン膜から形成するようにしたが、これに限らず窒化シリコン膜などから形成してもよい。

## 【0060】

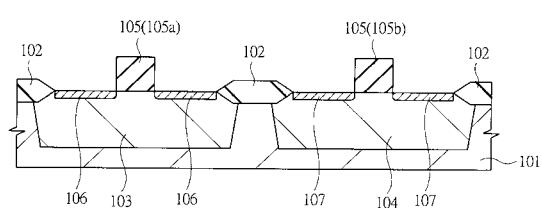

次に、図8に示すように、半導体基板101内であって、ダミー電極105aに整合して、半導体領域である低濃度n型不純物拡散領域106を形成する。低濃度n型不純物拡散領域106は、例えば、フォトリソグラフィ技術およびイオン注入法を使用して、リンやヒ素などのn型不純物を半導体基板101内に導入することにより形成することができる。同様に、ダミー電極105bに整合して、半導体領域である低濃度p型不純物拡散領域107を形成する。低濃度p型不純物拡散領域107は、例えば、フォトリソグラフィ技術およびイオン注入法を使用してボロンなどのp型不純物を半導体基板101内に導入することにより形成することができる。

## 【0061】

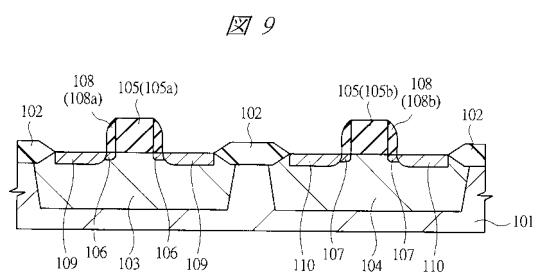

続いて、図9に示すように、半導体基板101の主面上に、例えば、プラズマCVD法を使用して窒化シリコン膜を形成した後、この窒化シリコン膜に対して異方性エッチングすることにより、ダミー電極105の側壁にサイドウォール108を形成する。なお、サイドウォール108を窒化シリコン膜より形成したが、これに限らず、例えば、酸化シリコン膜、酸窒化シリコン膜あるいは酸化シリコン膜と窒化シリコン膜との積層膜から形成しても良い。

## 【0062】

次に、サイドウォール108aに整合して、半導体基板101内の領域内に高濃度n型不純物拡散領域109を形成する。高濃度n型不純物拡散領域109は、例えば、フォトリソグラフィ技術およびイオン注入法を使用して形成され、低濃度n型不純物拡散領域106よりも高濃度にしてリンやヒ素などのn型不純物が導入されている。同様に、サイドウォール108bに整合して、半導体基板101内の領域に高濃度p型不純物拡散領域110を形成する。高濃度p型不純物拡散領域110は、例えば、フォトリソグラフィ技術およびイオン注入法を使用して形成され、低濃度p型不純物拡散領域107よりも高濃度にしてボロンなどのp型不純物が導入されている。

## 【0063】

次に、ダミー電極105、サイドウォール108は除去され、半導体基板101を洗浄した後、低濃度n型不純物拡散領域106、低濃度p型不純物拡散領域107、高濃度n

10

20

30

40

50

型不純物拡散領域 109 および高濃度 p 型不純物拡散領域 110 に導入した不純物を活性化するたの活性化アニールを行う。この活性化アニールは、例えば、850 ~ 1050 程度の高温で実施される。

#### 【0064】

上述した、ダミー電極 105 を形成し、このダミー電極 105 に整合して MIS トランジスタの低濃度 n 型不純物拡散領域 106 、低濃度 p 型不純物拡散領域 107 、高濃度 n 型不純物拡散領域 109 および高濃度 p 型不純物拡散領域 110 を形成した後、それら不純物拡散領域内の不純物を活性化するための活性化アニールを行う工程では、一般的な MIS トランジスタの製造方法のように、ゲート電極を形成した後に不純物の活性化アニールを行っていない。このため、一般的な半導体装置の製造方法では、活性化アニールによりゲート電極に高温の熱負荷がかかるが、本実施の形態 2 における半導体装置の製造方法では、後の工程で形成されるゲート電極に、高温の熱負荷をかけずに済むことができる。

#### 【0065】

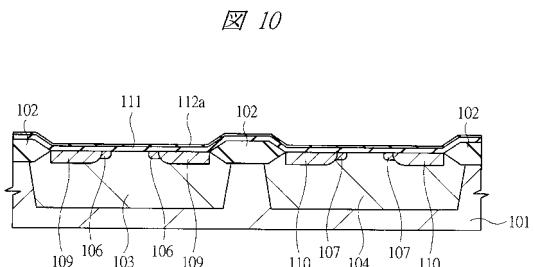

続いて、図 10 に示すように、熱酸化法を使用して、半導体基板 101 上に酸化シリコン膜 111 を形成する。

#### 【0066】

次に、酸化シリコン膜 111 上に、例えば、原子層制御成膜法 (ALD: Atomic Layer Deposition 法) を使用して、酸化金属物層である酸化タンタル (TaO<sub>x</sub>) 層 112a を 5 程度形成する。具体的には、タンタル (Ta) の原料ガス、例えば、Ta (OC<sub>2</sub>H<sub>5</sub>)<sub>5</sub> を約 300 に加熱した半導体基板 101 上に導入する。そして、窒素ガスにて Ta の原料ガスを排気した後、水蒸気 (H<sub>2</sub>O) を半導体基板 101 に導入し、窒素ガスで排気する。このようにして、5 程度の酸化タンタル層 112a を形成する。なお、酸化タンタル層 112a の形成に、ALD 法を使用する例を示したが、これに限らず、間欠型 CVD (Chemical Vapor Deposition) 法などを使用して形成してもよい。

#### 【0067】

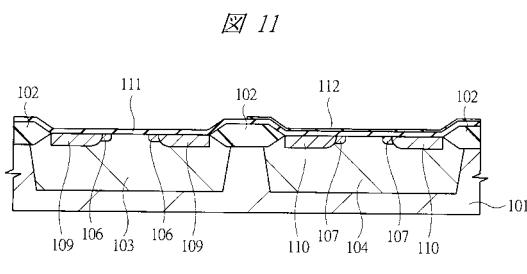

次に、図 11 に示すように、フォトリソグラフィ技術およびエッティング技術を使用して、酸化タンタル層 112a をエッティングし、p 型 MIS トランジスタ形成領域に酸化タンタル層 112 を形成する。

#### 【0068】

次に、酸素雰囲気中にて、この酸化タンタル層 112 を高温、例えば、800 程度でアニール処理する。なお、本実施の形態 2 では、酸素雰囲気中でアニール処理を行ったが、不活性雰囲気中で行ってもよい。また、本実施の形態 2 では、酸化タンタル層 112 を 800 程度でアニール処理を行ったが、熱処理温度は、600 ~ 900 程度の範囲が好ましい。

#### 【0069】

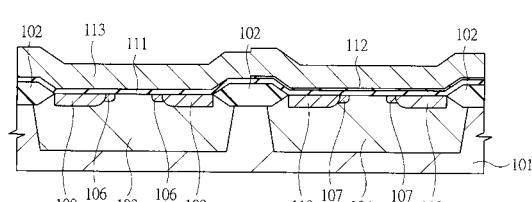

次に、図 12 に示すように、例えば、CVD 法を使用して、400 ~ 600 程度に加熱された半導体基板 101 上に、窒化タンタル膜 113 を形成する。なお、窒化タンタル膜 113 の形成に、CVD 法を使用する例を示したが、これに限らず、スパッタリング法、ALD 法などを使用して形成してもよい。

#### 【0070】

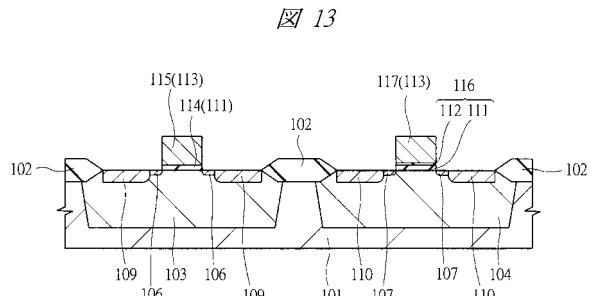

次に、図 13 に示すように、フォトリソグラフィ技術およびエッティング技術を使用して、n 型 MIS トランジスタ形成領域に、窒化タンタル 113 よりなるゲート電極 115 を形成し、このゲート電極 115 下に酸化シリコン膜 111 よりなるゲート絶縁膜 114 を形成する。また、p 型 MIS トランジスタ形成領域に、窒化タンタル 113 よりなるゲート電極 117 を形成し、このゲート電極 117 下に酸化タンタル層 112 および酸化シリコン膜 111 からなるゲート絶縁膜 116 を形成する。

#### 【0071】

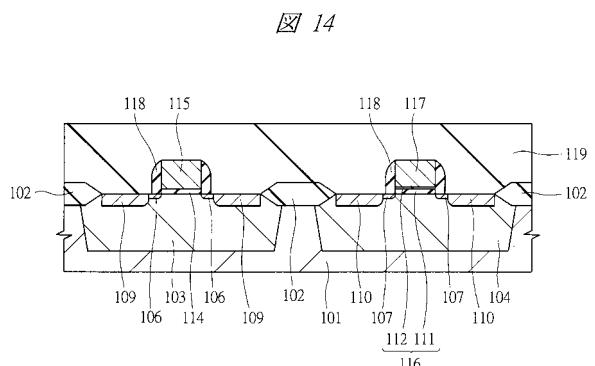

次に、図 14 に示すように、半導体基板 101 の主面上に、例えば、プラズマ CVD 法などを使用して半導体基板 101 上に窒化シリコン膜を形成した後、この窒化シリコン膜に対して異方性エッティングを行うことにより、サイドウォール 118 を形成する。

10

20

30

40

50

## 【0072】

次に、CVD法を使用して、半導体基板101の主面上に酸化シリコン膜よりなる層間絶縁膜119を形成した後、CMP法を使用して、表面を平坦化する。

## 【0073】

次に、図6に示すように、フォトリソグラフィ技術およびエッチング技術を使用して、層間絶縁膜119にコンタクトホール120を形成する。次いで、コンタクトホール120の底面、内壁および層間絶縁膜119上にチタン/窒化チタン膜121aを形成する。このチタン/窒化チタン膜121aは、チタン膜と窒化チタン膜の積層膜から形成され、例えば、スパッタリング法を使用することにより形成できる。

## 【0074】

次に、コンタクトホール120を埋め込むように、タンゲステン膜121bを形成する。タンゲステン膜121bは、例えば、CVD法を使用することにより形成することができる。そして、半導体基板101上に堆積された不要なチタン/窒化チタン膜121aおよびタンゲステン膜121bを、例えば、CMP法を使用して除去することにより、プラグ121を形成する。

## 【0075】

次に、層間絶縁膜119およびプラグ121上にチタン/窒化チタン膜122a、アルミニウム膜122b、チタン/窒化チタン膜122cを順次、形成する。これらの膜は、例えば、スパッタリング法を使用することにより形成できる。次いで、フォトリソグラフィ技術およびエッチング技術を使用することにより、これらの膜のパターニングを行い、配線122が形成される。

## 【0076】

このようにして、nチャネル型MISトランジスタQ<sub>1</sub>およびpチャネル型MISトランジスタQ<sub>2</sub>を形成することができる。なお、配線122の形成後、上述した層間絶縁膜119、プラグ121、配線122を形成する工程と同様の工程を繰り返すことにより、配線122の上部に多層に配線を形成し、最後にパッセーション膜で半導体基板101の全体を覆うことにより、CMOSデバイスが完成する。

## 【0077】

本実施の形態2で示したnチャネル型MISトランジスタQ<sub>1</sub>およびpチャネル型MISトランジスタQ<sub>2</sub>で異なるゲート絶縁膜構造を有する半導体装置とすることで、しきい値制御が可能となり、その結果消費電力の低い半導体装置を製造することができる。

## 【0078】

また、本実施の形態2で示したnチャネル型MISトランジスタQ<sub>1</sub>およびpチャネル型MISトランジスタQ<sub>2</sub>を有する半導体装置は、一般的に適用されるデュアルメタルゲート構造ではない。すなわち、本実施の形態2で示したnチャネル型MISトランジスタQ<sub>1</sub>およびpチャネル型MISトランジスタQ<sub>2</sub>を有する半導体装置の製造方法は、p型（あるいはn型）のゲート電極材料膜を形成し、次いで、n型（あるいはp型）のMISトランジスタが形成される領域内のゲート電極材料膜を選択的に除去し、その後、n型（あるいはp型）のゲート電極材料膜を形成する工程を含まない。このため、ゲート電極材料を除去する際のエッチング液やレジストを剥離する際の剥離液にゲート絶縁膜が晒されず、本実施の形態2における半導体装置の製造方法を適用することで、ゲート絶縁膜等の信頼性が大幅に向上することができる。

## 【0079】

（実施の形態3）

前記実施の形態2では、ゲート絶縁膜を構成する、金属の酸化物層を、原子層制御成膜法（ALD: Atomic Layer Deposition法）を使用して形成する例について説明したが、本実施の形態3では、金属膜を熱酸化することにより、金属の酸化物層を形成する例について説明する。

## 【0080】

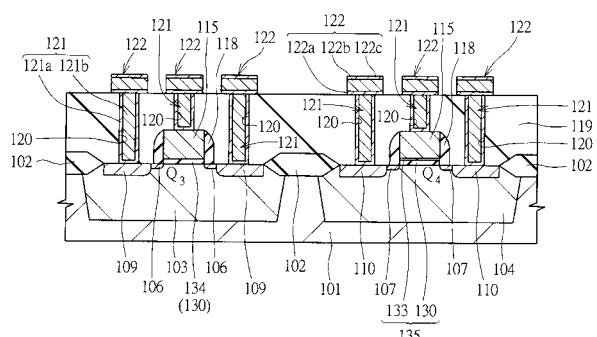

図15は、本実施の形態3におけるn型MISトランジスタQ<sub>3</sub>およびp型MISトラ

10

20

30

40

50

ンジスタ  $Q_4$  を示した断面図である。図 15において、n型MISトランジスタ  $Q_3$  および p型MISトランジスタのそれぞれの構成は、前記実施の形態2のn型MISトランジスタ  $Q_1$  および p型MISトランジスタ  $Q_2$  の構成とほぼ同様であるが、n型MISトランジスタ  $Q_3$  および p型MISトランジスタ  $Q_4$  を製造する方法において相違点があるため、以下説明する。

【0081】

まず、前記実施の形態2で示した図7～図9で示した工程までは同様である。

【0082】

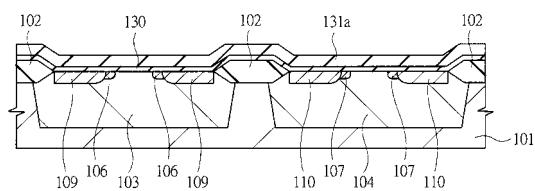

次に、図16に示すように、熱酸化法を使用して、半導体基板101上に酸化シリコン膜130を形成する。

10

【0083】

続いて、酸化シリコン膜130上に、例えば、プラズマCVD法を使用して窒化シリコン膜131aを形成する。

【0084】

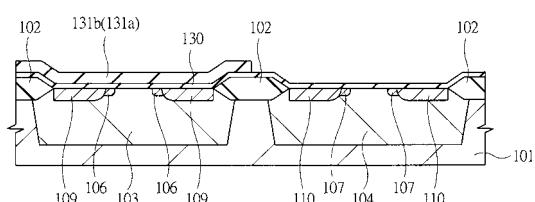

次に、図17に示すように、フォトリソグラフィ技術およびエッティング技術を使用して、p型MISトランジスタ  $Q_4$  領域の半導体基板101上の窒化シリコン膜131aを除去し、n型MISトランジスタ  $Q_3$  領域の半導体基板101上には窒化シリコン膜131a(131b)を残す。

20

【0085】

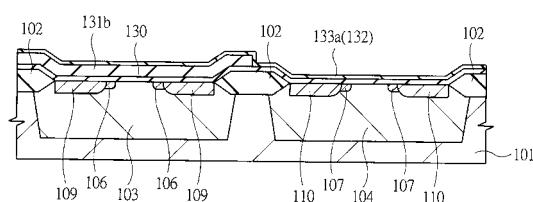

次に、図18に示すように、この半導体基板101上に、n型MISトランジスタ  $Q_3$  および p型MISトランジスタ  $Q_4$  のゲート電極材料(本実施の形態3では、TaNを示す)と同一種類の金属(本実施の形態3では、Taを示す)の金属物層132を、例えば、CVD法を使用して堆積する。

20

【0086】

次に、この金属物層132に熱酸化処理を800程度で行うことにより、金属の酸化物層(本実施の形態3では、酸化タンタル層を示す)133aが形成される。なお、本実施の形態3では、酸素雰囲気中に置かれた半導体基板101を800程度の熱処理で行ったが、熱処理温度は、600～1000程度の範囲が好ましい。

【0087】

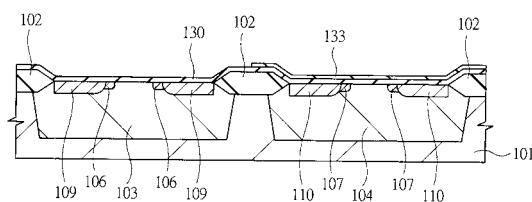

次に、図19に示すように、フォトリソグラフィ技術およびエッティング技術を使用して、酸化タンタル層133aをエッティングし、p型MISトランジスタ領域に酸化金属物層133を形成する。

30

【0088】

この後の工程は、前記実施の形態2で図12～図14および図6を用いて説明した工程と同様であり、それらの工程後、図15に示すように、n型MISトランジスタ  $Q_3$  および p型MISトランジスタ  $Q_4$  を形成することができる。なお、配線122の形成後、層間絶縁膜119、プラグ121、配線122を形成する工程と同様の工程を繰り返すことにより、配線122の上部に多層に配線を形成し、最後にパッセーション膜で半導体基板101の全体を覆うことにより、CMOSデバイスが完成する。

40

【0089】

本実施の形態3で示したnチャネル型MISトランジスタ  $Q_3$  のゲート絶縁膜134とp型MISトランジスタ  $Q_4$  のゲート絶縁膜135とを異なる構造とする半導体装置は、前記実施の形態2で示した半導体装置の効果と、同様の効果を得ることができる。

【0090】

また、酸化金属物層133を形成する工程は、ゲート電極材料(本実施の形態3では、TaN)と同一種類の金属(本実施の形態3では、Ta)の金属膜を、p型MISトランジスタ  $Q_4$  領域の酸化シリコン膜上に堆積させた後、熱酸化処理するため、酸化金属物層を形成する装置およびその工程が省略することができる。

【0091】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発

50

明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0092】

例えば、前記実施の形態1～3では、ゲート電極材料は、TaN(窒化タンタル)を用いたが、Ta、Ti、TiN、Hf、HfN、Zr、ZrN、Alおよび希土類金属、あるいは、これら金属材料中にSiを有する材料であってもよい。

【0093】

また、前記実施の形態2および前記実施の形態3では、n型MISトランジスタとp型MISトランジスタのゲート電極材料に同一種類の材料を使用し、p型MISトランジスタのゲート絶縁膜には、その金属材料の酸化物層を含み、n型MISトランジスタのゲート絶縁膜では、酸化物層を含まない構造としたが、p型MISトランジスタのゲート絶縁膜には、金属の酸化物層を含まず、n型MISトランジスタのゲート絶縁膜に、金属の酸化物層を含む構造としてもよい。例えば、ゲート電極材料を構成する金属に、ニッケル(Ni)、コバルト(Co)を用いて、p型MISトランジスタのゲート絶縁膜に含まれる金属の酸化物層に、酸化ニッケル(NiO)、酸化コバルト(CoO)を用いた場合である。

【0094】

また、前記実施の形態1～3では、酸化シリコン(第1絶縁膜)および酸化金属物層(第2絶縁膜)を含むゲート絶縁膜を使用したが、これに限らず、第1絶縁膜には、例えば、酸窒化シリコン(SiON)膜、また、第2絶縁膜には、例えば、Hf、Zr、Ta、Al、Ti、Nb、Sc、Y、La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、YbおよびLuからなる群から選ばれる少なくとも一種を含む金属シリケート層としてもよい。

【産業上の利用可能性】

【0095】

本発明は、半導体装置を製造する製造業に幅広く利用されるものである。

【図面の簡単な説明】

【0096】

【図1】本発明の実施の形態1における半導体装置を示した断面図である。

【図2】実施の形態1における半導体装置の製造工程を示した断面図である。

【図3】図2に続く半導体装置の製造工程を示した断面図である。

【図4】図3に続く半導体装置の製造工程を示した断面図である。

【図5】図4に続く半導体装置の製造工程を示した断面図である。

【図6】本発明の実施の形態2における半導体装置を示した断面図である。

【図7】実施の形態2における半導体装置の製造工程を示した断面図である。

【図8】図7に続く半導体装置の製造工程を示した断面図である。

【図9】図8に続く半導体装置の製造工程を示した断面図である。

【図10】図9に続く半導体装置の製造工程を示した断面図である。

【図11】図10に続く半導体装置の製造工程を示した断面図である。

【図12】図11に続く半導体装置の製造工程を示した断面図である。

【図13】図12に続く半導体装置の製造工程を示した断面図である。

【図14】図13に続く半導体装置の製造工程を示した断面図である。

【図15】本発明の実施の形態3における半導体装置を示した断面図である。

【図16】実施の形態3における半導体装置の製造工程を示した断面図である。

【図17】図16に続く半導体装置の製造工程を示した断面図である。

【図18】図17に続く半導体装置の製造工程を示した断面図である。

【図19】図18に続く半導体装置の製造工程を示した断面図である。

【符号の説明】

【0097】

- 2 素子分離領域

3 ウェル (n型ウェル)

4 ダミー電極

5 不純物拡散領域

6、6a 酸化シリコン膜

7、7a 酸化タンタル層

8 ゲート絶縁膜

9 ゲート電極

9a 窒化タンタル膜

101 半導体基板

102 素子分離領域

103 p型ウェル

104 n型ウェル

105、105a、105b ダミー電極

106 低濃度n型不純物拡散領域

107 低濃度p型不純物拡散領域

108、108a、108b サイドウォール

109 高濃度n型不純物拡散領域

110 高濃度p型不純物拡散領域

111 酸化シリコン膜

112、112a 酸化金属物層 (酸化タンタル層)

113 窒化タンタル膜

114 ゲート絶縁膜 (n型MISトランジスタのゲート絶縁膜)

115 ゲート電極 (n型MISトランジスタのゲート電極)

116 ゲート絶縁膜 (p型MISトランジスタのゲート絶縁膜)

117 ゲート電極 (p型MISトランジスタのゲート電極)

118 サイドウォール

119 層間絶縁膜

120 コンタクトホール

121a チタン/窒化チタン膜

121b タングステン膜

121 プラグ

122a チタン/窒化チタン膜

122b アルミニウム膜

122c チタン/窒化チタン膜

122 配線

130 酸化シリコン膜

131、131a、131b 窒化シリコン膜

132 金属物層

133、133a 酸化金属物層 (酸化タンタル層)

134 ゲート絶縁膜 (n型MISトランジスタのゲート絶縁膜)

135 ゲート絶縁膜 (p型MISトランジスタのゲート絶縁膜)

Q MISトランジスタ (p型MISトランジスタ)

Q<sub>1</sub> n型MISトランジスタ

Q<sub>2</sub> p型MISトランジスタ

Q<sub>3</sub> n型MISトランジスタ

Q<sub>4</sub> p型MISトランジスタ

【図1】

1: 半導体基板

6: 第1絶縁物 (酸化シリコン膜)

7: 第2絶縁物 (酸化タンタル層)

8: ゲート絶縁膜

9: ゲート電極 (窒化タンタル膜)

Q: MISトランジスタ (p型MISトランジスタ)

【図2】

【図3】

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【 図 17 】

【 18 】

【 図 1 9 】

## フロントページの続き

|                          |               |            |

|--------------------------|---------------|------------|

| (51)Int.Cl. <sup>7</sup> | F I           | テーマコード(参考) |

| H 0 1 L 21/8238          | H 0 1 L 27/08 | 1 0 2 D    |

| H 0 1 L 27/08            | H 0 1 L 27/08 | 3 2 1 D    |

| H 0 1 L 27/088           | H 0 1 L 27/08 | 3 2 1 F    |

| H 0 1 L 27/092           | H 0 1 L 21/88 | B          |

|           |       |      |      |      |      |      |      |      |      |      |      |

|-----------|-------|------|------|------|------|------|------|------|------|------|------|

| F ターム(参考) | 4M104 | AA01 | AA08 | AA09 | AA10 | BB02 | BB04 | BB06 | BB07 | BB08 | BB14 |

|           | BB16  | BB17 | BB18 | BB30 | BB36 | CC01 | CC05 | DD12 | DD21 | DD33 |      |

|           | DD37  | DD43 | DD51 | DD52 | DD53 | DD61 | DD62 | DD65 | EE03 | EE16 |      |

|           | EE17  | FF13 | FF18 | GG09 | GG10 | HH20 |      |      |      |      |      |

|           | 5F033 | GG04 | HH07 | HH08 | HH09 | HH10 | HH11 | HH18 | HH19 | HH20 | HH21 |

|           | HH31  | HH35 | MM05 | MM08 | MM13 | PP06 | PP15 | PP26 | PP27 | PP28 |      |

|           | QQ00  | QQ01 | QQ08 | QQ10 | QQ11 | QQ12 | RR01 | RR04 | RR06 | RR08 |      |

|           | RR11  | RR21 | RR22 | SS00 | SS07 | SS08 | SS15 | SS21 | VV06 | VV15 |      |

|           | XX33  | XX34 |      |      |      |      |      |      |      |      |      |

|           | 5F048 | AA09 | AC01 | AC04 | BA16 | BB01 | BB02 | BB04 | BB09 | BB11 | BB12 |

|           | BF01  | BF02 | BF07 |      |      |      |      |      |      |      |      |

|           | 5F140 | AA06 | AA08 | AA24 | AA27 | AA28 | AB03 | BA01 | BD01 | BD05 | BD07 |

|           | BD09  | BD12 | BD13 | BE07 | BE09 | BE17 | BF01 | BF05 | BF07 | BF08 |      |

|           | BF10  | BF59 | BG04 | BG08 | BG14 | BG27 | BG28 | BG30 | BG37 | BG43 |      |

|           | BG52  | BG53 | BH15 | BJ10 | BJ11 | BJ17 | BJ27 | BK02 | BK05 | BK13 |      |

|           | BK21  | BK25 | CA02 | CA03 | CB01 | CB04 | CB08 | CC03 | CE07 | CE20 |      |