(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-225614

(P2016-225614A)

(43) 公開日 平成28年12月28日(2016.12.28)

| (51) Int.Cl.                  | F 1                | テーマコード (参考) |

|-------------------------------|--------------------|-------------|

| <b>H01L 21/8247 (2006.01)</b> | H01L 27/10 4 3 4   | 5 F 0 8 3   |

| <b>H01L 27/115 (2006.01)</b>  | H01L 29/78 6 1 3 B | 5 F 1 0 1   |

| <b>H01L 29/786 (2006.01)</b>  | H01L 29/78 6 1 8 B | 5 F 1 1 0   |

| <b>H01L 21/336 (2006.01)</b>  | H01L 29/78 3 7 1   |             |

| <b>H01L 29/788 (2006.01)</b>  |                    |             |

審査請求 未請求 請求項の数 11 O L (全 30 頁) 最終頁に続く

|              |                              |          |                                                |

|--------------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2016-98070 (P2016-98070)   | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成28年5月16日 (2016.5.16)       | (72) 発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2015-106145 (P2015-106145) | (72) 発明者 | 熱海 知昭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成27年5月26日 (2015.5.26)       | (72) 発明者 | 遠藤 佑太<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (33) 優先権主張国  | 日本国 (JP)                     |          |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】集積度の高い半導体装置を提供する。

【解決手段】基板と、角柱状の絶縁体と、直列に接続された複数のトランジスタを有するメモリセルストリングと、を有し、角柱状の絶縁体は、基板上に配置され、メモリセルストリングは、角柱状の絶縁体の側面に配置され、複数のトランジスタは、それぞれゲート絶縁体と、ゲート電極と、を有し、ゲート絶縁体は、第1の絶縁体と、第2の絶縁体と、電荷蓄積層と、を有し、電荷蓄積層は、第1の絶縁体と第2の絶縁体と、の間に配置される半導体装置である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

基板と、角柱状の絶縁体と、直列に接続された複数のトランジスタを有するメモリセルストリングと、を有し、

前記角柱状の絶縁体は、前記基板上に配置され、

前記メモリセルストリングは、前記角柱状の絶縁体の側面に配置されることを特徴とする半導体装置。

**【請求項 2】**

基板と、角柱状の絶縁体と、複数の、直列に接続された複数のトランジスタを有するメモリセルストリングと、を有し、

前記角柱状の絶縁体は、前記基板上に配置され、

前記複数のメモリセルストリングは、前記角柱状の絶縁体の側面に配置されることを特徴とする半導体装置。

**【請求項 3】**

基板と、絶縁体と、直列に接続された複数のトランジスタを有するメモリセルストリングと、を有し、

前記絶縁体は、前記基板上に配置され、

前記メモリセルストリングは、前記絶縁体の側面に配置され、

前記複数のトランジスタは基板の上面に対する垂直方向に、互いに重なることを特徴とする半導体装置。

**【請求項 4】**

基板と、絶縁体と、第 1 乃至第 2 n トランジスタを有するメモリセルストリングと、を有し (n は 2 以上の整数)、

前記絶縁体は、前記基板上に配置され、

前記メモリセルストリングは、前記絶縁体の側面に配置され、

前記第 1 乃至第 n トランジスタのそれぞれのチャネル長方向は、基板の上面に対する垂直方向と平行であり、

前記第 1 乃至第 n トランジスタはそれぞれ直列に接続されることを特徴とする半導体装置。

**【請求項 5】**

請求項 4 において、

前記第 n + 1 乃至第 2 n トランジスタのそれぞれのチャネル長方向は、基板の上面に対する垂直方向と平行であり、

前記第 n + 1 乃至第 2 n トランジスタはそれぞれ直列に接続されることを特徴とする半導体装置。

**【請求項 6】**

請求項 5 において、

前記第 1 乃至第 n トランジスタと、前記第 n + 1 乃至第 2 n トランジスタが直列に接続されることを特徴とする半導体装置。

**【請求項 7】**

請求項 1 乃至請求項 6 のいずれか一において、

前記複数のトランジスタは、それぞれゲート絶縁体と、ゲート電極と、を有し、

前記ゲート絶縁体は、第 1 の絶縁体と、第 2 の絶縁体と、電荷蓄積層と、を有し、

前記電荷蓄積層は、前記第 1 の絶縁体と前記第 2 の絶縁体と、の間に配置されることを特徴とする半導体装置。

**【請求項 8】**

請求項 1 乃至請求項 7 のいずれか一において、

前記複数のトランジスタは、酸化物半導体を有することを特徴とする半導体装置。

**【請求項 9】**

請求項 8 において、

10

20

30

40

50

前記酸化物半導体は、インジウム、元素M（アルミニウム、ガリウム、イットリウムまたはスズ）および亜鉛を有することを特徴とする半導体装置。

【請求項 10】

請求項1乃至請求項9のいずれか一において、

さらに前記基板に配置された第 $2n+1$ のトランジスタと、第 $2n+2$ のトランジスタと、を有し、

前記第 $2n+1$ のトランジスタのソース端子は、前記メモリセルストリングの第1の端子と電気的に接続され、

前記第 $2n+2$ のトランジスタのドレイン端子は、前記メモリセルストリングの第2の端子と電気的に接続されることを特徴とする半導体装置。 10

【請求項 11】

請求項10において、

前記第 $2n+1$ のトランジスタおよび前記第 $2n+2$ のトランジスタは、単結晶シリコンを有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば、半導体、トランジスタおよび半導体装置に関する。または、本発明は、例えば、半導体、トランジスタおよび半導体装置の製造方法に関する。または、本発明は、例えば、半導体、表示装置、発光装置、照明装置、蓄電装置、記憶装置、プロセッサ、電子機器に関する。または、半導体、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の製造方法に関する。または、半導体装置、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の駆動方法に関する。 20

【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路および電子機器は、半導体装置を有する場合がある。 30

【背景技術】

【0004】

コンピュータなどに用いる大容量記憶装置として、半導体を用いた記憶装置に注目が集まっている。特に、NAND型フラッシュメモリは、メモリセル当たりの配線や電極の数が少なく、集積度を高めやすいことが知られている。また、多値化などの技術も実現され、年々記憶容量の増大が為されてきた。近年では、平面的なメモリセルの配置による高集積化の限界を迎えており、三次元的にメモリセルを配置する技術に置き換わりつつある（特許文献1参照。）。 40

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011-96340号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

集積度の高い半導体装置を提供することを課題の一とする。または、三次元的にメモリセルを配置した半導体装置を提供することを課題の一とする。または、記憶容量の大きい半導体装置を提供することを課題の一とする。または、保持期間の長いメモリセルを有する

半導体装置を提供することを課題の一とする。

【0007】

または、該半導体装置を有するモジュールを提供することを課題の一とする。または、該半導体装置、または該モジュールを有する電子機器を提供することを課題の一とする。または、新規な半導体装置を提供することを課題の一とする。または、新規なモジュールを提供することを課題の一とする。または、新規な電子機器を提供することを課題の一とする。

【0008】

または、ノーマリーオフの電気特性を有するトランジスタを提供することを課題の一とする。または、非導通時のリーク電流の小さいトランジスタを提供することを課題の一とする。または、サブスレッショルドスイング値の小さいトランジスタを提供することを課題の一とする。または、短チャネル効果の小さいトランジスタを提供することを課題の一とする。または、電気特性の優れたトランジスタを提供することを課題の一とする。または、信頼性の高いトランジスタを提供することを課題の一とする。または、高い周波数特性を有するトランジスタを提供することを課題の一とする。

10

【0009】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

20

【課題を解決するための手段】

【0010】

(1)

本発明の一態様は、基板と、角柱状の絶縁体と、直列に接続された複数のトランジスタを有するメモリセルストリングと、を有し、角柱状の絶縁体は、基板上に配置され、メモリセルストリングは、角柱状の絶縁体の側面に配置される半導体装置である。

【0011】

(2)

本発明の一態様は、基板と、角柱状の絶縁体と、複数の、直列に接続された複数のトランジスタを有するメモリセルストリングと、を有し、角柱状の絶縁体は、基板上に配置され、複数のメモリセルストリングは、角柱状の絶縁体の側面に配置されることを特徴とする半導体装置である。

30

【0012】

(3)

本発明の一態様は、(1)または(2)において、複数のトランジスタは、それぞれゲート絶縁体と、ゲート電極と、を有し、ゲート絶縁体は、第1の絶縁体と、第2の絶縁体と、電荷蓄積層と、を有し、電荷蓄積層は、第1の絶縁体と第2の絶縁体と、の間に配置される半導体装置である。

【0013】

(4)

本発明の一態様は、(1)乃至(3)のいずれか一において、複数のトランジスタは、酸化物半導体を有する半導体装置である。

40

【0014】

(5)

本発明の一態様は、(4)において、酸化物半導体は、インジウム、元素M(アルミニウム、ガリウム、イットリウムまたはスズ)および亜鉛を有する半導体装置である。

【0015】

(6)

本発明の一態様は、(1)乃至(5)のいずれか一において、さらに基板に配置された第1のトランジスタと、第2のトランジスタと、を有し、第1のトランジスタのソース端子

50

は、メモリセルストリングの第1の端子と電気的に接続され、第2のトランジスタのドレイン端子は、メモリセルストリングの第2の端子と電気的に接続される半導体装置である。

**【0016】**

(7)

本発明の一態様は、(6)において、第1のトランジスタおよび第2のトランジスタは、単結晶シリコンを有する半導体装置である。

**【発明の効果】**

**【0017】**

集積度の高い半導体装置を提供することができる。または、三次元的にメモリセルを配置した半導体装置を提供することができる。または、記憶容量の大きい半導体装置を提供することができる。または、保持期間の長いメモリセルを有する半導体装置を提供することができる。

10

**【0018】**

または、該半導体装置を有するモジュールを提供することができる。または、該半導体装置、または該モジュールを有する電子機器を提供することができる。または、新規な半導体装置を提供することができる。または、新規なモジュールを提供することができる。または、新規な電子機器を提供することができる。

20

**【0019】**

または、ノーマリーオフの電気特性を有するトランジスタを提供することができる。または、非導通時のリーク電流の小さいトランジスタを提供することができる。または、サブスレッショルドスイシング値の小さいトランジスタを提供することができる。または、短チャネル効果の小さいトランジスタを提供することができる。または、電気特性の優れたトランジスタを提供することができる。または、信頼性の高いトランジスタを提供することができる。または、高い周波数特性を有するトランジスタを提供することができる。

20

**【0020】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

30

**【図面の簡単な説明】**

**【0021】**

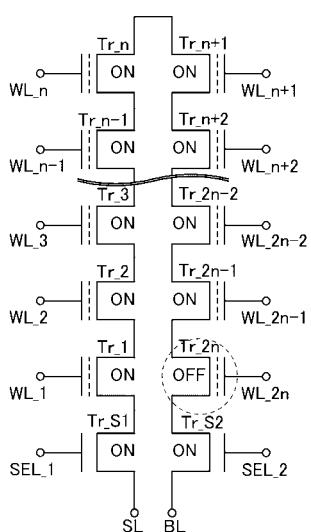

【図1】本発明の一態様に係る半導体装置の断面図および回路図。

【図2】本発明の一態様に係る半導体装置の動作を説明する模式図および断面図。

【図3】本発明の一態様に係る半導体装置の動作を説明する回路図。

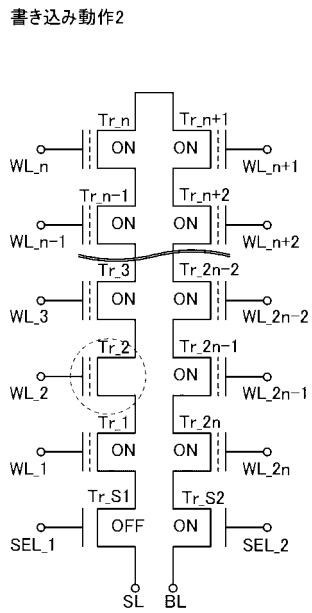

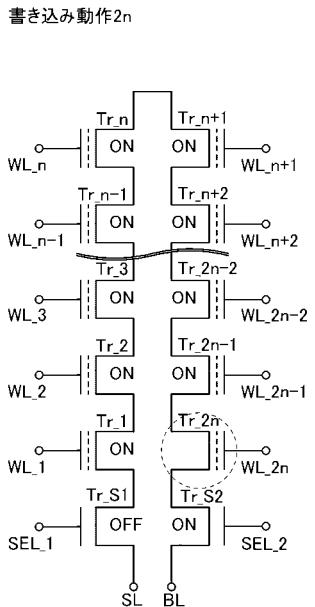

【図4】本発明の一態様に係る半導体装置の動作を説明する回路図。

【図5】本発明の一態様に係る半導体装置の動作を説明する回路図。

【図6】本発明の一態様に係る半導体装置の動作を説明する回路図。

【図7】本発明の一態様に係る半導体装置の動作を説明する回路図。

40

【図8】本発明の一態様に係る半導体装置の動作を説明する回路図。

【図9】本発明の一態様に係る半導体装置の動作を説明する回路図。

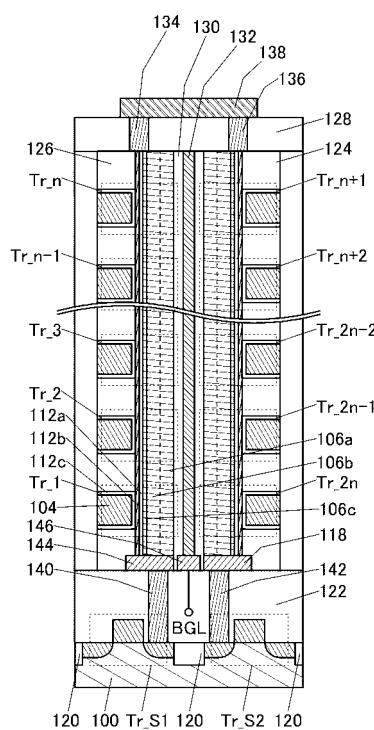

【図10】本発明の一態様に係る半導体装置の断面図。

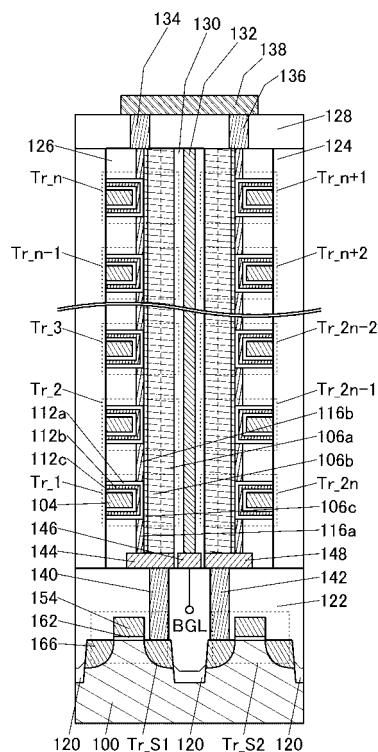

【図11】本発明の一態様に係る半導体装置の断面図。

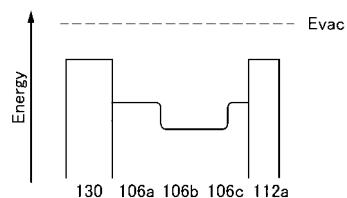

【図12】本発明の一態様に係るトランジスタのチャネル形成領域近傍のバンド図。

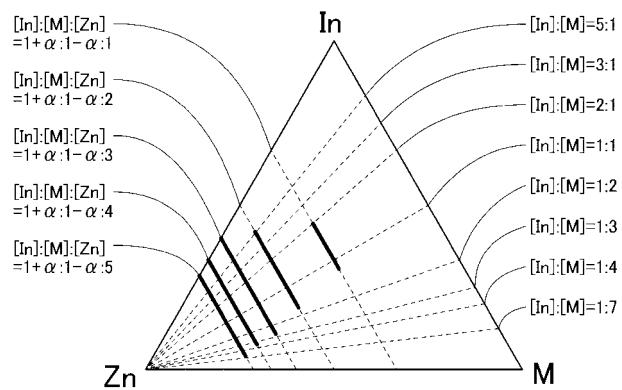

【図13】In-M-Zn酸化物の組成を説明する三角図。

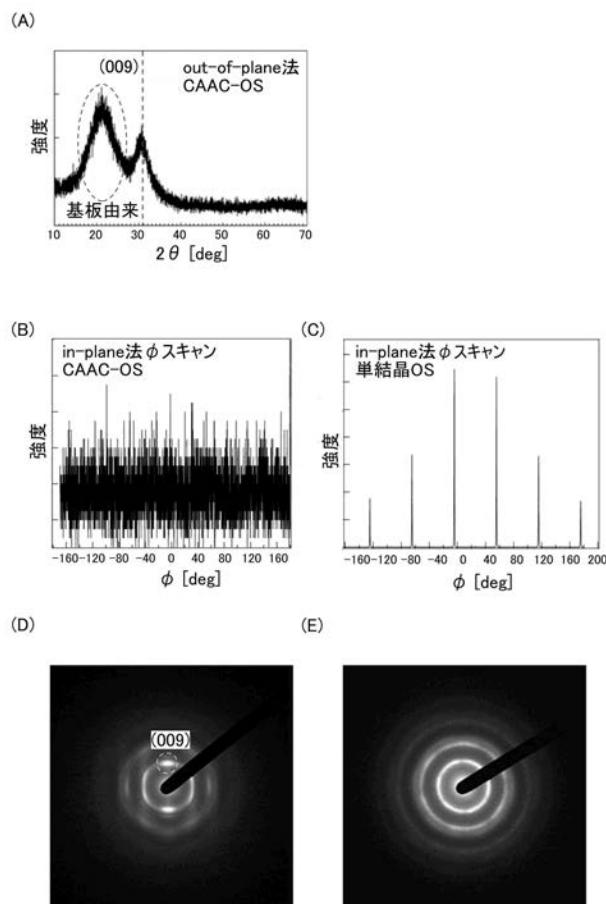

【図14】CAC-OSおよび単結晶酸化物半導体のXRDによる構造解析を説明する図、ならびにCAC-OSの制限視野電子回折パターンを示す図。

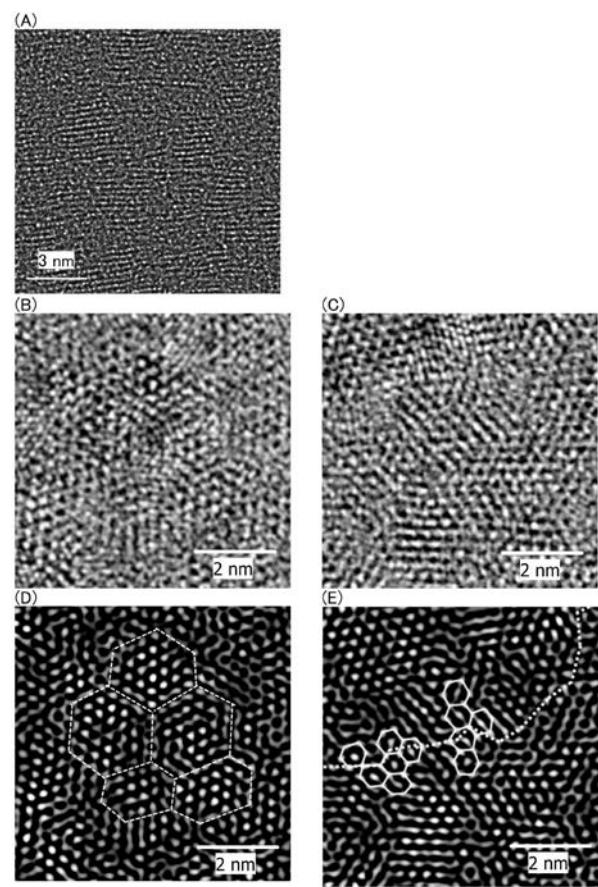

【図15】CAC-OSの断面TEM像、ならびに平面TEM像およびその画像解析像。

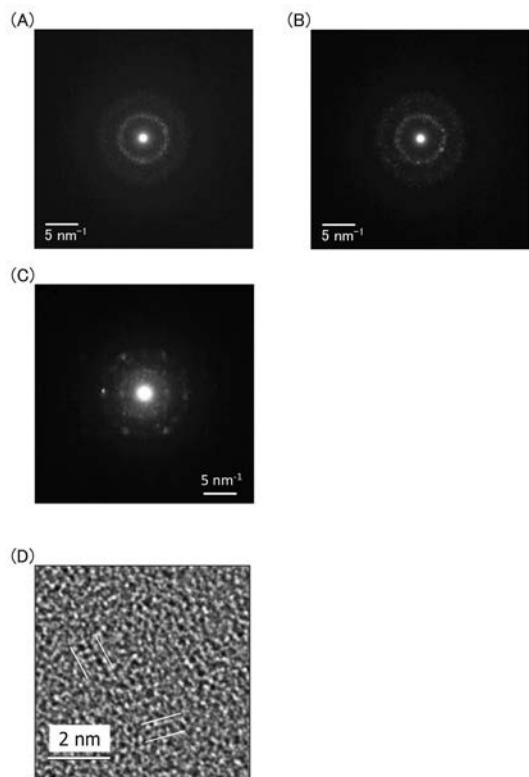

【図16】n<sub>c</sub>-OSの電子回折パターンを示す図、およびn<sub>c</sub>-OSの断面TEM像。

50

【図17】a - l i k e O Sの断面TEM像。

【図18】In - Ga - Zn酸化物の電子照射による結晶部の変化を示す図。

【発明を実施するための形態】

【0022】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

10

【0023】

なお、図において、大きさ、膜（層）の厚さ、または領域は、明瞭化のために誇張されている場合がある。

【0024】

なお、本明細書において、「膜」という表記と、「層」という表記と、を互いに入れ替えることが可能である。

【0025】

また、電圧は、ある電位と、基準の電位（例えば接地電位（GND）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。一般的に、電位（電圧）は、相対的なものであり、基準の電位からの相対的な大きさによって決定される。したがって、「接地電位」などと記載されている場合であっても、電位が0Vであるとは限らない。例えば、回路で最も低い電位が、「接地電位」となる場合もある。または、回路で中間くらいの電位が、「接地電位」となる場合もある。その場合には、その電位を基準として、正の電位と負の電位が規定される。

20

【0026】

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書などに記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

30

【0027】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体にDOS(Density of State)が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

40

【0028】

なお、本明細書において、AがBより迫り出した形状を有すると記載する場合、上面図または断面図において、Aの少なくとも一端が、Bの少なくとも一端よりも外側にある形状を有することを示す場合がある。したがって、AがBより迫り出した形状を有すると記載されている場合、例えば上面図において、Aの一端が、Bの一端よりも外側にある形状を有すると読み替えることができる。

【0029】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平

50

行」とは、二つの直線が - 30° 以上 30° 以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。したがって、85° 以上 95° 以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60° 以上 120° 以下の角度で配置されている状態をいう。

#### 【0030】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

#### 【0031】

##### <半導体装置>

以下では、本発明の一態様に係る半導体装置について説明する。

10

#### 【0032】

なお、以下では、n チャネル型トランジスタを想定して説明する。ただし、p チャネル型トランジスタに適用するために、適宜用語または符号などを読み替えて構わない。

#### 【0033】

##### <半導体装置の構造>

以下では、本発明の一態様に係る半導体装置の構造を例示する。

#### 【0034】

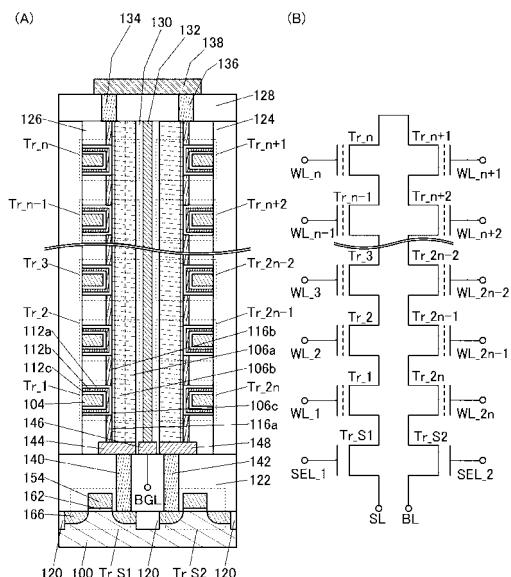

図1(A)は、本発明の一態様に係る半導体装置の断面図である。また、図1(B)は、図1(A)に示した半導体装置に対応する回路図である。

20

#### 【0035】

図1(A)に示す半導体装置は、基板 100 と、絶縁体 120 と、絶縁体 122 と、絶縁体 124 と、絶縁体 126 と、絶縁体 128 と、絶縁体 130 と、導電体 140 と、導電体 142 と、導電体 144 と、導電体 146 と、導電体 148 と、導電体 132 と、導電体 134 と、導電体 136 と、導電体 138 と、トランジスタ Tr\_S1 と、トランジスタ Tr\_S2 と、トランジスタ Tr\_1 乃至トランジスタ Tr\_2n (n は 2 以上の整数) と、を有する。

#### 【0036】

トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 は、基板 100 に設けられる。具体的には、トランジスタ Tr\_S1 は、基板 100 に設けられた一対の不純物領域 166 と、不純物領域 166 に挟まれたチャネル形成領域と、チャネル形成領域と重なる領域を有する導電体 154 と、チャネル形成領域と導電体 154 とに挟まれた絶縁体 162 と、を有する。ここで、導電体 154 はゲート電極としての機能を有し、絶縁体 162 はゲート絶縁体としての機能を有する。トランジスタ Tr\_S1 のゲート電極として機能する導電体 154 は、配線 SEL\_1 と電気的に接続される。また、トランジスタ Tr\_S2 のゲート電極として機能する導電体 154 は、配線 SEL\_2 と電気的に接続される。トランジスタ Tr\_S2 は、トランジスタ Tr\_S1 と同様の構造を有するものとして説明は省略するが、異なる構造を有していてもよい。トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 は、絶縁体 120 によって素子分離されている。素子分離の方法としては、STI (Shallow Trench Isolation) 法やLOCOS (Local Oxidation of Silicon) 法などが挙げられる。なお、トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 の構造としては、図1(A)に示した構造に限定されない。例えば、SOI (Silicon on Insulator) 基板に設けたトランジスタであってもよいし、FIN型のトランジスタであってもよい。

30

#### 【0037】

トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 上には、絶縁体 122 が配置される。絶縁体 122 上には、絶縁体 130 と、導電体 144 と、導電体 146 と、導電体 148 と、が配置される。絶縁体 130 は、角柱状または壁状であり、側面にトランジスタ Tr\_1 乃至トランジスタ Tr\_2n (n は 2 以上の整数) が配置される。なお、トランジスタ Tr\_1 乃至トランジスタ Tr\_n のそれぞれのチャネル長方向は基板の上面に対する垂直方向と平行であり、トランジスタ Tr\_n+1 乃至トランジスタ Tr\_2n のそ

40

50

それぞれのチャネル長方向は基板の上面に対する垂直方向と平行である。ただし、絶縁体 130 が角柱状または壁状でなくともよく、例えば円柱状であってもよい。なお、絶縁体 130 の一側面にはトランジスタ Tr\_1 乃至トランジスタ Tr\_n が配置され、別の側面にはトランジスタ Tr\_{n+1} 乃至トランジスタ Tr\_{2n} が配置される。n が大きいほど半導体装置の集積度は高くなる。例えば、n は 2、4、8、16、32、64、128 などの数とすればよい。

#### 【0038】

なお、導電体 132 は、絶縁体 130 を介してトランジスタ Tr\_1 乃至トランジスタ Tr\_{2n} と面する領域を有する。導電体 132 は、トランジスタ Tr\_1 乃至トランジスタ Tr\_{2n} のバックゲート電極（第 2 のゲート電極ともいう。）としての機能を有し、配線 BGL と電気的に接続される。

10

#### 【0039】

例えば、トランジスタ Tr\_1 は、絶縁体 106a と、半導体 106b と、絶縁体 106c と、導電体 116a と、導電体 116b と、絶縁体 112a と、電荷蓄積層 112b と、絶縁体 112c と、導電体 104 と、を有する。絶縁体 106a は、絶縁体 130 の側面に沿って配置される。半導体 106b は、絶縁体 106a を介して絶縁体 130 の側面に沿って配置される。絶縁体 106c は、半導体 106b および絶縁体 106a を介して絶縁体 130 の側面に沿って配置される。絶縁体 112a、導電体 116a および導電体 116b は、絶縁体 106c、半導体 106b および絶縁体 106a を介して絶縁体 130 と面する領域を有する。なお、絶縁体 112a は、導電体 116a と導電体 116b との間に配置される。電荷蓄積層 112b は、絶縁体 112a、絶縁体 106c、半導体 106b および絶縁体 106a を介して絶縁体 130 と面する領域を有する。絶縁体 112c は、電荷蓄積層 112b、絶縁体 112a、絶縁体 106c、半導体 106b および絶縁体 106a を介して絶縁体 130 と面する領域を有する。導電体 104 は、絶縁体 112c、電荷蓄積層 112b、絶縁体 112a、絶縁体 106c、半導体 106b および絶縁体 106a を介して絶縁体 130 と面する領域を有する。

20

#### 【0040】

よって、トランジスタ Tr\_1 において、半導体 106b はチャネル形成領域としての機能を有し、導電体 104 はゲート電極としての機能を有し、絶縁体 112a、電荷蓄積層 112b および絶縁体 112c はゲート絶縁体としての機能を有し、導電体 116a はソース電極としての機能を有し、導電体 116b はドレイン電極としての機能を有する。また、絶縁体 106a および絶縁体 106c は、半導体 106b の界面における欠陥準位密度を低減する機能を有する。絶縁体 106a、半導体 106b および絶縁体 106c に用いられる材料の組み合わせについては後述する。トランジスタ Tr\_1 のゲート電極として機能する導電体 104 は、配線 WL\_1 と電気的に接続される。なお、配線 WL\_1 は、ワード線としての機能を有する。なお、トランジスタ Tr\_1 は、図 1 (A) に示す構造に限定されるものではない。例えば、絶縁体 106a、絶縁体 106c などの一部の構成要素を有さなくてもよい。

30

#### 【0041】

トランジスタ Tr\_1 は、導電体 104 と半導体 106b との間に電荷蓄積層 112b を有する。そのため、トランジスタ Tr\_1 は、電荷蓄積層 112b の有する電荷の極性および量に対応するしきい値電圧となる。トランジスタ Tr\_1 は電荷蓄積層 112b によってしきい値電圧を制御できるため、しきい値電圧に応じたデータを記憶するメモリセル（記憶素子ともいう。）としての機能を有する。

40

#### 【0042】

図 2 (A) の左側に示すように、例えば、電荷蓄積層 112b に電子が蓄積されていない状態ではトランジスタ Tr\_1 のしきい値電圧はマイナスの値である。そして、図 2 (B) に示すように、電荷蓄積層 112b に電子が蓄積されると、電子から生じる電界を打ち消すためにしきい値電圧は変動し、図 2 (A) の右側のようにしきい値電圧はプラスの値となる。即ち、トランジスタ Tr\_1 は、電荷蓄積層 112b に電子が蓄積されていない

50

状態では導通するため `data "1"` を、電子が蓄積された状態では導通しないため `data "0"` をとる。ここでは、メモリセルが 2 値の場合について説明したが、3 値以上（例えば、4 値、8 値、16 値および 32 値など）の多値メモリセルとしてもよい。なお、電荷蓄積層 112b への電子の注入については後述する。

#### 【0043】

なお、トランジスタ `Tr_2` 乃至トランジスタ `Tr_2n` は、トランジスタ `Tr_1` と同様の構成を有する。ただし、トランジスタ `Tr_2` 乃至トランジスタ `Tr_2n` のゲート電極は、それぞれ配線 `WL_2` 乃至配線 `WL_2n` と電気的に接続される。なお、配線 `WL_2` 乃至配線 `WL_2n` は、それぞれワード線としての機能を有する。

#### 【0044】

このように、トランジスタ `Tr_1` 乃至トランジスタ `Tr_2n` は、それぞれがメモリセルの機能を有する。そして、トランジスタ `Tr_1` 乃至トランジスタ `Tr_2n` は直列に接続されていることから、それらをまとめて一つのメモリセルストリングと呼ぶことができる。また、メモリセルストリングは、例えば、基板 100 上にマトリクス状に配列させることができ、それぞれのメモリセルストリングには選択トランジスタが電気的に接続される。具体的には、基板 100 上の第 1 の方向に伸びる複数の直線と、第 2 の方向に伸びる複数の直線と、が交わる点上にメモリセルストリングを配列させればよい。第 1 の方向と第 2 の方向とが為す角度は、代表的には 45°。または 90°。とすればよいが、例えば、10° 以上 90° 以下、30° 以上 90° 以下、45° 以上 90° 以下または 60° 以上 90° 以下の範囲であればよく、メモリセルストリングの形状によって密度が高くなる配列が好ましい。ここで、例えば、第 1 の方向に沿って配線 `SL` および配線 `BL` を配置すれば、第 1 の方向に沿って形成されたメモリセルストリング間で配線 `SL` および配線 `BL` を共用することができる。ただし、メモリセルストリングの配列はマトリクス状に限定されるものではない。なお、配線 `SL` はソース線としての機能を有する。また、配線 `BL` はビット線としての機能を有する。

#### 【0045】

また、複数のメモリセルストリングをまとめてブロックと呼ぶ。一つのブロックは、例えば、第 1 の方向に  $a$  個（ $a$  は自然数。）、第 2 の方向に  $b$  個（ $b$  は自然数。）の  $a \times b$  個のメモリセルストリングをまとめたものとする。ただし、各ブロックでメモリセルストリングの数が異なっていてもよい。また、ブロックのまとめ方を任意に定めてもよい。ブロック内では、例えば、配線 `BGL` と導電体 132 が互いに電気的に接続される。また、異なるブロック間で、配線 `BGL` と導電体 132 が電気的に分離されていてもよい。一つのブロックにおいて、例えば、第 2 の方向に沿って配線 `WL_1` 乃至配線 `WL_2n` を配置すれば、第 2 の方向に沿って形成されたメモリセルストリング間で配線 `WL_1` 乃至配線 `WL_2n` を共用することができる。配線 `WL_1` 乃至配線 `WL_2n` は、ブロックごとに分割してもよいし、第 2 の方向に沿って配置されるブロック間で共用してもよい。配線 `WL_1` 乃至配線 `WL_2n` を共有するメモリセルのまとまりをページと呼ぶ。なお、配線 `BL` および配線 `SL` は、第 1 の方向に沿って配置されるブロック間で共用することができる。

#### 【0046】

トランジスタ `Tr_S1` は、ソース端子が配線 `SL` と電気的に接続され、ドレイン端子がメモリセルストリングの第 1 の端子と電気的に接続される。また、トランジスタ `Tr_S2` は、ドレイン端子が配線 `BL` と電気的に接続され、ソース端子がメモリセルストリングの第 2 の端子と電気的に接続される。このように、メモリセルストリングとの導通、非導通を選択するトランジスタであるため、トランジスタ `Tr_S1` およびトランジスタ `Tr_S2` を選択トランジスタと呼ぶことができる。

#### 【0047】

以下では、図 1 に示した半導体装置へのデータの書き込み動作および読み出し動作について説明する。

#### 【0048】

10

20

30

40

50

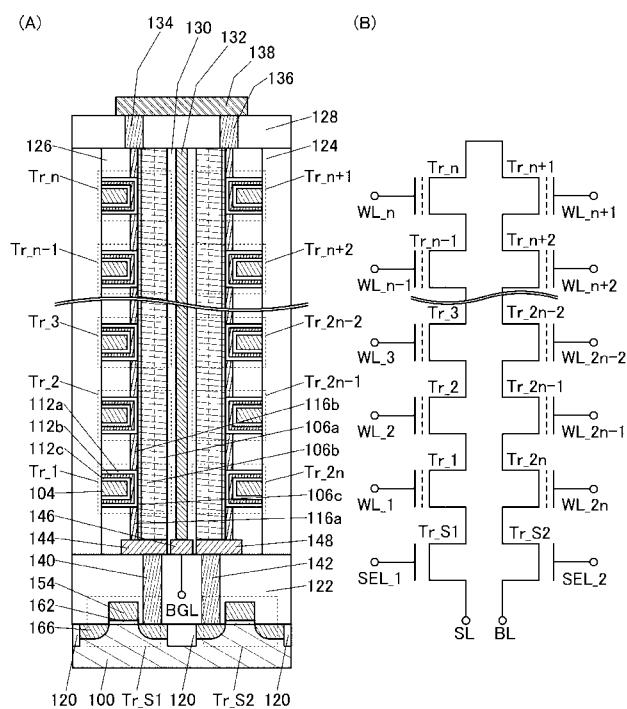

## &lt;リセット動作&gt;

各メモリセルにデータを書き込む場合は、書き込み動作の前にデータを消去（data "1"を書き込む）しておくことが好ましい。データを消去する動作をリセット動作ともいう。リセット動作は、ブロックごとに行う。例えば、データを消去したいブロックを選択し、図3(A)に示すように、導電体132と電気的に接続する配線BGLに消去電位V<sub>E</sub>（例えば15V）を印加し、配線WL\_1乃至配線WL\_2nには低電位（トランジスタTr\_1乃至トランジスタTr\_2nが非導通となる電位、例えば0V）を印加し、トランジスタTr\_S1およびトランジスタTr\_S2を導通させることで行うことができる。なお、導電体132を設けない場合は、配線SLおよび配線BLに消去電位V<sub>E</sub>を印加することでもリセット動作を行うことができる。リセット動作により、トランジスタTr\_1乃至トランジスタTr\_2nのそれぞれの電荷蓄積層112bに蓄積された電子を引き抜くことができる。

10

## 【0049】

一方、データを消去しないブロックについては、導電体132と配線BGLとの電気的な接続を切り、導電体132に消去電位V<sub>E</sub>が印加されないようにすればよい。または、図3(B)に示すようにデータを消去しないブロックと電気的に接続する配線WL\_1乃至配線WL\_2nに、トランジスタTr\_1乃至トランジスタTr\_2nが導通となる電位、例えば消去電位V<sub>E</sub>を印加すればよい。即ち、電荷蓄積層112bに、電子の引き抜きが起こる電位差を与えなければよい。

20

## 【0050】

なお、データの書き換えを行わないメモリセルのデータは、ブロックのリセット動作の前に別の領域に格納しておくことが好ましい。

## 【0051】

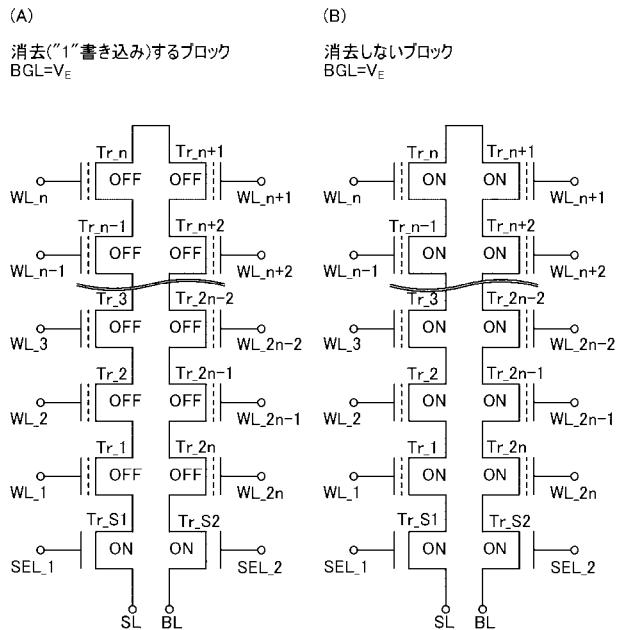

## &lt;書き込み動作&gt;

次に、各メモリセルへのデータの書き込み動作について図4、図5および図6を用いて説明する。

## 【0052】

データの書き込み動作は、上述したページごとに行うことができる。まず、書き込みを行うページのワード線に書き込み電位（例えば15V）を印加し、書き込みを行わないページのワード線に正電位（トランジスタが導通する電位、例えば3V）を印加する。ここでは、図4に示すように、まず配線WL\_1に書き込み電位を印加し、配線WL\_2乃至配線WL\_2nに正電位を印加する。そして、配線SLと電気的に接続するトランジスタTr\_S1を非導通状態とし、配線BLと電気的に接続するトランジスタTr\_S2を導通状態とする。そうすることで、書き込みを行うページのメモリセルには配線BLの電位が与えられる。したがって、配線BLの電位に応じたデータがメモリセルに書き込まれる。具体的には、配線BLの電位が低い電位（例えば0V）である場合、配線WL\_1に印加された書き込み電位との電位差が大きくなることによって電荷蓄積層112bに電子が注入される。また、配線BLの電位が正電位である場合、配線WL\_1に印加された書き込み電位との電位差が小さくなることによって電荷蓄積層112bには電子が注入されない。即ち、配線BLに低い電位が印加された場合にはメモリセルにdata "0"が書き込まれ、正電位が印加された場合にはメモリセルはdata "1"のままとなる。

30

## 【0053】

ここで、配線BLにメモリセルストリングごとに異なる電位を印加することで、ページごとのデータの書き込みを行うことができる。そして、同様のデータの書き込みを、図5および図6に示すように配線WL\_2乃至配線WL\_2nに対しても行うことで、ブロックまたは半導体装置全体のデータの書き込みを行うことができる。

## 【0054】

なお、メモリセルにdata "0"およびdata "1"以外のデータを書き込むこともできる。例えば、配線BLなどの電位や、電位を印加する時間によって電荷蓄積層112bに注入される電子量を制御すればよい。

40

50

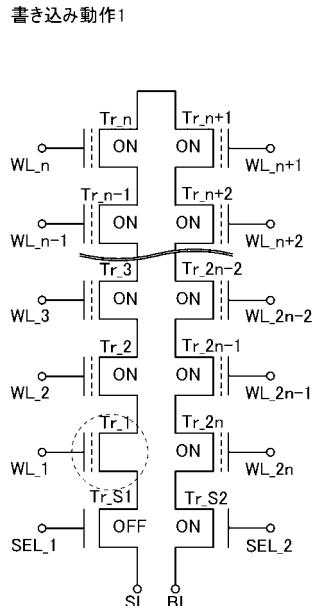

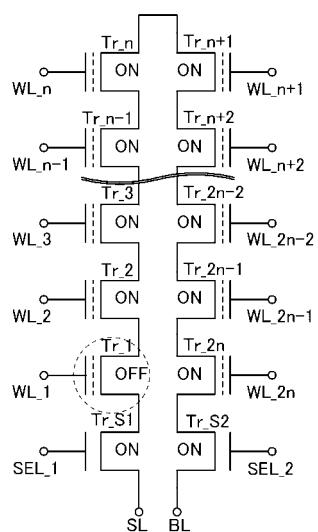

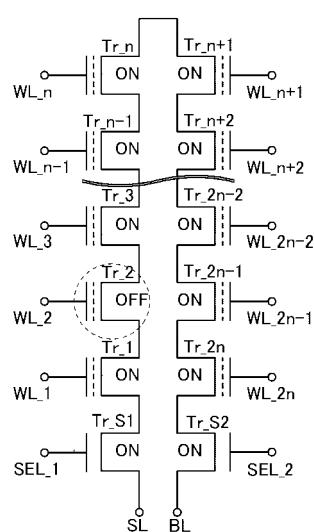

**【 0 0 5 5 】**

## &lt; 読み出し動作 &gt;

次に、各メモリセルに書き込まれたデータの読み出し動作について図7、図8および図9を用いた説明する。

**【 0 0 5 6 】**

データの読み出し動作も、ページごとに行うことができる。まず、読み出しを行うページのワード線に低い電位（例えば0V）を印加し、読み出しを行わないページのワード線に正電位（トランジスタが導通する電位、例えば3V）を印加する。ここでは、図7に示すように、まず配線WL\_1に低い電位を印加し、配線WL\_2乃至配線WL\_2nに正電位を印加する。そして、配線SLと電気的に接続するトランジスタTr\_S1、および配線BLと電気的に接続するトランジスタTr\_S2を導通状態とする。また、配線BLに読み出し電位（例えば1V）を印加し、配線SLに低い電位（例えば0V）を印加する。このとき、メモリセルがdata"1"であればメモリセルストリングに電流が流れ、data"0"であればメモリセルストリングに電流は流れない。したがって、このときの電流値を検出するか、配線BLの電位降下を検出することで、メモリセルのデータを読み出すことができる。

**【 0 0 5 7 】**

ここで、各メモリセルストリングのデータを配線BLに読み出すことで、ページ単位でデータを読み出すことができる。そして、同様のデータの読み出しを、図8および図9に示すように配線WL\_2乃至配線WL\_2nに対しても行うことで、ブロックまたは半導体装置全体のデータの読み出しを行うことができる。

**【 0 0 5 8 】**

以上に示したように、本発明の一態様に係る半導体装置は、三次元にメモリセルが配置されることで高い集積度を有する。したがって、投影面積辺りの記憶容量の大きい半導体装置である。例えば、1Tbyte以上、3Tbyte以上または10Tbyte以上の記憶容量を有する半導体装置である。また、データを長期間保持できるため、不揮発または実質的に不揮発な記憶素子を有する半導体装置と呼ぶこともできる。

**【 0 0 5 9 】**

本発明の一態様に係る半導体装置は、書き換えが可能であり、記憶容量が大きく、データを長期間保持することが可能であるため、コンピュータなどの記憶装置に好適である。例えば、コンピュータの内部でデータを保存する主記憶装置（メインメモリまたはメモリともいう。）や、コンピュータの外部でデータを保存する外部記憶装置（ストレージ、二次記憶装置ともいう。）などに用いることができる。外部記憶装置としては、メモリカードやSSD（Solid State Drive）などがある。

**【 0 0 6 0 】**

## &lt; 半導体装置の変形例 &gt;

本発明の一態様に係る半導体装置は、図1(A)に示した構造に限定されるものではない。例えば、図10に示すように、絶縁体106cを半導体106bおよび絶縁体106aを介して絶縁体130に沿った形状で配置してもよい。また、絶縁体112aを、絶縁体106c、半導体106bおよび絶縁体106aを介して絶縁体130に沿った形状で配置してもよい。また、電荷蓄積層112bを、絶縁体112a、絶縁体106c、半導体106bおよび絶縁体106aを介して絶縁体130に沿った形状で配置してもよい。また、図1(A)に示した導電体116aおよび導電体116bを有さなくてもよい。

**【 0 0 6 1 】**

または、図11に示すように、トランジスタTr\_S1およびトランジスタTr\_S2がFIN型トランジスタであってもよい。

**【 0 0 6 2 】**

## &lt; 半導体装置の構成要素 &gt;

以下では、半導体装置の構成要素について説明する。

**【 0 0 6 3 】**

絶縁体 120、絶縁体 122、絶縁体 124、絶縁体 126、絶縁体 128 および絶縁体 130 としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

10

## 【0064】

なお、絶縁体 120、絶縁体 122、絶縁体 124、絶縁体 126、絶縁体 128 および絶縁体 130 は、隣接する素子や配線などを分離する機能を有する場合があるため、比誘電率の低い絶縁体を用いることが好ましい。例えば、比誘電率が 5 以下、好ましくは 4 以下、さらに好ましくは 3 以下の絶縁体を用いる。具体的には、シリコンと、酸素と、を有する絶縁体や、さらにフッ素を有する絶縁体などを用いることが好ましい。また、絶縁体 120、絶縁体 122、絶縁体 124、絶縁体 126、絶縁体 128 および絶縁体 130 のいずれか一以上が空間であってもよい。

20

## 【0065】

絶縁体 120、絶縁体 122、絶縁体 124、絶縁体 126、絶縁体 128 および絶縁体 130 のいずれか一以上は、水素などの不純物および酸素をブロックする機能（透過させない）を有する絶縁体を有することが好ましい。トランジスタ  $T_r_1$  乃至トランジスタ  $T_r_n$  の近傍に、水素などの不純物および酸素をブロックする機能を有する絶縁体を配置することによって、トランジスタ  $T_r_1$  乃至トランジスタ  $T_r_n$  の電気特性を安定にすることができる。

30

## 【0066】

例えば、トランジスタ  $T_r_1$  乃至トランジスタ  $T_r_n$  が酸化物半導体を用いたトランジスタである場合、近接する絶縁体 130 または / および絶縁体 126 が過剰酸素を有する絶縁体であることが好ましい。過剰酸素は、酸化物半導体の酸素欠損の低減のために用いることができる。なお、過剰酸素とは、絶縁体中などに存在し、かつ絶縁体などと結合していない（遊離した）酸素、または絶縁体などとの結合エネルギーの低い酸素をいう。

30

## 【0067】

過剰酸素を有する絶縁体は、昇温脱離ガス分光法分析（TDS 分析）にて、100 以上 700 以下または 100 以上 500 以下の表面温度の範囲で  $1 \times 10^{18}$  atoms/cm<sup>3</sup> 以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup> 以上または  $1 \times 10^{20}$  atoms/cm<sup>3</sup> 以上の酸素（酸素原子数換算）を放出することもある。

40

## 【0068】

TDS 分析を用いた酸素の放出量の測定方法について、以下に説明する。

## 【0069】

測定試料を TDS 分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そして標準試料との比較により、気体の全放出量を計算することができる。

## 【0070】

例えば、標準試料である所定の密度の水素を含むシリコン基板の TDS 分析結果、および測定試料の TDS 分析結果から、測定試料の酸素分子の放出量 ( $N_{O_2}$ ) は、下に示す式で求めることができる。ここで、TDS 分析で得られる質量電荷比 32 で検出されるガスの全てが酸素分子由来と仮定する。 $CH_3OH$  の質量電荷比は 32 であるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数 17 の酸素原子および質量数 18 の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

50

## 【0071】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times$$

## 【0072】

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。  $S_{H_2}$  は、標準試料を TDS 分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、  $N_{H_2} / S_{H_2}$  とする。  $S_{O_2}$  は、測定試料を TDS 分析したときのイオン強度の積分値である。 は、 TDS 分析におけるイオン強度に影響する係数である。上に示す式の詳細に関しては、特開平 6 - 275697 公報を参照する。なお、上記酸素の放出量は、電子科学株式会社製の昇温脱離分析装置 EMD-WA1000S/W を用い、標準試料として一定量の水素原子を含むシリコン基板を用いて測定する。

10

## 【0073】

また、TDS 分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

## 【0074】

なお、  $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。

## 【0075】

または、加熱処理によって酸素を放出する絶縁体は、過酸化ラジカルを含むこともある。具体的には、過酸化ラジカルに起因するスピン密度が、  $5 \times 10^{17} \text{ spins/cm}^3$  以上であることをいう。なお、過酸化ラジカルを含む絶縁体は、電子スピン共鳴法 (ESR : Electron Spin Resonance) にて、  $g$  値が 2.01 近傍に非対称の信号を有することもある。

20

## 【0076】

ここで、トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 が単結晶シリコンまたは多結晶シリコンなどのシリコンを用いたトランジスタである場合、過剰酸素は電気特性を劣化させる要因となる場合がある。したがって、トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 に過剰酸素を混入させないために、絶縁体 122 が酸素透過性の低い絶縁体を有することが好ましい。

30

## 【0077】

一方、水素は、シリコンのダングリングボンドを終端させるために用いることができる。その結果、トランジスタ Tr\_S1 およびトランジスタ Tr\_S2 の電気特性を向上させることができる。ただし、水素は、トランジスタ Tr\_1 乃至トランジスタ Tr\_2n の電気特性を劣化させる要因となる場合があるため、絶縁体 122 が水素透過性の低い絶縁体を有することが好ましい。

## 【0078】

水素は、原子半径などが小さいため絶縁体中を拡散しやすい（拡散係数が大きい）。例えば、密度の低い絶縁体は、水素透過性が高くなる。言い換えれば、密度の高い絶縁体は水素透過性が低くなる。密度の低い絶縁体は、絶縁体全体の密度が低い必要はなく、部分的に密度が低い場合も含む。これは、密度の低い領域が水素の経路となるためである。水素を透過しうる密度は一意には定まらないが、代表的には  $2.6 \text{ g/cm}^3$  未満などが挙げられる。密度の低い絶縁体としては、例えば、酸化シリコンおよび酸化窒化シリコンなどの無機絶縁体、ならびにポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネートおよびアクリルなどの有機絶縁体などがある。密度の高い絶縁体としては、例えば、酸化マグネシウム、酸化アルミニウム、酸化ゲルマニウム、酸化ガリウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどがある。なお、密度の低い絶縁体および密度の高い絶縁体は、上述の絶縁体に限定されない。例えば、これらの絶縁体に、ホウ素、窒素、フッ素、ネオン、リン、塩素またはアルゴンから選ばれた一種以上の元素が含まれ

40

50

ていてもよい。

【0079】

また、結晶粒界を有する絶縁体は、水素透過性が高い場合がある。言い換えれば、結晶粒界を有さない（または結晶粒界が少ない）絶縁体は水素を透過させにくい。例えば、非多結晶絶縁体（非晶質絶縁体など）は、多結晶絶縁体と比べて水素透過性が低くなる。

【0080】

また、水素との結合エネルギーが高い絶縁体は、水素透過性が低い場合がある。例えば、水素と結合して水素化合物を作る絶縁体が、装置の作製工程または装置の動作における温度で水素を脱離しない程度の結合エネルギーを有すれば、水素透過性の低い絶縁体といえる。例えば、200以上1000以下、300以上1000以下、または400

以上1000以下で水素化合物を作る絶縁体は、水素透過性が低い場合がある。また、例えば、水素の脱離温度が、200以上1000以下、300以上1000以下、または400以上1000以下の水素化合物を作る絶縁体は、水素透過性が低い場合がある。一方、水素の脱離温度が、20以上400以下、20以上300

以下、または20以上200以下の水素化合物を作る絶縁体は、水素透過性が高い場合がある。また、容易に脱離する水素、および遊離した水素を過剰水素と呼ぶ場合がある。

【0081】

電荷蓄積層112bとしては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

【0082】

絶縁体112aおよび絶縁体112cとしては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

【0083】

電荷蓄積層112bは、絶縁体112aおよび絶縁体112cに挟まれて配置される。電荷蓄積層112bは、電子を蓄積する機能を有すればよい。例えば、電子トラップを有する絶縁体などが好適である。電子トラップは、不純物の添加やダメージを与えることなどによって形成することができる。また、電荷蓄積層112bと絶縁体112aとの界面、または電荷蓄積層112bと絶縁体112cとの界面に電子トラップを有してもよい。この場合、電荷蓄積層112bと絶縁体112aおよび電荷蓄積層112bと絶縁体112c、が異種接合であることが好ましい。電荷蓄積層112bと絶縁体112aとの界面に電子トラップを有する場合、絶縁体112cを設けなくてもよい場合がある。また、電荷蓄積層112bと絶縁体112cとの界面に電子トラップを有する場合、絶縁体112aを設けなくてもよい場合がある。なお、電荷蓄積層112bは、隣接するメモリセル間で共用されているため、電荷蓄積層112b内の電子の移動が起こりにくいことが好ましい。ただし、隣接するメモリセルと電荷蓄積層112bを分離させた場合は、電荷蓄積層112b内で電子の移動が起こってもよい。即ち、電荷蓄積層112bが半導体または導電体であってもよい。

【0084】

電荷蓄積層112bに電子を注入するために、絶縁体112aおよび絶縁体112cは、

10

20

30

40

40

50

ゲート電圧またはバックゲート電圧によって電子のトンネリングを起こす厚さであることが好ましい。ただし、メモリセルがデータを保持している状態での電子の流出を抑制するために、ゲート電圧またはバックゲート電圧が印加されていない状態での電子のトンネリングが起こらない厚さであることが好ましい。ただし、電子のトンネリングを完全になくすることは困難であるため、データが保持できる程度に電子のトンネリングが起こらない厚さとすればよい。例えば、絶縁体 112a および絶縁体 112c の厚さは、3 nm 以上 15 nm 以下、好ましくは 4 nm 以上 10 nm 以下とすればよい。また、電子の流出を抑制するために、エネルギーギャップの大きい絶縁体を用いることが好ましい。例えば、絶縁体 112a および絶縁体 112c のエネルギーギャップは、6 eV 以上 10 eV 以下、好ましくは 7 eV 以上 10 eV 以下、さらに好ましくは 8 eV 以上 10 eV 以下とすればよい。

10

#### 【0085】

具体的には、電荷蓄積層 112b としては、欠陥準位密度の高い窒化シリコン、窒化酸化シリコンまたは酸化ハフニウムが好適である。また、絶縁体 112a および絶縁体 112c としては、酸化シリコンまたは酸化窒化シリコンが好適である。

#### 【0086】

導電体 154、導電体 140、導電体 142、導電体 144、導電体 146、導電体 148、導電体 104、導電体 116a、導電体 116b、導電体 132、導電体 134、導電体 136 および導電体 138 としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニア、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンクスチルを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

20

#### 【0087】

以下では、絶縁体 106a、半導体 106b および絶縁体 106c について説明する。

#### 【0088】

半導体 106b の上下に絶縁体 106a および絶縁体 106c を配置することで、トランジスタの電気特性を向上させることができる場合がある。

30

#### 【0089】

絶縁体 106a は CAAc - OS を有することが好ましい。半導体 106b は CAAc - OS を有することが好ましい。絶縁体 106c は CAAc - OS を有することが好ましい。

#### 【0090】

半導体 106b は、例えば、インジウムを含む酸化物である。半導体 106b は、例えば、インジウムを含むと、キャリア移動度（電子移動度）が高くなる。また、半導体 106b は、元素 M を含むと好ましい。元素 M は、好ましくは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素 M に適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンクスチルなどがある。ただし、元素 M として、前述の元素を複数組み合わせても構わない場合がある。元素 M は、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素 M は、例えば、酸化物のエネルギーギャップを大きくする機能を有する元素である。また、半導体 106b は、亜鉛を含むと好ましい。酸化物は、亜鉛を含むと結晶化しやすくなる場合がある。

40

#### 【0091】

ただし、半導体 106b は、インジウムを含む酸化物に限定されない。半導体 106b は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む酸化物、ガリウムを含む酸化物、スズを含む酸化物などであっても構わない。

50

## 【0092】

半導体106bは、例えば、エネルギーギャップが大きい酸化物を用いる。半導体106bのエネルギーギャップは、例えば、2.5eV以上4.2eV以下、好ましくは2.8eV以上3.8eV以下、さらに好ましくは3eV以上3.5eV以下とする。

## 【0093】

例えば、絶縁体106aおよび絶縁体106cは、半導体106bを構成する酸素以外の元素一種以上、または二種以上から構成される酸化物である。半導体106bを構成する酸素以外の元素一種以上、または二種以上から絶縁体106aおよび絶縁体106cが構成されるため、絶縁体106aと半導体106bとの界面、および半導体106bと絶縁体106cとの界面において、欠陥準位が形成されにくい。

10

## 【0094】

絶縁体106a、半導体106bおよび絶縁体106cは、少なくともインジウムを含むと好ましい。なお、絶縁体106aがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高いとする。また、半導体106bがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが25atomic%より高く、Mが75atomic%未満、さらに好ましくはInが34atomic%より高く、Mが66atomic%未満とする。また、絶縁体106cがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高くする。なお、絶縁体106cは、絶縁体106aと同種の酸化物を用いても構わない。ただし、絶縁体106aまたは/および絶縁体106cがインジウムを含まなくとも構わない場合がある。例えば、絶縁体106aまたは/および絶縁体106cが酸化ガリウムであっても構わない。なお、絶縁体106a、半導体106bおよび絶縁体106cに含まれる各元素の原子数が、簡単な整数比にならなくても構わない。

20

## 【0095】

半導体106bは、絶縁体106aおよび絶縁体106cよりも電子親和力の大きい酸化物を用いる。例えば、半導体106bとして、絶縁体106aおよび絶縁体106cよりも電子親和力の0.07eV以上1.3eV以下、好ましくは0.1eV以上0.7eV以下、さらに好ましくは0.15eV以上0.4eV以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

30

## 【0096】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素ブロック性を有する。そのため、絶縁体106cがインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合[Ga/(In+Ga)]は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。

## 【0097】

このとき、ゲート電圧を印加すると、絶縁体106a、半導体106b、絶縁体106cのうち、電子親和力の大きい半導体106bにチャネルが形成される。

40

## 【0098】

ここで、絶縁体106aと半導体106bとの間には、絶縁体106aと半導体106bとの混合領域を有する場合がある。また、半導体106bと絶縁体106cとの間には、半導体106bと絶縁体106cとの混合領域を有する場合がある。混合領域は、欠陥準位密度が低くなる。そのため、絶縁体106a、半導体106bおよび絶縁体106cの積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド図となる（図12参照。）。なお、絶縁体106a、半導体106bおよび絶縁体106cは、それぞれの界面を明確に判別できない場合がある。

## 【0099】

50

このとき、電子は、絶縁体 106a 中および絶縁体 106c 中ではなく、半導体 106b 中を主として移動する。なお、絶縁体 106a および絶縁体 106c は、単独で存在した場合には導体、半導体または絶縁体のいずれの性質も取りうるが、トランジスタの動作時においてはチャネルを形成しない領域を有する。具体的には、絶縁体 106a と半導体 106bとの界面近傍、および絶縁体 106c と半導体 106b との界面近傍のみにチャネルが形成され、そのほかの領域にはチャネルが形成されない。したがって、トランジスタの動作上は絶縁体と呼ぶことができるため、本明細書中では半導体および導電体ではなく絶縁体と表記する。ただし、絶縁体 106a と、半導体 106b と、絶縁体 106c とは相対的な物性の違いによって半導体と絶縁体とを呼び分けられるだけであって、例えば、絶縁体 106a または絶縁体 106c として用いることのできる絶縁体を、半導体 106b として用いることができる場合がある。上述したように、絶縁体 106a と半導体 106b との界面における欠陥準位密度、および半導体 106b と絶縁体 106c との界面における欠陥準位密度を低くすることによって、半導体 106b 中で電子の移動が阻害されることが少なく、トランジスタのオン電流を大きくすることができます。

10

## 【0100】

また、トランジスタのオン電流は、電子の移動を阻害する要因を低減するほど、高くすることができます。例えば、電子の移動を阻害する要因のない場合、効率よく電子が移動すると推定される。電子の移動は、例えば、チャネル形成領域の物理的な凹凸が大きい場合にも阻害される。

20

## 【0101】

トランジスタのオン電流を大きくするためには、例えば、半導体 106b の上面または下面（被形成面、ここでは絶縁体 106a の上面）の、 $1 \mu\text{m} \times 1 \mu\text{m}$  の範囲における二乗平均平方根（RMS：Root Mean Square）粗さが 1 nm 未満、好ましくは 0.6 nm 未満、さらに好ましくは 0.5 nm 未満、より好ましくは 0.4 nm 未満とすればよい。また、 $1 \mu\text{m} \times 1 \mu\text{m}$  の範囲における平均面粗さ（Ra ともいう。）が 1 nm 未満、好ましくは 0.6 nm 未満、さらに好ましくは 0.5 nm 未満、より好ましくは 0.4 nm 未満とすればよい。また、 $1 \mu\text{m} \times 1 \mu\text{m}$  の範囲における最大高低差（P-V ともいう。）が 10 nm 未満、好ましくは 9 nm 未満、さらに好ましくは 8 nm 未満、より好ましくは 7 nm 未満とすればよい。RMS 粗さ、Ra および P-V は、エスアイアイ・ナノテクノロジー株式会社製走査型プローブ顕微鏡システム SPA-500 などを用いて測定することができる。

30

## 【0102】

また、トランジスタのオン電流を大きくするためには、絶縁体 106c の厚さは小さいほど好ましい。例えば、10 nm 未満、好ましくは 5 nm 以下、さらに好ましくは 3 nm 以下の領域を有する絶縁体 106c とすればよい。一方、絶縁体 106c は、チャネルの形成される半導体 106b へ、隣接する絶縁体を構成する酸素以外の元素（水素、シリコンなど）が入り込まないようロックする機能を有する。そのため、絶縁体 106c は、ある程度の厚さを有することが好ましい。例えば、0.3 nm 以上、好ましくは 1 nm 以上、さらに好ましくは 2 nm 以上の厚さの領域を有する絶縁体 106c とすればよい。また、絶縁体 106c は、他の絶縁体から放出される酸素の外方拡散を抑制するために、酸素をロックする性質を有すると好ましい。

40

## 【0103】

また、信頼性を高くするためには、絶縁体 106a は厚く、絶縁体 106c は薄いことが好ましい。例えば、10 nm 以上、好ましくは 20 nm 以上、さらに好ましくは 40 nm 以上、より好ましくは 60 nm 以上の厚さの領域を有する絶縁体 106a とすればよい。絶縁体 106a の厚さを、厚くすることで、隣接する絶縁体と絶縁体 106a との界面からチャネルの形成される半導体 106b までの距離を離すことができる。ただし、半導体装置の生産性が低下する場合があるため、例えば、200 nm 以下、好ましくは 120 nm 以下、さらに好ましくは 80 nm 以下の厚さの領域を有する絶縁体 106a とすればよい。

50

## 【0104】

例えば、半導体106bと絶縁体106aとの間に、例えば、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)において、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $2 \times 10^{18}$  atoms/cm<sup>3</sup>以下のシリコン濃度となる領域を有する。また、半導体106bと絶縁体106cとの間に、SIMSにおいて、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $2 \times 10^{18}$  atoms/cm<sup>3</sup>以下のシリコン濃度となる領域を有する。

10

## 【0105】

また、半導体106bは、SIMSにおいて、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下の水素濃度となる領域を有する。また、半導体106bの水素濃度を低減するために、絶縁体106aおよび絶縁体106cの水素濃度を低減すると好ましい。絶縁体106aおよび絶縁体106cは、SIMSにおいて、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下の水素濃度となる領域を有する。また、半導体106bは、SIMSにおいて、 $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下の窒素濃度となる領域を有する。また、半導体106bの窒素濃度を低減するために、絶縁体106aおよび絶縁体106cの窒素濃度を低減すると好ましい。絶縁体106aおよび絶縁体106cは、SIMSにおいて、 $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{15}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下の窒素濃度となる領域を有する。

20

30

## 【0106】

上述の3層構造は一例である。例えば、絶縁体106aまたは絶縁体106cのない2層構造としても構わない。または、絶縁体106aの上もしくは下、または絶縁体106cの上もしくは下に、絶縁体106a、半導体106bおよび絶縁体106cとして例示した半導体のいずれか一を有する4層構造としても構わない。または、絶縁体106aの上、絶縁体106aの下、絶縁体106cの上、絶縁体106cの下のいずれか二箇所以上に、絶縁体106a、半導体106bおよび絶縁体106cとして例示した半導体のいずれか一を有するn層構造(nは5以上の整数)としても構わない。

40

## 【0107】

## &lt;組成&gt;

以下では、In-M-Zn酸化物の組成について説明する。なお、元素Mは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステンなどがある。

50

## 【0108】

図13は、各頂点にIn、MまたはZnを配置した三角図である。また、図中の[In]はInの原子濃度を示し、[M]は元素Mの原子濃度を示し、[Zn]はZnの原子濃度を示す。

## 【0109】

In-M-Zn酸化物の結晶はホモロガス構造を有することが知られており、 $In_2MO_3$  ( $ZnO$ )<sub>m</sub> (mは自然数。)で示される。また、InとMとを置き換えることが可能であるため、 $In_{1+x}M_{1-x}O_3$  ( $ZnO$ )<sub>m</sub>で示すこともできる(-1 1)。これは、 $[In] : [M] : [Zn] = 1 + : 1 - : 1$ 、 $[In] : [M] : [Zn] = 1 + : 1 - : 3$ 、 $[In] : [M] : [Zn] = 1 + : 1 - : 4$ 、および $[In] : [M] : [Zn] = 1 + : 1 - : 5$ と表記した破線で示される組成である。なお、破線上の太線は、例えば、原料となる酸化物を混合し、1350で焼成した場合に固溶体となりうる組成である。

## 【0110】

よって、上述の固溶体となりうる組成に近づけることで、結晶性を高くすることができる。なお、スパッタリング法によってIn-M-Zn酸化物を成膜する場合、ターゲットの組成と膜の組成とが異なる場合がある。例えば、ターゲットとして原子数比が「1:1:1」、「1:1:1.2」、「3:1:2」、「4:2:4.1」、「1:3:2」、「1:3:4」、「1:4:5」のIn-M-Zn酸化物を用いた場合、膜の原子数比はそれぞれ「1:1:0.7 (0.5から0.9程度)」、「1:1:0.9 (0.8から1.1程度)」、「3:1:1.5 (1から1.8程度)」、「4:2:3 (2.6から3.6程度)」、「1:3:1.5 (1から1.8程度)」、「1:3:3 (2.5から3.5程度)」、「1:4:4 (3.4から4.4程度)」となる。したがって、所望の組成の膜を得るために、組成の変化を考慮してターゲットの組成を選択すればよい。

## 【0111】

## &lt;酸化物半導体の構造&gt;

以下では、酸化物半導体の構造について説明する。

## 【0112】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、CAAC-OS (c-axis-aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc-OS (nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体 (a-like OS: amorphous-like oxide semiconductor) および非晶質酸化物半導体などがある。

## 【0113】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体と、に分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-OS、多結晶酸化物半導体およびnc-OSなどがある。

## 【0114】

非晶質構造は、一般に、等方的であって不均質構造を持たない、準安定状態で原子の配置が固定化していない、結合角度が柔軟である、短距離秩序は有するが長距離秩序を有しない、などといわれている。

## 【0115】

即ち、安定な酸化物半導体を完全な非晶質 (completely amorphous) 酸化物半導体とは呼べない。また、等方的でない(例えば、微小な領域において周期構造を有する)酸化物半導体を、完全な非晶質酸化物半導体とは呼べない。一方、a-like OSは、等方的でないが、鬆(ボイドともいう。)を有する不安定な構造である。不安定であるという点では、a-like OSは、物性的に非晶質酸化物半導体に近い。

10

20

30

40

50

## 【0116】

&lt; C AAC - OS &gt;

まずは、C AAC - OSについて説明する。

## 【0117】

C AAC - OSは、c軸配向した複数の結晶部（ペレットともいう。）を有する酸化物半導体の一種である。

## 【0118】

C AAC - OSをX線回折(XRD: X-Ray Diffraction)によって解析した場合について説明する。例えば、空間群R-3mに分類されるInGaZnO<sub>4</sub>の結晶を有するC AAC - OSに対し、out-of-plane法による構造解析を行うと、図14(A)に示すように回折角(2θ)が31°近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、C AAC - OSでは、結晶がc軸配向性を有し、c軸がC AAC - OSの膜を形成する面（被形成面ともいう。）、または上面に略垂直な方向を向いていることが確認できる。なお、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、空間群Fd-3mに分類される結晶構造に起因する。そのため、C AAC - OSは、該ピークを示さないことが好ましい。

10

## 【0119】

一方、C AAC - OSに対し、被形成面に平行な方向からX線を入射させるin-plane法による構造解析を行うと、2θが56°近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub>の結晶の(110)面に帰属される。そして、2θを56°近傍に固定し、試料面の法線ベクトルを軸（c軸）として試料を回転させながら分析（スキャン）を行っても、図14(B)に示すように明瞭なピークは現れない。一方、単結晶InGaZnO<sub>4</sub>に対し、2θを56°近傍に固定してスキャンした場合、図14(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、XRDを用いた構造解析から、C AAC - OSは、a軸およびb軸の配向が不規則であることが確認できる。

20

## 【0120】

次に、電子回折によって解析したC AAC - OSについて説明する。例えば、InGaZnO<sub>4</sub>の結晶を有するC AAC - OSに対し、C AAC - OSの被形成面に平行にプローブ径が300nmの電子線を入射させると、図14(D)に示すような回折パターン（制限視野電子回折パターンともいう。）が現れる場合がある。この回折パターンには、InGaZnO<sub>4</sub>の結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によっても、C AAC - OSに含まれるペレットがc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が300nmの電子線を入射させたときの回折パターンを図14(E)に示す。図14(E)より、リング状の回折パターンが確認される。したがって、プローブ径が300nmの電子線を用いた電子回折によっても、C AAC - OSに含まれるペレットのa軸およびb軸は配向性を有さないことがわかる。なお、図14(E)における第1リングは、InGaZnO<sub>4</sub>の結晶の(010)面および(100)面などに起因すると考えられる。また、図14(E)における第2リングは(110)面などに起因すると考えられる。

30

## 【0121】

また、透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、C AAC - OSの明視野像と回折パターンとの複合解析像（高分解能TEM像ともいう。）を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像であってもペレット同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を明確に確認することができない場合がある。そのため、C AAC - OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

40

## 【0122】

50

図15(A)に、試料面と略平行な方向から観察したCAAC-OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正(Spherical Aberration Corrector)機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって観察することができる。

#### 【0123】

図15(A)より、金属原子が層状に配列している領域であるペレットを確認することができる。ペレット一つの大きさは1nm以上のものや、3nm以上のものがあることがある。したがって、ペレットを、ナノ結晶(nc:nanocrystal)と呼ぶこともできる。また、CAAC-OSを、CANC(C-Axis Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。ペレットは、CAAC-OSの被形成面または上面の凹凸を反映しており、CAAC-OSの被形成面または上面と平行となる。

10

#### 【0124】

また、図15(B)および図15(C)に、試料面と略垂直な方向から観察したCAAC-OSの平面のCs補正高分解能TEM像を示す。図15(D)および図15(E)は、それぞれ図15(B)および図15(C)を画像処理した像である。以下では、画像処理の方法について説明する。まず、図15(B)を高速フーリエ変換(FFT:Fast Fourier Transform)処理することでFFT像を取得する。次に、取得したFFT像において原点を基準に、 $2.8\text{ nm}^{-1}$ から $5.0\text{ nm}^{-1}$ の間の範囲を残すマスク処理する。次に、マスク処理したFFT像を、逆高速フーリエ変換(IFFT:Inverse Fast Fourier Transform)処理することで画像処理した像を取得する。こうして取得した像をFFTフィルタリング像と呼ぶ。FFTフィルタリング像は、Cs補正高分解能TEM像から周期成分を抜き出した像であり、格子配列を示している。

20

#### 【0125】

図15(D)では、格子配列の乱れた箇所を破線で示している。破線で囲まれた領域が、一つのペレットである。そして、破線で示した箇所がペレットとペレットとの連結部である。破線は、六角形状であるため、ペレットが六角形状であることがわかる。なお、ペレットの形状は、正六角形状とは限らず、非正六角形状である場合が多い。

30

#### 【0126】

図15(E)では、格子配列の揃った領域と、別の格子配列の揃った領域と、の間を点線で示している。点線近傍においても、明確な結晶粒界を確認することはできない。点線近傍の格子点を中心に周囲の格子点を繋ぐと、歪んだ六角形や、五角形または/および七角形などが形成できる。即ち、格子配列を歪ませることによって結晶粒界の形成を抑制していることがわかる。これは、CAAC-OSが、a-b面方向において原子配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためと考えられる。

40

#### 【0127】

以上に示すように、CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数のペレット(ナノ結晶)が連結し、歪みを有した結晶構造となっている。よって、CAAC-OSを、CAA crystal(c-axis-aligned a-b-plane-anchored crystal)を有する酸化物半導体と称することもできる。

#### 【0128】

CAAC-OSは結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、CAAC-OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。

#### 【0129】

50

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

#### 【0130】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。例えば、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。10

#### 【0131】

不純物および酸素欠損の少ないCAC-O<sub>S</sub>は、キャリア密度の低い酸化物半導体である。具体的には、 $8 \times 10^{11}$  個 / cm<sup>3</sup> 未満、好ましくは $1 \times 10^{11}$  / cm<sup>3</sup> 未満、さらに好ましくは $1 \times 10^{10}$  個 / cm<sup>3</sup> 未満であり、 $1 \times 10^{-9}$  個 / cm<sup>3</sup> 以上のキャリア密度の酸化物半導体とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAC-O<sub>S</sub>は、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

#### 【0132】

< n c - O S >

次に、n c - O Sについて説明する。20

#### 【0133】

n c - O SをXRDによって解析した場合について説明する。例えば、n c - O Sに対し、out-of-plane法による構造解析を行うと、配向性を示すピークが現れない。即ち、n c - O Sの結晶は配向性を有さない。

#### 【0134】

また、例えば、InGaZnO<sub>4</sub>の結晶を有するn c - O Sを薄片化し、厚さが34nmの領域に対し、被形成面に平行にプローブ径が50nmの電子線を入射させると、図16(A)に示すようなリング状の回折パターン(ナノビーム電子回折パターン)が観測される。また、同じ試料にプローブ径が1nmの電子線を入射させたときの回折パターン(ナノビーム電子回折パターン)を図16(B)に示す。図16(B)より、リング状の領域内に複数のスポットが観測される。したがって、n c - O Sは、プローブ径が50nmの電子線を入射させることでは秩序性が確認されないが、プローブ径が1nmの電子線を入射させることでは秩序性が確認される。30

#### 【0135】

また、厚さが10nm未満の領域に対し、プローブ径が1nmの電子線を入射させると、図16(C)に示すように、スポットが略正六角状に配置された電子回折パターンを観測される場合がある。したがって、厚さが10nm未満の範囲において、n c - O Sが秩序性の高い領域、即ち結晶を有することがわかる。なお、結晶が様々な方向を向いているため、規則的な電子回折パターンが観測されない領域もある。40

#### 【0136】

図16(D)に、被形成面と略平行な方向から観察したn c - O Sの断面のCs補正高分解能TEM像を示す。n c - O Sは、高分解能TEM像において、補助線で示す箇所などのように結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。n c - O Sに含まれる結晶部は、1nm以上10nm以下の大きさであり、特に1nm以上3nm以下の大きさであることが多い。なお、結晶部の大きさが10nmより大きく100nm以下である酸化物半導体を微結晶酸化物半導体(microcrystalline oxide semiconductor)と呼ぶことがある。n c - O Sは、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、CAC-O<sub>S</sub>におけるペレットと起源を同じくする可能性がある。50

ある。そのため、以下では n c - O S の結晶部をペレットと呼ぶ場合がある。

#### 【 0 1 3 7 】

このように、 n c - O S は、微小な領域（例えば、 1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、 n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、 n c - O S は、分析方法によっては、 a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。

#### 【 0 1 3 8 】

なお、ペレット（ナノ結晶）間で結晶方位が規則性を有さないことから、 n c - O S を、 R A N C ( R a n d o m A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体、または N A N C ( N o n - A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体と呼ぶこともできる。10

#### 【 0 1 3 9 】

n c - O S は、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、 n c - O S は、 a - l i k e O S や非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、 n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、 n c - O S は、 C A A C - O S と比べて欠陥準位密度が高くなる。

#### 【 0 1 4 0 】

< a - l i k e O S >

a - l i k e O S は、 n c - O S と非晶質酸化物半導体との間の構造を有する酸化物半導体である。20

#### 【 0 1 4 1 】

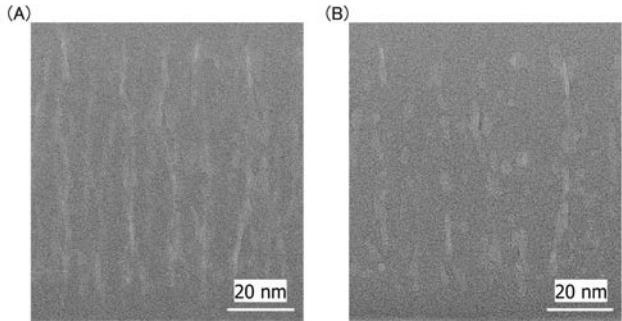

図 17 に、 a - l i k e O S の高分解能断面 TEM 像を示す。ここで、図 17 ( A ) は電子照射開始時における a - l i k e O S の高分解能断面 TEM 像である。図 17 ( B ) は  $4.3 \times 10^8 e^- / nm^2$  の電子 ( $e^-$ ) 照射後における a - l i k e O S の高分解能断面 TEM 像である。図 17 ( A ) および図 17 ( B ) より、 a - l i k e O S は電子照射開始時から、縦方向に延伸する縞状の明領域が観察されることがわかる。また、明領域は、電子照射後に形状が変化することがわかる。なお、明領域は、鬆または低密度領域と推測される。

#### 【 0 1 4 2 】

鬆を有するため、 a - l i k e O S は、不安定な構造である。以下では、 a - l i k e O S が、 C A A C - O S および n c - O S と比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。30

#### 【 0 1 4 3 】

試料として、 a - l i k e O S 、 n c - O S および C A A C - O S を準備する。いずれの試料も I n - G a - Z n 酸化物である。

#### 【 0 1 4 4 】

まず、各試料の高分解能断面 TEM 像を取得する。高分解能断面 TEM 像により、各試料は、いずれも結晶部を有する。

#### 【 0 1 4 5 】

なお、 I n G a Z n O<sub>4</sub> の結晶の単位格子は、 I n - O 層を 3 層有し、また G a - Z n - O 層を 6 層有する、計 9 層が c 軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009) 面の格子面間隔 (d 値ともいう。) と同程度であり、結晶構造解析からその値は 0.29 nm と求められている。したがって、以下では、格子縞の間隔が 0.28 nm 以上 0.30 nm 以下である箇所を、 I n G a Z n O<sub>4</sub> の結晶部と見なした。なお、格子縞は、 I n G a Z n O<sub>4</sub> の結晶の a - b 面に対応する。40

#### 【 0 1 4 6 】

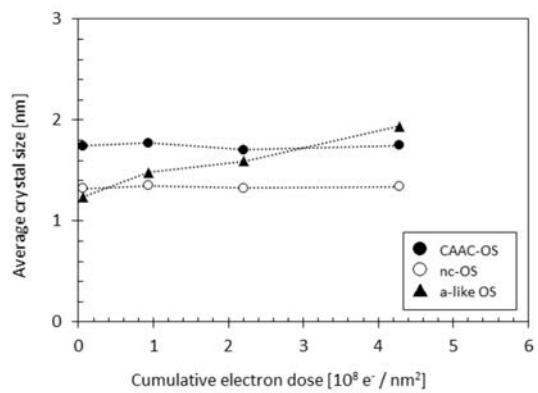

図 18 は、各試料の結晶部 (22 箇所から 30 箇所) の平均の大きさを調査した例である。なお、上述した格子縞の長さを結晶部の大きさとしている。図 18 より、 a - l i k e

10

20

30

40

50

O Sは、TEM像の取得などに係る電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。図18より、TEMによる観察初期においては1.2nm程度の大きさだった結晶部(初期核ともいう。)が、電子( $e^-$ )の累積照射量が $4.2 \times 10^8 e^- / nm^2$ においては1.9nm程度の大きさまで成長していることがわかる。一方、nc-OSおよびCAC-OSは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^- / nm^2$ までの範囲で、結晶部の大きさに変化が見られないことがわかる。図18より、電子の累積照射量によらず、nc-OSおよびCAC-OSの結晶部の大きさは、それぞれ1.3nm程度および1.8nm程度であることがわかる。なお、電子線照射およびTEMの観察は、日立透過電子顕微鏡H-9000NARを用いた。電子線照射条件は、加速電圧を300kV、電流密度を $6.7 \times 10^5 e^- / (nm^2 \cdot s)$ 、照射領域の直径を230nmとした。

10

## 【0147】

このように、a-like OSは、電子照射によって結晶部の成長が見られる場合がある。一方、nc-OSおよびCAC-OSは、電子照射による結晶部の成長がほとんど見られない。即ち、a-like OSは、nc-OSおよびCAC-OSと比べて、不安定な構造であることがわかる。

## 【0148】

また、鬆を有するため、a-like OSは、nc-OSおよびCAC-OSと比べて密度の低い構造である。具体的には、a-like OSの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満である。また、nc-OSの密度およびCAC-OSの密度は、同じ組成の単結晶の密度の92.3%以上100%未満である。単結晶の密度の78%未満である酸化物半導体は、成膜すること自体が困難である。

20

## 【0149】

例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、菱面体晶構造を有する単結晶InGaZnO<sub>4</sub>の密度は $6.357 g / cm^3$ である。よって、例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、a-like OSの密度は $5.0 g / cm^3$ 以上 $5.9 g / cm^3$ 未満である。また、例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、nc-OSの密度およびCAC-OSの密度は $5.9 g / cm^3$ 以上 $6.3 g / cm^3$ 未満である。

30

## 【0150】

なお、同じ組成の単結晶が存在しない場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

## 【0151】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a-like OS、nc-OS、CAC-OSのうち、二種以上を有する積層膜であってもよい。

40

## 【符号の説明】

## 【0152】

100 基板

104 導電体

106a 絶縁体

106b 半導体

106c 絶縁体

112a 絶縁体

112b 電荷蓄積層

112c 絶縁体

50

|         |       |

|---------|-------|

| 1 1 6 a | 導電体   |

| 1 1 6 b | 導電体   |

| 1 2 0   | 絶縁体   |

| 1 2 2   | 絶縁体   |

| 1 2 4   | 絶縁体   |

| 1 2 6   | 絶縁体   |

| 1 2 8   | 絶縁体   |

| 1 3 0   | 絶縁体   |

| 1 3 2   | 導電体   |

| 1 3 4   | 導電体   |

| 1 3 6   | 導電体   |

| 1 3 8   | 導電体   |

| 1 4 0   | 導電体   |

| 1 4 2   | 導電体   |

| 1 4 4   | 導電体   |

| 1 4 6   | 導電体   |

| 1 4 8   | 導電体   |

| 1 5 4   | 導電体   |

| 1 6 2   | 絶縁体   |

| 1 6 6   | 不純物領域 |

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

### 読み出し動作1

〔 四 8 〕

読み出し動作2

【 9 】

読み出し動作2n

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【図 1-4】

【 図 1 5 】

【図16】

【図17】

【図18】

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

*H 01 L 29/792 (2006.01)*

F ターム(参考) 5F083 EP17 EP18 EP22 EP33 EP34 EP76 ER03 ER09 ER14 ER19

ER23 GA10 GA11 GA25 HA02 JA02 JA03 JA04 JA05 JA36

JA37 JA38 JA39 JA40 JA44 JA56 JA58 JA60 KA01 KA05

KA11 NA01 ZA21

5F101 BA42 BA45 BB02 BB08 BC01 BD16 BD22 BD30 BD34 BD35

BE07

5F110 AA04 AA06 AA08 BB08 BB11 EE30 FF01 FF02 FF03 FF04

FF05 FF09 FF10 GG01 GG12 GG13 GG14 GG15 GG16 GG17

NN74