Filed Sept. 13, 1961

FIG. 1b OVERALL SYSTEN

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

R. B. ARNDT ETAL

3,260,997

FIG.4

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

ILLEGAL OPERATION

p1-8-

8 qM

STORED PROGRAM SYSTEM

93 Sheets-Sheet 14 Filed Sept. 13, 1961 SX XE <u>-81-</u>8 <u>0</u> → no-s 9 X <u>005</u> INSTR 46 (e£) **005** V 89-8 70Ž 8-2<u>1</u>ے 9E BISNI ΧO NSTR 26 8-58 1-X1 M 10 Ō 200 2X-2 107 SX-I ion 3x-2 1-XE χ̈́ν 000 000 00Z OPERATION CODE (43) oon (43) CODE 님 oon 60-8~ ILLEGAL OPERATION 3000 Z Hold CLR U00-09 MPI2 d<del> - ×</del> q

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

93 Sheets-Sheet 23 Filed Sept. 13, 1961 (II) OI BIZNI EGUAL SKIP 11-21 (II) SE ATSNI z INITIATE F2 15-15 (II) IE BISNI 14 3TAITINI 51-51 Z INSTR 26 (II) LOAD R 15-14 (II) || BISN| NON EDNAL SKIP 15-12 INSTR I2 (II) z **LESS SKIP** 91-źı (II) EI ATZNI GREATER SKIP REP INSTR (II) OF HISNI z E STORED INSTR 20 (II) 81-21 15-19 IN/OUT CHAN 2 M Haw STORE 13-55 15-53 CS → Ō INPUT (31) 13-54 d V I CHAN 2 RESUME 15-26 TU9TU0-S3 TERMINATE CHAN 2 I TERMINATE CHAN I TRANS CZ ENABLE (14) BEADY [0→C2] d 1<u>2-25</u> B=0 ★ (20) BEADY [0→C1] CHAN I TRANS CI ENABLE (14) 15-59 FI-00TPUT (28) z 6 dW Z C 15-33 (II) St BISNI SMART ATAU TUO AO A BAOTE OT 15-34 INSTR IG (II) V ROS 8**4**M 15-36 M ΛIO z (II) SI BISNI ₹<u>75-SI</u> 15-28 X+0 ENVBLE Z O♣O ENABLE

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

93 Sheets-Sheet 35 Filed Sept. 13, 1961 £S X <u>0</u> 52 £1,,80,, "DR" 13 R]-CTR 13 (17) ₹ 23 X 55 Q 22 SI "80" ZI "80" RJ-CTR 12 (17) <u>1</u>4 22 S X :2 ō 11 ,,80,, 11 ...80... R:-CTR 11 (17) N<sub>\*</sub> SI "0R" 4 <del>5</del>1 5 t ...80... (TI) + 8TO - (R <u>ξl X</u> "OB,, 3 <u>Σ "</u>90" R -CTR 3 (I7)

Filed Sept. 13, 1961

93 Sheets-Sheet 38 Filed Sept. 13, 1961 60A 61 \*U 10 60<sub>B</sub> 20-4 61 <sub>\*</sub>N 80A 519 Ιď 81 \*U <u>√\*23</u> 0 80A 519 20-40 M 81 <sub>\*</sub>N 1<del>\*</del> 23 708 RIS V 21 **\***U 7¥ 22 10 70*9* <u>815</u> 20-39 M 21 <sub>\*</sub>n <u>1¥</u>22 90B | 118 M 91 <sub>\*</sub> N N<sub>\*</sub>SI 10 10 908 SO-38 20-38 118 91 10 15 \*U G09 V 019 <u>91 ¥</u>U 01 40 10 908 ۱<sub>\*</sub> او N¥ 20 R04 <del>⊅1 </del>\*U ₽0H ۱,∗۱۱ B03 <u>دا ۴</u> اع 0 803 ۱3 **\*** اع ROS 71<u>,</u>15 20-28 BOI Ø <u>11 \*U</u> <u>108</u> Ø 11 **\***U 800 01\*0 \* U : Я <u>008</u> 22 01 \*1

100 SELS E, 13

STORED PROGRAM SYSTEM

93 Sheets-Sheet 39 Filed Sept. 13, 1961 (6£) I-Λ → d b -- A-5(39) IS-IS (6£) ∧<del>---</del> \*U Z Λ<del>-</del>d 21-33 MbO V04 70q AON SETS E\* 17 4 SI-I¢ MOS SETS E\* 16 86-12-M 21-25 904 出 (VO2 VO3 VO4) EI-I3 91 **\***U (VO2 VO3 VO4) PS-IS1 609 VOZ VO3 VO4 11<del>\*</del> 14 I (<u>NOS NO3 NO4</u>) ADS SEER E\* 15 **b**0d AOI SELS Ex Id Ł (IOA 00A)  $\begin{array}{c|c} \mathbb{E} & \mathbb{E} \\ \mathbf{F1G. 2Id} \\ \mathbf{v} & \text{register 8 translators} \end{array}$ (<u>NOO NOI</u>) (10A QOA) (<u>IOA OOA</u>) (IOV 00V) 01-12 (<u>IOV OOV</u>) EI-IS 7

Filed Sept. 13, 1961

25-192

22-167

GATE INHIBIT (23)

STORED PROGRAM SYSTEM

93 Sheets-Sheet 41 Filed Sept. 13, 1961 22-115 108 E5-01 E\* 11 F1-01 113 ᅙ 22-98 V 52-20 CS-II ΙΙŌ FF ΕX 12-22/ IMMA-S ENABLE INHIBIT 800 22-203 22-128 I F2-00 E\* 10 10 55-159 FI-00 Z EIO 90 Z6-52 69-22-05-40 010 4 OFX V 22-20 JAMA-2 TIBIHNI BIBANE OLO NEEN OLO (SI) (S → C 001 10 X 100 CS - OI 1 I 103 TIBIHNI 3J8AN3 100 N30 22-60 J9MA-2 00 00 1 000 E00 J9MA-2 Z 000 N39 MPO 452-129 ENABLE INHIBIT

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

93 Sheets-Sheet 6ଥ

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

July 12, 1966

R. B. ARNDT ETAL

3,260,997

STORED PROGRAM SYSTEM

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

STORED PROGRAM SYSTEM

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

FIG. 51a

Filed Sept. 13, 1961

FIG. 51b

Filed Sept. 13, 1961

FIG. 510

Filed Sept. 13, 1961

FIG. 51 d

Filed Sept. 13, 1961

FIG. 52a

Filed Sept. 13, 1961

FIG. 52b

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

Filed Sept. 13, 1961

# United States Patent Office

1

3,260,997 STORED PROGRAM SYSTEM Rolland B. Arndt, Minneapolis, and William Weigler, St. Paul, Minn., assignors to Sperry Rand Corporation, New York, N.Y., a corporation of Delaware Filed Sept. 13, 1961, Ser. No. 137,795 92 Claims. (Cl. 340—172.5)

This invention relates to instruction sequencing of a stored program data processing system, and more particu- 10 larly, to one wherein a next instruction can be acquired from memory simultaneously with the execution of a current instruction.

In data processing systems of the digital type, the manipulation and transfer of data words is normally 15 under control of instruction words in a program which is stored internally of the system in a memory unit. The data words are usually also stored within the memory The typical instruction sequencing requires that the memory address of an instruction word be generated 20 to acquire same for subsequently controlling the acquisition and manipulation of a data word within an arithmetic unit or the like. In the so-called single address system, the memory address of each instruction in the stored program is calculated by a unit of the control section 25 designated as a program address counter, or the like. The instruction word itself has a format including at least an operation code specifying the function to be executed, as well as the memory address of a data word to be used in execution of this function. The time re-  $^{30}$ quired for the processing of an instruction is usually measured commencing from the time that the program address counter references the memory to acquire the instruction itself, and ending with the time that the execution of the instruction using the data word has been 35 terminated. Therefore, for programming purposes, the processing time of each instruction in the program covers a period occupied by two successive memory reference cycles, the first being the reference for the instruction word and the second being the reference for the data  $^{40}$ word whose address is specified by the previously acquired instruction. Thus, for most programs devised for prior art systems, the number of arithmetic operations which can be processed in a given period of time is substantially less than would be the case if an execution 45 (which includes a memory reference for the operand) could be performed during each machine cycle.

The present invention permits a substantial decrease in effective processing time of instructions of a stored instruction word from a memory unit at the same time that the execution of a previously acquired instruction is being performed. Thus, as soon as the execution of a previously acquired instruction is terminated, a new instruction has already been placed into the control unit 55 from the memory unit, so that a new execution cycle can commence immediately without requiring an intervening Therefore, for cycle for instruction acquisition only. purposes of the programmer, each machine cycle of the system can normally be considered one in which a processing of a different instruction will occur. There would therefore be but few machine cycles in which the arithmetic unit of the system cannot be utilized, whereas in the

prior art, the arithmetic unit normally stands idle every other cycle. For a given number of instructions in the program, the total time required to process these instructions is therefore substantially less and may approach onehalf the time required to process the same number of instructions in the typical prior art system.

The above advantages of the present invention are obtained by providing at least two individual memories each of which can store both instruction and data words, and each of which has its own address and buffer transfer registers for gaining access thereto. The invention also has the ability to reference both memories simultaneously, one for the next instruction and the other for the data word to be used in execution of the previously acquired instruction. This feature is herein designated as an overlap instruction sequencing cycle. However, in certain programs it may be necessary to acquire the next instruction from the same memory that issues the operand data word used in the execution of the current instruction. In such cases, the next instruction does not begin until the operand used in the current instruction is extracted from this memory. Thus, the acquisition of the data word operand for the current instruction takes precedence over acquisition of the next instruction so that the overlap sequencing feature is inhibited, and the next instruction cannot be acquired from its memory until one machine cycle later. In this event, the programmer must consider that the processing time of the next instruction (whose acquisition has been delayed by inhibition of overlap) is extended by a time equal to the duration of one machine cycle.

It is therefore an object of the present invention to provide a data processing system having at least two individual and independent memory units for storing both instruction and data words, together with means for referencing said memory units simultaneously with a view toward extracting an instruction from one and a data word from the other.

Another object of the present invention is to provide a data processing system having at least two independent memory units for storing both instruction and data words wherein acquisition of a data word takes priority over acquisition of an instruction word if both are stored in the same memory unit.

A further object of the present invention is to provide a data processing system of the above described kind which utilizes a double rank instruction register for holding two instruction words at a time.

A further object of the present invention is to provide program by normally permitting the acquisition of an 50 a data processing system of the above described type which employs single address instructions, and has a double rank program address counter capable of simultaneously holding the memory addresses of two successive instructions of the stored program.

For some instruction words, such as those specifying multiply, divide, square root, and shift operations, the actual execution time in most cases requires more than one machine cycle as compared to execution times of one machine cycle for the simpler arithmetic operations such as add, subtract, etc. The present system provides control circuitry within the arithmetic unit for executing these extended sequence instructions without need for the instruction word to be continuously held in the program unit

execution is terminated. Therefore, upon initiation of the extended sequence execution, the program unit may be cleared of the initiating instruction word, and subsequent instrutcion words of the program are acquired from memory and executed by units of the system other than the arithmetic unit. Thus, the present system provides a maximum utilization of time in that the processing of non-arithmetic instructions, which follow an extended sequence instruction, need not be delayed until execution of the extended sequence istruction is terminated. ever, if a subsequent instruction is acquired which requires use of the arithmetic unit at the time that the arithmetic unit is executing a previously acquired extended sequence instruction, then the memory instruction sequencing of the system must be inhibited until the arith- 15 metic unit is free to accept another arithmetic instruction.

It is therefore another object of the present invention to provide a data processing system having at least two independent memories for storage of both instruction and data words wherein the acquisition and execution of non-arithmetic instructions can continue with overlap even though a previously acquired extended sequence instruction is being executed by the arithmetic unit.

For certain special instructions, the above described novel overlap feature must be modified. For example, 25 the execution of some instruction words requires that a jump be made in the program sequencing from an instruction memory address held by the program address counter to an instruction memory address held in the instruction word itself. In this case, the program address counter is 30 inhibited from referencing memory for the next instruction during one machine cycle, at which time a memory is referenced by a portion of the instruction word itself. Furthermore, a class of instruction words may require that the execution of an instruction word be prevented, 35with a skip being made to the next following instruction word in the program. This skip operation is usually conditional upon the result of an arithmetic operation in the arithmetic unit. Therefore, if the skip condition is sensed to be present, the program address counter is required to 40 calculate the address of the next instruction following the instruction to be skipped.

Consequently, yet another object of the present invention is to provide means in the system of the above described type to inhibit the normal operation of a program address counter when a jump instruction is to be executed.

A further object of the present invention is to modify the operation of the program address counter in the system of the above described type if an instruction skip con- 50 lators; dition is detected.

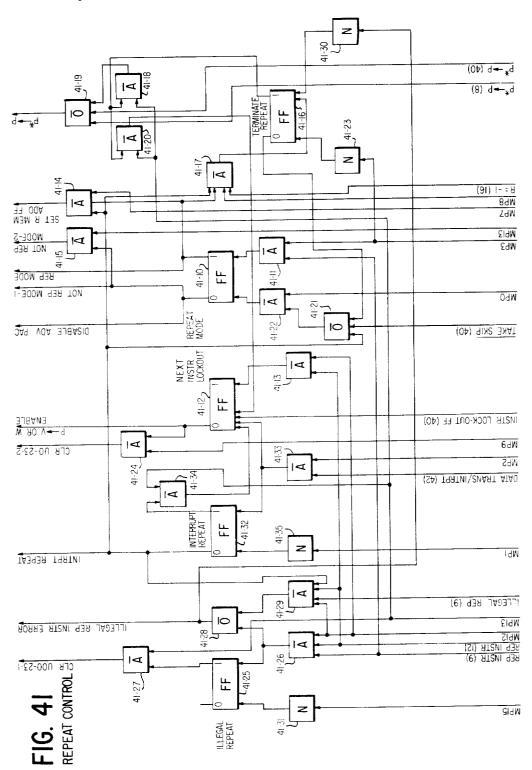

For repeated executions of a particular instruction word in the program, the technique in the present system is to precede the repeated instruction by a special instruction for the purpose of setting up certain control circuits designed to carry out the repeated operations. In this event, the repeated instruction is maintained in the instruction register until all of the required number of executions is terminated. Therefore, overlap of instruction acquisition and data operand acquisition is inhibited for this period of time so that the repeated instruction cannot be erased from the instruction register by the next following instruction.

It is therefore another object of the present invention to provide control means in the system of the above described type whereby the acquisition of instruction words from memory is inhibited during the execution of a repeated instruction.

Other conditions which affect the overlap instruction sequencing of the present invention are those in which a request is made for the computer to transfer a data word between it and some external unit, and those in which a request is made to interrupt the processing of main program instructions for the purpose of initiating a sub- 75 trol;

4

routine opeartion. In either of these cases, the overlap function is inhibited for at least one machine cycle so that special instructions can be forced into the program instruction register from sources other than the individual memories.

It is therefore a further object of the present invention to provide means in a system of the above described type to inhibit overlap, and thereby delay acquisition of an instruction in the program, upon granting of a request for a data word transfer or the initiating of a sub-routine.

These and other objects of the present invention will become apparent during the course of the following description when taken in conjunction with the drawings, which illustrate a preferred embodiment of the invention for carrying out the above described novel features.

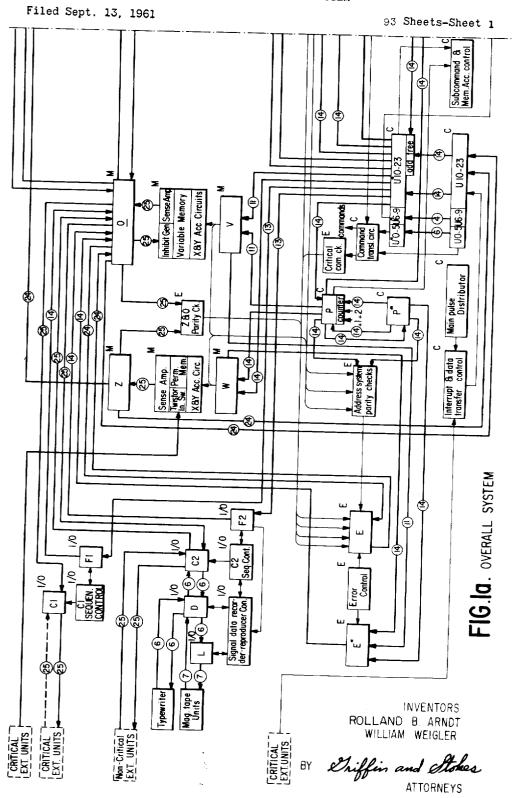

FIGURES 1a and 1b show an overall block diagram of the system incorporating the present invention;

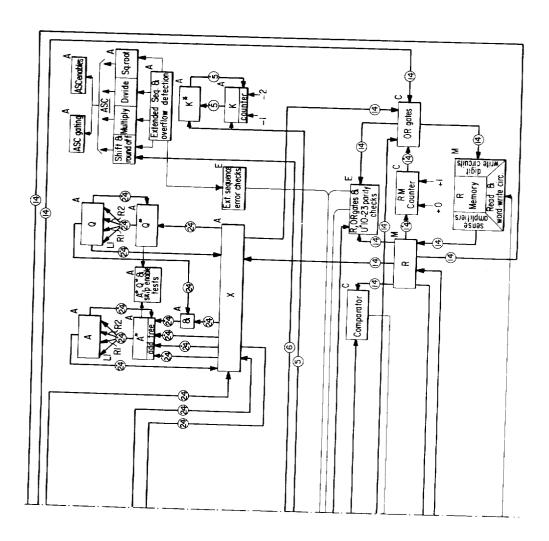

FIGURE 2 is a block diagram of the variable memory access circuits;

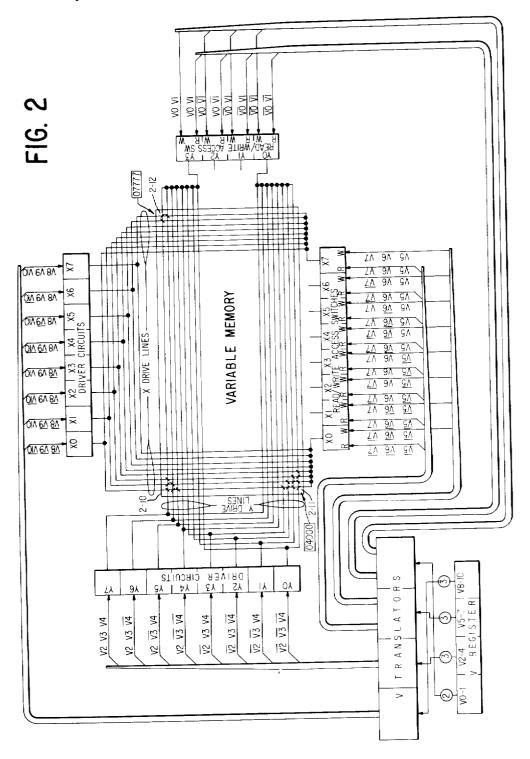

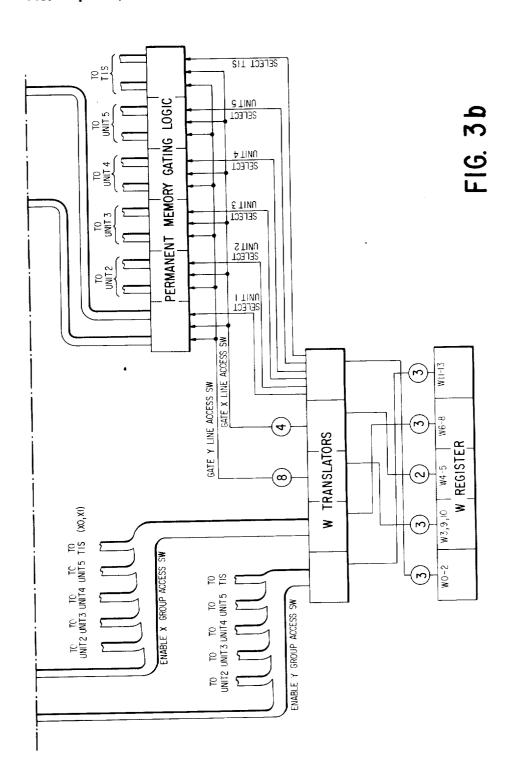

FIGURES 3a and 3b comprise a block diagram of the permanent memory access circuits;

FIGURES 4a through 4f show the basic logic elements used in the present system;

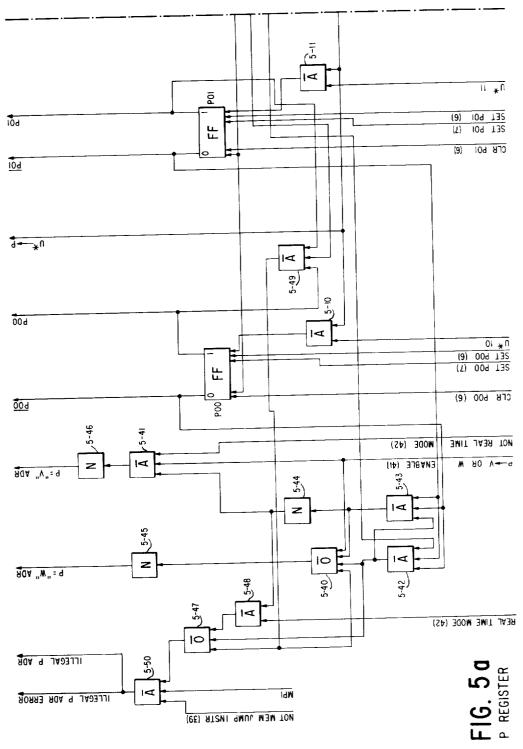

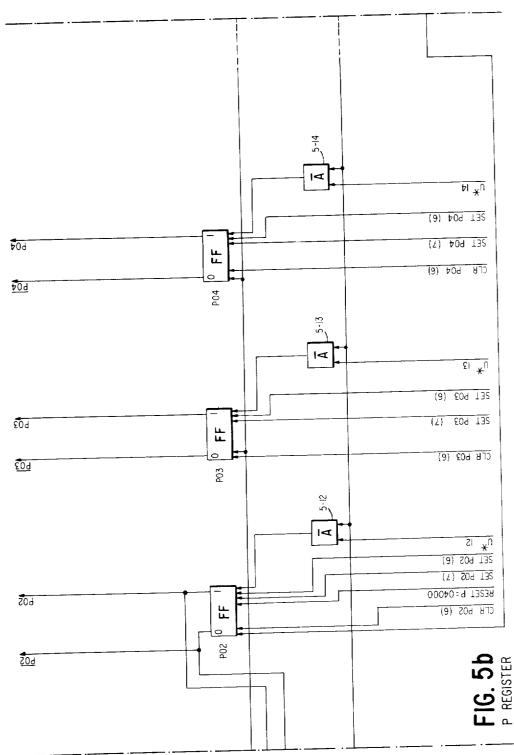

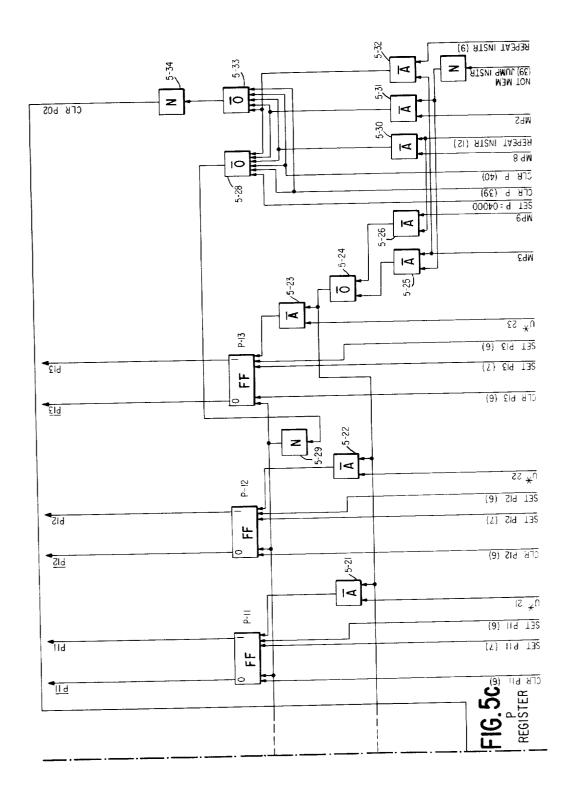

FIGURES 5a, 5b, and 5c show the P register;

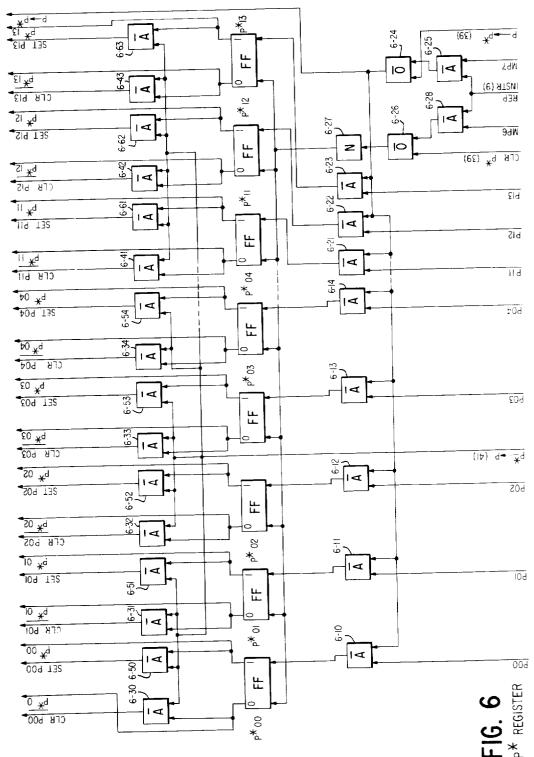

FIGURE 6 shows the P\* register;

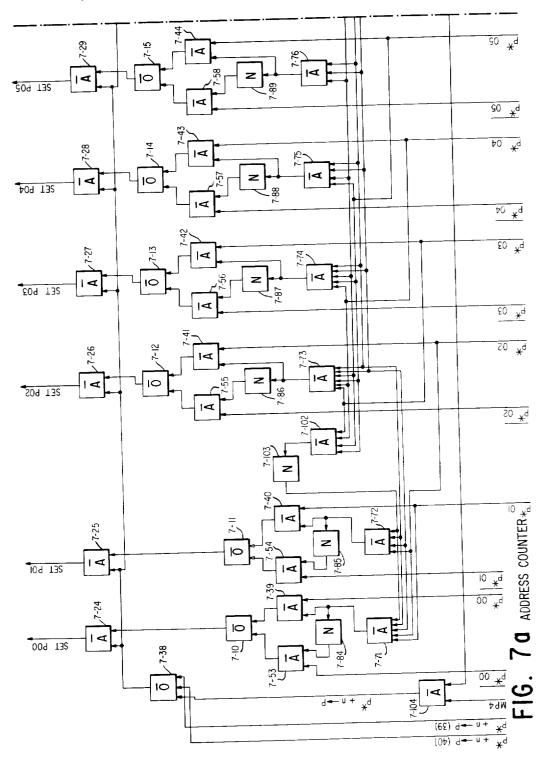

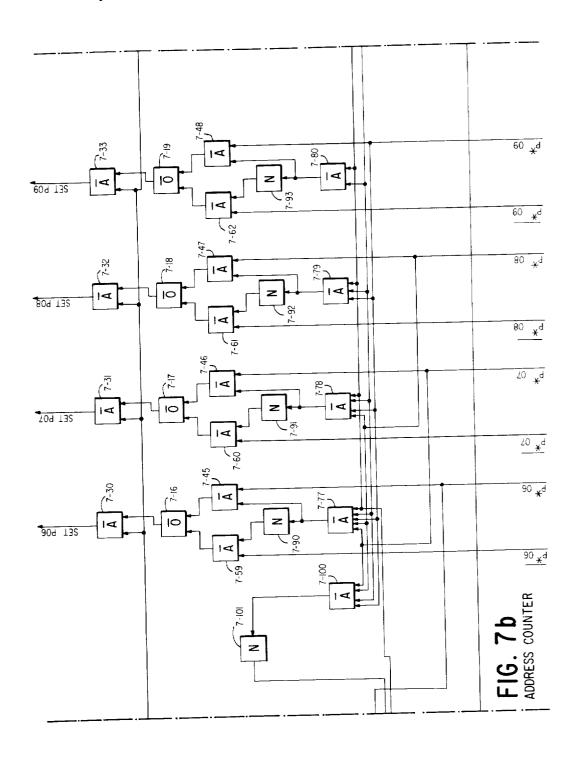

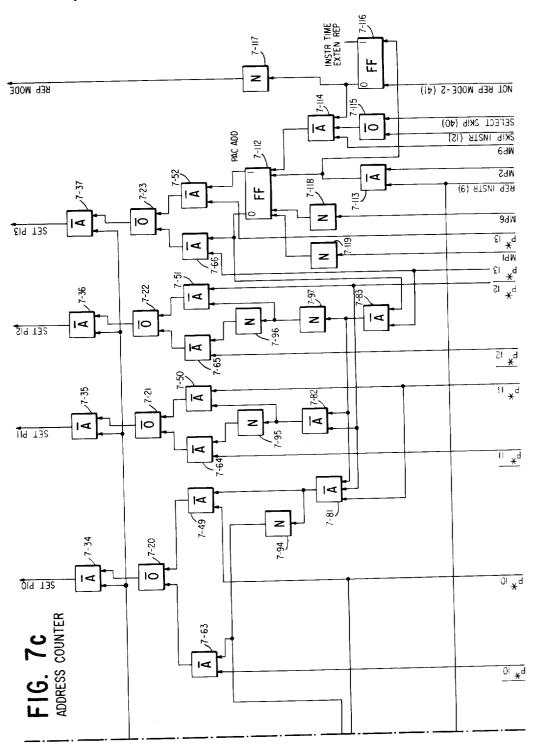

FIGURES 7a, 7b, and 7c show the PAC Address Counter;

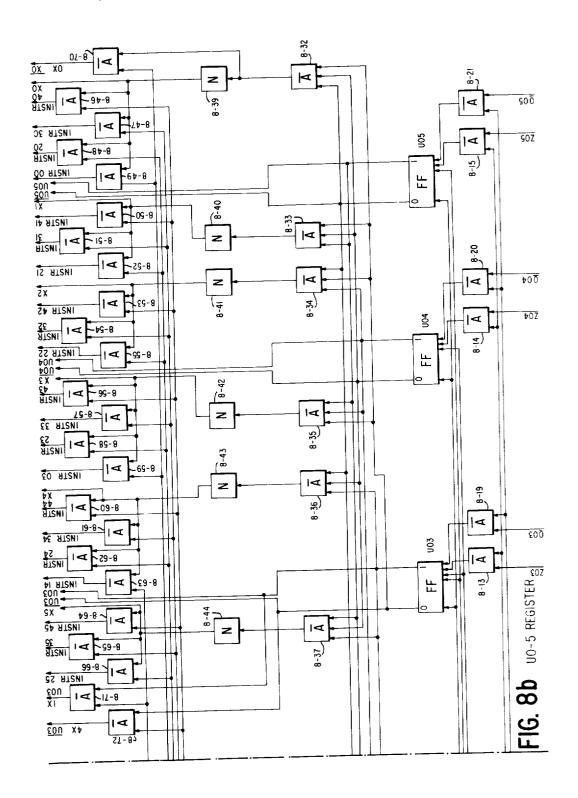

FIGURES 8a and 8b show U register stages 0 through 5;

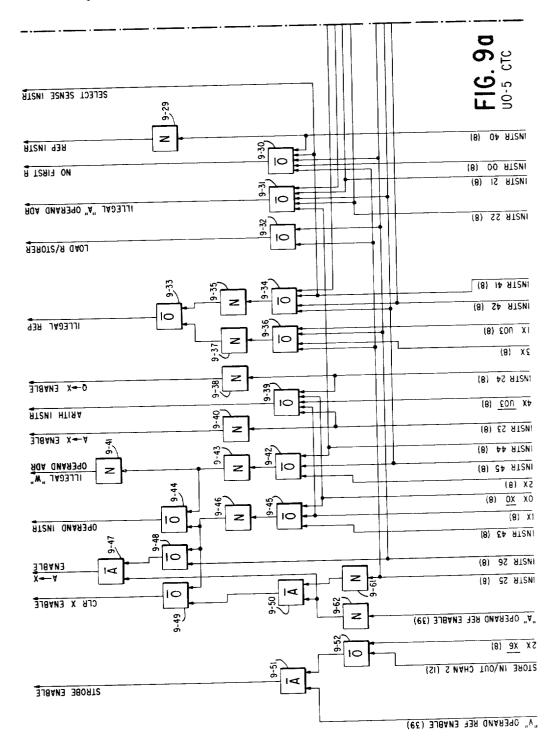

FIGURES 9a and 9b show the command translator circuits for the U register;

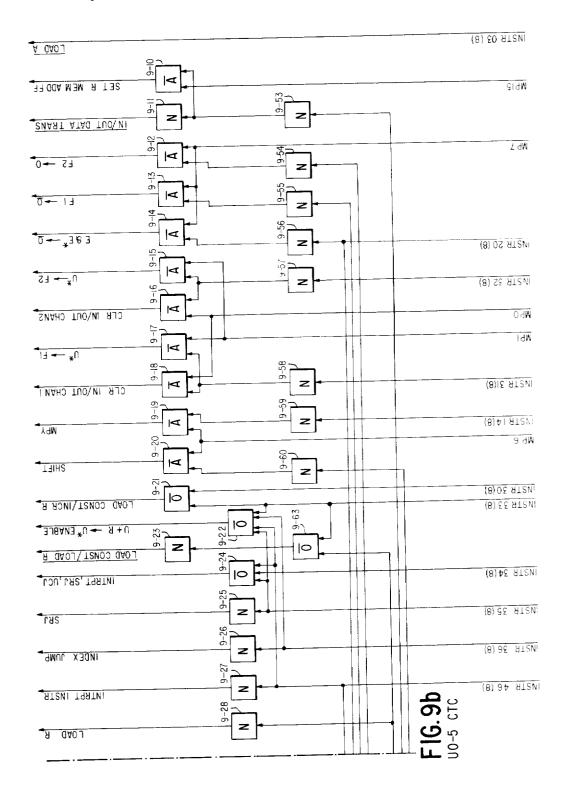

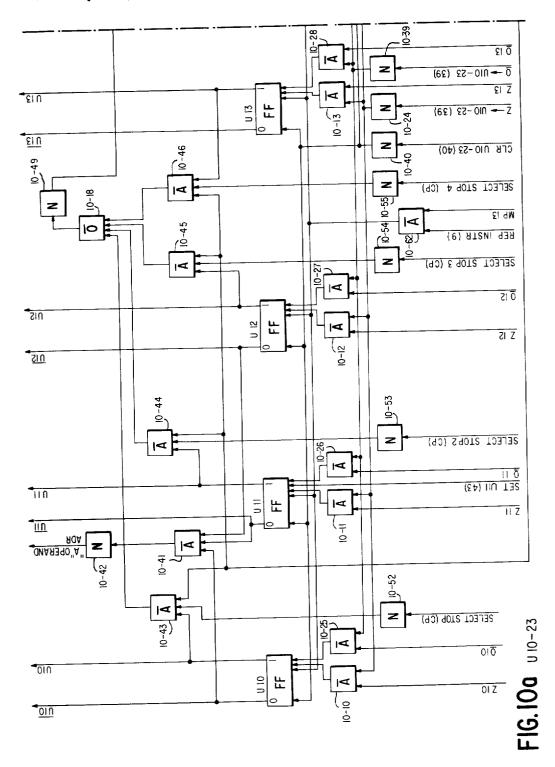

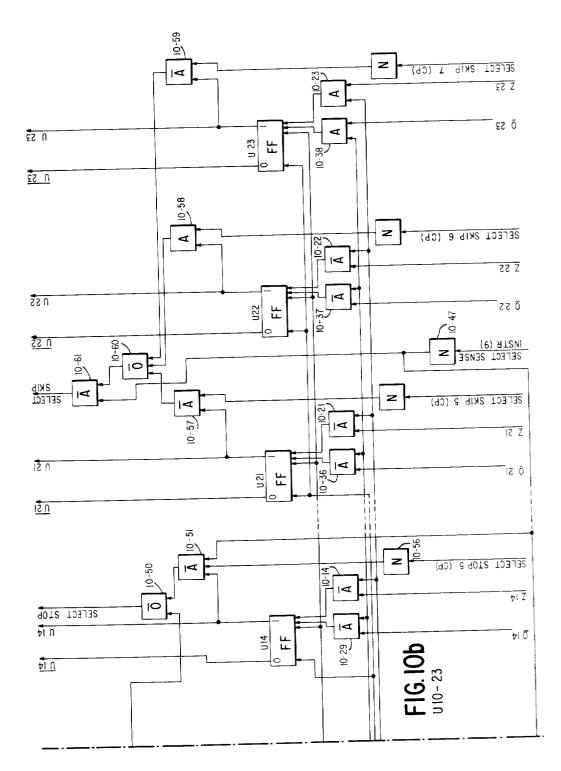

FIGURES 10a and 10b show U register stages 10 through 23;

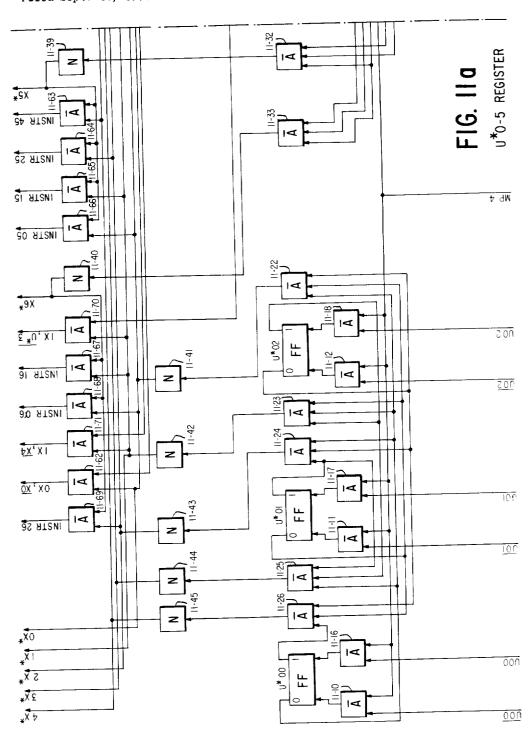

FIGURES 11a and 11b show  $U^*$  register stages  $\mathbf{0}$  through  $\mathbf{5}$ ;

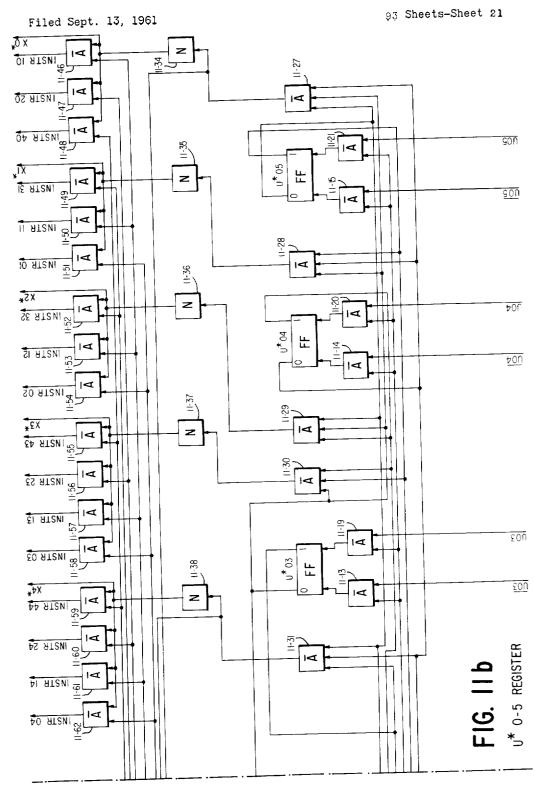

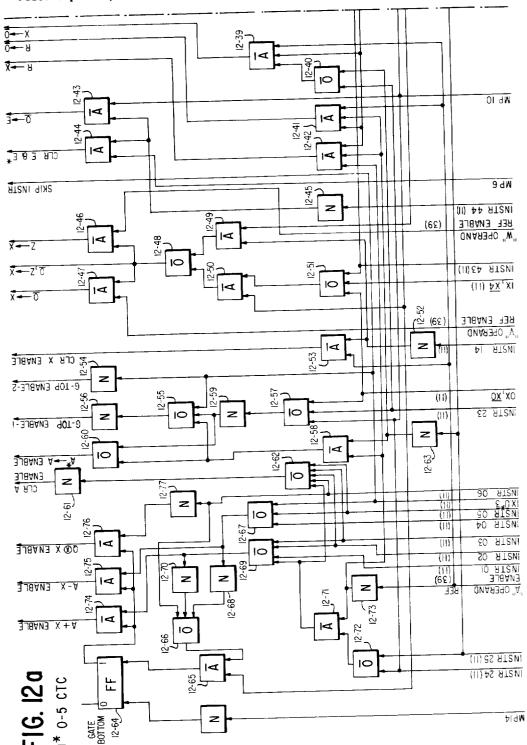

FIGURES 12a and 12b show the command translator circuits for the U\* register;

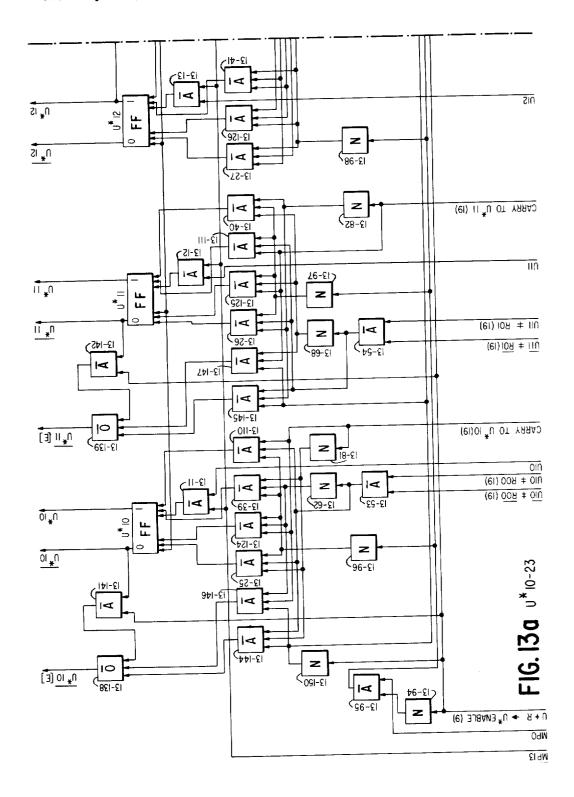

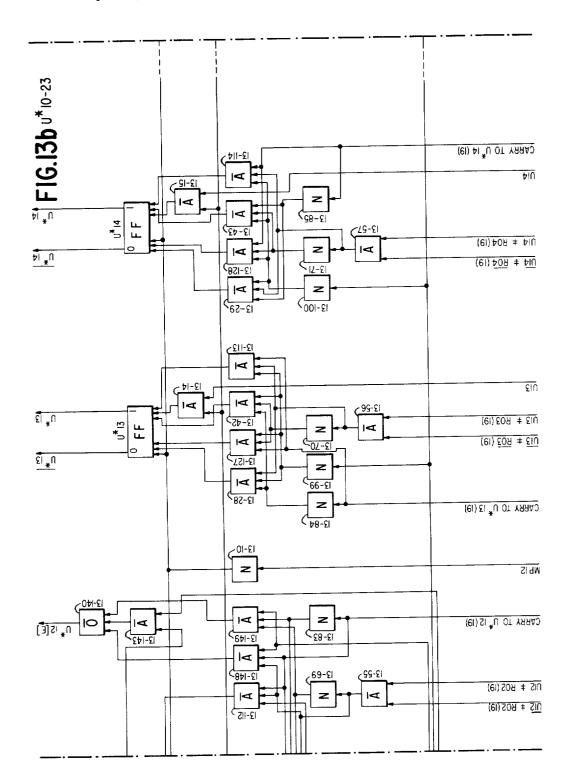

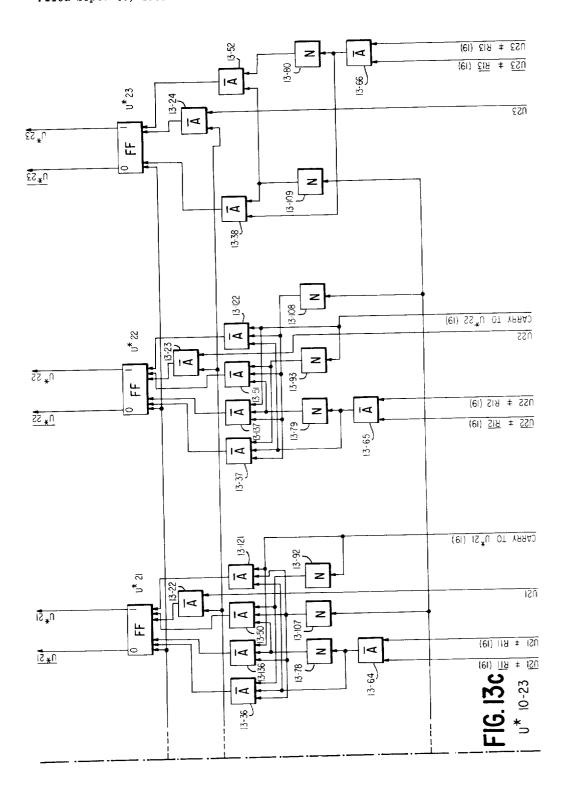

FIGURES 13a, 13b and 13c show U\* register stages 10 through 23;

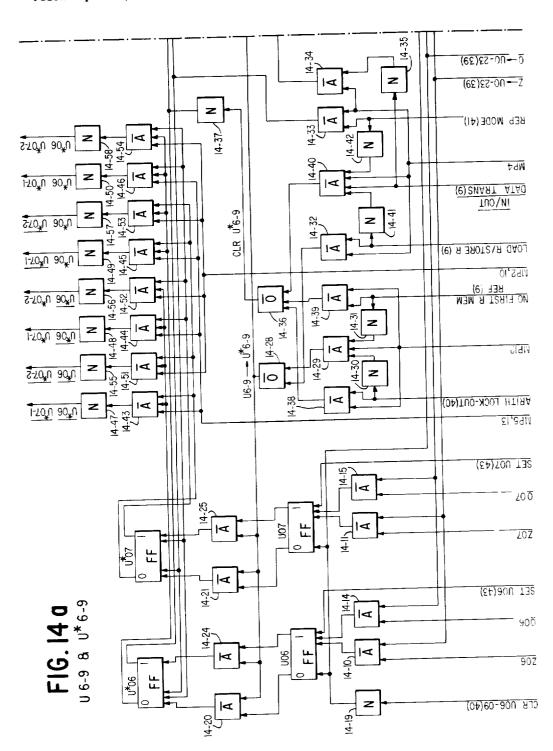

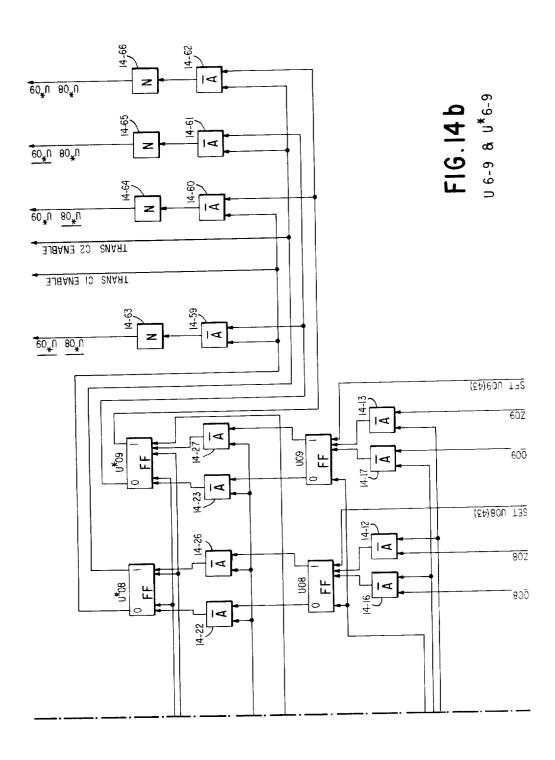

FIGURES 14a and 14b show U register stages 6 through 9 and U\* register stages 6 through 9;

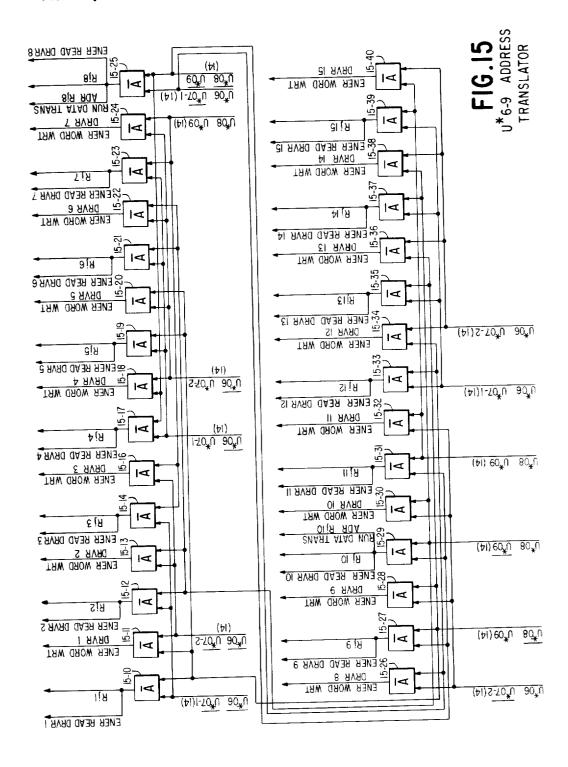

FIGURE 15 shows the address translator circuits for U\* register stages 6 through 9;

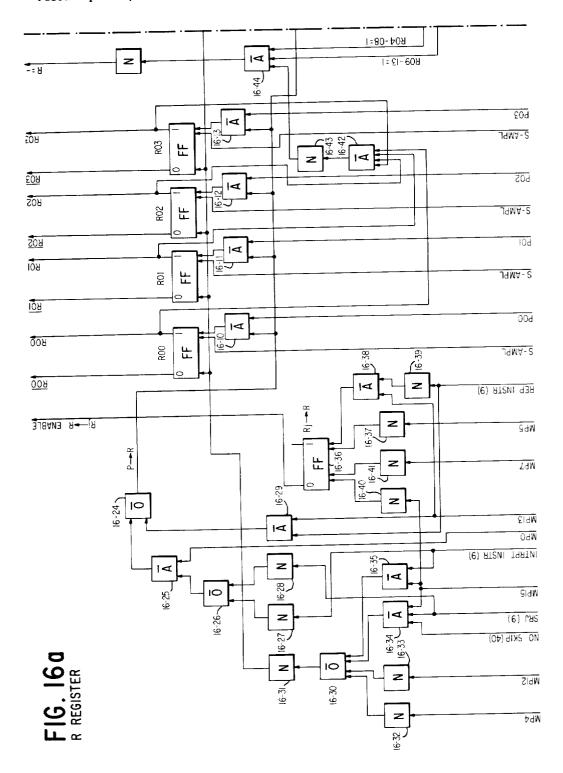

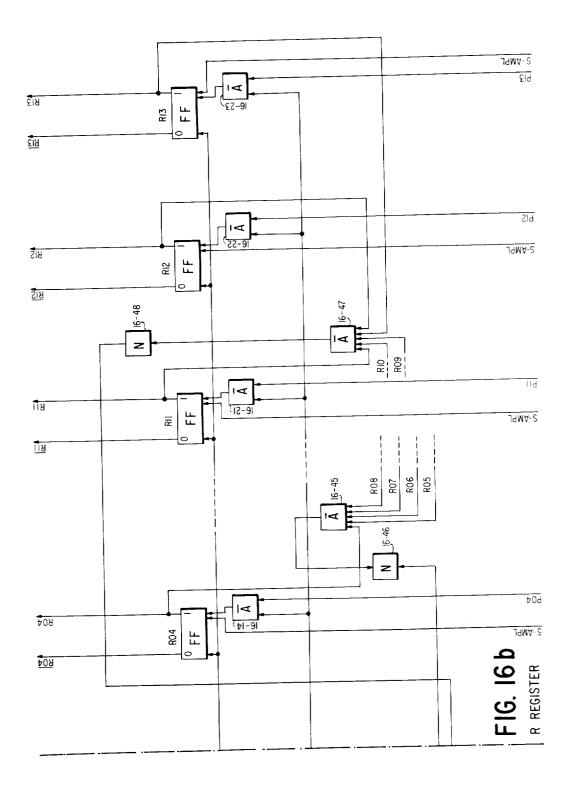

FIGURES 16a and 16b show the R register;

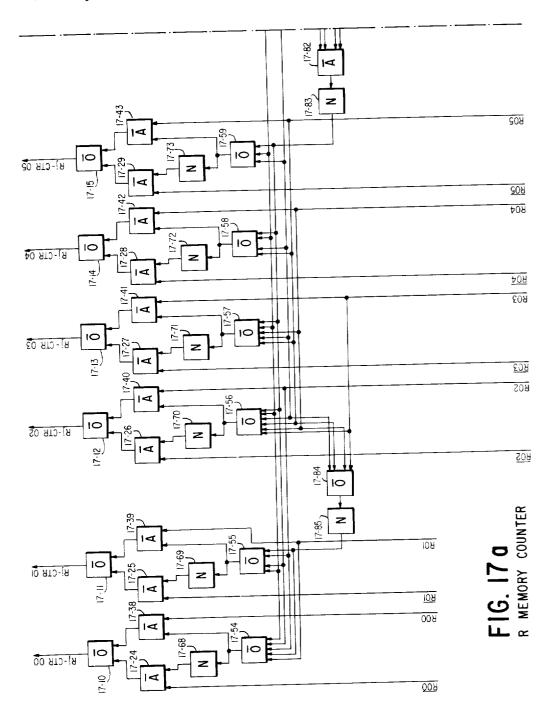

FIGURES 17a and 17b show the R Memory Counter;

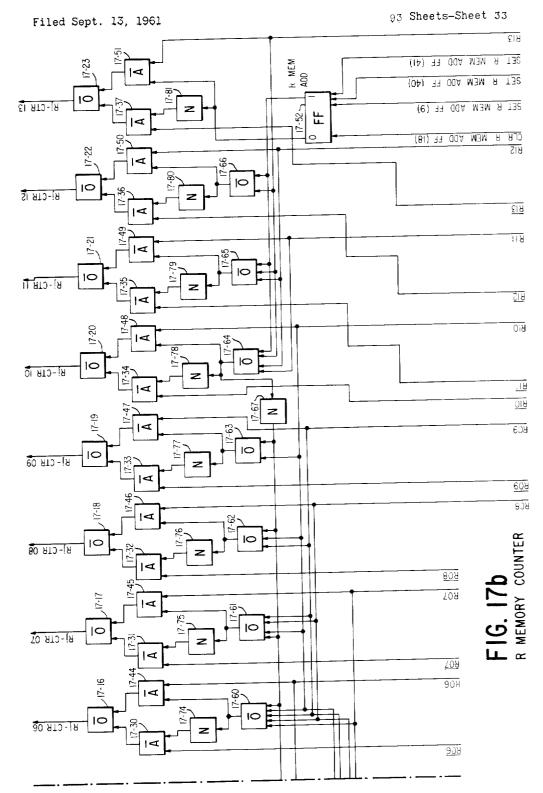

FIGURES 18a and 18b show the OR gates;

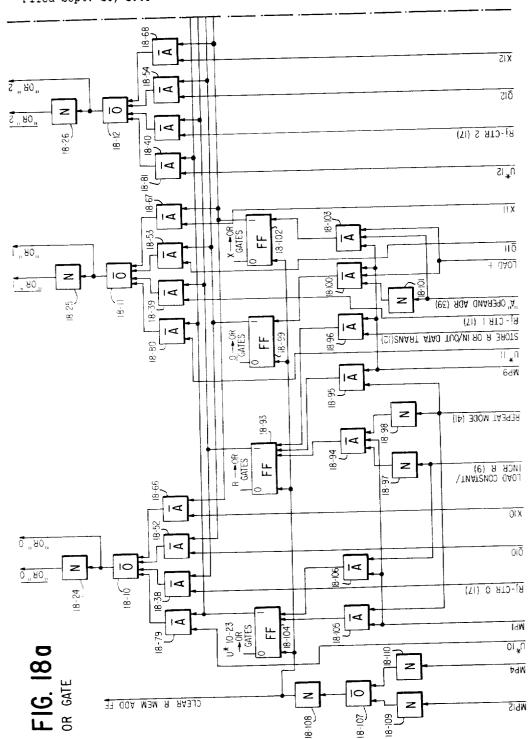

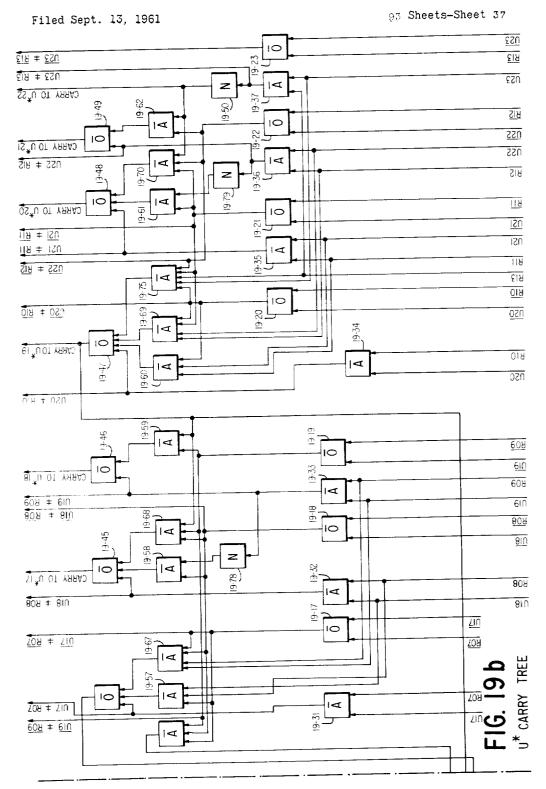

FIGURES 19a and 19b show the U\* Carry Tree;

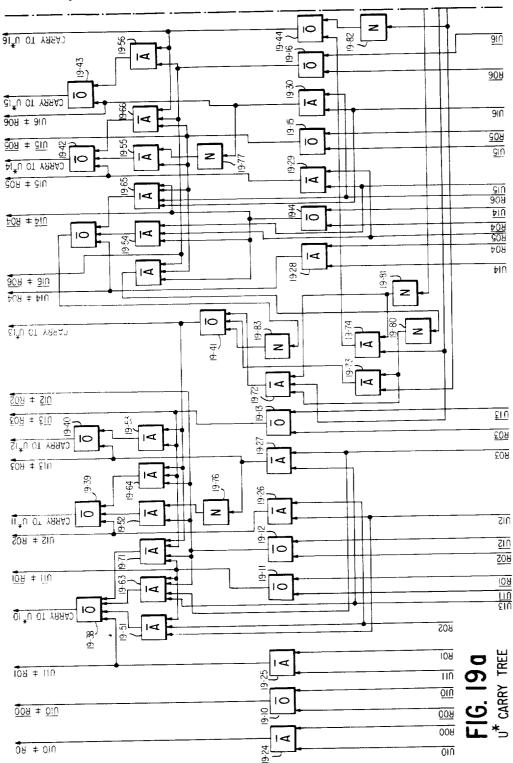

FIGURE 20 shows the comparator;

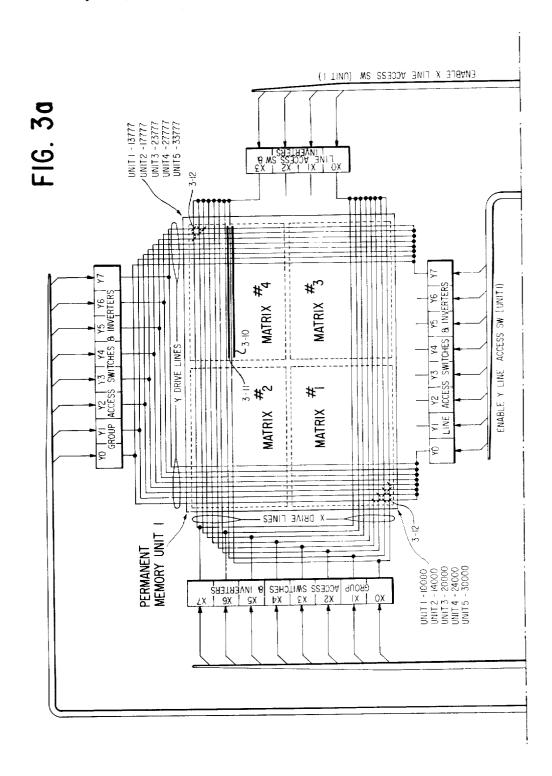

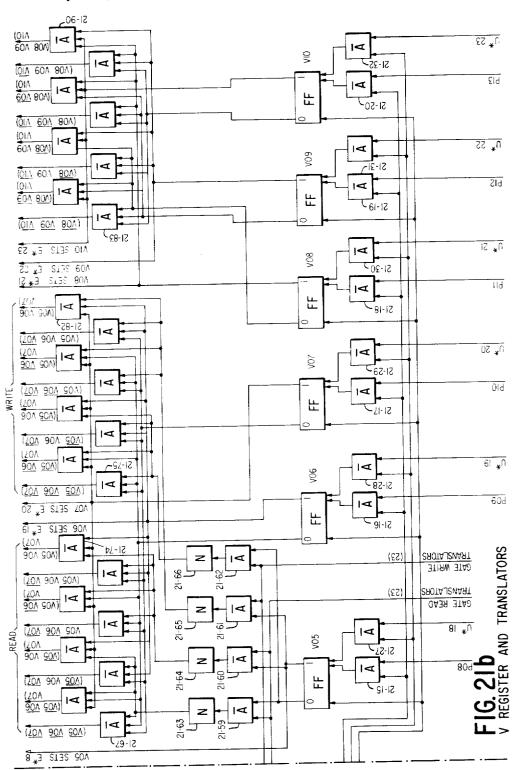

FIGURES 21a and 21b show the V register and trans-0 lators;

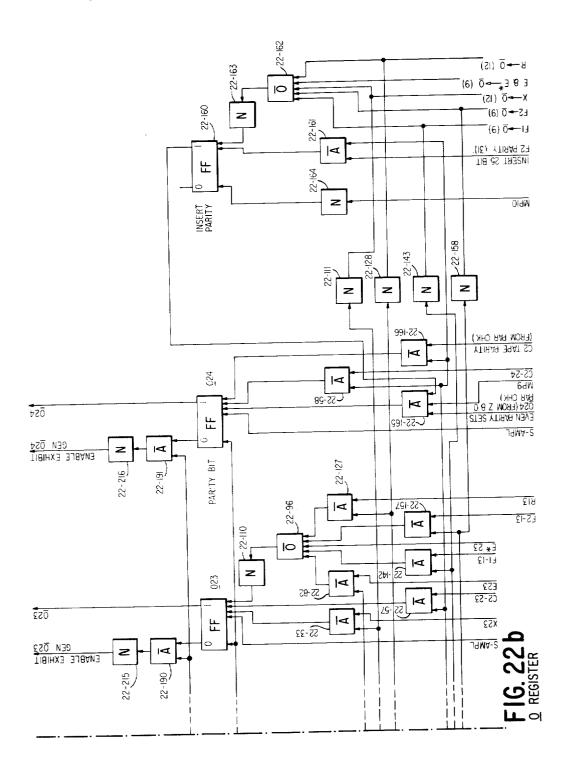

FIGURES 22a and 22b show the O register;

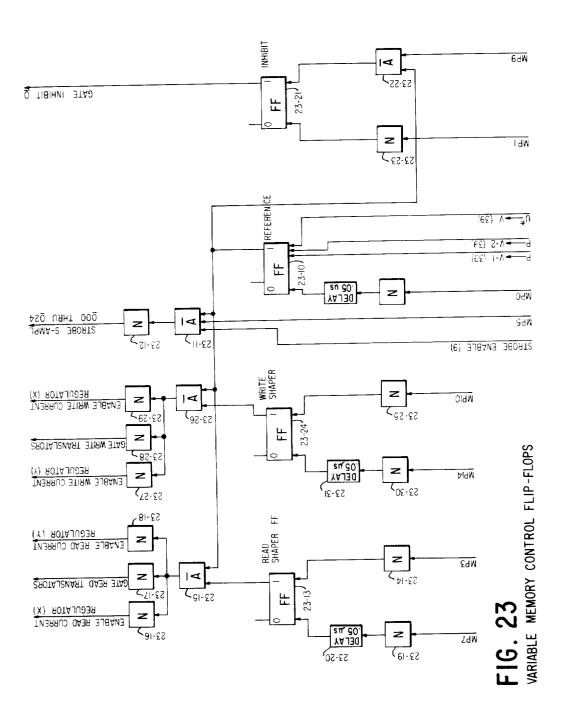

FIGURE 23 shows the variable memory control flip-flops;

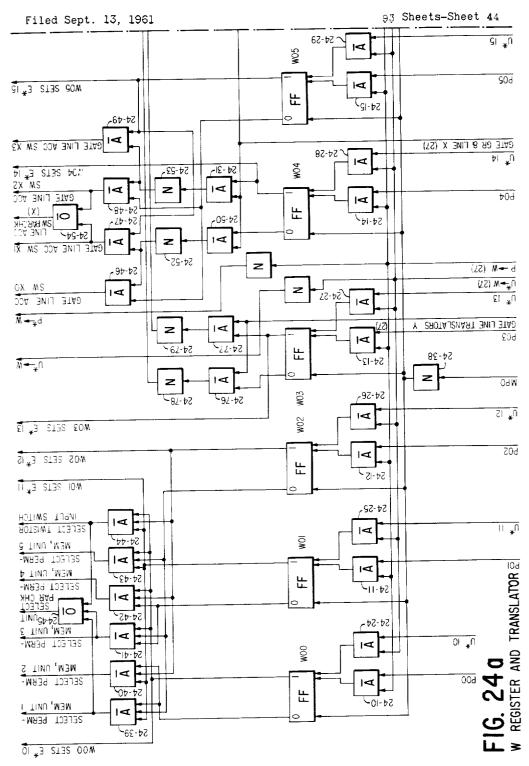

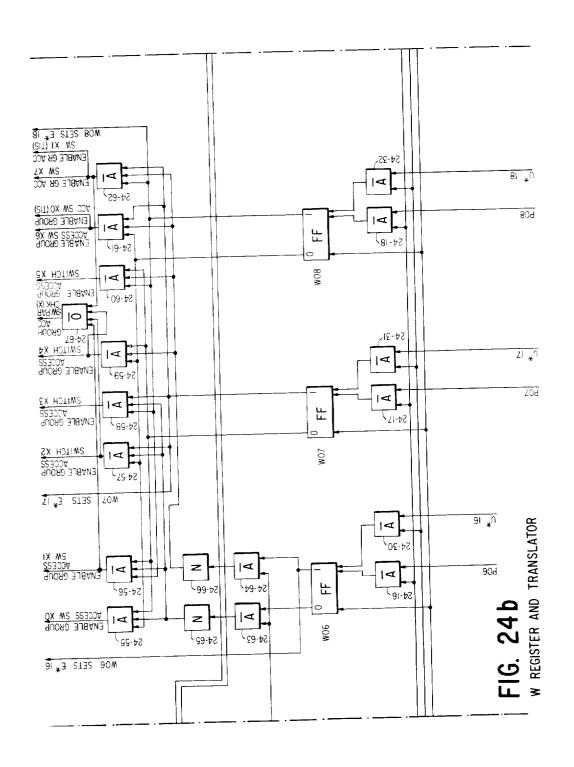

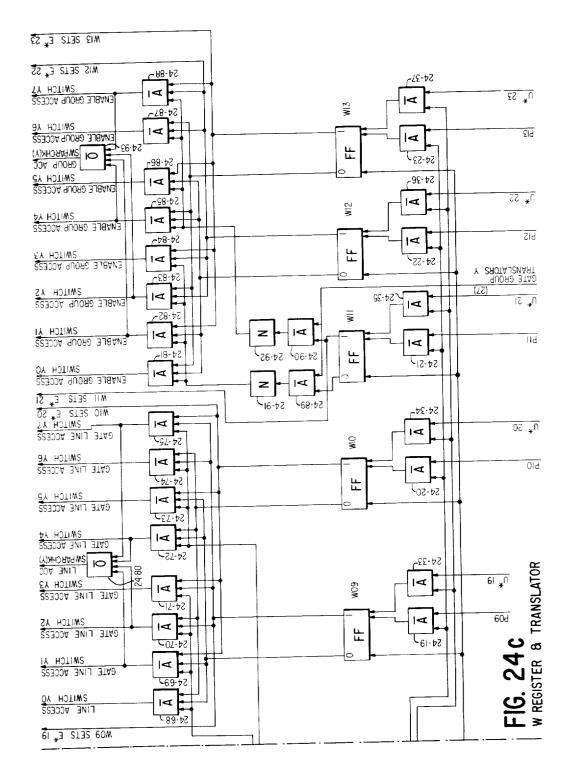

FIGURES 24a, 24b and 24c show the W register and translators;

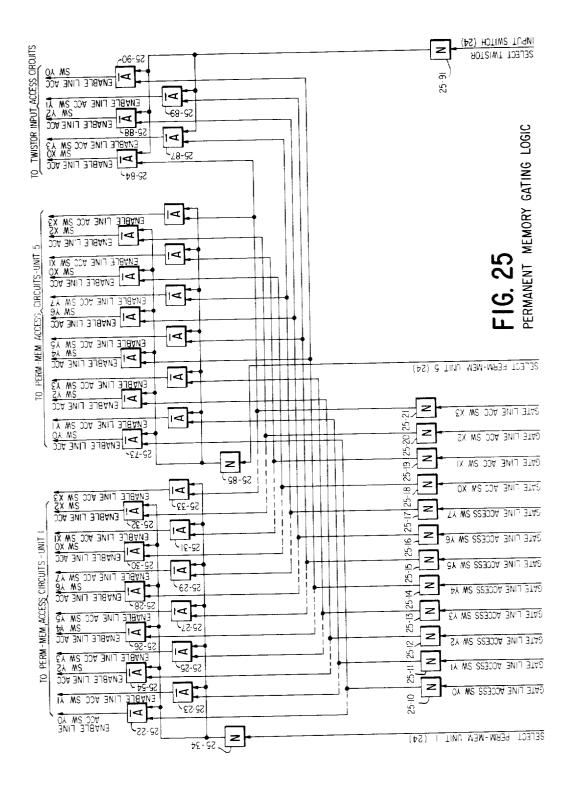

FIGURE 25 shows the permanent memory gating logic;

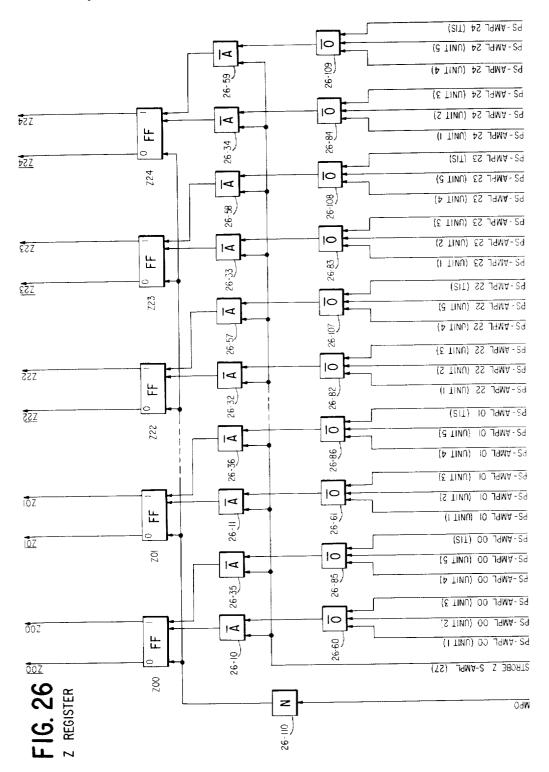

FIGURE 26 shows the Z register;

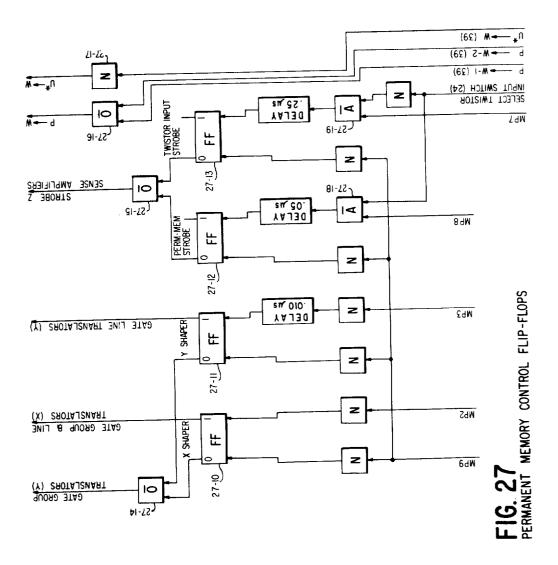

FIGURE 27 shows the permanent memory control flip-flops;

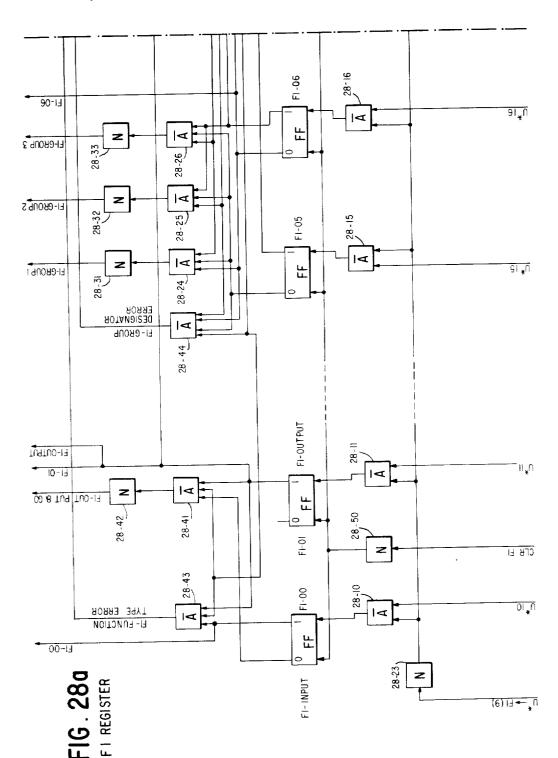

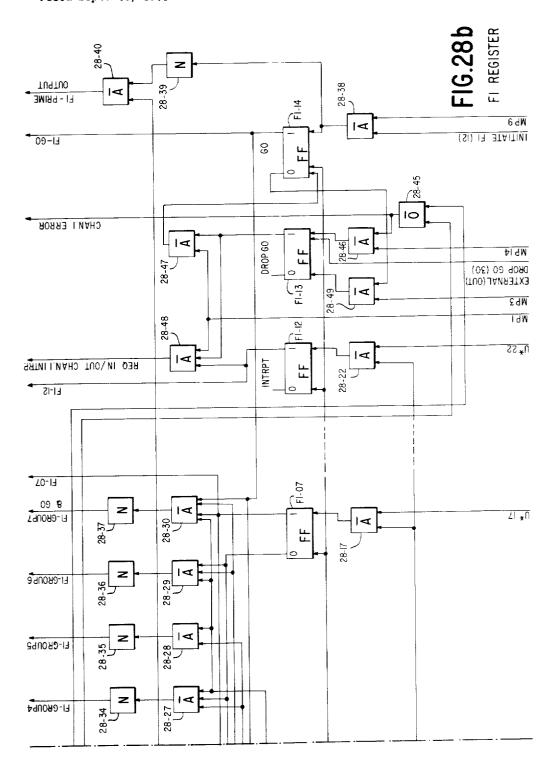

FIGURES 28a and 28b show the F1 register;

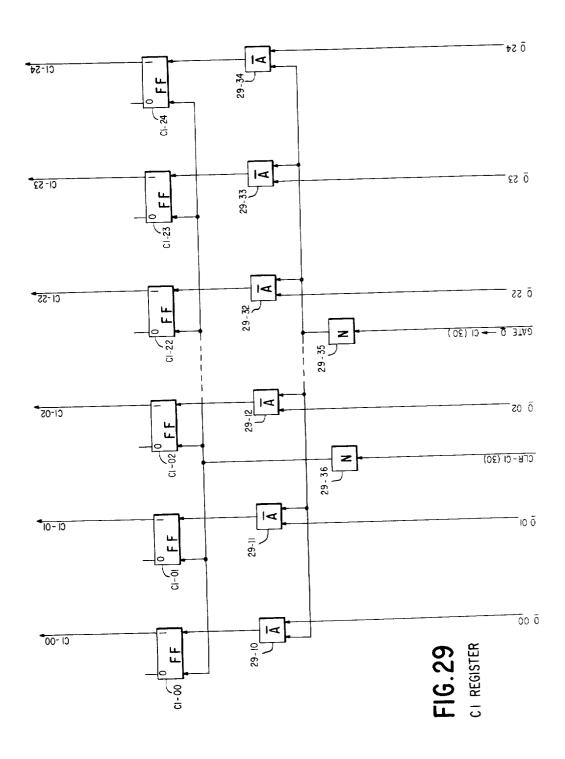

FIGURE 29 shows the C1 register;

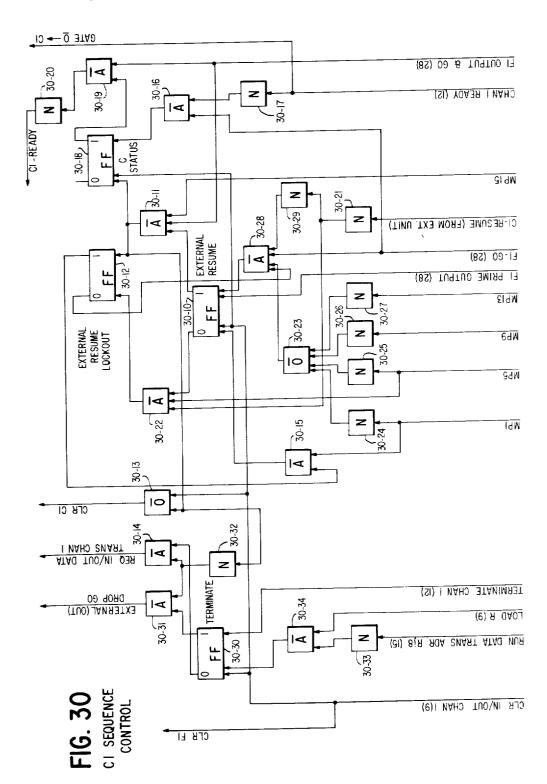

FIGURE 30 shows C1 sequence control;

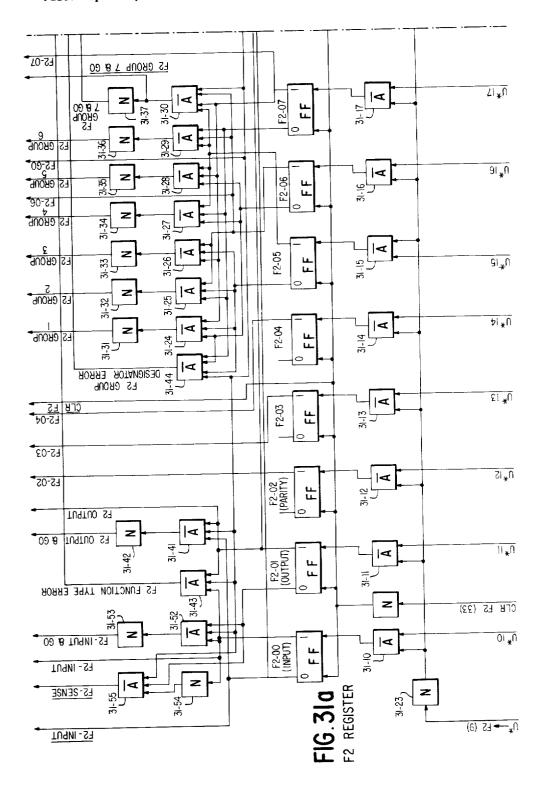

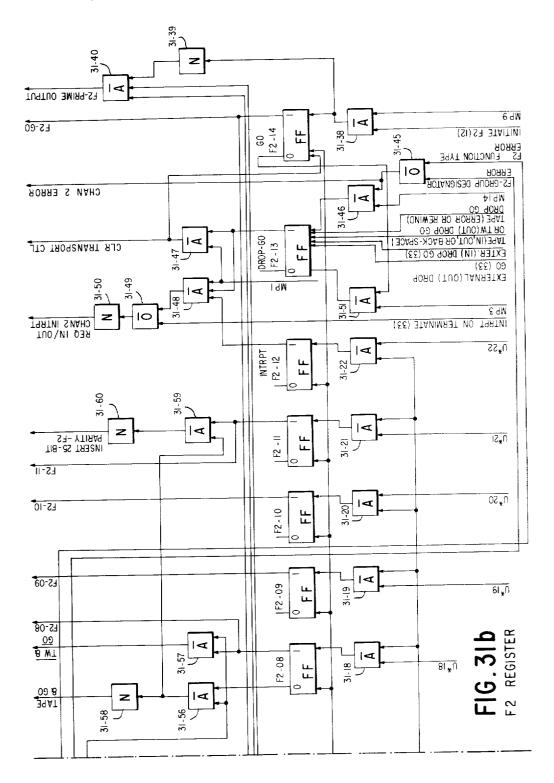

FIGURES 31a and 31b show the F2 register;

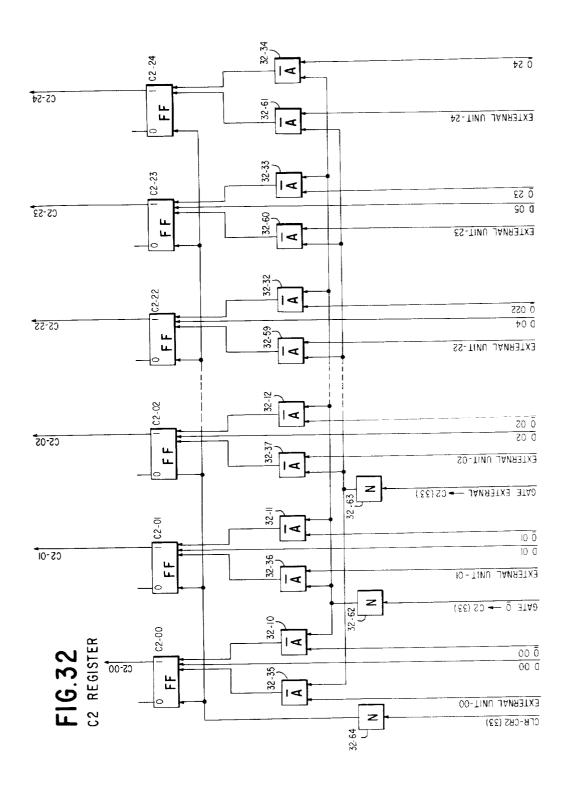

FIGURE 32 shows the C2 register;

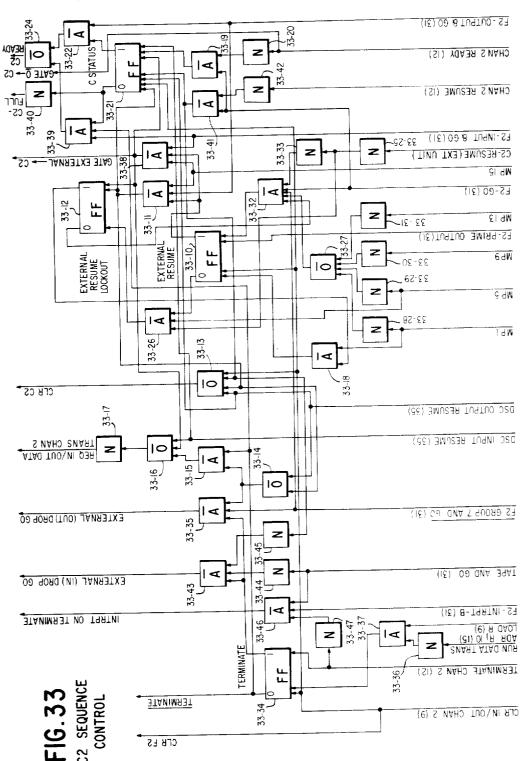

FIGURE 33 shows C2 sequence control:

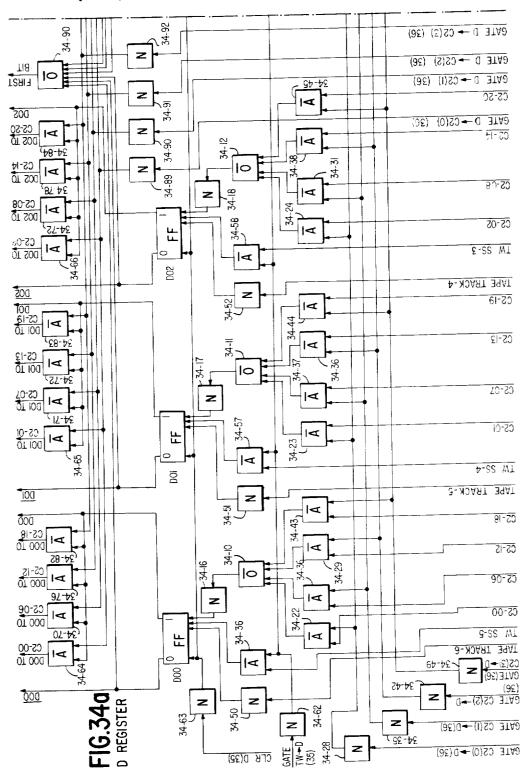

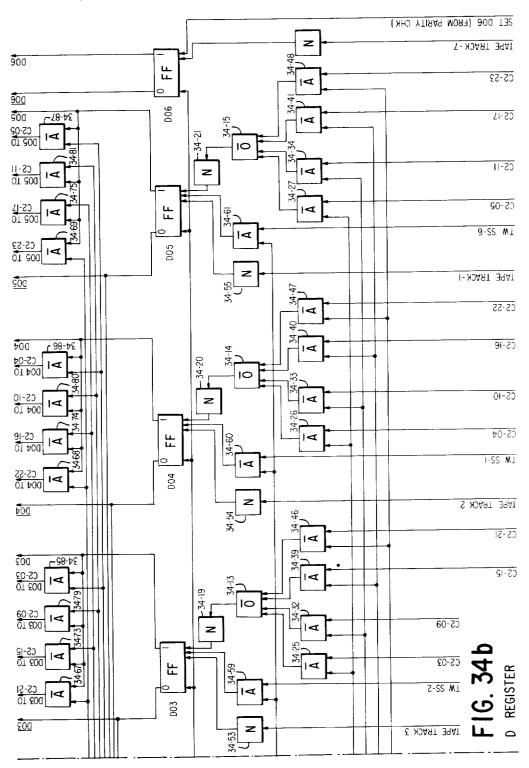

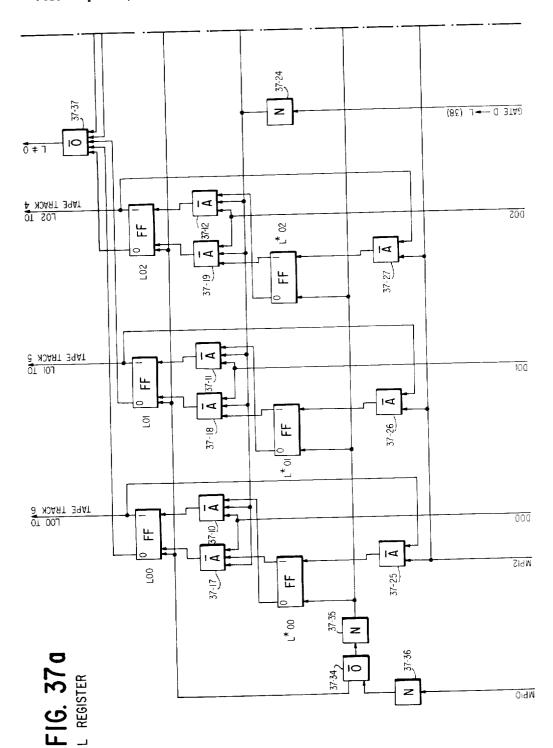

FIGURE 34a and 34b show the **D** register;

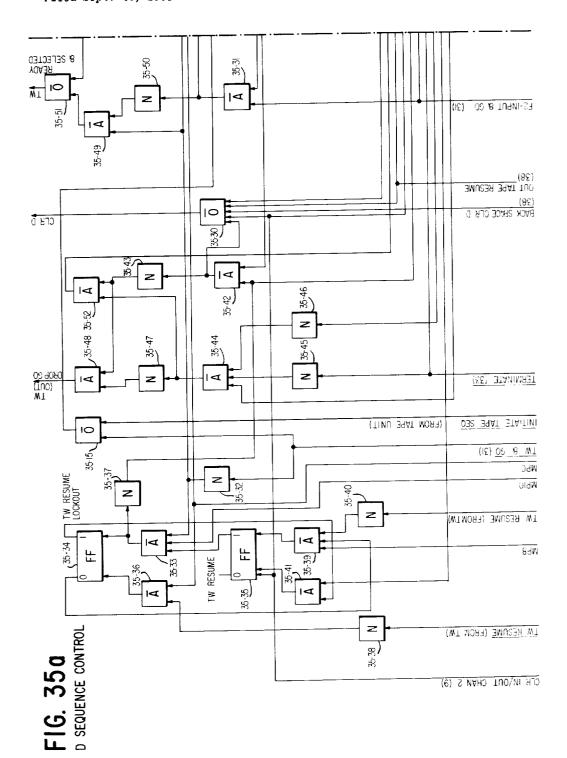

FIGURES 35a and 35b show D sequence control;

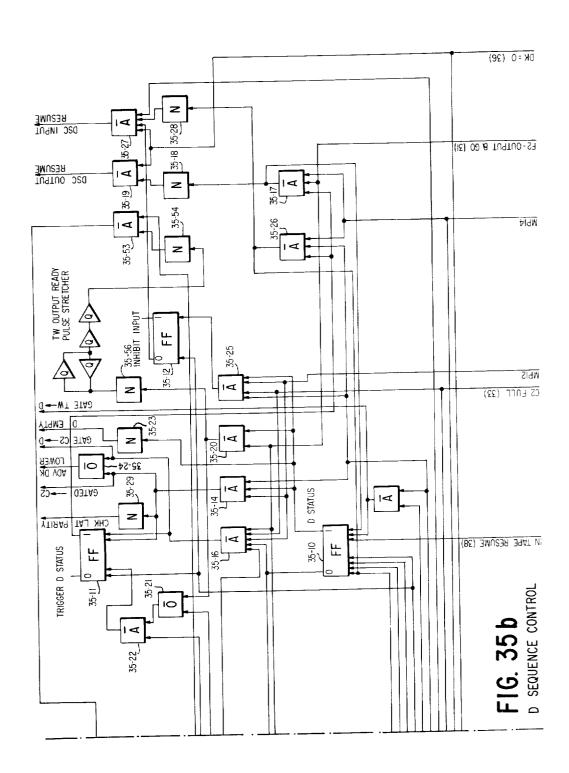

FIGURE 36 shows the D counter;

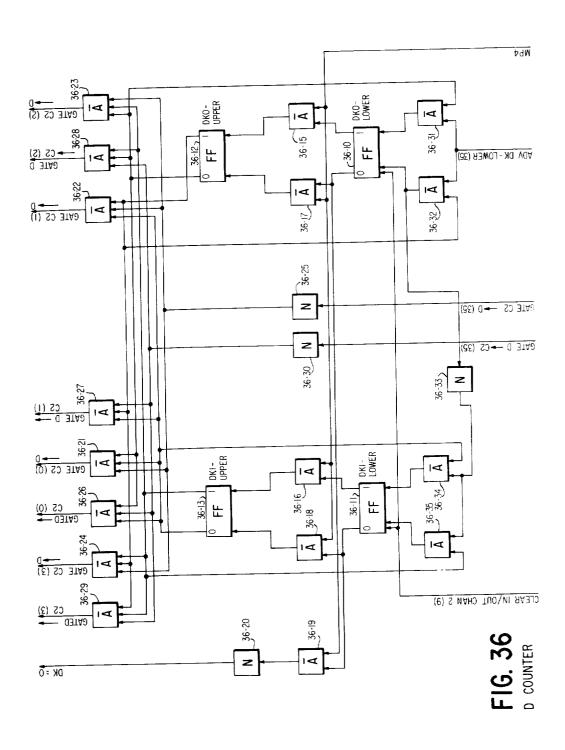

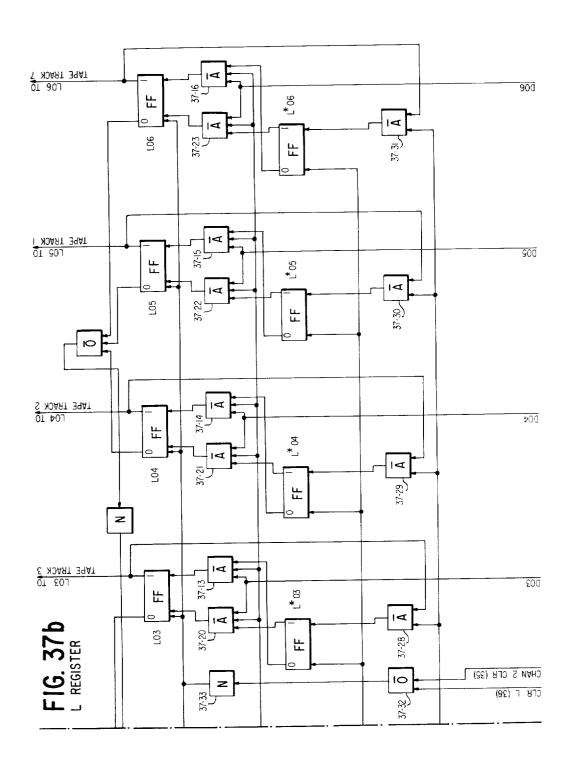

FIGURES 37a and 37b show the L register:

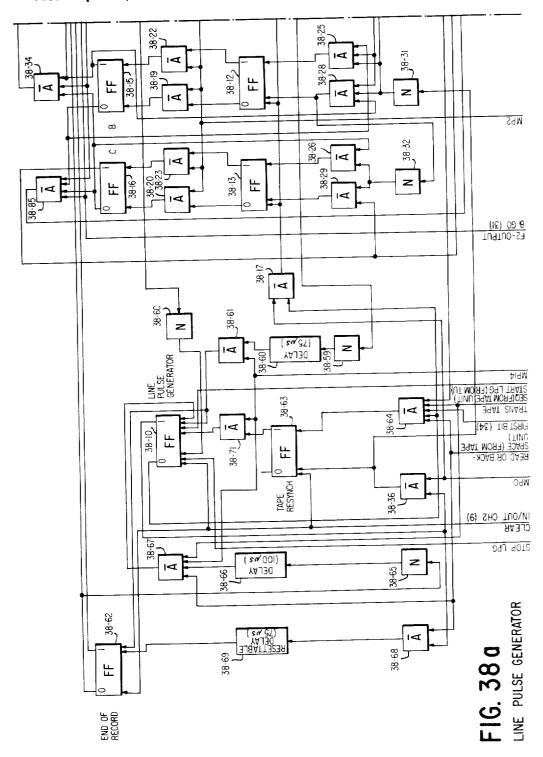

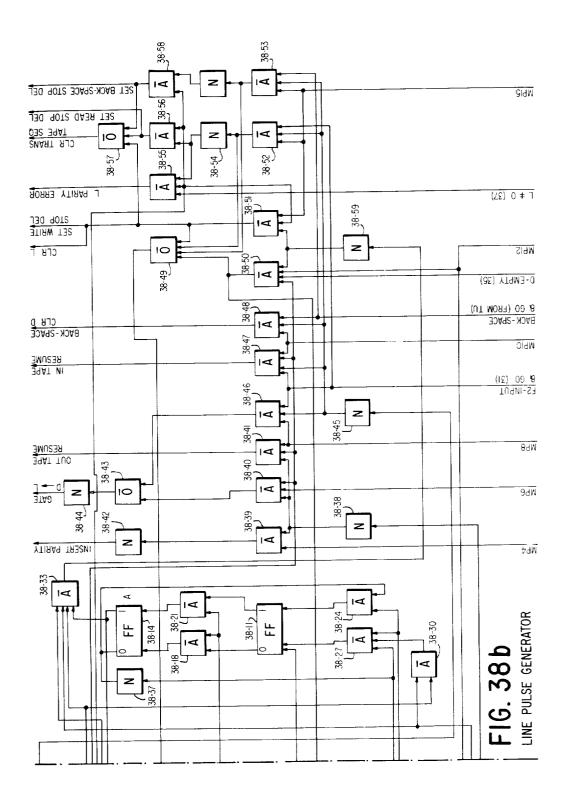

FIGURES 38a and 38b show the Line Pulse Generator:

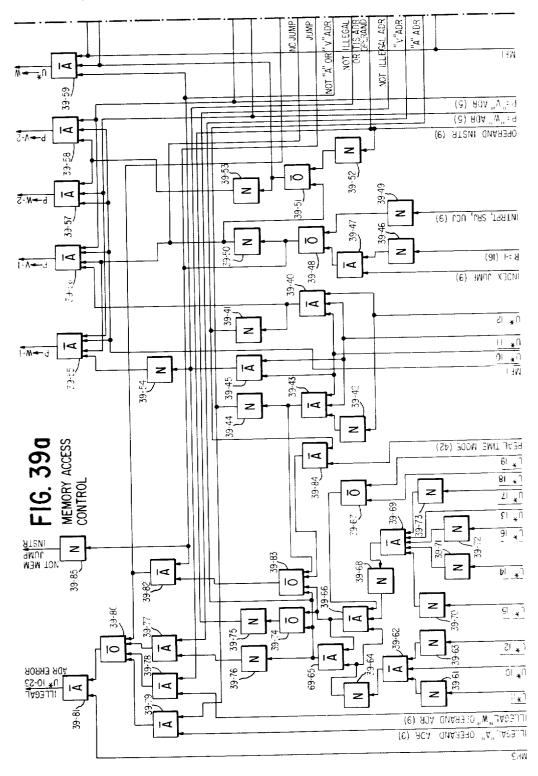

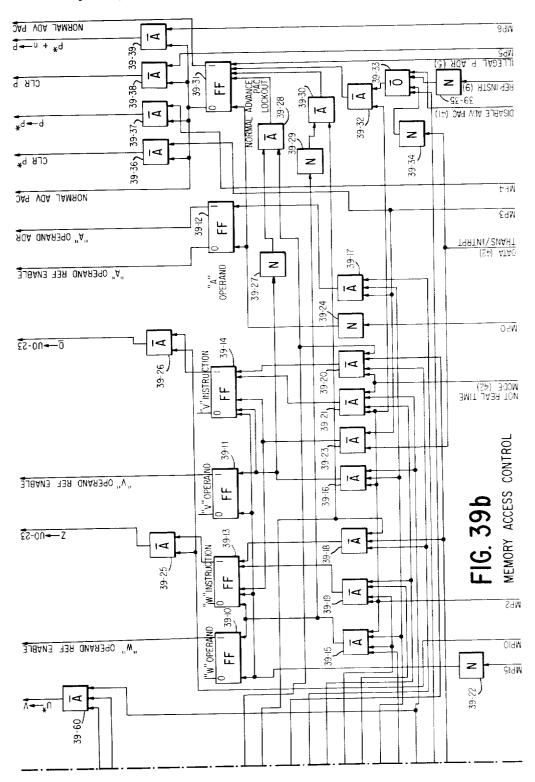

FIGURES 39a and 39b show the memory access con-

15

70

5

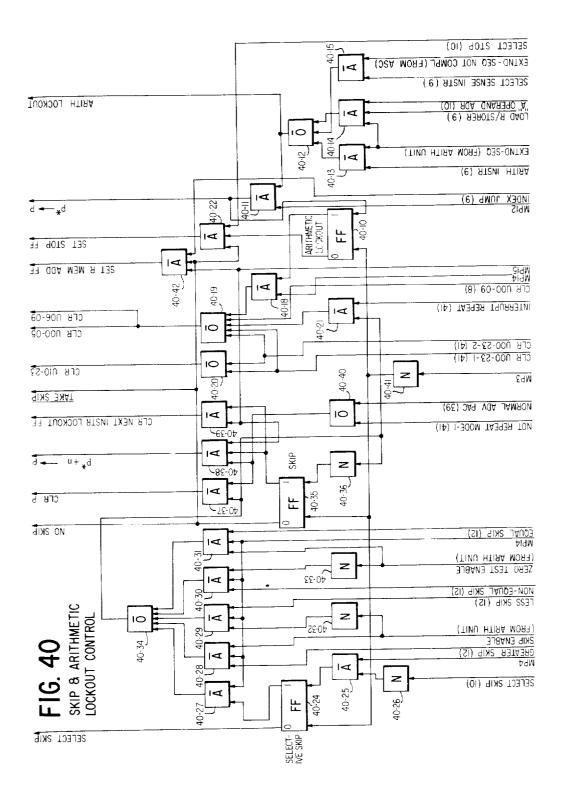

FIGURE 40 shows the skip and arithmetic lockout control;

FIGURE 41 shows the repeat control;

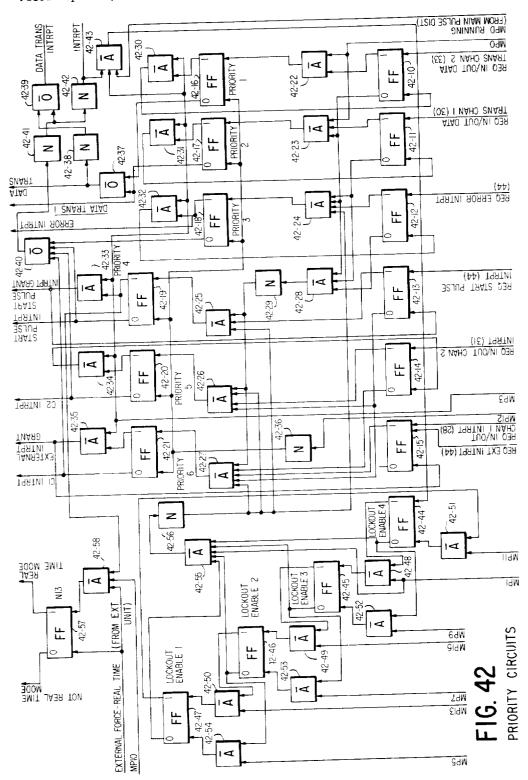

FIGURE 42 shows the priority circuits;

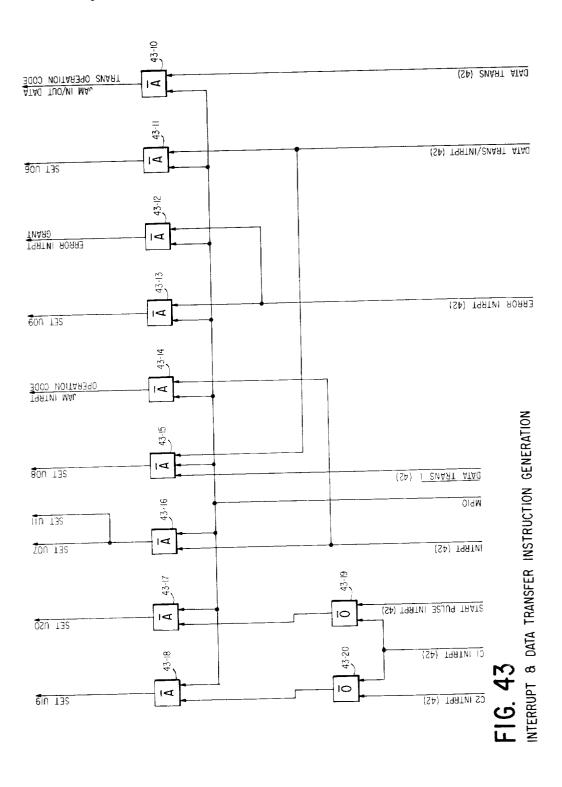

FIGURE 43 shows the interrupt and data transfer intruction generator;

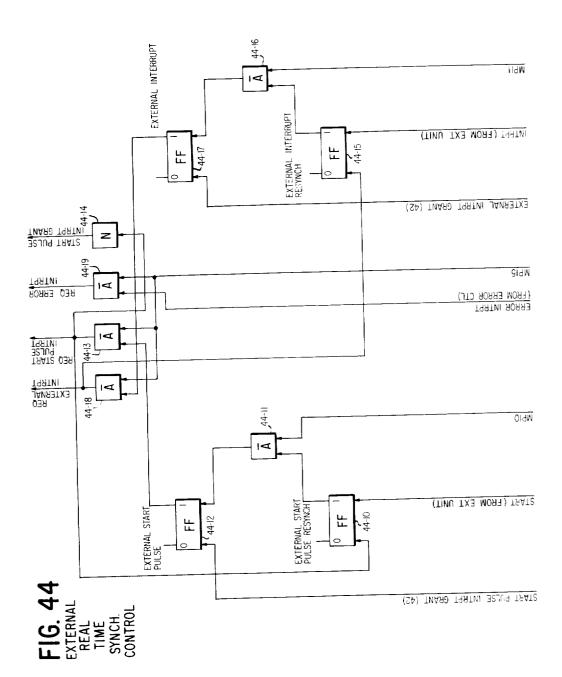

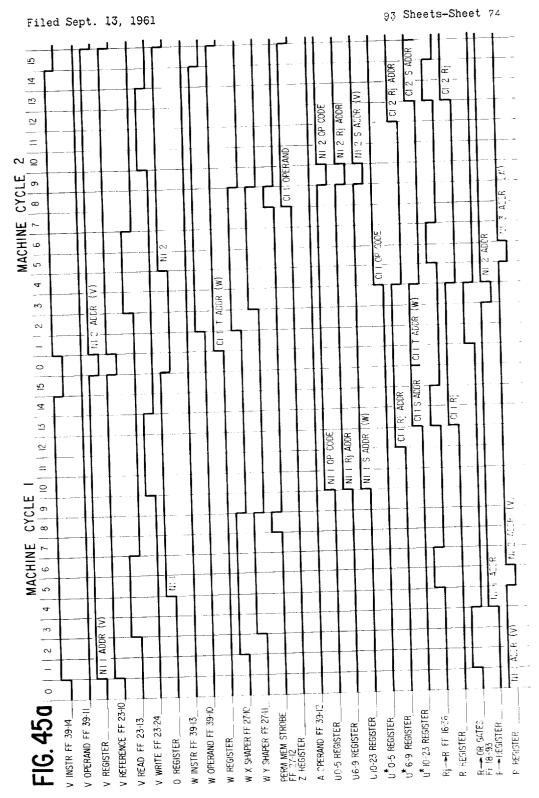

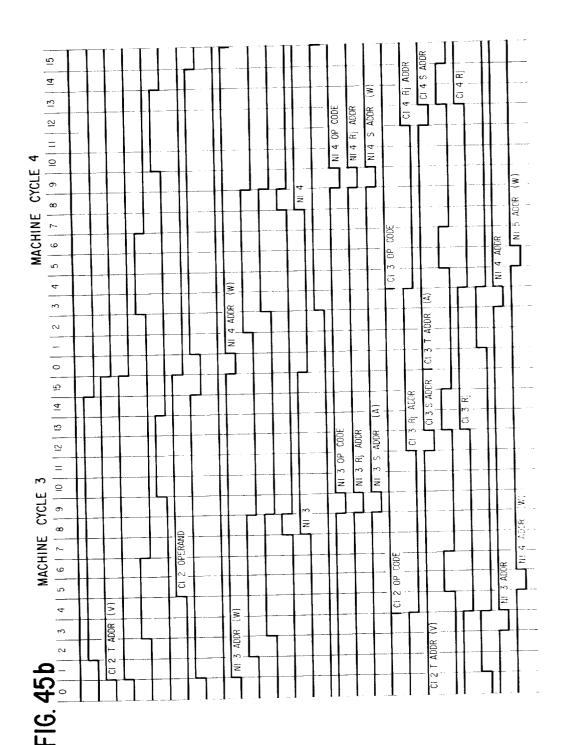

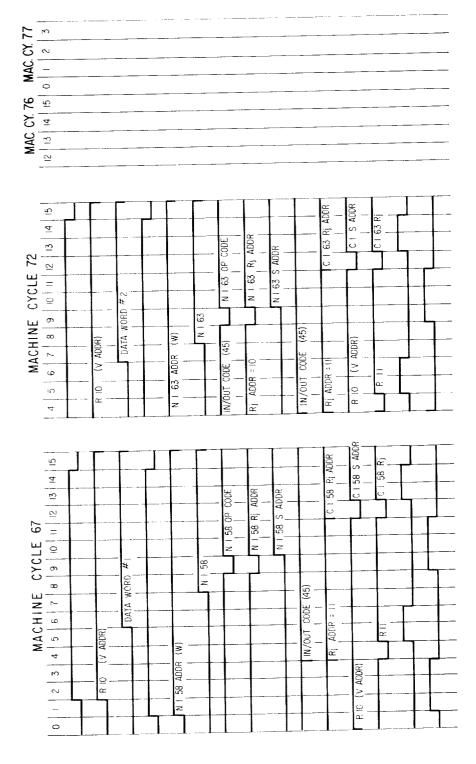

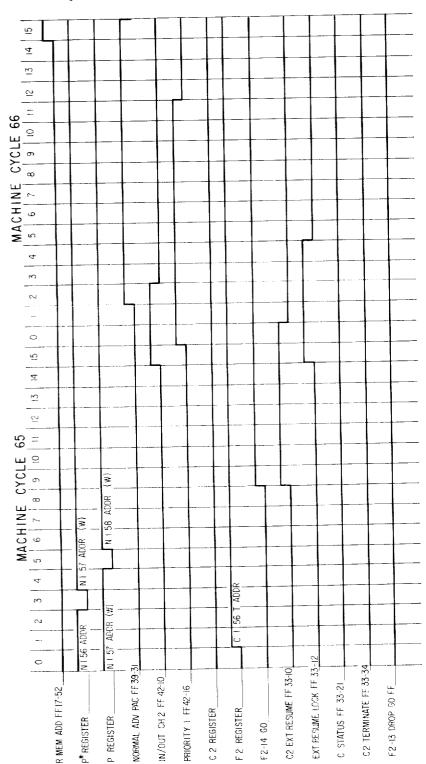

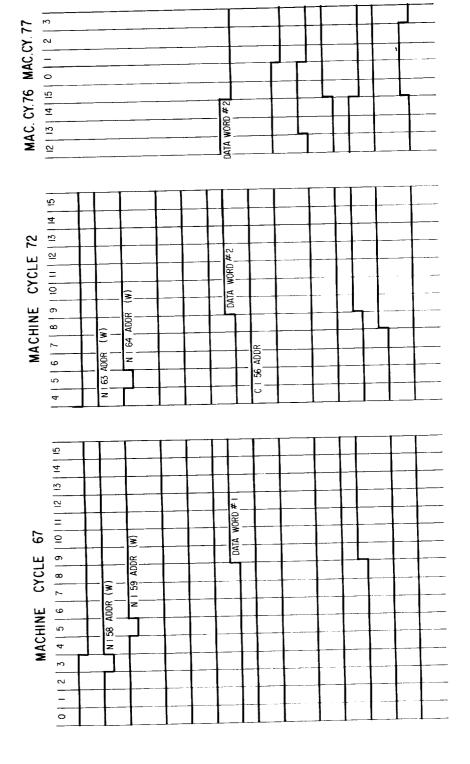

FIGURE 44 shows the external real time sync control; FIGURES 45a and 45b comprise a timing diagram illustrating operation of the invention when overlap is permissible;

FIGURE 46 is a timing diagram illustrating operation of the invention when overlap is inhibited;

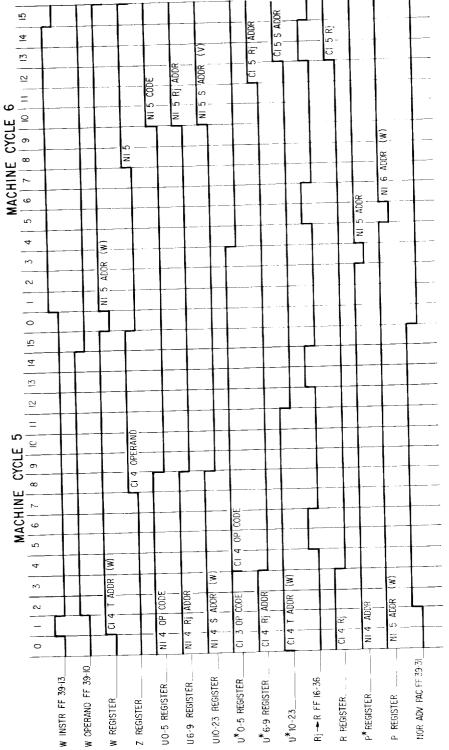

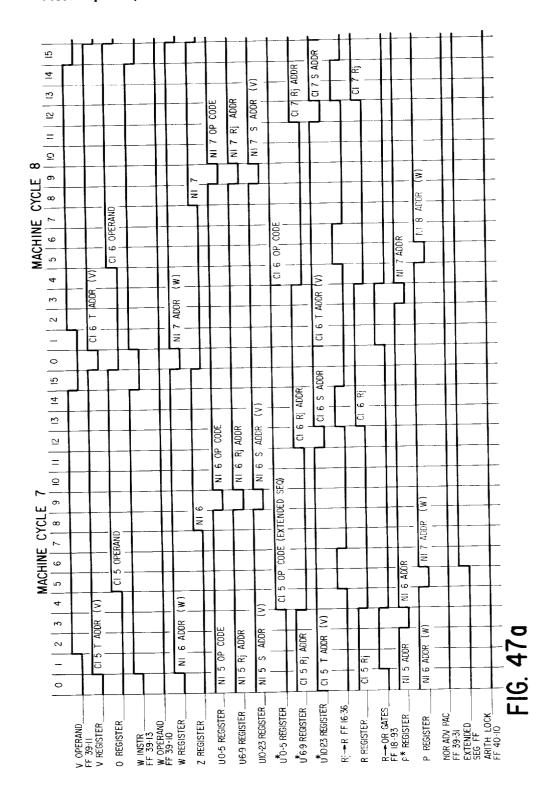

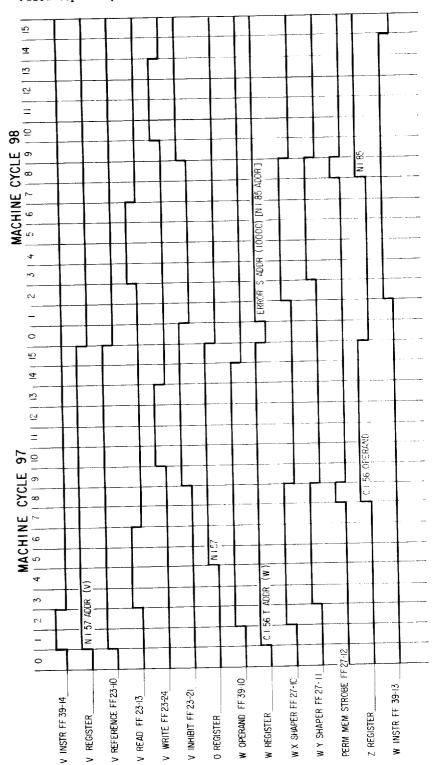

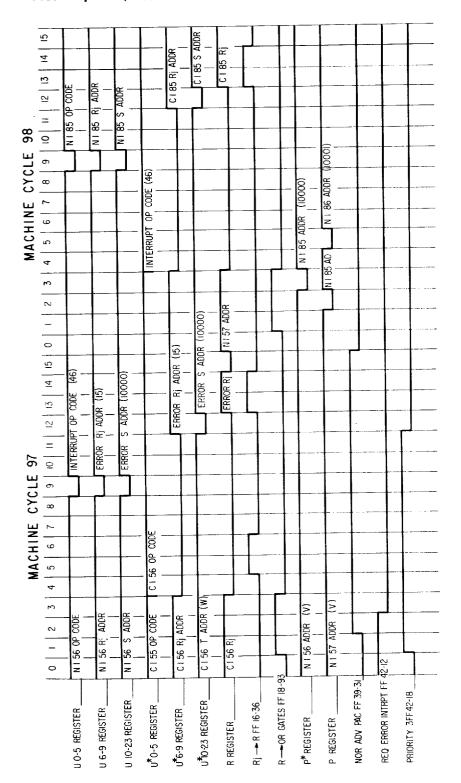

FIGURES 47a and 47b comprise a timing diagram illustrating operation of the invention during an extended sequence:

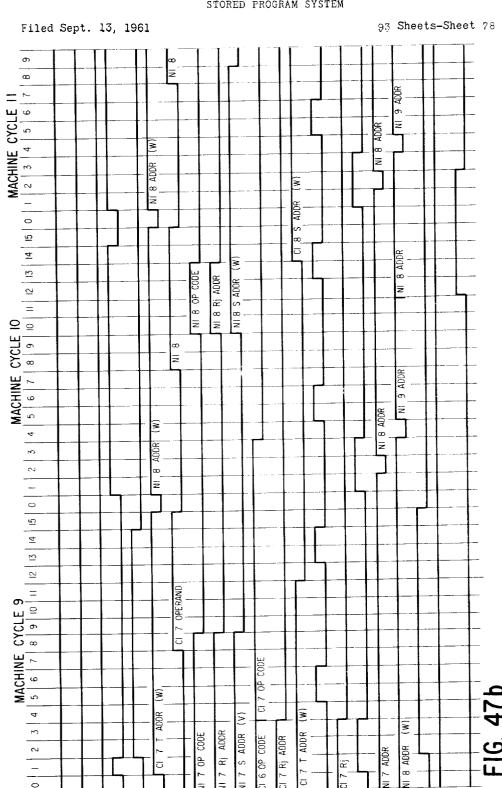

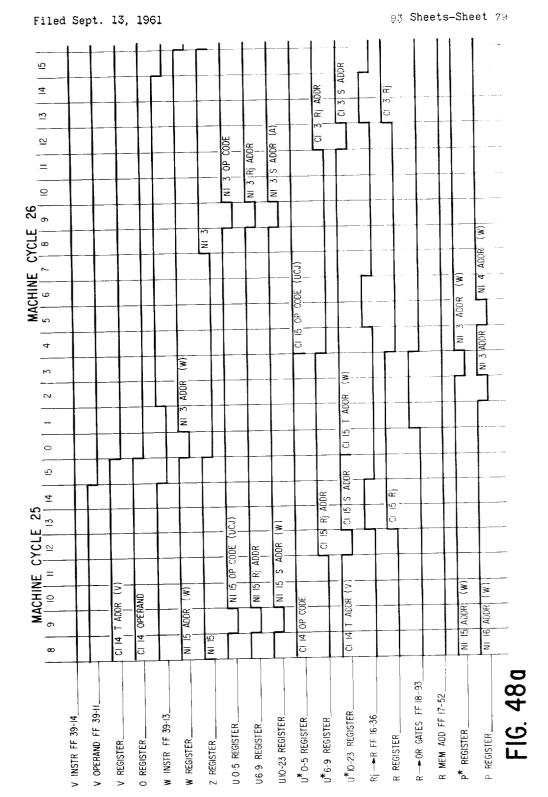

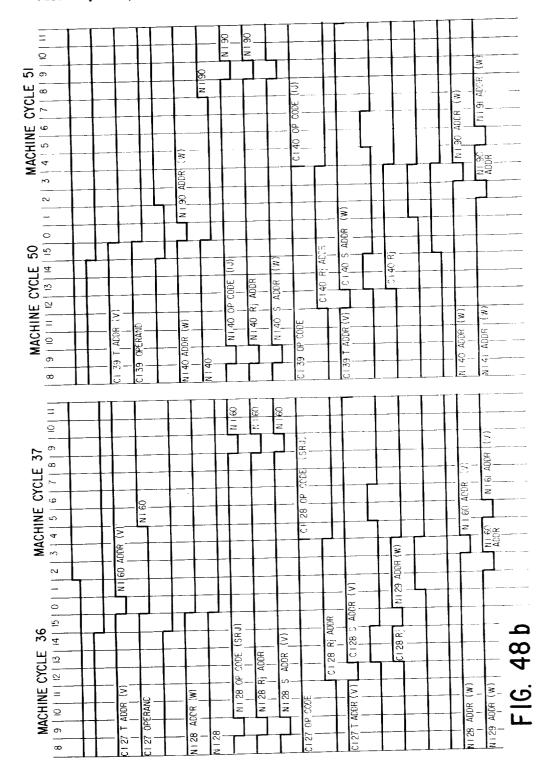

FIGURES 48a and 48b comprise a timing diagram illustrating operation of the invention when executing an instruction jump;

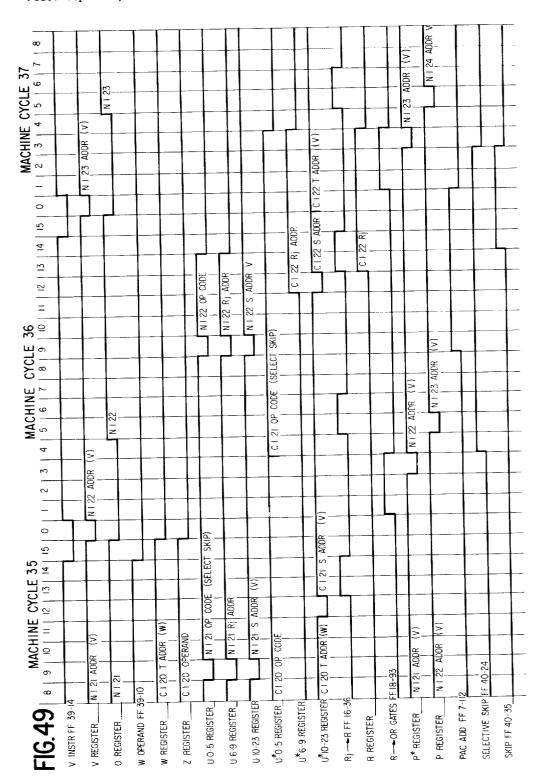

FIGURE 49 is a timing diagram illustrating operation of the invention when executing a selective skip instruction:

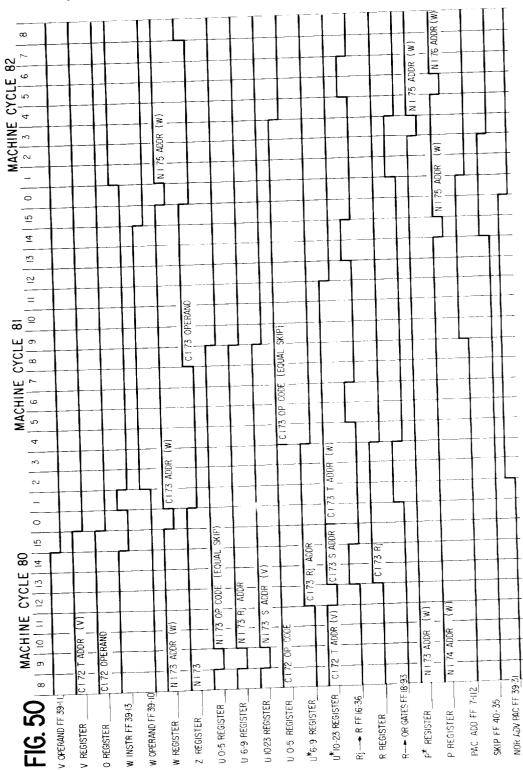

FIGURE 50 is a timing diagram illustrating operation of the invention when executing an arithmetic skip instruction;

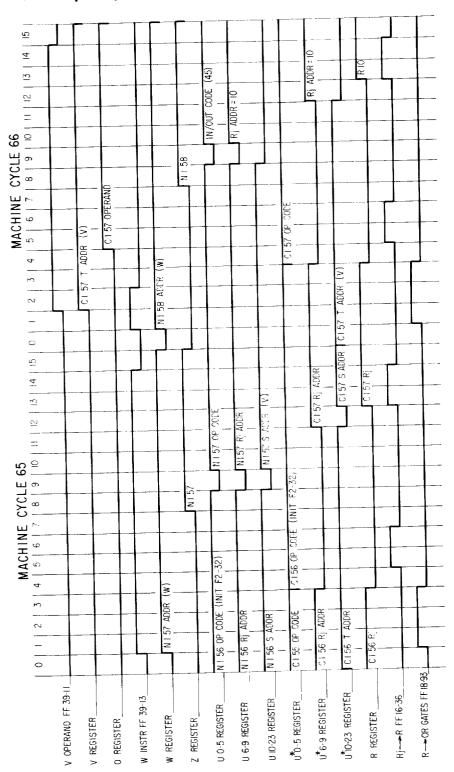

FIGURES 51a, 51b, 51c and 51d comprise a timing 25 diagram illustrating operation of the invention for an input-output data transfer operation;

FIGURES 52a and 52b comprise a timing diagram illustrating operation of the invention when an interrupt subroutine is requested:

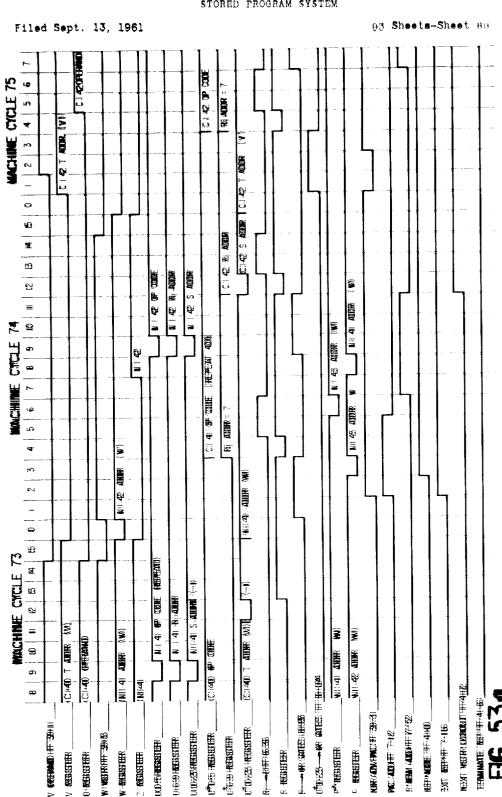

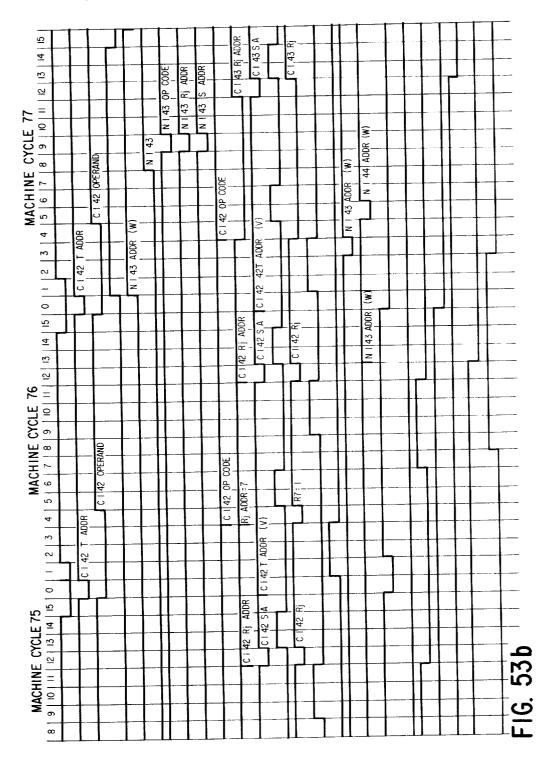

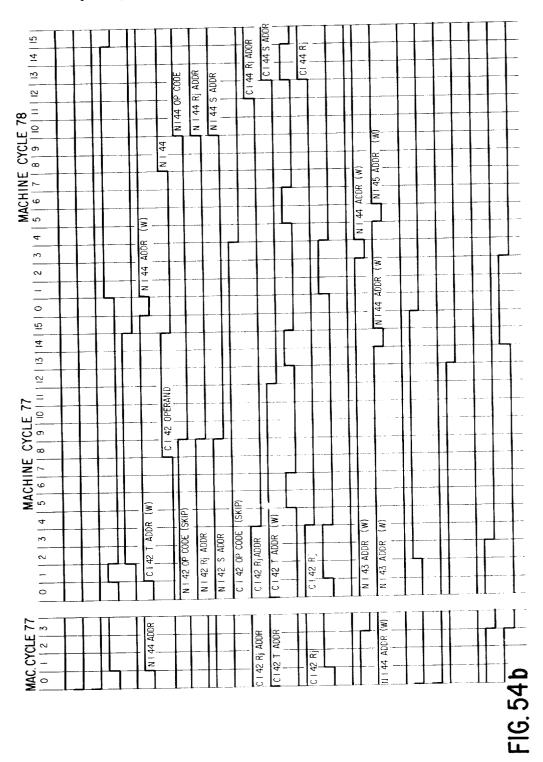

FIGURES 53a and 53b comprise a timing diagram illustrating operation of the invention when executing a repeated instruction;

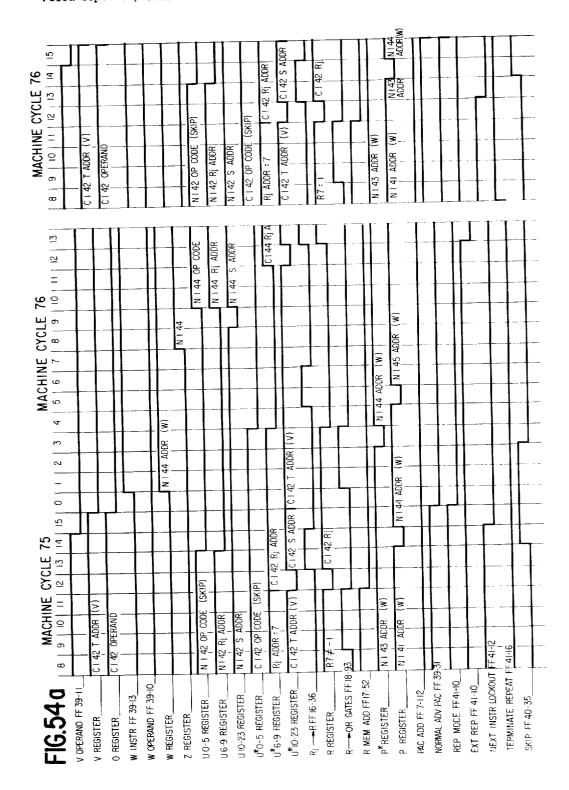

FIGURES 54a and 54b comprise a timing diagram illustrating operation of the invention when repeating 35 the operation of a skip instruction; and

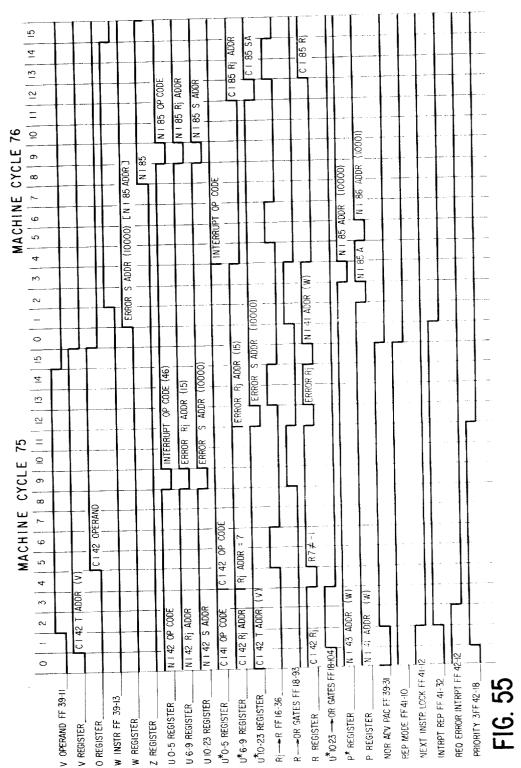

FIGURE 55 is a timing diagram illustrating the operation of the invention when an interrupt subroutine or data transfer is requested during the repeat mode.

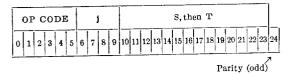

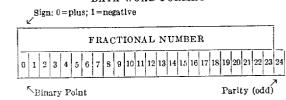

In the system disclosed herein, both words of data 40 and words of instruction are stored in memory locations and, when acquired therefrom, are employed in a manner similar to that shown in much of the prior art. example, an instruction word is comprised of 25 binary bits with parity and includes an operation code portion (OP CODE) specifying the function, e.g., ADD, SUB-TRACT, etc., to be executed. A word memory address portion "S" is also included which usually specifies the location of the data word (operand) to be used in execution of the operation code. Alternatively, this address portion can denote the address of the next instruction word to be processed, a constant, a shift control value, or other special values. Instruction words further contain an index address portion "j" which may be used to obtain a number from auxiliary storage for the purpose of adding same to the "S" address in order to modify the latter just prior to execution of the operation code. This modified word address portion of the instruction is designated as "T." Data words are also comprised of 25 binary bits with parity and represent numbers in fractional binary notation with a sign bit placed to the left of the binary point. Negative numbers are represented by the 2's complement of positive numbers. Thus, 0.1011 is equal to the decimal value of  $\frac{1}{2} + \frac{1}{8} + \frac{1}{16}$  or  $[+\frac{11}{16}]$ , while 1.0101 is equal to  $-1 + \frac{1}{4} + \frac{1}{16}$  or  $[-\frac{11}{16}]$ . The instruction and data  $-1+\frac{1}{4}+\frac{1}{16}$  or  $[-\frac{11}{16}]$ . word formats are illustrated below.

# INSTRUCTION WORD FORMAT

In general, "S" and "T" specify memory addresses wherein are stored operands. "j" specifies an address in an auxiliary memory (here designated as R memory) wherein is stored a modifying index number specified as R<sub>j</sub>.

Thus, R<sub>1</sub>+"S"="T."

#### DATA WORD FORMAT

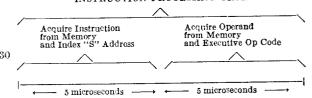

Basically, acquisition and execution of a single instruction requires 10 microseconds in the present system. As shown below, the basic instruction processing time is considered in terms of two 5-microsecond periods, where a 5-microsecond period is defined to be one machine cycle.

#### INSTRUCTION PROCESSING TIME

# TIME RELATIONSHIP IN THE BASIC INSTRUCTION

Common Commands, used to acquire an instruction, are executed during the first 5-microsecond period. During the next 5-microsecond period, the operand is acquired, and then used in the execution of the instruction.

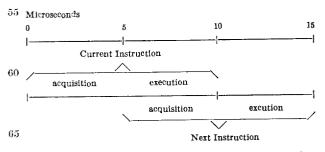

In order to effect a maximum utilization of time, the present invention is designed logically in a way that permits the simultaneous processing of certain portions of successive instructions. Thus, the memory acquisition time associated with the current instruction occurs during the same actual time as the execution time associated with the previous instruction. Likewise, the execution time associated with the current instruction and the memory acquisition time of the next instruction occur simultaneously. This association of successive instructions is illustrated below.

# NORMAL ASSOCIATION OF SUCCESSIVE INSTRUCTIONS

The illustration above shows that the computer may handle a new instruction every five microseconds. Therefore, for programming purposes, five microseconds can be considered the basic processing time requirement for any given instruction.

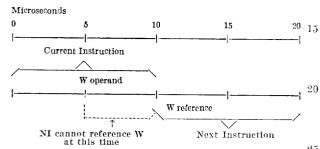

Two individual memories designated as W and V, plus the ability of the computer to reference both memories simultaneously, make this instruction-overlapping feature possible. However, in certain programs it may be necessary to acquire the next instruction from the same memory that issues the operand used in the current execution of the instruction. In such cases, the processing of the next instruction does not begin until the operand used in the current instruction is extracted from memory, thus adding five microseconds to the program at this point as shown below

# THE ASSOCIATION OF SUCCESSIVE INSTRUCTIONS WHEN AN ATTEMPT IS MADE TO SIMULTANEOUSLY REFERENCE THE SAME MEMORY

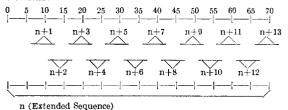

During the Multiply, Divide Square Root, and Shift instructions (hereafter called extended sequences), special conditions exist regarding the overlap of instructions. For these instructions from two to thirteen machine cycles may be required for execution by the arithmetic unit. 35 Only instructions which are non-arithmetic may be processed during the existence of an extended sequence since the arithmetic unit can only operate on one instruction at a time. During the extended sequence, each non-arithmetic instruction is handled in the conventional manner. A normal succession of non-arithmetic instructions during an extended sequence is subject to the same conditions as a normal succession of arithmetic or non-arithmetic instructions during those times that an extended sequence does not exist. A maximum of 13 non-arithmetic instruc- 45 tions can be processed during the extended sequence as shown below. The only instruction shown (other than the extended sequence itself) that may be arithmetic is n+13.

#### Microseconds

# THE RELATIONSHIP OF A SERIES OF NON-ARITHMETIC INSTRUCTIONS AND AN EXTENDED SEQUENCE

The number of instructions that is processed during an extended sequence reduces proportionally as the number of special conditions increases. Other conditions that influence the processing times of instructions are those in 70 which a jump or a skip instruction is being executed, or when an instruction is being repeated. Furthermore, the request by the system of an input/output data transfer or for an interrupt sub-routine also affects the normal program sequence.

| TABLE OF CONTENTS                                                     | Columns |

|-----------------------------------------------------------------------|---------|

| Overall System                                                        | 8       |

| 1.0. Control                                                          | 8       |

| 1.1. Memory                                                           |         |

| 1.2. Arithmetic                                                       | 15      |

| 1.3. Input/Output                                                     | 16      |

| 1.4. Error                                                            | 17      |

| General                                                               | 18      |

| 2.0. Memory Addresses                                                 | 18      |

| 2.1. Basic Circuits                                                   | 18      |

| Detailed Figure Description                                           | 20      |

| 3.0. Program Address Counter                                          | 20      |

| 8.1. Instruction Registers and Command Translators                    | 28      |

| 3.2. R Momory                                                         | 38      |

| 3.3. Variable Memory                                                  | 45      |

| 8.4. Permanent Memory and Twistor Input Switch                        | 49      |

| 3.5. Channel 1 Input/Output                                           | 54      |

| 3.6. Channel 2 Input/Output 3.7. Subcommand and Memory Access Control | 57      |

| 3.7. Subcommand and Memory Access Control                             | 73      |

| 8.8. Interrupt and Data Transfer Control                              | 79      |

| Operation                                                             | 84      |

| 4.0. Overlap                                                          | 84      |

| 4.1. Overlap Inhibition                                               | 87      |

| 4.3. Extended Sequence                                                | 89      |

| 4.3. Instruction Jump                                                 | 92      |

| 4.4. Instruction Skip                                                 | 96      |

| 4.5. Data Transfer                                                    | 100     |

| 4.6. Interrupt                                                        | 105     |

| 4.7. Repeated Instruction                                             | 108     |

| 4.8. Illegal Values                                                   | 116     |

#### OVERALL SYSTEM

FIGURE 1 is a block diagram of the overall system, which will first be described in order to subsequently make clear the relationships between the individual detailed The transmission of data between functional units is depicted with heavy connecting lines. Control paths between functional units are indicated by light connecting lines. The arrowhead(s) indicates in what direction data may be transferred from one functional unit to another or the relative paths of control between functional units. Arrowheads on both ends of a line indicate that data transmission or control paths may occur in either direction. A circle with a number within it is placed on all data flow lines. The number indicates the number of bits that are contained in the binary quantity that can be transmitted. Whenever a dot also appears within the circle, this indicates that the data is "double gated" from one functional unit to another. Double gated should be construed to mean that both the "0's" and "1's" of a binary quantity are transmitted. If no dot appears within the circle, the quantity is single gated, which means that only "1's" are transmitted. The letter (s) "A," "C," "I/O," "M," or "E" next to a particular block indicates that it is a part of the arithmetic, control, input/output, memory, or error units respectively.

### 1.0. Control

The Control Section receives, interprets, and directs the processing of each instruction. In directing the execution of an instruction, the Control Section exercises supervision over the activities of the computer by controlling the timing of all computer operations. The principal circuits of the Control Section are the Interrupt and Data Transfer Control, Instruction Register (U and U\* registers). Command Translator Circuits, Subcommand and Memory Access Control, Main Pulse Distributor, Program Address Counter (P and P\*), and R Memory Control. During the execution of an instruction, the instruction word is held in the Instruction Register. The Command Translator Circuits interpret the operation code portion of the instruction and determine which commands are required for its execution. The Subcommand and Memory Access Control interprets the address portion of the instruction and determines which memory section is to be referenced. The Command Translator Circuits and the Subcommand and Memory Access Control generate the commands in a specific sequence of steps necessary to execute the instruction. The Interrupt and Data Transfer Control enables the computer operation to be interrupted and directed to perform special operations. The R Memory Control is normally employed to reference R Memory and withdraw a number used to index the "S" address portion of the instruction word to form the "T" address portion.

Program Address Counter.-The Program Address Counter provides the memory address of the next instruction to be acquired. The memory address is entered in the Program Address Counter either manually or automatically from the Instruction Register as the result of an Interrupt or Jump instruction. As each instruction is acquired, the Program Address Counter normally advances by one count and thus presents the next address in order. In specific cases, however, the current instruction being executed will prevent the normal advancing of the Pro- 10 gram Address Counter. For example, a skip instruction forces the Program Address Counter to advance by two, while a Jump instruction or an Interrupt will force a new address into the Program Address Counter. An address is generated by the Program Address Counter in the fol- 15 be referenced. lowing manner:

P\* is cleared P is transmitted to P\* P is cleared  $(P^*+n)$  is transmitted to P (where n=1 or n=2)

P Register.—The P register is a 14-bit register which holds the memory address of the next instruction after it is computed by the Address Counter. An address can also be placed in P from U\*10-23 if a Jump instruction 25 is being performed. The P register communicates with the W and V address registers and with the R transfer register.

Address Counter.—The Address Counter provides a means for adding either one or two to the quantity in P\*, 30 i.e., it computes the address of the next instruction.

P\* Register.—The P\* register is a 14-bit register which holds the address of the instruction currently being performed.

Instruction Register.—This provides enabling signals 35 to the Command Translator Circuit, R Memory Read and Word-Write Circuits, and the Subcommand and Memory Access Control. The address portion of instruction is transmitted to one of several possible destinations as determined by the Command Translator Circuits and Sub- 40 command and Memory Access Control. For example, if the instruction code specifies a store operation, then the address portion will be treated as an address and transmitted to the appropriate memory as directed by the Subcommand and Memory Access Control. If the instruction is interpreted as a selective sense instruction, then the address poriton of the instruction will be treated as an operand to determine whether or not the action requested will occur. (The selective sense instructions are always sensed and interpreted, but are only executed if a corresponding sense selection has been made at the Computer Control Panel.)

In general, the Instruction Register receives an instruction word from either the Variable or Permanent Memory (or manually from the Computer Control Panel), 55 translates the operation code into commands, modifies the Variable or Permanent Memory address by some quantity from R Memory if necessary, and uses this modified or unmodified Variable or Permanent Memory address to obtain an operand from storage if one is required for the 60 instruction. The commands issued by the Command Translator Circuits make possible various operations by different sections of the computer so that the instruction can be performed in logical, sequential steps.

The registers which comprise the Instruction Register 65 and the main data paths for data transmitted to and from the Instruction Register are shown in FIGURE 1.

U and U\* Registers.—These registers are 24-bit registers used to hold a complete instruction word while various operations necessary for the execution of the instruction are being performed. A quantity can be entered into U0-23 via the Z or  $\underline{\mathrm{O}}$  transfer register, or manually from the Computer Control Panel (not shown).

10

operation code of an instruction while the code is being translated by the Command Translator Circuits.

(b) U\*0-5: This portion of the U\* register holds the operation code (after its transmission from U0-5) for further translation of the instruction by the Command Translator Circuits.

(c) U6-9: This portion of the U register holds the address of an R Memory index word which is referenced by the "j" address portion of the instruction. If no R memory word is required, no quantity is placed in U6-9.

(d) U\*6-9: This portion of the U\* register holds the j address (after its transmission from U6-9) of an R Memory word also. From this register the address can be translated, and the R Memory address specified can

(e) U10-23: This portion of the U register holds the "S" address of an operand in Permanent or Variable Memory or the Accumulator. The operand is required for the execution of the instruction.

(f) U\* Add Tree: The U\* Add Tree makes possible the addition of some quantity in the R register (R Memory) to the quantity in U10-23. This operation is especially useful for indexing. For some instructions, U10-23 is modified by the addition of the contents of the R register, and for others U10-23 is left unmodified and placed directly into U\*10-23.

(g) U\*10-23. This portion of the U\* register holds the modified "T" (or unmodified) Variable or Permanent Memory or Accumulator address of the instruction operand. Register bits U\*10-23 are the main portion of the Instruction Register that communicate directly with various sections of the computer.

Command Translator Circuits.—The Command Translator Circuits sense the output of the six highest order bits of the Instruction Register (U0-5 and U\*0-5), and translates each of 35 possible operation codes into a unique set of command enables. Timing pulses, generated by the Main Pulse Distributor, strobe these enables and thereby generate the commands in the sequence necessary to carry out the steps in the execution of each instruction.

Subcommand and Memory Access Control.—The Subcommand and Memory Access Control directs the referencing of all memory sections except R memory. It senses the outputs of the Instruction Register, Program 45 Address Counter and the Command Translator Circuit and determines which memory section is to be referenced. Using timing signals generated by the Main Pulse Distributor, the Subcommand and Memory Access Control issues the commands to reference the specific memory section.

There are two primary functions of Subcommand and Memory Access Control. The first primary function is the control of the computer during the execution of a Repeat, Selective Sense or Skip instruction, or during the execution of an "extended sequence instruction" (arithmetic lockout). An extended sequence instruction is an instruction that requires more than 5 microseconds (one machine cycle) for its execution; e.g., Divide, Multiply, etc. The second primary function is that of Permanent or Variable Memory access (Memory Access Control). The units comprising the Subcommand and Access Control are the following.

Repeat Control.—Repeat Control governs the repeat of an instruction and provides the circuitry necessary for the correct interruption of a Repeat instruction. If a Repeat instruction is interrupted, it is completed after the interrupte has been satisfied.

Skip and Arithmetic Lockout Control.—Skip and Arithmetic Lockout Control governs the performance of a Selective Sense Or Skip instruction and also permits the computer to delay the execution of an instruction following an extended sequence instruction until the extended sequence is completed, if the next instruction is an arith-(a) U0-5: This portion of the U register holds the 75 metic instruction (requires use of the Arithmetic Sec-

tion). All extended sequence instructions are performed in the Arithmetic Section.

Memory Access Control.-Memory Access Control governs the access to either Permanent or Variable Memory, or to the Accumulator. Instructions and operands can be referenced in memory. An instruction is a computer word that initiates a particular operation, e.g., Add, Load A, etc. An operand is a quantity (constant) referenced by the address portion of the instruction word that is to be used in the performance of the instruction.

In summary, Subcommand and Memory Access Control govern the special operations of the Repeat, Selective Sense, Skip, and extended sequence instructions. also controls the access or referencing of a word in Variable or Permanent Memory or the Accumulator.

Interrupt and Data Transfer Control.—The Interrupt Control circuits provide for the acceptance and processing of interrupt signals from both external and internal units. Interrupt signals are received by the Interrupt and Data Transfer Control and are assigned a priority. An interrupt signal is a command to the computer to discontinue present operation and process a new instruction. An instruction is generated by the Interrupt Control circuits and is forced into the Instruction register which then executes the instruction. All operations affecting the starting of the computer or deviating from a program must be processed by the Interrupt and Data Transfer Control.

Interrupt and Data Transfer Control consists of three basic parts: External Real Time Sync Control, Priority Circuits, and the Interrupt and Data Transfer Instruction Generation circuits. These circuits act collectively either to generate interrupts internally or to produce Interrupt and I/O Data Transfer instruction upon request from various sections of the computer. Any program 35being performed by the computer may be interrupted by an Interrupt instruction. If an interrupt request is received, all other interrupt requests are locked out for six instruction times so that an interrupt program can be performed. At the end of 6 instruction times, another interrupt program can be performed if an interrupt request is held in the Priority Circuits; otherwise the interrupted program will be resumed. Data transfers can be performed regardless of interrupt priorities. Also, no six-instruction-time lockout exists for I/O Data Trans- 45 fer instructions because they do not disrupt the main program completely as Interrupt instructions do.

External Real Time Sync Control.—External Real Time Sync Control produces Start Pulse and CI interrupt requests when a Start Pulse or CI interrupt request is 50 received externally from a critical external device. External Real Time Sync Control also gates the Error Interrupt request to the Priority Circuits.

Priority Circuits.—The Priority Circuits assign interrupt and data transfer requests, prearranged priorities, and also generate the 6 instruction-time lockout required by an interrupt program.

Interrupt and Data Transfer Instruction Generation. This portion of Interrupt and Data Transfer Control produces automatically the proper operation code, "i" reference, and memory address comprising a particular Interrupt or I/O Data Transfer instruction.

In summary, Interrupt and Data Transfer Control receives the interrupt and data transfer requests from external sources. If necessary, these interrupt and data 65 transfer requests are held, and at the proper time the first instruction of their respective program (for interrupts) is placed in U0-23. I/O Data Transfer instructions do not call for the execution of special programs. Therefore, a data transfer operation requires only that 70 the Data Transfer instruction be place in U0-23.

Main Pulse Distributor.—The Main Pulse Distributor produces the main pulses upon which all computer operations are based. The distributor produces a cycle of 12

Main pulses produced by the Main Pulse Distributor are pulse signals that are produced in a numerical sequence, i.e., 0, 1, 2, 3, through 15. There are 16 main pulses in a main pulse cycle. Each main pulse cycle is 5 microseconds in length. These main pulses are identified by the numbers 0 through 15 written MP0, MP1, etc.). Main pulses are issued to all sections of the computer to enable the performance of instructions in a logical, timeordered sequence. This unit is not shown in detail in the instant application.

R Memory Access and Control.—R Memory Access and Control provides access to the R memory. It also provides for the comparison of U\*10-23 with R register and for the addition of 1 to the quantity in the R register.

R Register.—The R register is a 14-bit data transfer register which provides an output communication path between R Memory and other sections of the computer. It contains, among other values, the number used to index the "S" address portion of an instruction.

OR Gates.—The OR Gates provide a 14-bit path for writing a quantity into R Memory from several sources, e.g., U\*10-23, X register, etc.

R Memory Counter.—The R Memory Counter provides the necessary circuitry for adding 1 to the R regis-25 ter if required and then entering (R+1) into R Memory via the OR Gates. Also, the content of R register may be gated through the counter without any change.

Comparator.—The Comparator compares R with U\*10-23 to determine when a data transfer operation should be terminated.

In summary, words which are read out of R Memory enter the R register and are thereafter distributed to the various portions of the computer. Words which are to be written into R Memory are transmitted to R Memory via the OR Gates. The quantity (R+1) can be written into R Memory via the OR Gates if required.

#### 1.1. Memory

The Memory Section of the system is made of three independent units of storage: Reference memory (designated R Memory), which consists of a small capacity, high-speed, destructive readout (DRO) ferrite core storage unit; Variable Memory, which consists of a medium capacity, destructive readout storage unit using a conventional magnetic core storage system; and Permanent Memory, which consists of a large capacity nondestructive readout (NDRO) storage unit using permanent magnets and a twistor matrix.

A fourth unit, the Twistor Input Switch (Twistor Input Unit) is associated with permanent Memory and acts as a high-speed input device between certain critical external units and the computer.

The characteristics of the three memory units are highspeed operation, random access to stored data, and retention of data when power is turned off (nonvolatility). All three storage units have provisions for checking par-Variable Memory, Permanent Memory, and the Twistor Input Switch each provide for storing parity along with the data word. Parity for the R Memory is stored in the Error Circuits.

R Memory.—The R Memory is recognized as a part of the Control Section because of the tasks it performs in modifying the address portion of instruction words and in storing data transfer addresses during subroutines. The description presented in the Memory Section treats only the physical operation of the unit as an independent storage device. For an explanation of R Memory as an integrated part of the complete system, refer to the above description of the Control Section. The R Memory is a magnetic core storage device capable of storing fifteen 14-bit words at address locations 1 through 15. The memory is word-organized and employs a coincident current write and a single current read cycle. Four bits of the instruction word are required to specify an address 16 main pulses, 0 through 15, then repeats this cycle. 75 in R Memory. Bits 6, 7, 8 and 9 of U\*, the second rank

of the instruction register, are translated to select one of 15 word addresses. Information is inserted into R Memory through the OR gates. This information may come from the O, X, U\* or R registers. R, the 14-bit rest of the computer and back into R Memory if desired. Parity for R Memory is stored and checked in the Error Circuits.

The Read and Word-Write Circuits provide the drive current for switching the state of selected memory devices. One Read Circuit and one Word-Write Circuit is associ- 10 ated with a specific address. Their selection is determined by enable signals from the translator circuits of bits 6-9 of the Instruction Register U\*. A Read Circuit, when enabled by U\*6-9, applies a full drive signal to the associated memory devices which drives them all to the "0" 15 state. The Word-Write Circuits, when enabled, apply a half write signal to the associated memory devices, which is not by itself of sufficient value to drive them to the "1" state. The additional force necessary to drive a given element to the "1" state is supplied by the Digit Write 20 Circuits. Therefore, only those elements which receive the Digit Write signal in addition to the Word-Write signal will switch to the "1" state.

The R-Memory device store the information. The element employed is the magnetic core. The cores are arranged in rows and columns in a 16 x 16 matrix. One Read wire and one Word-Write wire is threaded through each row of cores; one Digit Write wire and one Sense Wire is threaded through each column of cores. The application of signals to these wires enable the cores to switch to either the "0" or "1" state. The Sense Amplifiers receive and amplify the sense signals during a Read operation. The outputs set appropriate stages of the R-Register. The Digit Write Circuits supply drive current necessary to complement the Word-Write signal to effect the storing of "1's" in R Memory. Enables are supplied from the OR Gates.

Variable Memory.—The Variable Memory is a conventional magnetic core storage system. The unit contains 2048 address word locations capable of storing a 24-bit instruction word or operand (data word) plus parity. Characteristics are high-speed operation, random access to stored data, and retention of data when power is turned off (nonvolatility). The time required for one memory reference (the basic memory cycle) is 5 microseconds. Variable Memory is used to store input-output data, the results of intermediate calculations, error addresses, and variables. Except during the Real Time Mode, the Variable Memory may also be used to store instruction. A block diagram of Variable Memory and associated control circuitry is shown in FIGURE 2.

A read operation followed by a write operation make up what is called the basic cycle in Variable Memory. The duration and timing of these operations is controlled by the Variable Memory control flip-flops and clock 55 pulses from the Main Pulse Distributor. Major sequence commands for the transmission of address information to the V register and for data transmission to and from the O register are issued by the Control Section.

$\overline{V}$ , the 11-bit address register, selects one of the 2048 60 address locations during a Variable Memory reference. The translators associated with V simultaneously enable Xand Y access switches (selectors) and drivers at opposite ends of the drive lines to permit the flow of current through the cores. Once an address has been selected, 65 data is transferred from Variable Memory to the rest of the computer and from the rest of the computer to Variable Memory through  $\Omega$ , the 24-bit transfer register.

In addition to transferring a 24-bit data word, the  $\Omega$  register also contains an additional bit for storing parity. Parity is generated when data is sent to  $\Omega$  for storage in Variable Memory. The parity thus generated is stored in the memory along with the data word. Parity is checked when the word is taken out of the memory and placed in  $\Omega$  for transmission to other parts of the compared to the parts of the parts

puter. If a parity error exists, the address at which the error occurred is stored in the E\* register until such a time that the error can be analyzed. The address system also has provisions for checking parity. The address that is sent to the V register is checked against the parity of the P or U\* registers each time a Variable Memory reference is made. If there is a parity error, the address in P\* is stored in the E\* register until such a time that the error can be analyzed.

Permanent Memory.—The Permanent Memory is a word organized, large capacity, non-destructive readout storage unit. Information is stored in the memory in a pattern of permanent magnets arranged on a card. A twistor matrix is used to sense the presence or absence of a magnet for the bits of a word being addressed. The unit contains 10,240 address locations each capable of storing a 24-bit instruction word or constant plus parity. Characteristics of the unit are high-speed operation, random access to stored data, and retention of data when power is turned off (non-volatility). The time required for one memory reference (the basic memory cycle) is five microseconds. Permanent Memory is used to store critical constants and instruction words. Because the program is stored in permanent magnets, the cards in which the magnets are embedded are called "program cards." These cards are inserted along columns of twistor wires so that the magnets are close enough to set up an external magnetic field in the twistor wires. The presence or absence of a magnet denotes a "0" or a "1." Thus the program can be changed by inserting new program cards containing a revised pattern of magnets. A block diagram of Permanent Memory and associated control circuitry is shown in FIGURE 3.

A read operation followed by a bias operation make up what is called the basic cycle in Permanent Memory. The duration and timing of these operations is controlled by the Permanent Memory control flip-flops and by clock pulses from the Main Pulse Distributor. Major sequence commands for the transmission of address information to the W register and for data transmission to and from the Z register are issued by the Control Section. W, the 14-bit address register, selects one of the 10,240 address locations during a Permanent Memory reference. The translators associated with W simultaneously enable X and Y group access switches (selectors) and line access switches (selectors) at opposite ends of the drive lines to permit the flow of current through the word access cores. Switching the word access cores enables data to be read out of Permanent Memory. The information stored on the program cards is not destroyed by the read operation (nondestructive readout), therefore a write operation is not necessary. However, since the word access cores change stages during a read operation, a bias current which is on continuously is used to switch the cores back to their original state. Once the address has been selected and the read operation initiated, data is transmitted from Permanent Memory to the rest of the computer through Z, the 24-bit transfer register.

In addition to transferring a 24-bit data word, the Z register also contains an additional bit for parity. Parity is stored in the memory along with the data word and is checked when the word is taken out of the memory and placed in Z for transmission to other parts of the computer. If a parity error is found, the address at which the error occurred is stored in the E\* register until such a time that the error can be analyzed. The address system in Permanent Memory also has provisions for checking parity. The address that is sent to the W register is checked against the parity of the P or U\* register each time a Permanent Memory reference is made. If there is a parity error, the address in P\* is stored in the E\* register until a time that the error can be analyzed.

checked when the word is taken out of the memory and placed in O for transmission to other parts of the com- 75 (Twistor-Input Unit or TIS) is a word-organized device

0,200,00

that receives data from certain external units and makes it immediately available to the computer. The characteristics and principles of operation of the switching unit are similar to those of permanent Memory. However, since data from the external unit is continually 5 changing, the permanent magnets that are used as storage devices in Permanent Memory are replaced by electromagnets in the Twistor Input Switch, so that information being transmitted from the unit can be changed at random. The Twistor Input Switch has 48 address locations each of which is capable of storing a 24-bit word plus parity. Characteristics of the unit are high-speed operation, random access to stored data, and retention of data when power is turned off (assuming the inputs remain energized). The time required for reference (basic cycle) is 5 microseconds.

15

As in Permanent Memory, a read operation followed by a bias operation make up what is called the basic cycle in the Twistor Input Switch. The duration and timing of these operations is controlled by the Permanent Memory control flip-flops and by clock pulses from the Main Pulse Distributor. Timing for the data input is controlled by the external unit and interrupts may be generated at any time. Access circuits similar to those used in Permanent Memory are used to provide the read current and bias current in the Twistor Input Switch. Access to the 48 address locations is supplied by the 14-bit W register. Once the address has been selected and the read operation initiated, data from TIS is gated into the Z register for transmission to the rest of the 30 computer. The parity check in the Twistor Input Switch is identical to that in Permanent Memory.

#### 1.2. Arithmetic

The Arithmetic Section performs the basic operations of addition, subtraction, multiplication, division, square root, shifting and masking. The principal circuits are the arithmetic registers, X, Q, and (A), the Arithmetic Sequence Control (ASC), and the Shift Register (K). The Q, A, and K Registers are each double rank registers, with the second rank denoted by \*. The X register is single rank. In certain operations, A, and Q, and A\* and Q\* are combined to form double length registers. The extended registers are designated by the combinations AQ and A\*Q\* respectively. The numerical quantities of an arithmetic operation are manipulated 45 in the arithmetic registers; while ASC and the shift register are concerned with control operations. All arithmetic operations are performed in fractional, two's complement, binary arithmetic. For details of this section, reference may be had to co-pending U.S. applications Serial No. 137,805, filed September 13, 1961, and Serial No. 134,945 filed August 30, 1961, now Patent No. 3,192,366 dated June 29, 1965.

X Register.—The X Register is a 24 bit, single rank register. It functions, both as a buffer register and as an arithmetic register. As a buffer register, it serves as the data transfer register linking the arithmetic section to other computer sections. As an arithmetic register, it holds the addend, subtrahend, multiplicand, divisor, and root during the associated arithmetic operations. The X Register has neither shifting nor complementing properties. The complement of X, however, as well as the value 2X may be gated to the adder.

A Register.—The A Register, a 24 bit accumulator, is the principal register of the arithmetic section. It consists of the first rank register, A, and the second rank register A\* and associated adder. The A Register is involved in all arithmetic operations. It holds the augend and accumulated sum in addition, the minuend and difference in subtraction, the most significant bits of a product in multiplication, the most significant bits of a dividend and the remainder in division, and the radicand in square root. Shifting properties are provided during transfers from A\* to A. During multiply 75.

and divide operations, A and A\* are tied to Q and Q\*, respectively, to form double length registers.

Q Register.—The Q Register functions as an auxiliary register during operations of multiplication, division, and square root. In multiplication it holds the multiplier and the 24 least significant bits of the product; in division, the least significant bits of the dividend and the quotient; in square root, the remainder. Shifting properties are provided during transmissions from Q\* to Q. During multiply and divide operations, Q and Q\* are tied to A and A\*, respectively, to form double length registers.

Arithmetic Sequence Control. The ASC receives operation code enables from the Control Section and directs the sequence of operations involved in the arithmetic processes. During extended sequence operations (multiply, divide, square root, and shift) ASC operates with K to produce the iterations necessary to complete a designated instruction. An extended sequence is any instruction that requires more than one instruction time (5 microseconds) to execute. When an extended sequence is performed, ASC assumes control of the Arithmetic Section. Therefore, the Control Section of the computer is free to execute any subsequent instructions that do not require the use of the Arithmetic Section. The execution of those instructions that occur during an extended sequence and are arithmetic in nature (require the use of the Arithmetic Section) is delayed until the extended sequence is completed. Such a delay is called an arithmetic lockout.

K Register.—The K Register holds the shift count during the shift instruction and the iteration count during multiply, divide, and square root. As each shift or arithmetic iteration is performed,  $(K^*)$  is transmitted to the counter and reduced in count. If a single place shift or iteration is performed, the count is reduced by one; if a two place shift is executed the count is reduced by two. When K=0 the sequence is terminated.

$A^*$ ,  $Q^*$ , and Skip Enable Tests.—This unit (1) checks the contents of  $A^*$  to determine whether it equals 0 or -1, (2) checks the contents of  $Q^*$  to determine whether it equals 0, and (3) checks the sign of A,  $A^*$ , and X to determine whether A is greater than or equal to X, or whether A is less than X.

### 1.3. Input/Output

The Input/Output Section functions as a buffer for the exchange of data between the computer and the external equipment. Communication is provided on two channels, designated channel 1 and 2. Each operates independent of the other under direction of the control section. Channel 1 transfers data from the computer variable memory to critical external units. Channel 2 transfers data from the variable memory to non-critical external units and also exchanges data with the tape units and the typewriter. The principal circuits include the communication registers C1 and C2, the function registers F1 and F2, C1 and C2 Sequence controls, the D and L registers, and the Signal Data Recorder-Reproducer Control.

C1 and C2 Registers.—These registers, each 25 bits, form the data link between the computer and the external units. Although C1 is employed only as an output transfer register in the present system, the necessary hardware for an input operation may be included if desired.

F1 and F2 Registers.—The function registers F1 and F2, each 13 bits, are associated with C1 and C2, respectively. These registers receive the function code from the control section, translate it, and provide the control enables which designate the operation to be performed and unit which is to operate.

C1 and C2 Sequence Controls.—These circuits provide the proper timing for sequencing transfers of data.

of a dividend and the remainder in division, and the radicand in square root. Shifting properties are provided during transfers from A\* to A. During multiply 75 to multipl

put operation D receives 6 bit characters from C2 and transfers them to the typewriter or to tape units. During input operations D receives 7 bit characters from the tape units or typewriter and transfers them to C2.

L Register.—This 7 bit register (including parity) receives characters from the D register and converts "return to zero" data to "change on 1" data for recording on tape. It also is utilized in writing an end of record check mark, and in performing a longitudinal check on drop outs during a tape read operation.

Signal Data Recorder Reproducer Control.—These circuits control the operations of D and L during conversion of a 24 bit computer word to a 6 bit tape or typewriter character, and vice versa.

#### 1.4. Error

The basic function of the Error Section is the detection of errors that occur in all sections of the computer. There are two basic types of errors, program-generated and hardware-generated. Program-generated errors are classed as intermittent errors, since they result from erroneous programming and once generated, will probably not appear again. Hardware-generated errors can be intermittent also; the result of marginal conditions in the hardware. When the hardware fails completely, the error becomes "solid." Solid errors are those errors that are duplicated each time the hardware that produces the error is used. When errors are detected, those physical portions of the computer (C-planes and/or D units) that caused the error are located, by translation of the error itself and additional programming.

When an error occurs, the error and an "indicating program address" are stored in memory, thus enabling future references to both the error and indicating address. The indicating program address establishes a relationship between an error and its occurrence in a program. When an error occurs, certain bits of the E register are set, thereby producing in that register a quantity that specifies an error. This quantity (error) is implied in the statement: the error is stored. The Principal circuits of the error section are the various Error check circuits, the Error Register (E) and the Error Address Register (E\*). For details of this section, reference may be had to the above identified U.S. Application Serial No. 137,805.

\*\*E Register\*\*—The E Register, 25 bits, receives error data\*\*

E Register.—The E Register, 25 bits, receives error data from the detection hardware, translates the data, and produces error light indicator enables designating the D Unit and C plane at fault. It also issues error interrupts to the control section which then stores the error data in Variable Memory.

E\* Register.—This Register, 14 bits, records the address of the instruction in process at the time the error occurred, or in the case of an error on a memory reference, it records the address of the word being referenced. This data is also stored in variable memory for subsequent analysis.

Error Check Circuits.—These circuits are located in all computer sections and check data transmissions, command signal generations, timing operation, etc. to set a particular bit or bits of the E Register. These are as follows. O and Z Parity Check circuits determine which, if any, bits are lost when, during memory references, words are transmitted between the Variable Memory and the  $\underline{O}$ register or between the Permanent Memory and the Z register. R, OR Gates and U\*10-23 Parity Check Circuits check parity of the R register during R memory read operations, and sense parity of the OR Gates during R Memory write operations. Also, these circuits sense the parity of U\*10-23 so that, whenever required, reading 70 of parity from this portion of the U\* register is possible. Address System Parity Check Circuits detect the loss of bits and the generation of errors in the address system register; namely, U\*10-23, V, W, P, and P\*. Extended

18

gram time allocated to the extended-sequence instructions (Multiply, Divide, Square Root, and Shift) is exceeded. Critical Command Error Check Circuits determine whether commands that are critical to the computer arithmetic operations have been produced when required.

Error Indication and Control.—Error Control supervises the transmission of data between the E and E\* registers. Also, Error Control supervises the execution of those portions of the Error Interupt program that are related to the storage of detected errors. The E register communicates with the Error Detection Circuits and the Variable Memory via the O register. The E register receives all errors that the computer is capable of sensing and then, by employing error-analyzing programs, translates the word in E to a visual indication of faulty D-units or C-planes. These programs light error indicators on those C-planes and/or D-units that are functioning improperly.

In summary, the E\* register receives data from P\*, V, and W whenever an Error Interrupt is generated. Since P\*, V and W are address registers, E\* will receive an address when an error occurs. This address specifies the general location in the program at which the error occurred. Also, E\* communicates with Variable Memory via the O register, thus enabling the transmission of the contents of E to O during the Error Interrupt program. The Error Indication and Control portion of the Error Section receives indications of computer errors and other information (addresses) that is useful in the program diagnosis of these error indications. In addition, this function group includes the circuitry that controls the operation of the Error Section during the Error Interrupt program.

#### **GENERAL**

#### 2.0 Memory addresses

FIGURES 2 and 3 are block diagrams of the variable memory and permanent memory access circuits, respectively. However, a detailed description of each of these figures is postponed until after the V register and translator of FIGURE 21 or the W register and translator of FIGURE 24 have been discussed. For the present, it is sufficient to note that a variable memory 14 binary bit address is in the range of values from

# <u>00 100 000 000 000</u>

through 00 111 111 111 111, inclusive. By dividing this fourteen bit address into four groups of three binary bits each and one group of two binary bits, as shown, this variable memory address range may be more conveniently expressed in octal notation as 04000 through 07777, inclusive. A 14 binary bit permanent memory address is in the range of values from 01 000 000 000 000 through 11 011 111 111, inclusive. The permanent memory address range expressed in octal fashion therefore 10000 through 33777, inclusive. The twister input switch portion of the memory section may be referenced by a 14 binary bit address in the range of from

# <u>11 111 111 010 000</u>

through 11 111 111 111 111, inclusive. Again, this range may be expressed in octal fashion from 37720 through 37777, inclusive. If a data operand word is located in the accumulator register of the arithmetic unit (an "A" address) instead of in either the variable, permanent, or TIS memories, then this location is specified by a 14 binary bit address of 00 011 000 000 000, expressed in octal fashion as 03000. Also, octal numbers of 03XXX (where X designates any octal digit) can be used to indicate the "A" address. All other 14 bit binary combinations other than those specified above refer to non-existent memory locations.

## 2.1. Basic Circuit

register; namely, U\*10-23, V, W, P, and P\*. Extended

Sequence Error Check Circuits determine whether the pro75 which may be utilized as the basic logic element of the

system, while FIGURES 4b, 4c, and 4d indicate the symbols used in FIGURES 5 through 44 to signify the particular logical function of the basic element in a particular environment. For the logical combination of input signals, two or more PNP transistors T1 and T2 have their emitters grounded and their collectors connected to the center of a voltage divider consisting of resistors R1 and R2, with a negative potential being applied to the other terminal of R1 to reverse bias the transistor col-The output termi- 10 lector circuits in the normal fashion. nal 4-10 from the circuit is derived from the common junction of the transistor collectors. Individual input signals are applied to input terminals 4-11 and 4-12 which are respectively connected via resistors R3 and R4 to the base electrodes of T1 and T2. Capacitors C1 and 15 C2 are also shunted with R3 and R4 respectively, to perform a speed up function. The input signal applied to either terminal 4-11 or 4-12 is binary in nature in that it has two discrete potential levels such as is shown in the potentials, the circuit is designed such that the base electrode of the associated transistor is more negative than its grounded emitter so that conventional current flows in its collector electrode in the direction of the arrow. This so that the terminal 4-10 produces a positive going signal therefrom. Conversely, if a positive going input signal is applied to a terminal 4-11 or 4-12, then the base electrode of the associated transistor is raised to reduce or terminate the current in its output collector circuit. This 30 therefore drives terminal 4-10 toward the negative potential connected to the other terminal of R1, thus producing a negative going signal output. The ON condition of any one of the transistors associated with resistor R1 causes a positive output from terminal 4-10 35 such as indicated in FIGURE 4a. A negative going output from 4-10 is only generated if positive going signals are applied to the base electrodes of all of the transistors in the circuit. Thus, the circuit of FIGURE 4a acts logically as an AND-NOT circuit for positive input signals, 40 and as a NOR circuit for negative signals. Although two transistors T1 and T2 have been shown in FIGURE 4a, one transistor, or three transistors may be provided depending upon the number of input signals to be sensed by the circuit.

FIGURE 4b indicates the symbol utilized for the circuit of FIGURE 4a when it is to be used for detecting the coincidence of positive input signals. The character A placed in the middle of block 4-13 indicates the AND NOT function of the circuit, which generates a significant 50 negative output only when positive going signals are applied to all of its input terminals. In FIGURE 4c, the character  $\overline{O}$  placed in the middle of block 4-14 indicates that the basic circuit acts as a NOR circuit so that a significant positive output is obtained therefrom when 55 any one of its input signals is negative. In FIGURE 4d, the symbol N in the center of block 4-15 indicates a NOT function of the basic circuit such that the output is the inverted input. The basic circuit of FIGURE 4a will provide the NOT function if it includes only one 60transistor.

FIGURE 4e shows the block symbol used for a bistable flip-flop while FIGURE 4f shows the composition of the bistable flip-flop using two of the basic circuits in their logical NOR function. In FIGURE 4e, a flip-flop 4-16 is represented as having one or more set input terminals and one or more clear input terminals, with one set output (1) and one clear output (0) therefrom. A negative going signal applied to any one of the set input terminals of a flip-flop causes that flip-flop to assume a 70 state such that a positive signal is produced from its (1) output terminal. Conversely, a negative going signal applied to any one of the clear input terminals causes the flip-flop to assume a state such that a positive going signal is provided from its (0) output terminal. A flip-flop 75

having these characteristics may be constructed as shown in FIGURE 4f from two of the basic circuits acting as NOR gates. Each of the  $\overline{O}$  gates is respectively cross coupled by having its output connected to an input of the other as shown. Other inputs are provided to each of the  $\overline{0}$  gates 4-18 and 4-17 depending upon the number of set and clear input terminals required, respectively.

The operation of the logic configuration of FIGURE 4f is as follows, assuming that  $\overline{O}4-17$  receives negative "clear" signals as required, while  $\overline{O}4-18$  receives negative "set" signals as required. When neither a negative "clear" nor a negative "set" signal is to be applied to its associated input, the potentials of these inputs are all held positive. Assume first that a negative going "set" signal is temporarily applied to one of the set terminals of  $\overline{04}$ -18. As illustrated in FIGURE 4a, any negative going signal to the basic logic circuit produces a positive output therefrom. The positive output produced by  $\overline{O}4-18$  is apfigure. When the input signal is at the lower of its two 20 plied to one of the input terminals of  $\overline{0}4-17$ , with the signals applied to the other clear input terminals of this  $\overline{O}$ gate also being positive in the absence of a "clear" input signal. Therefore, in this situation, positive signals are applied to all input terminals of 04-17 such that it procurrent flows through R1 back to the negative potential 25 duces a negative output signal which in turn is applied to one of the inputs of  $\overline{04}$ -18. This negative signal from  $\overline{04}$ -17 maintains a positive output from  $\overline{04}$ -18 even after the temporary negative "set" signal disappears. Thus, the flip-flop is set to a stable state which produces a positive output from  $\overline{O4}$ -18 and a negative output from  $\overline{04}$ -17. In order to change stable states, a negative "clear" input must be temporarily applied to one of the clear input terminals of  $\overline{O4}$ -17, which thus produces a positive output therefrom. This positive output is applied to 04-18 further having positive signals applied to all of its set input terminals in the absence of a significant negative "set" signal. Therefore, the output from 04-18 becomes negative which in turn maintains the positive signals from  $\overline{O}4-17$  until a negative "set" signal is once again applied to  $\overline{O}4-18$ .

## DETAILED FIGURE DESCRIPTION

In the remaining FIGURES 5 through 44, all  $\overline{A}$  gates,  $\overline{O}$  gates, N gates, and control flip-flops are numbered in a manner to indicate the figure in which they are shown. Thus, the digit or digits to the left of the hyphen represents the figure number. For example, the term "A27-18" refers to an  $\overline{A}$  gate in FIGURE 27. Likewise, the term " $\overline{O}$ 27-16" refers to an  $\overline{O}$  gate in FIGURE 27. The term "FF27-10" refers to the X shaper flip-flop in FIG-URE 27. However, those flip-flops which comprise stages in any one of the various registers are designated only by the register letter followed by a digit or digits specifying its position in the register; i.e., P01 (or P1); U\*10, etc.

All signals entering a figure are specified by a word or words (sometimes abbreviated) usually indicating its function, as well as a digit or digits enclosed in parentheses for indicating the figure from which that signal is generated. The exceptions to this are if the signals are derived from either the set or clear output terminals of a flip-flop in a register, or if the signal is generated from a unit shown in FIGURE 1 which is not disclosed in detail in the instant application. In the case of the former, the register stage is identified but the figure in which it appears is not given.

#### 3.0. Program Address Counter