(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-503439

(P2006-503439A)

(43) 公表日 平成18年1月26日(2006.1.26)

| (51) Int.C1.                                  | F 1                                                                                                                                    | テーマコード (参考)                                                                                                |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                               |                                                                                                                                        | 審査請求 有 予備審査請求 有 (全 29 頁) 最終頁に続く                                                                            |

| <b>(21) 出願番号</b> 特願2004-545696 (P2004-545696) |                                                                                                                                        |                                                                                                            |

| <b>(86) (22) 出願日</b>                          | 平成15年10月10日 (2003.10.10)                                                                                                               | (71) 出願人 501209070<br>インフィネオン テクノロジーズ アクチ<br>エンゲゼルシャフト<br>ドイツ連邦共和国 81669 ミュンヘ<br>ン ザンクト マルティン シュトラーゼ<br>53 |

| <b>(85) 翻訳文提出日</b>                            | 平成17年4月18日 (2005.4.18)                                                                                                                 | (74) 代理人 110000338<br>特許業務法人原謙三国際特許事務所                                                                     |

| <b>(86) 國際出願番号</b>                            | PCT/DE2003/003354                                                                                                                      | (72) 発明者 ブレーダーロー, ラルフ<br>ドイツ連邦共和国 85586 ポーイン<br>グ ズーデンテンシュトラーゼ 51                                          |

| <b>(87) 國際公開番号</b>                            | W02004/038802                                                                                                                          | (72) 発明者 ハートヴィヒ, ジェシカ<br>ドイツ連邦共和国 85579 ノイビー<br>ベルク ウンタービーベアガーナー シュトラ<br>ーゼ 25                             |

| <b>(87) 國際公開日</b>                             | 平成16年5月6日 (2004.5.6)                                                                                                                   |                                                                                                            |

| <b>(31) 優先権主張番号</b>                           | 102 48 723.5                                                                                                                           |                                                                                                            |

| <b>(32) 優先日</b>                               | 平成14年10月18日 (2002.10.18)                                                                                                               |                                                                                                            |

| <b>(33) 優先権主張國</b>                            | ドイツ (DE)                                                                                                                               |                                                                                                            |

| <b>(81) 指定国</b>                               | EP (AT, BE, BG, CH, CY, CZ, DE, DK, EE,<br>ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR<br>, CN, JP, KR, SG, US) |                                                                                                            |

(54) 【発明の名称】キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

## (57) 【要約】

プレーナ型であることが好ましいトランジスタ (142) とキャパシタ (144) とを有する集積回路構造 (140) が開示されている。キャパシタ (44) の下部電極は、トランジスタ (142) のチャネル領域と共に、1つのSOI基板に配置されている。回路構造 (140) は、簡単に製造でき、優れた電子特性を有している。

**【特許請求の範囲】****【請求項 1】**

電気的に絶縁性の絶縁領域と、少なくとも1つの連続した領域とを有する集積回路構造(140)であって、

上記連続した領域は、キャパシタ(144)を形成しているとともに、上記絶縁領域に近接した電極領域(34)と、

誘電体領域(46)と、

絶縁領域から離れた電極領域(56)とをこの順で有しており、

上記絶縁領域が、平面に配置された絶縁層(14)の一部であり、

上記集積回路構造(140)の上記キャパシタ(144)と、少なくとも1つの能動素子(142)とが、上記絶縁層(14)に対して同じ側に配置されており、

上記絶縁領域に近接した電極領域(34)と、上記素子(142)の活性領域(84)とが、絶縁層(14)の配置されている平面と平行な平面に配置されている、集積回路構造(140)。

**【請求項 2】**

少なくとも1つの電界効果トランジスタ(142)にて特徴付けされており、

この電界効果トランジスタ(142)のチャネル領域(84)が、活性領域であり、上記チャネル領域(84)が、ドープまたは非ドープされていることが好ましく、

および／または、電界効果トランジスタ(142)の制御電極(54)が、絶縁領域から離れた電極領域(56)と同じ材料および／または同じドーパント濃度の材料を含み、

および／または、電界効果トランジスタ(142)の制御電極絶縁領域(42)が、誘電体領域(46)と同じ材料および／または同じ厚みを有する材料を含み、

および／または、電界効果トランジスタ(142)の制御電極絶縁領域(42)が、誘電体領域(46)とは異なる材料および／または異なる厚みを有する材料を含む請求項1に記載の回路構造(140)。

**【請求項 3】**

上記電界効果トランジスタ(142)が、プレーナ型の電界効果トランジスタであり、

および／または、上記トランジスタが、補助端子領域(58, 59)を含み、

これらの補助端子領域は、端子領域(80, 82)と同じ導電型ではあるが少なくとも1桁だけ小さいドーパント濃度にドーピングされており、

および／または、上記トランジスタが、補助ドーピング領域を備え、これらの補助ドーピング領域は、端子領域(80, 82)および／または補助端子領域(58, 59)に近接して配置されており、端子領域(80, 82)および／または補助端子領域(58, 59)とは異なる導電性型のドーピングを有し、

および／または、上記制御電極(54)が、金属半導体組成物、特に、ケイ化物領域(92)を含む領域に隣接している、請求項2に記載の回路構造(140)。

**【請求項 4】**

トランジスタ(142)の1つの端子領域(80, 82)またはトランジスタ(142)の両方の端子領域(80, 82)が、絶縁層(14)に隣接し、

および／または、少なくとも1つの端子領域(80, 82)が、金属半導体組成物を含む領域、好ましくはケイ化物領域(90, 96)と隣接し、

および／または、少なくとも1つの端子領域(80, 82)の絶縁領域から離れた境界面が、活性領域(84)よりも、絶縁層(14)から離れており、または、

および／または、絶縁領域から離れた少なくとも一つの端子領域(80, 82)の境界面が、活性領域(84)よりも、絶縁層(14)から離れており、

または、絶縁領域から離れた少なくとも一つの端子領域(80, 82)の境界面が、活性領域(84)が絶縁領域から離れた活性領域(84)の境界面よりも絶縁層(14)に近接して配置されている、請求項2または3に記載の回路構造(140)。

少なくとも1つの端子領域(80, 82)の絶縁領域から離れた境界面が、活性領域(84)の絶縁領域から離れた境界面よりも、絶縁層(14)の近くに配置されている、請

10

20

30

40

50

求項 2 または 3 に記載の回路構造 ( 1 4 0 )。

**【請求項 5】**

スペーサ ( 6 0 , 6 2 ) が、制御電極 ( 5 4 ) の両側に配置されており、これらのスペーサは、制御電極 ( 5 4 ) とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンを含み、または、これらのスペーサは、制御電極 ( 5 4 ) とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンからなり、

および / または、スペーサ ( 6 4 , 6 6 ) が、絶縁領域から離れた電極領域 ( 5 6 ) の少なくとも一方側に配置されており、このスペーサは、上記絶縁領域から離れた上記電極領域 ( 5 6 ) とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンを含み、または、このスペーサは、上記絶縁領域から離れた上記電極領域 ( 5 6 ) とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンからなり、10

および / または、制御電極 ( 5 4 ) に配置されたスペーサ ( 6 2 a ) と、絶縁領域から離れた電極領域 ( 5 6 ) に配置されたスペーサ ( 6 4 a ) とが相互に接触する、請求項 2 から 4 のいずれか 1 項に記載の回路構造 ( 1 4 0 )。

**【請求項 6】**

上記電界効果トランジスタ ( 1 4 2 ) の端子領域 ( 8 2 ) と、キャパシタ ( 1 4 4 ) の絶縁領域に近接した電極領域 ( 3 4 ) とが、相互に隣接し、境界で導電性接続されており、

および / または、絶縁領域に近接した電極領域 ( 3 4 ) に隣接する上記トランジスタ ( 1 5 2 ) の端子領域 ( 5 9 a ) が、金属半導体組成物を含む領域、特に、ケイ化物領域に隣接せず、20

および / または、他の端子領域 ( 8 0 a ) が、金属半導体組成物を含む領域 ( 7 0 a ) に隣接する、請求項 2 から 5 のいずれか 1 項に記載の回路構造 ( 1 4 0 )。

**【請求項 7】**

端子領域 ( 8 2 ) に隣接する、絶縁領域に近接した電極領域 ( 3 4 ) の側面が、上記側面を横断するように配置されている、絶縁領域に近接した電極領域 ( 3 4 ) の側面よりも長く、好ましくは少なくとも 2 倍または少なくとも 5 倍は長く、

トランジスタ ( 1 4 2 ) が、好ましくはトランジスタ幅 ( W 1 ) を有し、このトランジスタ幅は、最小形状 ( F ) の倍数であり、好ましくは 3 倍または 5 倍を上回り、30

または、端子領域 ( 8 2 ) に隣接する、絶縁領域に近接した電極領域 ( 3 4 ) の側面を横断するように配置されている、絶縁領域に近接した電極領域 ( 3 4 ) の側面が、端子領域 ( 8 2 ) に隣接している側面よりも長く、好ましくは少なくとも 2 倍または少なくとも 5 倍は長く、

トランジスタ ( 1 5 2 ) が、好ましくはトランジスタ幅 ( W 2 ) を有しており、このトランジスタ幅は、最小形状 ( F ) の 3 倍未満であり、好ましくは最小形状 ( F ) の 2 倍未満である、請求項 6 に記載の回路構造 ( 1 4 0 )。

**【請求項 8】**

上記絶縁領域に近接した上記電極領域 ( 3 4 ) が、単結晶領域、好ましくはドープされた半導体領域であり、

および / または、上記絶縁領域に近接した上記電極領域 ( 3 4 ) および / または活性領域 ( 8 4 ) が、1 0 0 nm 未満、または、5 0 nm 未満の厚みを有しており、40

および / または、上記活性領域 ( 8 4 ) が、単結晶領域、好ましくはドープまたは非ドープされた半導体領域であり、

および / または、上記絶縁層 ( 1 4 ) が、一方の側面で、担体基板 ( 1 2 ) 、好ましくは担体基板に隣接し、この担体基板は、半導体材料を含むんでいるか、または、半導体材料、特にシリコンまたは単結晶シリコンからなり、

および / または、上記絶縁層 ( 1 4 ) が、他方の側面で、上記絶縁領域に近接した上記電極領域 ( 3 4 ) に隣接し、

および / または、境界面が、好ましくは 2 つの相互に平行な面に完全に含まれており、

および / または、絶縁層 ( 1 4 ) が、電気的に絶縁性のある材料、好ましくは酸化物、50

特に二酸化シリコンを含み、

または、電気的に絶縁性のある材料、好ましくは酸化物、特に二酸化シリコンからなり、

および／または、能動素子（142）が、トランジスタ、好ましくは電界効果トランジスタ、特にブレーナ型の電界効果トランジスタである、請求項1～7のいずれか1項に記載の回路構造（140）。

#### 【請求項9】

上記誘電性領域（46）が、二酸化シリコンを含み、または、二酸化シリコンからなり

、

および／または、上記誘電性領域（46）が、4以上または10以上または50以上の誘電定数を有する材料からなり、

および／または、上記絶縁領域から離れた上記電極領域（56）が、シリコン、好ましくは多結晶シリコンを含み、または、シリコン、好ましくは多結晶シリコンからなり、

および／または、上記絶縁領域から離れた上記電極領域（56）が、金属を含み、または、金属からなり、

および／または、上記絶縁領域から離れた上記電極領域（56）が、低インピーダンス材料、好ましくは窒化チタン、窒化タンタル、ルビジウムまたは高ドープしたシリコングルマニウムを含み、

および／または、上記絶縁領域から離れた上記電極領域（56）が、金属半導体組成物を含む領域、特にケイ化物領域（96）に隣接する、上記請求項1～8のいずれか1項に記載の回路構造（140）。

#### 【請求項10】

上記回路構造が、少なくとも1つの処理器、好ましくはマイクロ処理器を含み、

および／または、上記キャパシタ（154）と能動素子（152）とが、メモリセル（150）を、特に、ダイナミックRAMメモリユニットに形成し、

および／または、メモリセルが、キャパシタ（152）およびただ1つのトランジスタ（152）、または、キャパシタ（Cs）および複数のトランジスタ（M1～M3）、好ましくは3つのトランジスタ（M1～M3）のどちらかを含む、請求項1～9のいずれかに記載の回路構造（140）。

#### 【請求項11】

キャパシタ（144）を有する集積回路構造（140）、特に上記請求項1から10のいずれか1項に記載の回路構造（140）の製造方法において、

規定の順序に制限されることなく、

電気的に絶縁性の材料から成る絶縁層（14）と、半導体層（16）とを含む基板（10）を用意し、

キャパシタ用の少なくとも1つの電極領域（34）を形成するため、および、トランジスタ（142）用の少なくとも1つの活性領域（84）を形成するために、半導体層（16）をパターン化し、

半導体層（16）をパターン化した後、少なくとも1つの誘電性層（42、46）を生成し、

誘電性層（42、46）を生成した後、電極層（41）を生成し、

上記電極層（41）の絶縁領域から離してキャパシタ（144）の電極（56）を形成する方法工程を実施する方法。

#### 【請求項12】

パターン化の前に半導体層（16）に少なくとも1つの補助層（18、20）、好ましくは窒化シリコン層（20）および／または酸化物層（18）を形成する工程であって、補助層（20）が、半導体層（16）のパターン化中に、好ましくはハードマスクの機能を果たすようになっており、

および／または、好ましくは誘電性層（42、46）の生成前に、トランジスタ（142）のチャネル領域（84）をドーピングし、

角取り酸化物（26、28）を形成するために、好ましくは電極層（41）を形成する

10

20

30

40

50

前に、熱酸化し、

および／または、好ましくは誘電性層（42，44，46）を生成する前に、上記絶縁領域に近接した電極（34）をドーピングし、

および／または、トランジスタ（122）の活性領域（84）に、誘電性層と同時に誘電性層（42，46）を生成し、

および／または、上記絶縁領域から離れた電極領域（56）の形成と同時にトランジスタ（142）の制御電極（54）を形成することを特徴とする、請求項11に記載の方法。

### 【請求項13】

好ましくはトランジスタ（142）の制御電極（54）をパターン化した後に、トランジスタ（142）の端子領域（80，82）よりも低いドーパント濃度を有する補助端子領域（58，59）を形成し、

および／または、好ましくは制御電極（54）をパターン化する前に、補助ドーピング領域を形成し、

トランジスタ（142）の制御電極（54）をパターン化した後に、更なる補助層（60から66）、好ましくは窒化シリコン層または二酸化シリコン層、特にTEOS層を形成し、

および／または、更なる補助層（60～66）を異方性エッティングすることを特徴とする、請求項11または12に記載の方法。

### 【請求項14】

上記絶縁領域から離れた電極領域（56）を形成した後、および／または、トランジスタ（142）の制御電極（54）をパターン化した後、半導体材料（16）からなる露出領域に、選択的エピタキシーを行い、

および／または、上記絶縁領域から離れた電極領域（56）を形成した後、および／または制御電極（54）をパターン化した後、および、好ましくはエピタキシーの後、トランジスタ（122）の端子領域（70、72）をドーピングすることを特徴とする、請求項11から13のいずれか1項に記載の方法。

### 【請求項15】

電極層（54）、および／または、露出半導体領域（16）に、金属半導体組成物、特に、ケイ化物を選択的に形成することを特徴とする、請求項11から14のいずれか1項に記載の方法。

### 【発明の詳細な説明】

### 【発明の詳細な説明】

### 【0001】

本発明は、電気的に絶縁性の絶縁領域と、少なくとも1つのキャパシタとを有する集積回路構造に関する。キャパシタは、連続した領域、すなわち、絶縁領域に近接した電極領域と、誘電性領域と、絶縁領域から離れた電極領域とからこの順で形成されている。

### 【0002】

電気的に絶縁性の絶縁領域は、例えば20 の室温で  $10^{12}$  cm<sup>-2</sup> (オームセンチメートル) を上回る抵抗を有する電気的に絶縁性のある材料(例えば、酸化物、特に二酸化シリコン)からなる。電極領域は、例えば20 の室温で、 $10^{-4}$  cm<sup>-2</sup> を下回る電気抵抗を有する金属を含んでいる。あるいは、電極領域は、例えば高ドープされた多結晶シリコンを含んでいる。誘電性領域は、同じく、電気的に絶縁性のある材料(例えば、酸化物、特に約3.9の誘電定数を有する二酸化シリコン)からなる。しかしながら、著しく大きな誘電定数を有する誘電性材料も、誘電性領域に使用される。

### 【0003】

本発明の目的は、キャパシタを有し、簡単に製造できる集積回路構造を提供することである。目的は、上記回路構造を、特に少ないプロセス工程および特に少ないリソグラフィーマスクを使用して製造できるようにすることである。さらに、目的は、キャパシタを有する集積回路構造の簡単な製造方法を提供することである。

10

20

30

40

50

**【 0 0 0 4 】**

この回路構造に関する目的は、特許請求項1に記載の特徴を有する集積回路構造によって達成される。発展形態は、従属請求項に記載されている。

**【 0 0 0 5 】**

本発明の回路構造では、絶縁領域が、1つの平面に配置された絶縁層の一部である。キャパシタおよび集積回路構造の少なくとも1つの能動素子、好ましくは集積回路構造の全ての能動素子は、絶縁層の同じ側に存在している。さらに、絶縁領域に近接した電極領域および素子の活性領域は、1つの平面に配置されている。この平面は、絶縁層が配置されている平面に対して平行である。

**【 0 0 0 6 】**

本発明の回路構造は、簡単に構成されている。また、本発明の回路構造を、簡単な方法で製造できる。なぜなら、絶縁領域に近接した電極領域と、活性領域とが、1つの平面に配置されているからである。さらに、絶縁領域に近接した電極領域と活性領域とが、絶縁領域によって絶縁されている。従って、自由に選択可能な電位を、キャパシタの両方の電極領域に印加できる。

10

**【 0 0 0 7 】**

さらに、キャパシタは、優れた電子特性を有している。寄生容量と有効容量に関する抵抗との間の比率が小さい。漏れ電流が少ない。容量の差動非線形性が少ない。なお、異なる差動容量は、空間電荷ゾーンに由来するものである。アナログ容量では、差動容量が、動作点において有効な容量である。容量が、広い動作点範囲にわたって一定である。得られる容量／面比率が大きく、例えば1平方 $\mu\text{m}$ につき10フェムトファラッドを上回るか、または、1平方 $\mu\text{m}$ につき20フェムトファラッドを上回ることさえある。

20

**【 0 0 0 8 】**

さらに、能動素子とキャパシタとの間に、他の層または他の層連続は不要である。その結果、必要な層の数を少なくし、集積回路構造の平面性を高められる。

**【 0 0 0 9 】**

一発展形態では、能動素子が、電界効果トランジスタである。電界効果トランジスタのチャネル領域は、活性領域である。電界効果トランジスタの制御電極は、パターン化された電極層の一部であり、このパターン化された電極層には、キャパシタの絶縁領域から離れた電極領域も配置されている。制御電極と絶縁領域から離れた電極領域とは、同じ材料からなる。これらの領域の厚みおよびそのドーパント濃度も一致している。一実施形態では、電界効果トランジスタの制御電極絶縁領域が、キャパシタの誘電性領域と同じ材料からなる。これらの領域の厚みも一致している。

30

**【 0 0 1 0 】**

この措置により、キャパシタの製造および電界効果トランジスタの製造には、たった3つの製造プロセスがあればよい。電界効果トランジスタ、および、同じ層に位置しているキャパシタの領域を、共通してパターン化できる。キャパシタを製造するための追加のマスクは、キャパシタの下部電極領域を、電界効果トランジスタのチャネル領域とは異なるようにドープする場合にだけ必要である。更なる追加のマスクは、材料および／または制御電極絶縁領域とキャパシタの誘電性領域との絶縁厚みが異なる場合にだけ必要である。しかしながら、たとえそうであっても、回路構造の製造に必要なマスクの数は依然として少ない。

40

**【 0 0 1 1 】**

次の発展形態では、電界効果トランジスタが、ブレーナ型の電界効果トランジスタである。すなわち、ゲート電極を制御するために有効な面が、絶縁層に対して平行に存在している。電界効果トランジスタは、HDD端子領域（高ドープされたドレイン）の他に、場合によっては、LDD端子領域（軽くドープされたドレイン）または補助端子領域、および／または、ここでは補助ドーピング領域として表されている、いわゆるポケットまたはハロをさらに含んでいる。

**【 0 0 1 2 】**

50

他の実施形態では、制御電極が、ケイ化物領域に隣接している。この措置により、制御電極と簡単に接触できる。さらに、接触抵抗とシート抵抗とが低減される。本発明の回路構造の次の発展形態では、電界効果トランジスタの端子領域が、絶縁層に隣接している。一実施形態では、端子領域が、同じくケイ化物領域に接している。ケイ化物を形成するために充分な材料が存在しているのは、端子領域の半導体層が、ケイ化物形成の前にも後にも、絶縁領域に近接した電極の領域よりも厚くなっている場合である。

#### 【0013】

次の発展形態では、スペーサが、制御電極の両側に配置されている。これらのスペーサは、電極層とは異なる材料を含んでいるか、または、異なる材料からなり、特に、半導体エピタキシャル層を生成するためのエピタキシー方法の間のエピタキシャル層成長のための開始点としては適していない材料（例えば、窒化シリコン）からなる。スペーサを使用することにより、制御電極の側部領域が被覆され、その結果、そこからはエピタキシーが進行せず、短絡回路が回避される。

#### 【0014】

一実施形態では、同じく、スペーサが、絶縁領域から離れた電極領域の少なくとも一方側に配置されている。このスペーサは、制御電極に配置されたスペーサと同じ機能を果たしている。ゲートに配置されたスペーサと、キャパシタの電極に配置されたスペーサとが、相互に接触すると、マスキングが生じる。このマスキングにより、例えばマスクされた領域では、ドーピングまたはケイ化が防止される。

#### 【0015】

一発展形態では、トランジスタの1つの接続領域に隣接する、絶縁領域に近接した電極領域の側が、この側を横断するように配置されている、絶縁領域に近接電極領域の側よりも、好ましくは少なくとも2倍、または少なくとも5倍は長い。この場合、トランジスタは、最小形状の倍数の（好ましくは、3倍または5倍の）トランジスタ幅を有している。この措置により、トランジスタとキャパシタとの間に、特に低インピーダンスの接続が生じる。これにより、特にアナログ回路にあるいわゆるアナログ容量では、電子特性が向上する。このようなアナログ回路の例としては、アナログ - デジタル変換機があげられる。アナログ容量の他の例としては、操作電圧線または信号線での円滑な電圧スパイクのために使用できる、いわゆるバイパス容量があげられる。

#### 【0016】

代替の発展形態では、これとは対照的に、端子領域に隣接している絶縁領域に近接した電極領域の側面を横断するように配置されている側面であって、絶縁領域に近接した電極領域の側面が、端子領域に隣接している側面よりも長く、好ましくは少なくとも2倍または少なくとも5倍は長い。この場合、トランジスタのトランジスタ幅は、最小形状の3倍を下回る、好ましくは最小形状の2倍を下回っている。特にメモリセルの場合は、措置によって、キャパシタの下部電極の非反応抵抗が高まり、その結果、メモリ容量の急速な放電が阻止される。

#### 【0017】

次の発展形態では、電界効果トランジスタの端子領域と、キャパシタの絶縁領域に近接した電極領域とが相互に隣接し、導電接続を形成している。こうして、D R A M（ダイナミックランダムアクセスメモリ；Dynamic Random Access Memory）の簡単に構成されたメモリセルが生じ、絶縁領域に近接した下部電極と接触するための追加の措置は必要ない。この発展形態を、特に、ゲートおよびキャパシタの被覆電極において相互に接触するスペーサと組み合わせて使用する。

#### 【0018】

一発展形態では、絶縁領域に近接した電極領域と、活性領域とが、半導体材料を含む半導体領域である。なお、半導体材料とはすなわち、 $10^{-6}$  と  $10^{+12}$  cmとの間、特に、 $10^{-5}$  と  $10^{+10}$  cmとの間の電気抵抗を有する材料（例えば、ゲルマニウム、シリコンまたはヒ化ガリウム）である。キャパシタの絶縁領域に近接した電極領域の抵抗は、一実施形態では、ドーピングによって低減されている。

10

20

30

40

50

## 【0019】

回路構造の一発展形態では、絶縁領域に近接した電極領域および活性領域が、ドープまたは非ドープ単結晶領域である。単結晶層の能動素子の電子特性は、特に良好である。さらに、キャパシタの単結晶電極の電気抵抗を、ドーピングによって特に良好に低減できる。一実施形態では、絶縁領域に近接した電極領域と活性領域とが、100nm未満の厚みを有しており、50nm未満の厚みのことさえある。

## 【0020】

次の発展形態では、いわゆるSOI基板(Silicon On Insulator)のように、絶縁層が担体基板に隣接している。このような基板は、簡単に製造できる。さらに、これらの基板に配置される電子回路は、特に良好な電子特性を有している。

10

## 【0021】

他の発展形態では、回路構造が、複数の論理的切り替え機能を有する少なくとも1つの処理器を含んでいる。一実施形態では、回路構造が、処理器の他に、複数のDRAMメモリユニット(ダイナミックランダムアクセスメモリ; Dynamic Random Access Memory)をさらに含んでいる場合は、埋め込み型メモリという用語も使用される。この回路構造を製造するには、論理部を製造するためにずれにせよ必要な本発明のプロセス工程およびマスクの他に、ほんの少数の追加のプロセス工程と追加のマスクとが、キャパシタまたはキャパシタに導電接続されているトランジスタを製造するために必要である。

## 【0022】

さらに、本発明は、他の観点では、集積回路構造の製造方法に関する。特に、本発明は、本発明または本発明の発展形態の1つに基づく回路構造の製造方法に関する。本発明の方法では、電気的に絶縁性の材料を含む絶縁層と、半導体層とを有する基板(例えば、SOI基板)を用意し、キャパシタ用の少なくとも1つの電極領域を形成するため、および、トランジスタの少なくとも1つの活性領域を形成するために、半導体層をパターン化し、半導体層をパターン化した後、誘電性層を生成し、誘電性層を生成した後、電極層を生成し、キャパシタの絶縁領域から離れた電極と、トランジスタの制御電極とを電極層に形成する方法工程を、規定の順序に制限されることなく実施する。

20

## 【0023】

本発明の方法は、プレーナ型の電界効果トランジスタをキャパシタと共に製造するのに特に適している。本発明の回路構造およびその発展形態の上記技術的効果は、本発明の方法およびその発展形態にも当てはまる。

30

## 【0024】

本発明の一実施例について、添付の図を参考にして以下に説明する。

## 【0025】

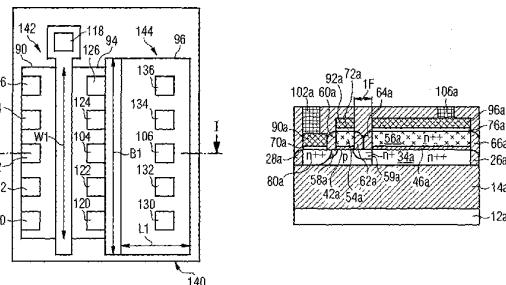

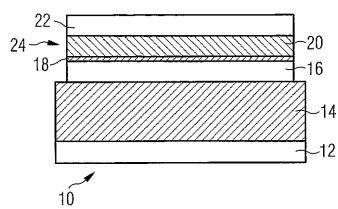

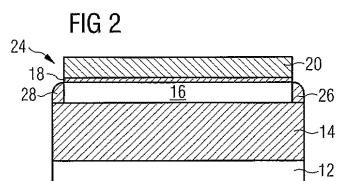

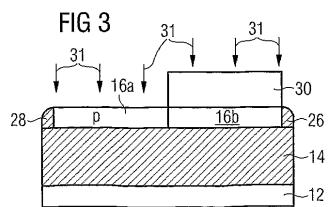

図1～図12は、集積トランジスタ-キャパシタ構造の製造の製造段階を示す図である。図13は、トランジスタ-キャパシタ構造を示す平面図である。図14は、トランジスタを有するDRAMメモリセルを示す断面図である。図15は、DRAMメモリセルの平面図である。図16は、3つのトランジスタを有するDRAMメモリセルの回路図である。

40

## 【0026】

図1～図12は、トランジスタ-キャパシタ構造の製造の製造段階を示し、切断面Iに沿った断面図に関するものである。この切断面は、電界効果トランジスタのチャネルに対して縦に、特に、チャネルの電流フローに対して縦になっている。切断面Iの位置は、図13にされている。

## 【0027】

まず、トランジスタ-キャパシタ構造の製造は、SOI基板10を用意する。このSOI基板10は、単結晶シリコンを含む担体基板12と、例えば二酸化シリコンを含むいわゆる埋め込み絶縁層14と、単結晶シリコンを含む薄い半導体層16とを有している。本実施例では、担体基板12の厚みは、550μmであり、絶縁層14の厚みは、100nmであり、半導体層16の厚みは、50nmである。この半導体層16の上には、例え

50

厚みが 5 nm の薄い二酸化シリコン層 18 が形成されている。

【0028】

SOI 基板 10 上に、図 1 に示すように、例えば CVD 方法（化学蒸着；Chemical Vapor Deposition）によって窒化シリコン層 20 を堆積する。実施例では、この窒化シリコン層 20 の厚みは、50 nm である。

【0029】

続いて、図 1 に示すように、リソグラフィー方法を実施する。このリソグラフィー方法によって、フォトレジスト層 22 を全面的に形成し、所定のレイアウトに応じて感光し、現像する。続いて、ハードマスクとして機能する窒化物層 20 と、二酸化シリコン層 18 と、半導体層 16 とを、例えば乾式エッチング方法によってパターン化する。このパターン化の結果、ほぼ四角形の底面を有する積層（メサともいう）24 が生じる。製造される電界効果トランジスタの幾何学形状、および、キャパシタの幾何学形状は、予め互いに独立して規定することができる。従って、これらの幾何学形状を最適化することができる。

【0030】

フォトリソグラフィー方法の代わりに、他の実施例において、電子線リソグラフィー方法または他の適切な方法を実施してもよい。また、さらに他の実施例では、ハードマスクを使用しなくてもよい。この場合には、例えばフォトレジスト層 22 を、さらに厚く形成する。

【0031】

続いて、図 2 に示すように、フォトレジスト層 22 の残りの領域を除去する。フォトレジスト層 22 を除去した後、熱酸化する。このプロセスでは、半導体層 16 の側面に角取り酸化物領域（Verrundungsoxidbereiche）26・28 が、形成される。この角取り酸化領域 26 は、後に端部に望ましくないチャネルが形成されることを防止する。

【0032】

また、絶縁を目的として、LOCOS 方法（シリコンの局部酸化；LOCal Oxidization of Silicon）または STI 方法（トレンチ分離；Shallow Trench Isolation）を、CMP 方法（化学機械研磨；Chemical Mechanical Polishing）と組み合わせて実施できる。

【0033】

次に、窒化物層 20 と二酸化シリコン層 18 との残りの領域を、例えば、乾式エッチングにより除去する。ここで、薄いスクリーン酸化物（不図示）を、後の埋め込み工程のために形成してもよい。その後、図 3 に示すように、nMOSFET を製造するために、フォトレジスト層 30 をさらに形成し、感光し、現像する。その結果、トランジスタのチャネル領域および端子領域用の領域のみマスクされていない（半導体層 16 のトランジスタ部 16a を参照）。

【0034】

これに対して、キャパシタ用に準備された領域は、マスクされている（半導体層 16 のキャパシタ部 16b を参照）。フォトレジスト層 30 を現像した後、イオン埋め込み 31 を実施し、トランジスタ部を p ドープ（例えば、p または p<sup>+</sup>）する。

【0035】

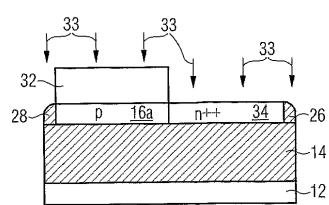

続いて、図 4 に示すように、さらにフォトリソグラフィー方法を実施する。このフォトリソグラフィー方法では、キャパシタを製造するための追加のマスクが必要である。フォトレジスト層 32 を形成し、マスクを用いて感光し、現像する。その結果、トランジスタ部 16a は、マスクされたままであり、キャパシタ部 16b はマスクされていない。

【0036】

その後、パターン化したフォトレジスト層 32 を用いて、イオン埋め込み 33 を実施する。このとき、キャパシタ部 16b が、強く n ドープ（すなわち、n<sup>++</sup> ドープ）され、下部電極領域 34 が生じる。

【0037】

イオン埋め込み 33 の間マスクされたトランジスタ部 16a では、ドーピングは変化しない。付加埋め込みの結果、下部電極領域 34 は低インピーダンスになる。例えば、ド-

10

20

30

40

50

ピング密度は、1立方センチメートルにつき $10^{20}$ 個のドーピング原子の密度となる。ドーピング密度は、1立方センチメートルにつき $10^{19}$ と $10^{21}$ 個との間の範囲のドーピング原子の密度であることが好ましい。ドーピング濃度が高まるにつれて、誘電体は、非ドープ領域または中くらいの強さにドープされた領域よりもより迅速に成長する。しかしながら、ドーピング濃度が高まるにつれて、生成される空間電荷ゾーンがより小さくなる。その結果、寄生効果も、同じくより小さくなる。

## 【0038】

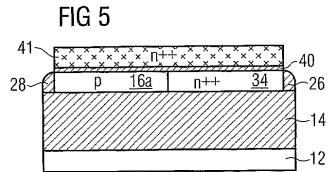

フォトトレジスト層32を、図5に示すように、続いて除去する。続いて、半導体層16のトランジスタ部16aの露出領域と、下部電極領域34の露出領域とに、薄い二酸化シリコン層40を生成する。この二酸化シリコン層は、トランジスタの領域のゲート酸化物42と、キャパシタの領域の誘電体46とから形成されている。10

## 【0039】

この二酸化シリコン層40は、例えば、熱によって成長させることができる。本実施例では、二酸化シリコン層40は、非ドープシリコンの領域では2nmの厚みを有している。他の実施例では、更なるリソグラフィー方法を使用して、キャパシタの下部電極領域34上に、半導体層16のトランジスタ部16b上とは異なる材料を含む誘電体、および/または、異なる厚みを有する誘電体を生成する。

## 【0040】

続いて、図5にさらに示すように、インシチュドープ(*in-situ*)、または、後からドープした多結晶シリコンを堆積し、ポリシリコン層41を生成する。このポリシリコン層41の厚みは、例えば100nmである。また、このポリシリコン層41のドーピング濃度は、1立方cmにつき $10^{21}$ 個のドーピング原子である。ここで、n伝導型の強いドーピングを、同じく、符号 $n^{++}$ で表す。またドーピング原子としては、例えばリン原子を用いる。他の実施例において、良好な伝導性があり、適切な材料仕事関数を有する代替材料を、ポリシリコン層41の代わりに使用してもよい。20

## 【0041】

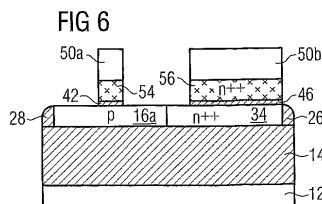

続いて、図6に示すように、特にゲート電極54をパターン化するために、リソグラフィー方法をさらに実施する。このために、フォトトレジスト層を形成し、感光し、現像する。これによって、フォトトレジスト領域50a・50bが生成される。その後、ポリシリコン層41と二酸化シリコン層40とを、例えばエッティングによってパターン化する。その結果、フォトトレジスト層領域50aの下側にゲート電極54が生じる一方、フォトトレジスト層領域50bの下側に被覆電極56が生じる。エッティングは、それぞれ、半導体層16のトランジスタ部16a、および、下部電極領域34で停止する。30

## 【0042】

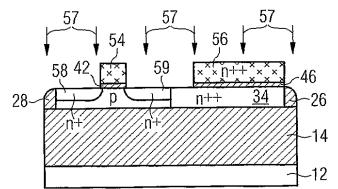

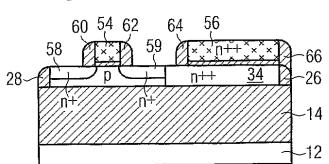

このエッティングの後に、図7に示すように、フォトトレジスト層領域50a・50bを除去する。次に、イオン埋め込み57を行う。これは、弱くドープされたLDD領域58・59(軽くドープされたドレイン; Lightly Doped Drain)を、半導体層16のトランジスタ部16aの上部領域に生成するためである。

## 【0043】

続いて、図8に示すように、薄いTEOS層または窒化シリコン層を、例えばCVD方法(化学蒸着; Chemical Vapor Deposition)によって、全面的に堆積する。窒化シリコン層60の厚みは、本実施例では50nmである。続いて、さらに同図に示すように、TEOS層を異方性エッティングプロセスでエッチバックし、ゲート電極54の側壁にスペーサ60・62を形成する一方、被覆電極56の側壁にスペーサ64・66を形成する。40

## 【0044】

これにより、ゲート電極54と被覆電極56とは、全ての側面が絶縁される。それゆえ、ゲート電極54および被覆電極56の側面では、エピタキシーが不可能である。その結果、短絡が回避される。

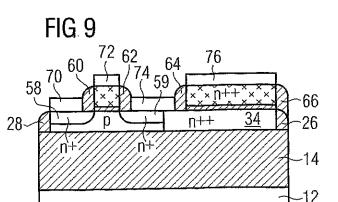

## 【0045】

続いて、図9に示すように、選択的エピタキシー方法を行う。この方法により、単結晶50

エピタキシャル層が、LDD領域58・59および下部電極領域54の露出領域部に成長される。このため、エピタキシャル領域70・74が、半導体層16の単結晶シリコン上に生成される。このエピタキシャル領域70・74は、それぞれ、ゲート電極54および被覆電極56の高さの半分まで伸びている。エピタキシャル領域70・74を、「隆起」ソース／ドレイン領域とも呼ぶ。

#### 【0046】

エピタキシャル領域70・74のエピタキシャル層の厚みは、主に、半導体層16の厚みと、以下で説明するケイ化反応とに依存している。このケイ化反応は、既存のシリコンを消費する。従って、反応用に相当する多くのシリコンを用意する。この措置により、ドレイン／ソース領域の領域でチャンネル端子が「引き剥がれる」ことを防止することができる。ゲート電極54と被覆電極56とには、それぞれ、エピタキシャル領域72・76が配置されている。エピタキシャル領域72・76が配置されない他のゲート材料を使用してもよい。

#### 【0047】

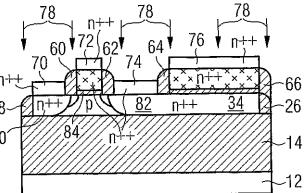

エピタキシーメソッドの後、図10に示すように、イオン埋め込み78（例えば、 $n^{++}$ 、すなわち、強いnドープ）を行う。これは、高ドープされた、すなわち、低インピーダンスのソース／ドレイン80・82を製造するためである。このプロセスのときに、エピタキシャル領域70～76もドープする。マスクは、ここでは、CMOS（相補型金属酸化膜半導体；Complementary Metal Oxide Semiconductor）プロセス時に、相補的トランジスタを有する領域を分離するためだけに必要である。ソース／ドレイン領域82と、キャパシタの下部電極領域34との間が接続される。

#### 【0048】

半導体層16のトランジスタ部16aのソース／ドレイン領域80・82間にあるチャネル領域84は、pドープされたままである。スペーサ60・62と、ゲートスタックとは、埋め込み時に埋め込みマスクとしての機能を果たす。

#### 【0049】

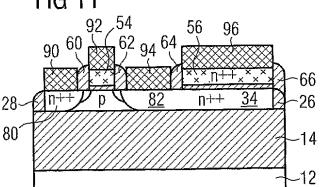

ケイ化反応方法（自己整合ケイ化反応）は、図11に示すように、HDD埋め込み（高密度ドレイン；High Density Drain）の後に行う。このために、例えば、ニッケル層を、全面的に堆積する。例えば500の温度で、ケイ化ニッケルが、エピタキシャル領域70～76の中、すなわち、ソース／ドレイン領域80・82、ゲート電極54、および被覆電極56上に生じる（ケイ化物領域90～96を参照）。ニッケルの代わりに、摂氏1400度以上の融点を有する他の金属、特に、高融点金属を使用することもできる。これは、例えばケイ化チタン、または、ケイ化コバルトを製造するためのものである。

#### 【0050】

図11に示す実施例では、エピタキシャル領域70～76が完全にケイ化されている。これに対して、半導体層16および被覆領域56は、ケイ化されていない。他の実施例において、半導体層16と被覆電極56との領域も、ケイ化されていてもよい。

#### 【0051】

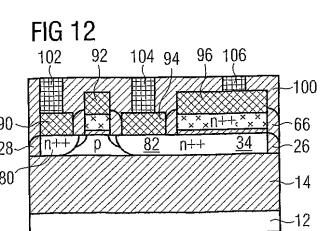

次に、図12に示すように、パッシベーション層100を形成する。このパッシベーション層100の例としては、TEOS層（テトラエチル・オルトリシリケート；Tetra Ethyl Ortho Silicate）、BPSG層（硼素・リンケイ酸ガラス；Bor Phosphorous Silicate Glass）、または、他の適切な材料を含む層が挙げられる。

#### 【0052】

このパッシベーション層100中に、フォトリソグラフィー方法を用いて、コンタクトホールをエッチングにて形成し、このコンタクトホールに例えばタンゲステンを充填する。このタンゲステンの充填により、コンタクト部102・104・106が生じる。

#### 【0053】

これらのコンタクト部102・104・106は、この順番で、それぞれ、ケイ化物領域90、94および96に繋がっている。続いて、コンタクト部102・104・106を、金属被覆層または複数の金属被覆層（図示せず）の相互連結部とさらに接続する。こ

のとき、従来のCMOSプロセス（「バックエンド」とも呼ばれる）を行う。

#### 【0054】

一般的には、接着をより良好にするために、または、拡散障壁として用いるために、コンタクトホールへ中間層をさらに導入する。図の煩雑化を避けるため、図12にはこれらの中間層を記載しない。これらの中間層は、例えば窒化チタンからなる。そして、金属の相互連結部を製造する。この金属の相互連結部は、銅をトレンチに充填する例えればいわゆる2重ダマシン方法を用いて製造する。続いて、化学機械研磨（CMP）によって研磨する。しかしながら、他の方法（例ええば、アルミニウム層のエッティング）を使用してもよい。

#### 【0055】

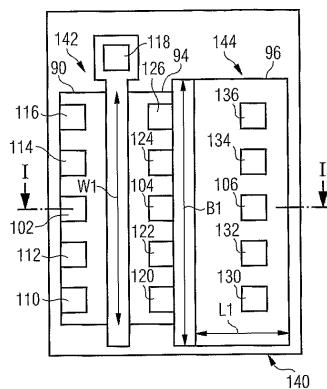

図13は、プレーナ型のSOI-FET142と、キャパシタ144とを含むトランジスタ-キャパシタ構造140を示す、平面図である。トランジスタ142は、最小形状Fの約10倍に相当するトランジスタ幅W1を有している。このトランジスタ幅には、接続部102の他に、ケイ化物領域90に繋がるさらに4つの接触部110～116がある。

#### 【0056】

また、接触部104の他に、同じく、ケイ化物領域94に繋がるさらに4つの接触部120～126がある。また、接触部106の他に、さらに4つの接触部130～136が、ケイ化物96に繋がっており、従って、被覆電極56にも繋がっている。

#### 【0057】

キャパシタ144の長さL1は、その幅B1よりもかなり短い。本実施例では、この幅B1が、トランジスタ幅にほぼ相当する。長さL1は、幅B1のたった約3分の1である。これらの寸法および複数の接続部102～136によって、キャパシタ144を、非常に迅速に逆充電できる。

#### 【0058】

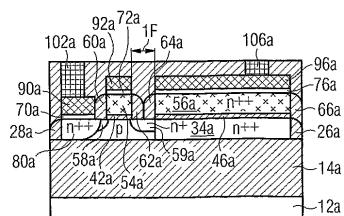

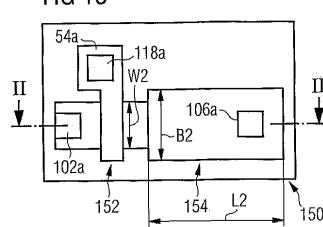

トランジスタ-キャパシタ構造の好ましい応用分野は、ダイナミックメモリセル、特に、図14および図15に記載のような、いわゆる埋め込みDRAMメモリセル150である。メモリセル150は、たった1つのアクセストランジスタ152とキャパシタ154とを含んでいる。図1～図12に関する上記方法工程を、メモリセル150の製造時にも実施することができる。従って、図14および図15では、同じ素子を同じ参照符号ではあるが小文字aを後に付けて識別する。

#### 【0059】

従って、プレーナ型の電界効果トランジスタ152は、特に、制御電極54aと、ゲート酸化物42aと、LDD領域58a・59aと、端子領域80a・82と、スペーサ60a・62aとを含んでいる。キャパシタ154は、下部電極領域34aと、誘電体46aと、被覆電極66aと、スペーサ64aとを含んでいる。

#### 【0060】

端子領域80a、制御電極54a、および被覆電極56a上のそれぞれのエピタキシャル領域70a、72aおよび76aは、完全にケイ化されていない。従って、ケイ化物領域90a～96aは、上記エピタキシャル領域70a・72aおよび76a上に配置されている。

#### 【0061】

図14に、断面II-IIIでのメモリセル150を示す。断面II-IIIを、図15に示す。この断面II-IIIは、トランジスタ152のチャネルにおける電流フローに対して縦方向である。被覆電極56aとゲート電極54aとの間の距離が、最小形状1Fに短縮されている。ゲート電極54aに配置されたスペーサ62aと、被覆電極56aに配置されたスペーサ64aとが相互に接触している。

#### 【0062】

従って、ドレインはケイ化されない。さらに、このことは、ドレイン側には、LDD領域59aだけが存在し、追加の端子領域は存在しないことも意味している。接続部もドレイン領域には繋がっていない。LDD領域59aは、下部電極領域34aに直接繋がって

10

20

30

40

50

いる。こうして上昇した下部電極領域 3 4 a の接触抵抗は、キャパシタ 1 5 4 の放電を阻止する。キャパシタ 1 5 4 の放電も、キャパシタの幅 B 2 がキャパシタの長さ L 2 よりも著しく短いことにより、阻止される。プレーナ型の S O I ドランジスタ 1 5 2 の低い漏れ電流も、メモリ容量の迅速な放電を防止する。

#### 【 0 0 6 3 】

漏れ電流を最小にし、かつ、実装密度はできるだけ高くなるように、トランジスタ 1 5 2 は、例えば 1 . 5 F ~ 3 F の小さなトランジスタ幅 W 2 を有している。キャパシタ 1 5 4 は、水平なストリップの形状を有している。この水平なストリップの長さ L 2 は、メモリセル 1 5 0 が必要とする最小メモリ容量によって決まる。トランジスタ幅 W 2 とキャパシタの幅 B 2 とは、ほぼ一致している。例えば、偏差は、50 パーセント未満である。キャパシタ 1 5 4 を、図 1 3 および図 1 4 のトランジスタ 1 5 2 よりも短くして示す。

#### 【 0 0 6 4 】

中くらいの大きさの S R A M メモリユニット（静的ランダムアクセスメモリ；Static Random Access Memory）を迅速な埋め込み D R A M で置換する場合、例えば、マイクロ処理器メモリ階層の第 2 および第 3 アクセスレベルで、すなわち、第 2 および第 3 レベルキャッシュで、以下の演算を行う。例えば、これまで S R A M メモリセルは、 $134 F^2$  の面を有していた（ただし、F は、最小形状である）。例えば 3 . 9 の誘電定数 r を有する誘電体を使用するならば、以下の演算に基づいて、1 つのメモリセルにつき 1 0 フェムトファラッドの代表的埋め込み D R A M 容量 C H E M を実現できる。酸化物容量は、すなわち：

$$C O X = r / t p h y s = 34 . 5 f F / \mu m^2$$

である。ただし、t p h y s は、実施例では 1 n m になる酸化物厚みである。その結果、メモリ容量が必要とする面 A M E M 、すなわち：

$$A M E M = C M E M / C O X = 0 . 29 \mu m^2$$

が生じる。

#### 【 0 0 6 5 】

65 n m に等しい最小形状 F では、これは、容量のための 69 F<sup>2</sup> またはアクセストランジスタを含む全体的なメモリセルのための 90 F<sup>2</sup> に相当する。従って、埋め込み D R A M メモリセルの面は、134 F<sup>2</sup> の S R A M セルサイズよりもかなり小さい。

#### 【 0 0 6 6 】

有効な酸化物厚みが 1 n m であり、修正が、ゲートおよび上部シリコン空乏のためには 0 . 8 n m であれば、量子力学的な効果により、

$$C O X = 3 . 9 0 / t o x = 19 f F / \mu m^2$$

の面につき、1 容量が生じる。ただし、1 . 8 n m に等しい t o x は、電気的に有効な酸化物厚みを表しており、0 は、自由空間での誘電率を表している。金属ゲートを使用する場合は、電気的に有効な酸化物厚みは、ゲート空乏が存在しなくなるので、約 0 . 4 n m だけ少なくなる。その結果、1 面毎の容量は、

$$C O X = 3 . 9 0 / t o x = 24 f F / \mu m^2$$

に上昇する。

#### 【 0 0 6 7 】

本発明の容量は、いわゆるスパイクを減衰するため、および、集積回路構造の電圧供給時の混信を減衰するためのいわゆるバイパス容量としても使用される。本発明の容量は、特に発振器またはアナログ - デジタル変換機のアナログ容量としても非常に適している。この容量は、いわゆる混合信号回路のため、すなわち、アナログ容量（例えば、メモリセルにあるメモリ容量）を有する回路にも使用される。

#### 【 0 0 6 8 】

他の実施例では、ゲート酸化物の代りに、個別の高 K D R A M 誘電体を使用することもできる。なお、この個別の高 K D R A M 誘電体では、r が 100 を上回り、有効な酸化物厚みが、0 . 1 n m に等しい t e f f を下回っている。個別の高 K D R A M 誘電体の例としては、バリウムストロンチウムチタン酸塩（B S T ）またはエピタキシャルバリウム

10

20

30

40

50

ストロンチウムチタン酸塩を含む誘電体があげられる。これにより、DRAMメモリセルの所用面は、約 $22\text{ F}^2$ に低減する。第2付加マスクを使用して、SOI STACK上の高K誘電体のための領域を規定する。

#### 【0069】

本発明では、容量を、FET面に、すなわち、SOI基板上のいわゆる上部シリコンに集積する。トランジスタの特に高品質のゲート誘電体をキャパシタの誘電体として使用するならば、SOI容量を製造するためにさらに必要なプロセス工程は1つだけである。

#### 【0070】

従来の技術的構成にさらに提供される利点は、純粋な論理ブロックと埋め込みDRAMブロックとの間のプレーナ型の遷移部である。さらに、深いヴィアおよび接触部は回避されている。

#### 【0071】

図1～図15を参照しながら説明した実施例では、LDDドーピング(軽くドープしたドレイン; Lightly Doped Drain)とHDDドーピング(高ドープしたドレイン; Highly Doped Drain)との双方を実施した。これに対し、他の実施例では、HDDドーピングだけを実施し、LDDドーピングを実施しない。別の実施例において、トランジスタとキャパシタとを、別々に、相互に離して配置し、それぞれに、独自の接続部を設けるてもよい。

#### 【0072】

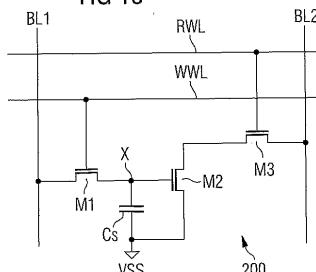

図16に、3つのトランジスタM1～M3と、キャパシタCsとを有するDRAMメモリセル200(ダイナミックランダムアクセスメモリ; Dynamic Random Access Memory)の回路図を示す。DRAMメモリセル200は、図1～図12に関して説明した方法工程で製造されたものである。例えば図14に示すトランジスタ152は、第1の場合のトランジスタM1である。従って、キャパシタ154は、キャパシタCsである。第1の場合では、導電接続部が、半導体層16において下部電極領域34aに隣接している追加のパッドから、トランジスタM2のゲートに繋がっている。

#### 【0073】

あるいは、第2の場合のレイアウトを、トランジスタ152がトランジスタM2に相当し、キャパシタ154がキャパシタCsに相当するように選択する。第2の場合は、被覆電極56aがトランジスタM1の1つの端子領域およびトランジスタM2のゲートと導電接続されている。

#### 【0074】

メモリセル200の回路は、書き込み用のサブ回路と、読み出し用のサブ回路とを含んでいる。キャパシタCsの電荷は、読み出しプロセス中に変更されない。その結果、読み出し操作の後に、この電荷を更新する必要もない。

#### 【0075】

書き込み用のサブ回路は、書き込みトランジスタM1とキャパシタCsとを含んでいる。トランジスタM1のゲート端子は、書き込みワード線WWLと接続されている。トランジスタM1のソース端子は、書き込みビット線BL1と接続されている。上記第1の場合に基づいた特に良好な電気特性を有する回路構成では、トランジスタM1のドレイン端子が、キャパシタ154の下部電極34aによって形成されるメモリ節点Xと繋がっている。キャパシタCsまたは154の被覆電極56aは、接地電位VSSになっている。第2の場合に基づく代替形態では、トランジスタM1のドレイン端子が、キャパシタ154の被覆電極56aによって形成されるメモリ節点Xと繋がっている。キャパシタCsの下部電極34aは、接地電位VSSになっている。

#### 【0076】

読み出し用のサブ回路は、トランジスタM2・M3を含んでいる。トランジスタM3のゲート端子は、読み出しワード線RWLと接続されている。トランジスタM3のドレイン端子は、読み出しビット線BL2と接続されている。この読み出しビット線BL2を、読み出し操作の開始前に、例えば操作電位VDDになるように充電する。トランジスタM3

10

20

30

40

50

のソース端子は、トランジスタM 2 の1つのドレイン端子と接続されている。トランジスタM 2 のゲート端子は、メモリ節点Xと接続されている。トランジスタM 2 のソース端子は、接地電位V S S になっている。

#### 【0077】

トランジスタM 2 は、増幅器の機能を果たす。従って、メモリ節点Xで電荷損失が生じる場合でさえ、信頼性のある読み出しが依然として可能である。メモリ節点Xに正の電荷があるならば、トランジスタM 2 は、スイッチオン状態であり、事前充電した読み出しビット線B L 2 を、読み出し操作時に放電する。

#### 【0078】

トランジスタM 2 のゲート - ソース容量がキャパシタC s と並列に接続されているので 10

、有効メモリ容量C e f f は上昇する：

$$C_{eff} = C_s + C_{GS} \quad (M2)$$

ただし、C s は、キャパシタC s の容量であり、C GS は、トランジスタM 2 のゲート - ソース容量である。この製造方法によると、ゲート酸化物およびキャパシタ誘電体を同じ誘電性層に生成し、この層がどこでも同じ厚みであるならば、メモリキャパシタC s とトランジスタM 2 との1面毎の容量は、例えば同じ大きさである。

#### 【0079】

メモリセル200の所用面は、有効なメモリ容量C e f f に対する条件によって決まる。低い漏れ電流、および、結果的に読み出し電流を高くすることになる高いトランジスタ利得では、メモリキャパシタC s の大きさを小さく出来る。キャパシタC s のために必要な面、および、その電気特性は、複数のメモリセル200を有するメモリユニットを経済的に製造するための主要条件である。複数のメモリセル200を有するメモリユニットも、処理器メモリ階層のS R A M を置換するために適している。

#### 【図面の簡単な説明】

#### 【0080】

【図1】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図2】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図3】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図4】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図5】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図6】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図7】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図8】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図9】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図10】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図11】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図12】集積トランジスタ - キャパシタ構造の製造の製造段階を示す図である。

【図13】トランジスタ - キャパシタ構造の平面図である。

【図14】トランジスタを有するD R A M メモリセルの断面図である。

【図15】D R A M メモリセルの平面図である。

【図16】3つのトランジスタを有するD R A M メモリセルの回路図である。

#### 【符号の説明】

#### 【0081】

|       |          |

|-------|----------|

| I、II  | 断面       |

| 1 0   | S O I 基板 |

| 1 2   | 担体基板     |

| 1 4   | 絶縁層      |

| 1 6   | 半導体層     |

| 1 6 a | トランジスタ部  |

| 1 6 b | キャパシタ部   |

10

20

30

40

50

|               |                  |    |

|---------------|------------------|----|

| 1 8           | 二酸化シリコン層         |    |

| 2 0           | 窒化シリコン層          |    |

| 2 2           | フォトレジスト層         |    |

| 2 4           | 積層               |    |

| 2 6 , 2 8     | 酸化物角取り部          |    |

| 3 0 , 3 2     | フォトレジスト層         |    |

| 3 3           | 埋め込み             |    |

| 3 4           | 下部電極領域           |    |

| 4 0           | 二酸化シリコン層         |    |

| 4 1           | ポリシリコン層          | 10 |

| 4 2           | ゲート酸化物           |    |

| 4 6           | 誘電体              |    |

| 5 0 a 、 5 0 b | フォトレジスト層領域       |    |

| 5 4           | ゲート電極            |    |

| 5 6           | 被覆電極             |    |

| 5 7           | 埋め込み             |    |

| 5 8 , 5 9     | LDD領域            |    |

| 6 0 ~ 6 6     | スペーサ             |    |

| 7 0 ~ 7 6     | エピタキシャル領域        |    |

| 7 8           | 埋め込み             | 20 |

| 8 0 , 8 2     | ソース / ドレイン領域     |    |

| 8 4           | チャネル領域           |    |

| 9 0 ~ 9 6     | ケイ化物領域           |    |

| 1 0 0         | パッシベーション層        |    |

| 1 0 2 ~ 1 3 6 | 接続部              |    |

| 1 4 0         | トランジスタ - キャパシタ構造 |    |

| 1 4 2         | 電界効果トランジスタ       |    |

| 1 4 4         | キャパシタ            |    |

| W 1 , W 2     | トランジスタ幅          |    |

| L 1 , L 2     | 長さ               | 30 |

| B 1 , B 2     | 幅                |    |

| A             | 面                |    |

| F             | 最小形状             |    |

| 1 5 0         | メモリセル            |    |

| 1 5 2         | 電界効果トランジスタ       |    |

| 1 5 4         | キャパシタ            |    |

| 2 0 0         | メモリセル            |    |

| M 1 ~ M 3     | トランジスタ           |    |

| C s           | キャパシタ            |    |

| B L 1         | 書き込みビット線         | 40 |

| B L 2         | 読み出しビット線         |    |

| R W L         | 読み出しワード線         |    |

| W W L         | 書き込みワード線         |    |

| X             | メモリ節点            |    |

| V D D         | 操作電位             |    |

| V S S         | 接地電位             |    |

【図 1】

FIG 1

【図 2】

【図 3】

【図 4】

FIG 4

【図 5】

【図 6】

【図 7】

FIG 7【図 10】

FIG 10【図 8】

FIG 8

【図 11】

【図 9】

【図 12】

【図13】

FIG 13

【図14】

FIG 14

【図15】

FIG 15

【図16】

FIG 16

## 【手続補正書】

【提出日】平成16年11月18日(2004.11.18)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

## 【請求項1】

電気的に絶縁性の絶縁領域と、少なくとも1つの連続した領域とを有する集積回路構造(140)であって、

上記一連の領域は、キャパシタ(144)を形成しているとともに、上記絶縁領域に近接した電極領域(34)と、

誘電体領域(46)と、

絶縁領域から離れた電極領域(56)とをこの順で有しており、

上記絶縁領域が、平面に配置された絶縁層(14)の一部であり、

上記集積回路構造(140)の上記キャパシタ(144)と、少なくとも1つの能動素子(142)とが、上記絶縁層(14)に対して同じ側に配置されており、

上記絶縁領域に近接した電極領域(34)と、上記素子(142)の活性領域(84)とが、絶縁層(14)の配置されている平面と平行な平面に配置されており、

キャパシタ(154)と能動素子(152)とが、記憶セル(150)を形成しており

少なくとも一つの処理器を含むことを特徴とする、集積回路構造。

## 【請求項2】

少なくとも1つの電界効果トランジスタ(142)にて特徴付けされており、

この電界効果トランジスタ(142)のチャネル領域(84)が、活性領域であり、上記チャネル領域(84)が、ドープまたは非ドープされていることが好ましく、

および／または、電界効果トランジスタ(142)の制御電極(54)が、絶縁領域から離れた電極領域(56)と同じ材料および／または同じドーパント濃度の材料を含み、

および／または、電界効果トランジスタ(142)の制御電極絶縁領域(42)が、誘電体領域(46)と同じ材料および／または同じ厚みを有する材料を含み、

および／または、電界効果トランジスタ(142)の制御電極絶縁領域(42)が、誘電体領域(46)とは異なる材料および／または異なる厚みを有する材料を含む請求項1に記載の回路構造(140)。

#### 【請求項3】

上記電界効果トランジスタ(122)が、プレーナ型の電界効果トランジスタであり、

および／または、上記トランジスタが、補助端子領域(58, 59)を含み、

これらの補助端子領域は、端子領域(80, 82)と同じ導電型ではあるが少なくとも1桁だけ小さいドーパント濃度にドーピングされており、

および／または、上記トランジスタが、補助ドーピング領域を備え、これらの補助ドーピング領域は、端子領域(80, 82)および／または補助端子領域(58, 59)に近接して配置されており、端子領域(80, 82)および／または補助端子領域(58, 59)とは異なる導電性型のドーピングを有し、

および／または、上記制御電極(54)が、金属半導体組成物、特に、ケイ化物領域(92)を含む領域に隣接している、請求項2に記載の回路構造(140)。

#### 【請求項4】

トランジスタ(142)の1つの端子領域(80, 82)またはトランジスタ(142)の両方の端子領域(80, 82)が、絶縁層(14)に隣接し、

および／または、少なくとも1つの端子領域(80, 82)が、金属半導体組成物を含む領域、好ましくはケイ化物領域(90, 96)と隣接し、

および／または、少なくとも1つの端子領域(80, 82)の絶縁領域から離れた境界面が、活性領域(84)よりも、絶縁層(14)から離れており、または、

および／または、絶縁領域から離れた少なくとも一つの端子領域(80, 82)の境界面が、活性領域(84)よりも、絶縁層(14)から離れており、

または、絶縁領域から離れた少なくとも一つの端子領域(80, 82)の境界面が、活性領域(84)が絶縁領域から離れた活性領域(84)の境界面よりも絶縁層(14)に近接して配置されている、請求項2または3に記載の回路構造(140)。

少なくとも1つの端子領域(80, 82)の絶縁領域から離れた境界面が、活性領域(84)の絶縁領域から離れた境界面よりも、絶縁層(14)の近くに配置されている、請求項2または3に記載の回路構造(140)。

#### 【請求項5】

スペーサ(60, 62)が、制御電極(54)の両側に配置されており、これらのスペーサは、制御電極(54)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンを含み、または、これらのスペーサは、制御電極(54)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンからなり、

および／または、スペーサ(64, 66)が、絶縁領域から離れた電極領域(56)の少なくとも一方側に配置されており、このスペーサは、上記絶縁領域から離れた上記電極領域(56)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンを含み、または、このスペーサは、上記絶縁領域から離れた上記電極領域(56)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンからなり、

および／または、制御電極(54)に配置されたスペーサ(62a)と、絶縁領域から離れた電極領域(56)に配置されたスペーサ(64a)とが相互に接触する、請求項2から4のいずれか1項に記載の回路構造(140)。

#### 【請求項6】

上記電界効果トランジスタ(142)の端子領域(82)と、キャパシタ(144)の

絶縁領域に近接した電極領域（34）とが、相互に隣接し、境界で導電性接続されており、

および／または、絶縁領域に近接した電極領域（34）に隣接する上記トランジスタ（152）の端子領域（59a）が、金属半導体組成物を含む領域、特に、ケイ化物領域に隣接せず、

および／または、他の端子領域（80a）が、金属半導体組成物を含む領域（70a）に隣接する、請求項2から5のいずれか1項に記載の回路構造（140）。

#### 【請求項7】

端子領域（82）に隣接する、絶縁領域に近接した電極領域（34）の側面が、上記側面を横断するように配置されている、絶縁領域に近接した電極領域（34）の側面よりも長く、好ましくは少なくとも2倍または少なくとも5倍は長く、

トランジスタ（142）が、好ましくはトランジスタ幅（W1）を有し、このトランジスタ幅は、最小形状（F）の倍数であり、好ましくは3倍または5倍を上回り、

または、端子領域（82）に隣接する、絶縁領域に近接した電極領域（34）の側面を横断するように配置されている、絶縁領域に近接した電極領域（34）の側面が、端子領域（82）に隣接している側面よりも長く、好ましくは少なくとも2倍または少なくとも5倍は長く、

トランジスタ（152）が、好ましくはトランジスタ幅（W2）を有しており、このトランジスタ幅は、最小形状（F）の3倍未満であり、好ましくは最小形状（F）の2倍未満である、請求項6に記載の回路構造（140）。

#### 【請求項8】

上記絶縁領域に近接した上記電極領域（34）が、単結晶領域、好ましくはドープされた半導体領域であり、

および／または、上記絶縁領域に近接した上記電極領域（34）および／または活性領域（84）が、100nm未満、または、50nm未満の厚みを有しており、

および／または、上記活性領域（84）が、単結晶領域、好ましくはドープまたは非ドープされた半導体領域であり、

および／または、上記絶縁層（14）が、一方の側面で、担体基板（12）、好ましくは担体基板に隣接し、この担体基板は、半導体材料を含むんでいるか、または、半導体材料、特にシリコンまたは単結晶シリコンからなり、

および／または、上記絶縁層（14）が、他方の側面で、上記絶縁領域に近接した上記電極領域（34）に隣接し、

および／または、境界面が、好ましくは2つの相互に平行な面に完全に含まれており、

および／または、絶縁層（14）が、電気的に絶縁性のある材料、好ましくは酸化物、特に二酸化シリコンを含み、

または、電気的に絶縁性のある材料、好ましくは酸化物、特に二酸化シリコンからなり、

および／または、能動素子（142）が、トランジスタ、好ましくは電界効果トランジスタ、特にブレーナ型の電界効果トランジスタである、請求項1～7のいずれか1項に記載の回路構造（140）。

#### 【請求項9】

上記誘電性領域（46）が、二酸化シリコンを含み、または、二酸化シリコンからなり、

および／または、上記誘電性領域（46）が、4以上または10以上または50以上の誘電定数を有する材料からなり、

および／または、上記絶縁領域から離れた上記電極領域（56）が、シリコン、好ましくは多結晶シリコンを含み、または、シリコン、好ましくは多結晶シリコンからなり、

および／または、上記絶縁領域から離れた上記電極領域（56）が、金属を含み、または、金属からなり、

および／または、上記絶縁領域から離れた上記電極領域（56）が、低インピーダンス材料、好ましくは窒化チタン、窒化タンタル、ルビジウムまたは高ドープしたシリコンゲ

ルマニウムを含み、

および／または、上記絶縁領域から離れた上記電極領域（56）が、金属半導体組成物を含む領域、特にケイ化物領域（96）に隣接する、上記請求項1～8のいずれか1項に記載の回路構造（140）。

【請求項10】

上記処理器が、マイクロ処理器であり、

および／または、上記キャパシタ（154）と能動素子（152）とが、メモリセル（150）を、ダイナミックRAMメモリユニットに形成し、

および／または、メモリセルが、キャパシタ（152）およびただ1つのトランジスタ（152）、または、キャパシタ（Cs）および複数のトランジスタ（M1～M3）、好ましくは3つのトランジスタ（M1～M3）のどちらかを含む、請求項1～9のいずれかに記載の回路構造（140）。

【請求項11】

上記請求項1から10のいずれか1項に記載の回路構造（140）にキャパシタ（144）を有する集積回路構造（140）の製造方法において、

規定の順序に制限されることなく、

電気的に絶縁性の材料から成る絶縁層（14）と、半導体層（16）とを含む基板（10）を用意し、

キャパシタ用の少なくとも1つの電極領域（34）を形成するため、および、トランジスタ（142）用の少なくとも1つの活性領域（84）を形成するために、半導体層（16）をパターン化し、

半導体層（16）をパターン化した後、少なくとも1つの誘電性層（42、46）を生成し、

誘電性層（42、46）を生成した後、電極層（41）を生成し、

上記電極層（41）の絶縁領域から離してキャパシタ（144）の電極（56）を形成する方法工程を実施する方法。

【請求項12】

パターン化の前に半導体層（16）に少なくとも1つの補助層（18、20）、好ましくは窒化シリコン層（20）および／または酸化物層（18）を形成する工程であって、補助層（20）が、半導体層（16）のパターン化中に、好ましくはハードマスクの機能を果たすようになっており、

および／または、好ましくは誘電性層（42、46）の生成前に、トランジスタ（142）のチャネル領域（84）をドーピングし、

角取り酸化物（26、28）を形成するために、好ましくは電極層（41）を形成する前に、熱酸化し、

および／または、好ましくは誘電性層（42、44、46）を生成する前に、上記絶縁領域に近接した電極（34）をドーピングし、

および／または、トランジスタ（122）の活性領域（84）に、誘電性層と同時に誘電性層（42、46）を生成し、

および／または、上記絶縁領域から離れた電極領域（56）の形成と同時にトランジスタ（142）の制御電極（54）を形成することを特徴とする、請求項11に記載の方法。

【請求項13】

好ましくはトランジスタ（142）の制御電極（54）をパターン化した後に、トランジスタ（142）の端子領域（80、82）よりも低いドーパント濃度を有する補助端子領域（58、59）を形成し、

および／または、好ましくは制御電極（54）をパターン化する前に、補助ドーピング領域を形成し、

トランジスタ（142）の制御電極（54）をパターン化した後に、更なる補助層（60から66）、好ましくは窒化シリコン層または二酸化シリコン層、特にTEOS層を形

成し、

および／または、更なる補助層（60～66）を異方性エッチングすることを特徴とする、請求項11または12に記載の方法。

【請求項14】

上記絶縁領域から離れた電極領域（56）を形成した後、および／または、トランジスタ（142）の制御電極（54）をパターン化した後、半導体材料（16）からなる露出領域に、選択的エピタキシーを行い、

および／または、上記絶縁領域から離れた電極領域（56）を形成した後、および／または制御電極（54）をパターン化した後、および、好ましくはエピタキシーの後、トランジスタ（122）の端子領域（70、72）をドーピングすることを特徴とする、請求項11から13のいずれか1項に記載の方法。

【請求項15】

電極層（54）、および／または、露出半導体領域（16）に、金属半導体組成物、特に、ケイ化物を選択的に形成することを特徴とする、請求項11から14のいずれか1項に記載の方法。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/DE 03/03354

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H01L27/12 H01L21/84

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the International search (name of data base and, where practical, search terms used)

EPO-Internal, PAJ, WPI Data, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                           | Relevant to claim No. |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | PATENT ABSTRACTS OF JAPAN<br>vol. 2000, no. 14,<br>5 March 2001 (2001-03-05)<br>-& JP 2000 312006 A (SEIKO EPSON CORP),<br>7 November 2000 (2000-11-07)<br>abstract; figures | 1-11,13,<br>15        |

| Y        | & US 6 569 717 B1 (MURADE MASAO)<br>27 May 2003 (2003-05-27)<br>abstract; figures 8d,2a-2h                                                                                   | 12,14                 |

| Y        | US 4 753 896 A (MATLOUBIAN MISHEL)<br>28 June 1988 (1988-06-28)<br>abstract; figures 1a-1d                                                                                   | 12                    |

| Y        | US 5 998 807 A (FRANOSCH MARTIN ET AL)<br>7 December 1999 (1999-12-07)<br>abstract; figures                                                                                  | 14                    |

|          |                                                                                                                                                                              | -/-                   |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents:

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

- \*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed Invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed Invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

29 June 2004

Date of mailing of the International search report

06/07/2004

## Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

## Authorized officer

Wirner, C

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/DE 03/03354

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                           |                       |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|

| Category <sup>a</sup>                                | Citation of document, with indication, where appropriate, of the relevant passages                        | Relevant to claim No. |

| X                                                    | US 6 414 345 B1 (SUZAWA HIDEOMI)<br>2 July 2002 (2002-07-02)<br>abstract; figures 4E,4F<br>-----          | 1,2,<br>4-11,13       |

| X                                                    | US 6 140 162 A (YEO JU-CHEON)<br>31 October 2000 (2000-10-31)<br>abstract; figures 2-4<br>-----           | 1,2,<br>4-11,13       |

| X                                                    | US 6 417 057 B1 (KONUMA TOSHIMITSU ET AL)<br>9 July 2002 (2002-07-09)<br>abstract; figures 1a-1g<br>----- | 1,2,<br>4-11,13       |

| X                                                    | US 6 133 075 A (OHNUMA HIDETO ET AL)<br>17 October 2000 (2000-10-17)<br>abstract; figures<br>-----        | 1,2,<br>4-11,13       |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/DE 03/03354

| Patent document cited in search report |    | Publication date |                            | Patent family member(s)                                                                         | Publication date                                                                                   |

|----------------------------------------|----|------------------|----------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| JP 2000312006                          | A  | 07-11-2000       | JP US JP                   | 3399432 B2 6569717 B1 2000312005 A                                                              | 21-04-2003 27-05-2003 07-11-2000                                                                   |

| US 6569717                             | B1 | 27-05-2003       | JP JP JP                   | 3399432 B2 2000312006 A 2000312005 A                                                            | 21-04-2003 07-11-2000 07-11-2000                                                                   |

| US 4753896                             | A  | 28-06-1988       | JP JP                      | 2638004 B2 63288058 A                                                                           | 06-08-1997 25-11-1988                                                                              |

| US 5998807                             | A  | 07-12-1999       | DE EP JP                   | 59707274 D1 0838858 A2 10107294 A                                                               | 20-06-2002 29-04-1998 24-04-1998                                                                   |

| US 6414345                             | B1 | 15-08-2000       | JP JP US US US US US US US | 3312083 B2 7335903 A 5856689 A 5712495 A 6104051 A 6121652 A 2003201435 A1 6566684 B1 5998841 A | 05-08-2002 22-12-1995 05-01-1999 27-01-1998 15-08-2000 19-09-2000 30-10-2003 20-05-2003 07-12-1999 |

| US 6140162                             | A  | 31-10-2000       |                            | NONE                                                                                            |                                                                                                    |

| US 6417057                             | B1 | 09-07-2002       | JP US US US                | 7335904 A 6160269 A 5739549 A 2002079488 A1                                                     | 22-12-1995 12-12-2000 14-04-1998 27-06-2002                                                        |

| US 6133075                             | A  | 17-10-2000       | JP JP US US                | 10301146 A 10301147 A 2003138996 A1 6524896 B1                                                  | 13-11-1998 13-11-1998 24-07-2003 25-02-2003                                                        |

## INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE 03/03354

A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES

IPK 7 H01L27/12 H01L21/84

Nach der Internationalen Patentklassifikation (IPK) oder nach der nationalen Klassifikation und der IPK

## B. RECHERCHIERTE GEBIETE

Recherchierte Mindestprässtoff (Klassifikationssystem und Klassifikationssymbole)

IPK 7 H01L

Recherchierte aber nicht zum Mindestprässtoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der Internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

EPO-Internal, PAJ, WPI Data, INSPEC

## C. ALS WESENTLICH ANGESEHENE UNTERLAGEN

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich Unter Angabe der in Betracht kommenden Teile                                                                                      | Betr. Anspruch Nr. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| X          | PATENT ABSTRACTS OF JAPAN<br>Bd. 2000, Nr. 14,<br>5. März 2001 (2001-03-05)<br>-& JP 2000 312006 A (SEIKO EPSON CORP),<br>7. November 2000 (2000-11-07)<br>Zusammenfassung; Abbildungen | 1-11,13,<br>15     |

| Y          | & US 6 569 717 B1 (MURADE MASAO)<br>27. Mai 2003 (2003-05-27)<br>Zusammenfassung; Abbildungen 8d,2a-2h                                                                                  | 12,14              |

| Y          | US 4 753 896 A (MATLOUBIAN MISHEL)<br>28. Juni 1988 (1988-06-28)<br>Zusammenfassung; Abbildungen 1a-1d                                                                                  | 12                 |

| Y          | US 5 998 807 A (FRANOSCH MARTIN ET AL)<br>7. Dezember 1999 (1999-12-07)<br>Zusammenfassung; Abbildungen                                                                                 | 14                 |

|            |                                                                                                                                                                                         | -/-                |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen

Siehe Anhang Patentfamilie

\* Besondere Kategorien von angegebenen Veröffentlichungen :

\*A\* Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

\*E\* älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist

\*L\* Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

\*O\* Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

\*P\* Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist

\*T\* Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist

\*X\* Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erfinderischer Tätigkeit beruhend betrachtet werden

\*Y\* Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erfinderischer Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren anderen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann naheliegend ist

\*&\* Veröffentlichung, die Mitglied derselben Patentfamilie ist

Datum des Abschlusses der Internationalen Recherche

Absendeadatum des Internationalen Recherchenberichts

29. Juni 2004

06/07/2004

Name und Postanschrift der Internationalen Recherchenbehörde

Europäisches Patentamt, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Bevollmächtigter Bediensteter

Wirner, C

## INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE 03/03354

## C.(Fortsetzung) ALS WESENTLICH ANGESEHENE UNTERLAGEN

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                    | Betr. Anspruch Nr. |

|------------|-----------------------------------------------------------------------------------------------------------------------|--------------------|

| X          | US 6 414 345 B1 (SUZAWA HIDEOMI)<br>2. Juli 2002 (2002-07-02)<br>Zusammenfassung; Abbildungen 4E, 4F<br>-----         | 1,2,<br>4-11,13    |

| X          | US 6 140 162 A (YEO JU-CHEON)<br>31. Oktober 2000 (2000-10-31)<br>Zusammenfassung; Abbildungen 2-4<br>-----           | 1,2,<br>4-11,13    |

| X          | US 6 417 057 B1 (KONUMA TOSHIMITSU ET AL)<br>9. Juli 2002 (2002-07-09)<br>Zusammenfassung; Abbildungen 1a-1g<br>----- | 1,2,<br>4-11,13    |

| X          | US 6 133 075 A (OHNUMA HIDETO ET AL)<br>17. Oktober 2000 (2000-10-17)<br>Zusammenfassung; Abbildungen<br>-----        | 1,2,<br>4-11,13    |

## INTERNATIONALER RECHERCHENBERICHT

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/DE 03/03354

| Im Recherchenbericht angeführtes Patentdokument |    | Datum der Veröffentlichung |                                              | Mitglied(er) der Patentfamilie                                                                                          |                                                                                                                            | Datum der Veröffentlichung |

|-------------------------------------------------|----|----------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------|

| JP 2000312006                                   | A  | 07-11-2000                 | JP<br>US<br>JP                               | 3399432 B2<br>6569717 B1<br>2000312005 A                                                                                | 21-04-2003<br>27-05-2003<br>07-11-2000                                                                                     |                            |

| US 6569717                                      | B1 | 27-05-2003                 | JP<br>JP<br>JP                               | 3399432 B2<br>2000312006 A<br>2000312005 A                                                                              | 21-04-2003<br>07-11-2000<br>07-11-2000                                                                                     |                            |

| US 4753896                                      | A  | 28-06-1988                 | JP<br>JP                                     | 2638004 B2<br>63288058 A                                                                                                | 06-08-1997<br>25-11-1988                                                                                                   |                            |

| US 5998807                                      | A  | 07-12-1999                 | DE<br>EP<br>JP                               | 59707274 D1<br>0838858 A2<br>10107294 A                                                                                 | 20-06-2002<br>29-04-1998<br>24-04-1998                                                                                     |                            |

| US 6414345                                      | B1 | 15-08-2000                 | JP<br>JP<br>US<br>US<br>US<br>US<br>US<br>US | 3312083 B2<br>7335903 A<br>5856689 A<br>5712495 A<br>6104051 A<br>6121652 A<br>2003201435 A1<br>6566684 B1<br>5998841 A | 05-08-2002<br>22-12-1995<br>05-01-1999<br>27-01-1998<br>15-08-2000<br>19-09-2000<br>30-10-2003<br>20-05-2003<br>07-12-1999 |                            |

| US 6140162                                      | A  | 31-10-2000                 |                                              | KEINE                                                                                                                   |                                                                                                                            |                            |

| US 6417057                                      | B1 | 09-07-2002                 | JP<br>US<br>US<br>US                         | 7335904 A<br>6160269 A<br>5739549 A<br>2002079488 A1                                                                    | 22-12-1995<br>12-12-2000<br>14-04-1998<br>27-06-2002                                                                       |                            |

| US 6133075                                      | A  | 17-10-2000                 | JP<br>JP<br>US<br>US                         | 10301146 A<br>10301147 A<br>2003138996 A1<br>6524896 B1                                                                 | 13-11-1998<br>13-11-1998<br>24-07-2003<br>25-02-2003                                                                       |                            |

## フロントページの続き

|                          |              |            |

|--------------------------|--------------|------------|

| (51)Int.Cl.              | F I          | テーマコード(参考) |

| H 01 L 21/8234 (2006.01) | H 01 L 27/10 | 6 1 5      |

| H 01 L 21/8242 (2006.01) | H 01 L 27/10 | 6 7 1 C    |

| H 01 L 27/108 (2006.01)  |              |            |

(72)発明者 パシャ , クリストイアン

ドイツ連邦共和国 8 1 7 3 9 ミュンヘン アーゼンヴェーク 1 2

(72)発明者 レースナー , ヴォルフガング

ドイツ連邦共和国 8 5 5 2 1 オットブルン ステーテンシュトラーセ 2 3

(72)発明者 シュルツ , トーマス

アメリカ合衆国 テキサス州 7 8 7 4 1 オースティン # 1 3 1 0 サンリッジ ドライブ

2 9 0 0

F ターム(参考) 5F038 AC03 AC05 AC09 AC15 AC17 AC18 DF05 EZ02 EZ06 EZ14

EZ20

5F048 AB01 AC10 BA15 BA16 BB06 BB08 BB12 BC03 BC06 BF06

BF16 DA25 DA27 DA30

5F083 AD02 AD10 AD14 FR02 JA02 JA14 JA31 JA32 JA34 JA35

JA39 JA40

5F110 AA04 AA16 BB04 BB06 CC02 DD05 DD13 EE05 EE09 EE14

EE32 EE41 EE42 FF02 FF23 GG02 GG03 GG04 GG12 GG25

HJ13 HK05 HK34 HK40 HL01 HL02 HL04 HL12 HM02 HM15

HM17 NN02 NN22 NN23 NN62 NN65 NN66 NN72 QQ14