(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6031472号

(P6031472)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 617T |

| HO1L 21/8238 | (2006.01) | HO1L 29/78 | 617U |

| HO1L 27/092  | (2006.01) | HO1L 29/78 | 617L |

| HO1L 21/8234 | (2006.01) | HO1L 27/08 | 321G |

| HO1L 27/088  | (2006.01) | HO1L 27/08 | 102E |

請求項の数 16 (全 51 頁) 最終頁に続く

(21) 出願番号

特願2014-139489 (P2014-139489)

(22) 出願日

平成26年7月7日(2014.7.7)

(65) 公開番号

特開2015-35597 (P2015-35597A)

(43) 公開日

平成27年2月19日(2015.2.19)

審査請求日

平成27年7月29日(2015.7.29)

(31) 優先権主張番号

特願2013-142308 (P2013-142308)

(32) 優先日

平成25年7月8日(2013.7.8)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山元 良高

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 田中 哲弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 竹内 敏彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山根 靖正

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置および半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のゲート電極と、

前記第1のゲート電極上方の電子捕獲層と、

前記電子捕獲層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第2の酸化物半導体層は、前記第1の酸化物半導体層と前記第3の酸化物半導体層とに取り囲まれた領域を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よ

10

20

りも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きいことを特徴とする半導体装置。

【請求項2】

第1のゲート電極と、

前記第1のゲート電極上方の電子捕獲層と、

前記電子捕獲層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第3の酸化物半導体層は、前記第2の酸化物半導体層の上面に接する領域と、前記第2の酸化物半導体層の側面に接する領域と、前記第1の酸化物半導体層の側面に接する領域と、を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きいことを特徴とする半導体装置。

【請求項3】

第1のゲート電極と、

前記第1のゲート電極上方の第1の絶縁層と、

前記第1の絶縁層上方の第2の絶縁層と、

前記第2の絶縁層上方の第3の絶縁層と、

前記第3の絶縁層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第2の酸化物半導体層は、前記第1の酸化物半導体層と前記第3の酸化物半導体層とに取り囲まれた領域を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きく、

10

20

30

40

50

前記第1の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有し、

前記第2の絶縁層は、酸化ハフニウムを有し、

前記第3の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有すること

を特徴とする半導体装置。

## 【請求項4】

第1のゲート電極と、

前記第1のゲート電極上方の第1の絶縁層と、

前記第1の絶縁層上方の第2の絶縁層と、

前記第2の絶縁層上方の第3の絶縁層と、

前記第3の絶縁層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第3の酸化物半導体層は、前記第2の酸化物半導体層の上面に接する領域と、前記第2の酸化物半導体層の側面に接する領域と、前記第1の酸化物半導体層の側面に接する領域と、を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きく、

前記第1の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有し、

前記第2の絶縁層は、酸化ハフニウムを有し、

前記第3の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有すること

を特徴とする半導体装置。

## 【請求項5】

請求項1乃至請求項4のいずれか一において、

前記第1の酸化物半導体層の伝導帯下端のエネルギーは、前記第2の酸化物半導体層の伝導帯下端のエネルギーよりも、真空準位に近く、

前記第2の酸化物半導体の伝導帯下端のエネルギーと前記第1の酸化物半導体層の伝導帯下端のエネルギーとの差は、0.05eV以上2eV以下であり、

前記第3の酸化物半導体層の伝導帯下端のエネルギーは、前記第2の酸化物半導体層の伝導帯下端のエネルギーよりも、真空準位に近く、

前記第2の酸化物半導体の伝導帯下端のエネルギーと前記第3の酸化物半導体層の伝導帯下端のエネルギーとの差は、0.05eV以上2eV以下であることを特徴とする半導体装置。

## 【請求項6】

請求項1乃至請求項5のいずれか一において、

前記第2の酸化物半導体層の端部は丸みを帯びた形状を有することを特徴とする半導体装置。

## 【請求項7】

第1のゲート電極と、

10

20

30

40

50

前記第1のゲート電極上方の電子捕獲層と、

前記電子捕獲層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第2の酸化物半導体層は、前記第1の酸化物半導体層と前記第3の酸化物半導体層とに取り囲まれた領域を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きい半導体装置の作製方法であって、

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記電子捕獲層に電子を捕獲させることを特徴とする半導体装置の作製方法。

20

## 【請求項8】

第1のゲート電極と、

前記第1のゲート電極上方の電子捕獲層と、

前記電子捕獲層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第2の酸化物半導体層は、前記第1の酸化物半導体層と前記第3の酸化物半導体層とに取り囲まれた領域を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きい半導体装置の作製方法であって、

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記電子捕獲層に電子を捕獲させ、前記トランジスタのしきい値を増加させることを特徴とする半導体装置の作製方法。

40

## 【請求項9】

第1のゲート電極と、

50

前記第1のゲート電極上方の電子捕獲層と、

前記電子捕獲層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第3の酸化物半導体層は、前記第2の酸化物半導体層の上面に接する領域と、前記第2の酸化物半導体層の側面に接する領域と、

前記第1の酸化物半導体層の側面に接する領域と、を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きい半導体装置の作製方法であって、

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記電子捕獲層に電子を捕獲させることを特徴とする半導体装置の作製方法。

。

#### 【請求項10】

第1のゲート電極と、

前記第1のゲート電極上方の電子捕獲層と、

前記電子捕獲層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第3の酸化物半導体層は、前記第2の酸化物半導体層の上面に接する領域と、前記第2の酸化物半導体層の側面に接する領域と、

前記第1の酸化物半導体層の側面に接する領域と、を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きい半導体装置の作製方法であって、

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記電子捕獲層に電子を捕獲させ、前記トランジスタのしきい値を増加させることを特徴とする半導体装置の作製方法。

10

20

30

40

50

## 【請求項 1 1】

第 1 のゲート電極と、

前記第 1 のゲート電極上方の第 1 の絶縁層と、

前記第 1 の絶縁層上方の第 2 の絶縁層と、

前記第 2 の絶縁層上方の第 3 の絶縁層と、

前記第 3 の絶縁層上方の第 1 の酸化物半導体層と、

前記第 1 の酸化物半導体層上方の第 2 の酸化物半導体層と、

前記第 2 の酸化物半導体層と電気的に接続されたソース電極と、

前記第 2 の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第 2 の酸化物半導体層上方の第 3 の酸化物半導体層と、

前記第 3 の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第 2 のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第 2 の酸化物半導体層は、前記第 1 の酸化物半導体層と前記第 3 の酸化物半導体層とに取り囲まれた領域を有し、

トランジスタのチャネル長方向において、前記第 2 の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第 1 の酸化物半導体層は、前記第 2 の酸化物半導体層を構成する金属元素を一種以上有し、

前記第 3 の酸化物半導体層は、前記第 2 の酸化物半導体層を構成する金属元素を一種以上有し、

前記第 2 の酸化物半導体層の電子親和力は、前記第 1 の酸化物半導体層の電子親和力よりも大きく、

前記第 2 の酸化物半導体層の電子親和力は、前記第 3 の酸化物半導体層の電子親和力よりも大きく、

前記第 1 の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有し、

前記第 2 の絶縁層は、酸化ハフニウムを有し、

前記第 3 の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有する半導体装置の作製方法であって、

前記第 1 のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記第 2 の絶縁層に電子を捕獲させることを特徴とする半導体装置の作製方法。

## 【請求項 1 2】

第 1 のゲート電極と、

前記第 1 のゲート電極上方の第 1 の絶縁層と、

前記第 1 の絶縁層上方の第 2 の絶縁層と、

前記第 2 の絶縁層上方の第 3 の絶縁層と、

前記第 3 の絶縁層上方の第 1 の酸化物半導体層と、

前記第 1 の酸化物半導体層上方の第 2 の酸化物半導体層と、

前記第 2 の酸化物半導体層と電気的に接続されたソース電極と、

前記第 2 の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第 2 の酸化物半導体層上方の第 3 の酸化物半導体層と、

前記第 3 の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第 2 のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第 2 の酸化物半導体層は、前記第 1 の酸化物半導体層と前記第 3 の酸化物半導体層とに取り囲まれた領域を有し、

トランジスタのチャネル長方向において、前記第 2 の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第 1 の酸化物半導体層は、前記第 2 の酸化物半導体層を構成する金属元素を一種以上有し、

前記第 3 の酸化物半導体層は、前記第 2 の酸化物半導体層を構成する金属元素を一種以

10

20

30

40

50

上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きく、

前記第1の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有し、

前記第2の絶縁層は、酸化ハフニウムを有し、

前記第3の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有する半導体装置の作製方法であって、

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記第2の絶縁層に電子を捕獲させ、前記トランジスタのしきい値を増加させることを特徴とする半導体装置の作製方法。 10

#### 【請求項13】

第1のゲート電極と、

前記第1のゲート電極上方の第1の絶縁層と、

前記第1の絶縁層上方の第2の絶縁層と、

前記第2の絶縁層上方の第3の絶縁層と、

前記第3の絶縁層上方の第1の酸化物半導体層と、

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、 20

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第3の酸化物半導体層は、前記第2の酸化物半導体層の上面に接する領域と、前記第2の酸化物半導体層の側面に接する領域と、前記第1の酸化物半導体層の側面に接する領域と、を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、 30

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きく、

前記第1の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有し、

前記第2の絶縁層は、酸化ハフニウムを有し、

前記第3の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有する半導体装置の作製方法であって、 40

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記第2の絶縁層に電子を捕獲させることを特徴とする半導体装置の作製方法。

#### 【請求項14】

第1のゲート電極と、

前記第1のゲート電極上方の第1の絶縁層と、

前記第1の絶縁層上方の第2の絶縁層と、

前記第2の絶縁層上方の第3の絶縁層と、

前記第3の絶縁層上方の第1の酸化物半導体層と、 50

前記第1の酸化物半導体層上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と電気的に接続されたソース電極と、

前記第2の酸化物半導体層と電気的に接続されたドレイン電極と、

前記第2の酸化物半導体層上方の第3の酸化物半導体層と、

前記第3の酸化物半導体層上方のゲート絶縁層と、

前記ゲート絶縁層上方の第2のゲート電極と、を有し、

トランジスタのチャネル幅方向において、前記第3の酸化物半導体層は、前記第2の酸化物半導体層の上面に接する領域と、前記第2の酸化物半導体層の側面に接する領域と、前記第1の酸化物半導体層の側面に接する領域と、を有し、

トランジスタのチャネル長方向において、前記第2の酸化物半導体層の上面は、前記ソース電極及びドレイン電極と接する領域を有し、 10

前記第1の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第3の酸化物半導体層は、前記第2の酸化物半導体層を構成する金属元素を一種以上有し、

前記第2の酸化物半導体層の電子親和力は、前記第1の酸化物半導体層の電子親和力よりも大きく、

前記第2の酸化物半導体層の電子親和力は、前記第3の酸化物半導体層の電子親和力よりも大きく、

前記第1の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有し、 20

前記第2の絶縁層は、酸化ハフニウムを有し、

前記第3の絶縁層は、酸化シリコン、酸窒化シリコン、又は窒化シリコンを有する半導体装置の作製方法であって、

前記第1のゲート電極の電位を前記ソース電極の電位及び前記ドレイン電極の電位よりも高くして、前記第2の絶縁層に電子を捕獲させ、前記トランジスタのしきい値を増加させることを特徴とする半導体装置の作製方法。

**【請求項15】**

請求項7乃至請求項14のいずれか一において、

前記第1の酸化物半導体層の伝導帯下端のエネルギーは、前記第2の酸化物半導体層の伝導帯下端のエネルギーよりも、真空準位に近く、 30

前記第2の酸化物半導体の伝導帯下端のエネルギーと前記第1の酸化物半導体層の伝導帯下端のエネルギーとの差は、0.05eV以上2eV以下であり、

前記第3の酸化物半導体層の伝導帯下端のエネルギーは、前記第2の酸化物半導体層の伝導帯下端のエネルギーよりも、真空準位に近く、

前記第2の酸化物半導体の伝導帯下端のエネルギーと前記第3の酸化物半導体層の伝導帯下端のエネルギーとの差は、0.05eV以上2eV以下であることを特徴とする半導体装置の作製方法。

**【請求項16】**

請求項7乃至請求項15のいずれか一において、

前記第2の酸化物半導体層の端部は丸みを帯びた形状を有することを特徴とする半導体装置の作製方法。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置および半導体装置を有する装置に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電気機器は全て半導体装置である。

**【背景技術】**

**【0003】** 50

半導体を用いてトランジスタを構成する技術が注目されている。当該トランジスタは集積回路（I C）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

#### 【0004】

例えば、インジウム（In）、ガリウム（Ga）、および亜鉛（Zn）を含む非晶質酸化物半導体層を用いたトランジスタが特許文献1に開示されている。

#### 【0005】

また、酸化物半導体層を、積層構造とすることで、キャリアの移動度を向上させる技術が特許文献2、特許文献3に開示されている。

10

#### 【0006】

ところで、酸化物半導体層を用いたトランジスタは、オフ状態において極めてリーク電流が小さいことが知られている。例えば、酸化物半導体層を用いたトランジスタの低いリーク特性を応用した低消費電力のCPUなどが開示されている（特許文献4参照。）。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献1】特開2006-165528号公報

【特許文献2】特開2011-124360号公報

20

【特許文献3】特開2011-138934号公報

【特許文献4】特開2012-257187号公報

【特許文献5】特開2012-074692号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

回路の高集積化に伴い、トランジスタのサイズも微細化している。トランジスタを微細化すると、オン電流、オフ電流、しきい値、S値（サブスレッショルドスイギング値）などのトランジスタの電気特性が悪化する場合がある（特許文献5参照）。一般に、チャネル長を縮小すると、オン電流は増加するが、一方でオフ電流の増大、しきい値の変動の増大、S値の増大が起こる。また、チャネル幅のみを縮小すると、オン電流が小さくなる。

30

#### 【0009】

したがって、本発明の一態様は、しきい値が適正化された半導体装置を提供することを目的の一つとする。微細化に伴い顕著となる電気特性の悪化を抑制できる構成の半導体装置を提供することを目的の一つとする。または、集積度の高い半導体装置を提供することを目的の一つとする。または、オン電流の悪化を低減した半導体装置を提供することを目的の一つとする。または、低消費電力の半導体装置を提供することを目的の一つとする。または、信頼性の高い半導体装置を提供することを目的の一つとする。または、電源が遮断されてもデータが保持される半導体装置を提供することを目的の一つとする。または、特性の良い半導体装置を提供することを目的の一つとする。

30

#### 【0010】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

40

#### 【課題を解決するための手段】

#### 【0011】

本発明の一態様は、第1の半導体と、第1の半導体に電気的に接する電極と、第1の半導体を間に挟んで設けられる第1のゲート電極と第2のゲート電極と、第1のゲート電極と第1の半導体との間に設けられる電子捕獲層と、第2のゲート電極と第1の半導体との間に設けられるゲート絶縁層を有する半導体装置である。

50

**【0012】**

また、本発明の一態様は、上記半導体装置において、第1のゲート電極の電位を、電極の電位より高い状態として、125以上450以下で1秒以上維持することにより電子捕獲層に電子を捕獲せしめることを特徴とする半導体装置の作製方法である。

**【0013】**

また、上記構成において、第1の半導体を挟む第2の半導体および第3の半導体を有してもよく、第2の半導体は、第1の半導体と第1のゲート電極の間にあり、第3の半導体は、第1の半導体とゲート絶縁層の間にあってもよい。

**【0014】**

また、上記構成において、第1のゲート電極は、第1の半導体の上面および側面に面していることが好ましい。 10

**【0015】**

また、上記構成において、電子捕獲層は、酸化ハフニウム、酸化アルミニウム、酸化タンタル、アルミニウムシリケートのいずれかを含む。

**【発明の効果】****【0016】**

本発明の一態様を用いることにより、しきい値が適正化された半導体装置を提供することができる。また、微細化に伴い顕著となる電気特性の低下を抑制できる構成の半導体装置を提供することができる。または、集積度の高い半導体装置を提供することができる。または、低消費電力の半導体装置を提供することができる。または、信頼性の高い半導体装置を提供することができる。または、電源が遮断されてもデータが保持される半導体装置を提供することができる。 20

**【図面の簡単な説明】****【0017】**

【図1】実施の形態の半導体装置の例を示す図。

【図2】実施の形態の半導体装置の例を示す図。

【図3】実施の形態の半導体装置のバンド図の例を示す図。

【図4】実施の形態の半導体装置の特性を模式的に示す図と半導体装置を応用した回路の例を示す図。 30

【図5】実施の形態のメモリセルの例を示す図。

【図6】半導体装置の作製工程を示す図。

【図7】トランジスタを説明する上面図および断面図。

【図8】積層された半導体層のバンドの模式図。

【図9】トランジスタを説明する上面図および断面図。

【図10】トランジスタの作製方法を説明する図。

【図11】トランジスタの作製方法を説明する図。

【図12】トランジスタを説明する上面図および断面図。

【図13】トランジスタを説明する断面図。

【図14】本発明の一態様の半導体装置を用いた回路を説明する図。

【図15】実施の形態の半導体装置の回路図。 40

【図16】実施の形態の半導体装置のブロック図。

【図17】実施の形態の記憶装置を説明する回路図。

【図18】電子機器の例を示す図。

【図19】参考例で作製したトランジスタの電気特性評価を説明する図。

**【発明を実施するための形態】****【0018】**

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。 50

**【 0 0 1 9 】**

なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。

**【 0 0 2 0 】**

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合には入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

**【 0 0 2 1 】**

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。 10

**【 0 0 2 2 】****(実施の形態1)**

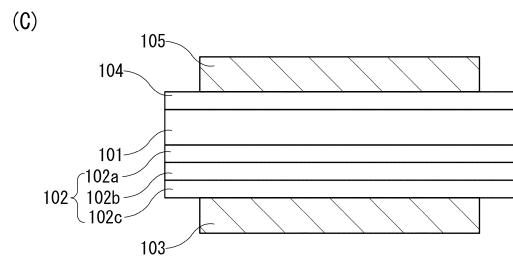

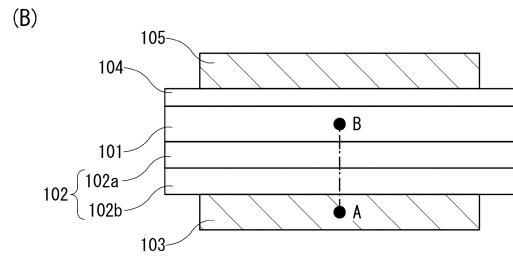

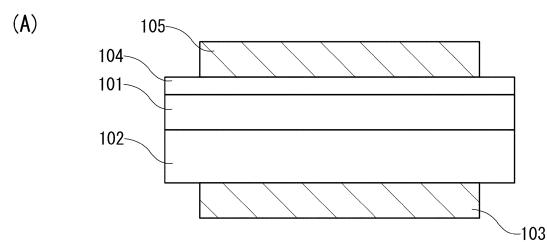

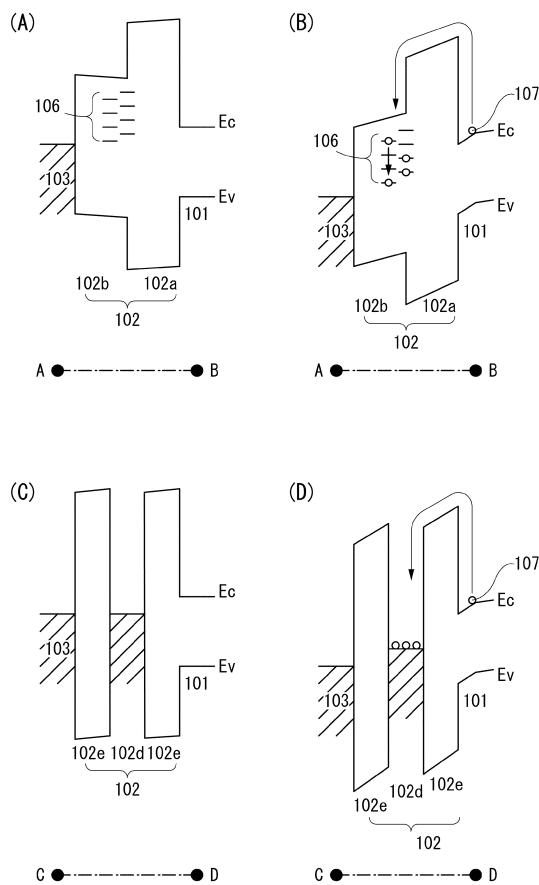

本実施の形態では、半導体層と電子捕獲層とゲート電極とを有する半導体装置の構成および動作原理、および、それを応用した回路について説明する。図1(A)は、半導体層101と電子捕獲層102とゲート電極103とゲート絶縁層104とゲート電極105とを有する半導体装置である。

**【 0 0 2 3 】**

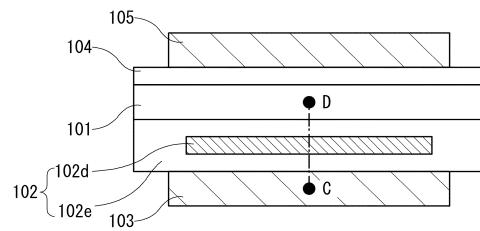

ここで、電子捕獲層102としては、例えば、図1(B)に示されるような、第1の絶縁層102aと第2の絶縁層102bの積層体でもよいし、図1(C)に示されるような、第1の絶縁層102a、第2の絶縁層102bと第3の絶縁層102cの積層体、あるいは、さらに多層の絶縁層の積層体でもよい。また、図2に示されるように、絶縁体102e中に、電気的に絶縁された導電層102dを有してもよい。絶縁体102eは複数の絶縁層より形成されてもよい。 20

**【 0 0 2 4 】**

例えば、図1(B)に示す半導体装置の点Aから点Bにかけてのバンド図の例を図3(A)に示す。図中、Ecは伝導帯下端、Evは価電子帯上端を示す。図3(A)では、ゲート電極103の電位はソース電極あるいはドレイン電極(いずれも図示せず)の電位と同じである。

**【 0 0 2 5 】**

この例では、第1の絶縁層102aのバンドギャップは第2の絶縁層102bのバンドギャップよりも大きく、第1の絶縁層102aの電子親和力は第2の絶縁層102bの電子親和力よりも小さいものとするが、これに限られない。 30

**【 0 0 2 6 】**

第1の絶縁層102aと第2の絶縁層102bの界面、あるいは、第2の絶縁層102bの内部に電子捕獲準位106が存在する。ゲート電極103の電位を、ソース電極あるいはドレイン電極の電位より高くすると、図3(B)に示すようになる。このように、一定の条件下で、ゲート電極103の電位を、ソース電極あるいはドレイン電極の電位より高くすることをしきい値適正化処理ともいう。ここで、ゲート電極103の電位は、ソース電極あるいはドレイン電極より1V以上高くしてもよい。また、ゲート電極103の電位は、この処理の終了した後にゲート電極105に印加される最高電位よりも低くてもよい。この処理においては、代表的には、ゲート電極103の電位とソース電極あるいはドレイン電極の差は、4V未満とするとよい。 40

**【 0 0 2 7 】**

なお、この処理において、ゲート電極105の電位はソース電極あるいはドレイン電極と同じであるとよい。この処理において、半導体層101に存在する電子107は、より電位の高いゲート電極103の方向に移動しようとする。そして、半導体層101からゲート電極103の方向に移動した電子107のいくらかは、電子捕獲準位106に捕獲される。

**【 0 0 2 8 】**

電子 107 が、第 1 の絶縁層 102a の障壁を超えて、第 2 の絶縁層 102b に達するには、いくつかの過程が考えられる。第 1 は、トンネル効果によるものである。トンネル効果は、第 1 の絶縁層 102a が薄いほど顕著となる。ただし、この場合、電子捕獲準位 106 に捕獲された電子が、トンネル効果により、再度、半導体層 101 に戻ってしまうことがある。

#### 【0029】

なお、ゲート電極 103 に適切な大きさの電圧を印加することで、第 1 の絶縁層 102a が比較的厚い場合でも、トンネル効果 (Fowler-Nordheim トンネル効果) を発現させることもできる。Fowler-Nordheim トンネル効果の場合には、ゲート電極 103 と半導体層 101 の間の電場の自乗に比例してトンネル電流が増加する。

10

#### 【0030】

第 2 は、電子 107 が、第 1 の絶縁層 102a 中の欠陥準位等のバンドギャップ中の捕獲準位をホッピングしながら、第 2 の絶縁層 102b に到達するものである。これは、Poole-Frenkel 伝導といわれる伝導機構であり、絶対温度が高いほど、捕獲準位が浅いほど、電気伝導性が高まる。

#### 【0031】

第 3 は、熱的な励起によって、電子 107 が、第 1 の絶縁層 102a の障壁を超えるものである。半導体層 101 に存在する電子の分布はフェルミ・ディラック分布にしたがい、一般的には、エネルギーの高い電子の比率は、高温であるほど多くなる。例えば、フェルミ面から 3 電子ボルトだけ高いエネルギーを有する電子の 300K (27) での密度を 1 としたとき、450K (177) では、 $6 \times 10^{16}$ 、600K (327) では、 $1.5 \times 10^{25}$ 、750K (477) では、 $1.6 \times 10^{30}$  となる。

20

#### 【0032】

電子 107 が、第 1 の絶縁層 102a の障壁を超えてゲート電極 103 に向かって移動する過程は、上記の 3 つの方法とそれらの組み合わせで生じていると考えられる。特に、第 2 の方法、第 3 の方法は、温度が高いと指數関数的に電流が増大することを示す。

#### 【0033】

また、Fowler-Nordheim トンネル効果も、第 1 の絶縁層 102a の障壁層の薄い部分 (エネルギーの大きな部分) の電子の密度が高いほど起こりやすいので、温度が高いことが有利である。

30

#### 【0034】

なお、以上の伝導機構による電流は、特にゲート電極 103 の電位が低い (5V 以下) 場合には、きわめて微弱であることが多いが、長時間の処理により、必要とする量の電子を電子捕獲準位 106 に捕獲せしめることができる。この結果、電子捕獲層 102 は負に帯電する。

#### 【0035】

すなわち、より高い温度 (半導体装置の使用温度あるいは保管温度よりも高い温度、あるいは、125 以上 450 以下、代表的には 150 以上 300 以下) の下で、ゲート電極 103 の電位をソース電極やドレイン電極の電位より高い状態を、1 秒以上、代表的には 1 分以上維持することで、半導体層 101 からゲート電極 103 に向かって、必要とする電子が移動し、そのうちのいくらかは電子捕獲準位 106 に捕獲される。このように電子を捕獲する処理のための温度を、以下、処理温度という。

40

#### 【0036】

このとき、電子捕獲準位 106 に捕獲される電子の量はゲート電極 103 の電位により制御できる。電子捕獲準位 106 に相応の量の電子が捕獲されると、その電荷のために、ゲート電極 103 の電場が遮蔽され、半導体層 101 に形成されるチャネルが消失する。

#### 【0037】

電子捕獲準位 106 により捕獲される電子の総量は、当初は、線形に増加するが、徐々に増加率が低下し、やがて、一定の値に収斂する。収斂する値は、ゲート電極 103 の電位

50

に依存し、電位が高いほどより多くの電子が捕獲される傾向にあるが、電子捕獲準位 106 の総数を上回ることはない。

#### 【0038】

電子捕獲準位 106 に捕獲された電子は、電子捕獲層 102 から他へ移動しないことが求められる。そのためには、第 1 には、第 1 の絶縁層 102a および第 2 の絶縁層 102b の厚さが、トンネル効果が問題とならない程度の厚さであることが好ましい。例えば、物理的な厚さが 1 nm より大きいことが好ましい。

#### 【0039】

一方で、第 1 の絶縁層 102a が厚すぎると、電子の移動の妨げとなるので、30 nm 以下とすることが好ましい。また、半導体装置のチャネル長に比較して、第 1 の絶縁層 102a、第 2 の絶縁層 102b が厚すぎると、サブスレショールド値が増加し、オフ特性が悪化するので、チャネル長は、第 1 の絶縁層 102a と第 2 の絶縁層 102b の酸化シリコン換算の厚さ (Equivalent Silicon Oxide Thickness) の 4 倍以上、代表的には 10 倍以上であるとよい。なお、いわゆる High-K 材料では、酸化シリコン換算の厚さが物理的な厚さよりも小さくなる。

#### 【0040】

代表的には、第 1 の絶縁層 102a の厚さは、10 nm 以上 20 nm 以下、第 2 の絶縁層 102b の、酸化シリコン換算の厚さは、1 nm 以上 25 nm 以下とするとい。

#### 【0041】

また、半導体装置の使用温度あるいは保管温度を処理温度よりも十分に低くすることが考えられる。例えば、電子が、3 電子ボルトの障壁を乗り越える確率は、120 のときは 300 のときの 10 万分の 1 未満である。したがって、300 で処理の際には障壁を乗り越えて容易に電子捕獲準位 106 に捕獲される電子が、120 で保管時には、障壁を乗り越えることが困難となり、電子が長期にわたって、電子捕獲準位 106 に捕獲された状態となる。

#### 【0042】

また、半導体層 101 で、ホールの有効質量が極めて大きい、あるいは、実質的に局在化していることも有効である。この場合には、半導体層 101 から第 1 の絶縁層 102a および第 2 の絶縁層 102b へのホールの注入がなく、したがって、電子捕獲準位 106 に捕獲された電子がホールと結合して消滅することもない。

#### 【0043】

また、第 2 の絶縁層 102b が、Poole-Frenkel 伝導を示す材料であってもよい。Poole-Frenkel 伝導は、上述のように、材料中の欠陥準位等を電子がホッピング伝導するものであり、欠陥準位の多い、あるいは、欠陥準位の深い材料は十分に電気伝導性が低く、電子捕獲準位 106 に捕獲された電子を長時間にわたって保持できる。

#### 【0044】

また、第 1 の絶縁層 102a、第 2 の絶縁層 102b に捕獲された電子を放出させるような電圧がかからないように回路設計、材料選定をおこなってもよい。例えば、In-Ga-Zn 系酸化物半導体のように、ホールの有効質量が極めて大きい、あるいは、実質的に局在化しているような材料では、ゲート電極 103 の電位が、ソース電極あるいはドレイン電極の電位より高い場合にはチャネルが形成されるが、低い場合には、絶縁体と同様な特性を示す。この場合には、ゲート電極 103 と半導体層 101 の間の電場が極めて小さくなり、Fowler-Nordheim トンネル効果、あるいは、Poole-Frenkel 伝導による電子伝導は著しく低下する。

#### 【0045】

なお、図 1 (C) のように、電子捕獲層 102 を 3 層の絶縁層で形成し、第 3 の絶縁層 102c の電子親和力を、第 2 の絶縁層 102b の電子親和力よりも小さくし、第 3 の絶縁層 102c のバンドギャップを、第 2 の絶縁層 102b のバンドギャップよりも大きくすると、第 2 の絶縁層 102b の内部、あるいは、他の絶縁層との界面にある電子捕獲準位

10

20

30

40

50

に捕獲された電子を保持する上で効果的である。

#### 【0046】

この場合には、第2の絶縁層102bが薄くても、第3の絶縁層102cが物理的に十分に厚ければ、電子捕獲準位106に捕獲された電子を保持できる。第3の絶縁層102cとしては、第1の絶縁層102aと同じまたは同様な材料を用いることができる。また、第2の絶縁層102bと同じ構成元素であるが、電子捕獲準位が十分に少ないものも用いることができる。電子捕獲準位の数（密度）は、形成方法によって異なる。

#### 【0047】

なお、図2のように、絶縁体102e中に電気的に絶縁された導電層102dを有する場合も、上記と同様な原理によって、導電層102dに電子が捕獲される。図3(C)および図3(D)にその例を示す。図3(C)では、ゲート電極103の電位はソース電極あるいはドレイン電極の電位と同じである。

10

#### 【0048】

ゲート電極103の電位を、ソース電極あるいはドレイン電極の電位より高くすると、図3(D)に示すようになる。半導体層101に存在する電子は、より電位の高いゲート電極103の方向に移動しようとする。そして、半導体層101からゲート電極103の方向に移動した電子のいくらかは、導電層102dに捕獲される。すなわち、図2に示される半導体装置において、導電層102dは、図1(B)の半導体装置における電子捕獲準位106と同等の機能を有する。

#### 【0049】

20

なお、導電層102dの仕事関数が大きいと、絶縁体102eとの間のエネルギー障壁が高くなり、捕獲された電子が他へ移動することを抑制できる。

#### 【0050】

上記において、第1の絶縁層102a、第2の絶縁層102b、第3の絶縁層102cは、それぞれ複数の絶縁層より構成されてもよい。また、同じ構成元素からなるが、形成方法の異なる複数の絶縁層から構成されてもよい。

#### 【0051】

例えば、第1の絶縁層102aと第2の絶縁層102bと同じ構成元素からなる絶縁層（例えば、酸化ハフニウム）で構成する場合、第1の絶縁層102aは、化学気相堆積(CVD)法あるいは原子層堆積(ALD法)で形成し、第2の絶縁層102bは、スパッタリング法で形成してもよい。

30

#### 【0052】

なお、CVD法としても、様々な方法を用いることが出来る。熱CVD法、光CVD法、プラズマCVD(PECVD)法、有機金属CVD(MOCVD)法、減圧CVD(LPCVD)法などの方法を用いることが出来る。よって、ある絶縁膜と別の絶縁膜において、異なるCVD法を用いて、絶縁膜を形成してもよい。

#### 【0053】

一般にスパッタリング法で形成される絶縁層はCVD法あるいはALD法で形成される絶縁層よりも欠陥を多く含み、電子を捕獲する性質が強い。同様な理由から、第2の絶縁層102bと第3の絶縁層102cと同じ構成元素からなる絶縁層で構成する場合、第2の絶縁層102bは、スパッタリング法で形成し、第3の絶縁層102cは、CVD法あるいはALD法で形成してもよい。

40

#### 【0054】

また、第2の絶縁層102bと同じ構成元素からなる複数の絶縁層で構成する場合、そのうちの1つは、スパッタリング法で形成し、別の1つは、CVD法あるいはALD法で形成してもよい。

#### 【0055】

このように電子捕獲層102が電子を捕獲すると、半導体装置のしきい値が増加する。特に、半導体層101が、バンドギャップが大きな材料（ワイドバンドギャップ半導体）であると、ゲート電極103およびゲート電極105の電位をソース電極の電位と同じとし

50

たときのソースドレイン間の電流（カットオフ電流（ $I_{cut}$ ））を大幅に低下させることができる。

#### 【0056】

例えば、バンドギャップ3.2電子ボルトのIn-Ga-Zn系酸化物であれば、 $I_{cut}$ 密度（チャネル幅1μmあたりの電流値）は1zA/μm ( $1 \times 10^{-21} \text{ A} / \mu\text{m}$ )以下、代表的には、1yA/μm ( $1 \times 10^{-24} \text{ A} / \mu\text{m}$ )以下とできる。

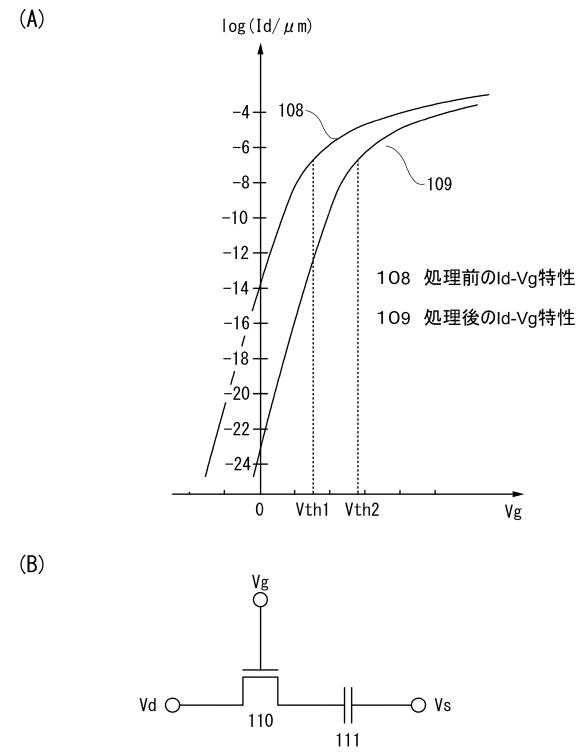

#### 【0057】

図4(A)は電子捕獲層102での電子の捕獲をおこなう前と、電子の捕獲をおこなった後での、室温でのソース電極ドレイン電極間のチャネル幅1μmあたりの電流( $I_d$ )のゲート電極105の電位( $V_g$ )依存性を模式的に示したものである。なお、ソース電極とゲート電極103の電位を0V、ドレイン電極の電位を+1Vとする。 $1 \text{ fA}$ より小さな電流は、直接は測定できないが、その他の方法で測定した値、サブスレショールド値等をもとに推定できる。なお、このような測定方法に関しては、参考例を参照するとよい。

#### 【0058】

最初、曲線108で示すように、半導体装置のしきい値は $V_{th1}$ であったが、電子の捕獲をおこなった後では、しきい値が増加し（プラス方向に移動し）、 $V_{th2}$ となる。また、この結果、 $V_g = 0$ での電流密度は、 $1 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-18} \text{ A} / \mu\text{m}$ )以下、例えば、 $1 \text{ zA} / \mu\text{m}$ 以上 $1 \text{ yA} / \mu\text{m}$ 以下となる。

#### 【0059】

例えば、図4(B)のように、容量素子111に蓄積される電荷をトランジスタ110で制御する回路を考える。ここで、容量素子111の電極間のリーク電流は無視する。容量素子111の容量が $1 \text{ fF}$ であり、容量素子111のトランジスタ110側の電位が+1V、 $V_d$ の電位が0Vであるとする。

#### 【0060】

トランジスタ110の $I_d - V_g$ 特性が図4(A)中の曲線108で示されるもので、チャネル幅が $0.1 \mu\text{m}$ であると、 $I_{cut}$ は約 $1 \times 10^{-15} \text{ A}$ （約 $1 \text{ fA}$ ）であり、トランジスタ110のこのときの抵抗は約 $1 \times 10^{15} \Omega$ である。したがって、トランジスタ110と容量素子111よりなる回路の時定数は約1秒である。すなわち、約1秒で、容量素子111に蓄積されていた電荷の多くが失われてしまうことを意味する。

#### 【0061】

トランジスタ110の $I_d - V_g$ 特性が図4(A)中の曲線109で示されるもので、チャネル幅が $0.1 \mu\text{m}$ であると、 $I_{cut}$ は約 $1 \times 10^{-24} \text{ A}$ （約 $1 \text{ yA}$ ）であり、トランジスタ110のこのときの抵抗は約 $1 \times 10^{24} \Omega$ である。したがって、トランジスタ110と容量素子111よりなる回路の時定数は約 $1 \times 10^9 \text{ s}$ （=約31年）である。すなわち、10年経過後でも、容量素子111に蓄積されていた電荷の $1/3$ は残っていることを意味する。

#### 【0062】

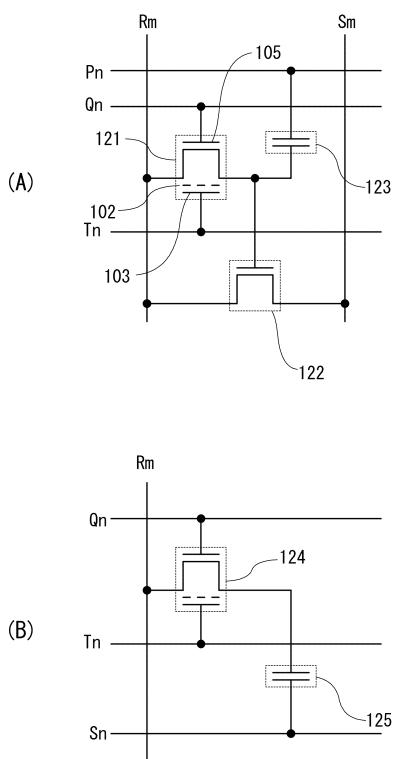

すなわち、トランジスタと容量素子という単純な回路で、かつ、それほど過大な電圧を印加しなくても、10年間の電荷の保持が可能である。このことは各種記憶装置に用いることができる。例えば、図5に示すようなメモリセルに用いることもできる。

#### 【0063】

図5(A)に示すメモリセルは、トランジスタ121、トランジスタ122、容量素子123からなり、トランジスタ121は、図1(A)に示したように、電子捕獲層102を有するトランジスタである。回路が形成された後で、上記に示したようなしきい値を増加させる処理をおこない、 $I_{cut}$ を低下させる。なお、図に示すように、電子捕獲層102中に電子を有するために、しきい値が変動したトランジスタは、通常のトランジスタとは異なる記号を用いる。

#### 【0064】

図5(A)に示すメモリセルはマトリクス状に形成され、例えば、 $n$ 行 $m$ 列のメモリセルであれば、読み出しワード線 $P_n$ 、書き込みワード線 $Q_n$ 、しきい値補正用配線 $T_n$ 、ビ

10

20

30

40

50

ット線 R m、ソース線 S m が接続する。なお、すべてのしきい値補正用配線が接続するような回路配置とすることにより、すべてのしきい値補正用配線の電位は同じ値となるようにしてよい。

#### 【 0 0 6 5 】

しきい値補正是以下のようにおこなえばよい。まず、すべての読み出しワード線、書き込みワード線、ソース線、ビット線の電位を 0 V とする。そして、メモリセルが形成されたウェハーあるいはチップを適切な温度に保持し、すべてのしきい値補正用配線の電位を適切な値（例えば、+3 V）として、適切な時間保持する。この結果、しきい値が適切な値になる。

#### 【 0 0 6 6 】

なお、メモリセルは図 5 (B) に示すような、トランジスタ 124、容量素子 125 からなるものでもよい。例えば、n 行 m 列のメモリセルであれば、ワード線 Q n、しきい値補正用配線 T n、ビット線 R m、ソース線 S n が接続する。しきい値補正の方法は図 5 (A) のものと同様にできる。

#### 【 0 0 6 7 】

ところで、このように電子捕獲層に電子を捕獲せしめて、しきい値を適正化して使用する場合には、その後の通常の使用において、電子捕獲層にさらに電子が追加されることは避けることが望ましい。例えば、さらなる電子の追加はしきい値のさらなる増加を意味し、回路の劣化をもたらす。

#### 【 0 0 6 8 】

電子捕獲層が半導体層の近傍にあり、かつ、半導体層よりも電位が高くなるような配線や電極が電子捕獲層をはさんで、半導体層に向き合って存在すると、通常の使用時においても、電子捕獲層に電子が捕獲される可能性がある。

#### 【 0 0 6 9 】

このようなことを防止するには、例えば、図 5 (A) あるいは図 5 (B) に示されるメモリセルにおいては、しきい値補正用配線 T n の電位を、ビット線 R m のとりうる最低の電位以下とすることが望ましい。

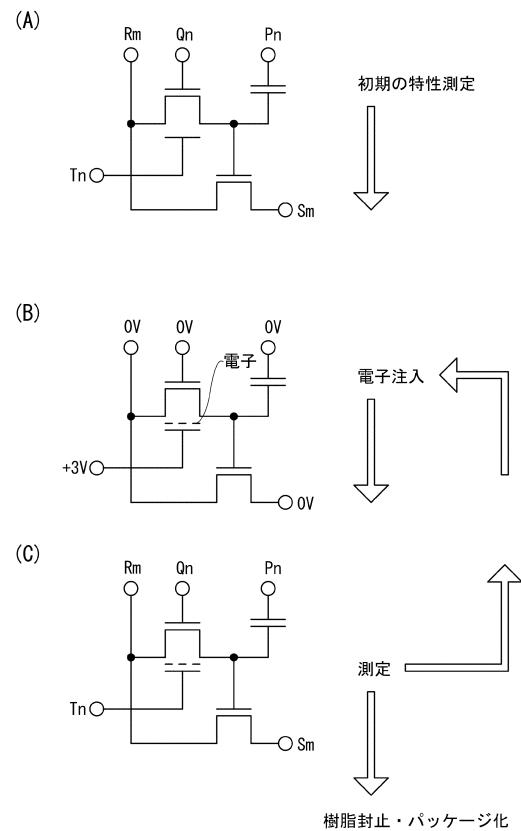

#### 【 0 0 7 0 】

例えば、図 6 に示すような工程が実施できる。まず、図 6 (A) に示すように、メモリセルが完成した後、初期特性を測定し、良品を選別する。ここで、良品の基準は断線等による回復不可能な動作不良に限定するとよい。まだ、しきい値が適正化されていないため、容量素子の電荷を長時間保持することはできないが、そのことは選別の基準とはならない。

#### 【 0 0 7 1 】

その後、図 6 (B) に示すように、電子を注入する。すなわち、電子捕獲層 102 に適切な量の電子を捕獲させる。この操作は上述のとおりおこなう。ここで、しきい値補正用配線がすべて接続されているのであれば、チップにパッドを設け、そこを介して電位を供給することができる。このとき、ゲート電極 103 の電位と、ソース電極あるいはドレイン電極のいずれか低い方の電位との差（ゲート電圧）は、1 V 以上 4 V 未満であり、かつ、このメモリセルが出荷された後でのゲート電極 105 とソース電極あるいはドレイン電極のいずれか低い方の電位との差より低いものとする。

#### 【 0 0 7 2 】

その後、図 6 (C) に示すように、再度、測定をおこなう。設定通りにしきい値が増加していることが良品の条件の一つである。この段階では、しきい値に異常のあるチップは不良品として、再度、電子注入をおこなってよい。良品は、ダイシング、樹脂封止後、パッケージ化して出荷する。

#### 【 0 0 7 3 】

しきい値の増加の程度は電子捕獲層 102 が捕獲する電子密度によって決まる。例えば、図 1 (B) に示す半導体装置において、第 1 の絶縁層 102 a と第 2 の絶縁層 102 b の界面においてのみ電子が捕獲される場合、しきい値は、Q / C (ただし、Q は捕獲された

10

20

30

40

50

電子の面密度、Cは第1の絶縁層102aの誘電率)だけ増加する。

**【0074】**

なお、上記のようにゲート電極103の電位によって、捕獲される電子の量が一定の値になることから、ゲート電極103の電位によって、しきい値の増加分を制御することもできる。

**【0075】**

例えば、ゲート電極103の電位を、ソース電極とドレイン電極の電位より1.5Vだけ高くし、温度を150乃至250、代表的には $200 \pm 20$ とする場合を考える。電子捕獲層102に電子が捕獲される前の半導体装置のしきい値(第1のしきい値、 $V_{th1}$ )が+1.1Vであったとすると、当初は、半導体層101にチャネルが形成されおり、電子捕獲層102に電子が捕獲される。その後、電子捕獲層102に捕獲される電子の量が増加し、チャネルが消失する。この段階で、電子捕獲層102での電子の捕獲はおこなわれなくなる。

10

**【0076】**

この場合には、ゲート電極103の電位が、ソース電極、ドレイン電極より1.5V高い段階でチャネルが消失するので、しきい値が、+1.5Vとなる。あるいは、電子捕獲層102に捕獲された電子によって、しきい値が、0.4Vだけ高くなったと言える。このように電子捕獲層102に捕獲された電子によって変化した後のしきい値を第2のしきい値( $V_{th2}$ )という。

20

**【0077】**

このような特性を用いれば、もともと相当なばらつきのあった複数の半導体装置のしきい値を適切な範囲内に収束させることもできる。例えば、第1のしきい値が+1.2V、+1.1V、+0.9Vである3つの半導体装置があるとする。これらの半導体装置に、上記の条件で処理をおこなえば、それぞれの半導体装置のしきい値が+1.5Vを大きく超えるような電子の捕獲は生じないので、3つの半導体装置とも第2のしきい値を+1.5V付近とすることができます。この場合、これら3つの半導体装置の電子捕獲層102に捕獲される電子の量(あるいは電子の面密度等)は異なる。

**【0078】**

なお、電子捕獲層102に捕獲される電子の数は、しきい値適正化処理の時間にも依存するので、しきい値適正化処理の時間によっても、しきい値を目的とするものとすることができる。

30

**【0079】**

ゲート電極103は各種の材料を用いることができる。例えば、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、TaおよびWなどの導電層を用いることができる。また、ゲート電極103は、上記材料の積層であってもよい。また、ゲート電極103には、窒素を含んだ導電層を用いてもよい。たとえば、ゲート電極103に窒化チタン層上にタングステン層の積層、窒化タンクステン層上にタンクステン層の積層、窒化タンタル層上にタンクステン層の積層などを用いることができる。

**【0080】**

なお、半導体層101に対向するゲート電極103の仕事関数は、半導体装置のしきい値を決定する要因のひとつであり、一般に、仕事関数が小さい材料であると、しきい値が小さくなる。しかしながら、上述のように、電子捕獲層102に捕獲する電子の量によりしきい値を調整できるので、ゲート電極103の材料の選択の幅が広がる。

40

**【0081】**

半導体層101は各種の材料を用いることができる。例えば、シリコンやゲルマニウム、シリコンゲルマニウム以外に、後述する各種酸化物半導体を用いることができる。

**【0082】**

第1の絶縁層102aは各種の材料を用いることができる。例えば、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジムお

50

および酸化タンタルを一種以上含む絶縁層を用いることができる。

【0083】

第2の絶縁層102bは各種の材料を用いることができる例えば、酸化ハフニウム、酸化アルミニウム、酸化タンタル、アルミニウムシリケートなどを一種以上含む絶縁層を用いることができる。

【0084】

第3の絶縁層102cは各種の材料を用いることができる。例えば、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジムおよび酸化タンタルを一種以上含む絶縁層を用いることができる。

10

【0085】

導電層102dは各種の材料を用いることができる。例えば、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta、W、Pt、Pdなどの導電層を用いることができる。また、導電層102dは、上記材料の積層であってもよい。また、導電層102dには、窒素を含んだ導電層を用いてもよい。

【0086】

特に仕事関数の高い材料として、白金、パラジウム等の白金族金属、窒化インジウム、窒化亜鉛、In-Zn系酸窒化物、In-Ga系酸窒化物、In-Ga-Zn系酸窒化物等の窒化物等を用いるとよい。

20

【0087】

絶縁体102eは各種の材料を用いることができる。例えば、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化タンタルを用いることができる。

【0088】

このように電子捕獲層102に必要な量の電子を捕獲させた半導体装置は、通常のMOS型半導体装置と同じである。MOS型半導体装置として用いる場合には、ゲート電極103の電位はつねに回路の最低電位とするとよい。

【0089】

なお、電子捕獲層102に電子を捕獲せしめる処理は、上記に限らず、例えば、半導体装置のソース電極あるいはドレイン電極に接続する配線メタルの形成後、あるいは、前工程（ウェハー処理）の終了後、あるいは、ウェーハーダイシング工程後、パッケージ後等、工場出荷前のいずれかの段階でおこなうとよい。いずれの場合にも、その後に125以上の温度に1時間以上さらされないことが好ましい。

30

【0090】

(実施の形態2)

本実施の形態では、本発明の一態様の半導体装置について図面を用いて説明する。なお、以下では、主として、しきい値補正用のゲート電極が基板と半導体層の間に存在するトランジスタについて説明するが、しきい値補正用のゲート電極と基板の間にと半導体層が存在するトランジスタであってもよい。

【0091】

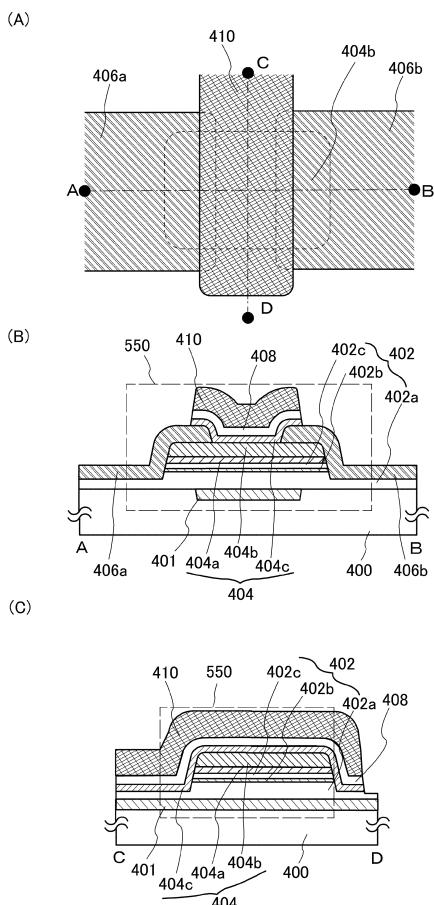

40

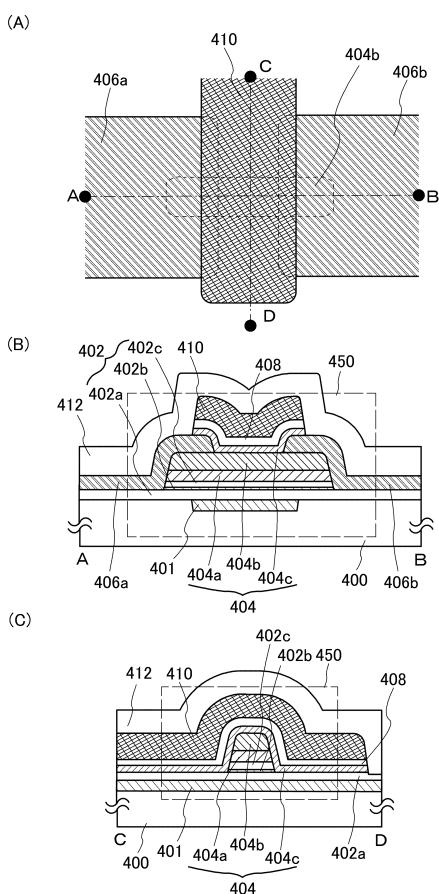

図7(A)乃至図7(C)は、本発明の一態様のトランジスタの上面図および断面図である。図7(A)は上面図であり、図7(A)に示す一点鎖線A-Bの断面が図7(B)、一点鎖線C-Dの断面が図7(C)に相当する。なお、図7(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線A-B方向をチャネル長方向、一点鎖線C-D方向をチャネル幅方向と呼称する場合がある。

【0092】

図7(A)乃至図7(C)に示すトランジスタ450は、基板400に埋め込まれたゲート電極401と、基板400およびゲート電極401上に設けられた、凹部および凸部を有する下地絶縁層402と、下地絶縁層402の凸部上の酸化物半導体層404aおよび酸化物半導体層404bと、酸化物半導体層404aおよび酸化物半導体層404b上の

50

ソース電極 406a およびドレイン電極 406b と、下地絶縁層 402 の凹部、下地絶縁層 402 の凸部（または凹部）の側面、酸化物半導体層 404a の側面、酸化物半導体層 404b の側面および酸化物半導体層 404b の上面、ソース電極 406a およびドレイン電極 406b と接する酸化物半導体層 404c と、酸化物半導体層 404c 上のゲート絶縁層 408 と、ゲート絶縁層 408 上で接し、酸化物半導体層 404b の上面および側面に面するゲート電極 410 と、ソース電極 406a、ドレイン電極 406b、およびゲート電極 410 上の酸化物絶縁層 412 と、を有する。

#### 【0093】

また、下地絶縁層 402 は、第1の絶縁層 402a と第2の絶縁層 402b と第3の絶縁層 402c を有し、実施の形態1で述べた電子捕獲層として機能する。また、酸化物半導体層 404a、酸化物半導体層 404b、および酸化物半導体層 404c を総称して多層半導体層 404 と呼称する。10

#### 【0094】

第2の絶縁層 402b に用いる材料を比誘電率が大きいものにすると、第2の絶縁層 402b を厚くすることができます。たとえば、誘電率が16の酸化ハフニウムを用いることにより、誘電率が3.9の酸化シリコンを用いる場合に比べて約4倍厚くすることが可能である。このため、捕獲された電子の流出を防止する上で好ましい。なお、第1の絶縁層 402a、第3の絶縁層 402c の厚さは、いずれも、1nm以上30nm以下、代表的には10nm以上20nm以下であり、第2の絶縁層 402b の厚さは、1nm以上100nm以下、代表的には5nm以上20nm以下である。20

#### 【0095】

なお、チャネル長とは、上面図において、半導体層とゲート電極とが重なる領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との距離をいう。すなわち、図7(A)では、チャネル長は、酸化物半導体層 404b とゲート電極 410 とが重なる領域における、ソース電極 406a とドレイン電極 406b との距離となる。チャネル幅とは、半導体層とゲート電極とが重なる領域における、ソースまたはドレインの幅をいう。すなわち、図7(A)では、チャネル幅は、酸化物半導体層 404b とゲート電極 410 とが重なる領域における、ソース電極 406a またはドレイン電極 406b の幅をいう。

#### 【0096】

下地絶縁層 402 を電子捕獲層として機能させることで、実施の形態1で述べたように第3の絶縁層 402c と第2の絶縁層 402b の界面、あるいは、第2の絶縁層 402b の内部に存在する電子捕獲準位に電子を捕獲することができる。このとき、電子捕獲準位に捕獲される電子の量はゲート電極 401 の電位により制御できる。30

#### 【0097】

また、ゲート電極 410 は、酸化物半導体層 404b を電気的に取り囲み、オン電流が高められる。このようなトランジスタの構造を、Surrounded Channel (S-Channel) 構造とよぶ。なお、S-Channel 構造では、電流は酸化物半導体層 404b の全体（バルク）を流れる。酸化物半導体層 404b の内部を電流が流れることで、界面散乱の影響を受けにくいため、高いオン電流を得ることができる。なお、酸化物半導体層 404b を厚くすると、オン電流を向上させることができる。40

#### 【0098】

また、トランジスタのチャネル長およびチャネル幅を微細化するとき、レジストマスクを後退させながら電極や半導体層等を加工すると電極や半導体層等の端部が丸みを帯びる（曲面を有する）場合がある。このような構成になることで、酸化物半導体層 404b 上に形成されるゲート絶縁層 408、ゲート電極 410 および酸化物絶縁層 412 の被覆性を向上させることができる。また、ソース電極 406a およびドレイン電極 406b の端部に生じる恐れのある電界集中を緩和することができ、トランジスタの劣化を抑制することができる。

#### 【0099】

また、トランジスタを微細化することで、集積度を高め、高密度化することができる。例えば、トランジスタのチャネル長を100nm以下、好ましくは40nm以下、さらに好ましくは30nm以下、より好ましくは20nm以下とし、かつ、トランジスタのチャネル幅を100nm以下、好ましくは40nm以下、さらに好ましくは30nm以下、より好ましくは20nm以下とする。本発明の一態様に係るトランジスタは、チャネル幅が上記のように小さくても、S-channel構造を有することでオン電流を高めることができる。

#### 【0100】

基板400は、単なる支持材料に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタ450のゲート電極410、ソース電極406a、およびドレイン電極406bの少なくとも一つは、上記の他のデバイスと電気的に接続されていてもよい。

10

#### 【0101】

下地絶縁層402は、基板400からの不純物の拡散を防止する役割を有するほか、多層半導体層404に酸素を供給する役割を担うことができる。また、上述のように基板400が他のデバイスが形成された基板である場合、下地絶縁層402は、層間絶縁層としての機能も有する。その場合、下地絶縁層402の表面には凹凸が形成されるため、表面が平坦になるようにCMP(Chemical Mechanical Polishing)法等で平坦化処理を行うことが好ましい。

20

#### 【0102】

また、トランジスタ450のチャネルが形成される領域において多層半導体層404は、基板400側から酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cが積層された構造を有している。また、酸化物半導体層404bは、酸化物半導体層404aおよび酸化物半導体層404cで取り囲まれている構造となっている。また、図7(C)に示すようにゲート電極410は、酸化物半導体層404bを電気的に取り囲む構造になっている。

#### 【0103】

ここで、一例としては、酸化物半導体層404bには、酸化物半導体層404aおよび酸化物半導体層404cよりも電子親和力(真空準位から伝導帯下端までのエネルギー)が大きい酸化物半導体を用いる。電子親和力は、真空準位と価電子帯上端とのエネルギー差(イオン化ポテンシャル)から、伝導帯下端と価電子帯上端とのエネルギー差(エネルギーギャップ)を差し引いた値として求めることができる。

30

#### 【0104】

酸化物半導体層404aおよび酸化物半導体層404cは、酸化物半導体層404bを構成する金属元素を一種以上含み、例えば、伝導帯下端のエネルギーが酸化物半導体層404bよりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

#### 【0105】

このような構造において、ゲート電極410に電界を印加すると、多層半導体層404のうち、伝導帯下端のエネルギーが最も小さい酸化物半導体層404bにチャネルが形成される。すなわち、酸化物半導体層404bとゲート絶縁層408との間に酸化物半導体層404cが形成されていることによって、トランジスタのチャネルがゲート絶縁層408と接しない領域に形成される構造となる。

40

#### 【0106】

また、酸化物半導体層404aは、酸化物半導体層404bを構成する金属元素を一種以上含んで構成されるため、酸化物半導体層404bと下地絶縁層402が接した場合の界面と比較して、酸化物半導体層404bと酸化物半導体層404aの界面に界面準位を形成しにくくなる。該界面準位はチャネルを形成することがあるため、トランジスタのしきい値が変動することがある。したがって、酸化物半導体層404aを設けることにより、

50

トランジスタのしきい値などの電気特性のばらつきを低減することができる。また、当該トランジスタの信頼性を向上させることができる。

#### 【0107】

また、酸化物半導体層404cは、酸化物半導体層404bを構成する金属元素を一種以上含んで構成されるため、酸化物半導体層404bとゲート絶縁層408が接した場合の界面と比較して、酸化物半導体層404bと酸化物半導体層404cとの界面ではキャリアの散乱が起こりにくくなる。したがって、酸化物半導体層404cを設けることにより、トランジスタの電界効果移動度を高くすることができる。

#### 【0108】

酸化物半導体層404aおよび酸化物半導体層404cには、例えば、Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHfを酸化物半導体層404bよりも高い原子数比で含む材料を用いることができる。具体的には、当該原子数比を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。前述の元素は酸素と強く結合するため、酸素欠損が酸化物半導体層に生じることを抑制する機能を有する。すなわち、酸化物半導体層404aおよび酸化物半導体層404cは酸化物半導体層404bよりも酸素欠損が生じにくいということができる。

#### 【0109】

なお、酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cが、少なくともインジウム、亜鉛およびM(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物であるとき、酸化物半導体層404aを $In : M : Zn = x_1 : y_1 : z_1$  [原子数比]、酸化物半導体層404bを $In : M : Zn = x_2 : y_2 : z_2$  [原子数比]、酸化物半導体層404cを $In : M : Zn = x_3 : y_3 : z_3$  [原子数比]とすると、 $y_1 / x_1$  および  $y_3 / x_3$  が  $y_2 / x_2$  よりも大きくなることが好ましい。 $y_1 / x_1$  および  $y_3 / x_3$  は  $y_2 / x_2$  よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、酸化物半導体層404bにおいて、 $y_2$  が  $x_2$  以上あるとトランジスタの電気特性を安定させることができる。ただし、 $y_2$  が  $x_2$  の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$  は  $x_2$  の3倍未満であることが好ましい。

#### 【0110】

酸化物半導体層404aおよび酸化物半導体層404cのZnおよびOを除いてのInとMの原子数比率は、InとMの合計を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。また、酸化物半導体層404bのZnおよびOを除いてのInとMの原子数比率は、InとMの合計を100atomic%としたとき、好ましくはInが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。

#### 【0111】

酸化物半導体層404aおよび酸化物半導体層404cの厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、酸化物半導体層404bの厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。また、酸化物半導体層404bは、酸化物半導体層404aおよび酸化物半導体層404cより厚い方が好ましい。

#### 【0112】

酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cには、例えば、インジウム、亜鉛およびガリウムを含んだ酸化物半導体を用いることができる。特に、酸化物半導体層404bにインジウムを含ませると、キャリア移動度が高くなるため好ましい。

#### 【0113】

なお、酸化物半導体層を用いたトランジスタに安定した電気特性を付与するためには、酸

10

20

30

40

50

化物半導体層中の不純物濃度を低減し、酸化物半導体層を真性または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体層のキャリア密度が、 $1 \times 10^{17} / \text{cm}^3$  未満であること、好ましくは $1 \times 10^{15} / \text{cm}^3$  未満であること、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$  未満であることを指す。

#### 【0114】

また、酸化物半導体層において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素はドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンは酸化物半導体層中で不純物準位の形成に寄与する。当該不純物準位は捕獲となり、トランジスタの電気特性を劣化させことがある。したがって、酸化物半導体層 404a、酸化物半導体層 404b、酸化物半導体層 404c の層中や、それぞれの界面において不純物濃度を低減させることが好ましい。10

#### 【0115】

酸化物半導体層を真性または実質的に真性とするために SIMS (Secondary Ion Mass Spectrometry) 分析において、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$  未満とする部分を有していることが好ましい。また、水素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $2 \times 10^{20} \text{ atoms/cm}^3$  以下、好ましくは $5 \times 10^{19} \text{ atoms/cm}^3$  以下、より好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$  以下、さらに好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  以下とする部分を有していることが好ましい。また、窒素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $5 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  以下、より好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$  以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$  以下とする部分を有していることが好ましい。20

#### 【0116】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$  未満とする部分を有していればよい。また、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、炭素濃度を $1 \times 10^{19} \text{ atoms/cm}^3$  未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$  未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$  未満とする部分を有していればよい。30

#### 【0117】

また、上述のように高純度化された酸化物半導体層をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さい。例えば、ソースとドレインとの間の電圧を 0.1V、5V、または、10V 程度とした場合に、トランジスタのチャネル幅で規格化したオフ電流を数 yA /  $\mu\text{m}$  から数 zA /  $\mu\text{m}$  にまで低減することが可能となる。40

#### 【0118】

なお、トランジスタのゲート絶縁層としては、シリコンを含む絶縁層が多く用いられるため、上記理由により多層半導体層のチャネルとなる領域は、本発明の一態様のトランジスタのようにゲート絶縁層と接しない構造が好ましいということができる。また、ゲート絶縁層と多層半導体層との界面にチャネルが形成される場合、該界面でキャリアの散乱が起これり、トランジスタの電界効果移動度が低くなることがある。このような観点からも、多層半導体層のチャネルとなる領域はゲート絶縁層から離すことが好ましいといえる。

#### 【0119】

したがって、多層半導体層 404 を酸化物半導体層 404a、酸化物半導体層 404b、

50

酸化物半導体層404cの積層構造とすることで、酸化物半導体層404bにチャネルを形成することができ、高い電界効果移動度および安定した電気特性を有したトランジスタを形成することができる。

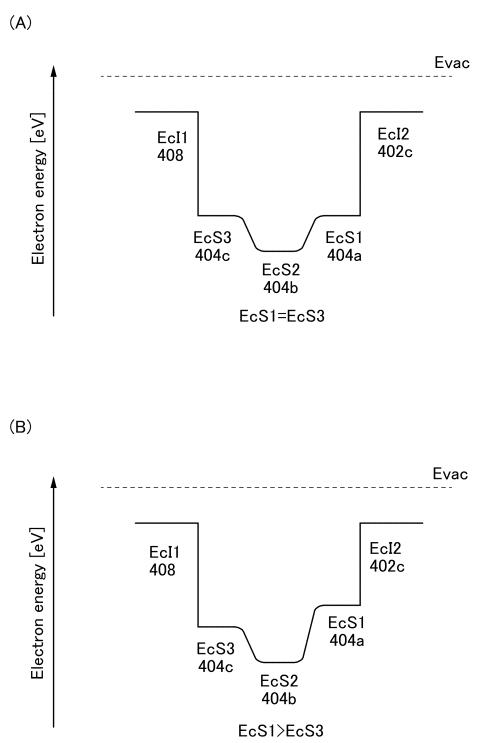

#### 【0120】

次に、多層半導体層404のバンド構造を説明する。バンド構造の解析は、酸化物半導体層404aおよび酸化物半導体層404cに相当する層としてエネルギーギャップが3.5eVであるIn-Ga-Zn酸化物、酸化物半導体層404bに相当する層としてエネルギーギャップが3.15eVであるIn-Ga-Zn酸化物を用い、多層半導体層404に相当する積層を作製して行っている。

#### 【0121】

酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cの厚さはそれぞれ10nmとし、エネルギーギャップは、分光エリプソメータ(HORIBA JOBIN YVON社UT-300)を用いて測定した。また、真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析(UPS: Ultraviolet Photoelectron Spectroscopy)装置(PHI社VersaProbe)を用いて測定した。

#### 【0122】

図8(A)は、真空準位と価電子帯上端のエネルギー差と、各層のエネルギーギャップとの差分として算出される真空準位と伝導帯下端のエネルギー差(電子親和力)から模式的に示されるバンド構造の一部である。図8(A)は、酸化物半導体層404aおよび酸化物半導体層404cと接して、酸化シリコン層を設けた場合のバンド図である。ここで、Evacは真空準位のエネルギー、EcI1およびEcI2は酸化シリコン層の伝導帯下端のエネルギー、EcS1は酸化物半導体層404aの伝導帯下端のエネルギー、EcS2は酸化物半導体層404bの伝導帯下端のエネルギー、EcS3は酸化物半導体層404cの伝導帯下端のエネルギーである。

#### 【0123】

図8(A)に示すように、酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cにおいて、伝導帯下端のエネルギーが連続的に変化する。これは、酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cを構成する元素が共通することにより、酸素が相互に拡散しやすい点からも理解される。したがって、酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cは組成が異なる層の積層体ではあるが、物性的に連続であるということもできる。

#### 【0124】

主成分を共通として積層された多層半導体層404は、各層を単に積層するのではなく連続接合(ここでは特に伝導帯下端のエネルギーが各層の間で連続的に変化するU字型の井戸構造)が形成されるように作製する。すなわち、各層の界面に捕獲中心や再結合中心のような欠陥準位を形成するような不純物が存在しないように積層構造を形成する。仮に、積層された多層半導体層の層間に不純物が混在していると、エネルギー・バンドの連続性が失われ、界面でキャリアが捕獲あるいは再結合により消滅してしまう。

#### 【0125】

なお、図8(A)では、EcS1とEcS3が同様である場合について示したが、それらが異なっていてもよい。例えば、EcS3よりもEcS1が高いエネルギーを有する場合、バンド構造の一部は、図8(B)のように示される。

#### 【0126】

例えば、EcS1 = EcS3である場合は、酸化物半導体層404aおよび酸化物半導体層404cにIn:Ga:Zn = 1:3:2、1:3:3、1:3:4、1:6:4または1:9:6(原子数比)、酸化物半導体層404bにIn:Ga:Zn = 1:1:1または3:1:2(原子数比)のIn-Ga-Zn酸化物などを用いることができる。また、EcS1 > EcS3である場合は、酸化物半導体層404aにIn:Ga:Zn = 1:6:4または1:9:6(原子数比)、酸化物半導体層404bにIn:Ga:Zn = 1:

10

20

30

40

50

: 1 : 1 または 3 : 1 : 2 (原子数比)、酸化物半導体層 404c に In : Ga : Zn = 1 : 3 : 2、1 : 3 : 3、1 : 3 : 4 (原子数比) の In - Ga - Zn 酸化物などを用いることができる。

#### 【0127】

図 8 (A)、図 8 (B) より、多層半導体層 404 における酸化物半導体層 404b がウェル (井戸) となり、多層半導体層 404 を用いたトランジスタにおいて、チャネルが酸化物半導体層 404b に形成されることがわかる。なお、多層半導体層 404 は伝導帯下端のエネルギーが連続的に変化しているため、U 字型井戸 (U Shape Well) とも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルということもできる。

10

#### 【0128】

なお、酸化物半導体層 404a および酸化物半導体層 404c と、酸化シリコン層などの絶縁層との界面近傍には、不純物や欠陥に起因した捕獲準位が形成され得る。酸化物半導体層 404a および酸化物半導体層 404c があることにより、酸化物半導体層 404b と当該捕獲準位とを遠ざけることができる。ただし、ECS1 または ECS3 と、ECS2 とのエネルギー差が小さい場合、酸化物半導体層 404b の電子が酸化物半導体層 404a または酸化物半導体層 404c を超えて捕獲準位に達することができる。マイナスの電荷となる電子が捕獲準位に捕獲されることで、トランジスタのしきい値はプラス方向にシフトしてしまう。

#### 【0129】

20

したがって、トランジスタのしきい値の変動を低減するには、ECS1 および ECS3 と、ECS2 との間にエネルギー差を設けることが必要となる。それぞれの当該エネルギー差は、0.1 eV 以上が好ましく、0.15 eV 以上がより好ましい。

#### 【0130】

なお、酸化物半導体層 404a、酸化物半導体層 404b、酸化物半導体層 404c には、結晶部が含まれることが好ましい。特に c 軸に配向した結晶を用いることでトランジスタに安定した電気特性を付与することができる。

#### 【0131】

なお、多層半導体層 404 に In - Ga - Zn 酸化物を用いる場合は、In のゲート絶縁層への拡散を防ぐために、酸化物半導体層 404c は酸化物半導体層 404b よりも In が少ない組成とすることが好ましい。

30

#### 【0132】

ソース電極 406a およびドレイン電極 406b には、酸素と結合し得る導電材料を用いることが好ましい。例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどを用いることができる。上記材料において、特に酸素と結合しやすい Ti や、後のプロセス温度が比較的高くできることなどから、融点の高い W を用いることがより好ましい。なお、酸素と結合し得る導電材料には、酸素が拡散し得る材料も含まれる。

#### 【0133】

40

酸素と結合し得る導電材料と多層半導体層を接触させると、多層半導体層中の酸素が、酸素と結合し得る導電材料側に拡散する現象が起こる。当該現象は、温度が高いほど顕著に起こる。トランジスタの作製工程には、いくつかの加熱工程があることから、上記現象により、多層半導体層のソース電極またはドレイン電極と接触した近傍の領域に酸素欠損が発生し、層中に僅かに含まれる水素と当該酸素欠損が結合することにより当該領域は n 型化する。したがって、n 型化した当該領域はトランジスタのソース領域またはドレイン領域として作用させることができる。

#### 【0134】

なお、チャネル長が極短いトランジスタを形成する場合、上記酸素欠損の発生によって n 型化した領域がトランジスタのチャネル長方向に延在することで短絡してしまうことがある。この場合、トランジスタの電気特性には、しきい値のシフトにより、実用的なゲート電圧でオンオフの制御ができない状態 (導通状態) が現れる。そのため、チャネル長が極

50

短いトランジスタを形成する場合は、ソース電極およびドレイン電極に酸素と結合しやすい導電材料を用いることが必ずしも好ましいとはいえない場合がある。

#### 【0135】

このような場合にはソース電極406aおよびドレイン電極406bには、上述した材料よりも酸素と結合しにくい導電材料を用いることが好ましい。当該導電材料としては、例えば、窒化タンタル、窒化チタン、またはルテニウムを含む材料などを用いることができる。なお、当該導電材料を酸化物半導体層404bと接触させる構成として、当該導電材料と前述した酸素と結合しやすい導電材料を積層してもよい。

#### 【0136】

第1の絶縁層402aと第3の絶縁層402c、ゲート絶縁層408には、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニアム、酸化ランタン、酸化ネオジムおよび酸化タンタルを一種以上含む絶縁層を用いることができる。また、第2の絶縁層402bには、酸化ハフニウム、酸化アルミニウム、アルミニウムシリケートなどを一種以上含む絶縁層を用いることができる。なお、第1の絶縁層402aと第3の絶縁層402cの厚さは、1nm以上30nm以下、好ましくは10nm以上20nm以下であり、第2の絶縁層402bの厚さは、1nm以上20nm以下、好ましくは5nm以上10nm以下である。

#### 【0137】

ゲート電極401とゲート電極410は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、TaおよびWなどの導電層を用いることができる。また、ゲート電極401とゲート電極410は、上記材料の積層であってもよい。また、ゲート電極401とゲート電極410には、窒素を含んだ導電層を用いてもよい。たとえば、ゲート電極401とゲート電極410に窒化チタン層上にタンゲステン層の積層、窒化タンゲステン層上にタンゲステン層の積層、窒化タンタル層上にタンゲステン層の積層などを用いることができる。

#### 【0138】

ゲート絶縁層408、およびゲート電極410上には酸化物絶縁層412が形成されてもよい。当該酸化物絶縁層には、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニアム、酸化ランタン、酸化ネオジムおよび酸化タンタルを一種以上含む絶縁層を用いることができる。また、当該酸化物絶縁層は上記材料の積層であってもよい。

#### 【0139】

ここで、酸化物絶縁層412は過剰酸素を有することが好ましい。過剰酸素を含む酸化物絶縁層とは、加熱処理などによって酸素を放出することができる酸化物絶縁層をいう。好ましくは、昇温脱離ガス分光法分析にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{19} \text{ atoms/cm}^3$ 以上である層とする。当該酸化物絶縁層から放出される酸素はゲート絶縁層408を経由して多層半導体層404のチャネル形成領域に拡散させることができることから、チャネル形成領域に形成された酸素欠損が形成された場合においても酸素を補填することができる。したがって、安定したトランジスタの電気特性を得ることができる。

#### 【0140】

半導体装置を高集積化するにはトランジスタの微細化が必須である。一方、トランジスタの微細化によりトランジスタの電気特性が悪化することが知られており、特にチャネル幅の縮小に直接起因して、オン電流は著しく低下する。

#### 【0141】

しかしながら、本発明の一態様のトランジスタでは、前述したように、酸化物半導体層404bのチャネルが形成される領域を覆うように酸化物半導体層404cが形成されており、チャネル形成層とゲート絶縁層が接しない構成となっている。そのため、チャネル形

10

20

30

40

50

成層とゲート絶縁層との界面で生じるキャリアの散乱を抑えることができ、トランジスタのオン電流を高くすることができる。

#### 【0142】

また、酸化物半導体層を真性または実質的に真性とすると、酸化物半導体層に含まれるキャリア数の減少により、電界効果移動度の低下が懸念される。しかしながら、本発明の一態様のトランジスタにおいては、酸化物半導体層に垂直方向からのゲート電界に加えて、側面方向からのゲート電界が印加される。すなわち、酸化物半導体層の全体的にゲート電界が印加されることとなり、電流は酸化物半導体層のバルクを流れる。これによって、高純度真性化による、電気特性の変動の抑制を達成しつつ、トランジスタの電界効果移動度の向上を図ることが可能となる。

10

#### 【0143】

また、本発明の一態様のトランジスタは、酸化物半導体層404bを酸化物半導体層404a上に形成することで界面準位を形成しにくくする効果や、酸化物半導体層404bを三層構造の中間層としてすることで上下からの不純物混入の影響を排除できる効果などを併せて有する。そのため、酸化物半導体層404bは酸化物半導体層404aと酸化物半導体層404cで取り囲まれた構造（また、ゲート電極410で電気的に取り囲まれた構造）となり、上述したトランジスタのオン電流の向上に加えて、しきい値の安定化や、S値を小さくすることができる。したがって、 $I_{cut}$ を下げることができ、消費電力を低減させることができる。また、トランジスタのしきい値が安定化することから、半導体装置の長期信頼性を向上させることができる。

20

#### 【0144】

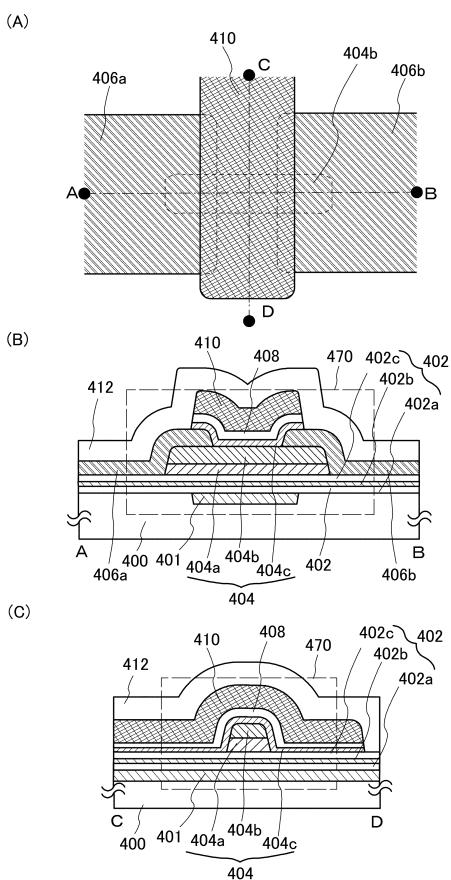

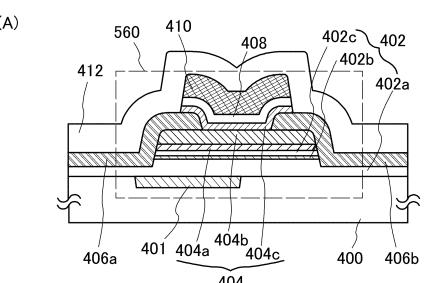

また、図9に示すトランジスタ470を用いることもできる。図9(A)乃至図9(C)は、トランジスタ470の上面図および断面図である。図9(A)は上面図であり、図9(A)に示す一点鎖線A-Bの断面が図9(B)、一点鎖線C-Dの断面が図9(C)に相当する。なお、図9(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

#### 【0145】

トランジスタ470は、ソース電極406aおよびドレイン電極406bを形成するとき、ソース電極406aおよびドレイン電極406bとなる導電層のオーバーエッチングがなく、下地絶縁層402がエッチングされていない形状となっている。

30

#### 【0146】

導電層のオーバーエッチングにより、下地絶縁層402をエッチングさせないようにするには、導電層と下地絶縁層402のエッチングでの選択比を大きくすればよい。

#### 【0147】

また、本実施の形態では、酸化物半導体層404bを酸化物半導体層404aおよび酸化物半導体層404cで挟んでいる構成であったがこれに限られず、酸化物半導体層404aおよび酸化物半導体層404cを有さず酸化物半導体層404bのみがゲート電極に電気的に取り囲まれている構成としてもよい。

#### 【0148】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

40

#### 【0149】

##### (実施の形態3)

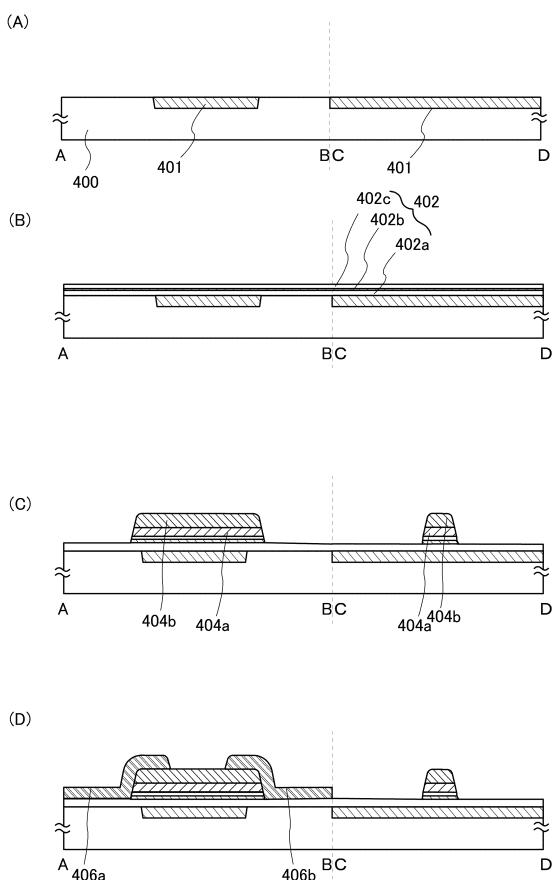

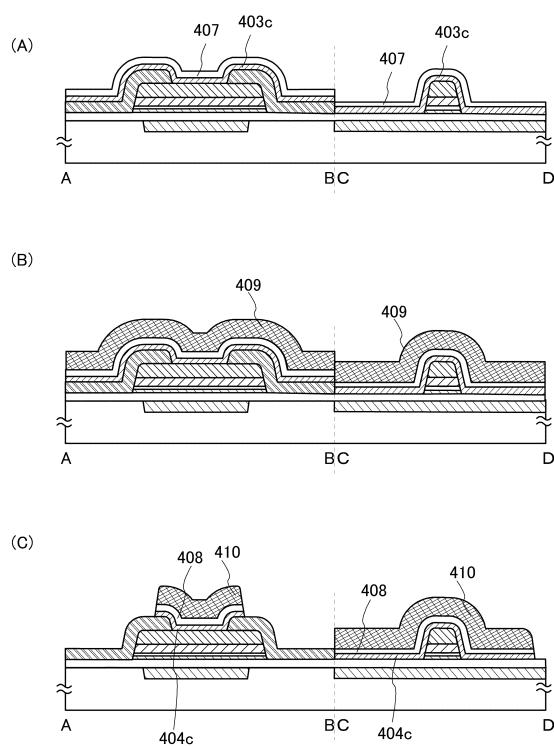

本実施の形態では、実施の形態2で説明した図7に示すトランジスタ450の作製方法について、図10および図11を用いて説明する。

#### 【0150】

まず、基板400上に線状の溝を複数本形成し、その上にAl、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta、W、またはこれらを主成分とする合金材料を用いて、導電層を堆積した後、平坦化およびエッチングしてゲート電極401を形成する（図10(A)参照）。導電層は、スパッタリング法やCVD法などにより形成するこ

50

とができる。

**【0151】**

基板400には、ガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI(Silicon On Insulator)基板などを用いることも可能であり、これらの基板上に半導体素子が設けられたものを用いてもよい。

**【0152】**

さらに第1の絶縁層402a、第2の絶縁層402b、第3の絶縁層402cよりなる下地絶縁層402を形成する(図10(B)参照)。

10

**【0153】**

なお、下地絶縁層402にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を添加してもよい。酸素を添加することによって、下地絶縁層402から多層半導体層404への酸素の供給をさらに容易にすることができる。

**【0154】**

次に、下地絶縁層402上に酸化物半導体層404a、酸化物半導体層404bをスパッタリング法、CVD法(MOCVD法、ALD法あるいはPECVD法を含む)、真空蒸着法またはパルスレーザー堆積(PLD法)を用いて形成する(図10(C)参照)。このとき、図示するように下地絶縁層402を若干過度にエッチングしてもよい。下地絶縁層402を過度にエッチングすることで、後に形成するゲート電極410で酸化物半導体層404cを覆いやすくすることができる。

20

**【0155】**

なお、酸化物半導体層404a、酸化物半導体層404bを島状に形成する際に、まず、酸化物半導体層404b上にハードマスクとなる層(たとえばタンゲステン層)およびレジストマスクを設け、ハードマスクとなる層をエッチングしてハードマスクを形成し、その後、ハードマスクを除去し、ハードマスクをマスクとして酸化物半導体層404a、酸化物半導体層404bをエッチングする。その後、レジストマスクを除去する。この時、エッチングするにつれて徐々にハードマスクが縮小していくため、自然にハードマスクの端部が丸みを帯び、曲面を有する。これに伴い、酸化物半導体層404bの形状も端部が丸みを帯び、曲面を有する。このような構成になることで、酸化物半導体層404b上に形成される、酸化物半導体層404c、ゲート絶縁層408、ゲート電極410、酸化物絶縁層412の被覆性が向上し、段切れ等の形状不良の発生を防ぐことができる。また、ソース電極406aおよびドレイン電極406bの端部に生じる恐れのある電界集中を緩和することができ、トランジスタの劣化を抑制することができる。

30

**【0156】**

また、酸化物半導体層404a、酸化物半導体層404bの積層、および後の工程で形成する酸化物半導体層404cを含めた積層において連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の装置(例えばスパッタリング装置)を用いて各層を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべく、クライオポンプのような吸着式の真空排気ポンプを用いて高真空排気( $5 \times 10^{-7}$  Paから $1 \times 10^{-4}$  Pa程度まで)できること、かつ、基板を100以上、好ましくは500以上に加熱できることが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に炭素成分や水分等を含む気体が逆流しないようにしておくことが好ましい。

40

**【0157】**

高純度真性酸化物半導体を得るために、チャンバー内を高真空排気するのみならずスパッタリングガスの高純度化も必要である。スパッタリングガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100

50

以下にまで高純度化したガスを用いることで酸化物半導体層に水分等が取り込まれることを可能な限り防ぐことができる。

#### 【0158】

酸化物半導体層404a、酸化物半導体層404b、および後の工程で形成される酸化物半導体層404cには、実施の形態2で説明した材料を用いることができる。例えば、酸化物半導体層404aにIn:Ga:Zn=1:3:4または1:3:2[原子数比]のIn-Ga-Zn酸化物、酸化物半導体層404bにIn:Ga:Zn=1:1:1[原子数比]のIn-Ga-Zn酸化物、酸化物半導体層404cにIn:Ga:Zn=1:3:4または1:3:2[原子数比]のIn-Ga-Zn酸化物を用いることができる。

#### 【0159】

また、酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cとして用いることのできる酸化物は、少なくともインジウム(In)もしくは亜鉛(Zn)を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

#### 【0160】

スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ランタノイドである、ラントン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)等がある。

#### 【0161】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn酸化物、Sn-Zn酸化物、Al-Zn酸化物、Zn-Mg酸化物、Sn-Mg酸化物、In-Mg酸化物、In-Ga酸化物、In-Ga-Zn酸化物、In-Al-Zn酸化物、In-Sn-Zn酸化物、Sn-Ga-Zn酸化物、Al-Ga-Zn酸化物、Sn-Al-Zn酸化物、In-Hf-Zn酸化物、In-La-Zn酸化物、In-Ce-Zn酸化物、In-Pr-Zn酸化物、In-Nd-Zn酸化物、In-Sm-Zn酸化物、In-Eu-Zn酸化物、In-Gd-Zn酸化物、In-Tb-Zn酸化物、In-Dy-Zn酸化物、In-Ho-Zn酸化物、In-Er-Zn酸化物、In-Tm-Zn酸化物、In-Yb-Zn酸化物、In-Lu-Zn酸化物、In-Sn-Ga-Zn酸化物、In-Hf-Ga-Zn酸化物、In-Al-Ga-Zn酸化物、In-Sn-Al-Zn酸化物、In-Sn-Hf-Zn酸化物、In-Hf-Al-Zn酸化物を用いることができる。

#### 【0162】

なお、ここで、例えば、In-Ga-Zn酸化物とは、InとGaとZnを主成分として有する酸化物という意味である。また、InとGaとZn以外の金属元素が入っていてもよい。また、本明細書においては、In-Ga-Zn酸化物で構成した層をIGZO層とも呼ぶ。

#### 【0163】

また、 $InMO_3 (ZnO)_m$ ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、MnおよびCoから選ばれた一つの金属元素または複数の金属元素を示す。また、 $In_2SnO_5 (ZnO)_n$ ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

#### 【0164】

ただし、実施の形態2に詳細を記したように、酸化物半導体層404aおよび酸化物半導体層404cは、酸化物半導体層404bよりも電子親和力が小さくなるように材料を選択する。

10

20

30

40

50

## 【0165】

なお、酸化物半導体層の形成には、スパッタリング法を用いることが好ましい。スパッタリング法としては、RFスパッタリング法、DCスパッタリング法、ACスパッタリング法等を用いることができる。特に、形成時に発生するゴミを低減でき、かつ厚さも均一とできることからDCスパッタリング法を用いることが好ましい。

## 【0166】

酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cとしてIn-Ga-Zn酸化物を用いる場合、In、Ga、Znの原子数比としては、例えば、In:Ga:Zn=1:1:1、In:Ga:Zn=2:2:1、In:Ga:Zn=3:1:2、In:Ga:Zn=1:3:2、In:Ga:Zn=1:3:4、In:Ga:Zn=1:4:3、In:Ga:Zn=1:5:4、In:Ga:Zn=1:6:6、In:Ga:Zn=2:1:3、In:Ga:Zn=1:6:4、In:Ga:Zn=1:9:6、In:Ga:Zn=1:1:4、In:Ga:Zn=1:1:2のいずれかの材料を用い、酸化物半導体層404aおよび酸化物半導体層404cの電子親和力が酸化物半導体層404bのものよりも小さくなるようにすればよい。10

## 【0167】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c (a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C (A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、(a-A)<sup>2</sup>+(b-B)<sup>2</sup>+(c-C)<sup>2</sup> r<sup>2</sup>を満たすことをいう。rとしては、例えば、0.05とすればよい。20

他の酸化物でも同様である。

## 【0168】

また、酸化物半導体層404bは、酸化物半導体層404aおよび酸化物半導体層404cよりもインジウムの含有量を多くするとよい。酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、s軌道の重なりが強くなるため、InがGaよりも多い組成となる酸化物はInがGaと同等または少ない組成となる酸化物と比較して移動度が高くなる。そのため、酸化物半導体層404bにインジウムの含有量が多い酸化物を用いることで、高い移動度のトランジスタを実現することができる。

## 【0169】

以下では、酸化物半導体層の構造について説明する。

## 【0170】

なお、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

## 【0171】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

## 【0172】

酸化物半導体層は、非単結晶酸化物半導体層と単結晶酸化物半導体層とに大別される。非単結晶酸化物半導体層とは、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor)層、多結晶酸化物半導体層、微結晶酸化物半導体層、非晶質酸化物半導体層などをいう。

## 【0173】

まずは、CAAC-OS層について説明する。

## 【0174】

CAAC-OS層は、複数の結晶部を有する酸化物半導体層の一つであり、ほとんどの結晶部は、一边が100nm未満の立方体内に収まる大きさである。したがって、CAAC-OS層に含まれる結晶部は、一边が10nm未満、5nm未満または3nm未満の立方4050

体内に収まる大きさの場合も含まれる。

**【0175】**

C AAC - OS層を透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって観察すると、明確な結晶部同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、C AAC - OS層は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0176】**

C AAC - OS層を、試料面と概略平行な方向から TEM によって観察（断面 TEM 観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C AAC - OS層の層を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、C AAC - OS層の被形成面または上面と平行に配列する。10

**【0177】**

一方、C AAC - OS層を、試料面と概略垂直な方向から TEM によって観察（平面 TEM 観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0178】**

断面 TEM 観察および平面 TEM 観察より、C AAC - OS層の結晶部は配向性を有していることがわかる。

**【0179】**

C AAC - OS層に対し、X線回折 (XRD : X-Ray Diffraction) 装置を用いて構造解析を行うと、例えば InGaZnO<sub>4</sub> の結晶を有する C AAC - OS層の out-of-plane 法による解析では、回折角 ( $2\theta$ ) が  $31^\circ$  近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (009) 面に由来することから、C AAC - OS層の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。20

**【0180】**

一方、C AAC - OS層に対し、c 軸に概略垂直な方向から X 線を入射させる in-plane 法による解析では、 $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (110) 面に由来する。InGaZnO<sub>4</sub> の単結晶酸化物半導体層であれば、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析（スキャン）を行うと、(110) 面と等価な結晶面に由来するピークが 6 本観察される。これに対し、C AAC - OS層の場合は、 $2\theta$  を  $56^\circ$  近傍に固定して スキャンした場合でも、明瞭なピークが現れない。30

**【0181】**

以上のことから、C AAC - OS層では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。したがって、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の ab 面に平行な面である。

**【0182】**

なお、結晶部は、C AAC - OS層を形成した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、C AAC - OS層の被形成面または上面の法線ベクトルに平行な方向に配向する。したがって、例えば、C AAC - OS層の形状をエッチングなどによって変化させた場合、結晶の c 軸が C AAC - OS層の被形成面または上面の法線ベクトルと平行にならないこともある。

**【0183】**

また、C AAC - OS層中の結晶化度が均一でなくてもよい。例えば、C AAC - OS層の結晶部が、C AAC - OS層の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、C AAC - OS層に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分4050

的に結晶化度の異なる領域が形成されることもある。

**【0184】**

なお、 $\text{InGaZnO}_4$  の結晶を有する CAAc - OS 層の out-of-plane 法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、CAAc - OS 層中の一部に、c 軸配向性を有さない結晶が含まれることを示している。CAAc - OS 層は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。

**【0185】**

CAAc - OS 層は、不純物濃度の低い酸化物半導体層である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体層の主成分以外の元素である。特に、シリコンなどの、酸化物半導体層を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体層から酸素を奪うことで酸化物半導体層の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体層内部に含まれると、酸化物半導体層の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体層に含まれる不純物は、キャリア捕獲中心やキャリア発生源となる場合がある。

**【0186】**

また、CAAc - OS 層は、欠陥準位密度の低い酸化物半導体層である。例えば、酸化物半導体層中の酸素欠損は、キャリア捕獲中心となることや、水素を捕獲することによってキャリア発生源となることがある。

**【0187】**

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体層は、キャリア発生源が少ないとため、キャリア密度を低くすることができます。したがって、当該酸化物半導体層を用いたトランジスタは、しきい値がマイナスとなる電気特性（ノーマリーオンともいう。）になることが多い。また、高純度真性または実質的に高純度真性である酸化物半導体層は、キャリア捕獲中心が少ないとため、当該酸化物半導体層を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体層のキャリア捕獲中心に捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体層を用いたトランジスタは、電気特性が不安定となる場合がある。

**【0188】**

また、CAAc - OS 層を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

**【0189】**

次に、微結晶酸化物半導体層について説明する。

**【0190】**

微結晶酸化物半導体層は、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体層に含まれる結晶部は、 $1\text{ nm}$  以上  $100\text{ nm}$  以下、または  $1\text{ nm}$  以上  $10\text{ nm}$  以下の大きさであることが多い。特に、 $1\text{ nm}$  以上  $10\text{ nm}$  以下、または  $1\text{ nm}$  以上  $3\text{ nm}$  以下の微結晶であるナノ結晶（nc : nanocrystalline）を有する酸化物半導体層を、nc - OS (nanocrystalline Oxide Semiconductor) 層と呼ぶ。また、nc - OS 層は、例えば、TEMによる観察像では、結晶粒界を明確に確認できない場合がある。

**【0191】**

nc - OS 層は、微小な領域（例えば、 $1\text{ nm}$  以上  $10\text{ nm}$  以下の領域、特に  $1\text{ nm}$  以上  $3\text{ nm}$  以下の領域）において原子配列に周期性を有する。また、nc - OS 層は、異なる結晶部間で結晶方位に規則性が見られない。そのため、層全体で配向性が見られない。したがって、nc - OS 層は、分析方法によっては、非晶質酸化物半導体層と区別が付かな

10

20

30

40

50

い場合がある。例えば、n c - O S 層に対し、結晶部よりも大きい径の X 線を用いる X R D 装置を用いて構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、n c - O S 層に対し、結晶部よりも大きいプローブ径（例えば 50 nm 以上）の電子線を用いる電子線回折（制限視野電子線回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S 層に対し、結晶部の大きさと近いか結晶部より小さいプローブ径（例えば 1 nm 以上 30 nm 以下）の電子線を用いる電子線回折（ナノビーム電子線回折ともいう。）を行うと、スポットが観測される。また、n c - O S 層に対しナノビーム電子線回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、n c - O S 層に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

#### 【 0 1 9 2 】

n c - O S 層は、非晶質酸化物半導体層よりも規則性の高い酸化物半導体層である。そのため、n c - O S 層は、非晶質酸化物半導体層よりも欠陥準位密度が低くなる。ただし、n c - O S 層は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 層は、C A A C - O S 層と比べて欠陥準位密度が高くなる。

#### 【 0 1 9 3 】

なお、酸化物半導体層は、例えば、非晶質酸化物半導体層、微結晶酸化物半導体層、C A A C - O S 層のうち、二種以上を有する積層であってもよい。

#### 【 0 1 9 4 】

C A A C - O S 層は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって形成することができる。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域が a - b 面から劈開し、a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、平板状またはペレット状のスパッタリング粒子は帶電しているためプラズマ中で凝集せず、結晶状態を維持したまま基板に到達し、C A A C - O S 層を形成することができる。

#### 【 0 1 9 5 】

酸化物半導体層 4 0 4 b の形成後に、第 1 の加熱処理を行ってもよい。第 1 の加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。また、第 1 の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。第 1 の加熱処理によって、酸化物半導体層 4 0 4 b の結晶性を高め、さらに下地絶縁層 4 0 2、酸化物半導体層 4 0 4 a から水素や水などの不純物を除去することができる。なお、酸化物半導体層 4 0 4 b を形成するエッチングの前に第 1 の加熱工程を行ってもよい。

#### 【 0 1 9 6 】

次に、酸化物半導体層 4 0 4 a および酸化物半導体層 4 0 4 b 上にソース電極 4 0 6 a およびドレイン電極 4 0 6 b となる第 1 の導電層を形成する。第 1 の導電層としては、A l、C r、C u、T a、T i、M o、W、またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタリング法などにより 100 nm のチタン層を形成する。また C V D 法によりタンゲステン層を形成してもよい。

#### 【 0 1 9 7 】

次に、第 1 の導電層を酸化物半導体層 4 0 4 b 上で分断するようにエッチングし、ソース電極 4 0 6 a およびドレイン電極 4 0 6 b を形成する（図 10 (D) 参照）。

#### 【 0 1 9 8 】

次に、酸化物半導体層 4 0 4 b、ソース電極 4 0 6 a およびドレイン電極 4 0 6 b 上に、酸化物半導体層 4 0 3 c を形成する。

#### 【 0 1 9 9 】

なお、酸化物半導体層 4 0 3 c を形成後に第 2 の加熱処理を行ってもよい。第 2 の加熱処理

10

20

30

40

50

理は、第1の加熱処理と同様の条件で行うことができる。第2の加熱処理により、酸化物半導体層403cから水素や水などの不純物を除去することができる。また、酸化物半導体層404aおよび酸化物半導体層404bから、さらに水素や水などの不純物を除去することができる。

#### 【0200】

次に、酸化物半導体層403c上にゲート絶縁層408となる絶縁層407を形成する(図11(A)参照)。絶縁層407は、スパッタリング法、化学気相堆積(CVD)法(有機金属化学堆積(MOCVD)法、原子層成膜(ALD)法あるいはプラズマ化学気相堆積(PECVD)法を含む)、真空蒸着法またはパルスレーザー堆積(PLD)法などを用いて形成することができる。

10

#### 【0201】

次に、絶縁層407上にゲート電極410となる第2の導電層409を形成する(図11(B)参照)。第2の導電層409としては、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta、W、またはこれらを主成分とする合金材料を用いることができる。第2の導電層409は、スパッタリング法やCVD法などにより形成することができる。また、第2の導電層409としては、窒素を含んだ導電層を用いてもよく、上記導電層と窒素を含んだ導電層の積層を用いてもよい。

#### 【0202】

次に、ゲート電極410を形成するためのレジストマスクを用いて、第2の導電層409を選択的にエッチングし、ゲート電極410を形成する(図11(C)参照)。なお、図7(C)に示すように、ゲート電極410は、酸化物半導体層404bを電気的に取り囲むように形成される。

20

#### 【0203】

続いて、上記レジストマスクまたはゲート電極410をマスクとして絶縁層407を選択的にエッチングし、ゲート絶縁層408を形成する。

#### 【0204】

続いて、上記レジストマスクまたはゲート電極410をマスクとして酸化物半導体層403cをエッチングし、酸化物半導体層404cを形成する。

#### 【0205】

つまり、酸化物半導体層404cの上端部はゲート絶縁層408の下端部と一致し、ゲート絶縁層408の上端部はゲート電極410の下端部と一致する。なお、ゲート電極410をマスクとしてゲート絶縁層408および酸化物半導体層404cを形成しているがこれに限られず、第2の導電層409の形成前にゲート絶縁層408および酸化物半導体層404cを形成してもよい。

30

#### 【0206】

次に、ソース電極406a、ドレイン電極406b、ゲート電極410上に酸化物絶縁層412を形成する(図7(B)、図7(C)参照)。酸化物絶縁層412は、第1の絶縁層402aと同様の材料、方法を用いて形成することができる。酸化物絶縁層412としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタル、もしくは窒素を含む酸化物絶縁層を用いるとよい。酸化物絶縁層412は、スパッタリング法、化学気相堆積(CVD)法(有機金属化学堆積(MOCVD)法、原子層成膜(ALD)法あるいはプラズマ化学気相堆積(PECVD)法を含む)、真空蒸着法またはパルスレーザー堆積(PLD)法を用いて形成することができ、多層半導体層404に対し酸素を供給できるよう過剰に酸素を含む層とすることが好ましい。

40

#### 【0207】

次に、第3の加熱処理を行ってもよい。第3の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第3の加熱処理により、下地絶縁層402、ゲート絶縁層408、酸化物絶縁層412から過剰酸素が放出されやすくなり、多層半導体層404の酸素欠損

50

を低減することができる。

**【0208】**

次に、第4の加熱処理を行う。第4の加熱処理は、125以上450以下、好ましくは150以上300以下の温度で、ゲート電極401の電位をソース電極やドレイン電極の電位より高い状態を、1秒以上、代表的には1分以上維持することで、多層半導体層404からゲート電極401に向かって、必要とする電子が移動し、そのうちのいくらかは第2の絶縁層402bの内部あるいは界面にある電子捕獲準位に捕獲される。このようにして、捕獲される電子の量を制御して、しきい値の増加の程度を制御することができる。

**【0209】**

以上の工程で、図7に示すトランジスタ450を作製することができる。

**【0210】**

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

**【0211】**

(実施の形態4)

本実施の形態では、プレナー構造のトランジスタについて説明する。

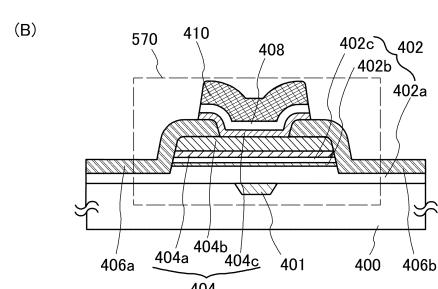

**【0212】**

図12(A)乃至図12(C)は、本発明の一態様のトランジスタの上面図および断面図である。図12(A)は上面図であり、図12(A)に示す一点鎖線A-Bの断面が図12(B)、一点鎖線C-Dの断面が図12(C)に相当する。なお、図12(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線A-B方向をチャネル長方向、一点鎖線C-D方向をチャネル幅方向と呼称する場合がある。

**【0213】**

図12(A)乃至図12(C)に示すトランジスタ550は、基板400上の下地絶縁層402と、下地絶縁層402上の酸化物半導体層404aおよび酸化物半導体層404bと、酸化物半導体層404aおよび酸化物半導体層404b上のソース電極406aおよびドレイン電極406bと、下地絶縁層402、酸化物半導体層404a、酸化物半導体層404b、ソース電極406aおよびドレイン電極406bと接する酸化物半導体層404cと、酸化物半導体層404c上のゲート絶縁層408と、ゲート絶縁層408上のゲート電極410と、ソース電極406a、ドレイン電極406b、およびゲート電極410上の酸化物絶縁層412と、を有する。また、下地絶縁層402は、第1の絶縁層402a、第2の絶縁層402b、第3の絶縁層402cを有し、実施の形態1で述べた電子捕獲層として機能する。また、酸化物半導体層404a、酸化物半導体層404b、および酸化物半導体層404cを総称して多層半導体層404と呼称する。

**【0214】**

実施の形態2のトランジスタ450と本実施の形態のトランジスタ550の相違点は、チャネル長およびチャネル幅がいずれも、多層半導体層404の厚さの2倍以上、代表的には10倍以上ということである。

**【0215】**

なお、チャネル長とは、上面図において、半導体層とゲート電極とが重なる領域における、ソース(ソース領域またはソース電極)とドレイン(ドレン領域またはドレイン電極)との距離をいう。すなわち、図12(A)では、チャネル長は、酸化物半導体層404bとゲート電極410とが重なる領域における、ソース電極406aとドレイン電極406bとの距離となる。チャネル幅とは、半導体層とゲート電極とが重なる領域における、ソースとドレインとが平行に向かい合っている長さをいう。すなわち、図12(A)では、チャネル幅は、酸化物半導体層404bとゲート電極410とが重なる領域における、ソース電極406aとドレイン電極406bとが平行に向かい合っている長さをいう。

**【0216】**

また、図13(A)に示すトランジスタ560を用いることもできる。図13(A)は、

10

20

30

40

50

トランジスタ560の断面図である。トランジスタ550とトランジスタ560の違いは、ゲート電極401がトランジスタ560は、ソース電極406aとは重なるが、ドレイン電極406bと重ならないことである。このため、ゲート電極401とドレイン電極406bとの寄生容量を低減できる。逆に、ゲート電極401を、ドレイン電極406bとは重なるが、ソース電極406aと重ならないように配置してもよい。

#### 【0217】

また、図13(B)に示すトランジスタ570を用いることもできる。図13(B)は、トランジスタ570の断面図である。トランジスタ560とトランジスタ570の違いは、ゲート電極401が、トランジスタ570は、ソース電極406a、ドレイン電極406bのいずれとも重ならないことである。このため、ゲート電極401とソース電極406a、ドレイン電極406bとの寄生容量を低減できる。 $I_{cut}$ を低減するには、チャネルの一部でもしきい値が高ければよいので、このような構成とすることもできる。

10

#### 【0218】

また、本実施の形態では、酸化物半導体層404bを酸化物半導体層404aおよび酸化物半導体層404cで挟んでいる構成であったがこれに限られず、酸化物半導体層404aおよび酸化物半導体層404cを有さず酸化物半導体層404bのみがある構成としてもよい。あるいは、酸化物半導体層404a、酸化物半導体層404b、酸化物半導体層404cのいずれか1つあるいいは2つだけで構成されてもよい。

#### 【0219】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

20

#### 【0220】

##### (実施の形態5)

本実施の形態では、本発明の一態様のトランジスタを利用した回路の一例について、図面を参照して説明する。

#### 【0221】

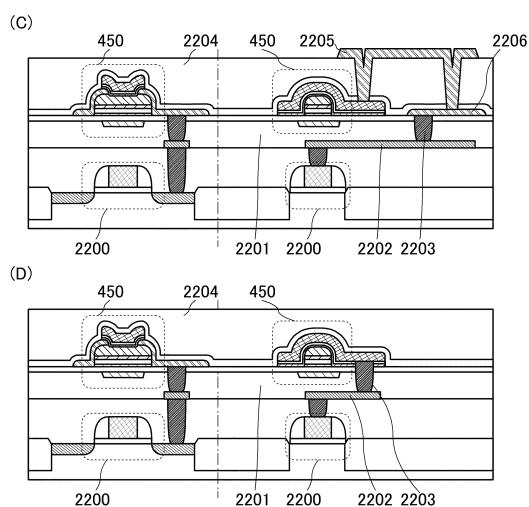

図14(A)、図14(B)に半導体装置の回路図を、図14(C)、図14(D)に半導体装置の断面図をそれぞれ示す。図14(C)、図14(D)はそれぞれ、左側にトランジスタ450のチャネル長方向の断面図を示し、右側にチャネル幅方向の断面図を示している。また回路図には、酸化物半導体が適用されたトランジスタであることを明示するために、「OS」の記載を付している。

30

#### 【0222】

図14(C)、図14(D)に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ2200を有し、上部に第2の半導体材料を用いたトランジスタを有する。ここでは、第2の半導体材料を用いたトランジスタとして、実施の形態2で例示したトランジスタ450を適用した例について説明する。

#### 【0223】

ここで、第1の半導体材料と第2の半導体材料は異なる禁制帯幅を持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等など)とし、第2の半導体材料を実施の形態2で説明した酸化物半導体とすることができる。酸化物半導体以外の材料として単結晶シリコンなどを用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が低い。

40

#### 【0224】

ここでは、トランジスタ2200がpチャネル型のトランジスタであるものとして説明するが、nチャネル型のトランジスタを用いて異なる回路を構成できることは言うまでもない。また、酸化物半導体を用いた実施の形態2に示すようなトランジスタを用いる他は、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

#### 【0225】

50

図14(A)、図14(C)、図14(D)に示す構成は、pチャネル型のトランジスタとnチャネル型のトランジスタを直列に接続し、且つ、それぞれのゲートを接続した、いわゆるCMOS回路の構成例について示している。

#### 【0226】

本発明の一態様の酸化物半導体が適用されたトランジスタは、オン電流が高められているため、回路の高速動作が可能となる。

#### 【0227】

図14(C)に示す構成では、トランジスタ2200の上部に、絶縁層2201を介してトランジスタ450が設けられている。また、トランジスタ2200とトランジスタ450の間には複数の配線2202が設けられている。また各種絶縁層に埋め込まれた複数のプラグ2203により、上層と下層にそれぞれ設けられた配線や電極が電気的に接続されている。また、トランジスタ450を覆う絶縁層2204と、絶縁層2204上に配線2205と、トランジスタの一対の電極と同一の導電層を加工して形成された配線2206と、が設けられている。

10

#### 【0228】

このように、2つのトランジスタを積層することにより、回路の占有面積が低減され、より高密度に複数の回路を配置することができる。

#### 【0229】

図14(C)では、トランジスタ450のソースまたはドレインの一方と、トランジスタ2200のソースまたはドレインの一方が配線2202やプラグ2203によって電気的に接続されている。また、トランジスタ450のゲートは、配線2205、配線2206、プラグ2203および配線2202などを経由して、トランジスタ2200のゲートと電気的に接続されている。

20

#### 【0230】

図14(D)に示す構成では、トランジスタ450のゲート絶縁層にプラグ2203を埋め込むための開口部が設けられ、トランジスタ450のゲートとプラグ2203とが接する構成となっている。このような構成とすることで回路の集積化が容易であるのに加え、図14(C)に示す構成と比較して経由する配線やプラグの数や長さを低減できるため、回路をより高速に動作させることができる。

30

#### 【0231】

ここで、図14(C)、図14(D)に示す構成において、トランジスタ450やトランジスタ2200の電極の接続構成を異ならせることにより、様々な回路を構成することができる。例えば図14(B)に示すように、それぞれのトランジスタのソースとドレインを接続した回路構成とすることにより、いわゆるアナログスイッチとして機能させることができる。

#### 【0232】

また、先の実施の形態のトランジスタを用いて、対象物の情報を読み取るイメージセンサ機能を有する半導体装置を作製することができる。

#### 【0233】

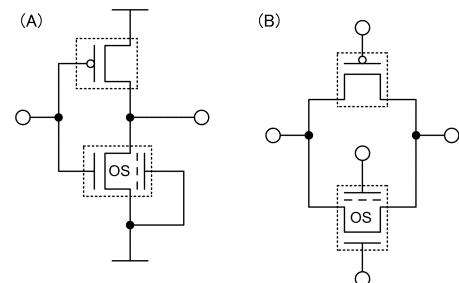

図15に、イメージセンサ機能を有する半導体装置の等価回路の一例を示す。

40

#### 【0234】

フォトダイオード602は、一方の電極がフォトダイオードリセット信号658に、他方の電極がトランジスタ640の一方のゲートに電気的に接続されている。トランジスタ640は、ソースまたはドレインの一方がフォトセンサ基準信号線672に、ソースまたはドレインの他方がトランジスタ656のソースまたはドレインの一方に電気的に接続されている。トランジスタ656は、一方のゲートがゲート信号線659に、ソースまたはドレインの他方がフォトセンサ出力信号線671に電気的に接続されている。また、トランジスタ640の他方のゲート(バックゲート)およびトランジスタ656の他方のゲート(バックゲート)は接地線673に接続される。

#### 【0235】

50

フォトダイオード 602 には、例えば、p 型の導電型を有する半導体層と、高抵抗な(i 型の導電型を有する)半導体層と、n 型の導電型を有する半導体層を積層する p i n 型のフォトダイオードを適用することができる。

#### 【0236】

フォトダイオード 602 に入射する光を検出することによって、被検出物の情報を読み取ることができる。なお、被検出物の情報を読み取る際に、バックライトなどの光源を用いることができる。

#### 【0237】

なお、トランジスタ 640 およびトランジスタ 656 には、先の実施の形態のいずれかで一例を示した、酸化物半導体にチャネルが形成されるトランジスタを用いることができる。10

。図 15 では、トランジスタ 640 およびトランジスタ 656 が、酸化物半導体を含むことを明確に判明できるよう、トランジスタの記号に「OS」と付記している。

#### 【0238】

トランジスタ 640 およびトランジスタ 656 は、上記実施の形態で一例を示したトランジスタであり、酸化物半導体層をゲート電極によって電気的に囲い込む構成を有することが好ましい。また、端部が丸みを帯び、曲面を有する酸化物半導体層を用いたトランジスタであると、酸化物半導体層上に形成される層の被覆性を向上させることができる。また、ソース電極およびドレイン電極の端部に生じる恐れのある電界集中を緩和することができ、トランジスタの劣化を抑制することができる。よって、トランジスタ 640 およびトランジスタ 656 は、電気的特性変動が抑制された電気的に安定なトランジスタである。20

該トランジスタを含むことで、図 15 で示すイメージセンサ機能を有する半導体装置として信頼性の高い半導体装置を提供することができる。

#### 【0239】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

#### 【0240】

##### (実施の形態 6)

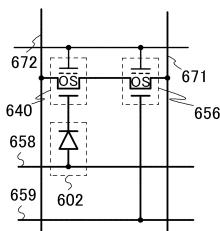

本実施の形態では、少なくとも先の実施の形態で説明したトランジスタを用いることができる、先の実施の形態で説明した記憶装置を含む CPU について説明する。

#### 【0241】

図 16 は、実施の形態 2 で説明したトランジスタを少なくとも一部に用いた CPU の一例の構成を示すブロック図である。

#### 【0242】

図 16 に示す CPU は、基板 1190 上に、ALU1191 (ALU: Arithmetic logic unit、演算回路)、ALUコントローラ 1192、インストラクションデコーダ 1193、インタラプトコントローラ 1194、タイミングコントローラ 1195、レジスタ 1196、レジスタコントローラ 1197、バスインターフェース 1198 (Bus I/F)、書き換え可能な ROM 1199、および ROM インターフェース 1189 (ROM I/F) を有している。基板 1190 は、半導体基板、SOI 基板、ガラス基板などを用いる。ROM 1199 および ROM インターフェース 1189 は、別チップに設けてよい。もちろん、図 16 に示す CPU は、その構成を簡略化して示した一例にすぎず、実際の CPU はその用途によって多種多様な構成を有している。例えば、図 16 に示す CPU または演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、CPU が内部演算回路やデータバスで扱えるビット数は、例えば 8 ビット、16 ビット、32 ビット、64 ビットなどとすることができます。

#### 【0243】

バスインターフェース 1198 を介して CPU に入力された命令は、インストラクションデコーダ 1193 に入力され、デコードされた後、ALU コントローラ 1192、インタラプトコントローラ 1194、レジスタコントローラ 1197、タイミングコントローラ40

50

1195に入力される。

**【0244】**

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行う。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

**【0245】**

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、内部クロック信号CLK2を上記各種回路に供給する。

**【0246】**

図16に示すCPUでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。あるいは、キャッシュメモリに用いてもよい。

**【0247】**

図16に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

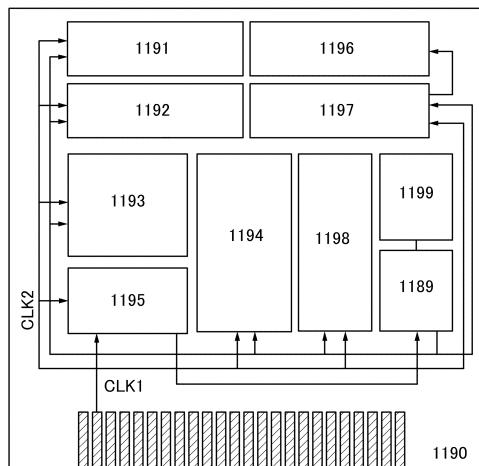

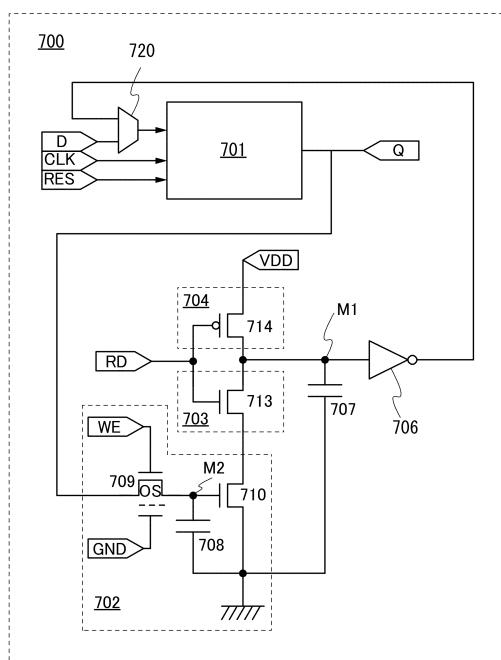

**【0248】**

図17は、レジスタ1196として用いることのできる記憶素子の回路図の一例である。記憶素子700は、電源遮断で記憶データが揮発する回路701と、電源遮断で記憶データが揮発しない回路702と、スイッチ703と、スイッチ704と、論理素子706と、容量素子707と、選択機能を有する回路720と、を有する。回路702は、容量素子708と、トランジスタ709と、トランジスタ710と、を有する。なお、記憶素子700は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していても良い。

**【0249】**

ここで、回路702には、先の実施の形態で説明したトランジスタを用いることができる。記憶素子700への電源電圧の供給が停止した際、回路702のトランジスタ709の両方のゲート（第1ゲートおよび第2ゲート）には接地電位（GND）が入力される構成とする。例えば、トランジスタ709のゲートが抵抗等の負荷を介して接地される構成とする。実施の形態1で説明したように、電子捕獲層に電子を捕獲せしめることでしきい値が増大したトランジスタ709は、Icutがきわめて低く、容量素子708に蓄積された電荷が長期間保持される。

**【0250】**

スイッチ703は、一導電型（例えば、nチャネル型）のトランジスタ713を用いて構成され、スイッチ704は、一導電型とは逆の導電型（例えば、pチャネル型）のトランジスタ714を用いて構成した例を示す。ここで、スイッチ703の第1の端子はトランジスタ713のソースとドレインの一方に対応し、スイッチ703の第2の端子はトラン

10

20

30

40

50

ジスタ713のソースとドレインの他方に対応し、スイッチ703はトランジスタ713のゲートに入力される制御信号RDによって、第1の端子と第2の端子の間の導通または非導通（つまり、トランジスタ713のオン状態またはオフ状態）が選択される。スイッチ704の第1の端子はトランジスタ714のソースとドレインの一方に対応し、スイッチ704の第2の端子はトランジスタ714のソースとドレインの他方に対応し、スイッチ704はトランジスタ714のゲートに入力される制御信号RDによって、第1の端子と第2の端子の間の導通または非導通（つまり、トランジスタ714のオン状態またはオフ状態）が選択される。

#### 【0251】

トランジスタ709のソースとドレインの一方は、容量素子708の一対の電極のうちの一方、およびトランジスタ710のゲートと電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ710のソースとドレインの一方は、低電位電源を供給することのできる配線（例えばGND線）に電気的に接続され、他方は、スイッチ703の第1の端子（トランジスタ713のソースとドレインの一方）と電気的に接続される。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）はスイッチ704の第1の端子（トランジスタ714のソースとドレインの一方）と電気的に接続される。スイッチ704の第2の端子（トランジスタ714のソースとドレインの他方）は電源電位VDDを供給することのできる配線と電気的に接続される。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）と、スイッチ704の第1の端子（トランジスタ714のソースとドレインの一方）と、論理素子706の入力端子と、容量素子707の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子707の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子707の一対の電極のうちの他方は、低電位電源を供給することのできる配線（例えばGND線）と電気的に接続される。容量素子708の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子708の一対の電極のうちの他方は、低電位電源を供給することのできる配線（例えばGND線）と電気的に接続される。

#### 【0252】

なお、容量素子707および容量素子708は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

#### 【0253】

トランジスタ709の第1ゲート（第1のゲート電極）には、制御信号WEが入力される。なお、トランジスタ709の第2ゲート（第2のゲート電極）の電位は、GNDに保持される。スイッチ703およびスイッチ704は、制御信号WEとは異なる制御信号RDによって第1の端子と第2の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第1の端子と第2の端子の間が導通状態のとき他方のスイッチの第1の端子と第2の端子の間は非導通状態となる。

#### 【0254】

トランジスタ709のソースとドレインの他方には、回路701に保持されたデータに対応する信号が入力される。図17では、回路701から出力された信号が、トランジスタ709のソースとドレインの他方に入力される例を示した。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）から出力される信号は、論理素子706によってその論理値が反転された反転信号となり、回路720を介して回路701に入力される。

#### 【0255】

なお、図17では、スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）から出力される信号は、論理素子706および回路720を介して回路701に入力する例を示したがこれに限定されない。スイッチ703の第2の端子（トランジ

10

20

30

40

50

タ713のソースとドレインの他方)から出力される信号が、論理値を反転させられることなく、回路701に入力されてもよい。例えば、回路701内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)から出力される信号を当該ノードに入力することができる。

#### 【0256】

図17におけるトランジスタ709は、実施の形態2で説明したトランジスタを用いることができる。第1ゲートには制御信号WEを入力し、第2ゲートには回路で最低の電位(例えばGND)を入力すればよい。

#### 【0257】

また、図17において、記憶素子700に用いられるトランジスタのうち、トランジスタ709以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子700に用いられるトランジスタ全てを、チャネルが酸化物半導体層で形成されるトランジスタとすることもできる。または、記憶素子700は、トランジスタ709以外にも、チャネルが酸化物半導体層で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることもできる。

#### 【0258】

図17における回路701には、例えばフリップフロップ回路を用いることができる。また、論理素子706としては、例えばインバータやクロックドインバータ等を用いることができる。

#### 【0259】

本発明の一態様における半導体装置では、記憶素子700に電源電圧が供給されない間は、回路701に記憶されていたデータを、回路702に設けられた容量素子708によって保持することができる。

#### 【0260】

また、酸化物半導体層にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体層にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ709として用いることによって、記憶素子700に電源電圧が供給されない間も容量素子708に保持された信号は長期間にわたり保たれる。こうして、記憶素子700は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。

#### 【0261】

また、スイッチ703およびスイッチ704を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路701が元のデータを保持しなおすまでの時間を短くすることができる。

#### 【0262】

また、回路702において、容量素子708によって保持された信号はトランジスタ710のゲートに入力される。そのため、記憶素子700への電源電圧の供給が再開された後、容量素子708によって保持された信号を、トランジスタ710の状態(オン状態、またはオフ状態)に変換して、回路702から読み出すことができる。それ故、容量素子708に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

#### 【0263】

このような記憶素子700を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰す

10

20

30

40

50

ることができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる。

#### 【0264】

本実施の形態では、記憶素子700をCPUに用いる例として説明したが、記憶素子700は、DSP(Digital Signal Processor)、カスタムLSI、PLD(Programmable Logic Device)等のLSI、RF-ID(Radio Frequency Identification)にも応用可能である。

#### 【0265】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

10

#### 【0266】

(実施の形態7)

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図18に示す。

20

#### 【0267】

図18(A)は携帯型ゲーム機であり、筐体501、筐体502、表示部503、表示部504、マイクロフォン505、スピーカー506、操作キー507、スタイルス508等を有する。なお、図18(A)に示した携帯型ゲーム機は、2つの表示部503と表示部504とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

#### 【0268】

30

図18(B)は携帯データ端末であり、第1筐体511、第2筐体512、第1表示部513、第2表示部514、接続部515、操作キー516等を有する。第1表示部513は第1筐体511に設けられており、第2表示部514は第2筐体512に設けられている。そして、第1筐体511と第2筐体512とは、接続部515により接続されており、第1筐体511と第2筐体512の間の角度は、接続部515により変更が可能である。第1表示部513における映像を、接続部515における第1筐体511と第2筐体512との間の角度に従って、切り替える構成としても良い。また、第1表示部513および第2表示部514の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

40

#### 【0269】

図18(C)はノート型パーソナルコンピュータであり、筐体521、表示部522、キーボード523、ポインティングデバイス524等を有する。

#### 【0270】

図18(D)は電気冷凍冷蔵庫であり、筐体531、冷蔵室用扉532、冷凍室用扉533等を有する。

#### 【0271】

図18(E)はビデオカメラであり、第1筐体541、第2筐体542、表示部543、

50

操作キー 544、レンズ 545、接続部 546 等を有する。操作キー 544 およびレンズ 545 は第1筐体 541 に設けられており、表示部 543 は第2筐体 542 に設けられている。そして、第1筐体 541 と第2筐体 542 とは、接続部 546 により接続されており、第1筐体 541 と第2筐体 542 の間の角度は、接続部 546 により変更が可能である。表示部 543 における映像を、接続部 546 における第1筐体 541 と第2筐体 542 の間の角度に従って切り替える構成としても良い。

#### 【0272】

図18(F)は普通自動車であり、車体 551、車輪 552、ダッシュボード 553、ライト 554 等を有する。

#### 【0273】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【参考例】

#### 【0274】

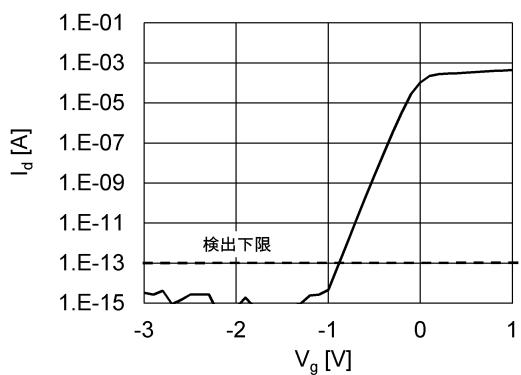

本参考例では、実施の形態1で示した  $1 \text{ yA} / \mu\text{m}$  以下という低い  $I_{cut}$  密度について、トランジスタを作製してオフ電流を求めた結果について説明する。使用した参考例トランジスタの構造は図7、図9、図10に示す、トランジスタ 450 と同様の構成である。ただし、参考例トランジスタは、ゲート絶縁層に電子捕獲層としての機能がない。

#### 【0275】

はじめに、参考例試料の作製方法について示す。

#### 【0276】

まず、シリコン基板上に下地絶縁層となる厚さ 300 nm の酸化窒化シリコン(SiON)層を形成した。酸化窒化シリコン層は、スパッタリング法によりアルゴンおよび酸素(アルゴン:酸素 = 25 sccm : 25 sccm)混合雰囲気下において、圧力 0.4 Pa、電源電力(電源出力) 5.0 kW を印加し、シリコン基板とターゲットとの間の距離を 60 mm、基板温度 100 の条件によって形成した。

#### 【0277】

酸化窒化シリコン層表面を研磨処理後、厚さ 20 nm の第1の酸化物半導体層と厚さ 15 nm の酸化物半導体層を積層して形成した。形成条件は、第1の酸化物半導体層は In : Ga : Zn = 1 : 3 : 2 (原子数比) の酸化物ターゲットを用いたスパッタリング法によりアルゴンおよび酸素(アルゴン:酸素 = 30 sccm : 15 sccm)混合雰囲気下において、圧力 0.4 Pa、電源電力 0.5 kW を印加し、ターゲットと基板の間の距離を 60 mm、基板温度 200 として形成し、第2の酸化物半導体層は In : Ga : Zn = 1 : 1 : 1 (原子数比) の酸化物ターゲットを用いたスパッタリング法によりアルゴンおよび酸素(アルゴン:酸素 = 30 sccm : 15 sccm)混合雰囲気下において、圧力 0.4 Pa、電源電力 0.5 kW を印加し、ターゲットと基板の間の距離を 60 mm、基板温度 300 として形成した。なお、第1の酸化物半導体層および第2の酸化物半導体層は、大気曝露せずに連続形成を行った。

#### 【0278】

続いて、加熱処理を行った。加熱処理は窒素雰囲気下、450 で 1 時間行った後、酸素雰囲気下、450 で行った。

#### 【0279】

続いて、第1の酸化物半導体層および第2の酸化物半導体層を、ICP (Inductive Coupled Plasma: 誘導結合型プラズマ) エッチング法により、三塩化ホウ素および塩素(BCl<sub>3</sub> : Cl<sub>2</sub> = 60 sccm : 20 sccm) 雰囲気下、電源電力 450 W、バイアス電力 100 W、圧力 1.9 Pa においてエッチングして島状の第1の酸化物半導体層および第2の酸化物半導体層に加工した。

#### 【0280】

続いて、第1の酸化物半導体層および第2の酸化物半導体層上に、ソース電極およびドレイン電極となるタンゲステン層を厚さ 100 nm 形成した。形成条件は、タンゲステンタ

10

20

30

40

50

ターゲットを用いたスパッタリング法によりアルゴン ( $A_r = 80 \text{ sccm}$ ) 霧囲気下において、圧力 0.8 Pa、電源電力(電源出力) 1.0 kW を印加し、シリコン基板とターゲットとの間の距離を 60 mm、基板温度 230 の条件によって形成した。

#### 【0281】

次に、タンゲステン層上にレジストマスクを形成して、エッチングを行った。エッチングは、ICPエッチング法により、四弗化炭素、塩素および酸素 ( $CF_4 : Cl_2 : O_2 = 45 \text{ sccm} : 45 \text{ sccm} : 55 \text{ sccm}$ ) 混合霧囲気下、電源電力 3000 W、バイアス電力 110 W、圧力 0.67 Pa にて第1のエッチングを行い、その後、酸素 ( $O_2 = 100 \text{ sccm}$ ) 霧囲気下、電源電力 2000 W、バイアス電力 0 W、圧力 3.0 Pa にて第2のエッチングを行い、さらにその後、四弗化炭素、塩素および酸素 ( $CF_4 : Cl_2 : O_2 = 45 \text{ sccm} : 45 \text{ sccm} : 55 \text{ sccm}$ ) 混合霧囲気下、電源電力 3000 W、バイアス電力 110 W、圧力 0.67 Pa にて第3のエッチングを行い、ソース電極およびドレイン電極を形成した。

10

#### 【0282】

次に、第2の酸化物半導体層、ソース電極およびドレイン電極上に厚さ 5 nm の第3の酸化物半導体層を形成した。形成条件は、In : Ga : Zn = 1 : 3 : 2 (原子数比) の酸化物ターゲットを用いたスパッタリング法によりアルゴンおよび酸素 (アルゴン : 酸素 = 30 sccm : 15 sccm) 混合霧囲気下において、圧力 0.4 Pa、電源電力 0.5 kW を印加し、ターゲットと基板の間の距離を 60 mm、基板温度 200 とした。

20

#### 【0283】

第3の酸化物半導体層を形成後、CVD法によりゲート絶縁層となる 10 nm の酸化窒化シリコン層を、シランおよび一酸化二窒素 ( $SiH_4 : N_2O = 1 \text{ sccm} : 800 \text{ sccm}$ ) 混合霧囲気下、圧力 200 Pa、電源電力 150 kW を印加し、ターゲットと基板の間の距離を 28 mm、基板温度 350 として形成した。

#### 【0284】

続いて、厚さ 10 nm の窒化チタン層および厚さ 10 nm のタンゲステン層を、スパッタリング法により形成した。窒化チタン層の形成条件は、スパッタリング法により窒素 (窒素 = 50 sccm) 霧囲気下において、圧力 0.2 Pa、電源電力 12 kW を印加し、ターゲットと基板の間の距離を 400 mm、基板温度 25 とした。タンゲステン層の形成条件は、スパッタリング法によりアルゴン ( $A_r = 100 \text{ sccm}$ ) 霧囲気下において、圧力 2.0 Pa、電源電力 1 kW を印加し、ターゲットと基板の間の距離を 60 mm、基板温度 230 とした。

30

#### 【0285】

次に、ICPエッチング法により、厚さ 10 nm の窒化チタン層および厚さ 10 nm のタンゲステン層の積層をエッチングした。エッチング条件は、塩素、四弗化炭素および酸素 ( $Cl_2 : CF_4 : O_2 = 45 \text{ sccm} : 55 \text{ sccm} : 55 \text{ sccm}$ ) 混合霧囲気下、電源電力 3000 W、バイアス電力 110 W、圧力 0.67 Pa において第1のエッチングを行い、第1のエッチングの後に塩素および三塩化ホウ素 ( $Cl_2 : BCl_3 = 50 \text{ sccm} : 150 \text{ sccm}$ ) 混合霧囲気下、電源電力 1000 W、バイアス電力 50 W、圧力 0.67 Pa において第2のエッチングを行い、ゲート電極を形成した。

40

#### 【0286】

次に、ゲート電極上に厚さ 20 nm の酸化アルミニウム層をスパッタリング法により形成し、その上に、厚さ 150 nm の酸化窒化シリコン層を CVD 法により形成した。

#### 【0287】

以上の工程を経て、参考例トランジスタを作製した。参考例トランジスタのチャネル長は 50 nm、チャネル幅は 40 nm であった。

#### 【0288】

次に作製したトランジスタにおいて、オフ電流を求めた。1 fA より小さな電流は、直接は測定できないため、作製した参考例トランジスタを並列に 25 万個並べて接続し、実質的なチャネル幅が 10 mm (40 nm × 25 万) のトランジスタを作製して Cut 密度

50

を求めた。

【0289】

図19にチャネル幅が10mmのトランジスタのドレインの電位が1V、ソースの電位が0VのときのId-Vg特性を示す。図19に示すようにオフ電流は $10^{-13}$ A以下(つまり、オフ電流密度は、 $10^{-17}$ A/ $\mu\text{m}$ 以下)であることが確認された。

【符号の説明】

【0290】

|       |         |    |

|-------|---------|----|

| 101   | 半導体層    |    |

| 102   | 電子捕獲層   |    |

| 102 a | 第1の絶縁層  | 10 |

| 102 b | 第2の絶縁層  |    |

| 102 c | 第3の絶縁層  |    |

| 102 d | 導電層     |    |

| 102 e | 絶縁体     |    |

| 103   | ゲート電極   |    |

| 104   | ゲート絶縁層  |    |

| 105   | ゲート電極   |    |

| 106   | 電子捕獲準位  |    |

| 107   | 電子      |    |

| 108   | 曲線      | 20 |

| 109   | 曲線      |    |

| 110   | トランジスタ  |    |

| 111   | 容量素子    |    |

| 121   | トランジスタ  |    |

| 122   | トランジスタ  |    |

| 123   | 容量素子    |    |

| 124   | トランジスタ  |    |

| 125   | 容量素子    |    |

| 400   | 基板      |    |

| 401   | ゲート電極   | 30 |

| 402   | 下地絶縁層   |    |

| 402 a | 第1の絶縁層  |    |

| 402 b | 第2の絶縁層  |    |

| 402 c | 第3の絶縁層  |    |

| 403 c | 酸化物半導体層 |    |

| 404   | 多層半導体層  |    |

| 404 a | 酸化物半導体層 |    |

| 404 b | 酸化物半導体層 |    |

| 404 c | 酸化物半導体層 |    |

| 406 a | ソース電極   | 40 |

| 406 b | ドレイン電極  |    |

| 407   | 絶縁層     |    |

| 408   | ゲート絶縁層  |    |

| 409   | 導電層     |    |

| 410   | ゲート電極   |    |

| 412   | 酸化物絶縁層  |    |

| 450   | トランジスタ  |    |

| 470   | トランジスタ  |    |

| 501   | 筐体      |    |

| 502   | 筐体      | 50 |

|       |                |    |

|-------|----------------|----|

| 5 0 3 | 表示部            |    |

| 5 0 4 | 表示部            |    |

| 5 0 5 | マイクロフォン        |    |

| 5 0 6 | スピーカー          |    |

| 5 0 7 | 操作キー           |    |

| 5 0 8 | スタイラス          |    |

| 5 1 1 | 筐体             |    |

| 5 1 2 | 筐体             |    |

| 5 1 3 | 表示部            |    |

| 5 1 4 | 表示部            | 10 |

| 5 1 5 | 接続部            |    |

| 5 1 6 | 操作キー           |    |

| 5 2 1 | 筐体             |    |

| 5 2 2 | 表示部            |    |

| 5 2 3 | キーボード          |    |

| 5 2 4 | ポインティングデバイス    |    |

| 5 3 1 | 筐体             |    |

| 5 3 2 | 冷蔵室用扉          |    |

| 5 3 3 | 冷凍室用扉          |    |

| 5 4 1 | 筐体             | 20 |

| 5 4 2 | 筐体             |    |

| 5 4 3 | 表示部            |    |

| 5 4 4 | 操作キー           |    |

| 5 4 5 | レンズ            |    |

| 5 4 6 | 接続部            |    |

| 5 5 0 | トランジスタ         |    |

| 5 5 1 | 車体             |    |