(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4647095号

(P4647095)

(45) 発行日 平成23年3月9日(2011.3.9)

(24) 登録日 平成22年12月17日(2010.12.17)

(51) Int.Cl.

G03F 1/08 (2006.01)

G06F 17/50 (2006.01)

F 1

G03F 1/08 A

G06F 17/50 654G

G06F 17/50 658M

G06F 17/50 666C

請求項の数 20 (全 27 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-512111 (P2000-512111)  |

| (86) (22) 出願日 | 平成10年9月17日 (1998.9.17)        |

| (65) 公表番号     | 特表2004-502961 (P2004-502961A) |

| (43) 公表日      | 平成16年1月29日 (2004.1.29)        |

| (86) 国際出願番号   | PCT/US1998/019439             |

| (87) 国際公開番号   | W01999/014637                 |

| (87) 国際公開日    | 平成11年3月25日 (1999.3.25)        |

| 審査請求日         | 平成17年9月16日 (2005.9.16)        |

| 審判番号          | 不服2008-25623 (P2008-25623/J1) |

| 審判請求日         | 平成20年10月6日 (2008.10.6)        |

| (31) 優先権主張番号  | 08/931,921                    |

| (32) 優先日      | 平成9年9月17日 (1997.9.17)         |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 60/059,306                    |

| (32) 優先日      | 平成9年9月17日 (1997.9.17)         |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 597035274<br>シノプシス、 インコーポレイテッド<br>SYNOPSYS, INC.<br>アメリカ合衆国 カリフォルニア 940<br>43-4033, マウンテンビュー, イ<br>ースト ミドルフィールド ロード 70<br>0 |

| (74) 代理人  | 100082005<br>弁理士 熊倉 賢男                                                                                                      |

| (74) 代理人  | 100067013<br>弁理士 大塚 文昭                                                                                                      |

| (74) 代理人  | 100086771<br>弁理士 西島 孝喜                                                                                                      |

| (74) 代理人  | 100109070<br>弁理士 須田 洋之                                                                                                      |

最終頁に続く

(54) 【発明の名称】データ階層レイアウトの補正と照合のための方法及び装置

## (57) 【特許請求の範囲】

## 【請求項 1】

集積回路レイアウトのための光学的近接補正を生成する方法であって、上記集積回路レイアウトを記述するデータが階層構造を含み、且つ、上記方法が、

上記集積回路レイアウト設計を第1入力として提供するステップ、

特定の補正基準セットを第2入力として提供するステップ、

上記特定の補正基準セットに合致するレイアウトの形質を識別するために上記集積回路レイアウトを分析するステップ、

上記特定の補正基準セットに合致する形質に関する上記特定の補正基準セットに応じて、光学的近接補正データを生成するステップ、及び

上記集積回路レイアウトの階層構造に対応する階層構造に形成された上記光学的近接補正データを含む第1プログラム・データを提供するステップを含むことを特徴とする方法。

。

## 【請求項 2】

上記集積回路レイアウトがGDS-IIデータ・ファイルで記述されていることを特徴とする請求項1に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

## 【請求項 3】

上記光学的近接補正データが、レイアウトへのセリフの追加に対応するデータを含むことを特徴とする請求項1に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項 4】**

上記光学的近接補正データが、トランジスタ・ゲートの補正に対応するデータを含むことを特徴とする請求項 1 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項 5】**

上記特定の補正基準セットが、レイアウト内のトランジスタ・ゲートを明確に識別するための基準を含むことを特徴とする請求項 1 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項 6】**

第 1 の補正されたレイアウトを記述する第 2 プログラム・データを作るために、上記第 1 プログラム・データを、集積回路レイアウトを記述するデータと組み合わせるステップを更に含むことを特徴とする請求項 1 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。 10

**【請求項 7】**

上記第 1 の補正されたレイアウトが集積回路に関する設計ルールのセットの範囲内に在るか否かを確認するために、上記第 2 プログラム・データを設計ルール・チェッカーに提供するステップを更に含むことを特徴とする請求項 6 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項 8】**

レイアウト精度パラメータのセットを提供するステップ、 20

上記第 1 の補正されたレイアウトを上記設計精度パラメータと比較するステップ、

特定の設計精度ルールのセットに従ってレイアウトの全領域を補正するためのモデルベースの補正手段を提供するステップ、及び

第 2 の補正されたレイアウトが上記レイアウト精度パラメータのセットの範囲内に入るよう上記第 2 の補正されたレイアウトを作るために、上記モデルベースの補正手段を上記第 1 の補正されたレイアウトに適用するステップを更に含むことを特徴とする請求項 6 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項 9】**

集積回路のレイアウトがツリー構造の複数のセルを含み、且つ、上記第 1 プログラム・データを提供するステップは、複数のセルに対応する複数のデルタ平面を生成するステップを含み、各デルタ平面は、デルタ平面に対応するセルの補正面とデルタ平面に対応するセルの子セルに対応するデルタ平面との間の差を表すデータを含むことを特徴とする請求項 1 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。 30

**【請求項 10】**

各セルに対する上記補正面が、上記補正面が平坦化されたセルデータに適用された場合には、セルに対する補正された設計に等しい出力データを生成するデータを含むことを特徴とする請求項 9 に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項 11】**

機器により読み取り可能であり、また、請求項 1 に記載の方法を遂行するために、機器が実行可能な命令のプログラムを明確に具体化するプログラム記憶装置。 40

**【請求項 12】**

請求項 1 に記載の方法を実行するための装置。

**【請求項 13】**

集積回路レイアウトのための光学的近接補正を生成する方法であって、上記集積回路レイアウトを記述するデータは複数のセルを含む階層ツリー構造を含み、且つ、上記方法は、

上記集積回路レイアウトを第 1 入力として提供するステップ、

特定の補正基準セットを第 2 入力として提供するステップ、

上記特定の補正基準セットに応じて階層ツリー構造内における複数のセルの各セル毎に第 1 補正層を生成することを含む、階層ツリー構造をコンパイルするステップ、 50

各セルのデルタ平面がセルの各子セル間の相互作用及びセルの初期ジオメトリとセルの各子セル間の相互作用の結果として表されるように、各セルの補正層を部分補正して各セルのデルタ平面を生成することを含む、階層ツリー構造をリンクするステップ、及び

上記デルタ平面を含む第1プログラム・データを提供するステップを含み、上記第1プログラム・データは、集積回路レイアウトの階層ツリー構造に対応するように階層的に形成されていることを特徴とする方法。

**【請求項14】**

上記階層ツリー構造内の各セルに関して、セルのデルタ平面とセルの子セルのデルタ平面との和は、セルの補正面を構成し、且つ、セルに対する上記補正面が、上記補正面が平坦化されたセルデータに適用された場合には、セルに対する補正された設計に等しい出力データを生成することになるデータを含むことを特徴とする請求項13に記載の集積回路レイアウトのための光学的近接補正を生成する方法。10

**【請求項15】**

上記集積回路レイアウトがGDS-IIデータ・ファイルで記述されていることを特徴とする請求項13に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項16】**

上記特定の補正基準セットが、レイアウト内のトランジスタ・ゲートを明確に識別するための手段を含むことを特徴とする請求項13に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項17】**

第1の補正されたレイアウトを記述する第2プログラム・データを作るために、上記第1プログラム・データを、集積回路レイアウトを記述するデータと組み合わせるステップを更に含むことを特徴とする請求項13に記載の集積回路レイアウトのための光学的近接補正を生成する方法。20

**【請求項18】**

上記第1の補正されたレイアウトが集積回路に関する設計ルールのセットの範囲内に在るか否かを確認するために、上記第2プログラム・データを設計ルール・チェッカーに提供するステップを更に含むことを特徴とする請求項17に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項19】**

レイアウト精度パラメータのセットを提供するステップ、

上記第1の補正されたレイアウトを上記設計精度パラメータと比較するステップ、

特定の設計精度ルールのセットに従ってレイアウトの全領域を補正するためのモデルベースの補正手段を提供するステップ、及び

第2の補正されたレイアウトが上記レイアウト精度パラメータのセットの範囲内に入るように上記第2の補正されたレイアウトを作るために、上記モデルベースの補正手段を上記第1の補正されたレイアウトに適用するステップを更に含むことを特徴とする請求項17に記載の集積回路レイアウトのための光学的近接補正を生成する方法。

**【請求項20】**

請求項13に記載の方法を実行するための装置。40

**【発明の詳細な説明】**

**【0001】**

(関連出願についての説明)

本出願は、ファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる1998年9月16日出願の「マスク記述のためのシステムにおけるデータ階層維持の方法及び装置」と題する米国仮特許出願の継続出願であり、当該出願日の恩典を請求する。更に、本出願は、ファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる1997年12月12日出願の出願番号第60/069,549号の「データ階層進化型マスク補正と照合の方法及び装置」と題する米国仮特許出願に関連しておりその通常の出願であり、当該出願日の恩典を請求し、これをここに援用する。50

上記の特許それぞれは本発明の譲渡人に譲渡されている。

【0002】

更に本出願は、ファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる1997年9月17日出願の出願番号第60/059,306号の「マスクの照合、補正、並びに設計ルール照合」と題する米国仮特許出願、及びファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる1998年9月16日出願の「マスクの照合、補正、並びに設計ルール照合」と題する米国特許出願に関連しており、これらをここに援用する。本出願は又、ファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティ、リナード・カーラクリンの発明になる1998年8月7日出願の「視認検査と照合システム」と題する米国特許出願にも関連しており、これをここに援用する。本出願は又、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる1997年9月17日出願の出願番号第08/931,921号の「位相シフト回路製造方法及び装置」と題する米国特許出願にも関連しており、これをここに援用する。上記の特許それぞれは本発明の譲渡人に譲渡されている。10

【0003】

(技術分野)

本発明は、集積回路製造の分野に関する。特に、高速且つ効率的な集積回路レイアウトの補正及び照合を可能とするコンセプト並びにシステム設計技術に関する。

【0004】

(関連技術の説明)20

集積回路(I C)を設計する際、通常、技術者は、特定の機能を果すすべく一体的に連結された個々の素子を含む基本設計回路の作成を支援するコンピュータ・シミュレーション・ツールに依存している。半導体基板において、実際に、この回路を作り上げるには、該回路を、物理的表現、即ち物理的レイアウトに変換する必要があり、こうすることにより、次に、それ自身をシリコン表面上に転写することが可能となる。完成されたI Cが該素子自身によって具現化されるような形状に、ディスクリート素子回路を変換するオペレーションにおいて、再び、コンピュータ支援設計(C A D)ツールがレイアウト設計者を支援することになる。これらの形状は、ゲート電極、フィールド酸化領域、拡散領域、金属相互接続等の、回路の個々の要素を作り上げる。

【0005】

これらのC A Dシステムに使用されるソフトウェア・プログラムは、通常、機能回路を作り出すように、予め定められた設計ルールのセットの下で機能するように構成されている。これらのルールは、しばしば、特定の情報処理及び設計に係る制限により決定される。例えば、該設計ルールは、素子又は配線が、互いに好ましからざる影響を与え合うことがないように、素子間又は相互接続配線間ににおける間隔の許容範囲を規定することもある。設計ルールによる制限は、よく、限界寸法と呼ばれる。回路の限界寸法は、通常、1本の配線の最少幅又は2本の配線間の最少間隔として規定される。従って、限界寸法により、I Cの全体的な大きさと密度が決定される。現在のI C技術において、最高技術水準の回路での最少限界寸法は、配線幅と間隔に関して約0.25ミクロンである。30

【0006】

回路レイアウトが作られると、集積回路(I C)を製造する次のステップは、そのレイアウトを半導体基板上に転写することである。光学的リソグラフィは、幾何学的形状をシリコン・ウェーハの表面上に転写するための公知プロセスである。通常、光学的リソグラフィ・プロセスは、半導体ウェーハの最表面上にフォトレジスト層を形成することから開始される。次に、通常クロムで形成された完全な非光透過性の不透明領域と、通常石英で形成された完全な光透過性の透明領域とを有するマスクが、フォトレジストがコートされたウェーハを覆うように配置される。次に、光が、可視光源又は紫外線光源によって、マスク上に照射される。この光は、通常、1個又は数個のレンズ、フィルタ、及び/又は鏡を含むレンズシステムを使って集束され、縮小されたマスク像をウェーハ上に生成する。光は、マスクの透明領域を通過して、その下のフォトレジスト層を露光するとともに、マスク

40

50

クの不透明領域により遮られ、その下のフォトレジスト層部分を露光されない状態のままでする。次に、露光されたフォトレジスト層は、通常、フォトレジスト層の露光／非露光領域を化学的に除去する過程で現像される。その結果として作り出されるものは、要求される幾何学形状、形質、配線、及び外形で規定された所要パターンを持つフォトレジスト層で覆われた半導体ウェーハである。次に、このパターンは、ウェーハの下層領域をエッチングするために使用される。

#### 【0007】

上記の設計ルールの他にも、光学的リソグラフィに用いられる露光ツールの解像度値によつても、集積回路レイアウトの設計者に対して制限が課せられる。露光ツールに対する解像度は、露光ツールがウェーハに関する繰り返し露光可能な最少の形質として規定される。現在、最も進化した光学露光ツールの解像度は、約0.25ミクロンである。レイアウトの限界寸法が小さくなり、それがリソグラフィ装置の解像度値に近づくにつれ、マスクとフォトレジストに現像された実際のレイアウトパターンとの間の一致性は著しく低下する。特に、回路形質のパターン現像における差は、相互の形質の近接度に左右されることが観察される。

10

#### 【0008】

IC設計におけるこれらの制限に留意する場合、ICパターンを記述するデータは、通常、GDS-IIデータ・ファイルのように、圧縮された階層的様式で表現される点に注目する必要がある。高レベルのパターン表現階層では、形質は、概念的様態で表される。例えば、メモリー・アレーは、所定のセルをある特定数の列と行を反復したものとして記述される。その次に低いレベルの階層に、サブセルAとBとを含む基本メモリー・セルを記述することも可能である。最後に、最も下のレベルでは、最も基本的なサブセルは、幾何学的な基本的矩形又は多角形を含んでいる。物理的マスクを生成するためには、先ず、階層的に記述されたすべての幾何学的インスタンスを列挙することによって、階層データを平坦化する必要がある。通常、階層を平坦化すると、パターンを表現するのに必要とされるデータ記憶量の値は、数桁増える結果となる。

20

#### 【0009】

階層を平坦化すると、特定のIC設計を表現するファイルのサイズをこのように大幅に増加する結果となるので、マスク製造過程の最終点で階層を平坦化することが望ましく、最も望ましいのは、物理的製造前において、マスク設計がEB装置にロードされる時点である。しかしながら現在、複雑なICのマスク製造においては、この平坦化プロセスは、より早いステップで行われる。これは、複雑なICの原型となるマスク設計が、通常、この原型の設計に係る多くのオペレーションの1つ1つを順次実行し完了した後に、加工されることに起因する。これらのオペレーションは、複雑なICの限界寸法が光学的リソグラフィの解像度の限度に接近するほど、複雑なIC用のマスクに精度が必要となるために行われる。現在、これらのオペレーションには、順次行われる原型設計データの平坦化が多少必要であり、望ましい時期より早いステップで設計データの平坦化を行う結果となっている。これらのオペレーションには、論理演算の実行、光学的近接補正の生成、位相をシフトしたマスクの生成、及びこれらのオペレーションを済ませたマスクの設計ルールの照合が含まれる。

30

#### 【0010】

特に、複雑性が一層制限された最近の集積回路の殆ど全てに対しては、フォトリソグラフィの終了後に望ましい画像がウェーハ上に正確に再現されるようにするために、原型マスク設計を光学的近接効果に関して修正することが要求される。近接効果は、間隔が非常に近接したパターン形質がウェーハのレジスト層にリソグラフィ転写されるときに生じる。間隔が非常に近接した形質部分を通過する光波は、相互作用し、その結果、最終転写パターン形質を歪曲させる。形質のサイズと間隔が、リソグラフィ・ツールの解像限界値に近づいたときに起きる別の問題は、角(凹及び凸)がそれぞれの角でエネルギーが集中したり又は不足したりすることにより、過剰露光又は過小露光となる傾向にあるということである。大型形質及び小型形質が、同じマスク・パターンから転写される時には、小型形質の

40

50

過剰露光又は過小露光という別の問題も起きる。

#### 【0011】

近接効果に関する問題を解決するために、多くの方法が開発されてきた。これらの方には、マスク配線幅の予補償、フォトレジスト層厚の可変化、多重層フォトレジスト・プロセスの使用、光学的結像と共に電子ビーム結像の使用、そして最後に、近接効果を補償するために、原型マスク・パターンに付加的な形質を加えることが含まれる。この最後の方法は光学的近接補正(OPC)として知られている。

#### 【0012】

OPCが利用されるときに原型マスクに加えられる追加形質は、通常、サブ・リソグラフィ(即ち、寸法が露光ツールの解像度より小さい)であり、従ってレジスト層に転写されない。代わりに、それらは、最終的に転写されるパターンを改善し、近接効果を補償するように、原型パターンと相互作用し合う。

10

#### 【0013】

最近では、OPC形質を含むようにマスク定義を調整することができるいくつかの既知のOPCソフトウェアを導入したプロダクトが存在する。しかし、現状においては、この利用可能なプロダクトは、正確さ、速さ、データ量、及び 作り出されたOPC補正後のマスク設計の照合という点で多くの制約がある。これは、現在のプロダクトが、OPC形質がマスク設計に加えられるとき、原型マスク設計の真の階層的データ・フォーマットを維持しないからである。これらのプロダクトでは、補正形質を加えて補正する前に、原型マスク設計を、先ず何らかの形式の平坦化されたデータ・フォーマットに展開する必要がある。これによって、結果として生じる補正された設計データ・ファイルのサイズが数倍に膨れ上がり、そのためOPC処理速度が低下することになる。更に、より重要なことであるが、これらは、マスク設計における真の階層データ・フォーマットの原型を維持していないために、原型マスクと同一の階層データ・フォーマットを必要とする従来の照合ツールを使用して、現在知られているOPC補正されたマスクを照合することは、極めて困難で且つ膨大な時間を必要とする。

20

#### 【0014】

従って、正確さ、速さ、データ量、結果の照合に関する現在知られているシステムの上記問題点を解決する、集積回路マスク設計をOPC補正するための方法及び装置が必要とされている。

30

#### 【0015】

##### (発明の概要)

先に論じたように、集積回路設計レイアウトに関する論理演算の補正及び実行のための現在知られているシステムでは、該設計の原型の階層を保存することができない。これは、データの大幅な増加、処理速度の低下、及び 従来の照合ツールの使用では補正処理された設計を迅速に照合できないということを含む幾つかの問題を引起す。

#### 【0016】

従って、本発明の一実施形態では、原型レイアウトの階層を維持する、光学的近接効果に対する集積回路レイアウト補正のための方法が提供される。該補正方法は、階層的に記述された集積回路レイアウトを第1入力として提供するステップと、特定の補正基準セットを第2入力として提供するステップとを含む。次に、集積回路レイアウトは、提供された特定の補正基準に合致するレイアウトの形質を識別するために分析される。補正の必要なマスクの区域が識別された後、特定の補正基準セットに応じて光学的近接補正データが生成される。最後に、集積回路レイアウトの階層構造に対応する階層構造内に、生成された光学的近接補正データを記憶した第1プログラム・データが生成される。

40

#### 【0017】

本方法の様々な代替実施形態では、生成された第1プログラム・データがハードディスク・ドライブ又はサーバーのようなコンピュータ読み取り可能媒体上に記憶され、集積回路レイアウトがGDS-IIデータ・ファイル又は他の階層的データ記述により記述される。上記実施形態の他の事例では、第1プログラム・データはGDS-IIデータ・ファイル又

50

は他の階層的データ記述により記述することもできる。

#### 【0018】

上記方法の更なる特徴としては、生成された光学的近接補正データは、レイアウトのセルフ形質の追加に対応するデータと、トランジスタ・ゲートの補正に対応するデータとを含む。上記方法の更なる実施形態では、特定の補正基準セットは、レイアウト内でトランジスタ・ゲートを明確に識別するための手段を含む。この事例は、生成された光学的近接補正データがトランジスタ又は配線の線端へのハンマー・ヘッド形質の追加に対応するデータを含むことにより更に特徴付けられる。

#### 【0019】

ある代替実施形態では、本方法は、第1の補正されたマスクを記述する第2プログラム・データを作るために、第1プログラム・データを、集積回路マスクを記述したデータと組み合わせる追加のステップにより更に特徴付けられる。この実施形態は、第3プログラム・データを作るために、第2プログラム・データを平坦化すること、及び 光学的に補正されたリソグラフィマスクを作るために、第3プログラム・データを利用するなどを含む他のステップを追加することにより更に特徴付けることができる。10

この実施形態は、第1の補正されたレイアウトが、集積回路に関する設計ルールのセットの範囲内に在るか否かを判定するために第2プログラム・データを設計ルール・チェッカーに提供するステップを追加することにより更に特徴付けることができる。

#### 【0020】

別の事例では、この実施形態は、レイアウト精度パラメータのセットを提供するステップと、第1の補正されたレイアウトを設計精度パラメータと比較するステップとの追加により更に特徴付けることができる。これらの追加されたステップは、特定の設計精度ルールのセットに従って、レイアウトの全区域を補正するためのモデルベースの補正手段を提供すること、及び 第2の補正されたレイアウトがレイアウト精度パラメータの範囲内に入るように第2の補正されたレイアウトを作るために、モデルベースの補正手段を第1の補正されたレイアウトに適用することを更に含む。20

この実施形態は、第2の補正されたレイアウトを設計ルール・チェッカーに提供するステップと、設計ルール・チェッカーを作動させるステップと、第2の補正されたレイアウトが集積回路に関する設計ルールのセットの範囲内に在るか否かを判定するステップとを追加することにより更に特徴付けられる。代わりに、上記実施形態は、第1の補正されたレイアウトを設計精度パラメータと比較するステップが、第2プログラム・データを、第1の補正されたレイアウトが作り出すことになる露光の模擬画像を作るチェッckerに提供すること、集積回路のために設計された露光の実際の画像を提供すること、及び 模擬画像と実際の画像との間の差を求めるなどを更に含むことで更に特徴付けられる。30

#### 【0021】

別の事例では、本方法は、第1プログラムを生成するステップが、複数のセルに対応する複数のデルタ平面を生成することを更に含むことによっても特徴付けられる。この実施形態では、各デルタ平面は、デルタ平面に対応するセルの補正面と、デルタ平面に対応するセルの子セルに対応するデルタ平面との間の差を表すデータを含む。この事例では、各セルに対する補正面は、補正面が平坦化されたセルデータに適用された場合には、セルに対する補正設計に等しい出力データを生成することになるデータを含む。40

#### 【0022】

また、基本的方法クレームの代替実施形態も提供される。この代替実施形態は、集積回路レイアウトを第1入力として提供するステップと、特定の補正基準を第2入力として提供するステップとを備えている。他のステップには、階層ツリー構造をコンパイルするステップが含まれ、これには、複数のセルの各セル毎に、第1補正層を、特定の補正基準セットに応じて階層ツリー構造に生成するステップが含まれる。また、階層ツリー構造をリンクするステップが含まれ、このリンクするステップは、各セル毎にデルタ平面を生成し、各セルのデルタ平面が、セルの各々の子セル間における相互作用、及びセルの初期幾何学形状とセルの各々の子セル間における相互作用を補正することにより、各セルの補正層を50

修正するステップを含む。最後にデルタ平面を含む第1プログラム・データが提供されるが、第1プログラム・データは、集積回路レイアウトの階層ツリー構造に対応するよう階層的に形成される。

本方法の代替実施形態では、上記方法に追加の限定が加えられ、階層ツリー構造内の各セルに関し、セルのデルタ平面とセルの子セルのデルタ平面の和がセルの補正面を構成し、セルに対する補正面は、補正面が平坦化されたセルデータに適用された場合には、セルに対する補正された設計に等しい出力データを生成するデータを含む。この代替法法の他の変形例は、主たる方法に関して先に論じたものと同様である。

#### 【0023】

最後に、上記実施形態の方法ステップは、一例においては、コンピュータによって、これらのステップを実行するプログラムを稼動することができ、ここにおいて、このプログラムは、ハードディスク・ドライブやサーバーのような何らかの適切なコンピュータ記憶媒体上に記憶される。

10

#### 【0024】

本発明は、方法ステップに関し、以上を要約すると、原型レイアウトの階層を維持する、光学的近接効果に対する集積回路レイアウトの補正のための装置として特徴付けることができる。この装置は、一実施形態では、集積回路レイアウトを受入れる第1入力と、特定の補正基準セットを受入れる第2入力と、集積回路レイアウトを分析し、特定の補正基準セットに合致する形質を識別するリソースとを含む。また、特定の補正基準セットに合致する形質に対する特定の補正基準セットに応じて光学的補正データを生成するリソースと、集積回路レイアウトの階層構造に対応する階層構造に形成された光学的補正データを含む第1プログラム・データを提供するリソースも提供される。

20

#### 【0025】

方法実施形態に関し以上で論じた特徴は、装置実施形態に関しても同様に適用できる。例えば、装置実施形態は、補正データに対するセリフ及びトランジスタ・ゲート補正の追加に備え、トランジスタ・ゲートを明確に識別するための手段を含む特定の補正基準セットに備えるように変更することもできる。

#### 【0026】

一代替実施形態では、装置は、第1の補正されたレイアウトを記述する第2プログラム・データを作るために、第1プログラム・データを、集積回路マスクを記述するデータと組み合わせる追加のリソースを含む。この実施形態は、第3プログラム・データを作るために第2プログラム・データを平坦化するリソースと、光学的に補正されたリソグラフィマスクを作るために第3プログラム・データを利用するリソースを追加することにより更に特徴付けることができる。この実施形態は、第1の補正されたレイアウトが、集積回路に関係する設計ルールのセットの範囲内に在るか否かを判定する設計ルール・チェッカーを提供することにより更に変更することができる。

30

#### 【0027】

もう1つの実施形態では、例えば、レイアウト精度パラメータのセットを受入れる第3入力と、第1の補正されたレイアウトを設計精度パラメータと比較するリソースのような更なる要素が追加される。また、特定の設計精度ルールのセットに従ってレイアウトの全区域を補正するためのモデルベースの補正手段を提供するリソースと、第2の補正されたレイアウトがレイアウト精度パラメータの範囲内に入るよう第2の補正されたレイアウトを作るためにモデルベースの補正手段を第1の補正されたレイアウトに適用するリソースとが提供されている。この実施形態は、第2の補正されたマスクを受入れ、第2の補正されたレイアウトが集積回路に関係する設計ルールのセットの範囲内に在るか否かを判定する設計ルール・チェッカーを追加することにより更に特徴付けることができる。

40

この実施形態は、第2プログラム・データを、第1の補正されたレイアウトが作り出すことになる露光の模擬画像を作るチェッカーに提供するリソースの追加によって更に特徴付けることができる。この場合、その集積回路のために設計された露光の実際の画像を提供するリソースと、模擬画像と実際の画像との間の差を求めるリソースも提供される。

50

**【 0 0 2 8 】**

最後に、上記実施形態の装置は、一例としては、コンピュータが集積回路レイアウトの光学的近接補正を生成するように具体化されたコンピュータ読み取り可能プログラム・コードを有する、コンピュータが利用可能な媒体含むコンピュータ・プログラム・プロダクトとすることもできる。ここにおいて、集積回路レイアウトを記述するデータは、階層構造を含んでいる。

説明及び図には多くの詳細な事項が含まれているが、本発明は請求の範囲によって定義される。それら請求の範囲に述べられている限定のみが本発明に適用される。

**【 0 0 2 9 】**

(実施形態の詳細な説明)

10

上記したように、フォトリソグラフィーマスクの製造では、IC設計を表すデータを、マスクの実際の製造過程における最終時点で平坦化することが有利である。しかしながら、この平坦化が望ましい時点以前に行われる場合もある。これは、これは、複雑なICの原型となるマスク設計が、通常、この原型の設計に係る多くのオペレーションの1つ1つを順次実行し完了した後に、加工されることに起因する。これらのオペレーションには、論理演算の実行、光学的近接補正の生成、位相をシフトしたマスクの生成、及びこれらのオペレーションを済ませたマスクの設計ルールの照合が含まれる。現在、これらのオペレーションには、順次行われる原型設計データの平坦化が多少必要であり、望ましい時期より早いステップで設計データの平坦化を行う結果となっている。この早期のデータの平坦化は、必要なデータ記憶量の値を大幅に増大させ、それに対応してこれらのオペレーションの速度が低下するという結果を招く。更に、現行の照合システムは通常、同一の入力データ階層を必要とするので、非階層的方法で設計を修正した場合、これらの修正された設計を照合する重要なステップの実行は、不可能でないとしても困難なものとなる。

20

**【 0 0 3 0 】**

本発明は、設計の原型における真の階層が維持されるように、入力階層IC設計に関するOPC補正のようなオペレーションを実行することにより上記問題の解決を図る。本発明における種々の実施形態には、集積回路製造で使用されるマスクの照合と補正とを行うための、そして設計レイアウトに関する論理演算を行うためのコンピュータ・システムが含まれている。これらの実施形態では、特定マスクの外観を定義する階層的マスク定義データを受入れる。次に、これらの実施形態では、データの出力セットを生成する。一実施形態では、この出力データは、OPC補正されたマスク定義を含んでいる。本発明の他の実施形態は、OPC補正又はマスク照合手法を実行するシステムを使って生成された実際のマスクを含んでいる。本発明のその他の実施形態では、OPC補正又はマスク照合技術を実行するコンピュータ・プログラムを有するコンピュータ読み取り可能媒体（例：ハードディスク、CD、及び他のコンピュータ・プログラム記憶装置ツール）を含んでいる。

30

**【 0 0 3 1 】**

図面に関連して本発明を説明する前に、本発明概念の一実施形態についての概要について説明する。このように、本発明の一実施形態では、レイアウトの階層的定義を受入れるため、そして設計レイアウトに関するオペレーションを実行するエンジンによって提供される補正情報を階層的に含む1つ或いはそれ以上の追加的データ層を生成するために、階層保存手段を使用する。これらの追加層は、その層の階層的定義で各ノードに関連づけられるように記憶される。

40

**【 0 0 3 2 】**

以下の定義を本明細書に使用する。補正面を平坦化されたノードに適用することにより、出力がそのノードに関する補正された設計となるように、補正面は、階層の何れのノード（セル）とも関連づけられる。デルタ平面は、本質的には、ノードの補正面と、その直下にある全ての子デルタ平面の合計との間の差である。従って、あるセルの補正面は、上記セルに対するデルタ平面に、上記セルの直下にある子セルのデルタ平面を足したものに等しい。階層の葉セルは子セルを持たないので、何れの葉セルにとっても補正面は上記葉セルのデルタ平面に等しくなる。この方法によれば、本発明の一実施形態では、レイアウト

50

の全体的な補正は、階層中の各セルに対するデルタ平面を保存するだけで提供できるようになるので、各セルの補正面を保存する必要が無くなる。

#### 【 0 0 3 3 】

本発明の一実施形態の背後にある基本的な思想を、コンパイルとリンクингとを含む2つのステップに分けて説明する。コンパイルステップでは、設計レイアウトに関して実行されるべきオペレーションに従って、階層中の全ての幾何学的初期形状に対して補正が生成される。リンクステップでは、親セルの子セルと親セルの初期の幾何学形状との光学的重なりにより、余分な補正が行われる。従って、追加的な補正だけが記憶される。

#### 【 0 0 3 4 】

デルタ・アルゴリズムは、子セルの重なり及び親セルの幾何学形状と子セルとの間の重なりのみを考慮することにより、デルタ／追加情報を計算処理する。重なりのみが親セルにとって必要な追加的補正変更に寄与することになるので、これらの区域のみが考慮される。重なり区域は単に幾何学形状の重なりにとどまる訳ではなく、近接重なりも含んでいる。より普遍的な定義を採用することにより、全ての近接効果／補正を考慮に入れることができる。あるセルにとってのデルタ・アルゴリズムの出力をここでそれ自身のデルタ平面と呼ぶことにする。階層ツリーの葉は、こうしてそれらの補正面に等しいデルタ平面を有する。

10

#### 【 0 0 3 5 】

コンパイル時には、全ての葉に対する補正面は、提供された平坦化されたデータに関する所要のオペレーションを実行するオペレーション・エンジンに対し、各葉毎の幾何学的初期形状を記述する平坦化されたデータを提供することによって生成される。リンク時には、どのサブセルも重なっていない場合は、この親セルにとっての補正面は、その子セルのデルタ平面の和に等しい（上に述べたように、この親セル用に記憶されるべき追加的デルタ平面情報は無くなる）。仮に重なりがあれば、重なり区域は平坦化され、平坦化された重なり区域に対する中間的な補正面が生成される。必然的に、この中間的補正区域は、その子供の全補正面の和を減算するために使用され、その差がリンクされるセルに対応するために階層的に記憶されるデルタ平面である。

20

#### 【 0 0 3 6 】

現在のGDS-II及び完全なレイアウトを記述する他の設計データベースフォーマットのほとんどは、別々の層に異なるマスク及びチップレベルを配置することを含んでいる。本発明の様々な実施形態に導入されようとしているものは、層コンセプトに関するねじり、即ち論理演算（例：XOR、AND）及び算術演算の両者が基盤とすることのできる算術層である。例えば、OPCオペレーションに関して、特定のOPC形質を表す補正層では、例えば「-1」は負のセリフを、「+1」は正のセリフを、そして「-2」はある1方向の重なりが微小な端突合せをそれぞれ意味するように算術層に基づくことができる。リンクング中は、構造を通して漸増又は微分補正を計算するために全補正層がアルゴリズムを使って算術的に生成される。これらのデルタ平面又は算術層は、識別可能な層としてデータベースフォーマットで露光される（例：+1、-1、-2等を層1、2、3にマッピング）。これにより、親セルに対する最終的な補正層が、親セルのデルタ平面、及び親セルの子供達、孫達、曾孫達、そして、葉のコンパイル時間の補正層からのものなどの、デルタ平面全ての増分の和に等しくなる。

30

#### 【 0 0 3 7 】

階層的データ管理は、デルタ・アルゴリズム又は上述した算術層が使用されない本発明の別の実施形態において補正の生成を行う際にも実行できる。この代替実施形態では、親セルとその子セルとの補正層間の差をとって記憶する代わりに、親子間の補正を比較するために論理演算を使用することができ、ここでは「算術的」差の代わりに「論理的」差が、親セルに記憶される。

40

#### 【 0 0 3 8 】

このように、以上を要約すると、本発明は、マスク記述のためのシステムにおけるデータ階層維持のための方法及び装置を提供する。本発明の好適実施形態の詳細な説明を、以下

50

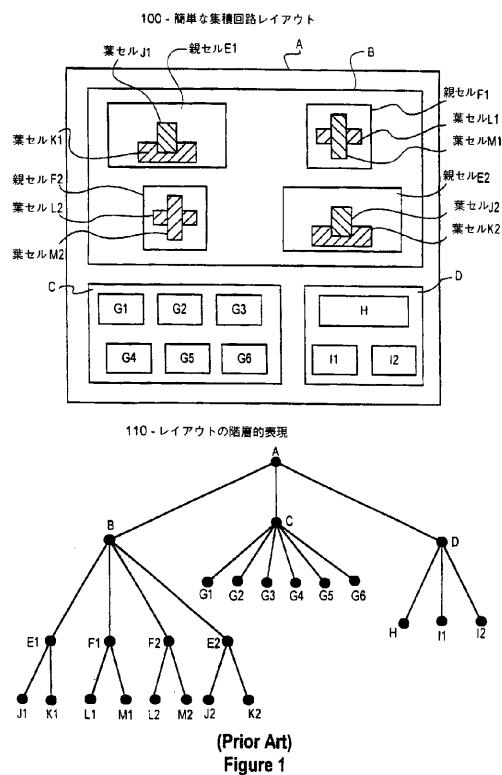

、図に従って行うが、図1は、単純な集積回路設計レイアウト100及び上記レイアウトの階層表現110を示している。回路レイアウト100は、親セルB、C、Dを含む最終的なセルAを含む。親セルCは、同一セルG1、G2、G3、G4、G5、G6を含む。親セルDは、セルH及び同一セルI1、I2を含む。親セルBは、同一の親セルE1、E2及び同一の親セルF1、F2を含む。親セルE1は、図1に示す初期幾何学形状構造を備えた葉セルJ1、K1を含む。親セルE2は、セルJ1、K1と同じ初期幾何学形状構造を備えた葉セルJ2、K2を含む。親セルF1は、図1に示す初期幾何学形状構造備えた葉セルL1、M1を含む。親セルF2は、セルJ1、K1と同じ初期幾何学形状構造を備えた葉セルL2、M2を含む。階層ツリーレイアウト110は、上記のセルをツリーフォーマットで示しており、ツリーの一番下が葉セルで、ツリーの一番上は最終的なセルA 10となっている。葉セルの各々は、時として本願では葉ノード又は子セルとも称され、一方葉ノード上方のセルの各々は、ここでは親セル又は単にノードと称されることもある。図1の集積回路設計レイアウト100は、以下に説明する本発明の実施形態に関連付けた参考IC設計として提供されている。図1に示す単純なICは、例示のためだけに用いるものであり、以下に述べる本発明の実施形態は階層的フォーマットで記述されるどのようなICにも応用可能である。

#### 【0039】

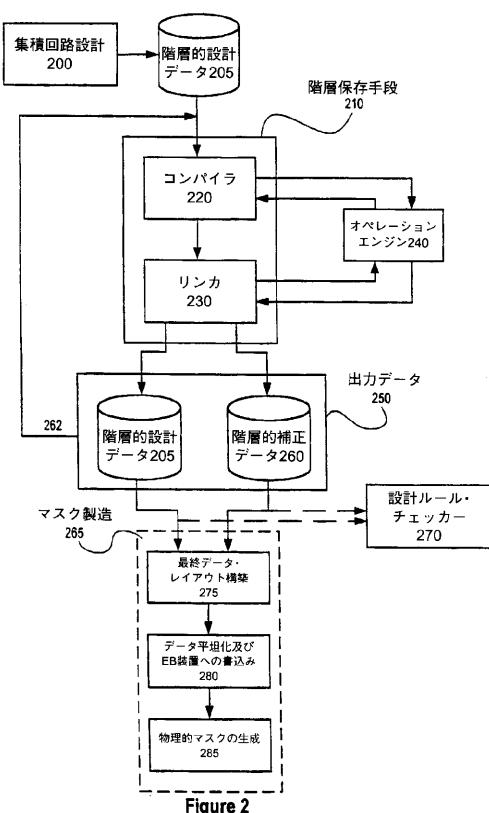

図2は、本発明の一実施形態を組み入れたシステムをブロック線図型式で示したものである。記述されているシステムは、結果的に修正されたIC設計が入力設計の原型における真の階層を維持するように、論理演算又は算術演算が階層的に記述された入力IC設計に関する実行できるものである。上記システムの一実施形態の基本的エレメントは、階層保存手段210とオペレーション・エンジン240とを含む。階層保存手段210はコンパイラ220とリンク230とを含む。 20

#### 【0040】

システムの階層保存手段210は、集積回路設計200を入力として記述する階層設計データ205を受入れる。階層保存手段210は、一実施形態ではGDS-IIフォーマットの階層設計データ205を受入れる。他の実施形態では、階層保存手段210は、どんな階層ファイルフォーマットで記述された階層設計データ205でも受入れる。階層保存手段210のコンパイラ220は、オペレーション・エンジン240と共に作動して、設計データ205の各ノードで幾何学的初期形状用の補正データ層を提供する。生成された補正データ層は、以下により詳しく説明するが、オペレーション・エンジン240により実行中のオペレーションに従って、各ノードで幾何学的初期形状に対してなされる変更を表現する。本発明の一実施形態では、オペレーション・エンジン240は、入力設計データ205に関するAND又はNOTのような論理演算を実行する。本発明の別の実施形態では、オペレーション・エンジン240は入力設計データ205に関する光学的近接補正を実行する。本発明の更に別の実施形態では、オペレーション・エンジン240は入力設計データ205の設計ルール照合を行う。 30

#### 【0041】

コンパイラ220が、入力設計データ205の各ノードに対する補正データ層を生成した後に、リンク230は、設計の各ノードに対するデルタ平面を生成するために、オペレーション・エンジン240と共に作動する。各セルに対するデルタ平面は、それが、特定セルに対する、補正データ層情報と特定セルにおける子セルの補正データ層全部との合計の差に等しくなるように生成される。一実施形態では、各セルに対するデルタ平面は、各セル内での重なりを考慮するだけで、デルタ/追加情報を計算するリンク230により処理されるデルタ・アルゴリズムにより生成される。一実施形態では、これらの重なりは、セルの子セル相互間の重なり及び親セル自身の初期幾何学形状とその子セルのそれとの重なりのみで構成されている。一実施形態では、これらの重なり区域は、単に幾何学形状の重なりにとどまらず、近接重複も含む。リンク230が、入力設計205の各ノードに対してデルタ平面を生成する手段となる処理については以下により詳しく述べる。 40

#### 【0042】

リンク 230 がデルタ平面を生成した後、階層保存手段 210 は、オペレーション・エンジン 240 により実行されるオペレーションに従って修正された入力設計 205 を表す出力データ 250 を生成するが、この出力データ 250 は、入力設計データ 205 の原型における真の階層を維持している。この出力データ 250 は、原型における変更されていない入力設計データ 205 と階層的補正データ・ファイル 260 とを含む。階層的補正データ・ファイル 260 は、設計データ 205 と補正データ 260 とが組み合わされたとき、オペレーション・エンジン 240 により原型設計データ 205 に関して実行されたオペレーションを表す修正された設計が生成されるように、設計データ 205 の各ノードに対するデルタ平面データを含む。

## 【0043】

10

階層的出力データ 250 は、多くの用途に使用できる。第 1 に、新しい論理演算又は算術演算を出力データ 250 に関する実行するために、配線 262 で階層保存手段 210 に送ることができる。更に、それは階層形式のため、新しく修正された出力設計が、設計中の特定集積回路に対する設計ルールに当てはまることを点検するために照合することができるよう、階層的データを受入れる従来型の設計ルール・チェッカー 270 に送ることもできる。更に、出力データ 250 は、最終的なデータレイアウト 275 を構築するように設計データ 205 を補正データ 260 と組み合わせ、この組み合わされたデータレイアウト 280 を平坦化し、この平坦化されたデータを電子ビーム装置に供給することによって、修正された設計データ 285 を具現化した実際の物理的なマスクを生成するマスク製造 265 にも使用できる。

## 【0044】

20

ここで、設計データ 205 の各ノードに対する補正データ層及びデルタ平面の生成について、更に明らかにする。図 1 に関して、コンパイラ 220 の一実施形態は、深度方向トラバースを用いて設計データにアクセスするが、その場合、最終的な親セルの各枝は、順番にアクセスされることになり、各枝はその葉ノードから上向きにアクセスされる。このように、図 1 については、コンパイラ 220 に関するこの実施形態は、集積回路レイアウト 100 のノードに以下の順序、即ち J1、K1、E1、L1、M1、F1、L2、M2、F2、J2、K2、E2、B、G1、G2、G3、G4、G5、G6、C、H、I1、I2、D、A の順にアクセスすることになる。コンパイラ 220 は、ツリーをトラバースしながら、オペレーション・エンジン 240 に、各セルの初期幾何学形状に対応する平坦化されたデータを提供する。オペレーション・エンジン 240 は、平坦化されたデータに関するオペレーションを実行し、このオペレーションの結果を階層保存手段 210 に戻す。例えば、図 1 について、仮に J1 がコンパイルされたとすると、オペレーション・エンジン 240 は平坦化されたデータ  $J' = J + J$  を戻すことになる。一実施形態では、データ記憶量は、 $J$  についての上記等式の解を出し  $J$  の値をセル  $J$  に対する補正層として記憶する階層保存手段 210 の分だけ減少する。この処理過程は、ツリー全体がトラバースされるまで設計内のセル毎に繰り返される。次に、設計データ 205 が以下の方法でリンク 230 によりリンクされる。ツリーは、上記方法で再度トラバースされ、各セル毎に重なり区域が見つけ出され平坦化される。次に、平坦化された重なり区域は、オペレーション・エンジン 240 に入力され、次に、このオペレーション・エンジン 240 が、データに関するオペレーションを行って、それを階層保存手段 210 に戻す。リンク 230 は、オペレーション・エンジン 240 から戻されたデータを使って、各セル毎のデルタ平面を生成するためにリンク 230 により使用される中間補正層を作り出す。デルタ平面の生成は図 6 並びに図 10 に関連させて、以下により詳しく説明する。次に、設計の各セル毎のデルタ平面は、階層補正データ・ファイル 260 に入力設計データ 205 の階層に対応する階層フォーマットで記憶される。

30

## 【0045】

40

図 2 に説明したように、本発明の一実施形態では、階層保存手段 210 は、コンパイラ 220 とリンク 230 との機能を実行するコンピュータ読み取り可能媒体上に記憶されたプログラム・コードを実行するコンピュータ・システムを含む。本発明の一実施形態では、

50

オペレーション・エンジン 240 も又コンピュータ読み取り可能媒体上に記憶されたプログラム・コードを実行するコンピュータ・システムを含む。本発明の一実施形態では、階層保存手段 210 とオペレーション・エンジン 240 とは、コンパイラ 220、リンク 230 及びオペレーション・エンジン 240 を合わせた機能を実行する、コンピュータ読み取り可能媒体上に記憶されたプログラム・コードを実行する単一のコンピュータ・システムを含む。別の実施形態では、階層保存手段 210 とオペレーション・エンジン 240 とは、2つ又はそれ以上の異なるプログラム・コードを実行する単一のコンピュータ・システム、又は2つ又はそれ以上の異なるプログラム・コードを実行する多数の別々のコンピュータ・システムの何れかを含むが、この場合、1つのコードは階層保存手段 210 の機能用であり、別のコードはオペレーション・エンジン 240 の機能用である。この実施形態では、階層保存手段 210 は、API を介してオペレーション・エンジン 240 にデータを選択的に送る。この実施形態では、本発明の階層保存手段 210 は、有用な階層データ出力を提供するために、現在存在するオペレーション・エンジン 240 と通信し、共に作動するように修正することができる。

10

#### 【0046】

上述したコンピュータ読み取り可能媒体は、ハードディスク、CD、フロッピーディスク、及びサーバーメモリを始めとするいずれのコンピュータ記憶装置ツールから成ってもよいがこれらに限定されるものではない。プログラム・コードを実行するコンピュータ・システムは、オペレーション・エンジン 240 と階層保存手段 210 との両方の場合においても、例えば、Windows NT (登録商標) オペレーティング・システム又は Sun Solaris (登録商標) ワークステーションを実行するデスクトップ・コンピュータを始めとして、相応しいものなら何れのコンピュータ・システムでもよい。

20

#### 【0047】

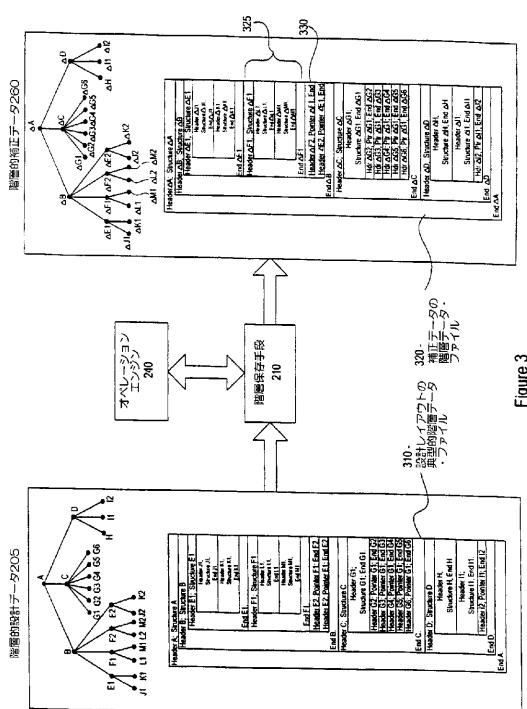

図 3 に移るが、これは図 2 のシステムの実施形態からの出力となる典型的な階層データ・ファイルを単純化して示したものである。補正データ 320 の階層データ・ファイルは、図 2 のシステムが図 1 の単純化された集積回路レイアウト 100 に関して作動するように適用された場合に生成される補正データの単純化バージョンを表している。上述のように、階層設計データ 205 は、階層補正データ 260 を提供するために、オペレーション・エンジン 240 と共に働く階層保存手段 210 に送信される。設計レイアウト 310 の単純化された階層データ・ファイルは、オペレーションの実行に際して、データの増加に本発明が及ぼす最少の効果を描くために示されている。というのは、図示のように、補正データの階層データ・ファイル 320 は、入力データ・ファイル 310 と 1 対 1 で対応する構造で記憶させることができるからである。これにより、マスク生産や設計ルール照合のような全体的に修正された設計に関する他の機能を実行するために、2つのデータ・ファイル 310 と 320 とを迅速に組み合わせを容易となる。

30

#### 【0048】

階層保存手段 210 がセルをトラバースするとき、階層保存手段 210 は、そのセルがすでにトラバースされたセルと同一であるか否かを判定することにも留意されたい。もし同一であるなら、階層保存手段は、上記セルに対するデルタ平面を直接確定するために処理時間を割くことはない。その代わりに、階層保存手段は、定義中の上記セルの第 1 インスタンスにポインタを提供することにより、真の階層を維持する。例えば、これは、図 1 に示すように、同一セルであるセル F1 と F2 とにより、補正データの階層データ・ファイル 320 により示される。先に述べたように、本発明の一実施形態では、階層保存手段 210 は、深度方向の形態で、葉ノードから最終的な親セルまで、設計データ 205 をトラバースする。このように、F1 は F2 の前にトラバースされることになり、このセルに対して、補正データ F1 は、ファイル 320 でラベル 325 により示されるように生成され記憶されることになる。しかしながら、セル F2 がトラバースされるときには、F1 用の補正データに対するポインタのみが記憶され、F2 に関しては、直接的な補正データは何も処理されない。これはラベル 330 により示される。このように、処理時間とデータボリュームとの両方が縮小される。

40

50

## 【0049】

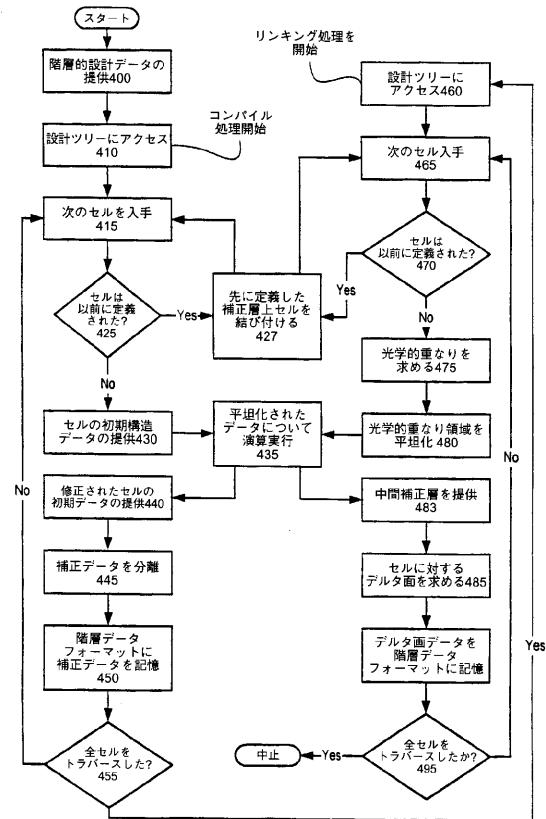

図4は、設計レイアウトの階層構造が本発明の一実施形態により維持される階層的集積回路設計に関する論理演算又は算術演算を行う方法を、フローチャート形式で示している。その最も単純なレベルでは、該方法はコンパイル処理とその後に続くリンク処理とから成っている。階層的設計データレイアウトが、ブロック400に提供されると、ブロック410で、先に図2と図3に関連して述べたやり方で設計ツリーにアクセスする。コンパイル処理はブロック415で開始されるが、ここではツリー内の第1セルに対する階層データが入手される。次にブロック425では、上記セルが以前に定義されているか否かが確認される。以前に定義されている場合には、入手されたセルは、以前に定義された補正データにブロック427で関連付けられ、ツリー中の次のセルがブロック415で入手される。上記セルが以前に定義されたことがない場合には、上記セルの平坦化された初期構造がブロック430で入手されて、ブロック435に送られ、そこで、その平坦化された初期データに関して、論理演算又は算術演算が実行される。次に、修正された平坦化された初期データがブロック440に送られ、次に、このデータは、スロック445で処理され、図2でJに関連して先に説明したように、所要の補正データを分離する。次に、分離された補正データは、ブロック450で原型設計データに対応する階層様式で記憶される。ブロック455では、セル全てがトラバースされたかどうかが確認される。トラバースされていたなら、リンク処理がブロック460で開始され、トラバースされていなかった場合には、全セルがトラバースされコンパイルされるまで、ブロック415でコンパイルが継続される。

10

20

## 【0050】

リンク処理は、コンパイル処理と同じやり方で、ブロック460で設計ツリーにアクセスすることから開始される。処理はブロック465で継続され、ここではツリー中の第1セルに対する階層データが入手される。次に、ブロック470で、上記セルが以前に定義されているか否かを確認する。以前に定義されている場合には、入手されたセルは、以前に定義された補正データにブロック427で関連付けられ、ツリー中の次のセルが、ブロック465で入手される。上記セルが、以前に定義されたことがない場合には、図2に関連して先に説明したように、上記セルの重なりがブロック475で確認される。次に、これらの重なり区域は、ブロック480で平坦化され、その平坦化されたデータがブロック435に送られ、ここでは先に論じたよう平坦化されたデータに関する論理演算又は算術演算が行われる。平坦化されたデータに関して行われたこの処理は、次に、ブロック483で中間補正層を生成するために使用され、ブロック485で、セルに対するデルタ平面が生成され、これがブロック490において階層的データ・フォーマットで記憶される。デルタ平面は、ツリー中の各セル毎に保存する必要のある唯一のデータである。先に述べたように、親セルとその子セルが決まると、親セルに対する補正情報とその子セル全部の補正データとの合計の差は、デルタ平面に等しいからである。従って、その後、階層ツリーの葉は、コンパイル時に確認された自身の補正面に等しいデルタ平面を有することとなる。ブロック495では、ツリー内のセル全てがトラバースされたかどうかを確認する。トラバースされていた場合は、処理は停止し、出力データは、先に述べたように、種々の機能のために使われるが、そうでない場合には、ツリー中の全セルがトラバースされてしまうまでブロック465でリンク処理が継続される。

30

40

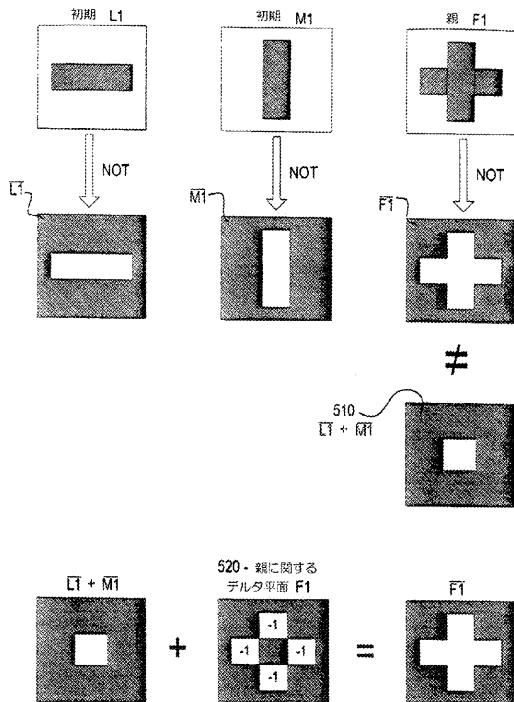

## 【0051】

図5は、本発明の特定の実施形態が、図1の親セルF1に関してどのように論理演算を実行するのかを示している。本例で必要とされているものは、親セルF1に関する論理NOT演算を実行することであると仮定する。必要とされている出力は、図5にF1(NOT)として示している。このオペレーションを直接実行することは、図4のブロック435に関連し先に述べた方法で、図2のオペレーション・エンジン240を使って、葉L1を表している平坦化されたデータに関してNOT演算を、そして、M1を表している平坦化されたデータに関してNOT演算を実行する。次に、これらのオペレーションの結果は、補正データが適当なノードに関係付けられるような階層的方法で記憶される。これらの結

50

果は、図5にL1(NOT)及びM1(NOT)として示している。しかしながら、本発明の教示が無ければ、単純にL1(NOT)とM1(NOT)とを合計することにより、必要とされるF1(NOT)を得ることはできない。このことを、L1(NOT)とM1(NOT)とを合計することにより得られる、間違った結果510により示している。

#### 【0052】

本発明の一実施形態は、正しい補正結果F1(NOT)を入手するために、次のようにオペレーションを行う。図2を参照すると、階層的設計データ205は、この単純な本例では、親セルF1を表すデータのみから構成されているが、このデータ205は、階層保存手段210のコンパイラ220に送られる。コンパイラ220は、葉L1を表す平坦化されたデータを、オペレーション・エンジン240に送るが、この場合、エンジン240は、供給されたデータに関して論理NOT演算を実行して、葉L1のNOTを表す平坦化されたデータを戻す。上に述べたように、コンパイラ220は次にL1に対する補正データを生成して、このデータを階層的補正データ・ファイル260に記憶する。同じ処理が、葉M1についても繰り返される。親セルF1に関する初期の幾何学形状が無いので、親セルF1のコンパイルは、F1に対する補正データを生成しない結果となる。F1のコンパイルの後、リンク230が働いて、リンクステップ中に親セルF1に対するデルタ平面520を生成するが、これについては図6に関連して後で詳しく説明する。デルタ平面520は、L1(NOT)及びM1(NOT)と合計されたとき、図5に示すように正しい要求される結果F1(NOT)が得られるように生成される。このデルタ平面データは、親セルF1に関するように、階層的補正データ・ファイル260に階層的に記憶される。本例は、本発明の一実施形態を、サンプルICレイアウトに関する特定の論理演算を実行する際に使用することについて示したものにすぎない。従って、本発明の本実施形態は、階層的方法で記述されたICレイアウトであれば如何なるICレイアウトでも、如何なる論理演算をも実行に用いることができるとは明らかである。

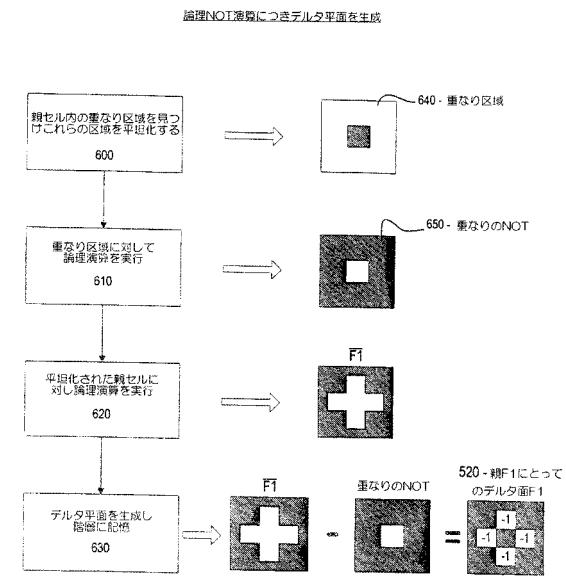

#### 【0053】

図6は、図5のデルタ平面520が本発明の一実施形態によりどのように生成されるかを帰納的に示している。図2に戻りこれを参照すると、オペレーション・エンジン240が、コンパイルステップ中に葉セルL1及びM1の平坦化された初期データに関してそれらに論理NOT演算を実行した後、階層保存手段210は、親F1のリンク中に作動して親セルと平坦化されたこれらの区域内に重なり区域を発見600し、重なり区域640を生成する。重なり区域640に対するこの平坦化されたデータは、次にブロック610でオペレーション・エンジン240に送られ、重なり650のNOTが、オペレーション・エンジン240により生成される。次に、論理NOT演算が、親F1に関して実行され、ブロック620で平坦化された形式のF1(NOT)を生成する。最後に、デルタ平面520は、重なり区域650のNOTと平坦化されたF1(NOT)との間の差をとることにより生成され、このデルタデータは階層的補正データ・ファイル260に記憶される。

#### 【0054】

OPC補正されたレイアウトを生成するためのシステムに、本発明を使用することについてこれより説明する。先に述べたように、集積回路設計の造形が次第に小型になるにつれ、光学的リソグラフィの解像限界が露光処理に及ぼす影響が増大する。例えば、回路形質のパターン現像における差は、形質相互間の近接度に左右されることが確認されている。近接効果は、間隔が非常に近接したパターン形質がウェーハのレジスト層にリソグラフィ転写されるときに起きる。間隔が非常に近接した形質部分の光波は相互作用しあって、その結果最終的転写パターン形質に歪が生じる。形質のサイズと間隔とがリソグラフィ・ツールの解像限界に近づいたときに起きる別の問題は、角(凹及び凸)がそれぞれの角にエネルギーが集中又は不足することにより過剰露光又は過小露光する傾向が強いということである。大型形質及び小型形質が同じマスク・パターンから転写される時には、小型形質の過剰露光又は過小露光という別の問題も起きる。

#### 【0055】

10

20

30

40

50

近接効果の問題を解決するために多くの方法が開発されてきた。これらの中には、マスク配線幅の予補償、フォトレジスト層厚の可変性、多重層フォトレジスト処理の使用、光学的結像と共に電子ビーム結像を使用すること、そして最後には、近接効果を補正するために原型マスク・パターンに付加的な形質を加えることが含まれる。この最後の方法は光学的近接補正(O P C)として知られている。

#### 【0056】

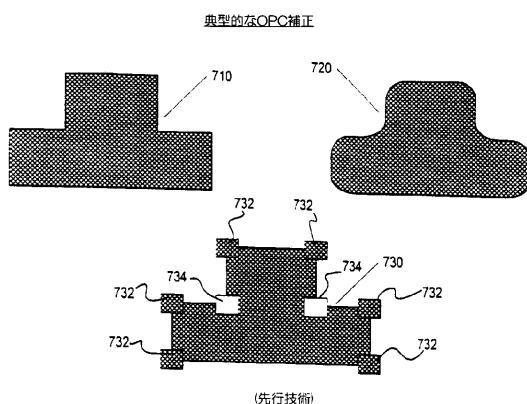

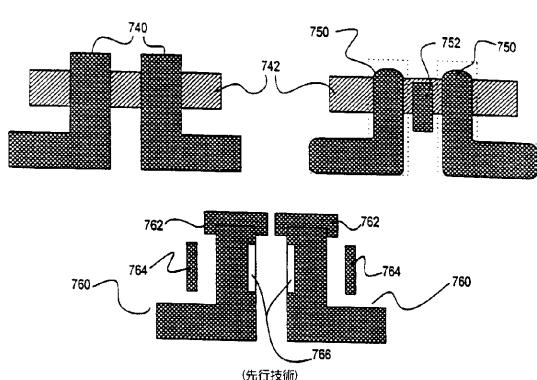

図7は、設計レイアウトに対して行うことが可能な光学的近接補正の例を示している。O P Cが使用されるときに原型マスクに加えられる追加形質は、通常サブ・リソグラフィ(即ち、露光ツールの解像度より小さな寸法を有する)であり、従ってレジスト層に転写されない。代わりに、それらは、最終的に転写されるパターンを改良し近接効果を補正するように、原型パターンと相互作用し合う。例えば、図7に示すように、所要パターン710が、近接効果に対する補正無しにリソグラフィ転写された場合には、実際にはパターン720のようになる。O P C手法を用いると、正のセリフ732と負のセリフ734とが所要パターン710に加えられて、近接効果を補正するために必要なマスク730を形成することができる。同様に、図7では、典型的な所要トランジスタ・ゲート・パターン740上の近接歪の効果を、実際に転写されたパターン750と752により示している。ハンマーヘッド762、補助棒764、及びバイアス棒766により表されるO P C補正が、原型の所要マスク・パターンに加えられると、原型の所望形状がより正確に転写されることになる。トランジスタ・ゲートの場合、ハンマーヘッド形状762は、配線の端が短くなるという影響を排除して、ゲートのポリシリコン部が、アクティブ領域742を越えて確実に延びるように設計されている。補助棒764は、転写されたゲートパターンの幅を縮小させる傾向にある分断ゲート効果を補正するよう設計されている。最後に、バイアス棒766は、追加的な転写パターン752により示される、密に詰め込まれたゲートの影響を排除するために設計されている。幾つかの例では、現に存在するO P Cプロダクトは、ルールをベースとしたアルゴリズムを用いて特定の幾何学形状に対する近接補正を生成する。このタイプのシステムでは、設計レイアウトは、予め定められたレイアウト・パターンについて分析され、先に述べたタイプのO P C形質の内の1つが、設計レイアウトのその区域に対して生成される。しかしながら、本発明の一実施形態とは違い、以前のO P Cプロダクトは原型設計レイアウトの真の階層的データ構造を維持する能力は無い。

#### 【0057】

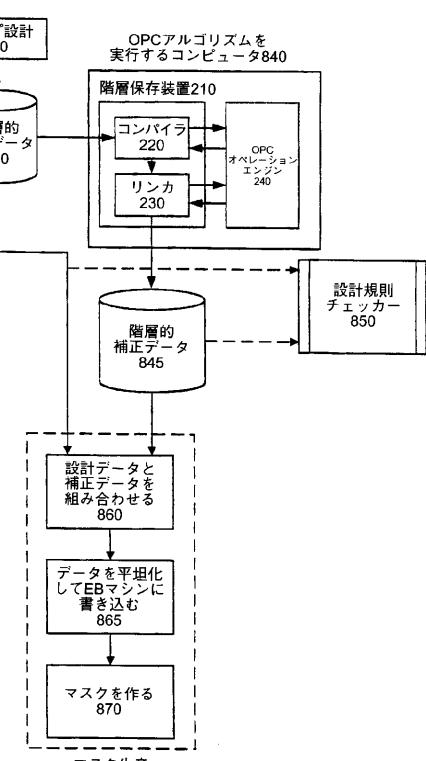

I C設計レイアウトに対するO P C補正の生成に供されると同時に、原型設計レイアウトの真の階層的データ構造を維持することが可能な本発明の一実施形態について、図8を参照し、以下に説明する。図8のシステムは、図2と図4それぞれにつき説明したシステム及び方法の特定の実施形態であるので、この説明には、参考として図2及び図4についての上記説明が含まれる。

#### 【0058】

図8において、集積回路チップ設計800は、階層設計データ810により表されており、それは一実施形態ではG D S - IIデータ・フォーマットで表されている。設計データ810は、本発明の一実施形態を組み入れているO P Cアルゴリズム840を実行するコンピュータ・システムに対する入力として提供される。コンピュータ・システム840は図2と図4に関連し先に説明した方法で階層的補正データ845を作り出すために作動する。これに関連して、コンピュータ・システム840は図2の階層保存手段210とオペレーション・エンジン240との両方を含んでいるが、コンピュータ・システム840のこのオペレーション・エンジン240は、入力設計データ810に関し作動して光学的近接補正を行う、明確に定義されたO P Cオペレーション・エンジン240である。

#### 【0059】

図8に示すように、出力階層的補正データ845は、O P C補正設計の設計ルール照合を行うために、原型設計データ810と共に従来型の設計ルール・チェック850に送られる。同様に、この出力は、ブロック860に示すように設計データ810を補正データ

10

20

30

40

50

845に組み合わせることにより、リソグラフィマスクを作るために使うこともできる。次に、この組み合わされたデータは、平坦化されて、EB装置が作動してマスク870を作るために、ブロック865に示すようにEB装置に書き込まれる。

#### 【0060】

図8のシステムの一実施形態では、コンピュータ・システム840は、コンパイラ220、リンク230、及びOPCオペレーション・エンジン240の機能を果たすコンピュータ読み取り可能媒体上に記憶されたコンピュータ・プログラム・コードを実行する。別の実施形態では、コンピュータ・システム840は、2つ又はそれ以上の異なるプログラム・コードを実行する単一のコンピュータ・システム、又は2つ又はそれ以上の異なるプログラム・コードを実行する多数の個別コンピュータ・システムの何れかを含むが、1つのプログラム・コードは階層保存手段210の機能用のもので、別のプログラム・コードはOPCオペレーション・エンジン240の機能用である。この実施形態では、階層保存手段210は、APIを介してOPCオペレーション・エンジン240にデータを選択的に送る。この実施形態を用いる場合は、本発明の階層保存手段210は、階層データ出力を役立てるために、現に存在しているOPCオペレーション・エンジン240と通信し作動するように修正することもできる。10

#### 【0061】

上記のコンピュータ読み取り可能媒体は、ハードディスク、CD、フロッピーディスク、及びサーバーメモリを始めとする何れのコンピュータ記憶装置ツールを含んでもよいが、これらに限定される訳ではない。プログラム・コードを実行するコンピュータ・システムは、OPCオペレーション・エンジン240と階層保存手段210との両方の場合においても、例えばWindows NT(登録商標)オペレーティング・システム又はSun Solaris(登録商標)ワークステーションを実行するデスクトップ・コンピュータを始めとして、相応しい何れのコンピュータ・システムで構成してもよい。20

#### 【0062】

単に、階層的入力が与えられることによりOPC補正を行うオペレーション・エンジンは、当分野で公知である。図8のシステムの一実施形態では、OPCエンジン240は、システムのユーザーが制御できる方法でOPC形質を生成することが可能な、ルールをベースとしたOPCである。例えば、ユーザーは、使用すべき補正ルール、及び 設計レイアウトに使用すべき形質のサイズを定義することができる。更に、システムの一実施形態では、バイアス配線766の場所とサイズとを、補正中のICパターン形質のサイズとピッチとにより変え、及び/又は、トランジスタ・ゲート領域のような設計の重大な区域だけに使用を限定することもできる。更に、本システムの別の実施形態では、OPCエンジン240は、トランジスタ・ゲートのような重大区域に範囲を限定した方法又は全体的なIC設計に範囲を広げた方法の何れでも、補助形質764を応用することもできる。更に本システム別の実施形態では、OPCエンジンは、重大区域に補正形質を選択的に配置すると同時に、正確な回路性能のためには補正形質を必要としない区域にはそれらを配置しないようにもできる。本実施形態の一例では、OPCエンジンはバイアス及び補助形質をトランジスタ・ゲートに配置するように制限し、ポリシリコンゲート層の重要でない連結領域は補正されないままとすることもできる。また。他の例では、OPCエンジンは重大なトランジスタ・ゲート線端を区別して、ハンマー・ヘッド補正をこれらの区域に適用して線端が短くなるのを緩和する。最後に、本発明の他の実施形態では、OPCオペレーション・エンジンは、本願で先に援用したファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲン・シュー・C・パティの発明になる1997年9月17日出願の出願番号第08/931,921号「位相シフト回路製造方法及び装置」と題する米国特許出願に開示されているもののような位相シフト・マスクのOPC補正に供することもできる。3040

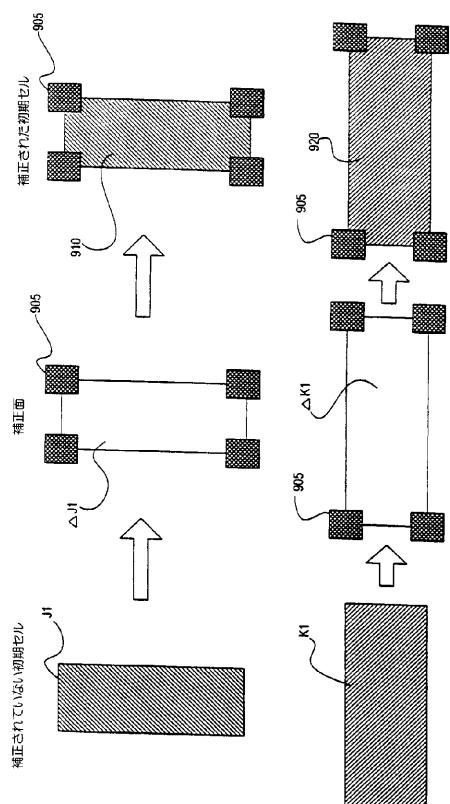

#### 【0063】

図9は、図8のシステムの一実施形態が、図1の葉セルJ1とK1との初期幾何学形状のOPC補正にどのように供されているかを示している。親セルE1の補正されていない葉セルJ1とK1とを示している。J1の平坦化された初期幾何学形状データが、階層保存50

手段 210 に送られると、コンパイラ 220 は OPC エンジン 240 と共に作動して、図 2 に関連し先に論じた方法で補正面 J1 を準備する。この事例では、OPC エンジンは、マスクが生産されウェーハを露光するために使用されるとき正しい結果を出すためには、J1 の初期幾何学形状が正のセリフ 905 を必要とすることを、自身のルール定義に基づき決定している。同じ処理が、補正面 K1 を生成するために、K1 の平坦化された初期幾何学形状に関しても実行されるが、ここでもやはり正のセリフ 905 が含まれている。次に、これらのセルの各々は、先に述べたように、リンク 230 によりリンクされて各セル毎にデルタ平面を生成する。これらのセルは葉ノードであり重なり区域を持たないので、それら各自のデルタ平面は、それらのコンパイルされた補正面に等しい。更に、補正された葉セル 910 と 920 を示しているが、それらは J1 + J1、及び K1 + K1 をそれぞれ表している。

#### 【0064】

図 10 (a) - (b) は、本発明の一実施形態による、図 4 の方法が、OPC オペレーションに関し、図 1 の親セル E1 内の重なり区域に対して、どのように中間補正面層を生成するかを示している。図 10 (a) は、補正済みの葉セル J1\_910 と、補正済みの葉セル K1\_920 の間の重なり区域 1000 を示している。図 2 及び図 4 に関連し先に述べたように、セル E1 に対するリンク処理中に、この重なり区域が確認され、この区域に対応するデータが平坦化される。平坦化された重なり区域は、次に、中間補正面 1020 を準備するために、上記データに関し作動する OPC オペレーション・エンジン 240 に送信される。ここに述べた事例のように、離散量が重ね合わされている初期構造では、負のセリフ 1010 が中間補正面用に準備されることに留意されたい。図 10 (b) に関連し以下に説明する状況では、代理親セル E1 が図示されており、補正された葉セル K1 及び K2 は、それぞれ 910b と 920b として示されている。この状況は 2 つの補正済み初期幾何学形状間の重なりが微小であることを示している。本発明の一実施形態では、中間補正面 1020b は、エッジ突合せ効果を補償するために -2 層が準備されるよう、これらの微小の重なり状況のために提供される。

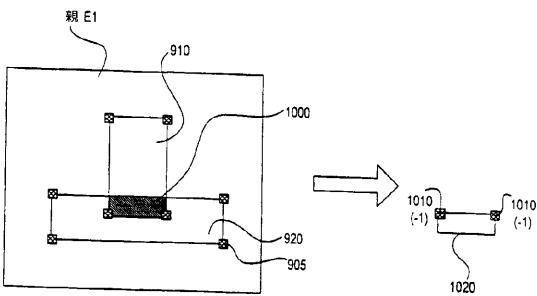

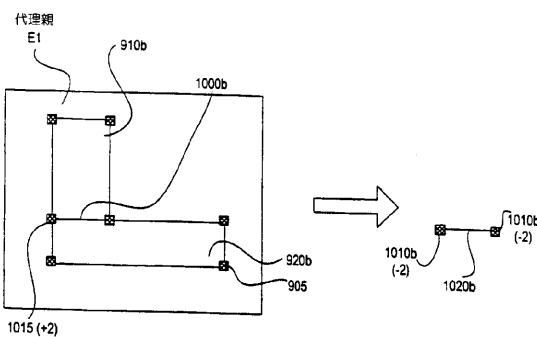

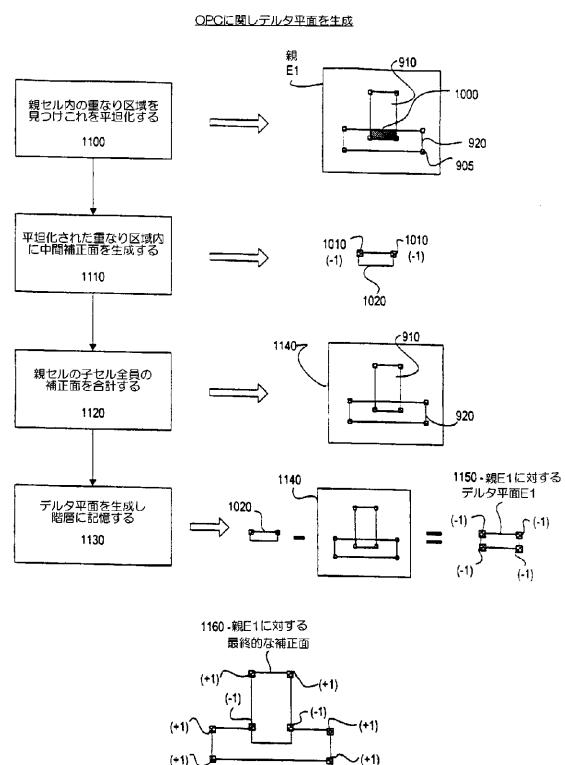

#### 【0065】

図 11 は、本発明の一実施形態による OPC オペレーションに対し、図 4 の方法が、図 1 の親セルのデルタ平面をどのように生成するかを示している。ブロック 1100 により説明するように、セル E1 についてのリンクステップで、E1 内の重なり区域が確認され、その区域データが平坦化される。これを重なり区域 1000 として示している。次に、ブロック 1110 により説明するように、この重なり区域 1100 に対する中間補正面 1020 が、図 10 (a) に関し先に説明したように生成される。ブロック 1120 では、E1 の子セル全ての補正面 910 と 920 とが合計され、合計された子セルの補正データ 1140 を生成する。ブロック 1130 により説明する最後のステップは、セル E1 に対するデルタ平面 1150 を生成して、このデータを階層的に記憶する。これは、一実施形態では、合計された子セルの補正データ 1140 を中間補正面 1020 から引いて、デルタ平面 1150 を求めることにより実現される。図 11 には、セル E1 の最終的補正面 1160 も示しているが、これは先に定義したように、ここでは OPC である特定のオペレーションをセルに対し正しく適用するために、セル設計データに適用する必要がある補正の総計を表している。補正面 1160 は、E1 のデルタ平面に E1 の子セル J1 と K1 それぞれの補正面 910 と 920 とを加えたもので構成される。

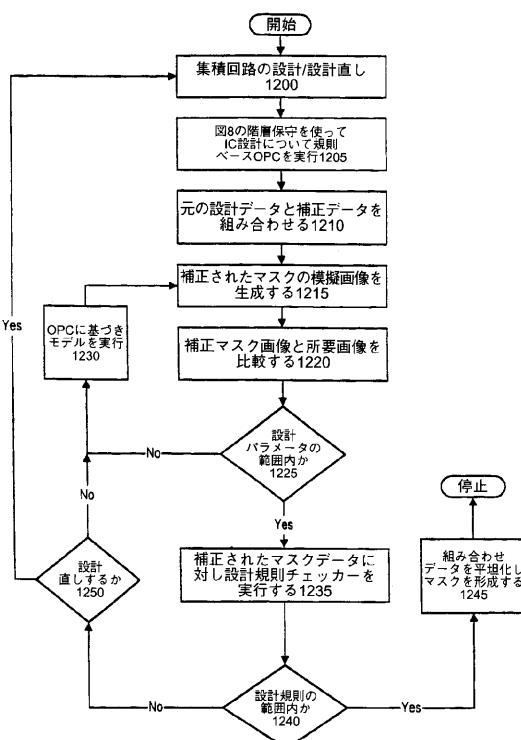

#### 【0066】

図 12 は、本発明の一実施形態を使って、設計レイアウトに OPC 補正を提供するための方法を示している。ブロック 1200 で、集積回路設計レイアウトがまず提供される。この設計レイアウトに対応する階層フォーマットの設計データが、次に、システムに送られるが、このシステムはブロック 1205 に示すように図 8 のシステムにより設計データに関するルールを基本とした OPC 補正を行う。図 8 のシステムが上に説明したように階層的補正データの出力を生成し、この補正データは、原型設計データに組み合わされてブロック 1210 に示すように、階層的に記述されたルールを基本とする OPC 補正設計データ

タを生成する。この補正済み設計データを使って、ブロック 1215 で、この補正済み設計データが作り出すことになるマスクの模擬画像が生成される。このシミュレーションは、それぞれ先に本願でも援用しているが、ファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる 1997 年 9 月 17 日出願の出願番号第 60/059,306 号「マスクの照合、補正、並びに設計ルール照合」と題する米国仮特許出願、ファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティの発明になる 1998 年 9 月 16 日出願の「マスクの照合、補正、並びに設計ルール照合」と題する米国特許出願、及び更に明確にはファン・チェン・チャン、ヤオ・ティン・ワン、ヤゲンシュ・C・パティ、及びリナード・カークリンの発明になる 1998 年 8 月 7 日出願の「視認検査と照合システム」と題する米国特許出願に概括的に説明されたようなホプキンス方程式を基本とするシミュレーション機器を使って生成することができる。10

#### 【0067】

次に、補正マスクの模擬画像は、ブロック 1220 で、必要とされる設計画像と比較され、ブロック 1225 に示すように最初のルールを基本とした OPC 補正がユーザーの定義した設計パラメータのセットの範囲内で設計を補正するのに十分であるか否かが判定される。この比較を実行するための方法は「マスクの照合、補正、及び設計ルール照合」と題する先に述べた米国仮特許出願及び同名の米国実用特許出願に開示されている。比較の結果が設計パラメータは達成されたとするものであれば、ブロック 1235 に示すように、補正済みの設計データは、特定の集積回路設計に対して確立された設計ルールのあらゆる違反に対して補正済みデータを分析する設計ルール・チェックにに入力されることになる。補正済み設計が、設計ルールの範囲内にある場合は、補正済みデータは平坦化されて、ブロック 1245 に示すように EB 装置を使ってマスクが製作される。設計ルールが満たされなかった場合、ブロック 1250 に示すようにマスクを設計し直すか否かに関する決定が下される。20

#### 【0068】

決定がマスクの設計し直しは行わずインタラクティブな補正処理を継続することにより問題の解決を図ろうというものであれば、モデルベースの OPC アルゴリズムが補正設計に関し実行される。同様に、原型補正済み設計データが、ブロック 1225 の設計パラメータを満たさない場合には、原型補正済み設計データはモデルベースの OPC アルゴリズムに入力される。モデルベースの OPC アルゴリズムは、次にブロック 1230 に示すように、原型補正済み設計に対して、より細かい仕様の補正を実行する為に使われる。モデルベースの OPC 補正設計は、次に、ブロック 1215 に送られ、ここでモデルベースの OPC 補正設計の模擬画像が作られ、所望される設計と再度比較される。OPC 補正設計を設計の分析のために従来型の設計ルール・チェックプロダクトに入力する前に、モデルベースの OPC 補正が行われた設計の模擬画像は、従来型の設計ルール・チェックに受入れられるフォーマットへと処理される必要がある。これを行う 1 つの方法は、エッジ照合手法に基づく模擬画像のマンハッタン幾何学表現を生成することであるが、これについては先に挙げ、本願に援用している「マスク照合、補正、及び設計ルール照合」と題する米国仮特許出願、並びに同名の米国実用特許出願により詳しく説明されている。この全体処理過程は、ユーザーが定義した設計パラメータ及び回路仕様設計ルールの両方を満たす補正設計が作り出されるまで継続される。3040

#### 【0069】

この処理の一実施形態では、モデルベースの OPC アルゴリズムは、ユーザーが定義した入力に応答可能である。例えば、一実施形態では、ユーザーは、データボリュームと全体的な処理速度を制御するために適用したいと考えている補正の複雑性レベルを制御することができる。同様に、別の実施形態では、ユーザーはモデルベースのアルゴリズムにより適用される補正形状のサイズを制御することができる。更に、別の実施形態では、ユーザーはアルゴリズムにより適用される補正基準を定義することができる。

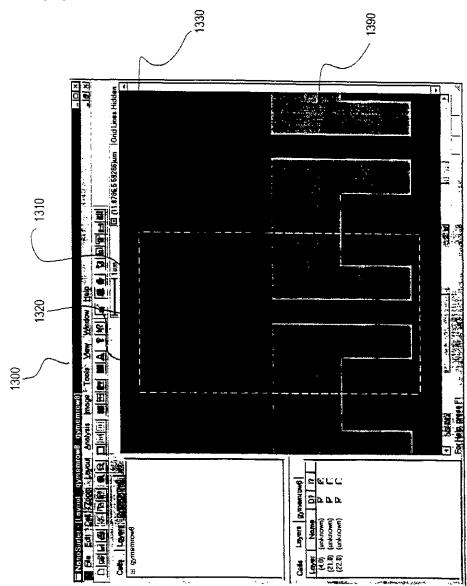

#### 【0070】

残る図 13 から図 19 は、階層的入力 IC 設計レイアウトに対する OPC 補正を提供する50

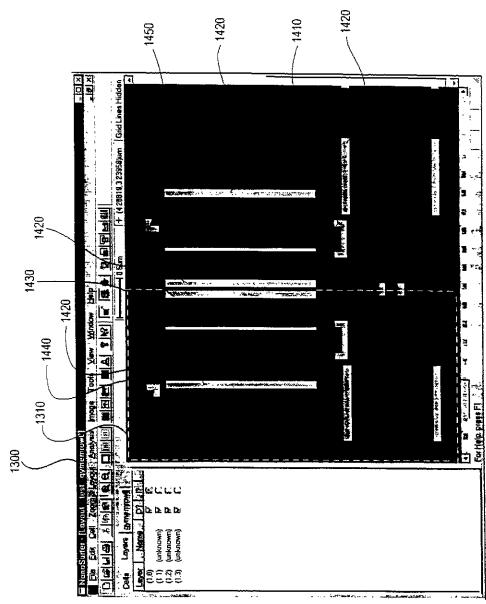

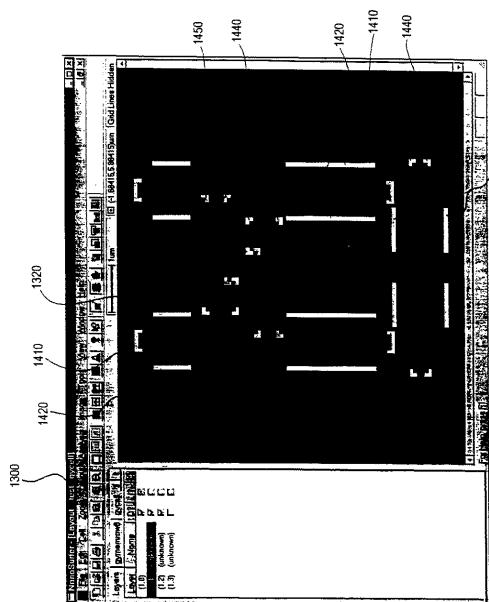

ために、本発明の一実施形態を実行しているコンピュータ・システムからのスクリーン・スナップショットの例を示している。例えば図13は、OPC補正予定の入力設計レイアウトのスクリーン・スナップショットの一例を示す。設計プログラムのユーザーインターフェース1300は、設計ウインドウ1330を含むが、ここにはIC設計レイアウトの補正される部分が示されている。設計レイアウトには、拡散層1390と初期構造のようなポリシリコン構造の層1320が含まれている。セル1310は、図1のサンプルの親セルE1及びF1と同じであるが、これも設計ウインドウ1330に描かれている。

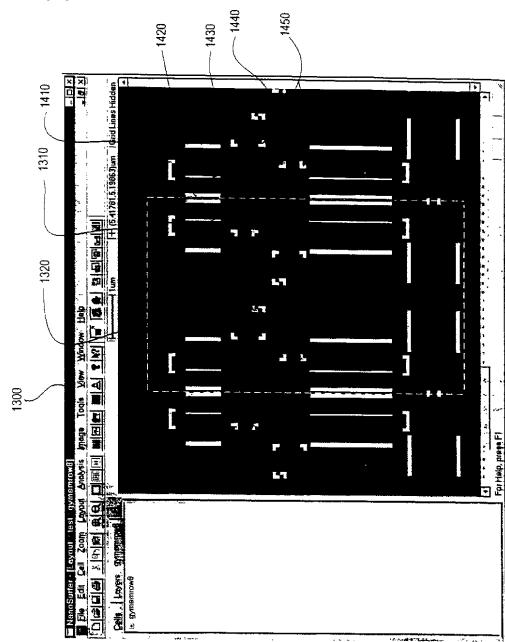

#### 【0071】

図14は、図13の入力設計に対しOPC補正を提供するために、本発明の一実施形態を実行しているコンピュータ・システムからの最終的な出力のスクリーン・スナップショットの一例を示す。ユーザー・インターフェースの設計ウインドウ1330は、OPC補正済みの初期構造1320を含むセル1310を示している。セル1310は、ハンマーへッド1410、補助配線1420、バイアス配線1430、正のセリフ1440、及び負のセリフ1450のようなOPC形状を含む。図14に示す出力は、設計全体への全OPC効果を補正するためになされるべき補正の全てを表している。こうして、これらの補正是、本発明のこの実施形態での最終的なリンク済みの出力を表すが、ここでは階層中におけるセル間の全ての重なりが既に解像され、補正されている。図14に示すOPC形状を、図14のスクリーンスナップの例をズームした図15により詳しく示す。

10

#### 【0072】

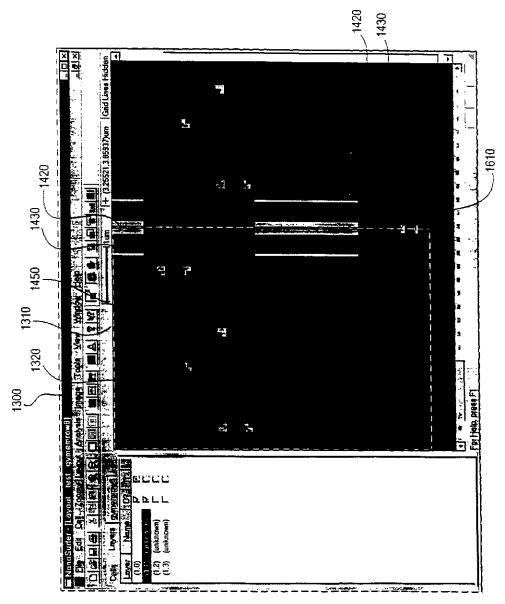

図16は、OPC補正を提供するために本発明の一実施形態を実行しているコンピュータ・システムからの-1OPC補正層のスクリーン・スナップショットの例を示している。この層は、補助配線1420、バイアス配線1430、及び負のセリフ1450を含むセル1310に対する補正を含んでいる。

20

#### 【0073】

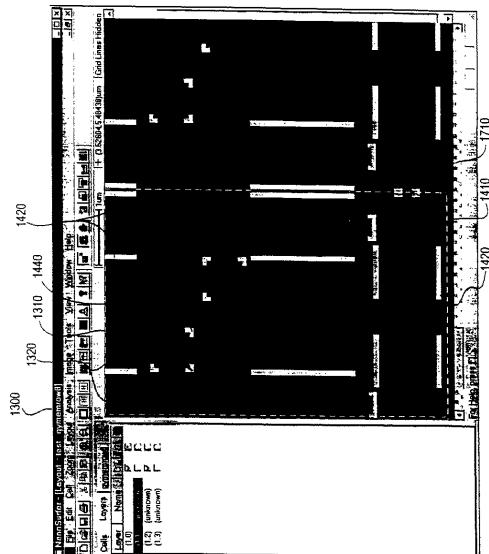

図17は、OPC補正を提供するために本発明の一実施形態を実行しているコンピュータ・システムからの+1OPC補正層のスクリーン・スナップショットの例を示している。この層は、ハンマーへッド1410、補助配線1420、及び正のセリフ1440を含むセル1310に対する補正を含んでいる。

#### 【0074】

図18は、OPC補正を提供するために本発明の一実施形態を実行しているコンピュータ・システムからの-2OPC補正層のスクリーン・スナップショットの例を示している。この層は、エッジ突合せ補正形質1810を含むセル1310に対する補正を含んでいる。

30

#### 【0075】

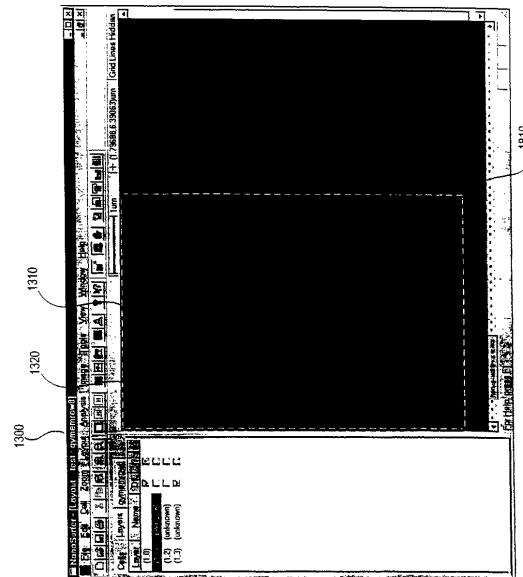

図19は、本発明の一実施形態を実行しているコンピュータ・システムにより、OPC補正された個別セル1310のスクリーン・スナップショットの一例を示す。設計ウインドウ1330は、リンクされた補正層が適用された状態のセル1310を示している。セル1310に適用された補正にはハンマーへッド1410、補助配線1420、正のセリフ1440、及び負のセリフ1450が含まれている。セル1310に対する補正是図14に示すものとは異なり、図14では設計全体への補正全てを表現しているが、図19ではセル1310を個別に補正するために必要な補正しか示していない。換言すれば、図19に示す補正是、セル1310と他の隣接するセルとの間の相互作用を考慮していないということである。例えば、図14のバイアス配線1430が図19には無いことに注目されたい。

40

#### 【0076】

本発明の説明に役立つ実施形態につき、添付の図面を参照しながらここで詳細に記述してきたが、本発明はこれらの実施形態だけに限定されないことを理解されたい。それらは本発明を開示された厳密な形態に限定したり制限したりすることを意図するものではない。このように、多くの修正及び変更のできることは当業者には明らかであろう。従って、本発明の範囲は上記請求の範囲及びその均等物によって定義されるものとする。

50

**【図面の簡単な説明】**

図面は、例により発明を説明するものであり、限定を加えるものではない。類似符号は同様の構成要素を指す。

**【図 1】** 単純な集積回路設計レイアウト及び上記レイアウトの階層ツリー表現を示す図である。

**【図 2】** 本発明の一実施形態のシステムレベルの描写を示す図である。

**【図 3】** 図 2 のシステムからの出力となる典型的な階層的データ・ファイルの簡潔な表現を示す図である。

**【図 4】** 本発明の一実施形態による、設計レイアウトの階層構造が維持される、階層的集積回路設計に関する論理演算又は算術演算を実行する方法をフローチャート形式で示す図である。10

**【図 5】** 本発明の一実施形態による、図 4 の方法が、図 1 の親セルの 1 つに関してどのように論理 NOT 演算に備えるかを示す図である。

**【図 6】** 本発明の一実施形態による、図 4 の方法が、論理NOT演算に関する図 1 における親セルの 1 つのデルタ平面を、どのように生成するかを示す図である。

**【図 7】** 設計レイアウトに対し行うことのできる光学的近接補正の例を示す図である。

**【図 8】** 本発明の一実施形態による、設計レイアウトに OPC 補正を提供するためのシステムを示す図である。

**【図 9】** 図 8 のシステムの一実施形態が、図 1 におけるセルの 1 つの初期幾何学形状の OPC 補正にどのように備えるかを示す図である。20

**【図 10 ( a )】** 本発明の一実施形態による図 4 の方法が、OPC オペレーションのための図 1 における親セルの 1 つの重なり区域に対してどのように補正層を生成するかを示す図である。

**【図 10 ( b )】** 本発明の一実施形態による図 4 の方法が、OPC オペレーションのための図 1 における親セルの 1 つの重なり区域に対してどのように補正層を生成するかを示す図である。

**【図 11】** 本発明の一実施形態による図 4 の方法が、OPC オペレーションのための図 1 における親セルの 1 つのデルタ平面をどのように生成するのかを示す図である。

**【図 12】** 本発明の一実施形態を使って、集積回路設計レイアウトに対して OPC 補正を提供するための更なる方法を示す図である。30

**【図 13】** 入力設計レイアウトの OPC 補正を提供するために、本発明の一実施形態を実行するコンピュータ・システムからの入力設計レイアウトのスクリーン・スナップショットの一例を示す図である。

**【図 14】** 図 13 の入力設計に対して OPC 補正を提供するために本発明の一実施形態を実行するコンピュータ・システムからの最終的な出力のスクリーン・スナップショットの一例を示す図である。

**【図 15】** 図 14 の最終的な出力のスクリーン・スナップショットの一例を拡大して示した図である。

**【図 16】** OPC 補正を提供するために本発明の一実施形態を実行するコンピュータ・システムからの - 1 OPC 補正層のスクリーン・スナップショットの一例を示す図である。40

**【図 17】** OPC 補正を提供するために本発明の一実施形態を実行するコンピュータ・システムからの + 1 OPC 補正層のスクリーン・スナップショットの一例を示す図である。

**【図 18】** OPC 補正を提供するために本発明の一実施形態を実行するコンピュータ・システムからの - 2 OPC 補正層のスクリーン・スナップショットの一例を示す図である。

**【図 19】** 本発明の一実施形態を実行するコンピュータ・システムにより OPC 補正された個々のセルのスクリーン・スナップショットの一例を示す図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

Figure 6

Figure 5

【図7(a)】

【図7(b)】

【図8】

Figure 8

【図 9】

Figure 9

【図 10 (a)】

Figure 10(a)

【図 10 (b)】

Figure 10(b)

【図 11】

Figure 11

【図 12】

Figure 12

【図13】

Figure 13

【図14】

Figure 14

【図15】

Figure 15

【図16】

Figure 16

【図17】

Figure 17

【図18】

Figure 18

【図19】

Figure 19

---

フロントページの続き

(31)優先権主張番号 60/069,549

(32)優先日 平成9年12月12日(1997.12.12)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/130,996

(32)優先日 平成10年8月7日(1998.8.7)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/153,783

(32)優先日 平成10年9月16日(1998.9.16)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/154,397

(32)優先日 平成10年9月16日(1998.9.16)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/154,415

(32)優先日 平成10年9月16日(1998.9.16)

(33)優先権主張国 米国(US)

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100141553

弁理士 鈴木 信彦

(72)発明者 チャン ファン チェン

アメリカ合衆国 カリフォルニア州 94043 マウンテン ヴィュー ロック ストリート

2434 - #9

(72)発明者 ワン ヤオ チン

アメリカ合衆国 カリフォルニア州 94086 サニーヴェイル コート マデラ アベニュー

970 - #311

(72)発明者 パティー ヤージエンシュ シー

アメリカ合衆国 カリフォルニア州 94024 ロス アルトス アムバー レーン 816

合議体

審判長 北川 清伸

審判官 伊藤 幸仙

審判官 森林 克郎

(56)参考文献 特表平11-509006号公報

特開平6-242595号公報

特開平3-80525号公報

欧州特許第927381号明細書

(58)調査した分野(Int.Cl., DB名)

G03F1/08

G03B1/08

G06F17/50