## SCHWEIZERISCHE EIDGENOSSENSCHAFT

BUNDESAMT FÜR GEISTIGES EIGENTUM

#### **® CH 656745 A5**

(51) Int. Cl.4: H01 L

29/78

## Erfindungspatent für die Schweiz und Liechtenstein

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

# 12 PATENTSCHRIFT A5

(21) Gesuchsnummer:

5338/81

(73) Inhaber:

International Rectifier Corporation, Los Angeles/CA (US)

(22) Anmeldungsdatum:

18.08.1981

(30) Priorität(en):

18.08.1980 US 178689

(72) Erfinder:

Lidow, Alexander, Manhattan Beach/CA (US) Herman, Thomas, Redondo Beach/CA (US)

(24) Patent erteilt:

15.07.1986

Patentschrift

veröffentlicht:

15.07.1986

Vertreter: E. Blum & Co., Zürich

## 64 Hochstrom-MOS-Feldeffekttransistor.

(57) Mehrere Source-Zellen (220, 221) sind an der Oberfläche eines Halbleiterchips angeordnet. Eine Drain-Elektrode (270) ist an der Unterseite des Chips vorgesehen. Die Source-Zellen (220, 221) besitzen eine sechseckförmige Konfiguration und sind jeweils von einem schmalen, sechseckförmigen Leiterbereich (130) umgeben, der unter einem Gate-Oxid (131) liegt. Das Halbleitermaterial unterhalb des Gate-Oxids (131) besitzt eine verhältnismässig hohe Dotierungskonzentation (N+) und Leitfähigkeit, wobei diese in seitlicher Richtung einen konstanten Wert besitzt. Dadurch wird der Wert der Lawinendurchbruchspannung verbessert und die Gefahr eines zweiten Durchbruchs verringert.

### PATENTANSPRÜCHE

- 1. Hochstrom-MOSFET-Anordnung, bestehend aus einem Halbleiter-Chip mit zwei zueinander parallelen Hauptoberflächen, mit einem sich von der einen Oberfläche des Chips wenigstens über einen Teil der Dicke des Chips erstreckenden Halbleiterkörperbereich [100, N(-)] mit einer relativ niedrigen Dotierung eines ersten Leitfähigkeitstyps; mit mehreren über die erste Chip-Oberfläche verteilten und sich in diese hineinerstrekkenden örtlichen Bereichen (113, 160; 114, 161) eines zweiten Leitfähigkeitstyps; mit mehreren sich jeweils in entsprechende dieser örtlichen Bereiche hinein erstreckenden Source-Bereichen (170, 171), die eine geringere Tiefe als der jeweilige zugeordnete örtliche Bereich (113, 114) besitzen und deren Aussenumfangsrand innerhalb des betreffenden örtlichen Bereichs in einem festen gegebenen Abstand von dessen Aussenumfangsrand an der 15 ersten Chip-Oberfläche verläuft, derart, dass kurze invertierbare Leitungskanäle (172, 173) gebildet werden, wobei die einzelnen örtlichen Bereiche an der ersten Chip-Oberfläche jeweils gemäss einem symmetrischen Netzgitter des Halbleiterkörperbereichs (100) voneinander getrennt sind; mit einer netzgitterförmigen Gate-Isolierschicht (131), welche sich über das erwähnte Netzgitter zwischen den örtlichen Bereichen erstreckt und die die örtlichen Bereiche umgebenden kurzen Leitungskanäle (172, 173) überlappt; mit einer auf der Gate-Isolierschicht (131) angeordneten netzgitterartigen Gate-Elektrode (132); mit einem ver- 25 tikalen leitenden Bereich [130, N(+)], der sich von unterhalb der Gate-Isolierschicht (131) zwischen jeweils benachbarten örtlichen Bereichen (113, 160; 114, 161) in Richtung auf die zweite Chip-Hauptoberfläche (270) erstreckt, wobei dieser vertikale leitende Bereich [130, N(+)] auf eine Tiefe unterhalb der ersten 30 ist, dass die Gate-Isolierschicht (131) aus einem Oxyd und die Chip-Oberfläche, die kleiner als die Tiefe der erwähnten örtlichen Bereiche (113, 114) ist, eine höhere Dotierungskonzentration als der erwähnte relativ niedrig dotierte Halbleiterkörperbereich [100, N(-)] besitzt, dadurch gekennzeichnet, dass die Dotierungskonzentration in dem vertikalen leitenden Bereich [N(+), 130] in seitlicher Richtung entlang der ersten Chip-Oberfläche unterhalb der Isolierschicht (131) einen konstanten Wert besitzt.

- 2. MOS-FET-Anordnung nach Anspruch 1, dadurch gekennzeichnet, dass die Dotierungskonzentration des vertikalen leitenden Bereichs [130, N(+)] unterhalb der Gate-Isolierschicht (131) mit zunehmender Tiefe unterhalb der ersten Chip-Oberfläche abnimmt und jeweils auf jedem Niveau einen konstanten Wert besitzt.

- 3. MOS-FET-Anordnung nach Anspruch 1 oder 2, dadurch 45 der DOS 2 940 699 beschrieben. gekennzeichnet, dass mit den einzelnen Source-Bereichen (170, 171) eine sich über die erste Chip-Oberfläche erstreckende Source-Elektrode (210) und mit der zweiten Chip-Oberfläche eine Drain-Elektrode (270) verbunden ist.

- 4. MOS-FET-Anordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der vertikale leitende Bereich [130, N(+)] eine Tiefe von etwa 1 Mikron unterhalb der ersten Chip-Oberfläche aufweist.

- 5. MOS-FET-Anordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die erwähnten örtlichen Bereiche (113, 160; 114, 161) mit dem zweiten Leitfähigkeitstyp und die Source-Bereiche (170, 171) einander entsprechende polygon- bzw. vieleckförmige Umfangsränder (140, 141, 142) aufweisen.

- 6. MOS-FET-Anordnung nach Anspruch 5, dadurch gekennzeichnet, dass die örtlichen Bereiche mit dem zweiten Leitfähigkeitstyp (113, 160; 114, 161) und die Source-Bereiche (170, 171) einander entsprechende sechseckförmige Umfangsbereiche aufweisen.

- 7. MOS-FET-Anordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die örtlichen Bereiche des zweiten Leitfähigkeitstyps jeweils einen tiefen Mittelbereich (113, 114) und einen flachen äusseren Umfangsbereich

- (160, 161) aufweisen und dass die Source-Bereiche (170, 171) jeweils über den flachen äusseren Umfangsbereichen (160, 161) ihrer zugehörigen örtlichen Bereiche liegen.

- 8. MOS-FET-Anordnung nach einem der vorhergehenden 5 Ansprüche, dadurch gekennzeichnet, dass auf der netzgitterförmigen Gate-Elektrode (132) wenigstens ein länglicher Gate-Kontakt (260) zur Kontaktierung des Netzgitters vorgesehen ist und dass der längliche Gate-Kontakt (260) koplanar mit der Source-Elektrode (250) und elektrisch von dieser isoliert ist.

- 9. MOS-FET-Anordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der Chip mit einem sich um den Aussenumfang der ersten Oberfläche herum erstreckenden potential-freien Schutzring (120) von dem zweiten Leitfähigkeitstyp versehen ist.

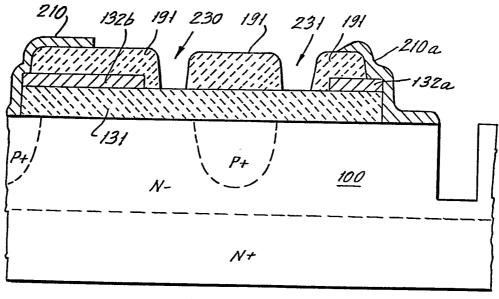

- 10. MOS-FET-Anordnung nach Anspruch 9, dadurch gekennzeichnet, dass der potential-freie Schutzring (120) von einem Oxyd (131) bedeckt ist, dass auf dem Aussenrand dieses Oxyds ein leitender Ring (132a) als Feldplatte aufgebracht und die Source-Elektrode (210) auf der innen gelegenen Oberfläche 20 des Oxyds (131) aufgebracht ist, dass das Oxyd (131) mit einem Silox-Überzug (191) versehen ist, und dass in dem Silox-Überzug (191) auf den gegenüberliegenden Seiten des Schutzrings (120) zwei Spalten (230, 231) zwischen der Feldplatte (132a) und der Source-Elektrode (210) vorgesehen sind.

- 11. MOS-FET-Anordnung nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass mit jedem der Source-Bereiche (170, 171) jeweils eine sich über die erste Chip-Oberfläche erstreckende Source-Elektrode (210) und mit der zweiten Chip-Oberfläche eine Drain-Elektrode (270) verbunden Gate-Elektrode (132) auf dem Oxyd aus polykristallinem Silizium besteht.

- 12. MOS-FET-Anordnung nach Anspruch 11, dadurch gekennzeichnet, dass über der Gate-Elektrode (132) aus polykri-35 stallinem Silizium eine Siloxschicht (191) vorgesehen ist, welche die Gate-Elektrode (132) von der Source-Elektrode (210) iso-

Die Erfindung betrifft eine Hochstrom-MOSFET-Anordnung gemäss Oberbegriff des Patentanspruchs 1.

Leitungs-MOSFETs mit niedrigem Durchlasswiderstand und hoher Durchbruchspannung sind bekannt und beispielsweise in

Bei dieser bekannten Anordnung sind die Source-Elektroden finger- bzw. kammartig ineinandergreifend angeordnete Source-Bereiche, die voneinander durch zwei von einem gemeinsamen Gate überdeckte parallele Kanalbereiche getrennt sind. Die An-50 ordnung weist einen ausserordentlich niedrigen Einschalt- oder Durchlasswiederstand auf und besitzt im übrigen die üblichen Vorteile einer MOSFET-Anordnung gegenüber einer Bipolar-Anordnung. Der niedrige Durchlasswiderstand wird infolge eines unterhalb dem Gate-Oxid und zwischen den beiden benach-55 barten Kanälen angeordneten verhältnismässig hochdotierten Leitfähigkeitsbereichs erzielt. Der hochdotierte Bereich führt zu einer gemeinsamen Drain-Elektrode. Die erhöhte Leitfähigkeit des Bereichs unterhalb des Oxids in dem zu der an der Unterseite vorgesehen Drain-Elektrode führenden Pfad beeinträchtigt 60 die Sperrspannungscharakteristik der Anordnung nicht. Infolgedessen war es möglich, den Durchlasswiderstand der MOS-FET-Anordnung wesentlich zu verringern, ohne irgendeine der übrigen erwünschten Eigenschaften zu beeinträchtigen.

Die in der erwähnten DOS 2 940 699 beschriebene Ausfüh-65 rungsform mit einem finger- bzw. kammartig ineinandergreifenden Source-Gebilde weist eine verhältnismässig niedrige Packungsdichte auf, erfordert verhältnismässig komplizierte Masken und besitzt eine verhältnismässig hohe Kapazitanz.

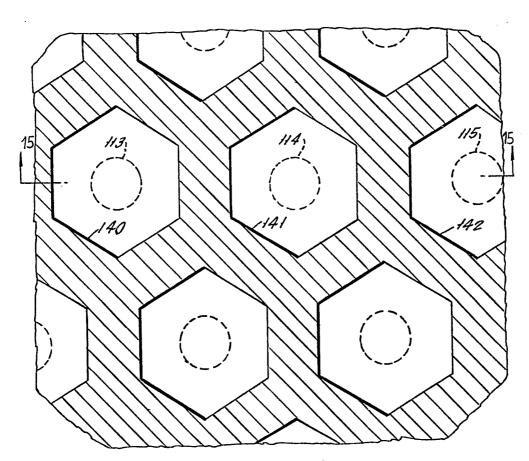

656 745

In der erwähnten DOS 2 940 699 ist jedoch auch eine Ausführung einer Leistungs-MOSFET-Anordnung mit dem erwähnten niedrigen Durchlasswiderstand beschrieben, bei der jedoch darüber hinaus eine sehr hohe Packungsdichte erzielbar ist und die mit verhältnismässig einfachen Masken hergestellt werden kann. Diese Anordnung besitzt weiter auch eine verhältnismässig niedrige Kapazitanz. Auch bei dieser Ausführungsform der erwähnten DOS 2 940 699 ist das Merkmal eines Bereichs erhöhter Leitfähigkeit unterhalb des Gate-Oxids vorgesehen und finden D-MOS-Herstellungstechniken Anwendung. Jedoch 10 derstand definiert, nicht ohne Veränderung der Polysiliciumbesitzen bei dieser Ausführungsform die einzelnen im Abstand voneinander angeordneten Source-Bereiche eine polygonale, d.h. vieleckförmige Konfiguration, und zwar vorzugsweise eine hexagonale oder sechseckige, um einen konstanten Abstand entlang den hauptsächlichen Längserstreckungen der auf der Oberfläche des Körpers verteilt angeordneten Source-Bereiche zu gewährleisten. Für eine gegebene Anordnung kann eine ausserordentlich hohe Anzahl kleiner derartiger hexagonaler Source-Elemente in der gleichen Oberfläche des Halbleiterkörpers erzeugt werden. Beispielsweise können 6600 derartige hexa- 20 gonale oder sechseckige Source-Bereiche in einer Chip-Fläche mit einer Abmessung von etwa 2,5  $\times$  3,6 mm (100  $\times$  140 Tausendstel Zoll) gebildet werden, um eine effektive Kanalbreite von etwa 55,9 mm (22 000 Tausendstel Zoll) zu erhalten und so eine sehr hohe Stromführungskapazität für die Anordnung zu ermöglichen. Als Gate-Vorrichtung ist ein Gate aus polykristallinem Silicium («Polysilicium-Gate») mit einer sechseckförmigen gitterartigen Konfiguration vorgesehen, das auf einer Oxidschicht angeordnet ist. Jeder Schenkel bzw. jede Seite dieser Gitterkonfiguration liegt jeweils über zwei in Abstand voneinander befindlichen Kanälen, welche durch Anlegen einer Spannung an das Polysilicium-Gate einer Inversion unterworfen werden können. Das Gate-Gebilde wird über die Oberseite der Anordnung her durch symmetrische längliche Gate-Kontaktfinger kontaktiert, welche einen guten Kontakt über die gesamte Oberfläche des Gates gewährleisten.

Die einzelnen vieleckigen Source-Bereiche werden jeweils durch eine zusammenhängende kontinuierliche leitende Source-Kontaktschicht kontaktiert, welche die einzelnen polygonalen Source-Bereiche durch Öffnungen in einer diese Source-Bereiche überdeckenden Isolierschicht kontaktiert. Diese Öffnungen können mittels herkömmlicher D-MOS-Lichtdruckverfahren hergestellt werden. Sodann wird ein Source-Anschlusskissenbereich für den Source-Leiter und ein Gate-Anschlusskissenbereich für die länglichen Gate-Finger sowie ein Drain-Anschlussbereich an der gegenüberliegenden Unterseite der Halbleiteranordnung vorgesehen.

Es können mehrere oder eine Vielzahl gleichartiger derartiger Chips auf einem einzigen Halbleiterplättchen erzeugt werden, wobei die einzelnen Elemente voneinander durch Reissbzw. Ritzlinien oder ein anderweitiges geeignetes Verfahren nach Abschluss der Herstellung voneinander geetrent werden.

Die Erzeugung des verhältnismässig hochleitenden Bereichs unterhalb dem Gate-Oxid erfolgte in der Weise, dass die Leitfähigkeit unterhalb dem Gate-Oxid in dem die verhältnismässig hohe Konzentration von Unreinheitsladungsträgern enthaltenden Bereich in den in seitlicher oder Querrichtung gesehen mittleren Bereichen verhältnismässig niedrig und in den in seitlicher oder Querrichtung verhältnismässig entfernten seitlichen Bereichen hoch ist. Als Folge dieser uneinheitlichen Verteilung in seitlicher oder Querrichtung ist die Avalanche- oder Lawinendurchbruchenergie der Anordnung nicht optimal. Ausserdem ist der effektive seitliche Widerstand unterhalb dem Source-Bereich und entlang der Erstreckung von den Kanalbereichen zu dem Metall auf der Oberfläche der Anordnung und in dem von der Source umschriebenen Bereich höher als optimal. Da dieser Widerstand verhältnismässig hoch ist, besitzt der aus den drei abwechselnden Leitfähigkeitsbereichen gebildete effektive Bipo-

lar-Transistor einen hohen Verstärkungsfaktor und kann leicht in den Durchlasszustand gelangen, wodurch ein Phänomen eines zweiten Durchbruchs eingeführt wird, wie es für eine Bipolar-Anordnung geläufig ist, jedoch normalerweise bei einer MOSFET-Anordnung vermieden wird. In dem Masse, als der Bereich unterhalb dem Source-Bereich zunehmend verarmt oder entleert wird, nimmt das Problem der Möglichkeit eines zweiten Durchbruchs zu. Im allgemeinen kann dieser Nebenschlussoder Parallelwiderstandsweg, welcher den parasitären Basiswi-Gate-Breite herabgesetzt werden, wodurch wiederum sich der Durchlasswiderstand der Anordnung erhöhen würde.

Der Erfindung liegt daher als Aufgabe die Schaffung einer MOSFET-Anordnung der oben erwähnten allgemeinen Art ge-15 mäss der DOS 2 940 699 zugrunde, die bei im übrigen gleichguten Eigenschaften einen verbesserten Wert der Avalancheoder Lawinendurchbruchspannung besitzt und bei der die Tendenz zum Auftreten eines zweiten Durchbruchs weitgehend vermieden wird.

Diese Aufgabe wird durch eine MOSFET-Anordnung mit den kennzeichnenden Merkmalen des Patentanspruchs 1 er-

Durch den in seitlicher Richtung konstanten Verlauf der Unreinheitskonzentration unterhalb dem Gate-Oxid kann die 25 Anordnung einen höheren Wert der Avalanche- bzw. Lawinenenergie aufweisen. Ausserdem hat das Fehlen eines Gradienten in seitlicher oder Querrichtung zur Folge, dass der aus parasitärem Basiswiderstand bestehende Parallelwiderstandspfad unterhalb dem Source-Bereich einen niedrigeren Wert als bei der be-30 kannten Anordnung erhalten kann, wodurch die Probleme hinsichtlich eines zweiten Durchbruchs infolge der Auswirkung des durch die verschiedenen pn-Übergänge gebildeten inhärenten Bipolar-Transistors weitgehend verringert werden. Während somit beispielsweise in einer N-Kanalanordnung nach dem Stand 35 der Technik mit zunehmender Entleerung oder Verarmung des P-Bereichs unterhalb dem N-Source-Bereich der parasitäre Basiswiderstand zunehmen würde, tritt bei der erfindungsgemässen Konfiguration mit in seitlicher Richtung konstanter Verteilung der Unreinheiten unterhalb dem Gate-Oxid nur eine gerin-40 ge Verarmung bzw. Entleerung auf und der parasitäre Basiswiderstand im Betriebszustand der Anordnung bleibt verhältnismässig niedrig. Da ferner diese betragsmässige Verringerung des effektiven Nebenschlusswiderstands unterhalb dem Source-Bereich ohne Änderung der Polysilicium-Gate Breite erreicht 45 wird, kann die Anordnung eine sehr kurze bzw. kleine Breite des Polysilicium-Gates behalten, beispielsweise von 13 bis 15

Der seitliche oder Quergradient Null der Verteilung einer Unreinheitsdotierung hoher Dichte unterhalb dem Gate-Oxid 50 lässt sich auf vielfache Weise erzeugen, beispielsweise kann dieser Bereich hoher Dotierungsdichte vor der Erzeugung der polygonalen oder vieleckförmigen Source-Zellen und vor der Erzeugung des Gate-Oxids implantiert werden.

Falls erwünscht, können zwei Implantationen vorgenommen 55 werden, eine vor der Bildung des Gate-Oxids und eine weitere nach der Herstellung des Gate-Musters aus polykristallinem Silicium, falls dies zur Herabsetzung der Miller-Kapazitanz gewünscht ist.

Bei einer bevorzugten Ausführungsform ist eine verhältnis-60 mässig hochleitfähige Implantation unterhalb des Gate-Oxids in einer Tiefe von etwa 1 Mikron unterhalb der Oxid-Oberfläche vorgesehen, wobei jedoch diese Implantation eine derartige Leitfähigkeitsverteilung bzw. einen Leitfähigkeitsgradienten aufweist, dass die Leitfähigkeit in Richtung zur Oberfläche des 65 Plättchens am höchsten ist und bei Annäherung an eine Tiefe von etwa 1 Mikron zunehmend abnimmt und dass die Ladungsträgerverteilung in seitlicher Richtung über die Breite des die hohe Dotierungskonzentration aufnehmenden Bereichs unterhalb des Gate-Oxids auf jedem Niveau unterhalb der Oberfläche einen konstanten Wert besitzt.

Im folgenden werden Ausführungsbeispiele der Erfindung anhand der Zeichnungen beschrieben; dabei zeigt:

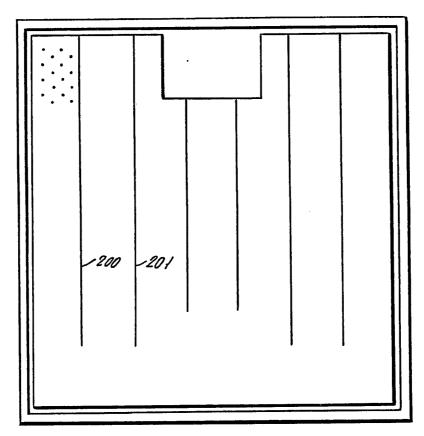

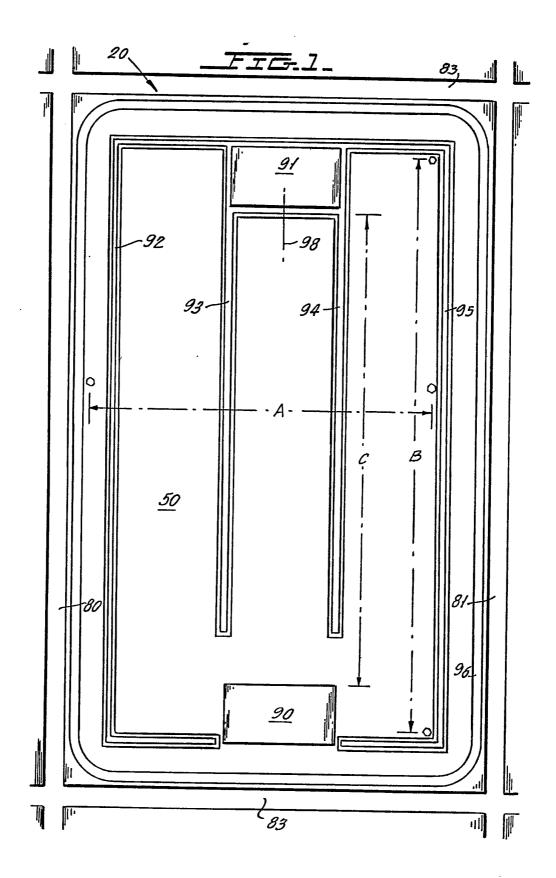

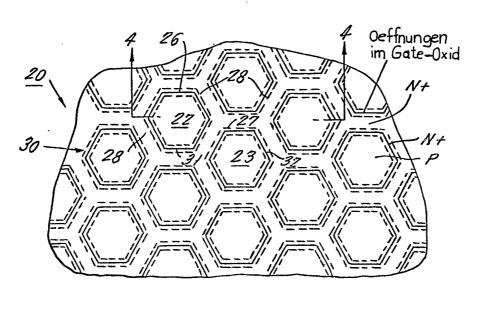

Fig. 1 in Draufsicht ein fertiges Element auf einem Halbleiterplättchen vor der Abtrennung des Elements von dem übrigen Teil des Plättchens, gemäss der DOS 2 940 699 nach dem Stand der Technik,

Fig. 2 in vergrösserter Detailansicht das Gate-Kissen aus Fig. 1 zur Veranschaulichung des Verhältnisses zwischen dem Gate-Kontakt und den Source-Polygonen im Bereich des Gate-Kissens,

Fig. 3 in Detaildraufsicht einen kleinen Teil aus dem Source-Bereich gemäss Fig. 1 während einer Stufe des Herstellungsverfahrens für die Anordnung,

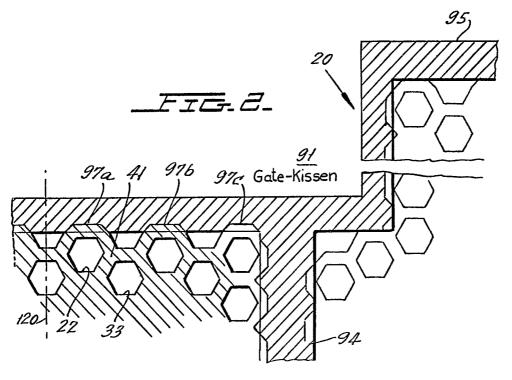

Fig. 4 eine Querschnittsansicht zu Fig. 3 im Schnitt längs der Linie 4-4 in Fig. 3,

Fig. 5 in ähnlicher Schnittansicht wie in Fig. 4 die Zufügung eines Polysilicium-Gates, einer Source-Elektrodenvorrichtung und einer Drain-Elektrode zu dem Plättchen.

Fig. 6 eine schematische Darstellung des Verlaufs der Konzentration der Dotierungsunreinheiten in seitlicher Richtung unterhalb dem Gate-Oxid, für die bekannte Anordnung gemäss Fig. 5.

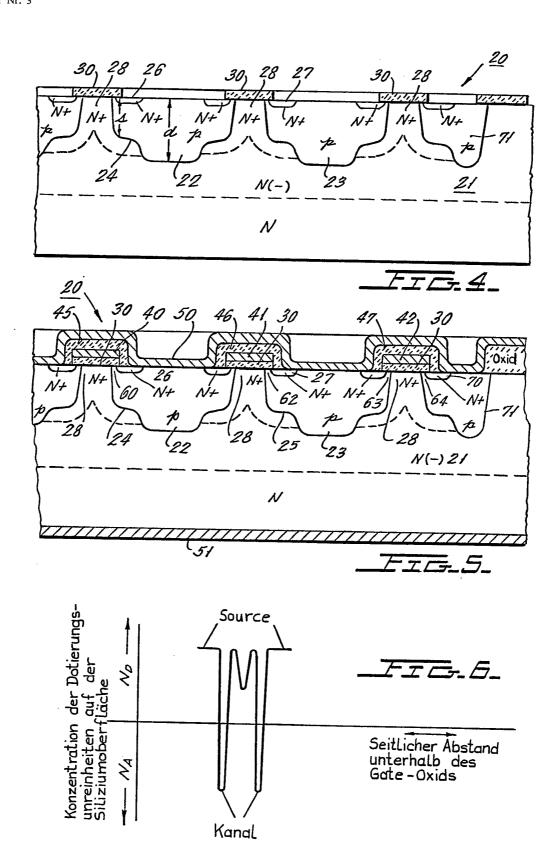

Fig. 7 das erste Masken-Lay-out für die Herstellungsbehandlung eines erfindungsgemässen Chips,

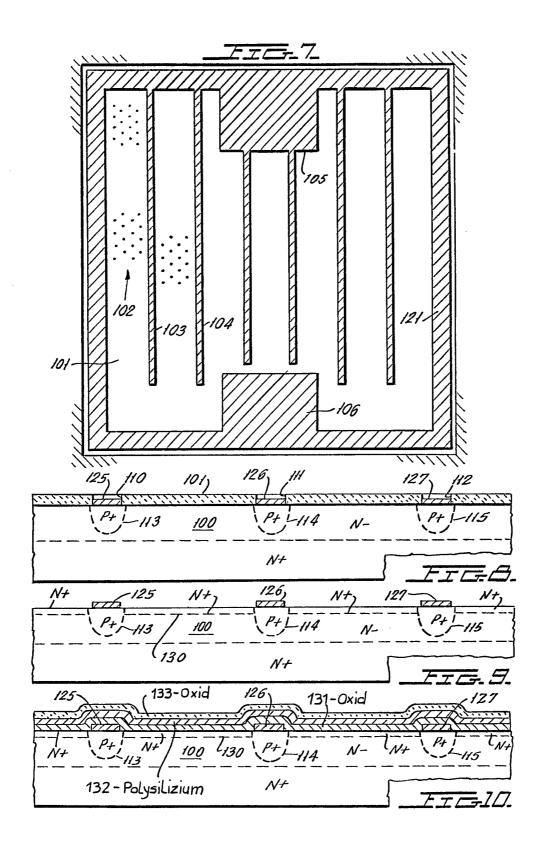

Fig. 8 den mittleren Bereich des Chips nach der Diffusion durch Fenster mit kleinem Durchmesser, welche unter Verwendung der Maske aus Fig. 7 in das Feld-Oxid geätzt wurden,

Fig. 9 den Chipabschnitt aus Fig. 8 nach der Aufbringung einer zweiten Maske zur Entfernung des übrigen Feld-Oxids unter Belassung kleiner Oxid-Kissen über den P(+)-Diffusionsbereichen, wobei eine N(+)-Implantation über der vollen freiliegenden Oberfläche des Plättchens gezeigt ist,

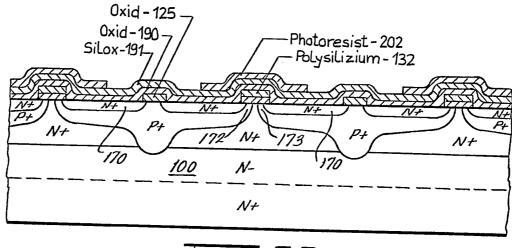

Fig. 10 den Chipabschnitt aus Fig. 9 nach der Aufbringung einer Oxidschicht, einer Polysiliciumschicht und einer zweiten Oxidschicht,

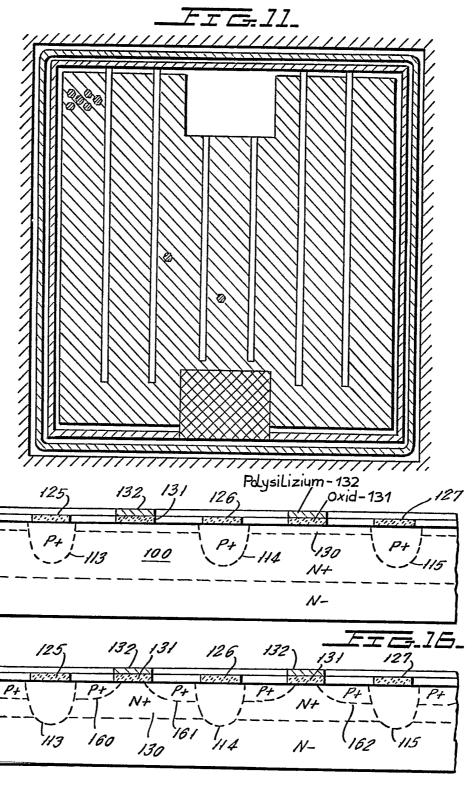

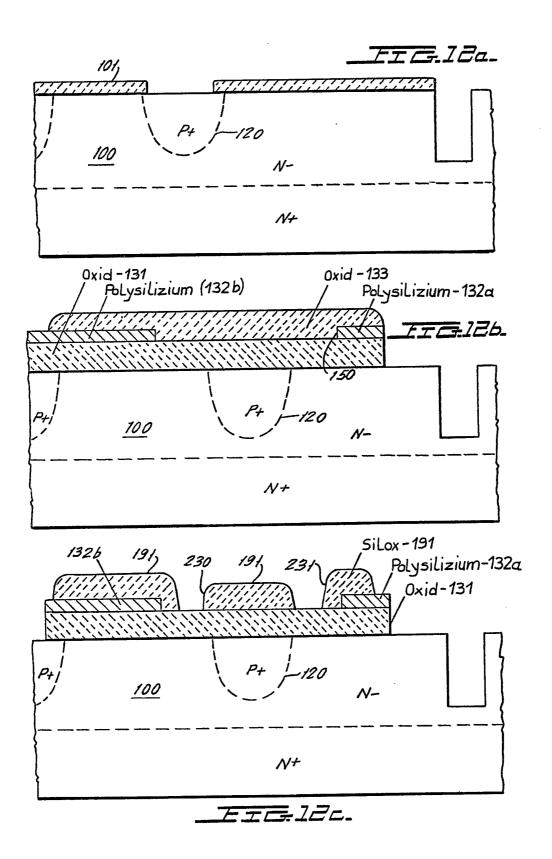

Fig. 11 die Konfiguration einer verwendeten dritten Maske, Fig. 12a bis 12e jeweils die Konfiguration der Umfangsbegrenzung des Chips in verschiedenen Stadien der Herstellungsbearbeitung des erfindungsgemässen Chips,

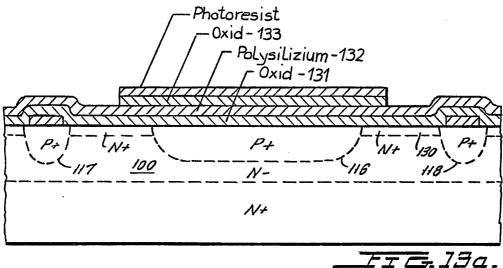

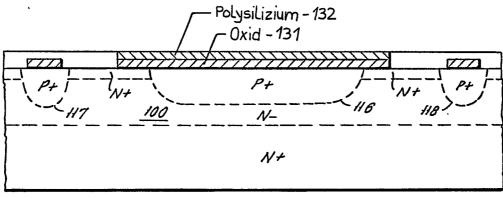

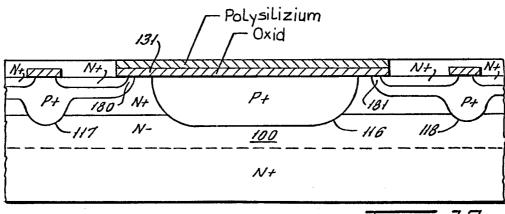

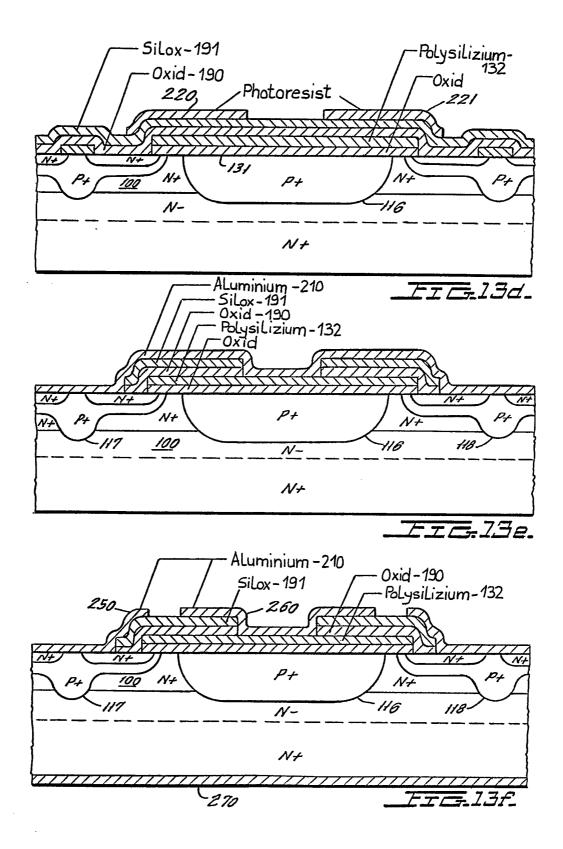

Fig. 13a bis 13f jeweils verschiedene Stufen bei der Herstellung eines typischen länglichen Gate-Fingers im Verlauf der Herstellungsbehandlung des Chips gemäss der Erfindung,

Fig. 14 in Draufsicht den Plättchenabschnitt aus Fig. 10 nach der Behandlung mit der Maske gemäss Fig. 11 zur Entfernung polygonal-förmiger Abschnitte aus dem oberen Oxid-Überzug in dem Abschnitt gemäss Fig. 10,

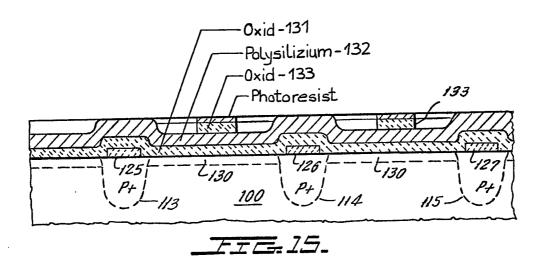

der Linie 15-15 in Fig. 14,

Fig. 16 eine Querschnittsansicht ähnlich wie in Fig. 15, nach dem Ätzen der Polysiliciumschicht und der darunterliegenden Oxidschicht zur Freilegung zentraler sechseckförmiger Öffnungen, welche sich bis zur Oberfläche des Chips erstrecken,

Fig. 17 den Abschnitt aus Fig. 16 nach der Diffusions- und Drive-Behandlung von P(+)-Ringen jeweils in die einzelnen sechseckförmigen Öffnungen,

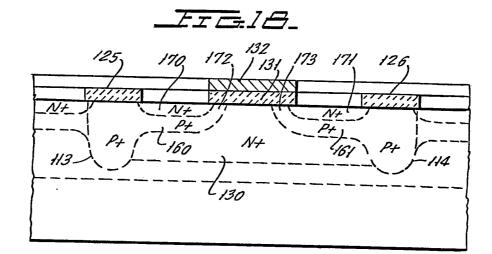

Fig. 18 den Abschnitt aus Fig. 17 nach der Implantation von Source-Ringen in P(+)-Ringe oder -Zellen aus Fig. 17, unter Anwendung selbst-ausrichtender Diffusionsverfahren zur Erzeugung mehrerer sechseckförmiger Kanäle, welche durch eine Gate-Spannung invertierbar sind,

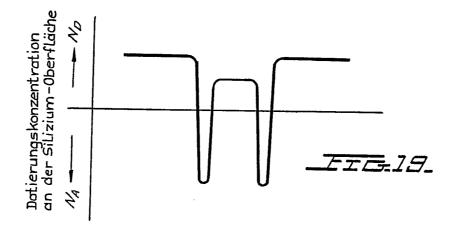

Fig. 19 den erfindungsgemäss erhaltenen Verlauf der Dotierungskonzentration unterhalb dem Gate-Oxid,

Fig. 20 das Plättchen aus Fig. 18 nach der Erzeugung einer Oxidschicht, einer Siloxschicht und eines unter Verwendung der Maske aus Fig. 21 erzeugten Photoabdeckermusters,

Fig. 21 ein die vierte Maske für das Herstellungsverfahren bildendes Masken-Lay-out,

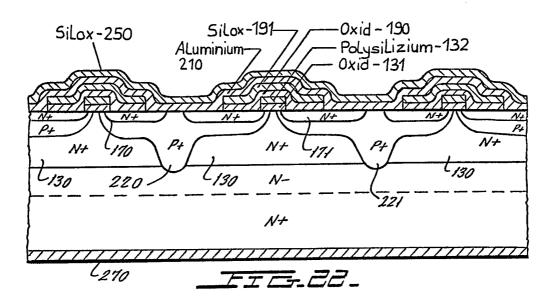

Fig. 22 den Chipabschnitt aus Fig. 20 nach dem Wegätzen der jeweils die sechseckförmigen Zellen bedeckenden zentralen 5 Oxid- und Siloxbereiche und nach der Aufbringung einer Aluminiumfolie über die gesamte Oberfläche der Anordnung zur Bildung der Source-Elektrode.

Zunächst wird die Anordnung nach dem Stand der Technik gemäss der DOS 2 940 699 beschrieben. Das dort beschriebene 10 Verfahren kann zur Herstellung einer Anordnung gemäss den vorliegenden Fig. 1 bis 5 modifiziert werden, derart, dass D-MOS-Herstellungsverfahren sowie Ionenimplantationsverfahren zur möglichst vorteilhaften Herstellung des pn-Übergangs und der möglichst vorteilhaften Plazierung der Elektroden ange-15 wandt werden können. Die Anordnung wird als N-Kanalanordnung vom Enhancement-(Verstärkungs-, Anreicherungs-)-Typ beschrieben; selbstverständlich können jedoch die Merkmale der nachfolgend beschriebenen Vorrichtung auch bei P-Kanalanordnungen und Anordnungen vom Entleerungs- oder Verar-20 mungs-Typ («depletion mode») Anwendung finden.

Die Polygon- oder Vieleck-Konfiguration der Source-Bereiche ist am besten aus den Fig. 3, 4 und 5 ersichtlich, die zunächst erläutert werden. In den Fig. 3 und 4 ist die Anordnung vor der Anbringung der Gate-, Source- und Drain-Elektroden 25 dargestellt. Die Fig. 3 und 4 zeigen eine Vielzahl von polygonaloder vieleckförmigen Source-Bereichen auf der einen Oberfläche der Anordnung; vorzugsweise sind die Vieleckbereiche sechseckförmig. Es können jedoch auch anderweitige Formen wie beispielsweise quadratische oder rechteckförmige Konfigu-30 rationen verwendet werden, jedoch ergibt die sechseckförmige Konfiguration eine bessere Gleichförmigkeit der Abstände zwischen benachbarten Source-Bereich-Begrenzungen.

Wie aus den Fig. 3 und 4 ersichtlich, sind die sechseckförmigen Source-Bereiche in einem Halbleiterkörper oder -plättchen 35 erzeugt, und zwar im gezeigten Ausführungsbeispiel in einem N-Plättchen 20 aus monokristallinem Silicium, auf dem ein dünner N-Epitaxialbereich 21 abgeschieden ist, wie am besten aus Fig. 4 ersichtlich. Sämtliche pn-Übergänge werden in der Epitaxialschicht 21 erzeugt. Mittels geeigneter Masken wird eine 40 Vielzahl von P-Bereichen nach Art der Bereiche 22 und 23 in den Fig. 3 und 4 in der einen Oberfläche des Halbleiterplättchens 21 erzeugt; diese Bereiche sind von insgesamt vieleckförmiger, vorzugsweise sechseckförmiger Konfiguration.

Es wird eine sehr grosse Zahl derartiger vieleckförmiger Be-45 reiche erzeugt. Beispielsweise werden in einer Anordnung mit einer Oberflächenabmessung von 2,5 × 3,6 mm ungefähr 6600 vieleckförmige Bereiche erzeugt, zur Erzielung einer Gesamt-Kanalbreite von etwa 55,9 mm. Jeder dieser vieleckförmigen Bereiche kann jeweils eine Weite oder Breite von etwa 25,4·10-3 Fig. 15 eine Querschnittsansicht zu Fig. 14 im Schnitt längs 50 mm oder weniger besitzen, gemessen in Richtung rechtwinklig zu zwei gegenüberliegenden Seiten des Sechsecks. Die Bereiche besitzen voneinander einen Abstand von etwa 15,2·10<sup>-3</sup> mm, gemessen in Richtung senkrecht zwischen benachbarten geraden Seiten benachbarter Polygonbereiche.

Die P(+)-Bereiche 22 und 23 haben eine Tiefe d von vorzugsweise etwa 5 Mikron, zur Erzielung einer hohen und zuverlässigen Feldcharakteristik. Ferner weist jeder derartige P-Bereich jeweils einen äusseren flachen oder Schelf-Bereich nach Art der Schelf-Bereiche 24 und 25 für die P-Bereiche 22 bzw.23 60 auf, mit einer Tiefe s von etwa 3,0 Mikron. Dieser Abstand soll so klein wie möglich sein, um den kapazitiven Widerstand der Anordnung zu verringern.

Die einzelnen Polygon- bzw. Vieleck-Bereiche einschliesslich der Polygon-Bereiche 22 und 23 nehmen polygonal- bzw. viel-65 eckförmige N(+)-Ringbereiche 26 bzw. 27 auf. Die Schelf-Bereiche 24 und 25 sind unterhalb der Bereiche 26 bzw. 27 angeordnet. Die N(+)-Bereiche 26 und 27 wirken mit einem relativ leitfähigen N(+)-Bereich 28 zusammen, bei dem es sich um den

656 745 5

zwischen benachbarten P-Polygonen befindlichen N(+)-Bereich handelt, welcher die verschiedenen Kanäle zwischen den Source-Bereichen und einem weiteren unten noch beschriebenen Drain-Kontakt bildet. Die hochleitfähigen N(+)-Bereiche 28 sind in der in der erwähnten DOS 2 940 699 beschriebenen Weise gebildet, zur Erzielung eines sehr niedrigen Durchlass-Widerstands für die Anordnung.

Aus den Fig. 3 und 4 ist ersichtlich, dass die gesamte Oberfläche des Plättchens mit einer Oxid-Schicht oder kombinierten herkömmlichen Oxid-Nitrid-Schichten bedeckt ist, die auf bekannte Weise zur Abdeckung bei der Bildung der verschiedenen pn-Übergänge erzeugt wird bzw. werden. Diese Schicht ist als Isolierschicht 30 dargestellt. Die Isolierschicht 30 ist mit polygon- bzw. vieleckförmigen Öffnungen nach Art der Öffnungen 31 und 32 unmittelbar oberhalb der Polygonal- bzw. Vieleck-Bereiche 22 bzw. 23 versehen. Die Öffnungen 31 und 32 überlappen mit ihren Begrenzungen oder Rändern die N(+)-Source-Ringe 26 und 27 für die Bereiche 22 bzw. 23. Die nach der Erzeugung der polygonförmigen Öffnungen verbliebenen Oxidstreifen 30 definieren bzw. bilden das Gate-Oxid der Anord-

Sodann kann gemäss Fig. 5 die Anordnung mit Elektroden versehen werden. Zu diesen Elektroden gehört unter anderem ein Gitter aus polykristallinem Silicium, mit über den Oxid-Abschnitten 30 liegenden Polysilicium-Abschnitten 40, 41 und 42.

Sodann wird auf das Gitter 40 aus polykristallinem Silicium ein SiO2-Überzug aufgebracht, der in Fig. 5 durch die Überzugsabschnitte 45, 46 und 47 veranschaulicht ist und die polykristallinen Silicium-Steuerelektroden von der später über der isoliert. In Fig. 5 ist die Source-Elektrode als leitender Überzug 50 aus einem beliebigen geeigneten Material, beispielsweise aus Aluminium, dargestellt. Des weiteren wird auch eine Drain-Elektrode 51 auf die Anordnung aufgebracht.

Das so erhaltene Gebilde gemäss Fig. 5 stellt eine N-Kanalanordnung dar, bei welcher jeweils die Kanalbereiche zwischen jedem der einzelnen Source-Bereiche und dem Halbleiterhauptkörper gebildet werden, der letztlich zu der Drain-Elektrode 51 führt. Somit wird ein Kanalbereich 60 zwischen dem mit der Source-Elektrode 50 verbundenen Source-Ring 26 und dem letztlich zur Drain-Elektrode 51 führenden N(+)-Bereich 28 gebildet. Der Kanal 60 wird bei Anlegen einer geeigneten Steuerspannung an das Gate 40 zu N-Leitfähigkeit invertiert. In entsprechender Weise sind jeweils Kanäle 61 und 62 zwischen dem mit dem Leiter 50 verbundenen Source-Bereich 26 bzw. dem Source-Bereich 27 und dem umgebenden N(+)-Bereich 28, der zur Drain-Elektrode 51 führt, gebildet. Somit werden bei Anlegen einer geeigneten Steuerspannung an das Polysilicium-Gate (einschliesslich des Fingers 41 in Fig. 5) die Kanäle 61 bzw. 62 leitend im Sinne einer Majoritätsladungsträgerleitung von der Source-Elektrode 50 zur Drain-Elektrode 51.

Die einzelnen Source-Bereiche bilden dabei parallele Leitungspfade, derart, dass beispielsweise die Kanäle 63 und 64 unterhalb dem Gate-Element 42 eine Leitung vom Source-Ring 27 und einem N-Source-Streifen 70 zu dem N(+)-Bereich 28 und von diesem zur Drain-Elektrode 51 bilden.

In den Fig. 4 und 5 ist ferner ein den Rand des Plättchens einschliessender oder einhüllender P-Bereich 71 dargestellt.

Der Kontakt 50 aus Fig. 5 ist vorzugsweise ein Aluminiumkontakt. Wie ersichtlich, liegt der Kontaktbereich für den Kontakt 50 zur Gänze über und in Ausrichtung mit dem tieferen Teil des P-Bereichs 22. Dies geschieht deshalb, um zu verhindern, dass das für die Elektrode 50 verwendete Aluminium sehr dünne Bereiche des P-Materials spike-artig durchdringt. Auf diese Weise können die durch die ringförmigen Schelf-Bereiche 24 und 25 gebildeten eigentlichen aktiven Kanalbereiche so dünn wie gewünscht ausgebildet sein, um die Kapazitanz der Anordnung zu verringern.

Fig. 1 zeigt eine vollständige fertige Anordnung unter Verwendung des Polygonal- oder vieleckförmigen -Source-Musters gemäss Fig. 5. Die in Fig. 1 dargestellte fertige vollständige Anordnung liegt innerhalb Ritz- bzw. Brechbereichen 80, 81, 82 und 83, mittels welcher mehrere einstückige Bereiche mit Abmessungen von jeweils 2,5  $\times$  3,6 mm von dem Hauptkörper des Halbleiterplättchens abgebrochen werden können.

Die beschriebenen Polygonal-Bereiche sind in mehreren Spalten und Reihen angeordnet. Beispielsweise entfallen auf die 10 Abmessung A 65 Spalten von Polygonal-Bereichen, bei einer Breite von etwa 2,1 mm. Die Abmessung B kann 100 Reihen oder Zeilen von Polygonal-Bereichen umfassen und etwa 3,8 mm betragen. Die Abmessung C zwischen einem Source-Anschlusskissen 90 und einem Gate-Anschlusskissen 91 kann 82 15 Zeilen bzw. Reihen von Polygonal-Elementen enthalten.

Das Source-Anschlusskissen 90 ist ein verhältnismässig schwerer Metallabschnitt, der direkt mit der Aluminium-Source-Elektrode 50 verbunden ist und eine bequeme Leiteranschlussverbindung für die Source-Elektrode darstellt.

Das Gate-Anschlusskissen 91 ist elektrisch mit einer Vielzahl von sich symmetrisch über die äussere Oberfläche des die Polygonal-Bereiche enthaltenden Flächenbereichs erstreckenden Fingern 92, 93, 94 bzw. 95 verbunden, welche die elektrische Verbindung mit dem polykristallinen Silicium-Gate bilden, wie un-25 ter Bezugnahme auf Fig. 2 beschrieben wird.

Schliesslich enthält der Aussenumfang der Anordnung einen tiefen P(+)-Diffusionsring, der mit einer in Fig. 1 gezeigten Feldplatte 96 verbunden sein kann,

Fig. 2 zeigt einen Teil des Gate-Kissens 91 sowie die Gategesamten Plättchenoberfläche abgeschiedenen Source-Elektrode 30 Finger 94 und 95. Zur Verringerung der R-C-Zeitverzögerungskonstanten der Anordnung ist es erwünscht, eine Vielzahl von Kontakten zu dem Polysilicium-Gate herzustellen. Das Polysilicium-Gate weist mehrere Bereiche nach Art der Bereiche 97a, 97b, 97c (Fig. 2) usw. auf, welche sich auswärts erstrek-35 ken und Fortsätze des Gate-Kissens und der Gate-Kissenelemente 94 und 95 aufnehmen. Die Polysilicium-Gate-Bereiche können bei der Herstellung des Oxid-Überzugs 45-46-47 in Fig. 5 freiliegend verbleiben und werden nicht mit der Source-Elektrode 50 überzogen. Es ist zu beachten, dass es sich bei der 40 Achse 98 in Fig. 2 um die in Fig. 1 gezeigte Symmetrieachse 98

> Die in den Fig. 1 bis 5 dargestellte und beschriebene MOS-FET-Anordnung hat sich im Betrieb bewährt. Jedoch besitzt die Anordnung nur eine begrenzte Avalanche-Energie und es 45 sind kleinere Probleme hinsichtlich des zweiten Durchbruchs aufgetreten. Es darf vermutet werden, dass diese Probleme auf die in einer seitlichen Richtung veränderliche Dichte des Bereichs erhöhter Dotierungskonzentration unterhalb dem Gate-Oxid und zwischen den beiden Kanälen zurückzuführen ist. So 50 wird bei der in Fig. 5 gezeigten Anordnung die Konzentration der Dotierungsunreinheiten in einer seitlichen Richtung unterhalb der Oxid-Oberfläche 30 in der in Fig. 6 veranschaulichten Weise variieren; Fig. 6 zeigt eine Darstellung der Donor- und Akzeptor-Konzentration der Silicium-Oberfläche als Funktion 55 des seitlichen Abstands entlang dem Gate-Oxid in Fig. 5.

Die Konzentration der Source-Bereiche 26 und 27 ist in Fig. 6 links bzw. rechts dargestellt; man erkennt, dass in der Mitte des Bereichs 28 unterhalb dem Oxid die Konzentration der N(+)-Dotierungsunreinheitsatome erniedrigt ist.

Als Folge dieser in seitlicher Richtung variablen bzw. schwankenden Dotierungskonzentration wird sich im Betriebszustand eine grössere Entleerung bzw. Verarmung unterhalb den P(+)-Bereichen 22 und 23 ergeben. Infolge dieser Verarmung bzw. Entleerung ist der effektive Widerstand rb' des aus den Bereichen 26, 22 und 21 gebildeten Bipolar-Transistors verhältnismässig hoch, derart, dass der Transistor einen hohen Verstärkungsfaktor besitzt und leicht in den Leitungs- oder Durchlasszustand gelangen kann. Diese Umschaltung in den

Durchlasszustand bewirkt die Ausbildung einer heissen Stelle auf der Anordnung und kann zur Zerstörung der Anordnung führen. Dieses Problem eines zweiten Durchbruchs tritt bei Bipolar-Anordnungen auf, wird jedoch an sich mit dem MOSFET vermieden. Zu beachten ist, dass mit zunehmender Entleerung bzw. Verarmung der P(+)-Bereiche 22 und 23 der einzelnen Zellen der Anordnung die Probleme eines zweiten Durchbruchs zunehmen.

Ein anderes durch die nicht-lineare Ladungsträgerverteilung entlang dem verhältnismässig hochleitenden Bereich unterhalb der Gates 30 verursachtes Problem besteht darin, dass die Avalanche- bzw. Lawinendurchbruchenergie der Anordnung etwas herabgesetzt wird, derart, dass die Anordnung etwas weniger beständig gegenüber Zerstörung durch hohe Spannungsspitzen ist, als dies möglich wäre.

Wie im folgenden noch näher erläutert wird, zeichnet sich die erfindungsgemässe Anordnung durch eine konstante Ladungsträgerdichte in einer seitlichen Richtung unterhalb des Gates 30 und zwischen den zu den Gates 30 führenden Source-Bereichen aus. Diese Ladungsträgerdichte ist unmittelbar unter- 20 halb dem Gate verhältnismässig hoch und nimmt mit zunehmendem Abstand unterhalb der Anordnungsoberfläche allmählich ab. Als Folge dieser neuartigen Verteilung der Ladungsträger unterhalb dem Gate-Oxid kommt es im Betriebszustand der Anordnung nur zu einer sehr geringen Entleerung bzw. Verarmung der P(+)-Bereiche 22 und 23, derart, dass der Nebenschlusswiderstand rb' unterhalb der Source-Bereiche einen geringen Wert behält und der in der Anordnung inhärent gebildete Bipolar-Transistor eine niedrige Verstärkung besitzt, derart, dass Probleme des zweiten Durchbruchs vermieden werden. Ausserdem ergibt der erfindungsgemässe Verlauf der Ladungsträgerdichte in dem Bereich unterhalb des Gates, derart, dass unmittelbar unterhalb des Gates eine höhere Konzentration vorliegt mit einer allmählich abnehmenden Konzentration in weiterer Entfernung von dem Gate, einen höheren Wert der Avalan- 35 und 104 führen zu einem Gate-Kissenbereich 105. Der Bereich che- oder Lawinenenergie für die Anordnung, derart, dass sie widerstandsfähiger gegen Beschädigung durch Überspannungsspitzen wird.

Wie im weiteren noch dargelegt wird, reicht eine verhältnismässig geringfügige Modifizierung im Herstellungsverfahren der Anordnung aus, um diese wichtigen Vorteile zu erzielen. Diese Modifikation bzw. dieser Unterschied besteht in der Anwendung einer N-Implantation und eines entsprechenden Drives vor der Erzeugung des Gate-Oxids, in einer Ausführungsform als N-Kanalanordnung. In diesem Zusammenhang ist zu beach- 45 ten, dass bei der Ausführungsform gemäss den Fig. 1 bis 5 unter Anwendung des in der erwähnten älteren Anmeldung DOS 2 940 699 beschriebenen Verfahrens die N(+)-Bereiche 28 nach der Abscheidung des Gate-Oxids auf der Anordnung gebildet werden. Dieses Verfahren hat die erwähnte nicht-lineare Ladungsträgerkonzentration längs der Oberfläche der Anordnung gemäss der Darstellung in den Fig. 5 und 6 zur Folge.

Nachfolgend wird die Erfindung anhand der Herstellung einer einzelnen Anordnung auf einem einzelnen Chip-Bereich, wie beispielsweise dem in Fig. 1 gezeigten Chip mit einer gering- 55 lung, um die Bor-Dotierungsatome tiefer in die Oberfläche des fügig unterschiedlichen Oberflächengeometrie, beschrieben. Und zwar erfolgt die Beschreibung für eine N-Kanalanordnung vom Entleerungs- oder Verarmungs-Typ. Für den Fachmann ist dabei selbstverständlich, dass sich die Erfindung auch zur Anwendung für P-Kanalanordnungen und sowohl für Anordnungen vom Entleerungs- oder Verarmungs-Typ wie auch vom Verstärkungs- oder Anreicherungs-Typ eignet.

Bei der Herstellung der erfindungsgemässen Anordnung besteht der erste Verfahrensschritt in der Abscheidung eines Feld-Oxids auf der Oberfläche eines eine Mehrzahl identischer Chips 65 enthaltenden einzelnen Plättchens. Selbstverständlich kann eine grosse Anzahl gleichartiger derartiger Plättchen gleichzeitig behandelt werden. Die einzelnen Plättchen können von der in

Fig. 8 in Teildarstellung gezeigten Art sein und jeweils aus einem N(+)-Körper mit einen durch Epitaxialabscheidung erzeugten (N-)-Bereich 100 bestehen. In einem typischen Fall kann das Plättchen gemäss Fig. 8 ein N(+)-Substrat von etwa  $0,36~\mathrm{mm}$  Dicke mit einer N(-)-Epitaxialschicht aufweisen, deren Dicke und spezifischer Widerstand von der gewünschten Sperrspannung abhängen. In einem typischen Fall kann die Epitaxialschicht 100 für das beschriebene Ausführungsbeispiel eine Dicke von etwa 35 Mikron und einen spezifischen Wider-10 stand von etwa 20 Ohm/cm besitzen.

Auf der Oberfläche der N(-)-Schicht 100 wird nach bekannten Standardverfahren ein Feld-Oxid 101 aufgebracht. Sodann wird auf die Oberseite des Oxids 101 ein geeigneter Photoabdecker aufgebracht und die Oberfläche durch eine Maske hin-15 durch mit UV-Licht belichtet, die beispielsweise das in Fig. 7 für jedes einzelne Chipelement gezeigte Muster aufweisen kann. Selbstverständlicch wird eine herkömmliche Glasmaske jeweils eine grosse Anzahl gleichartiger Muster nach Art des Musters von Fig. 7 enthalten.

Das so erzeugte Photoabdecker-Muster weist eine grosse Zahl von Kreisöffnungen kleineren Durchmessers auf, welche durch die Tupfenbereiche 102 erzeugt werden, die über den gesamten nicht-schraffierten Bereich der Maske in Fig. 7 verteilt sind. Diese Punkt-Tupfen bzw. -Flecken sind in gegeneinandner 25 versetzten Spalten angeordnet, derart, dass die Punkte in benachbarten Spalten ausgerichtet sind. Innerhalb jeder der einzelnen vertikalen Flächen zwischen den Gate-Fingerbereichen, beispielsweise also zwischen den Gate-Fingern 103 und 104, können beispielsweise etwa 24 Spalten derartiger Tupfen-Punk-30 te liegen. Jede Spaltenreihe kann beispielsweise 150 Punkte bzw. Tupfen enthalten. Es sei darauf hingewiesen, dass jeweils jeder derartige Punkt-Tupfen den Mittelpunkt einer in dem betreffenden einzelnen Chip-Element zu erzeugenden jeweiligen hexagonalen Zelle entspricht. Die länglichen Fingerbereiche 103 106 entspricht in seiner Lage einem Source-Kissen-Anschlussbereich, wie weiter unten noch beschrieben wird.

Das Oxid wird in den durch das mit der Maske gemäss Fig. 7 gebildete Photoabdecker-Muster freiliegenden Bereichen mit 40 einer geeigneten Ätzlösung geätzt, zur Erzeugung von Öffnungen 110, 111 und 112 in Fig. 8. Diese Öffnungen entsprechen den Stellen von drei der Maskenpunkte 102 in Fig. 7 und sind in Fig. 8 stark vergrössert und nicht massstabsgetreu dargestellt.

Nach dem Ätzvorgang wird die Photoabdecker-Maske abgelöst und das Plättchen in eine Ionenimplantationsvorrichtung eingebracht, in welcher Boratome in nicht durch die Oxid-Schicht 101 bedeckte Bereiche implantiert werden. Auf diese Weise werden P-Leitfähigkeits-Boratome durch die Öffnungen 50 110, 111 und 112 implantiert. Typischerweise können die Boratome in einer Dosierung von 5  $\times$  10<sup>13</sup> bis 1  $\times$  15<sup>15</sup> Atomen/cm² und mit Beschleunigungsspannungen von mehr als etwa 5 kV implantiert werden.

Auf diese Borimplantation folgt eine Drive-Wärmebehand-Plättchens zur Bildung der P(+)-Bereiche 113, 114 und 115 durch die Öffnungen 110, 111 bzw. 112 hineinzutreiben. Gleichzeitig wird ein verhältnismässig breiter länglicher P(+)-Bereich 116 beispielsweise unterhalb dem Fingerbereich 104 in 60 der Maske von Fig. 7 erzeugt, wie in Fig. 13a veranschaulicht. Dabei ist zu beachten, dass in Fig. 13a der Finger 116 unmittelbar zwischen P(+)-Bereichen 117 und 118 liegt, bei welchen es sich um Punkt-Tupfen in Reihen zu beiden Seiten des Fingers 104 handelt. In ähnlicher Weise wird ein länglicher P(+)-Kanal-Schutzring 120 um den Umfang des Chips herum erzeugt, entsprechend dem Maskenbereich 121 in der Maske aus Fig. 7 und wie in Fig. 12a veranschaulicht.

Im Verlauf der Borimplantation und der Eintreib-Wärmebe-

7 656 745

handlung wächst eine kleine Oxid-Schicht über der durch die Fenster 110, 111 und 112 freiliegenden Oxid-Oberfläche auf; diese kleine Oxid-Schicht ist in Form der Oxid-Schichten 125 bis 127 in Fig. 8 veranschaulicht. Diese Oxid-Schichten werden in ihrer Lage belassen, um in einem nachfolgenden Verfahrensschritt, der weiter unten im Zusammenhang mit der Implantation des Source-Bereichs beschrieben wird, als ein Diffusionsfenster zu dienen.

Als nächstes wird eine zweite Lichtdruckmaske aufgebracht, um das gesamte Oxid von der Oberfläche des Bereichs 100 zu entfernen mit Ausnahme derjenigen Oxid-Musterstellen, welche die unter Verwendung des Maske aus Fig. 7 diffundierten P(+)-Bereiche bedecken. Die für diesen Verfahrensschritt verwendete Maske entspricht in ihrem allgemeinen Lay-out der Maske aus Fig. 7, jedoch in Umkehrung.

Nach Erzeugung des Lichtdruckmaskenmusters über der gesamten Fläche mit Ausnahme der diffundierten P(+)-Bereiche wird eine Oxid-Ätzung vorgenommen, welche das in Fig. 9 für die Punkt-Tupfen-Bereiche gezeigte Muster ergibt. Dabei ist zu beachten, dass die einzelnen Oxid-Bereiche 125, 126 und 127 nach der Oxid-Ätzung und nach der Entfernung des Photoabdeckers von der Oberseite der Oxid-Elemente 125, 126 und 127 jeweils einen Durchmesser von mehr als etwa 6 Mikron besitzen sollen.

implantation vorbereitet, in welcher ein Phosphoratomstrahl auf die Chip-Oberfläche mit einer Spannung von etwa 120 kV und einer Implantationsdosis im Bereich von  $1 \times 10^{11}$  bis  $1 \times 10^{14}$ Phosphoratomen/cm<sup>2</sup> gerichtet wird. Diese Implantation erzeugt den in Fig. 9 als N(+)-Bereich 130 veranschaulichten dünnen Oberflächenüberzug, und zwar in allen Bereichen, die nicht durch die Oxid-Punkt-Tupfen oder anderweitige in den Verfahrensschritten gemäss Fig. 8 und gemäss der Maske aus Fig. 7 erzeugte Oxid-Muster oberhalb der P(+)-Bereiche übergezeigten Bereichen an den Gate-Kontaktfingerbereichen erzeugt. Die N(+)-Implantationsschicht 130 gestattet die Bildung des erfindungsgemässen hochleitenden Bereichs unterhalb dem im weiteren Verlauf erzeugten Gate-Oxid, wobei dieser hochleitende Bereich eine konstante Dichte in seitlicher Richtung und einen Gradienten von einer verhältnismässig hohen Konzentration zu einer relativ niedrigen Konzentration, beginnend von der Chip-Oberfläche unterhalb des Gate-Oxids abwärts in den Chip-Körper hinein, besitzt.

Nach der Erzeugung der N(+)-Implantation 130 wird das Plättchen in ein Oxidationsrohr eingebracht und eine Oxid-Schicht 131 auf der Oberseite des Plättchens aufgewachsen. Danach wird eine Polysilicium-Schicht 132 auf der Oxid-Schicht 131 aufgewachsen. Die polykristalline Silicium-Schicht 132 kann typischerweise eine Dicke von etwa 0,5·10<sup>-3</sup> besitzen und bildet die Gate-Elektrode der fertigen Anordnung nach der weiteren nachfolgend beschriebenen Behandlung.

Die Polysilicium-Schicht 132 wird als nächstes mit einer zweiten Oxid-Schicht 133 überzogen. Danach wird eine dritte Maske auf die Oberfläche der Anordnung gemäss Fig. 10 aufgebracht und ein Photoabdecker durch das in Fig. 11 veranschaulichte Maskenmuster hindurch belichtet. In Fig. 11 sind die undurchlässigen Bereiche der Photoabdecker-Maske in dunklen oder kreuzschraffierten Linien dargestellt. Fig. 15 zeigt die Oberfläche der Anordnung aus Fig. 10 nach der Ätzung durch die mit dem Muster gemäss Fig. 11 gebildete Maske hindurch. Die Maske aus Fig. 11 weist in den grossflächigen schraffierten Bereichen zwischen den Gate-Kontaktfingern ein Muster aus jeweils auf die einzelnen Punkt-Tupfen 102 der Maske aus Fig. 7 zentrierten Polygonal- bzw. Vieleck-Bereiche auf. Jeder dieser Polygonal- bzw. Vieleck-Bereiche bildet, wie weiter unten noch gezeigt wird, jeweils eine der Polygonal-Zellen, welche zwischen der Ober- und Unterseite des Chips in Parallelschaltung liegen.

Nachdem auf der Oberfläche der Oxid-Schicht 133 unter Verwendung des Maskenmusters aus Fig. 11 das Photoabdekker-Muster erzeugt ist, erfolgt eine Oxid-Ätzung zur Herausätzung von polygonalen bzw. vieleckförmigen Öffnungen in der Oxid-Schicht 133. Als Folge dieser Ätzung verbleibt ein Hexagonal-Gitter in der Oberfläche der Schicht 133 und unter den entsprechenden Teilen des Photoabdecker-Gitters.

Es sei darauf hingewiesen, dass die typischen polygon- bzw. vieleckförmigen Öffnungen 140, 141 und 142 in der Oxid-10 Schicht 133 über den P(+)-Tupfen-Bereichen 113, 114 bzw. 115 zentriert sind, wie aus Fig. 14 ersichtlich, welche einen kleinen Teil des Polygon-Zellbereichs aus den Fig. 11 und 15 in Draufsicht zeigt.

Das in den Fig. 14 und 15 verbliebene Oxid-Gitter 133 dient 15 dann als Maske für eine nachfolgende Polysilicium-Ätzung. In einer nunmehr ausgeführten Ätzung werden Polygonal-Öffnungen in der polykristallinen Silicium-Schicht 132 ausgeätzt. Danach werden unter Verwendung des polykristallinen Siliciums als Maske in einer Oxid-Ätzung hexagonalförmige Öffnungen 20 in der Oxid-Schicht 131 geätzt, wie in Fig. 16 veranschaulicht. Nach diesen verschiedenen Ätzvorgängen verbleibt auf der Oberfläche der N(-)-Epitaxial-Schicht 100 ein polygon- bzw. vieleckförmiges Netzwerk aus einer unteren Oxid-Schicht 131 und einer oberen Polysilicium-Schicht 132, das die Gate-Vor-Danach wird das Plättchen gereinigt und für eine Phosphor- 25 richtung für die Anordnungen bildet, die in den anschliessenden Verfahrensschritten hergestellt werden.

Während das das Polysilicium-Gate 132 und die zugehörige darunterliegende Oxid-Schicht 131 definierende Hexagonal-Gitter gemäss den Fig. 14, 15 und 16 erzeugt wird, wird mit dersel-30 ben Oxid-Ätzung und Polysilicium-Ätzung gleichzeitig das Muster für die längsgestreckten Gate-Kontaktfinger, wie beispielsweise den in Fig. 7 gezeigten Kontaktfinger 104, erzeugt. Somit erstreckt sich die über der Oxid-Schicht 131 liegende Polysilicium-Schicht 132 entlang der Chip-Oberfläche, wobei die Auszogen sind. Der N(+)-Bereich 130 wird auch in den in Fig. 13a 35 senränder des Streifens 131-132 als Zellenrand dienen, der mit der um die P(+)-Bereiche 117 bzw. 118 zu erzeugenden Zelle zusammenwirkt. Das gleiche gilt selbstverständlich für alle anderen Zellen in den die Zellen 117 bzw. 118 enthaltenden Zellenspalten bzw. -reihen.

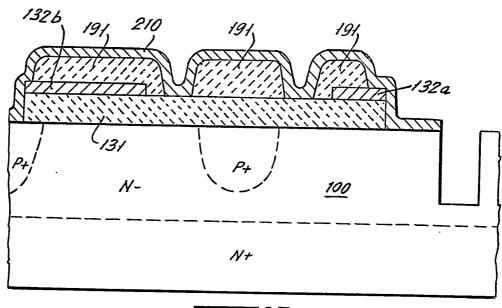

> Die Polysilicium-Schicht 132 und die Oxid-Schicht 133 umschliessen, wie in Fig. 12b ersichtlich, den Aussenumfang der Anordnung. Die Polysilicium-Schicht wird am Umfang der Anordnung und im Bereich 150 abgeschnitten durch geeignete Maskierungs- und Ätz-Schritte während der Ätzung der Polysi-45 licium-Schicht 132 gemäss den Fig. 14 und 15 zur Bildung des Hexagonal-Gittermusters, und es werden äussere Ringe 132a

> Nach der Ätzung der Oxid-Schicht 131 und der Polysilicium-Schicht 132 nach dem eben beschriebenen Verfahren wer-50 den die Plättchen in eine Implantationsapparatur eingebracht. Sodann wird eine Borimplantation an der Plättchenoberfläche vorgenommen, derart, dass P-Leitfähigkeitsträger in die Fenster implantiert werden, die in den Oxid- und Polysilicium-Überzügen auf der Plättchenoberfläche erzeugt wurden und ei-55 ne Maske für den Implantations-Borstrahl bilden.

Der Bohrstrahl kann eine Spannung von etwa 50 kV und eine Dosierung von 5  $\times$  10<sup>13</sup> bis 5  $\times$  10<sup>14</sup> Atomen/cm<sup>2</sup> besitzen. Auf die Implantation folgt eine Diffusions-Drive-Behandlung, die von 30 bis 120 Minuten bei einer Temperatur im Bereich 60 von 1150°C bis 1250°C variieren kann. Durch diesen Vorgang werden P(+)-Ringe 160, 161 und 162 gebildet, die in der aus Fig. 17 ersichtlichen Weise die einzelnen P(+)-Punkte-Tupfen-Bereiche 113, 114 bzw. 115 umgeben. Während der Diffusions-Drive-Behandlung für die P(+)-Bereiche 160, 161 und 162 wird 65 gleichzeitig auch der N(+)-Bereich 130 in eine grössere Tiefe unter der Plättchenoberfläche eingetrieben, wie in Fig. 17 veranschaulicht.

Nach dieser Drive-Behandlung wird die Aussenoberfläche

des Plättchens beispielsweise mittels Fluorwasserstoffsäure entglast und das Plättchen sodann wieder in einen Ofen verbracht und POCl3 in einem geeigneten Trägergas während einer Zeitdauer von 10 bis 50 Minuten bei einer Temperatur von 850°C bis 1000°C ausgesetzt. Durch diesen Verfahrensschritt werden die N(+)-Source-Ringe wie beispielsweise die N(+)-Ringe 170 und 171 erzeugt, welche die P-Bereiche 113 und 114 in Fig. 18 umgeben. Entsprechende Source-Ringe nach Art der Ringe 170 und 171 umschliessen jeweils jede der auf der Oberfläche des Chips erzeugten Tausenden von Zellen; sie haben jeweils einen sechseckförmigen Aussenumfang und zwischen den Aussenumfängen bestehen konstante Abstände von etwa 13 bis 15 Mikron zwischen benachbarten Sechseck-Elementen.

Die Source-Ringe 170 und 171 definieren jeweils innerhalb der P(+)-Bereiche 160 bzw. 161 sechseckförmige bzw. hexagonale Kanäle nach Art der Kanäle 172 und 173 in Fig. 18, welche zu dem gemeinsamen N(+)-Bereich 130 unterhalb des Gate-Oxids 131 führen.

Als Folge dieses Prozesses ergibt sich die in Fig. 19 veranschaulichte Verteilung von Donoren und Akzeptoren in dem N(+)-Bereich 130 unterhalb dem Gate-Oxid 131. Ein Vergleich zwischen den Fig. 19 und 6 lässt erkennen, dass die Verteilung der Donoren an der Oberfläche des Plättchens im Falle der Fig. 19 konstant ist, und nicht wie in Fig. 6 gezeigt schwankend. Ausserdem ist die Donoren-Dichte im oberen Teil des Plättchens grösser als in dem tieferen Bereich, mit dem vorteilhaften Ergebnis, dass hierdurch die Verarmung in den Bereichen 160 und 161 im Betriebszustand der Anordnung herabgesetzt und damit der Widerstand unterhalb den Source-Bereichen 170 und 171 verringert wird. Hierdurch wiederum wird die Auswirkung des unbeabsichtigt durch die verschiedenen pn-Übergänge gebildeten Bipolar-Transistors verringert und die mit diesem Transistor in Verbindung stehenden Probleme hinsichtlich eines zweiten Durchbruchs werden vermieden. Gleichzeitig wird durch diesen Aufbau auch die Avalanche- bzw. Lawinendurchbruchenergie der Anordnung erhöht.

Wie aus Fig. 13c ersichtlich, werden während der in Verbindung mit den Fig. 17 und 18 beschriebenen P(+)- und N(+)-Implantationsschritte auch die hexagonalen P(+)-Bereiche 117 und 118 erzeugt. Die Ränder der Zellen in jeder der Bereiche 117 und 118 erhaltenden Spalten definieren unterhalb der gegenüberliegenden Seiten der Oxid-Streifen 131 des Gate-Fingers liegende Kanalabschnitte 180 und 181.

Nach der Bildung der Source-Bereiche nach Art der Bereiche 170 und 171 in den Verfahrensschritten gemäss den Fig. 17 45 und 18 wird die Anordnung wiederum beispielsweise durch Ätzen in Fluorwasserstoffsäure entglast.

Nach dem Entglasen wird das Plättchen erneut in ein Oxidationsrohr eingebracht und es wird, wie aus Fig. 20 ersichtlich, eine Oxid-Schicht 190 über der gesamten Aussenoberfläche der Anordnung aufgewachsen. Danach wird eine Silox-Schicht 191 über der Oxid-Oberfläche abgeschieden. Das Plättchen wird sodann in einen Flussofen verbracht, um das Silox wieder in einen Fliesszustand zu bringen. Silox ist bekanntlich ein mit Phosphor dotiertes Siliciumoxid, das wieder fliessfähig gemacht wer- 55 über dem P(+)-Bereich 116 liegenden mittleren Aluminiumfinden kann, zur Erzeugung eines kontinuierlichen glasigen Überzugs, welcher den Konturen der Oberfläche, auf welche er aufgebracht wird, folgt. Vorzugsweise enthält die Silox-Schicht 191 7 bis 10 Gew.-% Phosphor. Es wird darauf hingewiesen, dass die Oxid-Schicht 190 und die Silox-Schicht 191 auch über dem länglichen Gate-Fingerbereich gemäss Fig. 13d aufgebracht werden, sowie über dem Aussenumfang der Anordnung gemäss Fig.12b (dort nicht dargestellt).

Danach wird eine in Fig. 21 veranschaulichte vierte Maske auf die Oberseite des Plättchens aufgebracht und ein Photoabdecker-Muster auf der Plättchenoberseite gemäss der Konfiguration der Maske aus Fig. 21 erzeugt, wobei die dunklen Bereiche der Maske in Fig. 21 nicht-polymerisierte Bereiche des Pho-

toabdeckers darstellen. Das Punkt-Tupfen-Muster in der Maske von Fig. 21 erzeugt Öffnungen, die mit den anfänglichen P(+)-Implantationsbereichen nach Art der Bereiche 113, 114 und 115 ausgerichtet sind, während die Linien nach Art der Linien 200 5 und 201 für die Gate-Fingerbereiche über den Mittellinien der Gate-Fingermuster in der Maske von Fig. 7 liegen.

Nach der Erzeugung der in Fig. 20 bei 202 dargestellten Photoabdecker-Maskierung werden jeweils zentrale Bereiche für jede der Polygonal-Zellen freigelegt und eine Oxid-Ätzbe-10 handlung durchgeführt, in welcher das freiliegende Silox 191, das freiliegende Oxid 190 und das Oxid 125 weggeätzt werden und die Oberseite des Epitaxial-Bereichs 100 in der Mitte der einzelnen Polygonal-Zellen freigelegt wird.

Sodann wird das Plättchen gereinigt und auf die gesamte 15 freiliegende Oberseite des Plättchens Aluminium aufgedampft, wie in Fig. 22 durch die Aluminiumschicht 210 veranschaulicht.

Gemäss Fig. 22 sind sämtliche P(+)-Bereiche vereinigt, unter Bildung der P(+)-Zellen 220 und 221, welche ringförmige Source-Elemente 170 und 171 enthalten. Die N(+)-Bereiche 130 20 besitzen eine Tiefe von beispielsweise mehr als etwa 1 Mikron unter der Oberseite. Es ist zu beachten, dass jeder der P(+)-Bereiche jeweils die gewünschte Schelf-Konfiguration unter den N(+)-Ringen aufweist, wie weiter oben anhand von Fig. 5 be-

Die Wirkung des Maske aus Fig. 21 auf die längsverlaufenden Gate-Finger ist in Fig. 13d dargestellt; wie ersichtlich ermöglicht die Maske aus Fig. 21 die Bildung eines Schlitzes in dem Photoabdecker-Muster mit den Abschnitten 220 und 221 in Fig. 13d, unter Freilassung eines Mittelspalts über dem Silox-30 Überzug 191. Auf diese Weise wird in der auf die Erzeugung des Photoabdecker-Musters folgenden Oxid-Ätzung das freiliegende Silox 191 in Fig. 13d und sodann die Oxid-Schicht 190 darunter weggeätzt, unter Freilegung der darunterliegenden polykristallinen Silicium-Schicht 132. Danach wird, wie aus Fig. 35 13e ersichtlich, die gesamte freiliegende Oberfläche der Kontaktfinger mit der Aluminium-Schicht 210 überzogen.

Die Auswirkung der Maske aus Fig. 21 auf die Konfiguration am Aussenrand des Chips ist aus Fig. 12c ersichtlich. Die Maske gemäss Fig. 21 maskiert den umschliessenden Umfangs-40 bereich in solcher Weise, dass bei der anschliessenden Oxid-Ätzung längliche Fenster 230 und 231 durch die Silox-Schicht 191 geätzt werden. Dieser doppelte Einschnitt verhindert eine Polarisierung des durch Rückflussbehandlung erzeugten Silox-Glases 191.

Sodann wird gemäss Fig. 12d über dem freiliegenden Gate-Fingerbereich der Aluminium-Überzug 210 aufgebracht.

Als nächste Maske findet in dem erfindungsgemässen Verfahren eine Maske Verwendung, welche die Aufbringung einer Photoabdecker-Maske ermöglicht, mittels welcher Streifen oder 50 Fenster 250 und 260 in jeden der längsverlaufenden Gate-Finger geätzt werden können, wie in Fig. 13f dargestellt. Somit wird ein geeignetes Photoabdecker-Muster aufgebracht und sodann eine Aluminium-Ätzung unter Verwendung eines geeigneten Atzmittels für Aluminium durchgeführt, zur Isolierung des nur gers. Dieser Aluminiumfinger dient als Gate-Kontakt, der mit dem polykristallinen Silicium 132 verbunden ist, das seinerseits ein kontinuierlicher Teil des sich über die gesamte Oberfläche des Chips erstreckenden Polygonal- bzw. Vieleck-Maschennet-60 zes ist. Auf diese Weise werden die Gate-Finger elektrisch mit einer grossen Anzahl einzelner Sechseck-Bereiche verbunden. um eine gute elektrische Anschlussverbindung zu der gesamten Gate-Oberfläche für den Chip zu gewährleisten.

Gleichzeitig ermöglicht die Maske die weitere Behandlung 65 des umschliessenden Umfangsrandes des Chips durch Ätzen der Aluminium-Schicht in den Bereichen 230 und 231, wie aus Fig. 12e ersichtlich. Fig. 12e lässt erkennen, dass die Metallisierung 210 einen abgeschnittenen Ringbereich 210a aufweist, der elek9 656 745

trisch mit dem darunter befindlichen polykristallinen Silicium-Bereich 132a verbunden ist und als Feldstopperring wirkt. Da der Bereich 210a mit der Drain-Elektrode verbunden ist, kann der N(-)-Bereich unterhalb dem Ring 210 und am Aussenumfang des Chips infolge einer Ladung auf dem polykristallinen Silicium-Bereich 132a nicht invertiert werden. Der Aussenumfang der Metallisierung 210 ist mit dem Ring 132b verbunden, wie aus Fig. 12e ersichtlich, wobei der Ring 132b als eine Feldplatte wirkt.

Nach der Aluminium-Ätzung wird der Photoabdecker entfernt und über der gesamten freiliegenden Oberfläche des Plättchens und sämtlicher Chips innerhalb des Plättchens wird Silox aufgebracht. Diese zweite Silox-Schicht 250 (Fig. 22) dient zum Schutz und wird keiner Flussbehandlung unterworfen. Die Silox-Schicht 250 hat eine niedrigere Phosphorkonzentration als die erste Schicht 191, beispielsweise kann die Phosphorkonzentration im Bereich von 2 Gew.-% bis 4 Gew.-% liegen.

Danach wird eine sechste Maske auf die Anordnung aufgebracht, welche die gesamte Oberfläche mit Ausnahme der vergrösserten Kissenbereiche für den Anschluss zum Gate und Source (entsprechend den Bereichen 105 und 106 in Fig. 7) maskiert. Das Plättchen wird sodann in ein Ätzmittel für Silox eingetaucht, welches das Silox von den Kissenbereichen entfernt und den Aluminiumüberzug auf den Kissen freilegt. Sodann

wird der Photoabdecker von dem Plättchen abgelöst und das Plättchen in geeigneter Weise gereinigt.

Sodann wird ein Rückseitenmetall, das aus Schichten von Chrom, Nickel und Silber besteht, auf das Plättchen in Form 5 der Rückseitenelektrode 270 aufgebracht, die als Drain-Anschlussbereich für die Anordnung dient.

Sodann werden sämtliche Chips in geeigneter Weise getestet und längs der Anreiss- bzw. Bruchlinien aus dem Plättchen herausgebrochen, wie in Verbindung mit Fig. 1 beschrieben wurde, und sodann gereinigt. Mit den Source- und Gate-Kissen werden sodann geeignete Elektrodendrähte verbunden und die Anordnung wird in einem Gehäuse montiert, das mit der Drain-Elektrode 270 verbunden sein kann.

Die Erfindung wurde vorstehend anhand einer zellenförmi-15 gen Anordnung für die Source-Zellen gemäss der älteren Anmeldung DOS 2 940 699 beschrieben. Selbstverständlich eignet sich die Erfindung auch zur Anwendung bei fingerförmig ineinandergreifenden Source-Konfigurationen, wie sie ebenfalls in der älteren Anmeldung DOS 2 940 699 beschrieben sind.

Die Erfindung wurde vorstehend anhand einer bevorzugten Ausführungsform beschrieben, die jedoch selbstverständlich in mannigfacher Weise abgewandelt und modifiziert werden kann, ohne dass hierdurch der Rahmen der Erfindung verlassen wird

FFE-17

EIGIGE.

ET = 136.

FFE-13c-

TIG.14.

FIG.20.