(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4070245号

(P4070245)

(45) 発行日 平成20年4月2日(2008.4.2)

(24) 登録日 平成20年1月25日(2008.1.25)

(51) Int.Cl.

G 11 B 5/60 (2006.01)

G 11 B 21/21 (2006.01)

F 1

G 11 B 5/60

G 11 B 21/21P

C

請求項の数 14 (全 12 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平10-532955                 |

| (86) (22) 出願日 | 平成10年1月20日(1998.1.20)        |

| (65) 公表番号     | 特表2000-513861(P2000-513861A) |

| (43) 公表日      | 平成12年10月17日(2000.10.17)      |

| (86) 國際出願番号   | PCT/US1998/001197            |

| (87) 國際公開番号   | W01998/034219                |

| (87) 國際公開日    | 平成10年8月6日(1998.8.6)          |

| 審査請求日         | 平成16年11月2日(2004.11.2)        |

| (31) 優先権主張番号  | 08/785,570                   |

| (32) 優先日      | 平成9年1月21日(1997.1.21)         |

| (33) 優先権主張国   | 米国(US)                       |

|           |                                                                           |

|-----------|---------------------------------------------------------------------------|

| (73) 特許権者 | クウォンタム・コーポレイション<br>アメリカ合衆国、95110 カリフォルニア州、サン・ノゼ、テクノロジー・ドライブ、1650、スイート・800 |

| (74) 代理人  | 弁理士 深見 久郎                                                                 |

| (74) 代理人  | 弁理士 森田 俊雄                                                                 |

| (74) 代理人  | 弁理士 伊藤 英彦                                                                 |

| (74) 代理人  | 弁理士 堀井 豊                                                                  |

最終頁に続く

(54) 【発明の名称】 2軸遮へい導体トレースアレイを備えたサスペンション

## (57) 【特許請求の範囲】

## 【請求項1】

記憶媒体に近接する読み取り/書き込みヘッド/スライダーセンブリを支持するためかつヘッドを読み取り/書き込み回路に電気的に相互接続するためのロードビームを含む一体化されたロードビームアセンブリであって、

前記ロードビーム上に配置され、前記読み取り/書き込みヘッド/スライダーセンブリの近くまで延在する総体的に平坦な導電部材と、

前記導電部材上に形成される第1の電気絶縁層と、

前記第1の電気絶縁層上に形成される第1の電気信号トレース経路と、

前記第1の電気信号トレース経路上に形成される第2の電気絶縁層と、

前記第2の電気絶縁層上に形成され、前記第1の電気信号トレース経路を電気的干渉から遮へいするための導電遮へい層と、

前記導電部材によって前記第1の電気信号トレース経路の直下に定められる長手方向のウインドウとを含み、前記長手方向のウインドウの幅を選択して前記アセンブリの電気インピーダンスを制御する、一体化されたロードビームアセンブリ。

## 【請求項2】

前記総体的に平坦な導電部材はフレクシヤを含み、前記フレクシヤは、前記ロードビームに接続され、前記読み取り/書き込みヘッド/スライダーセンブリを前記記憶媒体に近接させて位置決めするためのジンバルを含む、請求項1に記載の一体化されたロードビームアセンブリ。

10

20

## 【請求項 3】

前記第1の電気絶縁層上に形成され、前記第1の電気信号トレース経路に関し横方向にオフセットされて第1の導体トレース対を形成する第2の電気信号トレース経路をさらに含む、請求項1に記載の一体化されたロードビームアセンブリ。

## 【請求項 4】

前記遮へい層は前記第1の電気信号トレース経路および前記第2の電気信号トレース経路を覆っている、請求項3に記載の一体化されたロードビームアセンブリ。

## 【請求項 5】

前記遮へい層は前記総体的に平坦な導電部材に接地される、請求項4に記載の一体化されたロードビームアセンブリ。

10

## 【請求項 6】

前記導電部材上に配置された第3の電気絶縁層と、前記第3の電気絶縁層上に第2の対として形成されて第2の導体トレース対を形成する第3および第4の電気信号トレース経路とをさらに含み、前記第1の導体トレース対は前記導電部材の長手方向の1つの端部領域に沿い配置され、前記第2の導体トレース対は前記1つの端部領域から横断方向に間隔をおいた前記導電部材の長手方向の別の端部領域に沿い配置される、請求項3に記載の一体化されたロードビームアセンブリ。

## 【請求項 7】

前記長手方向のウィンドウは少なくともその一部分が誘電材料により占められている、請求項1に記載の一体化されたロードビームアセンブリ。

20

## 【請求項 8】

前記長手方向のウィンドウは薄膜金属堆積層として形成されるシールドを含む、請求項1に記載の一体化されたロードビームアセンブリ。

## 【請求項 9】

記憶媒体に近接する読み取り/書き込みヘッド/スライダアセンブリを支持するためかつヘッドを読み取り/書き回路に電気的に相互接続するための一体化されたロードビームアセンブリであつて、

前記読み取り/書き込みヘッド/スライダアセンブリを末端で支持する総体的に平坦に形成されたロードビームと、

前記ロードビーム上に配置され、前記読み取り/書き込みヘッド/スライダアセンブリの近くまで延在する総体的に平坦な導電部材と、

30

前記導電部材上に配置される第1の電気絶縁層と、

前記第1の電気絶縁層上に配置される少なくとも1つの電気信号トレース経路と、

前記総体的に平坦な導電部材に接続され、前記少なくとも1つの電気信号トレース経路に重なり取囲む関係でかつ前記少なくとも1つの電気信号トレース経路から間隔をおいて配置されるシールドと、

前記導電部材によって前記少なくとも1つの電気信号トレース経路の直下に定められる長手方向のウィンドウとを含み、前記長手方向のウィンドウの幅を選択して前記アセンブリの電気インピーダンスを制御する、一体化されたロードビームアセンブリ。

## 【請求項 10】

40

前記少なくとも1つの電気信号トレース経路上に配置され、前記シールドを前記トレース経路から分離する第2の電気絶縁層をさらに含む、請求項9に記載の一体化されたロードビームアセンブリ。

## 【請求項 11】

前記第1の電気絶縁層上に配置され前記シールドにより囲まれる実質的に並列する信号経路を規定する複数の電気信号トレース経路を含む、請求項9に記載の一体化されたロードビームアセンブリ。

## 【請求項 12】

記憶媒体に近接する読み取り/書き込みヘッド/スライダアセンブリをロードビーム上で支持するためかつヘッドを読み取り/書き回路に電気的に相互接続するための一体化されたフレクシャ

50

/導体構造であって、

前記読み取り/書き込みヘッド/スライダアセンブリを支持するためのジンバルを有する総体的に平坦な導電フレクシヤ部材と、

前記フレクシヤ部材上に配置される第1の電気絶縁層と、

前記第1の電気絶縁層上に配置される第1および第2の電気信号トレース経路と、

前記第1および第2の電気信号トレース経路上に配置される第2の電気絶縁層と、

第2の電気絶縁層上に配置され、前記第1および第2の電気信号トレース経路を遮へいするための電気シールドと、

前記導電部材によって前記第1および第2の電気信号トレース経路の直下に定められる長手方向のウィンドウとを含み、前記長手方向のウィンドウの幅を選択して前記アセンブリの電気インピーダンスを制御し、

前記一体化されたフレクシヤ/導体構造は前記ロードビーム上に配置されるので姿勢の低いサスペンションアセンブリが与えられる、一体化されたフレクシヤ/導体構造。

10

【請求項13】

前記電気シールドは前記導電フレクシヤ部材に接続される、請求項12に記載の一体化されたフレクシヤ/導体構造。

【請求項14】

前記電気シールドは前記第2の絶縁層上に堆積され延在して前記導電フレクシヤ部材とのコンタクトを取る薄膜金属を含む、請求項13に記載の一体化されたフレクシヤ/導体構造。

20

【発明の詳細な説明】

関連出願の参照

本願は、1996年10月3日に出願され、「最適化された電気パラメータのための多層一体化導体トレースアレイを備えたサスペンション (Suspension with Multi-Layered Integrated Conductor Trace Array for Optimized Electrical Parameters)」と題された、同時係属中の米国特許出願第08/720,833号の一部継続出願であり、その開示を本明細書において引用により援用する。

発明の分野

この発明は包括的に、磁気ハードディスクドライブにおいて使用するためのヘッドサスペンションアセンブリと一体的に形成された導体トレースアレイを電気的に遮へいするための構造および方法に関する。

30

発明の背景

現代の磁気ハードディスクドライブは典型的に、回転固定記憶ディスクと、データ変換器をディスクの回転軸に関し異なる放射方向の場所で位置決めすることによりディスクの各記録面上の多数の同心データ記憶トラックを定めるためのヘッドポジショナとを含む。ヘッドポジショナは一般にアクチュエータと呼ばれる。当該技術では多数のアクチュエータ構造が既知であるが、現在最も頻繁に用いられているのはインライン回転音声コイルアクチュエータであり、その理由は、簡素で高性能かつ回転軸に関しマスバランスを取ることが可能であることであり、後者は摂動に対するアクチュエータの感度を減じるために重要なものである。従来はディスクドライブ内において閉ループサーボシステムを用いて音声コイルアクチュエータを動作することによりヘッドをディスク記憶面に関して位置決めしている。

40

单一または二素子設計でもよい読み取り/書き込み変換器は、典型的には、変換器を動いている媒体の表面から少し離れたところで支持するための空気軸受面を有するセラミックスライダ構造の上に設けられる。单一書き込み/読み取素子設計は典型的に2線接続を必要とし、別個の読み取りおよび書き込み素子を有する二素子設計は2線接続を2対必要とする。特に別個の誘導性書き込み素子を有する磁気抵抗(MR)ヘッドは一般に、4本のワイヤを必要とする。空気軸受スライダおよび読み取り/書き込み変換器を組合せたものはまた、読み取り/書き込みヘッドまたは記録ヘッドとして知られている。

一般的にスライダは、サスペンションのロードビーム構造の末端側の端部に装着されたジ

50

ンバルフレクシャ構造に取付けられる。ばねがロードビームおよびヘッドをディスクに向けて付勢する一方で、スライダに関するディスクの回転により生じたヘッド下の空気圧がヘッドをディスクから離れるように押す。ジンバルによりスライダがディスク表面に向かって「飛行」の姿勢を取りかつその表面形状を辿ることが可能になる。平衡距離が「空気軸受」を定め、かつヘッドの「飛行の高さ」を決定する。空気軸受を利用してヘッドをディスク表面から離して支持することにより、ヘッドはヘッド／ディスクの界面において、境界潤滑状況というよりもむしろ流体潤滑状況下で動作する。空気軸受は、変換器の効率を低下させる変換器と媒体との間の空間を維持する。しかしながら、直接的な接触を避けることにより、ヘッドおよびディスク構成部品の信頼性および耐用寿命が大幅に向上する。それにもかかわらず、面積密度の増大に対する要求は、ヘッドが擬似接触状態で、または境界潤滑接触状況においてすら動作することを必要とするかもしれない。

現在、公称の飛行の高さは0.5から2マイクロインチのオーダである。磁気記憶密度は、ヘッドがディスクの記憶表面に近づくに従って増大する。したがって飛行の高さが非常に低いことは、ディスクドライブの相応な運用寿命にわたる装置の信頼性と引換えになる。同時に、記憶表面へのおよび記憶表面からのデータ転送速度が増大しつつあり、秒速200メガビットに近づきつつあるデータ速度は実際の計画範囲内である。

ディスクドライブ産業は、アクチュエータアセンブリの動く質量を減少させ、変換器がディスク表面により近づいて動作できるようにするために、スライダ構造のサイズおよび質量を徐々に減少させているが、前者はシーク性能を向上させ、後者はより高い面積密度と引換え可能な変換器の効率の向上をもたらすものである。通常スライダのサイズ（したがって質量）は、いわゆる標準の100%スライダ（「ミニスライダ」）を参照して特徴付けられる。したがって70%、50%および30%スライダ（それぞれ「マイクロスライダ」、「ナノスライダ」および「ピコスライダ」）という用語は、標準のミニスライダの線形寸法に関し適用できるパーセントに応じて定められる線形寸法を有するごく最近の低質量のスライダを指す。20%の「フェムトスライダ」のような30%ピコスライダよりも小さなスライダが現在検討されており、ヘッドの販売者による初期開発段階にある。スライダ構造は小さくなるに従って一般的にはより柔軟に振る舞うジンバルを必要とするものである。したがって、スライダに装着された導体のワイヤの本質的なスチフネスが、多大な望ましくない機械バイアス効果を生む可能性がある。

この本質的なワイヤのスチフネスまたはバイアスの効果を減少させるために、ヘッドに近接してフレクシャの末端側の端部で位置決めされたボンディングパッドで導体が露出するように、ワイヤを絶縁可撓性重合樹脂フレクシャと効果的に一体化させた、一体化フレクシャ／導体構造が提案されている。マツザキ（Matsuzaki）への米国特許第5,006,946号はこのような構成の例を開示している。ベニン（Bennin）他への米国特許第5,491,597号、エインズリ（Ainslie）他への米国特許第4,761,699号、およびエルペルディング（Erpelding）他への米国特許第4,996,623号は、当該技術で既知であるさらに他の例を開示している。このような配線構成には何らかの性能およびアセンブリについての利点があるが、開示されたような可撓性重合樹脂材料をフレクシャおよびジンバル構造に導入するには多数の困難な設計上の問題がある。たとえば、樹脂材料の熱膨張特性は、先行技術によるステンレス鋼構造と同じではなく、何らかの必須の接着層を含むこのような樹脂構造の長期耐久性については未知である。したがって、一体化された導体フレックス回路フレクシャ構造のほとんどの利点を取り入れる一方で、先行技術による製造およびロードビーム装着法との互換性をほとんど残した、ハイブリッドステンレス鋼フレクシャおよび導体構造が提案されている。このようなハイブリッド設計は典型的には、近接して設けられたプリアンプチップ、およびヘッド／ディスクアセンブリに装着された回路板上に（他の回路とともに）典型的には設けられる下流の読み取りチャネル回路といった、関連のドライブエレクトロニクスへのヘッドの電気的相互接続のための絶縁および導電トレース層が設けられた、ステンレス鋼フレクシャを用いている。

「ジンバルフレクシャおよび電気相互接続アセンブリ（Gimbal Flexure and Electrical Interconnect Assembly）」と題されたベニン他への米国特許第5,491,597号に

10

20

30

40

50

より教示されるように、開示された先行技術の方策では、たとえば純なまし銅よりも明らかに電気抵抗が高いベリリウム銅合金のような、導電トレース層のためのばね材料の使用を必要とする。他方、純なまし銅は高周波では電気導体として十分であるが、ばね状の機械的レジリエンスよりもむしろ延性が高く、したがって相互接続トレース材料について所望される機械的ばね特性に欠けている。たとえばニッケルベース層上にめっきまたは堆積された純銅からなるトレースは、ベニン他の方策が依拠するベリリウム銅合金に代わるものとなる。

このハイブリッドフレクシャ設計は、フレクシャの末端側のヘッドが取付けられた端部にあるボンディングパッドからフレクシャの基部側の端部へと比較的長く延在する導体トレース対または4本のワイヤの組を用いて、関連のサスペンション構造の長さに沿い読取／書込ヘッドからプリアンプまたは読取チャネルチップへの導電経路を与える。導体トレースはフレクシャにごく近接して総体的に並列かつ間隔が設けられた関係で位置決めされるため、露出したトレースは、今まで各ヘッドの読取／書込素子を下流の処理エレクトロニクスに接続するのに用いられている従来の微細なより対線の自己遮へい特性に欠けている。したがって露出したトレースは、ヘッドの読取素子において誘導される非常に低レベルの信号を歪ませるまたはマスキングし得る望ましくない信号をピックアップしやすい。

マイクロストリップ線技術は、ループおよび導体内キャパシタンスは、伝送線路を形成しているマイクロストリップの寸法および／またはマイクロストリップ間の間隔を変えることによって変更可能であると教示している。しかしながら、ヘッドサスペンションロードビームとともに使用するための一体化トレースアレイ配線方法の場合、導体の寸法は、トレース相互接続アレイのためにフレクシャ上で利用できる空間を含む機械的制約に支配され、トレース導体の寸法は、インピーダンス整合または同調に関する限り大きく変更することはできない。

プリント回路導体はより対線の属性を有さないため、雑音が、トレース相互接続アレイの電気的性能に影響を及ぼす要因となり得る。以前の、1996年10月3日に出願された、同一人に譲渡され同時係属中の米国特許出願第08/724,978号は、書込経路導電トレースを用いることにより読取経路導電トレースを遮へいし得ると教示しているが、実際にはこの方策は、電気的理由とは反対に構造上の理由により状況によっては適切でないと考えられる。たとえば、ロードビーム構造の機械的対称性を保つためには、読取トレースおよび書込トレースは分離され、ロードビームの対向する長手方向の端部に沿い別々の経路を取るようにされる。このような対称的な配置を取ると、書込トレースを用いて読取トレースを遮へいすることはできない。したがって、ハードディスクドライブのヘッド取付構造において使用される導体トレースアレイにおける改良されたトレース導体遮へいが必要であるが未だに得られていない。

#### 発明の概要および目的

この発明の包括的な目的は、先行技術の制限および欠点を克服する、読取／書込ヘッドを関連の読取／書込回路に電気的に相互接続するための、2軸で遮へいされた一体化導体トレースアレイを有する、姿勢が低く、強固でかつ信頼性の高い高性能のサスペンションアセンブリを提供することである。

この発明の他の包括的な目的は、効果的に遮へいされた多層トレースジオメトリが制御されることにより先行技術の制限および欠点を克服する、一体化されたサスペンションおよび導体構造を提供することである。

この発明の他の目的は、ハードディスクドライブにおけるスライダ上に設けられた読取／書込ヘッド素子を支持し電気的に接続するための、改良されたサスペンションおよび多層で2軸で遮へいされた導体トレースアレイを提供することである。

この発明の原理に従うサスペンションアセンブリは、記憶媒体に近接する読取／書込ヘッド／スライダアセンブリを支持するため、かつヘッドを読取／書込回路に電気的に相互接続するための、ロードビームおよびフレクシャを含む。このアセンブリはさらに、たとえばフレクシャ上に配置された第1の電気絶縁層と、導体トレース対を形成しつつ第1の電気絶縁層上に総体的に並列および間隔が設けられた関係で配置された第1および第2の電

10

20

30

40

50

気信号トレース経路と、導体トレース対を覆う第2の電気絶縁層と、第2の電気絶縁層上に形成され導体トレース対を外部からの電気的干渉から遮へいするための導電遮へい層とを含む。ある好ましい形式では、遮へい層はフレクシャに接地される。別の好ましい形式では、遮へい層はフレクシャにより与えられる接地面に關し電気的に浮動状態とされ、遮へい層の厚みは、干渉波頭の周波数での表皮効果の深さよりも大きい。

この発明のある関連の局面では、間隔が設けられ総体的に並列する信号トレース経路の第1および第2の対は、第1の導体トレース対がフレクシャの1つの長手方向の端部領域に沿い形成され、第2の導体トレース対がその1つの長手方向の端部領域に対し横断方向において対向するフレクシャの別の長手方向の端部領域に沿い形成されるように、フレクシャ上に形成されるため、第2の導体トレース対は長手方向の対称軸に關し第1の導体トレース対と実質的に対称をなす。

この発明の上記およびその他の目的、利点、局面および特徴は、添付の図面と関連付けて示された以下の好ましい実施例の詳細な説明を考慮することにより、認識および理解がより深まるであろう。

#### 【図面の簡単な説明】

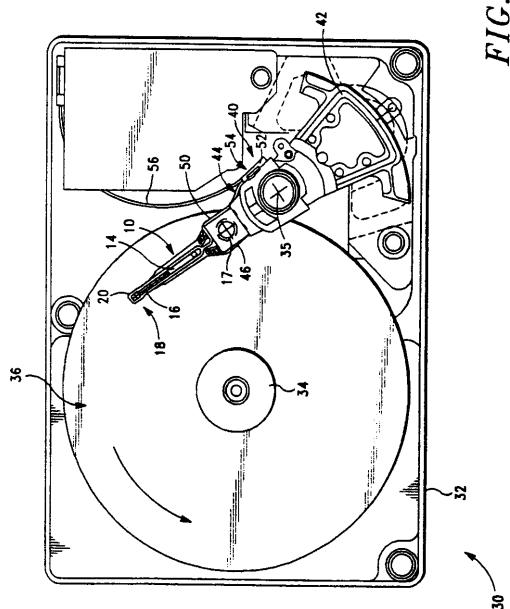

図1は、この発明の原理を取り入れた遮へいされた多層導電トレースアレイを備えるサスペンションアセンブリを有するアクチュエータを含む、ハードディスクドライブのヘッドディスクアセンブリの拡大平面図である。

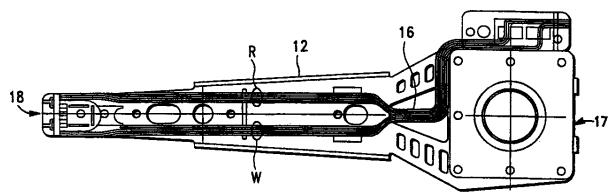

図2は、この発明の原理に従う遮へいされた導電トレースを有する図1のヘッドディスクアセンブリに含まれる、一体化されたフレクシャ／導体ロードビーム構造の拡大平面図である。

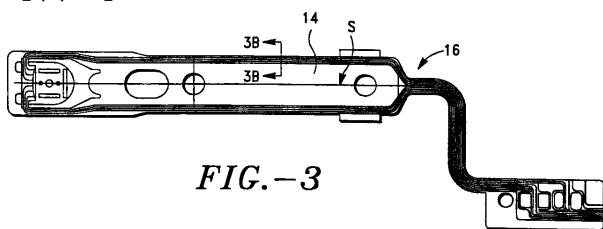

図3は、同調された導電トレースアレイを取り入れた一体化配線を有する図2のロードビーム構造のフレクシャの拡大平面図である。

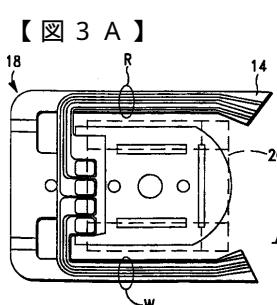

図3Aは、図3のフレクシャトレースアレイの読み取り／書き込みヘッド接続領域の大幅に拡大された平面図であり、ヘッドスライダは破線の輪郭で示されている。

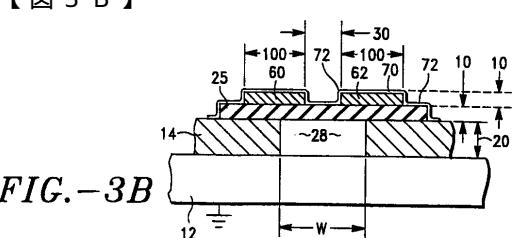

図3Bは、図3における線3B-3Bに沿う立面断面を大幅に拡大した図であり、この発明の原理に従いトレース対の2つの導電トレースを遮へいするための外側の誘電層上に形成される薄膜導電シールド（遮へい）を示す。

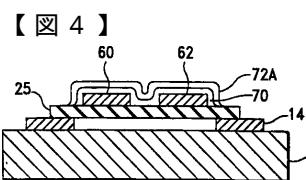

図4は、この発明の原理に従うトレースの対を遮へいするための一体化された浮動遮へい層を示す、図3Bと同様の図である。

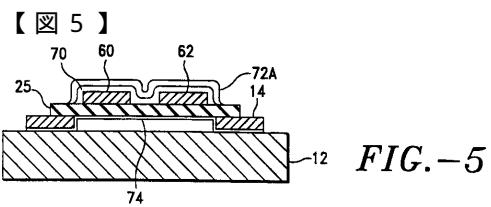

図5は、この発明の原理に従いフレクシャ層で金属を堆積させることによりシールドを形成することを示す、図4と同様の図である。

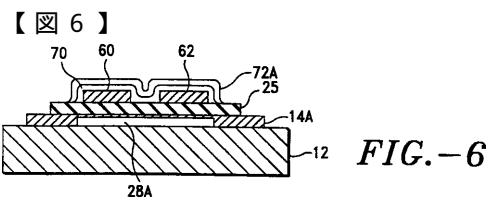

図6は、この発明の原理に従いフレクシャ層で部分的にエッチングされたキャビティを形成することを示す、図4と同様の図である。

図7は、この発明の原理に従い誘電充填体材料で充填されたフレクシャ層で部分的にエッチングされたキャビティを形成することを示す、図4と同様の図である。

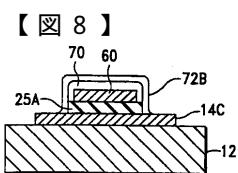

図8は、この発明の原理を取り入れた、シングルエンドの配置において単一の導電トレースを遮へいするための外側の誘電層上に形成された薄い導電シールドを示す、図3Bと同様の図である。

#### 好ましい実施例の詳細な説明

図面を参照すると、図面を通して同じ参照符号は同じまたは対応する部分を示しており、図1は、ハードディスクドライブ30のヘッド／ディスクアセンブリ（HDA）の平面図である。ハードディスクドライブ30は、フレクシャ14を備えるロードビーム12を含む少なくとも1つのロードビームアセンブリ10を用いる。フレクシャ14は、この発明の好ましい実施例として遮へいされたトレース相互接続アレイ16を含む。図1は、意図される動作環境内で用いられるフレクシャ14および遮へいされたトレース相互接続アレイ16を備えるロードビームアセンブリ10を示す。

この例では、ディスクドライブ30は、曲線で示された矢印の方向に少なくとも1つの記憶ディスク36を回転させるためのスピンドル34（およびスピンドルモータ（図示せず））を支持するための、たとえば固定ベース32を含む。ドライブ30はまた、回転する

10

20

30

40

50

ように旋回点 35 でベース 32 に取付けられた回転アクチュエータアセンブリ 40 を含む。アクチュエータアセンブリ 40 は、制御回路（図示せず）により選択的にエネルギーが与えられたときにアクチュエータ E ブロック 44 およびヘッドアーム 46（およびロードビームアセンブリ 10）を移動させることによって対向する記憶ディスクの面上に定められた放射方向のトラック位置でこれらを位置決めする、音声コイル 42 を含む。ロードビームアセンブリ 10 の少なくとも 1 つは、基部側の端部 17 で、たとえば従来のボールスウェーブ加工技術によりヘッドアーム 46 の末端側の端部に固定される。

必ずしも必要ではないが従来、2つのロードビームアセンブリ 10 がディスク 36 間においてヘッドアーム 46 に装着され、1つのロードビーム構造 10 が、スピンドル 34 において間隔が設けられた複数のディスク 36 からなるディスクの積み重ねのうちの最上部のディスクの上方および最下部のディスクの下方でヘッドアームに取付けられる。トレース相互接続構造 16 は、E ブロック 44 の側部に固定されたたとえばセラミックハイブリッド回路基板 52 に延在する可撓性のトレース / 膜セグメント 50 に接続する。セラミックハイブリッド回路 52 は読み取りプリアンプ / 書込ドライバ回路を形成する半導体チップ 54 を固定および接続する。（ある応用例では、表面に載置された I C 54 を備えるフレックス回路基板がセラミックハイブリッド回路基板 52 よりも好ましいことがある。）最も好ましくは、チップ 54 はハイブリッド回路 52 のセラミック基板および E ブロックの側壁との間で入れ子状にされ、適切な導電性接着剤または熱伝達化合物によりその側壁に固定されて、チップ 54 の動作中に生じる熱は伝導により E ブロックに放散し、対流により周囲空気体積へと外に向かって放散する。フレックス回路 56 は、基板 52 およびディスクドライブの他の電子回路（図 1 には示さず）へのおよびそこからの電気接続を与える。

図 2、3、3A および 3B に示すように、ロードビームアセンブリ 10 は、総体的に平坦に形成されたステンレス鋼ロードビーム 12 と、長いフレクシャ 14 とを含む。この例では、フレクシャ 14 は、たとえば厚みがおよそ 20 - 25 ミクロンで最も好ましくは 25 ミクロンである薄いステンレス鋼シート材料からなる。導電トレース 60 および 62 は、間隔がおかれて総体的に並列な関係で形成され、厚みおよそ 10 - 18 ミクロンの銅の導体であり、最も好ましくは厚みは 10 ミクロンである。図 3B に示した導体トレース 60 および 62 は、たとえば、フレクシャ 14 の基部側の端部 17 でヘッド 20 の読み取り素子から、ロードビームアセンブリ 10 のスライダを支持する末端側の端部 18 に位置する別の接続パッドアレイ 22 へと延在する、相互接続構造 16 の読み取り経路導体トレース対を形成する。同様の導体トレース対が、ヘッド 20 の書き込み素子への接続のための書き込み経路 W を形成する。

最も好ましくは、導体トレース対 R および W は、フレクシャの所望の機械的特性を損なわないように、対称をなすように形成されかつフレクシャ 14 の長手方向の端部に沿い長手方向の対称軸 S（図 3）を中心として間隔を設けられる。変換器ヘッドスライダ 20（図 3A で破線の輪郭で示す）は、ロードビーム構造 10 の末端側の端部 18 で適切な接着剤によりジンバル 14 に取付けられる。図 3C に示すように、末端側の端部 18 における接続パッド 22 は、たとえば超音波溶接された金のボールボンド 56 により、スライダボディ 20 の後縁上に形成された二素子（4 导体）薄膜磁気抵抗読み取り / 薄膜誘導性書き込み構造 26 の整列した接続パッド 24 に接続するために与えられる。必ずしも必要ではないが最も好ましくは、スライダボディ 20 は 30 % ピコスライダである。

相互接続構造 16 は、ステンレス鋼フレクシャ 14 に取付けられた導体アレイ 16 の導電トレース 60 および 62 間に介在する高誘電性ポリイミド膜ベース 25 を含む。誘電層 25 の厚みはおよそ 10 - 18 ミクロンであり、最も好ましくは約 10 ミクロンである。誘電層 25 を、たとえばシルクスクリーニング、スピンドルコーティング、または精密ブレードまたはローラでのコーティングといった何らかの適切な方法により液体状態で与えてもよい。ポリイミドを備える接着剤によるように、ポリイミド誘電層 25 を与える他の方法は、この発明の意図する範囲内である。

共同発明者による、同一人に譲渡される 1996 年 10 月 3 日に出願され、「トリミング

10

20

30

40

50

されたインピーダンスを有する一体化された導体を備えるサスペンション (Suspension with Integrated Conductors Having Trimmed Impedance) 」と題された、米国特許出願第 08/720,836 号の開示を本明細書に引用により援用するが、この出願により教示されるように、フレクシャ 14 は読み取り / 書込ヘッドのためのジンバル取付けを与えることに加え、好ましくは導体構造 16 の導電トレース 60 および 62 に沿って制御された幅 (w) および配置で 1 つ以上の開口部またはトラフ 28 を定める。フレクシャ 14 に沿って定められた長手方向の開口部 28 は、たとえば、導体構造のインダクタンス、キャパシタンスおよびラインインピーダンスの抵抗成分を、導体アレイ 16 に関する幅寸法 (W) を変化させることにより同調させることを可能にする様で、導体アレイ 16 に関して配置され間隔が取られる。

プリント回路導体は、より対線と同じ電気的自己遮へいの属性を有さないため、雑音が重要な要素となり得る。1996年10月3日に出願され、「自己遮へい一体化導体トレースアレイを備えるヘッドサスペンション (Head Suspension with Self-Shielding Integrated Conductor Trace Array) 」と題された、同一人に譲渡される同時係属中の米国特許出願第 08/724,978 号は、書込導体トレースを読み取りトレース導体から離して配置するアレイレイアウトにより読み取り経路トレース導体を遮へいし得ることを開示している。しかしながら、たとえば図 3 に示すようにフレクシャ 14 の機械的対称性を保つことが必要だということは、実際にはフレクシャ 14 の対向する端部に沿って読み取りおよび書込導体の対 R および W の経路を別々に取ることが最良であることを示唆している。この図 3 に示したトレース導体対の所望の対称配置は、読み取りトレース導体のシールド (遮へい) として書込トレース導体を用いることを効果的に除外する。

図 3B に示すように、この発明の原理に従うと、相互接続アレイ 16 は、好ましくは相互接続トレースアレイ 16 の 2 つの層において重なり合って整列するように配置された 1 対の導電トレース 60 および 62 を含む。第 1 の絶縁ポリイミド (可撓性重合樹脂材料) 層 25 は、トレース 60 および 62 を薄いステンレス鋼フレクシャ 14 から分離する。ポリイミドの外側の絶縁誘電層 70 は、第 1 および第 2 のトレース 60 および 62 上に形成される。外側の誘電層 70 の厚みはたとえば 3.14 ミクロンであり、最も好ましくは、フレクシャ 14 に追加されるスチフネスを最小とするためには約 3 ミクロンである。外側のシールド (遮へい) 72 は、最も好ましくは、たとえば 0.1 から 1.0 ミクロンの厚みで (最も好ましくは約 0.1 ミクロン) 外側のポリイミド層 70 上に薄膜金属層として堆積することにより形成される。薄膜堆積層 72 は、ステンレス鋼フレクシャ 14 との電気的接地コンタクトを取るために、外側の層 70 の横方向の端部を超えて、内側の誘電層 25 の端部上まで続く。フレクシャ 14 の方では、E ブロックおよびアクチュエータ構造 40 を通してハードディスクドライブのベース 32 に接地されるロードビーム 12 に接地される。薄膜シールド層 72 を設けて、たとえば読み取り素子トレース導体対 R を含むトレース 60 および 62 を遮へいする。外側の誘電層 70 は内側の誘電層 25 と同様の誘電特性を有し、何らかの適切な方法で与えることができる。シールド薄膜層 72 は、好ましくは銅、銀、金またはステンレス鋼からなり、最も好ましくは銅の膜からなる。

図 3B に示すように、薄膜シールド (遮へい) 72 は、フレクシャ 14 に電気的に接地され、フレクシャ 14 の全体的な所望の機械特性に調和する適切な厚みを有することができる。薄膜シールド層 72 は接地されているため、各トレース 60 および 62 から共通の接地面へのキャパシタンスを増大する効果がある。この共通の接地面へのキャパシタンスは、参照する米国特許出願第 08/720,836 号の教示に従うパターニングされた反応性イオンエッティングまたはイオンミリングプロセスによるように、シールド 72 において長手方向に延在するウインドウを定めることにより、減少させることができかつトレースアレイインピーダンスをトリミングすることができる。その代わりとして、共通接地面へのキャパシタンスは、フレクシャ 14 の所望の機械的特性が損なわれない限りは外側の誘電層 70 の厚みを減少させることによって減じることができる。

この発明の図 4 の例では、シールド 72A は誘電層 25 で終端をなし、したがって接地面に接し電気的に浮動状態となる。この実施例では、シールド 70A の厚みは当該技術の電気

設計者にとって重要な設計上の検討事項となる。たとえばもし、ある周波数  $f$  での干渉信号または雑音の波頭が接地されていない導体シールド 72 A に衝突すれば、波頭は以下の一次元近似に従い表皮深さ  $\delta$  まで浸透するであろう。

$$\delta = \frac{1}{\sqrt{\pi f \mu \sigma}} \quad (\text{等式1})$$

式中  $\delta$  はメートルで表わされ、 $f$  はヘルツで表わされ、 $\mu$  は導体シールド 72 A を形成する金属の透磁率であり、 $\sigma$  はその導電率である。周波数が同じ場合  $\sigma$  が高いほどシールド層 72 A は薄くなる。たとえば、接地されていない銅の被覆層 72 A が 100 MHz で与えられた場合、銅に対する表皮深さは 6.6 ミクロンとなるであろう。 $(\sigma = 5.8 \times 10^7 \text{ S/m} \text{ および } \mu = \mu_0 = 4 \times 10^{-7} \text{ H/m})$  このように、厚み 6.6 ミクロンの接地されていない被覆層 72 A は、100 MHz の周波数で入来する干渉波頭を止めるのに効果的であろう。被覆層 72 A は接地しなければ、結果として生じる接地面キャパシタンスを導体トレース対の近隣から取除くというさらなる利点を有する。浮動導電遮へい層 72 は、接地接続経路を設けることなく外側の誘電層の上に適切な金属選択堆積またはめっきにより与えることができる。

図 5 の実施例では、シールド（遮へい）74 は、たとえばフレクシャ 14 および / またはロードビーム 12 に電気的に接続される適切な厚みの金属膜のたとえば電着により、誘電層 25 に対して形成される。図 6 の例では、フレクシャ 14 A は部分的にエッティングにより取除かれてキャビティ 28 A を定める。図 7 の例では、フレクシャ 14 B もまた部分的にエッティングによって取除かれ、結果として生じるキャビティは適切な誘電材料 76 によって充填される。

遮へいされたトレースアレイ構造は、フォトリソグラフィおよび選択性エッティングにより、または接着剤などを用いて導電トレースおよびシールドを誘電層に選択的堆積、積層または接着することによって、何らかの適切なパターニング技術を用いて形成される。このトレースアレイ構造は、被覆層 72 または 72 A がロードビーム 14 と組合されかつこれと協働して読取対 R の 2 つの導電トレース 60 および 62、および / または書込対 W の 2 つの導電トレースを遮へいするため、「2 軸で遮へいされる」と言われる。トレース 60 および 62 は読取または書込素子のための好ましい信号経路として示されているが、図 8 の例において示されるように接地リターンシールド 72 B を介してシングルエンドのまたは不平衡信号経路を形成する単一のトレース導体 60 を、本明細書において説明された技術により効果的に遮へいし得ることを当業者であれば認識するであろう。さらに、開示を本明細書に引用により援用する、1996年10月3日に出願され、「ハードディスクドライブにおける R / W ヘッド相互接続のための多トレース伝送線路 (Multi-trace Transmission Lines for R/W Head Interconnect in Hard Disk Drive)」と題された、同一人に譲渡される同時係属中の米国特許出願第 08/726,450 号により教示されるように、複数のトレースを並列の接続配置として設けてインダクタンスが減少した単一の信号経路を提供することができる。当業者ならば図 4 - 8 の断面図を見れば理解するであろうが、これらの断面図は非常に図式的なものであり、一定の率で示すことを意図したものではない。事実、実際のロードビーム 12 および / またはフレクシャ 14 の断面の幅は、この発明の原理を示すために提示したものであり実際の構成部品のための作業場用の図面を意図したものではないこれらの図面によって示されるものよりも、かなり大きくなる可能性がある。

この発明について、現在好ましい実施例すなわちジンバルを実現する堆積された導体フレクシャ構造という点から述べてきたが、当業者であれば、たとえば、近接して取付け、堆積または埋込まれた導体に絶縁の上塗りを施し遮へいを行なったものを備える一体化されたジンバルロードビーム構造またはその他の導電サスペンション部材と関連付けても利用できることが明白であろう。したがって、この開示は制限として解釈されるべきものではないことを理解する必要がある。当業者ならば上記開示を読めば種々の変形例および修正例が必ず明らかになるであろう。したがって、以下のクレームはこの発明の真の精神およ

10

20

30

40

50

び範囲内のすべての変形例および修正例を包含するものとして解釈されることを意図している。

【図 1】

FIG. - 1

【図 2】

FIG. - 2

【図 3】

FIG. - 3

FIG. - 3A

【図 3 B】

FIG. - 3B

---

フロントページの続き

- (72)発明者 アキン・ジュニア, ウイリアム・アール

アメリカ合衆国、95037 カリフォルニア州、モーガン・ヒル、ブルックビュー・コート、1

045

- (72)発明者 バラクリシュナン, アルン

アメリカ合衆国、94555 カリフォルニア州、フレモント、ルーシオン・アベニュー、4683

- (72)発明者 ウイリアムズ, スティーブン・ピイ

アメリカ合衆国、95037 カリフォルニア州、モーガン・ヒル、シカモア・ドライブ、150

35

- (72)発明者 カーペンター, クリストファー・エム

アメリカ合衆国、94086 カリフォルニア州、サンイベイル、エス・フランセス・ストリート

、549

審査官 鈴木 重幸

- (56)参考文献 特開平07-262541 (JP, A)

特開平09-282624 (JP, A)

特表平11-507465 (JP, A)

特開平10-125023 (JP, A)

特開平08-264911 (JP, A)

特開平01-162212 (JP, A)

特開平04-021918 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11B 5/56 - 5/60

G11B 21/16 - 21/26