(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-237805

(P2012-237805A)

(43) 公開日 平成24年12月6日(2012.12.6)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30 | 338 3K107   |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 5C080     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 621M 5C094  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 624B 5C380  |

|                             | G09G 3/20 | 680G        |

審査請求 未請求 請求項の数 17 O L (全 29 頁) 最終頁に続く

|           |                              |          |                                        |

|-----------|------------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2011-105285 (P2011-105285) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成23年5月10日 (2011.5.10)       | (74) 代理人 | 100094363<br>弁理士 山本 孝久                 |

|           |                              | (74) 代理人 | 100118290<br>弁理士 吉井 正明                 |

|           |                              | (74) 代理人 | 100120640<br>弁理士 森 幸一                  |

|           |                              | (72) 発明者 | 多田羅 智史<br>東京都港区港南1丁目7番1号 ソニー株式会社内      |

|           |                              | (72) 発明者 | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】表示装置及び電子機器

## (57) 【要約】

【課題】画素内に作り込む容量素子をメタル層 - メタル層間以外に形成することで、画素の断面構造の自由度を上げることを可能にした表示装置及び当該表示装置を有する電子機器を提供する。

【解決手段】電気光学素子及びトランジスタを含む画素が配置されて成る表示装置において、トランジスタのゲート電極と同じ層のメタル層と、トランジスタのソース領域及びドレイン領域を形成する半導体層との間に、メタル層に電圧を印加することによって、画素内に作り込む容量素子を形成するようにする。

【選択図】図1 0

**【特許請求の範囲】****【請求項 1】**

電気光学素子及びトランジスタを含む画素が配置されて成り、

前記画素は、前記トランジスタのゲート電極と同じ層のメタル層と、前記トランジスタのソース領域及びドレイン領域を形成する半導体層との間に、前記メタル層に電圧が印加されることによって形成される容量素子を有する

表示装置。

**【請求項 2】**

前記メタル層に印加する電圧は、前記半導体層の表面にチャネルを形成できる電圧である

10

請求項 1 に記載の表示装置。

**【請求項 3】**

前記メタル層に印加する電圧は、前記メタル層と前記半導体層との間の誘電体の容量を  $C_0$ 、前記メタル層と前記半導体層との間の容量を  $C$  とするとき、 $C / C_0 = 1$  となる電圧値以上である

請求項 2 に記載の表示装置。

**【請求項 4】**

前記容量素子は、前記電気光学素子の等価容量の補助として用いられる

請求項 1 に記載の表示装置。

20

**【請求項 5】**

前記トランジスタは、前記電気光学素子に対して直列に接続され、当該電気光学素子を駆動する駆動トランジスタであり、

前記容量素子は、その一方の電極が前記駆動トランジスタのソース／ドレイン電極に接続されている

請求項 4 に記載の表示装置。

**【請求項 6】**

前記容量素子は、前記メタル層に印加する電圧として一定の電圧が他方の電極に与えられる

請求項 5 に記載の表示装置。

30

**【請求項 7】**

前記画素は、行列状に配置されて画素アレイ部を構成しており、

前記一定の電圧は、前記容量素子の他方の電極に行単位で繋がる電圧供給ラインを通して前記容量素子の他方の電極に与えられる

請求項 6 に記載の表示装置。

**【請求項 8】**

前記容量素子の他方の電極に行単位で繋がる電圧供給ラインを前記画素アレイ部の外周部で束ねることによって当該画素アレイ部の周りに環状の共通電圧供給ラインが形成されており、

前記一定の電圧は、前記環状の共通電圧供給ライン及び前記電圧供給ラインを通して前記容量素子の他方の電極に与えられる

40

請求項 7 に記載の表示装置。

**【請求項 9】**

前記画素アレイ部が形成されるパネルの両端部側に、前記環状の共通電圧供給ラインに繋がるパッドが形成されており、

前記一定の電圧は、前記パッド、前記環状の共通電圧供給ライン及び前記電圧供給ラインを通して前記容量素子の他方の電極に与えられる

請求項 8 に記載の表示装置。

**【請求項 10】**

前記容量素子は、前記メタル層に印加する電圧としてパルス化された電圧が他方の電極に与えられる

50

請求項 5 に記載の表示装置。

【請求項 1 1】

前記駆動トランジスタに電源を供給する電源供給線の電位は、前記電気光学素子を発光駆動する電流を供給するための第 1 電源電位と、前記電気光学素子に対して逆バイアスを掛けるための第 2 電源電位とで切り替え可能となっており、

前記パルス化された電圧は、前記電源供給線の電位が前記第 1 電源電位のときに高電位になる

請求項 1 0 に記載の表示装置。

【請求項 1 2】

前記パルス化された電圧は、低電位側が前記第 2 電源電位に設定されている

10

請求項 1 1 に記載の表示装置。

【請求項 1 3】

前記画素は、行列状に配置されて画素アレイ部を構成しており、

前記パルス化された電圧は、行単位で前記容量素子の他方の電極に与えられる

請求項 1 0 に記載の表示装置。

【請求項 1 4】

前記パルス化された電圧は、前記画素アレイ部を行単位に走査する走査回路から出力される

請求項 1 3 に記載の表示装置。

【請求項 1 5】

前記パルス化された電圧は、前段の画素行に属する前記電源供給線から与えられる

20

請求項 1 3 に記載の表示装置。

【請求項 1 6】

前記容量素子の他方の電極は、前段の画素行に属する前記電源供給線に接続されている

請求項 1 5 に記載の表示装置。

【請求項 1 7】

電気光学素子及びトランジスタを含む画素が配置されて成り、

前記画素は、前記トランジスタのゲート電極と同じ層のメタル層と、前記トランジスタのソース領域及びドレイン領域を形成する半導体層との間に、前記メタル層に電圧が印加されることによって形成される容量素子を有する

30

表示装置を有する電子機器。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本開示は、表示装置及び電子機器に関し、特に、電気光学素子を含む画素が行列状に配置されてなるフラットパネル型（平面型）の表示装置及び当該表示装置を有する電子機器に関する。

【背景技術】

【0 0 0 2】

フラットパネル型の表示装置として、有機エレクトロルミネッセンス（E L ;Electroluminescence）表示装置、液晶表示装置（L C D ;liquid crystal display）、プラズマ表示装置（P D P ;Plasma Display Panel）等が広く知られている。

40

【0 0 0 3】

この種の表示装置にあっては、電気光学素子及びトランジスタを含む画素（画素回路）が、基板（パネル）上に行列状（マトリクス状）に配置されている。また、表示装置の画素、例えば、有機 E L 表示装置の画素は、電気光学素子及びトランジスタの他に、保持容量や補助容量等の容量素子を画素内に有している（例えば、特許文献 1 参照）。

【先行技術文献】

【特許文献】

【0 0 0 4】

50

する理由についての説明に供する図である。

【図 9】本開示の実施形態に係る画素の断面構造を示す断面図である。

【図 10】実施例 1 に係る画素回路の回路図である。

【図 11】補助容量の他方の電極に対して外部から一定の電圧を与えるためのパネルレイアウト例を示す図である。

【図 12】半導体層の電位に対してメタル層の電位が低くなることで、輝度が低下するメカニズムについての説明に供するタイミング波形図である。

【図 13】半導体容量の容量特性を示す図である。

【図 14】有機 E L 素子の動作点が画素毎にばらつくと輝度ムラになるメカニズムについての説明に供するタイミング波形図である。 10

【図 15】実施例 2 の説明に供するタイミング波形図である。

【図 16】実施例 2 に係る駆動タイミング例を示すタイミング波形図である。

【図 17】実施例 2 に係る駆動タイミング例を実現するためのパネル構成例を示すシステム構成図である。 20

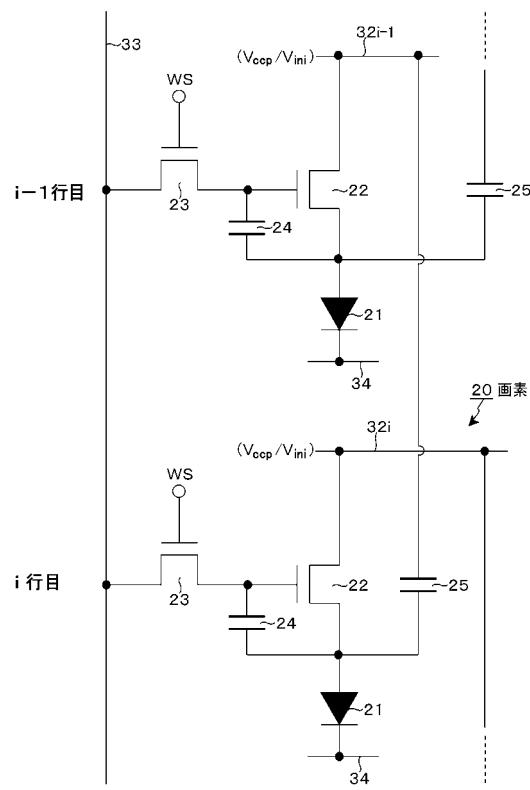

【図 18】実施例 2 の変形例に係る画素回路の回路図である。

【図 19】本開示が適用されるテレビジョンセットの外観を示す斜視図である。

【図 20】本開示が適用されるデジタルカメラの外観を示す斜視図であり、(A) は表側から見た斜視図、(B) は裏側から見た斜視図である。

【図 21】本開示が適用されるノート型パソコンコンピュータの外観を示す斜視図である。 20

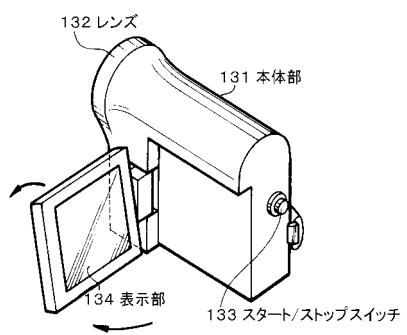

【図 22】本開示が適用されるビデオカメラの外観を示す斜視図である。

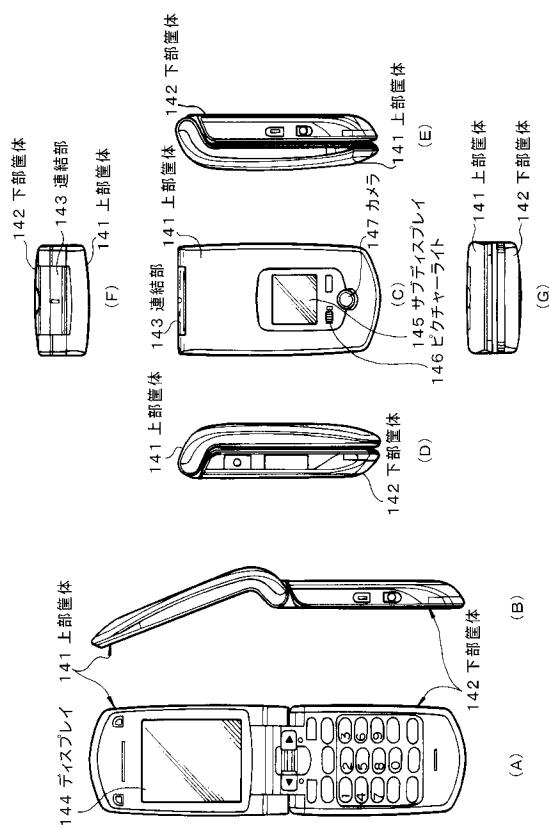

【図 23】本開示が適用される携帯電話機を示す外観図であり、(A) は開いた状態での正面図、(B) はその側面図、(C) は閉じた状態での正面図、(D) は左側面図、(E) は右側面図、(F) は上面図、(G) は下面図である。

#### 【発明を実施するための形態】

##### 【0011】

以下、本開示の技術を実施するための形態（以下、「実施形態」と記述する）について図面を用いて詳細に説明する。なお、説明は以下の順序で行う。

##### 1. 本開示が適用される有機 E L 表示装置

###### 1 - 1 . システム構成

###### 1 - 2 . 基本的な回路動作

###### 1 - 3 . ボトムゲート構造とトップゲート構造

##### 2. 実施形態の説明

###### 2 - 1 . 実施例 1

###### 2 - 2 . 実施例 2

##### 3. 適用例

##### 4. 電子機器

##### 【0012】

##### < 1. 本開示が適用される有機 E L 表示装置 >

##### 【1 - 1 . システム構成】

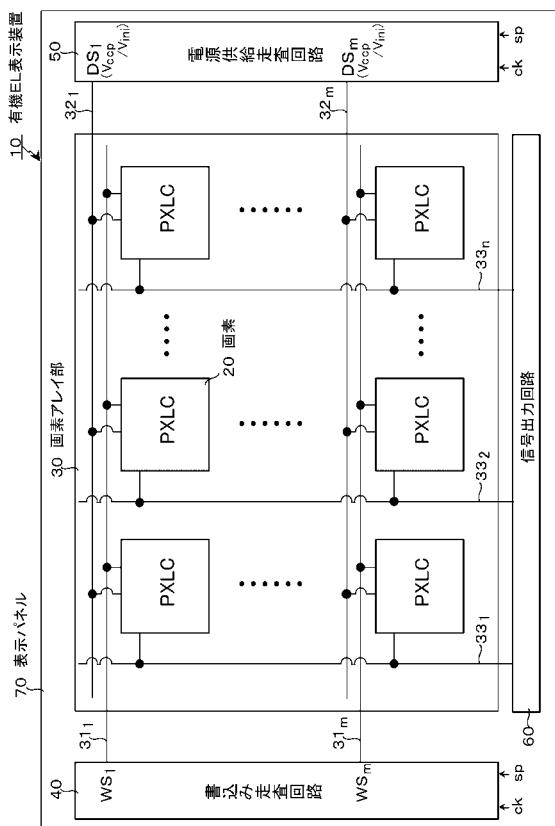

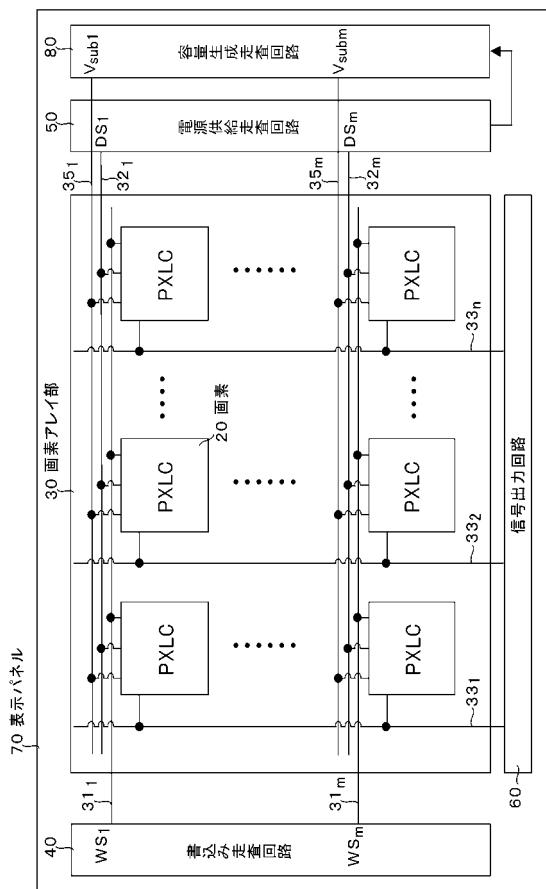

図 1 は、本開示が適用されるアクティブマトリクス型表示装置の基本的な構成の概略を示すシステム構成図である。 40

##### 【0013】

アクティブマトリクス型表示装置は、電気光学素子に流れる電流を、当該電気光学素子と同じ画素内に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタによって制御する表示装置である。絶縁ゲート型電界効果トランジスタとしては、典型的には、TFT (Thin Film Transistor ; 薄膜トランジスタ) が用いられる。

##### 【0014】

ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子、例えば有機 E L 素子を、画素（画素回路）の発光素子として用いるア

クティブマトリクス型有機EL表示装置の場合を例に挙げて説明するものとする。

【0015】

図1に示すように、本適用例に係る有機EL表示装置10は、有機EL素子を含む複数の画素20と、当該画素20が行列状に2次元配置されてなる画素アレイ部30と、当該画素アレイ部30の周辺に配置される駆動回路部とを有する構成となっている。駆動回路部は、書き込み走査回路40、電源供給走査回路50及び信号出力回路60等からなり、画素アレイ部30の各画素20を駆動する。

【0016】

ここで、有機EL表示装置10がカラー表示対応の場合は、カラー画像を形成する単位となる1つの画素（単位画素）は複数の副画素（サブピクセル）から構成され、この副画素の各々が図1の画素20に相当することになる。より具体的には、カラー表示対応の表示装置では、1つの画素は、例えば、赤色（Red；R）光を発光する副画素、緑色（Green；G）光を発光する副画素、青色（Blue；B）光を発光する副画素の3つの副画素から構成される。

10

【0017】

但し、1つの画素としては、RGBの3原色の副画素の組み合わせに限られるものではなく、3原色の副画素に更に1色あるいは複数色の副画素を加えて1つの画素を構成することも可能である。より具体的には、例えば、輝度向上のために白色（White；W）光を発光する副画素を加えて1つの画素を構成したり、色再現範囲を拡大するために補色光を発光する少なくとも1つの副画素を加えて1つの画素を構成したりすることも可能である。

20

【0018】

画素アレイ部30には、m行n列の画素20の配列に対して、行方向（画素行の画素の配列方向）に沿って走査線 $3_{1,1} \sim 3_{1,m}$ と電源供給線 $3_{2,1} \sim 3_{2,m}$ とが画素行毎に配線されている。更に、m行n列の画素20の配列に対して、列方向（画素列の画素の配列方向）に沿って信号線 $3_{3,1} \sim 3_{3,n}$ が画素列毎に配線されている。

20

【0019】

走査線 $3_{1,1} \sim 3_{1,m}$ は、書き込み走査回路40の対応する行の出力端にそれぞれ接続されている。電源供給線 $3_{2,1} \sim 3_{2,m}$ は、電源供給走査回路50の対応する行の出力端にそれぞれ接続されている。信号線 $3_{3,1} \sim 3_{3,n}$ は、信号出力回路60の対応する列の出力端にそれぞれ接続されている。

30

【0020】

画素アレイ部30は、通常、ガラス基板などの透明絶縁基板上に形成されている。これにより、有機EL表示装置10は、平面型（フラット型）のパネル構造となっている。画素アレイ部30の各画素20の駆動回路は、アモルファスシリコン TFT または低温ポリシリコン TFT を用いて形成することができる。低温ポリシリコン TFT を用いる場合には、図1に示すように、書き込み走査回路40、電源供給走査回路50、及び、信号出力回路60についても、画素アレイ部30を形成する表示パネル（基板）70上に実装することができる。

40

【0021】

書き込み走査回路40は、クロックパルスckに同期してスタートパルスspを順にシフト（転送）するシフトレジスタ回路等によって構成されている。この書き込み走査回路40は、画素アレイ部30の各画素20への映像信号の信号電圧書き込みに際して、走査線 $3_1$ （ $3_{1,1} \sim 3_{1,m}$ ）に対して書き込み走査信号WS（ $WS_1 \sim WS_m$ ）を順次供給することによって画素アレイ部30の各画素20を行単位で順番に走査（線順次走査）する。

【0022】

電源供給走査回路50は、クロックパルスckに同期してスタートパルスspを順にシフトするシフトレジスタ回路等によって構成されている。この電源供給走査回路50は、書き込み走査回路40による線順次走査に同期して、第1電源電位 $V_{ccp}$ と当該第1電源電位 $V_{ccp}$ よりも低い第2電源電位 $V_{ini}$ とで切り替わることが可能な電源電位DS（ $DS_1$

50

$\sim D S_m$ ) を電源供給線 3 2 ( 3 2<sub>1</sub> ~ 3 2<sub>m</sub> ) に供給する。後述するように、電源電位 D S の  $V_{ccp}$  /  $V_{ini}$  の切替えにより、画素 2 0 の発光 / 非発光の制御が行なわれる。

【 0 0 2 3 】

信号出力回路 6 0 は、信号供給源(図示せず)から供給される輝度情報に応じた映像信号の信号電圧(以下、単に「信号電圧」と記述する場合もある)  $V_{sig}$  と基準電圧  $V_{ofs}$  を選択的に出力する。ここで、基準電圧  $V_{ofs}$  は、映像信号の信号電圧  $V_{sig}$  の基準となる電位(例えば、映像信号の黒レベルに相当する電位)であり、後述する閾値補正処理の際に用いられる。

【 0 0 2 4 】

信号出力回路 6 0 から出力される信号電圧  $V_{sig}$  / 基準電圧  $V_{ofs}$  は、信号線 3 3 ( 3 3<sub>1</sub> ~ 3 3<sub>n</sub> ) を介して画素アレイ部 3 0 の各画素 2 0 に対して、書き込み走査回路 4 0 による走査によって選択された画素行の単位で書き込まれる。すなわち、信号出力回路 6 0 は、信号電圧  $V_{sig}$  を行(ライン)単位で書き込む線順次書き込みの駆動形態を探っている。

【 0 0 2 5 】

(画素回路)

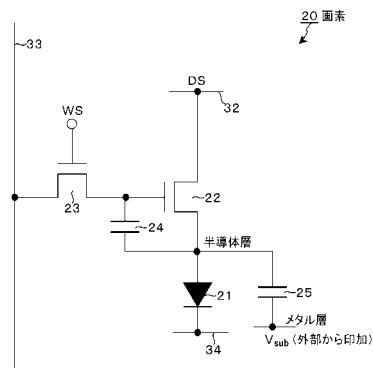

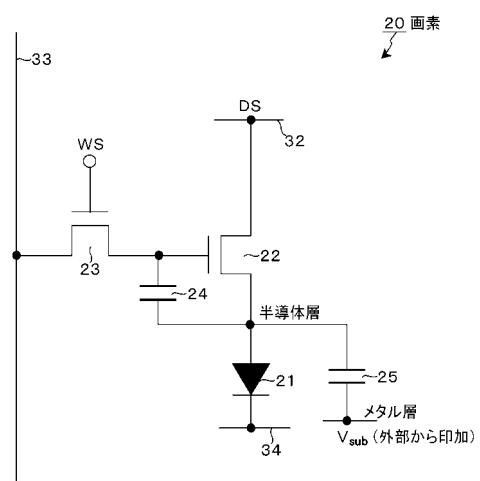

図 2 は、画素(画素回路) 2 0 の具体的な回路構成の一例を示す回路図である。画素 2 0 の発光部は、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である有機 EL 素子 2 1 から成る。

【 0 0 2 6 】

図 2 に示すように、画素 2 0 は、有機 EL 素子 2 1 と、有機 EL 素子 2 1 に電流を流すことによって当該有機 EL 素子 2 1 を駆動する駆動回路とによって構成されている。有機 EL 素子 2 1 は、全ての画素 2 0 に対して共通に配線(所謂、ベタ配線)された共通電源供給線 3 4 にカソード電極が接続されている。

【 0 0 2 7 】

有機 EL 素子 2 1 を駆動する駆動回路は、駆動トランジスタ 2 2 、書き込みトランジスタ 2 3 、保持容量 2 4 、及び、補助容量 2 5 を有する構成となっている。駆動トランジスタ 2 2 及び書き込みトランジスタ 2 3 として N チャネル型の TFT を用いることができる。但し、ここで示した、駆動トランジスタ 2 2 及び書き込みトランジスタ 2 3 の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。更に、以下に記述するトランジスタや保持容量、有機 EL 素子等の結線関係についても、この形態に限られるものではない。

【 0 0 2 8 】

駆動トランジスタ 2 2 は、一方の電極(ソース / ドレイン電極)が有機 EL 素子 2 1 のアノード電極に接続され、他方の電極(ソース / ドレイン電極)が電源供給線 3 2 ( 3 2<sub>1</sub> ~ 3 2<sub>m</sub> ) に接続されている。

【 0 0 2 9 】

書き込みトランジスタ 2 3 は、一方の電極(ソース / ドレイン電極)が信号線 3 3 ( 3 3<sub>1</sub> ~ 3 3<sub>n</sub> ) に接続され、他方の電極(ソース / ドレイン電極)が駆動トランジスタ 2 2 のゲート電極に接続されている。また、書き込みトランジスタ 2 3 のゲート電極は、走査線 3 1 ( 3 1<sub>1</sub> ~ 3 1<sub>m</sub> ) に接続されている。

【 0 0 3 0 】

駆動トランジスタ 2 2 及び書き込みトランジスタ 2 3 において、一方の電極とは、ソース / ドレイン領域に電気的に接続された金属配線を言い、他方の電極とは、ドレイン / ソース領域に電気的に接続された金属配線を言う。また、一方の電極と他方の電極との電位関係によって一方の電極がソース電極ともなればドレイン電極ともなり、他方の電極がドレイン電極ともなればソース電極ともなる。

【 0 0 3 1 】

保持容量 2 4 は、一方の電極が駆動トランジスタ 2 2 のゲート電極に接続され、他方の電極が駆動トランジスタ 2 2 の他方の電極、及び、有機 EL 素子 2 1 のアノード電極に接続されている。

10

20

30

40

50

## 【0032】

補助容量25は、一方の電極が有機EL素子21のアノード電極に、他方の電極が共通電源供給線34にそれぞれ接続されている。この補助容量25は、有機EL素子21の等価容量の容量不足分を補うべく当該等価容量の補助となって、保持容量24に対する映像信号の書き込みゲインを高めるために設けられるものである。

## 【0033】

ここでは、補助容量25の他方の電極を共通電源供給線34に接続するとしているが、他方の電極の接続先としては、共通電源供給線34に限られるものではなく、固定電位のノードであればよい。補助容量25の他方の電極を固定電位のノードに接続することで、有機EL素子21の容量不足分を補い、保持容量24に対する映像信号の書き込みゲインを高めるという所期の目的を達成することができる。10

## 【0034】

上記構成の画素20において、書き込みトランジスタ23は、書き込み走査回路40から走査線31を通してゲート電極に印加されるHighアクティブの書き込み走査信号WSに応答して導通状態となる。これにより、書き込みトランジスタ23は、信号線33を通して信号出力回路60から供給される、輝度情報に応じた映像信号の信号電圧 $V_{sig}$ または基準電圧 $V_{ofs}$ をサンプリングして画素20内に書き込む。この書き込まれた信号電圧 $V_{sig}$ または基準電圧 $V_{ofs}$ は、駆動トランジスタ22のゲート電極に印加されるとともに保持容量24に保持される。

## 【0035】

駆動トランジスタ22は、電源供給線32( $32_1 \sim 32_m$ )の電源電位DSが第1電源電位 $V_{ccp}$ にあるときには、一方の電極がドレイン電極、他方の電極がソース電極となって飽和領域で動作する。これにより、駆動トランジスタ22は、電源供給線32から電流の供給を受けて有機EL素子21を電流駆動にて発光駆動する。より具体的には、駆動トランジスタ22は、飽和領域で動作することにより、保持容量24に保持された信号電圧 $V_{sig}$ の電圧値に応じた電流値の駆動電流を有機EL素子21に供給し、当該有機EL素子21を電流駆動することによって発光させる。20

## 【0036】

駆動トランジスタ22は更に、電源電位DSが第1電源電位 $V_{ccp}$ から第2電源電位 $V_{ini}$ に切り替わったときには、一方の電極がソース電極、他方の電極がドレイン電極となってスイッチングトランジスタとして動作する。これにより、駆動トランジスタ22は、有機EL素子21への駆動電流の供給を停止し、有機EL素子21を非発光状態にする。すなわち、駆動トランジスタ22は、有機EL素子21の発光/非発光を制御するトランジスタとしての機能をも併せ持っている。30

## 【0037】

この駆動トランジスタ22のスイッチング動作により、有機EL素子21が非発光状態となる期間(非発光期間)を設け、有機EL素子21の発光期間と非発光期間の割合(デューティ)を制御することができる。このデューティ制御により、1表示フレーム期間に亘って画素が発光することに伴う残像ボケを低減するために、特に動画の画品位をより優れたものとすることができる。40

## 【0038】

電源供給走査回路50から電源供給線32を通して選択的に供給される第1, 第2電源電位 $V_{ccp}$ ,  $V_{ini}$ のうち、第1電源電位 $V_{ccp}$ は有機EL素子21を発光駆動する駆動電流を駆動トランジスタ22に供給するための電源電位である。また、第2電源電位 $V_{ini}$ は、有機EL素子21に対して逆バイアスを掛けるための電源電位である。この第2電源電位 $V_{ini}$ は、基準電圧 $V_{ofs}$ よりも低い電位、例えば、駆動トランジスタ22の閾値電圧を $V_{th}$ とするとき $V_{ofs} - V_{th}$ よりも低い電位、好ましくは、 $V_{ofs} - V_{th}$ よりも十分に低い電位に設定される。

## 【0039】

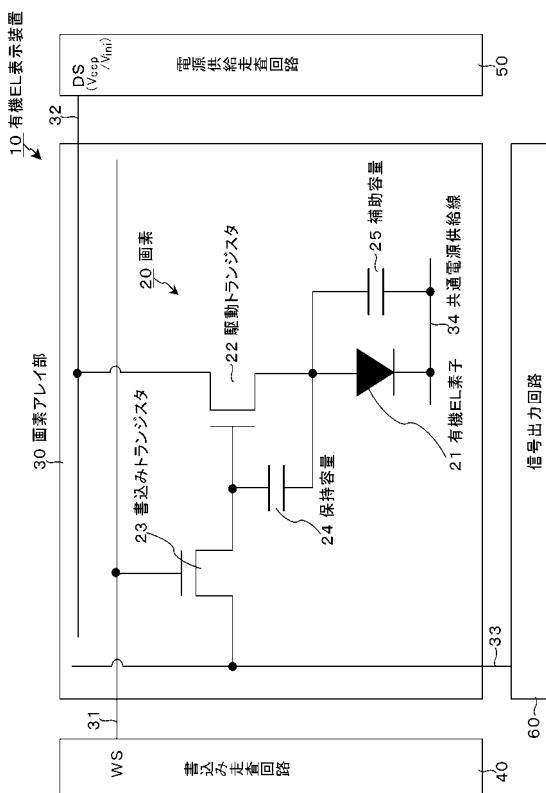

[1-2. 基本的な回路動作]

10

20

30

40

50

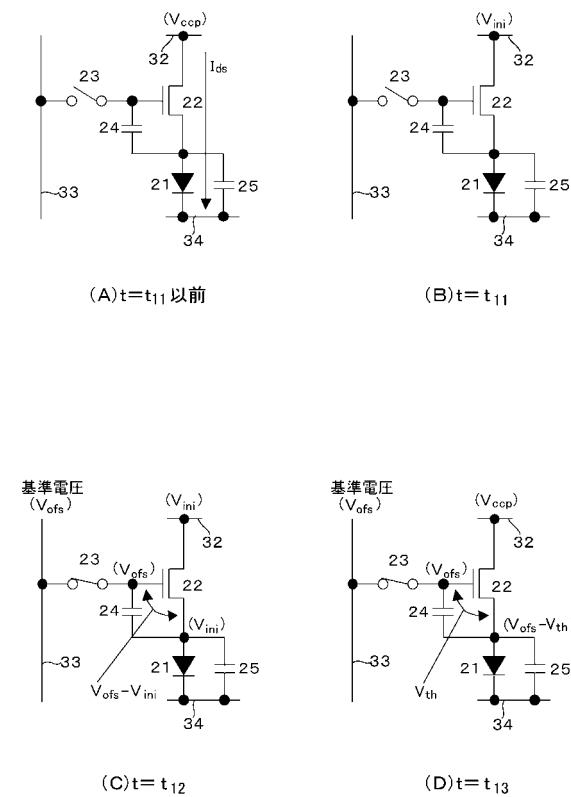

続いて、上記構成の有機EL表示装置10の基本的な回路動作について、図3のタイミング波形図を基に図4及び図5の動作説明図を用いて説明する。尚、図4及び図5の動作説明図では、図面の簡略化のために、書き込みトランジスタ23をスイッチのシンボルで図示している。

#### 【0040】

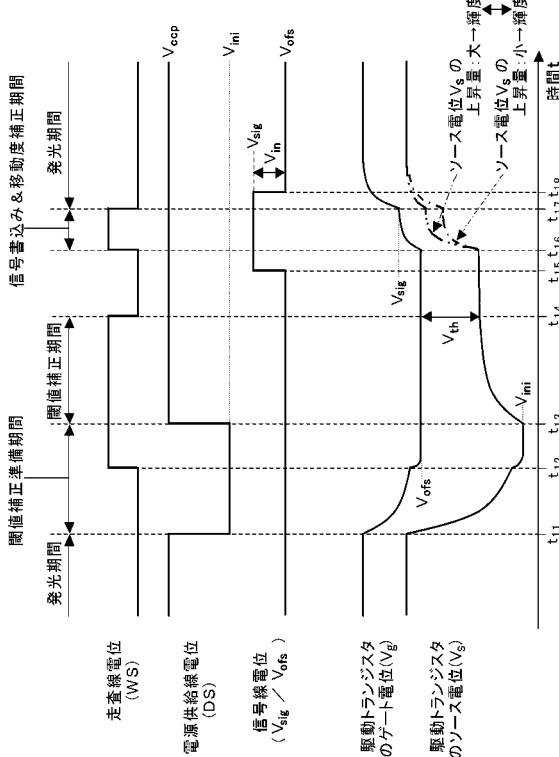

図3のタイミング波形図には、走査線31の電位(書き込み走査信号)WS、電源供給線32の電位(電源電位)DS、信号線33の電位( $V_{sig}$  /  $V_{ofs}$ )、駆動トランジスタ22のゲート電位 $V_g$ 及びソース電位 $V_s$ のそれぞれの変化を示している。

#### 【0041】

(前表示フレームの発光期間)

図3のタイミング波形図において、時刻 $t_{11}$ 以前は、前の表示フレームにおける有機EL素子21の発光期間となる。この前表示フレームの発光期間では、電源供給線32の電位DSが第1電源電位(以下、「高電位」と記述する) $V_{ccp}$ にあり、また、書き込みトランジスタ23が非導通状態にある。

#### 【0042】

このとき、駆動トランジスタ22は飽和領域で動作するように設計されている。これにより、図4(A)に示すように、駆動トランジスタ22のゲート-ソース間電圧 $V_{gs}$ に応じた駆動電流(ドレン-ソース間電流) $I_{ds}$ が、電源供給線32から駆動トランジスタ22を通して有機EL素子21に供給される。従って、有機EL素子21が駆動電流 $I_{ds}$ の電流値に応じた輝度で発光する。

#### 【0043】

(閾値補正準備期間)

時刻 $t_{11}$ になると、線順次走査の新しい表示フレーム(現表示フレーム)に入る。そして、図4(B)に示すように、電源供給線32の電位DSが高電位 $V_{ccp}$ から、信号線33の基準電圧 $V_{ofs}$ に対して $V_{ofs} - V_{th}$ よりも十分に低い第2電源電位(以下、「低電位」と記述する) $V_{ini}$ に切り替わる。

#### 【0044】

ここで、有機EL素子21の閾値電圧を $V_{thel}$ 、共通電源供給線34の電位(カソード電位)を $V_{cath}$ とする。このとき、低電位 $V_{ini}$ を $V_{ini} < V_{thel} + V_{cath}$ とすると、駆動トランジスタ22のソース電位 $V_s$ が低電位 $V_{ini}$ にほぼ等しくなるために、有機EL素子21は逆バイアス状態となって消光する。

#### 【0045】

次に、時刻 $t_{12}$ で走査線31の電位WSが低電位側から高電位側に遷移することで、図4(C)に示すように、書き込みトランジスタ23が導通状態となる。このとき信号出力回路60から信号線33に対して基準電圧 $V_{ofs}$ が供給された状態にあるために、駆動トランジスタ22のゲート電位 $V_g$ が基準電圧 $V_{ofs}$ になる。また、駆動トランジスタ22のソース電位 $V_s$ は、基準電圧 $V_{ofs}$ よりも十分に低い電位、即ち、低電位 $V_{ini}$ にある。

#### 【0046】

このとき、駆動トランジスタ22のゲート-ソース間電圧 $V_{gs}$ は $V_{ofs} - V_{ini}$ となる。ここで、 $V_{ofs} - V_{ini}$ が駆動トランジスタ22の閾値電圧 $V_{th}$ よりも大きくないと、後述する閾値補正処理を行うことができないために、 $V_{ofs} - V_{ini} > V_{th}$ なる電位関係に設定する必要がある。

#### 【0047】

このように、駆動トランジスタ22のゲート電位 $V_g$ を基準電圧 $V_{ofs}$ に固定し、かつ、ソース電位 $V_s$ を低電位 $V_{ini}$ に固定して(確定させて)初期化する処理が、後述する閾値補正処理(閾値補正動作)を行う前の準備(閾値補正準備)の処理である。従って、基準電圧 $V_{ofs}$ 及び低電位 $V_{ini}$ が、駆動トランジスタ22のゲート電位 $V_g$ 及びソース電位 $V_s$ の各初期化電位となる。

#### 【0048】

(閾値補正期間)

10

20

30

40

50

次に、時刻  $t_{13}$  で、図 4 (D) に示すように、電源供給線 3 2 の電位  $V_{DS}$  が低電位  $V_{in}$  から高電位  $V_{ccp}$  に切り替わると、駆動トランジスタ 2 2 のゲート電位  $V_g$  が基準電圧  $V_{fs}$  に保たれた状態で閾値補正処理が開始される。すなわち、ゲート電位  $V_g$  から駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  を減じた電位に向けて駆動トランジスタ 2 2 のソース電位  $V_s$  が上昇を開始する。

#### 【0049】

ここでは、便宜上、駆動トランジスタ 2 2 のゲート電位  $V_g$  の初期化電位  $V_{ofs}$  を基準とし、当該初期化電位  $V_{ofs}$  から駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  を減じた電位に向けてソース電位  $V_s$  を変化させる処理を閾値補正処理と呼んでいる。この閾値補正処理が進むと、やがて、駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  が駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  に収束する。この閾値電圧  $V_{th}$  に相当する電圧は保持容量 2 4 に保持される。

10

#### 【0050】

尚、閾値補正処理を行う期間（閾値補正期間）において、電流が専ら保持容量 2 4 側に流れ、有機 EL 素子 2 1 側には流れないようにするために、有機 EL 素子 2 1 がカットオフ状態となるように共通電源供給線 3 4 の電位  $V_{cath}$  を設定しておくこととする。

#### 【0051】

次に、時刻  $t_{14}$  で、走査線 3 1 の電位  $WS$  が低電位側に遷移することで、図 5 (A) に示すように、書き込みトランジスタ 2 3 が非導通状態となる。このとき、駆動トランジスタ 2 2 のゲート電極が信号線 3 3 から電気的に切り離されることによってフローティング状態になる。しかし、ゲート - ソース間電圧  $V_{gs}$  が駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  に等しいために、当該駆動トランジスタ 2 2 はカットオフ状態にある。従って、駆動トランジスタ 2 2 にドレイン - ソース間電流  $I_{ds}$  は流れない。

20

#### 【0052】

##### (信号書き込み & 移動度補正期間)

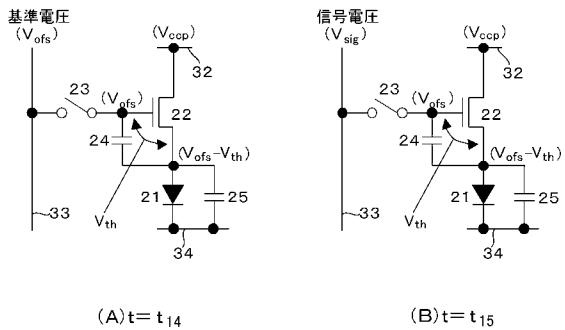

次に、時刻  $t_{15}$  で、図 5 (B) に示すように、信号線 3 3 の電位が基準電圧  $V_{ofs}$  から映像信号の信号電圧  $V_{sig}$  に切り替わる。続いて、時刻  $t_{16}$  で、走査線 3 1 の電位  $WS$  が高電位側に遷移することで、図 5 (C) に示すように、書き込みトランジスタ 2 3 が導通状態になって映像信号の信号電圧  $V_{sig}$  をサンプリングして画素 2 0 内に書き込む。

30

#### 【0053】

この書き込みトランジスタ 2 3 による信号電圧  $V_{sig}$  の書き込みにより、駆動トランジスタ 2 2 のゲート電位  $V_g$  が信号電圧  $V_{sig}$  になる。そして、映像信号の信号電圧  $V_{sig}$  による駆動トランジスタ 2 2 の駆動の際に、当該駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  が保持容量 2 4 に保持された閾値電圧  $V_{th}$  に相当する電圧と相殺される。この閾値キャセルの原理の詳細については後述する。

#### 【0054】

このとき、有機 EL 素子 2 1 は、カットオフ状態（ハイインピーダンス状態）にある。従って、映像信号の信号電圧  $V_{sig}$  に応じて電源供給線 3 2 から駆動トランジスタ 2 2 に流れる電流（ドレイン - ソース間電流  $I_{ds}$ ）は、有機 EL 素子 2 1 の等価容量及び補助容量 2 5 に流れ込む。これにより、有機 EL 素子 2 1 の等価容量及び補助容量 2 5 の充電が開始される。

40

#### 【0055】

有機 EL 素子 2 1 の等価容量及び補助容量 2 5 が充電されることにより、駆動トランジスタ 2 2 のソース電位  $V_s$  が時間の経過とともに上昇していく。このとき既に、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  の画素毎のばらつきがキャセルされており、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  は当該駆動トランジスタ 2 2 の移動度  $\mu$  に依存したものとなる。尚、駆動トランジスタ 2 2 の移動度  $\mu$  は、当該駆動トランジスタ 2 2 のチャネルを構成する半導体薄膜の移動度である。

#### 【0056】

ここで、映像信号の信号電圧  $V_{sig}$  に対する保持容量 2 4 の保持電圧  $V_{gs}$  の比率、即ち

50

、書込みゲイン  $G$  が 1 (理想値) であると仮定する。すると、駆動トランジスタ 2 2 のソース電位  $V_s$  が  $V_{ofs} - V_{th} + V$  の電位まで上昇することで、駆動トランジスタ 2 2 のゲート ソース間電圧  $V_{gs}$  は  $V_{sig} - V_{ofs} + V_{th} - V$  となる。

#### 【0057】

すなわち、駆動トランジスタ 2 2 のソース電位  $V_s$  の上昇分  $V$  は、保持容量 2 4 に保持された電圧 ( $V_{sig} - V_{ofs} + V_{th}$ ) から差し引かれるように、換言すれば、保持容量 2 4 の充電電荷を放電するように作用する。換言すれば、ソース電位  $V_s$  の上昇分  $V$  は、保持容量 2 4 に対して負帰還がかけられたことになる。従って、ソース電位  $V_s$  の上昇分  $V$  は負帰還の帰還量となる。

#### 【0058】

このように、駆動トランジスタ 2 2 に流れるドレイン - ソース間電流  $I_{ds}$  に応じた帰還量  $V$  でゲート ソース間電圧  $V_{gs}$  に負帰還をかけることで、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  の移動度  $\mu$  に対する依存性を打ち消すことができる。この打ち消す処理が、駆動トランジスタ 2 2 の移動度  $\mu$  の画素毎のばらつきを補正する移動度補正処理である。

#### 【0059】

より具体的には、駆動トランジスタ 2 2 のゲート電極に書き込まれる映像信号の信号振幅  $V_{in}$  (=  $V_{sig} - V_{ofs}$ ) が高い程ドレイン - ソース間電流  $I_{ds}$  が大きくなるため、負帰還の帰還量  $V$  の絶対値も大きくなる。従って、発光輝度レベルに応じた移動度補正処理が行われる。

#### 【0060】

また、映像信号の信号振幅  $V_{in}$  を一定とした場合、駆動トランジスタ 2 2 の移動度  $\mu$  が大きいほど負帰還の帰還量  $V$  の絶対値も大きくなるため、画素毎の移動度  $\mu$  のばらつきを取り除くことができる。従って、負帰還の帰還量  $V$  は、移動度補正処理の補正量とも言える。移動度補正の原理の詳細については後述する。

#### 【0061】

##### (発光期間)

次に、時刻  $t_{17}$  で、走査線 3 1 の電位  $WS$  が低電位側に遷移することで、図 5 (D) に示すように、書込みトランジスタ 2 3 が非導通状態となる。これにより、駆動トランジスタ 2 2 のゲート電極は、信号線 3 3 から電気的に切り離されるためにフローティング状態になる。

#### 【0062】

ここで、駆動トランジスタ 2 2 のゲート電極がフローティング状態にあるときは、駆動トランジスタ 2 2 のゲート - ソース間に保持容量 2 4 が接続されていることにより、駆動トランジスタ 2 2 のソース電位  $V_s$  の変動に連動してゲート電位  $V_g$  も変動する。

#### 【0063】

このように、駆動トランジスタ 2 2 のゲート電位  $V_g$  がソース電位  $V_s$  の変動に連動して変動する動作が、換言すれば、保持容量 2 4 に保持されたゲート - ソース間電圧  $V_{gs}$  を保ったまま、ゲート電位  $V_g$  及びソース電位  $V_s$  が上昇する動作がブーストアップ動作である。

#### 【0064】

駆動トランジスタ 2 2 のゲート電極がフローティング状態になり、それと同時に、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  が有機 EL 素子 2 1 に流れ始めることにより、当該電流  $I_{ds}$  に応じて有機 EL 素子 2 1 のアノード電位が上昇する。

#### 【0065】

そして、有機 EL 素子 2 1 のアノード電位が  $V_{the} + V_{cath}$  を越えると、有機 EL 素子 2 1 に駆動電流が流れ始めるため有機 EL 素子 2 1 が発光を開始する。また、有機 EL 素子 2 1 のアノード電位の上昇は、即ち、駆動トランジスタ 2 2 のソース電位  $V_s$  の上昇に他ならない。そして、駆動トランジスタ 2 2 のソース電位  $V_s$  が上昇すると、保持容量 2 4 のブーストアップ動作により、駆動トランジスタ 2 2 のゲート電位  $V_g$  も連動して上

10

20

30

40

50

昇する。

#### 【0066】

このとき、ブートストラップゲインが1（理想値）であると仮定した場合、ゲート電位 $V_g$ の上昇量はソース電位 $V_s$ の上昇量に等しくなる。故に、発光期間中、駆動トランジスタ22のゲート-ソース間電圧 $V_{gs}$ は、 $V_{sig} - V_{ofs} + V_{th} - V$ で一定に保持される。そして、時刻 $t_{18}$ で信号線33の電位が映像信号の信号電圧 $V_{sig}$ から基準電圧 $V_{ofs}$ に切り替わる。

#### 【0067】

以上説明した一連の回路動作において、閾値補正準備、閾値補正、信号電圧 $V_{sig}$ の書き込み（信号書込み）、及び、移動度補正の各処理動作は、1水平走査期間（1H）において実行される。また、信号書き込み及び移動度補正の各処理動作は、時刻 $t_{16} - t_{17}$ の期間において並行して実行される。10

#### 【0068】

##### 〔分割閾値補正〕

尚、ここでは、閾値補正処理を1回だけ実行する駆動法を採る場合を例に挙げて説明したが、この駆動法は一例に過ぎず、この駆動法に限られるものではない。例えば、閾値補正処理を移動度補正及び信号書き込み処理と共に1H期間に加えて、当該1H期間に先行する複数の水平走査期間に亘って分割して閾値補正処理を複数回実行する、所謂、分割閾値補正を行う駆動法を採ることも可能である。

#### 【0069】

この分割閾値補正の駆動法によれば、高精細化に伴う多画素化によって1水平走査期間として割り当てられる時間が短くなったとしても、閾値補正期間として複数の水平走査期間に亘って十分な時間を確保することができる。従って、1水平走査期間として割り当てられる時間が短くなても、閾値補正期間として十分な時間を確保できるため、閾値補正処理を確実に実行できることになる。20

#### 【0070】

##### 〔閾値キャンセルの原理〕

ここで、駆動トランジスタ22の閾値キャンセル（即ち、閾値補正）の原理について説明する。駆動トランジスタ22は、飽和領域で動作するように設計されているために定電流源として動作する。これにより、有機EL素子21には駆動トランジスタ22から、次式（1）で与えられる一定のドレイン-ソース間電流（駆動電流） $I_{ds}$ が供給される。30

$$I_{ds} = (1/2) \cdot \mu (W/L) C_{ox} (V_{gs} - V_{th})^2 \quad \dots \dots (1)$$

ここで、Wは駆動トランジスタ22のチャネル幅、Lはチャネル長、 $C_{ox}$ は単位面積当たりのゲート容量である。

#### 【0071】

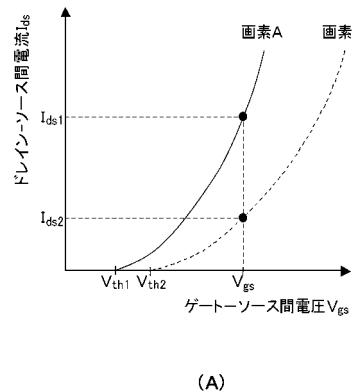

図6（A）に、駆動トランジスタ22のドレイン-ソース間電流 $I_{ds}$ 対ゲート-ソース間電圧 $V_{gs}$ の特性を示す。図6（A）の特性図に示すように、駆動トランジスタ22の閾値電圧 $V_{th}$ の画素毎のばらつきに対するキャンセル処理（補正処理）を行わないと、閾値電圧 $V_{th}$ が $V_{th1}$ のときに、ゲート-ソース間電圧 $V_{gs}$ に対応するドレイン-ソース間電流 $I_{ds}$ が $I_{ds1}$ になる。40

#### 【0072】

これに対して、閾値電圧 $V_{th}$ が $V_{th2}$ （ $V_{th2} > V_{th1}$ ）のとき、同じゲート-ソース間電圧 $V_{gs}$ に対応するドレイン-ソース間電流 $I_{ds}$ が $I_{ds2}$ （ $I_{ds2} < I_{ds1}$ ）になる。すなわち、駆動トランジスタ22の閾値電圧 $V_{th}$ が変動すると、ゲート-ソース間電圧 $V_{gs}$ が一定であってもドレイン-ソース間電流 $I_{ds}$ が変動する。

#### 【0073】

一方、上記構成の画素（画素回路）20では、先述したように、発光時の駆動トランジスタ22のゲート-ソース間電圧 $V_{gs}$ は $V_{sig} - V_{ofs} + V_{th} - V$ である。従って、これを式（1）に代入すると、ドレイン-ソース間電流 $I_{ds}$ は、次式（2）で表される。

$$I_{ds} = (1/2) \cdot \mu (W/L) C_{ox} (V_{sig} - V_{ofs} - V)^2 \quad \dots \dots (2)$$

10

20

30

40

50

## 【0074】

すなわち、駆動トランジスタ22の閾値電圧 $V_{th}$ の項がキャンセルされており、駆動トランジスタ22から有機EL素子21に供給されるドレイン-ソース間電流 $I_{ds}$ は、駆動トランジスタ22の閾値電圧 $V_{th}$ に依存しない。その結果、駆動トランジスタ22の製造プロセスのばらつきや経時変化等により、駆動トランジスタ22の閾値電圧 $V_{th}$ が画素毎に変動したとしても、ドレイン-ソース間電流 $I_{ds}$ が変動しないために、有機EL素子21の発光輝度を一定に保つことができる。

## 【0075】

## 〔移動度補正の原理〕

次に、駆動トランジスタ22の移動度補正の原理について説明する。図6(B)に、駆動トランジスタ22の移動度 $\mu$ が相対的に大きい画素Aと、駆動トランジスタ22の移動度 $\mu$ が相対的に小さい画素Bとを比較した状態で特性カーブを示す。駆動トランジスタ22をポリシリコン薄膜トランジスタなどで構成した場合、画素Aや画素Bのように、画素間で移動度 $\mu$ がばらつくことは避けられない。10

## 【0076】

画素Aと画素Bで移動度 $\mu$ にはばらつきがある状態で、駆動トランジスタ22のゲート電極に対して、例えば両画素A, Bに同レベルの信号振幅 $V_{in}$ (=  $V_{sig} - V_{offs}$ )を書き込んだ場合を考える。この場合、何ら移動度 $\mu$ の補正を行わないと、移動度 $\mu$ の大きい画素Aに流れるドレイン-ソース間電流 $I_{ds1}$ と移動度 $\mu$ の小さい画素Bに流れるドレイン-ソース間電流 $I_{ds2}$ との間には大きな差が生じてしまう。このように、移動度 $\mu$ の画素毎のばらつきに起因してドレイン-ソース間電流 $I_{ds}$ に画素間で大きな差が生じると、画面のユニフォーミティ(一様性)が損なわれる。20

## 【0077】

ここで、先述した式(1)のトランジスタ特性式から明らかなように、移動度 $\mu$ が大きいほどドレイン-ソース間電流 $I_{ds}$ が大きくなる。従って、負帰還における帰還量 $V$ は移動度 $\mu$ が大きくなるほど大きくなる。図6(B)に示すように、移動度 $\mu$ の大きな画素Aの帰還量 $V_1$ は、移動度の小さな画素Bの帰還量 $V_2$ に比べて大きい。

## 【0078】

そこで、移動度補正処理によって駆動トランジスタ22のドレイン-ソース間電流 $I_{ds}$ に応じた帰還量 $V$ でゲート-ソース間電圧 $V_{gs}$ に負帰還をかけることにより、移動度 $\mu$ が大きいほど負帰還が大きくかかることになる。その結果、移動度 $\mu$ の画素毎のばらつきを抑制することができる。30

## 【0079】

具体的には、移動度 $\mu$ の大きな画素Aで帰還量 $V_1$ の補正をかけると、ドレイン-ソース間電流 $I_{ds}$ は $I_{ds1}$ から $I_{ds1}$ まで大きく下降する。一方、移動度 $\mu$ の小さな画素Bの帰還量 $V_2$ は小さいために、ドレイン-ソース間電流 $I_{ds}$ は $I_{ds2}$ から $I_{ds2}$ までの下降となり、それ程大きく下降しない。結果的に、画素Aのドレイン-ソース間電流 $I_{ds1}$ と画素Bのドレイン-ソース間電流 $I_{ds2}$ とはほぼ等しくなるために、移動度 $\mu$ の画素毎のばらつきが補正される。

## 【0080】

以上をまとめると、移動度 $\mu$ の異なる画素Aと画素Bがあった場合、移動度 $\mu$ の大きい画素Aの帰還量 $V_1$ は移動度 $\mu$ の小さい画素Bの帰還量 $V_2$ に比べて大きくなる。つまり、移動度 $\mu$ が大きい画素ほど帰還量 $V$ が大きく、ドレイン-ソース間電流 $I_{ds}$ の減少量が大きくなる。40

## 【0081】

従って、駆動トランジスタ22のドレイン-ソース間電流 $I_{ds}$ に応じた帰還量 $V$ で、ゲート-ソース間電圧 $V_{gs}$ に負帰還をかけることで、移動度 $\mu$ の異なる画素のドレイン-ソース間電流 $I_{ds}$ の電流値が均一化される。その結果、移動度 $\mu$ の画素毎のばらつきを補正することができる。すなわち、駆動トランジスタ22に流れる電流(ドレイン-ソース間電流 $I_{ds}$ )に応じた帰還量(補正量) $V$ で、駆動トランジスタ22のゲート-ソース

10

20

30

40

50

間電圧  $V_{gs}$  に対して、即ち、保持容量 24 に対して負帰還をかける処理が移動度補正処理となる。但し、上述したような閾値補正や移動度補正は、本発明において必須の動作ではなく、上述したような各種補正や発光等も、そのような動作やタイミングに限られるものではない。

#### 【0082】

##### [2-3. ボトムゲート構造とトップゲート構造]

ところで、上記構成の有機EL表示装置10において、画素20のトランジスタ、具体的には、駆動トランジスタ22及び書き込みトランジスタ23を形成するTFTは、構造面から、ボトムゲート構造とトップゲート構造とに大別される。ボトムゲート構造は、ゲート電極が半導体層に対して基板側に位置する構造である。トップゲート構造は、ゲート電極が半導体層に対して基板と反対側に位置する構造である。10

#### 【0083】

画素20のトランジスタとして、ボトムゲート構造のTFTを用いる場合、ゲート電極のメタル層とソース／ドレイン電極のメタル層との間には、半導体層と膜厚の薄い絶縁膜が介在する。従って、ゲート電極のメタル層とソース／ドレイン電極のメタル層とを対向配置させることで、これらメタル層-メタル層間に、膜厚の薄い絶縁膜を誘電体として容量を形成することができる。そして、このメタル層-メタル層間に絶縁膜を介して形成される容量を、画素20内に作り込む容量素子、例えば、有機EL素子21の等価容量の補助としての機能を持つ補助容量25として用いることができる。

#### 【0084】

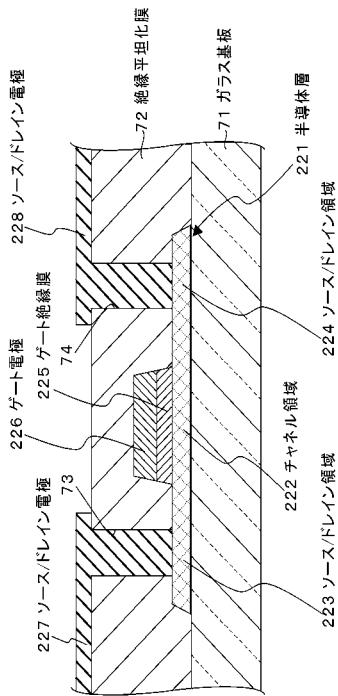

一方、画素20のトランジスタとして、トップゲート構造のTFTを用いる場合は、トランジスタ等を含む回路部の上の平坦化を図るために当該回路部の上に絶縁平坦化膜を形成し、その上にソース／ドレイン電極のメタル層を形成する構成が採られる。画素20のトランジスタが駆動トランジスタ22の場合について、図7を用いてより具体的に説明する。20

#### 【0085】

図7に示すように、基板、例えばガラス基板71の上に、駆動トランジスタ22の半導体層221が形成されている。この半導体層221において、その中央部の領域がチャネル領域222となり、当該チャネル領域222の両端部側の領域がソース／ドレイン領域223, 224となる。そして、半導体層221のチャネル領域222の上にゲート絶縁膜225が成膜され、当該ゲート絶縁膜225の上にゲート電極226が形成される。30

#### 【0086】

このようにして形成された駆動トランジスタ22を含むTFT回路部の上の平坦化を図るために、駆動トランジスタ22を含むTFT回路部の上には、絶縁平坦化膜72が形成される。この絶縁平坦化膜72には、半導体層221の両端部のソース／ドレイン領域223, 224に臨むコンタクトホール73, 74が形成される。そして、平坦化膜72の上に、ソース／ドレイン電極237, 238が形成されるとともに、コンタクトホール73, 74に配線材料（電極材料）が埋め込まれることによってソース／ドレイン電極237, 238とソース／ドレイン領域223, 224とが電気的に接続されている。40

#### 【0087】

上述したように、画素20のトランジスタとして、トップゲート構造のTFTを用いる場合は、絶縁平坦化膜72は、主に平坦化を目的とするものであることから、その膜厚についてはゲート絶縁膜225の膜厚に比べて非常に厚くならざるを得ない。そして、絶縁平坦化膜72の膜厚が厚いと、ゲート電極226のメタル層とソース／ドレイン電極237, 238のメタル層との間に容量を形成することはできない。

#### 【0088】

このような理由から、画素20内に作り込む容量素子を、メタル層-メタル層間以外に形成することができれば、画素20の断面構造の自由度を上げることができる。この点については、画素20のトランジスタとして、トップゲート構造のTFTを用いる場合に限らず、ボトムゲート構造のTFTを用いる場合においても同様のことと言える。50

## 【0089】

&lt;2. 実施形態の説明&gt;

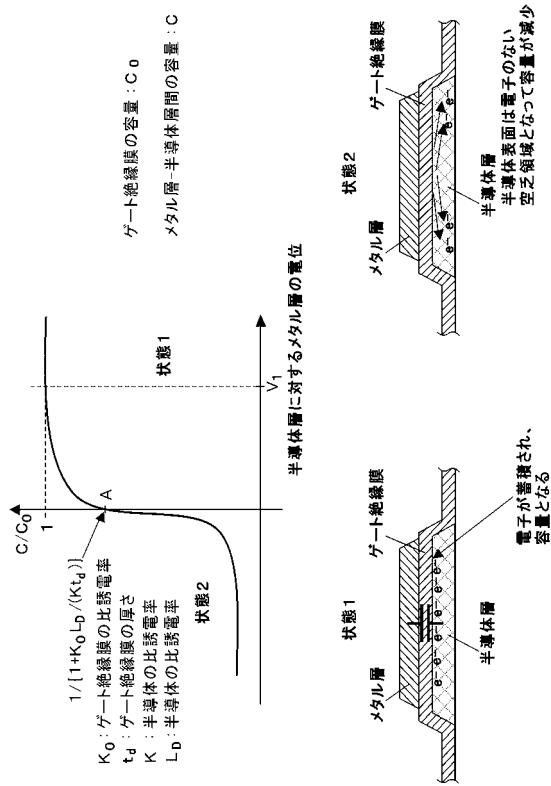

本開示の実施形態では、画素20の断面構造の自由度を上げるために、トランジスタのゲート電極と同じ層のメタル層と、トランジスタのソース／ドレイン領域を形成する半導体層との間に、画素内に作り込む容量素子を形成する構成を探る。メタル層・半導体層間に容量素子を形成するには、メタル層に電圧を印加することが必要となる。メタル層・半導体層間に容量素子を形成するに当たって、メタル層に電圧を印加する理由について、図8を用いて以下に説明する。

## 【0090】

図8には、画素20を駆動する際の動作のような周波数が高い動作での半導体層とメタル層とのC(容量) - V(電圧)特性を示す。図8のC-V特性において、横軸は半導体層に対するメタル層の電位を表わしている。また、縦軸はゲート絶縁膜の容量を $C_0$ とし、メタル層・半導体層間に容量素子を形成するときの両者の比 $C/C_0$ を表わしている。

## 【0091】

図8のC-V特性において、特性カーブが縦軸と交わる点Aの $C/C_0$ は、次式で表わされる

$$A(C/C_0) = 1 / \{ 1 + K_0 L_D / (K t_d) \}$$

上記の式において、 $K_0$ はゲート絶縁膜の比誘電率、 $t_d$ はゲート絶縁膜の厚さ、 $K$ は半導体の比誘電率、 $L_D$ はキャリアの遮蔽距離である。

## 【0092】

ここで、画素20のトランジスタが例えばNチャネル型のMOSトランジスタである場合について考える。

## 【0093】

Nチャネル型のMOSトランジスタの場合、半導体層に対してメタル層に十分高い電圧を印加すると、図8の状態1に示すように、半導体層の表面に電子が蓄積される、即ち、半導体層の表面にチャネルが形成される。これにより、半導体層とメタル層との間に介在するゲート絶縁膜を誘電体として容量が形成される。メタル層に印加する電圧は、半導体層の表面に十分にチャネルが形成されるだけの電圧ということになる。

## 【0094】

図8のC-V特性において、 $V_1$ はゲート絶縁膜の容量 $C_0$ が見えるようになる電圧値、換言すれば、誘電体であるゲート絶縁膜の容量 $C_0$ がメタル層・半導体層間に容量 $C$ となる(即ち、 $C/C_0 = 1$ )電圧値である。一方、半導体層に対してメタル層に低い電圧を印加すると、図8の状態2に示すように、半導体層の表面には電子のない空乏領域が広がる。これにより、半導体層とメタル層との間にゲート絶縁膜を誘電体として形成される容量の容量値が小さくなる。

## 【0095】

上述したことから明らかなように、ゲート絶縁膜を挟んでメタル層と半導体層とが対向して配置されている画素構造においても、メタル層に電圧を印加することで、半導体層の表面にチャネルが形成されるため、ゲート絶縁膜を誘電体として容量を形成することができる。そして、この容量を画素20内に作り込む容量素子、例えば、図2の画素回路における補助容量25として用いることで、画素20内に作り込む容量素子をメタル層・メタル層間に形成することができるため、画素20の断面構造の自由度を上げることができる。

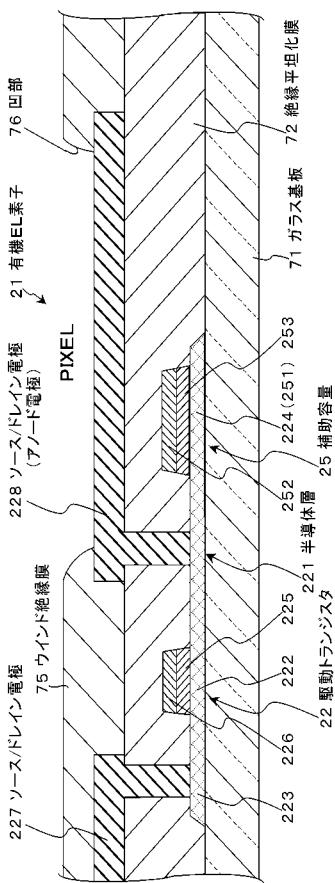

## 【0096】

図9は、本開示の実施形態に係る画素の断面構造を示す断面図である。図9には、図2の画素回路における駆動トランジスタ22及び補助容量25を図示している、即ち、メタル層・半導体層間にゲート絶縁膜を誘電体として形成される容量を補助容量25として用いる例を図示している。また、図9において、図7と同等部位には同一符号を付して示している。

## 【0097】

10

20

30

40

50

図7でも述べたように、ガラス基板71の上には、駆動トランジスタ22を含むTFT回路部が形成されている。駆動トランジスタ22は、ガラス基板71上に形成された半導体層221と、当該半導体層221のチャネル領域222と対向して設けられたゲート電極226と、半導体層221とゲート電極226との間に設けられたゲート絶縁膜225とによって構成されている。半導体層221において、チャネル領域222を挟む両端部がソース／ドレイン領域223，224である。

#### 【0098】

この駆動トランジスタ22を含むTFT回路部の上には、主に平坦化を目的として絶縁平坦化膜72が形成されている。この絶縁平坦化膜72の上には、ソース／ドレイン電極237，238を含む配線層が形成されている。本例の場合、駆動トランジスタ22の一方のソース／ドレイン電極238は、有機EL素子21のアノード電極を兼ねる構成となっている。ソース／ドレイン電極237，238を含む配線層の上にはウインド絶縁膜75が形成されている。そして、ウインド絶縁膜75の開口部（凹部）76に有機EL素子21の有機層（図示せず）が形成され、ウインド絶縁膜75の上には有機EL素子21のカソード電極（図示せず）が全画素共通に形成される。

10

#### 【0099】

かかる構成の画素構造において、半導体層221は、有機EL素子21の下方まで延在して設けられている。この半導体層221の一方の端部、即ち、ソース／ドレイン領域224は、補助容量25の一方の電極251を兼ねている。この一方の電極251と対向して他方の電極252が、駆動トランジスタ22のゲート電極226と同じメタル層として形成されている。一方の電極251と他方の電極252との間には、ゲート絶縁膜253が設けられている。

20

#### 【0100】

そして、先述したように、半導体層221、即ち、一方の電極251の表面に十分にチャネルが形成されるだけの電圧を、メタル層である他方の電極252に印加するようとする。これにより、半導体層221の表面に電子が蓄積されるため、ゲート絶縁膜253を誘電体として容量が形成され、当該容量が画素2に作り込む容量素子、本例では、補助容量25となる。

30

#### 【0101】

上述したように、補助容量25の一方の電極251を半導体層221で形成し、補助容量25の他方の電極252をメタル層で形成した場合において、当該他方の電極252に対する電圧の印加に関する具体的な実施例について以下に説明する。

30

#### 【0102】

##### [2-1. 実施例1]

図10は、実施例1に係る画素回路の回路図であり、図中、図2と同等部位には同一符号を付して示している。

#### 【0103】

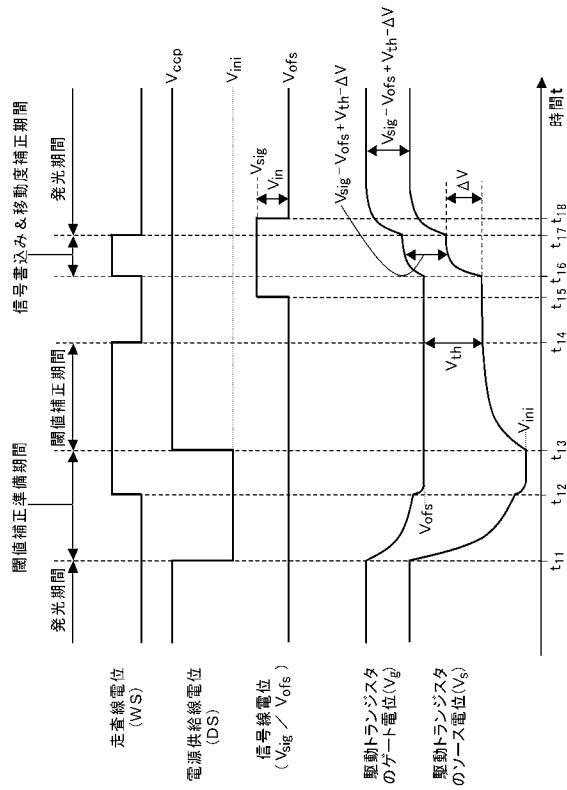

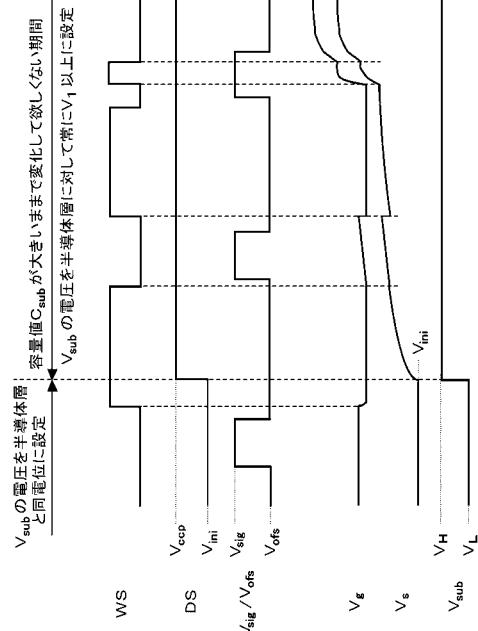

本実施例1に係る画素回路では、補助容量25の他方の電極を、図2の画素回路の場合のように、接地レベルの共通電源供給線34に接続するのではなくオープン状態とし、当該他方の電極に対して、外部の電源部（図示せず）から一定の電圧 $V_{sub}$ を与える構成を採っている。

40

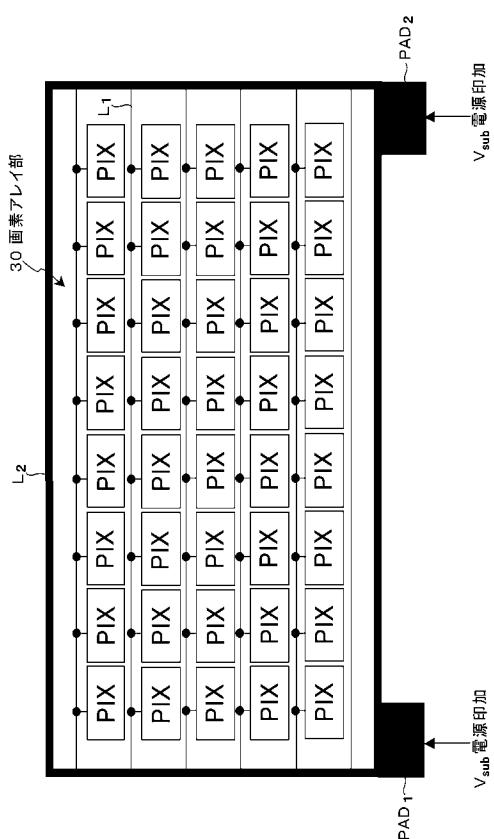

#### 【0104】

補助容量25の他方の電極に対して外部から一定の電圧 $V_{sub}$ を与えるためのパネルレイアウト例を図11に示す。図11に示すように、画素回路の補助容量25の他方の電極に行単位で繋がる電圧供給ライン $L_1$ を、画素アレイ部30の外周部で束ねて、画素アレイ部30の周りに例えば環状に共通電圧供給ライン $L_2$ を形成する。そして、環状の共通電圧供給ライン $L_2$ に繋がるパッド $PAD_1$ ,  $PAD_2$ をパネルの左右両端部側に形成し、これらパッド $PAD_1$ ,  $PAD_2$ 、共通電圧供給ライン $L_2$ 、及び、電圧供給ライン $L_1$ を通して補助容量25の他方の電極に対して、パネル外部の電源部（図示せず）から一定の電圧 $V_{sub}$ を与えるようにする。

50

## 【0105】

このように、特に、パネルの左右両端部側のパッド P A D<sub>1</sub>, P A D<sub>2</sub>から環状の共通電圧供給ライン L<sub>2</sub>に対して電圧を与えるようにすることで、各画素の補助容量 25 の他方の電極に対して一定の電圧 V<sub>sub</sub>を安定に供給できる。これによって、各画素の補助容量 25 の容量値 C<sub>sub</sub>のばらつきを抑えることができるため、安定した補助容量 25 の容量値 C<sub>sub</sub>で画素回路を駆動することが可能になる。

## 【0106】

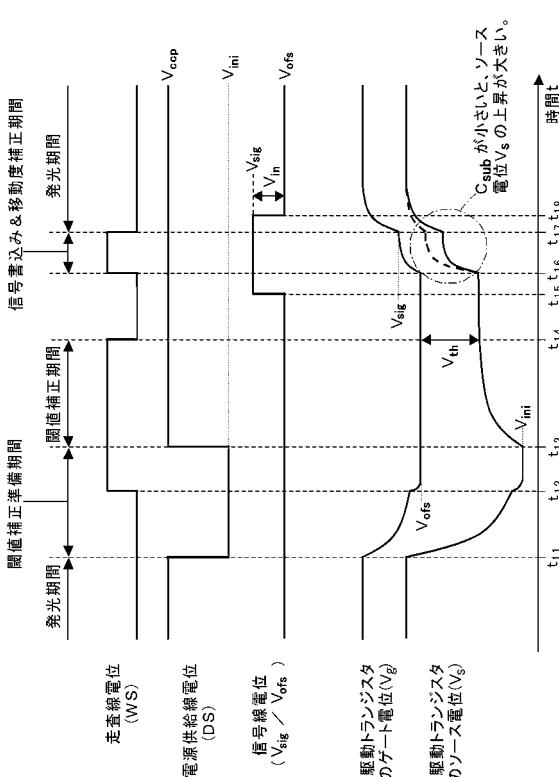

ここで、外部から与える一定の電圧 V<sub>sub</sub>としては、高階調の映像信号の書き込み時の駆動トランジスタ 22 のソース電位に対して、先述した電圧値 V<sub>1</sub>、即ち、ゲート絶縁膜の容量 C<sub>0</sub>が見えるようになる電圧値 V<sub>1</sub>以上の電圧である必要がある。もし、駆動トランジスタ 22 のソース電位、即ち、半導体層の電位に対して、補助容量 25 の他方の電極の電位、即ち、メタル層の電位が低くなってしまうと、補助容量 25 の容量値 C<sub>sub</sub>が減少するため、画素 20 の発光輝度が低下する。10

## 【0107】

ここで、半導体層の電位に対してメタル層の電位が低くなることで、輝度が低下するメカニズムについて、図 12 のタイミング波形図を用いて説明する。

## 【0108】

信号書き込み & 移動度補正時に補助容量 25 の容量値 C<sub>sub</sub>が規定値よりも小さいと、図 12 に破線で示すように、駆動トランジスタ 22 のゲートに映像信号の信号電圧 V<sub>sig</sub>を書き込んだときのソース電圧 V<sub>s</sub>の上昇が、大きくなる。これにより、発光直前の駆動トランジスタ 22 のゲート - ソース間電圧 V<sub>gs</sub>が小さくなってしまうために、有機 EL 素子 21 の輝度が低下する。20

## 【0109】

ここで、有機 EL 素子 21 の等価容量の容量値を C<sub>oled</sub>とし、保持容量 24 の容量値を C<sub>s</sub>とすると、信号書き込み時の駆動トランジスタ 22 のソース電圧 V<sub>s</sub>の上昇量 V<sub>s</sub>は次式で表わされる。

$$V_s = (V_{sig} - V_{ofs}) / (C_s + C_{sub} + C_{oled})$$

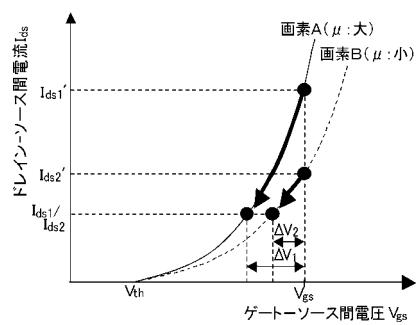

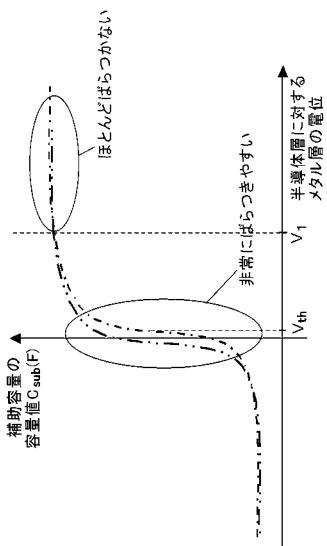

## 【0110】

本実施例 1 に係る画素回路では、補助容量 25 の他方の電極に対して一定の電圧 V<sub>sub</sub>を与えるようにしているので問題ないのであるが、もし、発光期間中に補助容量 25 の容量値 C<sub>sub</sub>が大から小に変動してしまうと、有機 EL 素子 21 の特性がデプレッションにシフトしたのと同じ効果を持つことになる。これにより、有機 EL 素子 21 の動作点が変動してしまう。そして、有機 EL 素子 21 の動作点が画素毎にばらつくと輝度ムラになってしまう。30

## 【0111】

ここで、有機 EL 素子 21 の動作点が画素毎にばらつくと輝度ムラになるメカニズムについて、図 13 及び図 14 を用いて説明する。

## 【0112】

半導体容量の容量特性は、図 13 に示すように、閾値電圧 V<sub>th</sub>付近の容量値が電圧によって大きく変わるところでばらつきやすい。そのため、補助容量 25 の他方の電極の電圧 V<sub>sub</sub>が半導体層の電位、即ち、駆動トランジスタ 22 のソース電位 V<sub>s</sub>に対して閾値電圧 V<sub>th</sub>付近になってしまふと、補助容量 25 の容量値 C<sub>sub</sub>が大きい画素と、当該容量値 C<sub>sub</sub>が小さい画素とが同一パネル内に混在することになる。図 13 において、補助容量 25 の容量値 C<sub>sub</sub>が大きい画素の特性を一点鎖線で示し、補助容量 25 の容量値 C<sub>sub</sub>が小さい画素の特性を二点鎖線で示している。40

## 【0113】

そして、補助容量 25 の容量値 C<sub>sub</sub>が大きい画素については、図 14 に一点鎖線で示すように、駆動トランジスタ 22 のソース電圧 V<sub>s</sub>の上昇量が小さいため輝度が高くなる。一方、補助容量 25 の容量値 C<sub>sub</sub>が小さい画素については、図 14 に二点鎖線で示すように、駆動トランジスタ 22 のソース電圧 V<sub>s</sub>の上昇量が小さいため輝度が低くなる。50

このように、同一パネル内に輝度が高い画素と輝度が低い画素とが混在することになるため、当該輝度のばらつきが輝度ムラとして視認される。

#### 【0114】

##### [2-2. 実施例2]

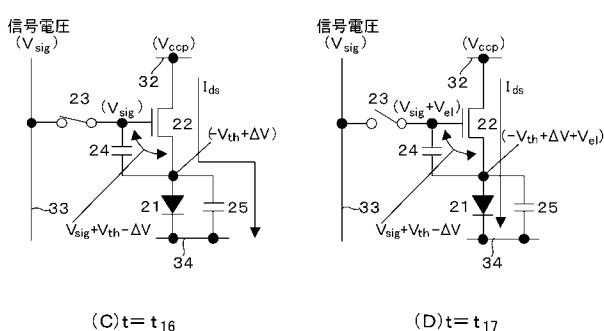

次に、実施例2に係る画素回路について説明する。実施例2に係る画素回路は回路構成として、図10に示した実施例1に係る画素回路と同じ回路構成を採る。すなわち、補助容量25の他方の電極をオープン状態とする。そして、実施例1では、補助容量25の他方の電極に対して一定の電圧 $V_{sub}$ を与えるようにしていたのに対して、実施例2では、当該他方の電極に対して与える電圧 $V_{sub}$ をパルス化する構成を採る。

#### 【0115】

具体的には、図15のタイミング波形図に示すように、補助容量25の容量値 $C_{sub}$ が大きいまま変化して欲しくない期間では、パルス化された電圧 $V_{sub}$ を高電圧 $V_H$ とする。ここで、高電圧 $V_H$ は、先述したことから明らかなように、高階調の映像信号の書き込み時の駆動トランジスタ22のソース電位に対して電圧値 $V_1$ 以上の電圧である。補助容量25の容量値 $C_{sub}$ が大きいまま変化して欲しくない期間は、電源供給線32の電位DSが第1電源電位 $V_{ccp}$ となる期間である。そして、補助容量25の容量値 $C_{sub}$ が大きいまま変化して欲しくない期間以外の期間では、パルス化された電圧 $V_{sub}$ を低電圧 $V_L$ とする。

#### 【0116】

半導体層とメタル層との間に形成される容量は、メタル層に電圧を印加し続けると、特性がエンハンスマントにシフトしてしまうことから信頼性が懸念される。また、エンハンスマントにシフトするスピードも画素によって違うため、当該スピードの違いによって画素間で容量値にばらつきが生じる。

#### 【0117】

このような理由から、電圧 $V_{sub}$ をパルス化し、メタル層に電圧を印加し続けないようにする、換言すれば、補助容量25の両端間に対する電圧の印加時間をできるだけ短くすることで、補助容量25の信頼性を確保することができる。

#### 【0118】

特に、有機EL素子21の消光期間では、駆動トランジスタ22のソース電位 $V_S$ が電源供給線32の電位DSの第2電源電位 $V_{ini}$ となることから、パルス化された電圧 $V_{sub}$ の低電圧 $V_L$ を第2電源電位 $V_{ini}$ とする。このように、補助容量25の容量値 $C_{sub}$ が大きいまま変化して欲しくない期間以外の期間では、補助容量25の他方の電極の電位を第2電源電位 $V_{ini}$ に落とすことにより、補助容量25の両端間の電圧は0Vとなる。そうすることで、補助容量25の信頼性をより確実に確保できるため、容量の信頼性に起因する輝度ムラや輝度低下を防ぐことができる。

#### 【0119】

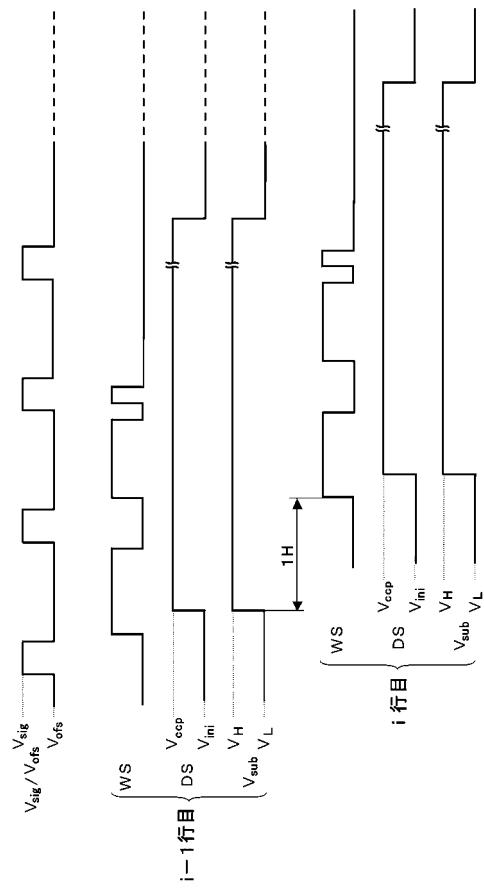

図16は、実施例2に係る駆動タイミング例を示すタイミング波形図である。図16には、i-1行目とi行目の2つの画素行(ライン)についての走査線31の電位(走査信号)WS、電源供給線32の電位DS、及び、パルス化された電圧 $V_{sub}$ の各波形を示している。

#### 【0120】

図16に示すように、パルス化された電圧 $V_{sub}$ については、1ライン(1行)毎に1H(1水平期間)ずらし、また、電源供給線32の電位DSに同期させることが望ましい。そして、上述したように、パルス化された電圧 $V_{sub}$ の高電圧 $V_H$ を、高階調の映像信号の書き込み時の駆動トランジスタ22のソース電位に対して電圧値 $V_1$ 以上の電圧とし、低電圧 $V_L$ を、電源供給線32の電位DSの第2電源電位 $V_{ini}$ とする。

#### 【0121】

補助容量25の他方の電極に対してパルス化された電圧 $V_{sub}$ を供給する、実施例2に係る駆動タイミング例を実現するためのパネル構成例を図17に示す。

#### 【0122】

図17に示すように、走査回路として、書き込み走査回路40及び電源供給走査回路50

10

20

30

40

50

に加えて、補助容量 25 を生成するための容量生成走査回路 80 を例えば表示パネル 70 上に設けるようにする。この容量生成走査回路 80 は、電源供給走査回路 50 の動作、具体的には、電源供給線 32 の電位 DS に同期に同期して、画素行を順に走査しつつパルス化された電圧  $V_{sub1} \sim V_{subm}$  を順次出力し、走査線 35<sub>1</sub> ~ 35<sub>m</sub> を通して各画素 20 の補助容量 25 の他方の電極に供給する。

#### 【0123】

##### (実施例 2 の変形例)

実施例 2 では、補助容量 25 の他方の電極に対してパルス化された電圧  $V_{sub}$  を供給する駆動タイミング例を実現するために、補助容量 25 を生成するための容量生成走査回路 80 を専用に備える構成を探っているが、その変形例として次の構成を探ることも可能である。すなわち、電圧  $V_{sub}$  をパルス化するという観点からすれば、図 18 に示すように、前段（1行前）の画素行に属する電源供給線 32 の電位 DS をパルス化された電圧  $V_{su}$  として供給する構成を探ることも可能である。これを実現するには、補助容量 25 の他方の電極を前段の画素行に属する電源供給線 32 に接続すればよい。

10

#### 【0124】

何故ならば、電源供給線 32 の電位 DS の高電位側が高階調の映像信号の書き込み時の駆動トランジスタ 22 のソース電位に対して電圧値  $V_1$  以上であり、低電位側が第 2 電源電位  $V_{ini}$  であり、電源供給線 32 の電位 DS は、先述した電圧  $V_{sub}$  の電位の条件を満足するからである。この場合、補助容量 25 の他方の電極に印加される電圧  $V_{sub}$  のタイミングが実施例 2 の場合のタイミングに対して 1H のずれが生じるが、当該 1H のずれを無視できる程度のものであるとすれば、基本的に、実施例 2 の場合と同様の作用、効果を得ることが可能になる。

20

#### 【0125】

##### <3. 適用例>

上記実施形態では、駆動トランジスタ 22 及び書き込みトランジスタ 23 の 2 つのトランジスタと、保持容量 24 及び補助容量 25 の 2 つの容量素子を有する画素回路に適用した場合を例に挙げて説明したが、本開示は当該画素回路への適用に限られるものではない。すなわち、更に多い数のトランジスタを有する画素回路や、更に多い数の容量素子を有する画素回路等に対しても適用可能である。

30

#### 【0126】

また、上記実施形態においては、有機 EL 表示装置に適用した場合を例に挙げて説明したが、本開示はこの適用例に限られるものではない。具体的には、本開示は、無機 EL 素子、LED 素子、半導体レーザー素子など、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子（発光素子）を用いた表示装置全般に対して適用可能である。更には、電流駆動型の電気光学素子を用いた表示装置以外にも、液晶表示装置やプラズマ表示装置等、画素内に容量素子を有する構成を探る表示装置全般に対して適用可能である。

30

#### 【0127】

##### <4. 電子機器>

以上説明した本開示による表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示部（表示装置）に適用できる。一例として、図 19 ~ 図 23 に示す様々な電子機器、例えば、デジタルカメラ、ノート型パソコン、携帯電話等の携帯端末装置、ビデオカメラなどの表示部に適用することが可能である。

40

#### 【0128】

先述した実施形態の説明から明らかなように、本開示による表示装置によれば、画素内に作り込む容量素子を、メタル層 - 半導体層間に容量素子を形成するに当たって、容量素子の信頼性を確保し、輝度ムラや輝度低下を防ぐことができる。従って、あらゆる分野の電子機器において、その表示部として本開示による表示装置を用いることで、高品位の表示画像を得ることができる。

50

## 【0129】

本開示による表示装置は、封止された構成のモジュール形状のものをも含む。一例として、画素アレイ部に透明なガラス等の対向部が貼り付けられて形成された表示モジュールが該当する。尚、表示モジュールには、外部から画素アレイ部への信号等を入出力するための回路部やFPC（フレキシブルプリントサーキット）等が設けられていてもよい。

## 【0130】

以下に、本開示が適用される電子機器の具体例について説明する。

## 【0131】

図19は、本開示が適用されるテレビジョンセットの外観を示す斜視図である。本適用例に係るテレビジョンセットは、フロントパネル102やフィルターガラス103等から構成される映像表示画面部101を含み、その映像表示画面部101として本開示による表示装置を用いることにより作製される。10

## 【0132】

図20は、本開示が適用されるデジタルカメラの外観を示す斜視図であり、(A)は表側から見た斜視図、(B)は裏側から見た斜視図である。本適用例に係るデジタルカメラは、フラッシュ用の発光部111、表示部112、メニュースイッチ113、シャッターボタン114等を含み、その表示部112として本開示による表示装置を用いることにより作製される。

## 【0133】

図21は、本開示が適用されるノート型パーソナルコンピュータの外観を示す斜視図である。本適用例に係るノート型パーソナルコンピュータは、本体121に、文字等を入力するとき操作されるキーボード122、画像を表示する表示部123等を含み、その表示部123として本開示による表示装置を用いることにより作製される。20

## 【0134】

図22は、本開示が適用されるビデオカメラの外観を示す斜視図である。本適用例に係るビデオカメラは、本体部131、前方を向いた側面に被写体撮影用のレンズ132、撮影時のスタート/ストップスイッチ133、表示部134等を含み、その表示部134として本開示による表示装置を用いることにより作製される。

## 【0135】

図23は、本開示が適用される携帯端末装置、例えば携帯電話機を示す外観図であり、(A)は開いた状態での正面図、(B)はその側面図、(C)は閉じた状態での正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。本適用例に係る携帯電話機は、上側筐体141、下側筐体142、連結部(ここではヒンジ部)143、ディスプレイ144、サブディスプレイ145、ピクチャーライト146、カメラ147等を含んでいる。そして、ディスプレイ144やサブディスプレイ145として本開示による表示装置を用いることにより、本適用例に係る携帯電話機が作製される。30

## 【0136】

## &lt;5. 本開示の構成&gt;

(1) 電気光学素子及びトランジスタを含む画素が配置されて成り、

前記画素は、前記トランジスタのゲート電極と同じ層のメタル層と、前記トランジスタのソース領域及びドレイン領域を形成する半導体層との間に、前記メタル層に電圧が印加されることによって形成される容量素子を有する40

表示装置。

(2) 前記メタル層に印加する電圧は、前記半導体層の表面にチャネルを形成できる電圧である

前記(1)に記載の表示装置。

(3) 前記メタル層に印加する電圧は、前記メタル層と前記半導体層との間の誘電体の容量を $C_0$ 、前記メタル層と前記半導体層との間の容量を $C$ とするとき、 $C / C_0 = 1$ となる電圧値以上である

前記(2)に記載の表示装置。

10

20

30

40

50

(4) 前記容量素子は、前記電気光学素子の等価容量の補助として用いられる

前記(1)から前記(3)のいずれかに記載の表示装置。

(5) 前記トランジスタは、前記電気光学素子に対して直列に接続され、当該電気光学素子を駆動する駆動トランジスタであり、

前記容量素子は、その一方の電極が前記駆動トランジスタのソース／ドレイン電極に接続されている

前記(4)に記載の表示装置。

(6) 前記容量素子は、前記メタル層に印加する電圧として一定の電圧が他方の電極に与えられる

前記(5)に記載の表示装置。

10

(7) 前記画素は、行列状に配置されて画素アレイ部を構成しており、

前記一定の電圧は、前記容量素子の他方の電極に行単位で繋がる電圧供給ラインを通して前記容量素子の他方の電極に与えられる

前記(6)に記載の表示装置。

(8) 前記容量素子の他方の電極に行単位で繋がる電圧供給ラインを前記画素アレイ部の外周部で束ねることによって当該画素アレイ部の周りに環状の共通電圧供給ラインが形成されており、

前記一定の電圧は、前記環状の共通電圧供給ライン及び前記電圧供給ラインを通して前記容量素子の他方の電極に与えられる

前記(7)に記載の表示装置。

20

(9) 前記画素アレイ部が形成されるパネルの両端部側に、前記環状の共通電圧供給ラインに繋がるパッドが形成されており、

前記一定の電圧は、前記パッド、前記環状の共通電圧供給ライン及び前記電圧供給ラインを通して前記容量素子の他方の電極に与えられる

前記(8)に記載の表示装置。

(10) 前記容量素子は、前記メタル層に印加する電圧としてパルス化された電圧が他方の電極に与えられる

前記(5)に記載の表示装置。

(11) 前記駆動トランジスタに電源を供給する電源供給線の電位は、前記電気光学素子を発光駆動する電流を供給するための第1電源電位と、前記電気光学素子に対して逆バイアスを掛けるための第2電源電位とで切り替え可能となっており、

30

前記パルス化された電圧は、前記電源供給線の電位が前記第1電源電位のときに高電位になる

前記(10)に記載の表示装置。

(12) 前記パルス化された電圧は、低電位側が前記第2電源電位に設定されている

前記(11)に記載の表示装置。

(13) 前記画素は、行列状に配置されて画素アレイ部を構成しており、

前記パルス化された電圧は、行単位で前記容量素子の他方の電極に与えられる

前記(10)から前記(12)のいずれかに記載の表示装置。

(14) 前記パルス化された電圧は、前記画素アレイ部を行単位に走査する走査回路から出力される

40

前記(13)に記載の表示装置。

(15) 前記パルス化された電圧は、前段の画素行に属する前記電源供給線から与えられる

前記(13)に記載の表示装置。

(16) 前記容量素子の他方の電極は、前段の画素行に属する前記電源供給線に接続されている

前記(15)に記載の表示装置。

(17) 電気光学素子及びトランジスタを含む画素が配置されて成り、

前記画素は、前記トランジスタのゲート電極と同じ層のメタル層と、前記トランジスタ

50

のソース領域及びドレイン領域を形成する半導体層との間に、前記メタル層に電圧が印加されることによって形成される容量素子を有する

表示装置を有する電子機器。

【符号の説明】

【0 1 3 7】

10...有機EL表示装置、20...画素(画素回路)、21...有機EL素子、22...駆動トランジスタ、23...書き込みトランジスタ、24...保持容量、25...補助容量、30...画素アレイ部、31( $31_1 \sim 31_m$ )...走査線、32( $32_1 \sim 32_m$ )...電源供給線、33( $33_1 \sim 33_n$ )...信号線、34...共通電源供給線、40...書き込み走査回路、50...電源供給走査回路、60...信号出力回路、70...表示パネル、80...容量形成走査回路

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

(B)

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図 22】

## 【図 2 3】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 1 2 E

H 0 5 B 33/14 A

F ターム(参考) 3K107 AA01 BB01 CC33 CC41 DD39 EE03 FF04 HH05

5C080 AA06 AA07 BB05 CC03 DD05 FF11 JJ02 JJ03 JJ04 JJ05

JJ06 KK02 KK07 KK43 KK47

5C094 AA48 BA03 BA27 DA13 EA10 FB12 FB19 GA10

5C380 AA01 AA02 AA03 AB06 AB11 AB12 AB18 AB22 AB24 AB34

AB35 AB36 AB46 AC07 AC08 AC09 AC11 AC12 BA38 BA39

BB02 BE03 CA08 CA12 CB01 CB19 CB20 CB26 CC02 CC03

CC04 CC06 CC07 CC27 CC30 CC33 CC41 CC62 CC72 CC77

CD022 DA02 DA06 DA47 HA08